# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 554 128

51 Int. Cl.:

G01N 27/414 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

Fecha de presentación y número de la solicitud europea: 10.10.2011 E 11808312 (0)

Fecha y número de publicación de la concesión europea: 30.09.2015 EP 2625514

(54) Título: Dispositivo ISFET

(30) Prioridad:

08.10.2010 GB 201017023

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 16.12.2015

73) Titular/es:

DNAE GROUP HOLDINGS LIMITED (100.0%) Ugli Campus Block C 56 Wood Lane W127 SB London, GB

(72) Inventor/es:

TOUMAZOU, CHRISTOFER y AL-AHDAL, ABDULRAHMAN

(74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

## **DESCRIPCIÓN**

Dispositivo ISFET

### Campo de la invención

La presente invención se refiere a un dispositivo y a un procedimiento para conmutar una salida eléctrica de acuerdo con la concentración de iones de una muestra.

#### **Antecedentes**

En general los ISFET se construyeron para una medición (analógica) de tiempo continuo con circuitos de preprocesamiento analógicos alrededor de los mismos. Normalmente la conversión de analógico a digital es una de las etapas del procesamiento. Este es el caso en el que se necesita un continuo de valores. Sin embargo, hay muchas aplicaciones en las que se solicita una decisión de sí / no. Por ejemplo, en la hibridación del ADN y la detección de inserción SNP, es suficiente para detectar que un procedimiento se ha realizado o no con una respuesta sí / no (5) (6). Otras aplicaciones requieren simplemente una comparación entre las concentraciones de dos elementos químicos en una solución. Por ejemplo, si la creatinina es de mayor concentración que la urea o viceversa (7).

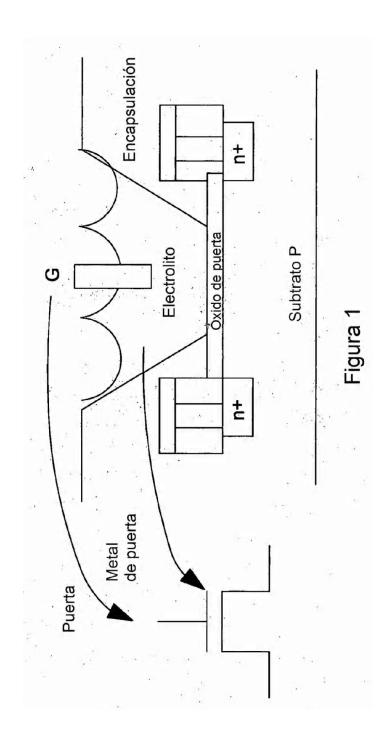

Un transistor de efecto de campo sensible a iones (ISFET) se compone de un transistor de efecto de campo (FET) cuya puerta está expuesta a cargas iónicas en un electrolito. Un electrodo de referencia se sumerge en la solución de electrolito que entra en contacto con el óxido de la puerta del transistor. Véase la figura 1. Por lo tanto, la combinación del electrolito y el electrodo de referencia desempeñan el papel de la puerta en un MOSFET normal. El óxido de la puerta convierte la membrana sensible a iones. Los modos de funcionamiento eléctricos de un FET pueden expresarse por:

20 Débil

5

10

15

$$I_{DS} = I_{DO} \frac{W}{L} e^{\left(\frac{V_{GS} - V_{t}}{nU_{T}}\right)}$$

Triodo de inversión

$$I_{DS} = \mu C_{ox} \frac{W}{L} \left[ (V_{gs} - V_t) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(1)

Región de saturación

$$I_{DS} = \frac{1}{2}\mu C_{ox} \frac{W}{L} (V_{GS} - V_t)^2 (1 + \lambda V_{DS})$$

25

40

Las caídas de tensión que surgen de las interacciones del electrodo de referencia, el electrolito y la membrana sensible a iones pueden verse como parte de o la tensión de origen de la puerta  $(V_{gs})$  o la tensión de umbral  $(V_t)$ . Esto se soporta por el hecho de que es su diferencia la que aparece en las relaciones MOSFET  $I_{d}$ - $V_{gs}$  en todas las regiones de funcionamiento, ecuación (1).

A partir de la analogía anterior, se debate si el electrodo de referencia desempeña de manera remota el papel de la puerta MOS (1). Por lo tanto, el electrolito desempeña el papel de la puerta de metal que entra en contacto con el óxido de la puerta. En el MOSFET, Vt se decide por el material de puerta, el dopaje del sustrato, su aislador y las cargas en este sistema, ecuación (2). Es una constante para cada dispositivo; y debido a que el procedimiento de fabricación está muy bien controlado, su variación a través de los dispositivos está bien controlada. Sin embargo, en el ISFET de acuerdo con esta analogía, el electrolito ha pasado a formar parte de este sistema haciendo su Vt en función de las propiedades del electrolito, ecuación (3) (1). La tensión umbral puede expresarse por:

MOSFET

$$V_{t} = \frac{\Phi_{M} - \Phi_{Sl}}{q} - \frac{Q_{ox} + Q_{SS} + Q_{B}}{C_{ox}} + 2\phi_{f}$$

(2)

ISFET

$$V_{t} = -\Psi + \chi^{sol} - \frac{\Phi_{Sl}}{q} - \frac{Q_{ox} + Q_{ss} + Q_{B}}{C_{ox}} + 2\phi_{f}$$

(3)

en la que:  $\phi_M$  es la función de trabajo del metal,  $\phi_{Si}$  es la función de trabajo de silíceo, q es la carga del electrón, Qox es la carga acumulada en el aislante de óxido, Qss es la carga atrapada en la interfaz de óxido de silicio, QB es la carga de agotamiento en la masa de silicio, Cox es la capacitancia de óxido de la puerta, y  $\phi_f$  define el inicio de la inversión en función de los niveles de dopaje de silicio. En la ecuación (3),  $\phi_M$  se sustituye tanto por el parámetro químico del potencial  $\psi$  de interfaz de la membrana-electrolito sensible a iones, como por el potencial de dipolo de

superficie del electrolito en contacto con la membrana  $X^{sol}$  sensible a iones. El primero es una función de la concentración de iones de electrolito, en el que el pH es una posible medida de la misma. El último es una constante. La ecuación (3) sugiere que la tensión de umbral del ISFET puede modificarse usando la concentración de iones de electrolito (1).

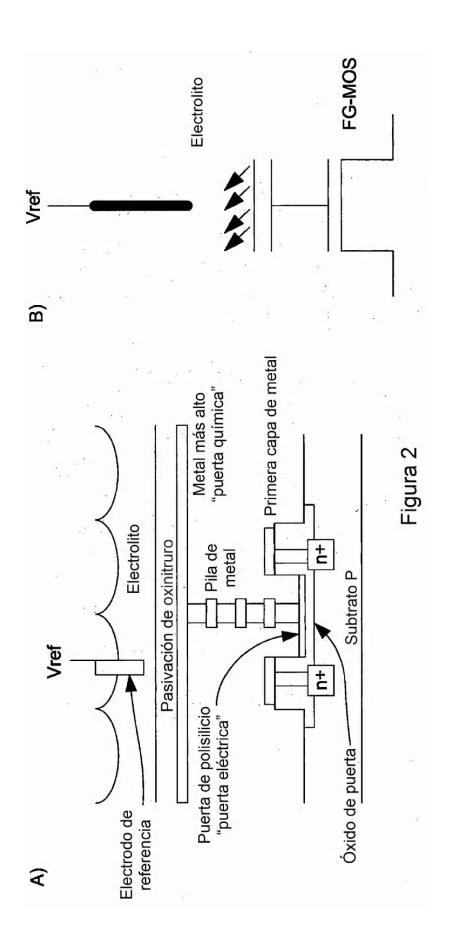

5 En 1999, Bausells y col. integraron un ISFET usando el procedimiento CMOS convencional de metal doble y único poli-siticon de 1μm de Atmel-ES2 (10). Ellos integraron un amplificador CMOS convencional en la misma matriz. Básicamente, el ISFET se dio, por primera vez, en una puerta de poli-silicio que era flotante y estaba conectada a la pila de metal hasta la capa de metal superior en la que se detectaron los iones a través de la pasivación del oxinitruro. Esta idea básica se realizó por otros y los ISFET se construyeron en diferentes procedimientos de CMOS comerciales con capas múltiples de metal (10) (11) (12).

Es interesante observar que la parte de transistor en este caso es efectivamente un FG-MOSFET y la parte sensible se parece a un condensador sensible a iones en el que el metal superior es una placa y el electrolito forma la segunda, mientras que la pasivación es la capa de aislamiento. Esto es muy similar al sensor de iones capacitivo tradicional que resulta si se elimina el electrodo de referencia.

La capacitancia de pasivación de la puerta del transistor puede considerarse dividida para hacer dos estructuras diferentes. Por lo tanto, la puerta de transistor del ISFET puede llamarse la "puerta eléctrica" y el metal más alto bajo la membrana sensible a iones podría llamarse la "puerta química".

Por lo tanto, V<sub>t</sub> es una constante dependiente del procedimiento dado por la ecuación (2). La dependencia química introducida en la ecuación (3) puede expresarse como parte de la tensión de puerta de flotación del ISFET dada por:

$$V_{FG} = V_{ref} - \Psi + \chi^{sol} + V_{Opass} \tag{4}$$

en la que,  $V_{\text{Qpass}}$  se debe a las cargas atrapadas en la capa de pasivación.

20

25

40

45

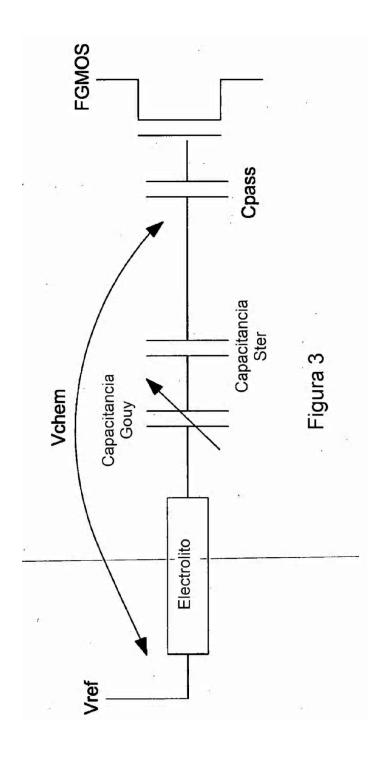

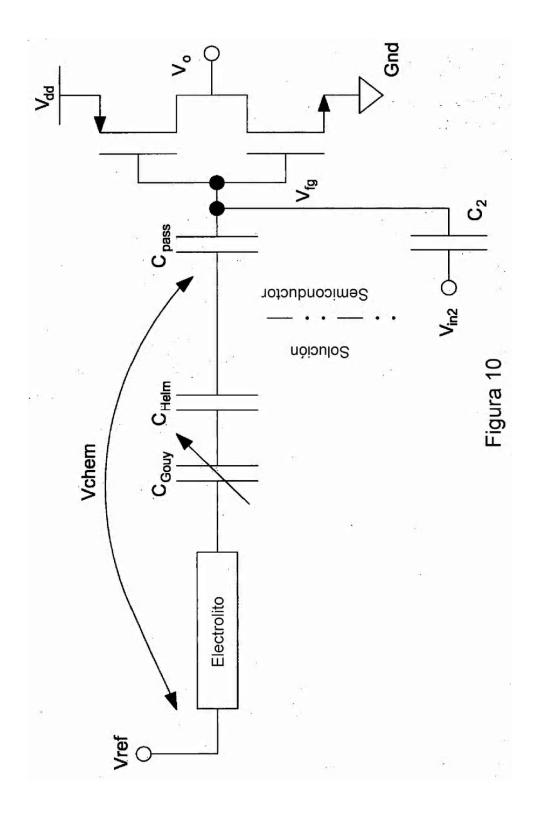

Usando el modelo de disociación de sitio y el modelo de doble capa de Gouy-Chapman-Stern, el ISFET puede modelarse como en la figura 2. En la que  $V_{\text{chem}}$  es la tensión química derivada a partir del electrolito y su interfaz para tanto el electrodo de referencia como para la membrana de detección de iones (6).

$$V_{chem} = \gamma + V_{Qpass} + 2.3\alpha U_T pH \tag{5}$$

En la que,  $\gamma$  es una agrupación de todos los términos independientes del pH a partir de las cargas atrapadas de pasivación que es  $V_{Qpass}$ .  $U_T$  es la tensión térmica normal, y  $\alpha$  es un parámetro de sensibilidad con valores entre 0 <  $\alpha$  < 1. Su máximo proporciona el límite teórico conocido como la sensibilidad de Nernstian proporcionado por 59,2 mV/pH a 25 °C (1).

La mayoría de las publicaciones sobre ISFET consideran Vt como un parámetro en función del pH. Los inventores han apreciado que desde un punto de vista de circuito puro, el ISFET es efectivamente un FGMOS convencional con su puerta acoplada de manera capacitiva a las tensiones superpuestas Vref y Vchem. Por lo tanto, se las considera que forman la entrada de puerta de flotación y se asume Vt como una constante, como un MOSFET convencional. Por lo tanto, un cambio de pH puede verse como una modulación de Vgs en lugar de Vt. Sin embargo, desde un punto de vista físico, no hay ningún cambio en el sistema y se mantiene el mismo análisis. Por lo tanto, las ecuaciones (1) y (2) siguen siendo válidas, la ecuación (3) no es más relevante, y la ecuación (5) representa la tensión química.

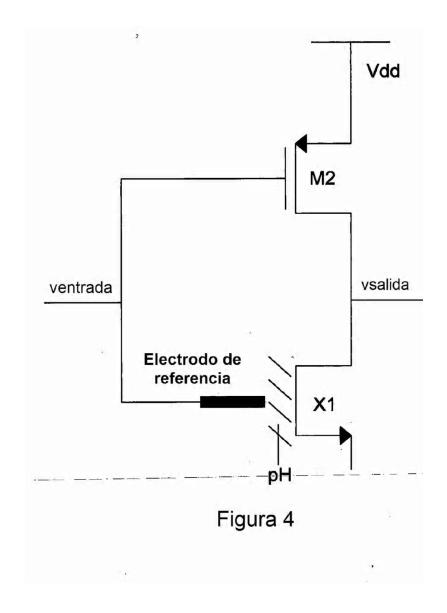

El primer intento de usar un ISFET para construir un inversor se debió al Dr. Shepherd y sus colegas (5) (16). La figura 4 muestra un ISFET como un NMOS en un amplificador inversor AB de clase convencional con el papel del PMOS realizado por un transistor normal. La entrada está conectada tanto a la puerta del PMOS (M2) como al electrodo de referencia del n-ISFET (X1). Por lo tanto, el umbral de conmutación del circuito cambia en proporción al pH de la solución.

Por lo tanto, los cambios de pH modulan la tensión de puerta del n-MOS, pero no la del p-MOS. Es decir, solo la mitad del par complementario es sensible al pH. El transistor de armar ve una entrada diferente a la del transistor de desarme, siendo la diferencia V<sub>chem</sub>.

Sin embargo, esto puede ser aceptable si no hay cargas atrapadas de deriva o de pasivación. Una  $V_t$  del ISFET puede tener una variación inicial, debido a las cargas atrapadas de pasivación, en el intervalo de unos pocos voltios (17) (12). Esto puede hacer la función de conmutación del circuito no operativa, especialmente si el n-ISFET tiene una tensión de umbral negativa.

Nishiguchi Katsuhiko y col. (Applied Physics Letters, volumen 94, nº 16, 21 de Abril de 2009, páginas 163106-163106) describen los ISFET de nanocables de Si con una puerta de flotación compartida.

#### Sumario de la invención

5

Los aspectos de la invención se exponen en las reivindicaciones adjuntas. De acuerdo con un primer aspecto, un primer dispositivo semiconductor para detectar un cambio en una concentración de iones de una muestra comprende una pluralidad de transistores de efecto de campo (FET) acoplados a una puerta de flotación común y a una capa de detección de iones expuesta a la muestra y acoplada a la puerta de flotación.

Durante el funcionamiento, se enciende o se apaga una corriente a través de los transistores en función de la magnitud de la concentración de iones en la muestra en la proximidad de la capa de detección en comparación con un umbral de conmutación.

El dispositivo puede construirse usando unos procedimientos de CMOS comerciales.

De acuerdo con un segundo aspecto, se proporciona un circuito para detectar una pluralidad de reacciones químicas y evaluar una función lógica que tiene el resultado de cada una de la pluralidad de reacciones químicas como sus entradas, comprendiendo el circuito al menos una cámara de reacción para cada una de la pluralidad de reacciones químicas, reacciones químicas que cambian una concentración de iones en la cámara de reacción. Cada cámara de reacción está provista de un dispositivo de acuerdo con el primer aspecto desvelado anteriormente, proporcionando cada dispositivo una señal de salida digital cuyo estado está en función de la concentración de iones de esa cámara, y en la que las salidas están acopladas entre sí para formar un circuito de procesamiento de señales digitales para evaluar una función lógica.

De acuerdo con un tercer aspecto, un procedimiento proporciona una salida que representa una concentración de un ion objetivo en una muestra. El procedimiento comprende proporcionar un conmutador CMOS que comprenda una pluralidad de transistores de efecto de campo (FET) acoplados a una puerta de flotación común y una capa de detección de iones expuesta a la muestra y acoplada a la puerta de flotación; exponiendo la capa sensible a iones a la muestra para conmutar un estado del conmutador CMOS a encendido o apagado; y emitir una señal desde el conmutador CMOS.

Usando una puerta de flotación común, el dispositivo puede conmutar de alta sensibilidad a cambios iónicos y de baja sensibilidad a otros componentes como una carga atrapada.

Modificando los circuitos inversores conocidos, los inventores han aumentado la sensibilidad por órdenes de magnitud. Los inversores excitados de alta sensibilidad de pH hacen posible detectar pequeños cambios de pH que de otro modo no serían factibles. Esto mejora las sensibilidades de medición y relaja las restricciones en los volúmenes y las concentraciones de muestra.

30 Este circuito puede usarse para realizar operaciones de monitorización de la reacción y umbralización del pH para una cámara de reacción. Su salida digital puede usarse para construir circuitos digitales convencionales con entradas procedentes de diferentes cámaras de reacción. Esto facilita la construcción de laboratorio basada en ISFET completamente digitales en aplicaciones de microplacas.

## Breve descripción de los dibujos

Las realizaciones específicas de la invención se describirán a continuación solamente a modo de ejemplo con referencia a las figuras adjuntas, en las que:

La figura 1 es una ilustración en sección transversal de un ISFET y análogamente al MOSFET;

La figura 2 es (A) una representación en sección transversal de un ISFET construido con un procedimiento CMOS convencional y, (B) su representación de circuito;

40 La figura 3 es un modelo de un ISFET;

La figura 4 es un inversor ISFET de la técnica anterior;

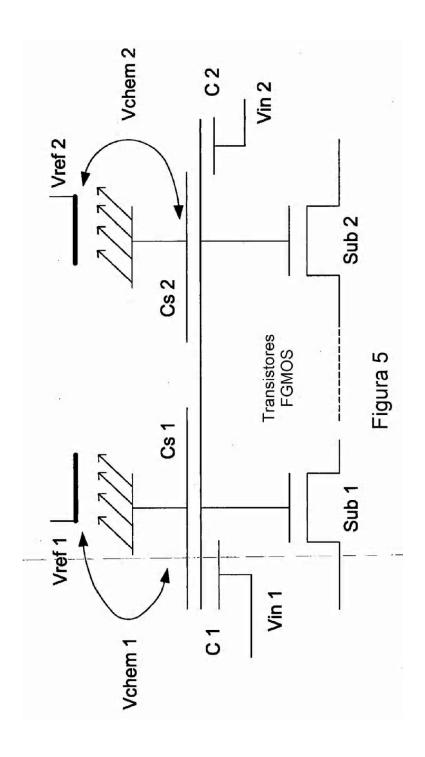

La figura 5 es una ilustración de un dispositivo sensible a iones generalizado con múltiples entradas;

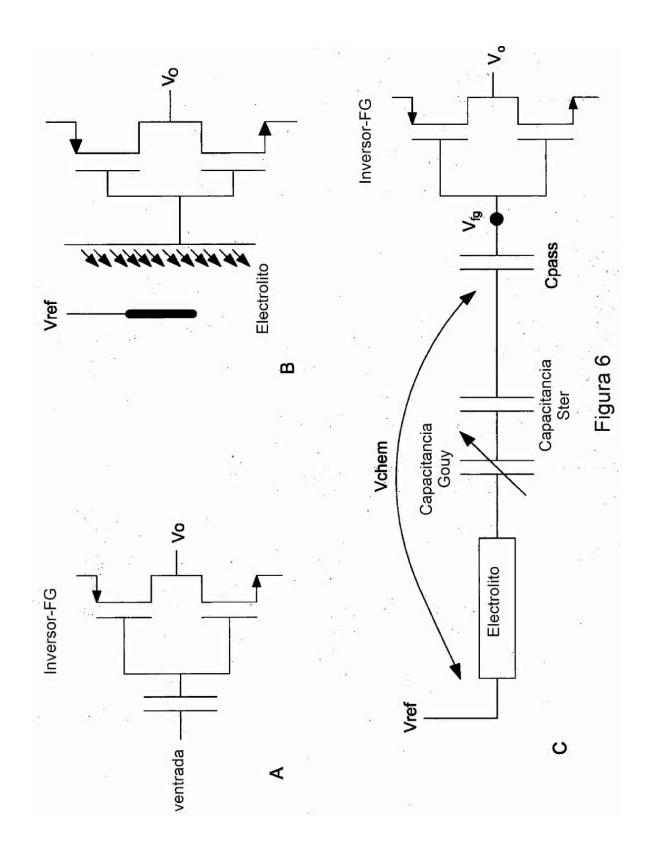

La figura 6 es (A) una representación esquemática de un FGMOS, (B) una representación esquemática de un inversor ISFET, (C) un circuito equivalente del inversor ISFET;

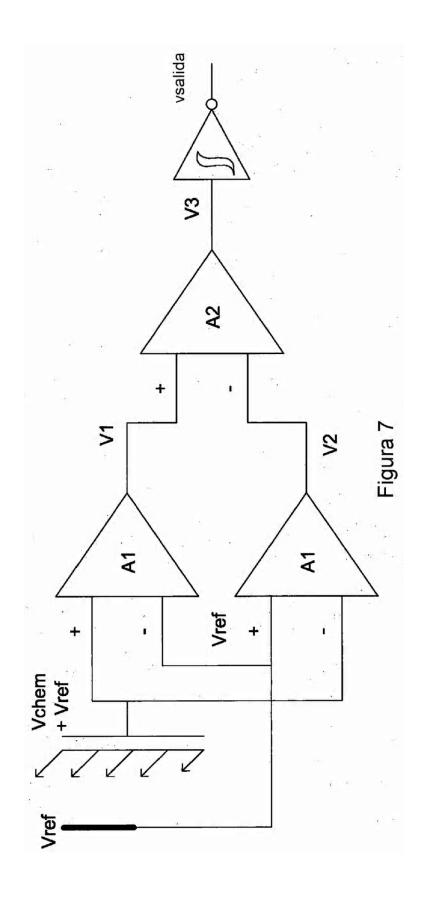

La figura 7 es una representación de circuito de un inversor químico amplificado;

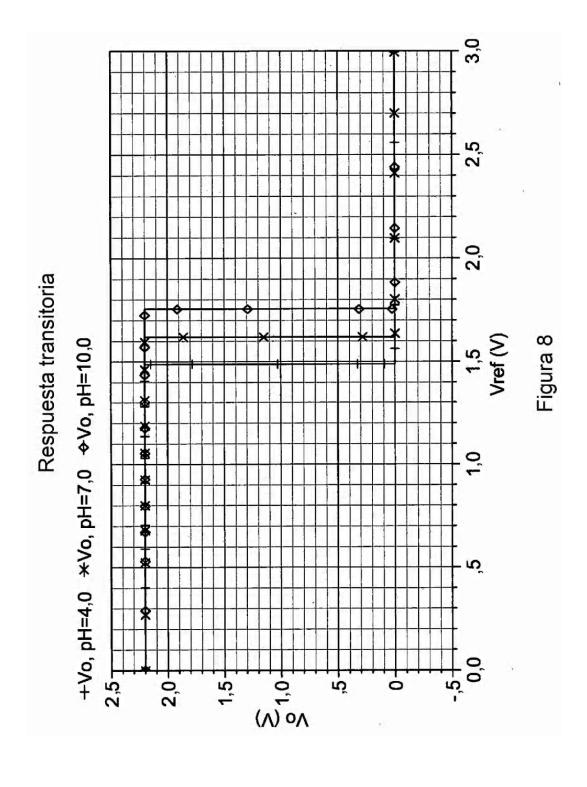

La figura 8 es una gráfica que muestra el punto de conmutación para un inversor ISFET;

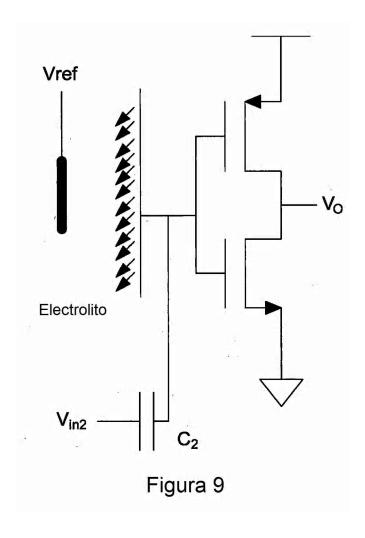

La figura 9 muestra un inversor ISFET con una segunda entrada;

La figura 10 es un modelo de un inversor químico basado en un ISFET de sensibilidad mejorada;

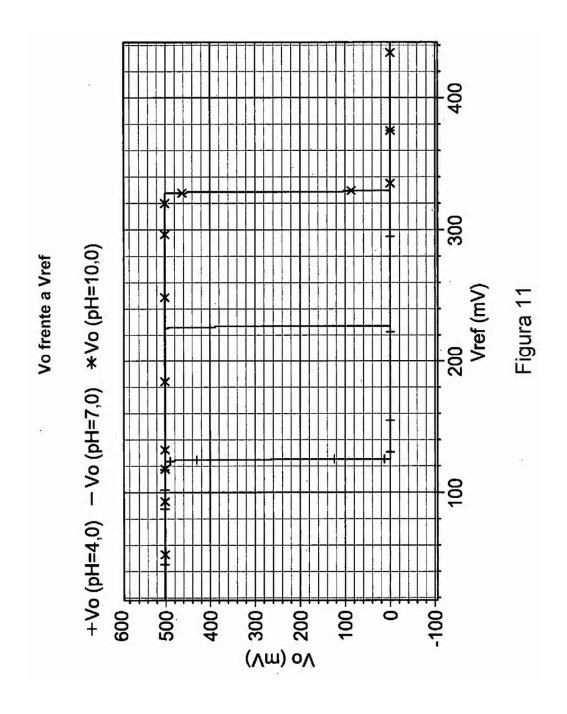

La figura 11 es una gráfica que muestra la salida de la Vref barrida para el circuito de la figura 10 con la segunda entrada Vin2 constante; y

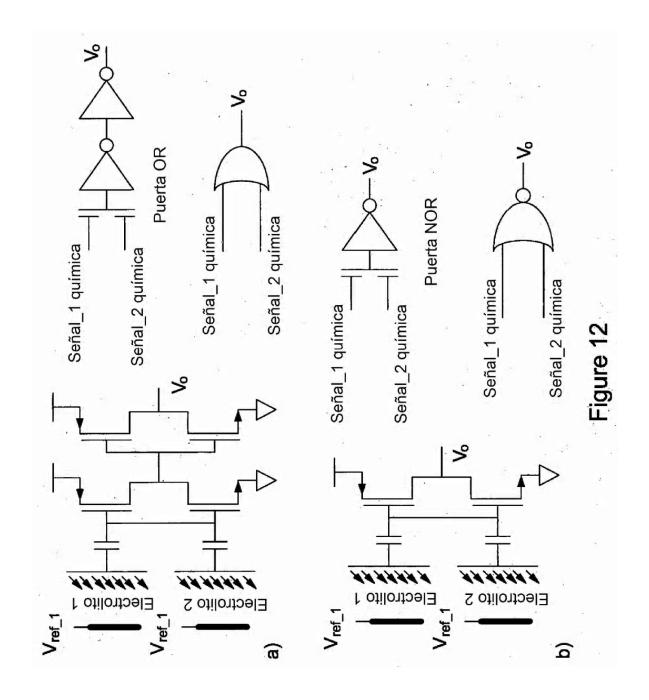

La figura 12 son unos diagramas de circuito de a) una puerta AND y b) una puerta OR.

#### Descripción detallada

15

40

45

En las discusiones siguientes, un ISFET puede verse como un FET acoplado de manera capacitiva a una señal química. La parte de transistor puede tratarse como un FGMOS normal. El sistema comprende un electrodo de referencia, un electrolito, una membrana de detección y el metal por debajo forman de manera colectiva una entidad que puede llamarse un condensador sensible a iones (ISCAP).

Con este punto de vista, un ISFET tradicional es básicamente un ISCAP a modo de la única entrada a un FGMOS. Sin embargo, en general, uno o más ISCAP son posibles entradas a una red de puertas flotantes de un número n de transistores FGMOS. Un número de otras entradas acopladas de manera capacitiva son también posibles, como se muestra por Vin1 y Vin2 en la figura 5.

La tensión de puerta de flotación puede expresarse como una suma ponderada de las tensiones que están acopladas de manera capacitiva a la misma. Es decir:

$$V_{FG} = \frac{(V_{ref1} + V_{chem1})C_{s1}}{C_{tot}} + \frac{(V_{ref2} + V_{chem2})C_{s2}}{C_{tot}} + \frac{V_{in1}C_{1}}{C_{tot}} + \frac{V_{in2}C_{2}}{C_{cot}} + \frac{V_{sub1}C_{g1}}{C_{tot}} + \frac{V_{sub2}C_{g2}}{C_{tot}}$$

(6)

$C_{g1}$  y  $C_{g2}$  son las capacidades de óxido de puerta de los dos transistores en la figura. Pueden ser una buena aproximación de las capacitancias de los transistores si están en inversión y se forma un canal. Por simplicidad, se supone que son constantes y los tamaños de puerta son lo suficientemente grandes como para reemplazar las capacidades parásitas.

Ya que puede acoplarse un número de entradas de manera capacitiva a la puerta de flotación y su potencial se define por la suma ponderada de las tensiones de las puertas de entrada (13). Por lo tanto, el ISFET de la figura 5 es un FG-MOS con una sola entrada que es la superposición de Vref y Vchem que están acopladas de manera capacitiva por la capa sensible a iones de pasivación. Su tensión (Vfg) de puerta de flotación viene dada por:

$$V_{fg} = \frac{(V_{ref} + V_{chem}) * C_{pass} + V_{GD}C_{GD} + V_{GS}C_{GS} + V_{GB}C_{GB}}{C_{tot}}$$

(7)

En la que, C<sub>pass</sub> es la capacitancia de pasivación, C<sub>tot</sub> es la capacitancia total vista por la puerta de flotación (15). Y V<sub>DG</sub>, V<sub>GS</sub>, V<sub>GB</sub>, C<sub>GD</sub>, C<sub>GS</sub>, C<sub>GB</sub> son el drenaje de puerta del transistor, el origen de puerta, y las tensiones de masa de puerta y las capacidades de manera consecutiva. El factor C<sub>pass</sub>/C<sub>tot</sub> reduce el efecto de V<sub>chem</sub> y por lo tanto la sensibilidad del pH. Sin embargo, puede hacerse próxima a la unidad maximizando la relación (C<sub>pass</sub>/C<sub>tot</sub>) es decir, diseñando la puerta química mucho más grande que la puerta eléctrica. Esta es una de las razones de la sensibilidad sub-Nernstiana conocida de los ISFET construidos con los procedimientos de CMOS convencionales.

Un inversor FG convencional se compone de transistores NMOS y PMOS de puerta de flotación en un amplificador inversor de clase AB convencional como se muestra de manera esquemática en la figura 6-A. La única entrada de este inversor se acopla de manera capacitiva a las dos puertas de flotación.

De acuerdo con la invención, una pluralidad de ISFET comparten la misma membrana de detección de iones y la puerta de flotación. En una realización preferida, un inversor, dos ISFET, un NMOS y un PMOS, están dispuestos como se muestra en la figura 6-B. La figura 6-C, es un esquema de circuito equivalente para un inversor de este tipo.

Este circuito puede usarse para realizar operaciones de monitorización de la reacción y umbralización del pH para una cámara de reacción. Puede usarse para procesar señales desde una serie de ISFET expuestos a una serie de cámaras de reacción. Cada cámara se coloca en la parte superior de un inversor de par ISFET ya sea con una V<sub>ref</sub> global o local. Cada píxel de la serie proporciona una salida digital que puede engancharse o procesarse digitalmente en el mismo CI sin la necesidad de una conversión de analógico a digital. Esto facilita la construcción de aplicaciones de laboratorio en microprocesador basadas en ISFET completamente digitales.

Para mejorar la sensibilidad al pH, puede usarse un amplificador para amplificar V<sub>chem</sub>, que es efectivamente la diferencia entre la puerta de flotación y el electrodo de referencia sumergido en el electrolito bajo ensayo. El circuito de la figura 7 es una posible realización. La tensión [V<sub>3</sub> = 2 A<sub>1</sub> A<sub>2</sub> V<sub>chem</sub>] es una versión amplificada de la tensión a través del ISCAP que refleja el pH del electrolito. Su salida se alimenta a un circuito disparador Schmitt. La salida (V<sub>salida</sub>) es una señal digital que conmuta el estado cuando el pH de la solución sufre un cambio mayor que un valor umbral.

#### Resultados:

En el ISFET de la figura 6-B, la entrada se suministra a la puerta de flotación de un amplificador de transistor único. En función de la región de funcionamiento, se sigue una de las relaciones  $I_d$ - $V_{gs}$  de la ecuación (1). Normalmente o  $I_d$  o  $V_{ds}$  se hace constante mientras que la otra representa la salida.

Para el inversor de la figura 6-C, con el fin de encontrar la tensión umbral de conmutación, su circuito se divide en dos partes: la parte de entrada que se usa para encontrar V<sub>fg</sub> que es la entrada a la segunda parte: el inversor convencional. Para conservar la carga V<sub>fg</sub> viene dada por:

$$V_{fg} = \frac{C_{pass}}{C_{tot}} \left( V_{chem} + V_{ref} \right) + \frac{VC_{nMOS} + VC_{pMOS}}{C_{tot}}$$

(8)

en la que :

10

15

20

25

35

40

45

$(VC_{xMOS} = V_{GDx}C_{GDx} + V_{GSx}C_{GSx} + V_{GBx}C_{GBx})$  y (x) es (n) para n-MOS y (p) para p-MOS.

Para el inversor convencional, la tensión ( $V_{sth}$ ) de umbral de conmutación es el punto en el que la tensión ( $V_{fg}$ ) de puerta de flotación de entrada es igual a la salida ( $V_0$ ). Por lo tanto los dos transistores están en saturación como  $V_{gs}$  =  $V_{ds}$ . Esto se descubre igualando las corrientes a través de los dos transistores y resolviendo para este punto. Fue descubierto en (18) – página 186, siendo:

$$V_{sth} = \frac{V_{tn} + r(V_{dd} + V_{tp})}{1 + r}; \quad \text{en la que} \quad r = \sqrt{\frac{-k_p}{k_n}}$$

(9)

En la que,  $V_{tn}$  y  $V_{tp}$  son tensiones de umbral mientras que  $\kappa_n$  y  $\kappa_p$  son {movilidad ( $\mu$ ) x capacitancia de óxido de puerta ( $C_{ox}$ )} para NMOS y PMOS respectivamente. Esto es para una inversión fuerte y una baja  $V_{dd}$  de tal manera que los dos transistores no alcanzan la saturación de velocidad (18). Por lo tanto, la conmutación tiene lugar cuando  $V_{fg} = V_{sth}$ , lo que da:

$$(V_{chem} + V_{ref}) = \frac{c_{tot}}{c_{pass}} V_{sth} - \frac{vc_{nMos} + vc_{pMos}}{c_{pass}}$$

(10)

La conmutación se dispara por la suma de  $V_{\text{chem}}$  y  $V_{\text{ref}}$ . El primer término está en función del pH, como en la ecuación (5). Incluye  $V_{\text{Qpass}}$  que se manifiesta así mismo como un cambio en el punto de conmutación.  $V_{\text{ref}}$  se decide por el usuario y es análoga a la  $V_{\text{entrada}}$  del inversor FG, teniendo en cuenta la diferencia en la capacidad de acoplamiento.  $V_{\text{chem}}$  tiene el efecto de cambiar la tensión umbral de conmutación si  $V_{\text{ref}}$  es la entrada. De la misma manera, si  $V_{\text{chem}}$  es la entrada  $V_{\text{ref}}$  cambiará el punto de conmutación.

#### Resultados

Una realización a modo de ejemplo del dispositivo se trata a continuación incluyendo los resultados de su uso en una realización a modo de ejemplo del procedimiento.

Los transistores tienen una longitud de  $0.35~\mu m$ , pero sus anchuras son de  $4~\mu m$  y  $12~\mu m$  para los dispositivos N y P, respectivamente. En la figura, la  $V_{ref}$  se barre por el ISFET y el punto de conmutación se encuentra para valores de pH de 4.0,~7.0 y 10.0. Los puntos de conmutación son 1.49~V,~1.63~V y 1.76~V respectivamente. Esto proporciona una sensibilidad de 44.52~mV/pH. Se usa una  $V_{dd}$  de 2.2~V.

La salida se amortigua por dos inversores MOS que aumentan en tamaño con el fin de proporcionar la corriente suficiente para accionar la carga introducida por el adaptador de conexión y la PCB de ensayo. La zona sensible química es de  $35 \times 200 \ \mu m^2$ . Un solo electrodo de referencia de vidrio de unión Ag/AgCl se sumerge en el electrolito bajo ensayo con el fin de aplicar la  $V_{ref}$ . Se elige debido a su tensión de unión estable. Se ensayan tres soluciones de amortiguación de pH diferentes (4,0, 7,0 y 10,0).

La tensión de referencia se barre para cada caso con el fin de encontrar el valor que provoque el cambio para los diferentes valores de pH. La sensibilidad, medida como el cambio de tensión de conmutación, se descubre que es de 28,33 mV/pH.

El funcionamiento de conmutación puede accionarse solamente por el cambio de pH. La  $V_{ref}$  puede fijarse cerca del punto de conmutación del pH actual. Esta es la condición inicial de la lógica "1". Si el pH de la solución se cambia valorando 0,1 M de HCl para bajar el pH a 6,5  $\pm$  0,1. Esto da un "0" lógico. A continuación, 0,1 M de NaOH puede valorarse con el fin de llevar el pH de nuevo a 7,0  $\pm$  0,1. Puede proporcionarse una segunda entrada a la puerta de flotación del ISFET, como se muestra en la figura 9. Esta disposición proporciona el inversor con dos entradas: la entrada sensible a iones acoplada a través de la capacitancia de pasivación y la segunda entrada (Vin2) acoplada a través de la capacitancia ( $C_2$ ). La tensión de puerta de flotación resultante es la suma ponderada de estas dos entradas.

Al hacer la segunda capacitancia ( $C_2$ ) de la entrada muy pequeña comparada con la capacitancia ( $C_{pass}$ ) de pasivación, es posible usar esta entrada ( $V_{in2}$ ) como la entrada de inversor eléctrica mientras que la señal química se usa como una puerta de control. Por lo tanto, el punto de conmutación denominado\*  $V_{in2}$  se vuelve muy sensible a los cambios de pH. De hecho, es una versión a escala de la sensibilidad al pH denominada  $V_{ref}$ . El factor de escala es la relación  $C_{pass}/C_2$ . La elección de esta relación está en función de la aplicación y es preferentemente mayor que 10, más preferentemente mayor que 50, 100, 500 o 1000.

Ya que un número de nodos están acoplados de manera capacitiva a la puerta de flotación, su potencial se define por la suma ponderada de las entradas. La tensión ( $V_{fa}$ ) de puerta de flotación viene dada por:

$$V_{fg} = \frac{C_{pass}}{C_{tot}} (V_{chem} + V_{ref}) + \frac{C_2}{C_{tot}} V_{in3} + \frac{VC_{nMOS} + VC_{pMOS}}{C_{tot}}$$

(11)

10 en la que:

5

$$(VC_{nMOS} = V_{Dn}C_{GDn} + V_{Sn}C_{GSn} + V_{Bn}C_{GBn})$$

У

35

$$(VC_{pMOS} = V_{Dp}C_{GDp} + V_{Sp}C_{GSp} + V_{Bp}C_{GBp}).$$

En este caso, VC<sub>nMOS</sub> es la contribución del nMOS a la tensión de puerta de flotación. Es decir, su tensión de drenaje (V<sub>Dn</sub>) multiplicada por su capacitancia de drenaje de puerta (C<sub>GDn</sub>), su tensión de origen (V<sub>Sn</sub>) multiplicada por su capacitancia de puerta (C<sub>GSn</sub>), y su tensión de cuerpo (V<sub>Bn</sub>) multiplicada por la capacitancia de cuerpo de puerta (C<sub>GBn</sub>). Todas las tensiones se refieren a tierra. El sufijo (n) significa nMOS. VC<sub>pMOS</sub> es la contribución del pMOS a la tensión de puerta de flotación. Se calcula de una manera similar. C<sub>pass</sub> es la capacitancia de pasivación, V<sub>chem</sub> es la tensión química en función del pH dada por la ecuación 11. V<sub>ref</sub> es la tensión de electrodo de referencia, y C<sub>tot</sub> es la capacitancia total vista por la puerta de flotación. Incluye todas las demás capacidades parásitas no tratadas por separado en el presente documento.

Es habitual suponer que la puerta de flotación no tenga cargas y por lo tanto tener una tensión inicial de cero. Sin embargo, esto puede no ser el caso en la vida real, en la que ellas mismas se manifiestan como un cambio en la tensión inicial de la puerta de flotación.

A partir de la ecuación 11, el factor C<sub>pass</sub>/C<sub>tot</sub> reduce el efecto de V<sub>chem</sub> y por lo tanto la sensibilidad del pH. Sin embargo, puede hacerse cercano a la unidad maximizando la relación (C<sub>pass</sub>/C<sub>tot</sub>). Es decir, diseñando la capacitancia de pasivación mucho más grande que la suma de todas las otras capacidades en el circuito. Esta es una de las razones de la sensibilidad sub-Nernstiana de los ISFET construidos con los procedimientos de CMOS convencionales. El segundo término de la ecuación (11) es la segunda entrada reducida por C<sub>2</sub>/C<sub>pass</sub>. El recíproco de esta relación es la amplificación de la sensibilidad al pH denominada Vin2. Por lo tanto, su elección debería tener en cuenta los requisitos de aplicación y en el mismo momento minimizar C<sub>2</sub> para permitir más espacio para la sensibilidad química.

Un inversor funcionando en una inversión débil tiene su tensión (V<sub>sth</sub>) de umbral de conmutación cuando los dos transistores tienen la misma corriente:

$$V_{sth} = \frac{V_{dd} - |V_{tp}| + \ln(\frac{l_{sn}}{l_{sp}})V_{tn}}{1 + \ln(\frac{l_{sn}}{l_{sp}})}$$

(12)

$V_{tn}$  y  $V_{tp}$  son las tensiones de umbral, mientras que  $I_{sn}$  e  $I_{sp}$  son las corrientes de origen de los transistores NMOS y PMOS, respectivamente.  $V_{dd}$  es la tensión de alimentación.

Esta tensión umbral de conmutación de la ecuación (3) está en función solo de los parámetros de MOS. La conmutación se produce cuando  $V_{FG}$  cambia cruzando  $V_{sth}$  yendo más alta o más baja que la misma.

Ya que la tensión de puerta de flotación es una función de sus voltajes acoplados como en la ecuación (1), estas entradas afectan a su punto de conmutación. Por lo tanto, definir su sensibilidad al pH no es tan sencillo como en el caso de un único ISFET. Puede definirse como el cambio inducido por el pH en V<sub>fg</sub>. Pero, esto es difícil de medir ya que no hay acceso directo a la misma. Pero es posible hacer referencia a una de sus entradas, concretamente: V<sub>ref</sub> o Vin2. Por lo tanto, la sensibilidad al pH se manifiesta como el cambio en la tensión de conmutación, debido al cambio de pH, como se ve barriendo una cualquiera de las mismas mientras se mantiene la otra constante.

La sensibilidad de la puerta de flotación de este inversor para el pH hace referencia a  $V_{ref}$  mientras  $V_{in2}$  es constante, se descubre por:

$$V_{fg}$$

sensibilidad para el pH  $\frac{dV_{fg}}{dpH} = \frac{C_{pass}}{C_{tot}} 2.3 \alpha U_T \text{V/pH}$  (13)

$$V_{fg}$$

sensibilidad para  $V_{ref} = \frac{dV_{fg}}{dV_{ref}} = \frac{C_{pass}}{C_{tot}}$  Por lo tanto, (14)

$$V_{fg}$$

sensibilidad para el ph, hace referencia a  $V_{ref} = \frac{dV_{fg}}{dpH} \times \frac{dV_{ref}}{dV_{fg}} = \frac{dV_{ref}}{dpH} = 2.3 \alpha U_T V/pH$  (15)

Por lo tanto, a pesar del hecho de que el efecto de  $V_{ref}$  en  $V_{fg}$  se reduce por la relación  $C_{pass}/C_{tot}$ , la sensibilidad al pH cuando se hace referencia a  $V_{ref}$  no es como la propia  $V_{Chem}$  que se reduce en la misma proporción. El escalado cancela la salida.

Sin embargo, si Vin2 se usa para cambiar  $V_{fg}$  mientras que la  $V_{ref}$  está fija, entonces:

5

10

25

35

$$V_{fg}$$

sensibilidad para  $V_{in2} = \frac{dV_{fg}}{dV_{in2}} = \frac{C_2}{C_{tot}}$  (16)

$$V_{fg}$$

sensibilidad para el ph, hace referencia a  $V_{in3} = \frac{dv_{in2}}{dpH} \times \frac{dv_{in2}}{dv_{fg}} = \frac{dv_{in2}}{dpH} = \frac{c_{pass}}{c_2} 2.3 \alpha U_T V/pH$  (17)

Por lo tanto, si Vin2 se usa como la entrada en la que  $V_{ref}$  es constante y la puerta química desempeña el papel de una puerta de control que cambia el punto de conmutación, entonces la sensibilidad al pH del circuito con referencia a Vin2 se amplía mediante  $C_{pass}/C_2$ .

Esto es posible, por diseño, para hacer  $C_{pass} = AC_2$ . A continuación, la sensibilidad al pH se amplía por la relación A sin la necesidad de cualquier tipo de amplificador. Por lo tanto, usando Vin2 como la entrada eléctrica del inversor, el peso de acoplamiento se usa para mejorar la sensibilidad al pH.

El experto en la materia escogerá esta relación de amplificación de acuerdo con su aplicación de tal manera que cuando Vin2 se barre a través de su intervalo completo, corresponderá a valores de pH observables. Por ejemplo, si el cambio de pH esperado se extiende dos unidades de pH, por ejemplo desde el pH 6 al pH 8; y Vin2 se permite que se extienda entre los valores de 0 a 1 V y la sensibilidad de pH esperada haciendo referencia a  $V_{ref}$  es 30 mV/pH, entonces un valor de  $C_{pass}/C_2 = A = 1$  V/30 mV/2 = 16.  $V_{ref}$  debería elegirse de tal manera que establezca la salida del circuito con la lógica inicial deseada y con el inversor en el límite de conmutación. Esto permitirá que los cambios de pH sean fácilmente detectables por Vin2.

Por ejemplo, en una realización a modo de ejemplo, la tensión umbral del dispositivo N-MOS es 0.59 V y la tensión umbral del dispositivo PMOS es -0.72 V. Por lo tanto, usar una  $V_{dd}$  de 0.5 V garantiza un funcionamiento sub-umbral limitando la tensión máxima que un transistor ve menor que su voltaje de umbral.

A continuación, puede barrerse V<sub>ref</sub> para encontrar un valor que provoque la conmutación (<sub>Vref, sth</sub>). El pH del electrolito se escalona desde el pH 4,0 al pH 7,0 al pH 10,0. Vin2 se establece en cero voltios.

La salida se muestra en la figura. La sensibilidad simulada es por lo tanto:  $\frac{\Delta V_{ref,sch}}{\Delta pH} = 33.9 \ mV/pH$ .

$C_{pass}$  = 420 fF y  $C_2$  = 3 fF lo que da un factor de escala de  $C_{pass}/C_2$  = 140. Por lo tanto, la sensibilidad al pH con respecto a Vin2 es { $(C_{pass}/C_2)$  x 0,0339} = 4,7 V/pH.  $V_{ref}$  se mantiene constante en el límite de conmutación, mientras que Vin2 se barre para encontrar el punto de conmutación (Vin2, sth) para valores de pH.

Mientras que la disposición del inversor puede usarse para detectar un cambio de pH de 0,1, la señal Vin2 adicional acoplada a la puerta de flotación por un factor de escalación arbitrariamente grande puede detectar incluso un cambio más pequeño, por ejemplo de 0,001.

La sensibilidad alta no se obtiene mejorando la sensibilidad física del ISFET. En su lugar, la sensibilidad al pH puede hacerse de este modo muy alta mediante la explotación de la naturaleza de la puerta de flotación del ISFET construido con un procedimiento CMOS sin modificar. Mientras que pueden obtenerse resultados similares usando un amplificador, esto viene con costes adicionales de zona, potencia y ruido. La ventaja en este caso es la alta ganancia sin estos problemas asociados.

## ES 2 554 128 T3

Este circuito puede servir como un bloque de construcción básico para una serie de conmutadores de pH, formando píxeles. Ellos son capaces de proporcionar la salida digital a partir de las entradas químicas o biológicas. Con retroalimentación al electrodo de referencia, es posible cambiar la tensión de umbral de conmutación para reflejar la región de interés de pH necesaria.

- Preferentemente, la capa de detección se expone a una cámara que tenga una concentración de un ion objetivo. La concentración de iones puede ser constante de tal manera que las señales de salida del conmutador ISFET serán constantes. La concentración de iones puede variar en el tiempo o como el resultado de una reacción química de tal manera que las señales de salida del conmutador ISFET detectarán un cambio en la concentración de iones.

- Preferentemente, la reacción química es la incorporación de un nucleótido en un ácido nucleico de tal manera que se liberan protones. El ácido nucleico puede ser desconocido y los reactivos de nucleótidos conocidos de tal manera que la salida del circuito indica un cambio (de la falta del mismo) en el pH que se observa debido a los reactivos de nucleótidos que son complementarios (o no) con el ácido nucleico desconocido.

- En algunas realizaciones, hay una pluralidad de cámaras, cada una de las cuales está expuesta a los dispositivos de la invención para detectar una concentración de un ion objetivo, o detectar un cambio en una concentración de un ion objetivo. Las salidas de los dispositivos pueden conectarse para realizar operaciones lógicas tales como AND, NAND, OR, NOR, XOR, XNOR y sus combinaciones. Los expertos en la materia apreciarán cómo esto puede realizarse. Un circuito a modo de ejemplo se muestra en la figura 12.

- Aunque la invención se ha descrito en términos de las realizaciones preferidas como se ha expuesto anteriormente, debería entenderse que estas realizaciones son solamente ilustrativas y que las reivindicaciones no se limitan a esas realizaciones. Los expertos en la materia serán capaces de realizar modificaciones y alternativas a la vista de la divulgación que se contemplan como que caen dentro del ámbito de las reivindicaciones adjuntas.

#### Referencias:

20

- 1- P. Bergveld, "Thirty years of ISFETOLOGY What happened in the past 30 years and what may happen in the next 30 years", Sensores y actuadores, volumen 88, páginas 1-20, 2003.

- 2- Leila Shepherd, Pantelis Georgiou, and Chris Toumazou, "A novel voltage clamped CMOS ISFET sensor interface", Simposio internacional del IEEE sobre circuítos y sistemas ISCAS, páginas 3331-3334, 2007.

- 3- Christofer Toumazou, Bhusana Premanode, Leila Shepherd; Patente de Estados Unidos US 2010/0159461 A1, "Ion Sensitive Field Effect Transistors", fecha de publicación: 24 de Junio de 2010.

- 4- Tadayuki Matsuo and Masayoshi Esashi, "Methods of ISFET Fabrication", Sensores y actuadores, volumen 1, páginas 77-96, 1981.

- 5- J. Bausells, J. Carrabina, A. Errachid, A. Merlos, "Ion-sensitive field-effect transistors fabricated in a commercial CMOS technology", Sensores y actuadores B 57, páginas 56-62, 1999.

- 6- P.A. Hammond, D. Ali, D.R.S. Cumming, "A Single-Chip pH Sensor Fabricated by a Conventional CMOS Process", Actas de sensores del IEEE, volumen 1, páginas 350-355, 2002.

- 7- Winston Wong, Leila Shepherd, Pantelis Georgiou and Chris Toumazou, "Towards ISFET based DNA Logic for Rapid nucleic acid detection", Conferencia de sensores del IEEE páginas 1451 -1454, 2009.

- 8- Tadashi Shabata, and Tadahiro Ohmi, "A Functional MOS Transistor Featuring Gate-Level Weighted Sum and Threshold Operations", Dispositivos de transacciones del IEEE, volumen 39, N° 6, páginas 1444 1455, 1992.

- 9- P. Georgiou and C. Toumazou, "CMOS Based Programmable ISFET", Cartas de electronica, volumen 44 № 22, 2008, páginas 1289 1290.

- 10- W. Wong Jr, P. Georgiou, C. -P. Ou, and C. Toumazou, "PG-ISFET based DNA-logic for reaction monitoring", Cartas de electronica, volumen 46, № 5, 2010, páginas 330 332.

- 11- Prakash, S.B.; Abshire, P.; "A CMOS capacitance sensor that monitors cell viability", Conferencia de sensores del IEEE 2005, páginas 1177 1180.

- 45 12- Shibata, T.; Kosaka, H.; Ishii, H.; Ohmi, T.; "A neuron-MOS neural network using self-learning-compatible synapse circuits", Diario de circuitos de estado sólido del IEEE, volumen: 30, edición 8, páginas 913 922, 1995.

- 13- Jayant, K.; Porri, T.; Erickson, J.W.; Kan, E.C.; "Label-free electronic detection of growth factor induced cellular chatter on chemoreceptive neuron MOS (CvMOS) transistors", Conferencia international sobre sensores de estado sólido, actuadores and microsistemas, páginas 1814-1817, 2009.

40

# ES 2 554 128 T3

- 14- Themistoklis Prodromakis, Yan Liu, Timothy Constandinou, Pantelis Georgiou, Chris Toumazou, "Exploiting CMOS Technology to Enhance the Performance of ISFET Sensors", Cartas de dispositivo electronico del IEEE, volumen 31, Nº 9, páginas 1053-1055, 2010.

- 15- Sunil Purushothaman, Chris Toumazou, and Chung-Pei Ou, "Proton and Single nucleotide polymorphism detection: A simple use for the Ion Sensitive Field Effect Transistor", Sensores y actuadores, B 114, páginas 964 968, 2006.

5

10

15

20

- 16- Qintao Zhang, Vivek Subramanian, "DNA hybridisation detection with organic thin film transistors: Toward Fast Disposable DNA microarray chip". Biosensores and bioelectronica, volumen 22, páginas 3182 3187, 2007.

- 17- S. Purushothaman, C. Toumazou, and J. Georgiou, "Towards Fast Solid State DNA Sequencing", Simposio internacional del IEEE sobre circuítos y sistemas, páginas IV-169 IV-172, 2002.

- 18- P. Georgiou and C. Toumazou,"CMOS Programmable Gate ISFET", Cartas electronicas, volumen 44, páginas 1289-1290, 2008.

- 19- Liu Yan, Pantelis Georgiou, Timothy G. Constandinou, David Garner and Chris Toumazou, "An Auto-Offset-Removal circuit for chemical sensing based on the PG-ISFET", Simposio internacional del IEEE sobre circuítos y sistemas, ISCAS 2009, páginas 1165-1168.

- 20- Austriamicrosystems, "0.35 mm CMOS C35 Process Parameters", número de documento: ENG-182, revisión#: 6.0, 12.12.2008.

- 21- Mark J. Milgrew; and David R. S. Cumming, "Matching the Transconductance Characteristics of CMOS ISFETArrays by Removing Trapped Charge", Transacción del IEEE de dispositivos electronicos, volumen 55, № 4, páginas 1074-1079, 2008.

- 22- Jan, M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic, "Digital Integrated Circuits", Prentice Hall, segunda edición, 2003.\*

#### **REIVINDICACIONES**

- 1. Un dispositivo semiconductor para detectar una concentración de iones de una muestra, comprendiendo el dispositivo:

- una pluralidad de transistores de efecto de campo (FET) acoplados a una puerta de flotación común; y

una capa de detección de iones expuesta a la muestra y acoplada a la puerta de flotación;

caracterizado porque, en uso, se enciende o se apaga una corriente a través de los transistores en función de la magnitud de la concentración de iones en la muestra en la proximidad de la capa de detección en comparación con un umbral de conmutación.

- Un dispositivo de acuerdo con la reivindicación 1 y que comprende además un electrodo de referencia expuesto a

la muestra, en el que una tensión de entrada acoplada al electrodo de referencia está dispuesta para establecer el umbral de conmutación de la pluralidad de FET.

- 3. Un dispositivo de acuerdo con cualquier reivindicación anterior, en el que la pluralidad de FET comprende un FET de tipo P y un FET de tipo N dispuestos en una configuración de comparador.

- 4. Un dispositivo de acuerdo con la reivindicación 1, en el que la pluralidad de FET comprende un FET de tipo P y un FET de tipo N dispuestos en una configuración de inversor.

- 5. Un dispositivo de acuerdo con la reivindicación 1, en el que la pluralidad de FET comprende un FET de tipo P y un FET de tipo N que están dispuestos en una configuración de inversor que tiene una señal de salida que es una salida de lógica uno o de lógica cero de acuerdo con una concentración de iones de la muestra.

- Un dispositivo de acuerdo con cualquier reivindicación anterior, en el que los FET están polarizados en una inversión débil.

- 7. Un dispositivo de acuerdo con cualquier reivindicación anterior, en el que los FET están polarizados de tal manera para conmutar entre la saturación y el corte.

- 8. Un dispositivo de acuerdo con cualquier reivindicación anterior, que comprende además una o más primeras señales de entrada eléctricas acopladas a la puerta de flotación para eliminar o añadir una carga a la puerta de flotación para establecer un umbral de conmutación para la pluralidad de transistores.

- 9. Un dispositivo de acuerdo con la reivindicación 8, en el que la una o más primeras señales de entrada eléctricas están dispuestas para acoplarse a la puerta de flotación para establecer el umbral de conmutación y desacoplarse cuando no se establece el umbral de conmutación.

- 10. Un dispositivo de acuerdo con la reivindicación 8 o 9, en el que dicha una o más primeras señales de entrada eléctricas comprenden una señal conectada a una tensión positiva y una señal conectada a una tensión negativa.

- 11. Un dispositivo de acuerdo con cualquier reivindicación anterior, que comprende además una segunda señal de entrada eléctrica acoplada a la puerta de flotación, en el que la segunda señal de entrada eléctrica está dispuesta para cambiar en magnitud con el fin de conmutar la pluralidad de transistores de efecto de campo.

- 12. Un dispositivo de acuerdo con la reivindicación 11, en el que la capa de detección de iones está acoplada a la puerta de flotación por una primera capacitancia y en el que la segunda señal de entrada eléctrica está acoplada a la puerta de flotación por una segunda capacitancia.

- 13. Un circuito para detectar una pluralidad de reacciones químicas y evaluar una función lógica que tiene el resultado de cada una de la pluralidad de reacciones químicas como sus entradas, comprendiendo el circuito al menos una cámara de reacción para cada una de la pluralidad de reacciones químicas, reacciones químicas que cambian una concentración de iones en la cámara de reacción;

- en el que cada cámara de reacción está provista de un dispositivo de acuerdo con cualquier reivindicación anterior, proporcionando cada dispositivo una señal de salida digital cuyo estado está en función de la concentración de iones de una muestra en esa cámara, y en la que las salidas se acoplan entre sí para formar un circuito de procesamiento de señales digitales para evaluar una función lógica.

- 45 14. Un procedimiento para proporcionar una salida que representa una concentración de un ion objetivo en una muestra, comprendiendo el procedimiento:

- proporcionar un conmutador CMOS que comprende una pluralidad de transistores de efecto de campo (FET) acoplados a una puerta de flotación común y una capa de detección de iones expuesta a la muestra y acoplada a la puerta de flotación;

- exponer la capa sensible a iones a la muestra para conmutar un estado del conmutador CMOS a encendido o apagado; y

- emitir una señal desde el conmutador CMOS.

20

25

40