(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 562 031**

(51) Int. Cl.:

**H03M 13/27** (2006.01)

**H04L 27/26** (2006.01)

**H04L 1/00** (2006.01)

**H04L 27/00** (2006.01)

**H04L 27/34** (2006.01)

**H04L 5/00** (2006.01)

**H03M 13/25** (2006.01)

**H03M 13/29** (2006.01)

**H03M 13/11** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: **24.10.2008 E 11183243 (2)**

(97) Fecha y número de publicación de la concesión europea: **06.01.2016 EP 2403147**

---

(54) Título: **Aparato y método de procesamiento de datos**

(30) Prioridad:

**30.10.2007 GB 0721271 30.10.2007 GB 0721272

30.10.2007 GB 0721270 30.10.2007 GB 0721269

19.11.2007 GB 0722645 20.11.2007 GB 0722728

26.11.2007 JP 2007304689

26.11.2007 JP 2007304690**

(45) Fecha de publicación y mención en BOPI de la traducción de la patente:

**02.03.2016**

(73) Titular/es:

**SONY CORPORATION (100.0%)

1-7-1 Konan, Minato-ku

Tokyo 108-0075, JP**

(72) Inventor/es:

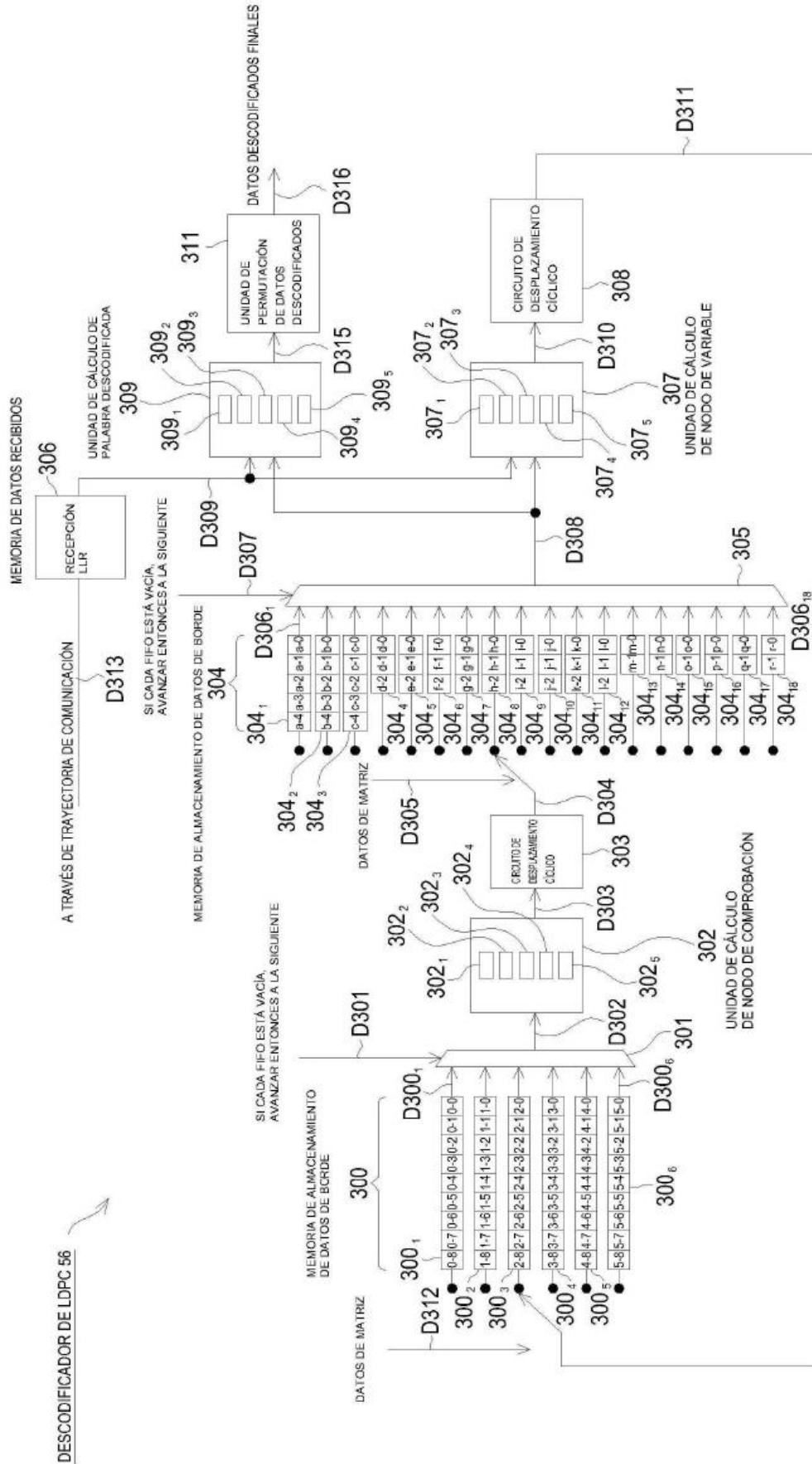

**TAYLOR, MATTHEW PAUL ATHOL;

ATUNGSIRI, SAMUEL ASANBENG;

YOKOKAWA, TAKASHI y

YAMAMOTO, MAKIKO**

(74) Agente/Representante:

**LEHMANN NOVO, María Isabel**

**ES 2 562 031 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## DESCRIPCIÓN

Aparato y método de procesamiento de datos

### Campo de la invención

5 La presente invención se refiere a métodos y aparatos de procesamiento de datos para recuperar bits de datos desde un cierto número de señales de sub-portadora de un símbolo Multiplexado por División de Frecuencias Ortogonales (OFDM) para formar una corriente de bits de salida.

Realizaciones de la presente invención pueden proporcionar un receptor OFDM.

### Antecedentes de la invención

10 El estándar de Difusión de Video Digital Terrestre (DVB-T) utiliza Multiplexado por División de Frecuencia Ortogonal (OFMD) para comunicar datos que representan imágenes de video y de sonido a receptores por medio de una señal de comunicación de radiodifusión. Se sabe que existen dos modos conocidos para el estándar de DVB-T que se conocen como el modo de 2k y el modo de 8k. El modo de 2k proporciona 2048 sub-portadoras mientras que el modo de 8k proporciona 8192 sub-portadoras. De manera similar, se ha proporcionado para el estándar de Radiodifusión Portátil de Video Digital (DVB-H) un modo de 4k, en el que número de sub-portadoras es de 4096.

15 15 Esquemas de codificación de corrección de error, tal como codificación LDPC/BCH, que han sido propuestos para el DVB-T2, se comportan mejor cuando el ruido y la degradación de los valores de símbolo resultantes de la comunicación están sin relacionar. Los canales de radiodifusión terrestre pueden adolecer de desvanecimiento correlacionado en los dominios tanto del tiempo como de la frecuencia. Como tales, separando bits de datos codificados en diferentes señales de sub-portadora del símbolo de OFMD tanto como sea posible, el rendimiento de 20 los esquemas de codificación de corrección de error se puede incrementar.

Con el fin de mejorar la integridad de los datos comunicados utilizando DVB-T o DVB-H, se conoce el hecho de proporcionar un intercalador de símbolo a efectos de intercalar símbolos de datos de entrada según son mapeados tales símbolos sobre las señales de sub-portadora de un símbolo de OFMD. Para el modo de 2k y el modo de 8k, se ha divulgado una disposición en el estándar de DVB-T para generar las direcciones que efectúen el mapeo. De igual modo, para el modo de 4k del estándar de DVB-H, se ha proporcionado una disposición para generar direcciones para mapeo, y un generador de dirección para implementar este mapeo ha sido divulgado en la solicitud de patente europea nº 04251667.4. El generador de dirección comprende un registro de desplazamiento de retroalimentación lineal que es operable para generar una secuencia de bits pseudo aleatoria y un circuito de permutación. El circuito de permutación permuta el orden del contenido del registro de desplazamiento de retroalimentación lineal con el fin 30 de generar una dirección. La dirección proporciona una indicación de una posición de memoria de la memoria de intercalador para escribir el símbolo de dato de entrada en, o leer el símbolo de dato de entrada desde, la memoria de intercalador para el mapeado sobre una señal de sub-portadora del símbolo de OFMD. De forma similar, un generador de dirección del receptor está dispuesto para generar direcciones de la memoria de intercalador para escribir los símbolos de datos recibidos en, o leer los símbolos de datos que salen desde, la memoria de intercalador 35 para formar una corriente de símbolos de salida.

De acuerdo con un desarrollo adicional del estándar de Radiodifusión de Video Digital Terrestre, conocido como CVB-T2, existe un deseo de mejorar la comunicación de bits de datos, y más en particular de proporcionar una disposición mejorada para intercalar bits de datos codificados con códigos LDPC y símbolos de datos sobre las señales de sub-portadora de símbolos de OFDM.

40 40 En un artículo denominado "*A novel, high-speed, reconfigurable demapper-symbol deinterleaver architecture for DVB-T*", de Horvath et al, publicado en la ISCAS '99, el acto de la Conferencia Internacional sobre Circuitos y Sistemas del IEEE de 1999, en Orlando, Florida, EE. UU., desde el 30 de mayo al 2 de junio de 1999, se divulga un algoritmo reconfigurable para el desmapeo de la señal, el cual se puede utilizar en receptores DVB-T (Difusión de Video Digital, versión Terrestre). El algoritmo/la arquitectura soporta tanto el modo de transmisión jerárquico como 45 no jerárquico, para disposiciones en las cuales se utilizan esquemas de modulación diferentes y tasas de codificación. El receptor incluye un intercalador de símbolos y un intercalador de bits.

Los documentos EP 1 463 255 y EP 1 463 256 divulan un intercalador para mapear símbolos de datos en las sub-portadoras de un símbolo de OFDM. El intercalador incluye un generador de direcciones. El intercalador introduce 50 por lectura el número predeterminado de símbolos de datos en la memoria del intercalador y extrae por lectura los símbolos de datos sobre las sub-portadoras del símbolo de OFDM, siendo el orden de salida por lectura diferente al orden de entrada por lectura, lo que se determina a partir de un conjunto de direcciones con el efecto de que los símbolos de datos sean intercalados. El conjunto de direcciones que se generan en el generador de direcciones puede proporcionar intercalación para un transmisor o receptor DVB de modo de 4K.

En un artículo denominado “*IEEE 802.16 TG4 OFDM PHY Proposal for the 802.16b PHY Layer*”, el grupo de trabajo de acceso inalámbrico de banda ancha del IEEE 802.16, de Segal Y. et al, del 4 de marzo de 2001 (2001-03-04), páginas 1-53, se divulga una especificación para una capa física que incluye una disposición para portar datos utilizando símbolos de OFDM.

- 5 El documento US 6.353.900 divulga un intercalador que incluye un generador de dirección para generar una dirección de una memoria de intercalador utilizando un generador de número pseudo-aleatorio. Los datos se escriben en la memoria de intercalador en un orden secuencial y a continuación son extraídos por lectura desde el generador de dirección utilizando direcciones especificadas por el generador de dirección.

#### Sumario de la invención

- 10 De acuerdo con la presente invención, se proporciona un aparato de procesamiento de datos dispuesto en funcionamiento para recuperar bits de datos desde símbolos de datos recibidos desde un número predeterminado de señales de sub-portadora de un símbolo Multiplexado por División de Frecuencias Ortogonales (OFDM) para formar una corriente de bits de salida. El aparato de procesamiento de datos comprende un desentrelazador de símbolos que puede funcionar para introducir por lectura en una memoria de entrelazador de símbolos el número predeterminado de símbolos de datos desde las señales de sub-portadora OFDM, y para extraer por lectura de la memoria de entrelazador de símbolos los símbolos de datos adentro de una corriente de símbolos de salida para efectuar el mapeo, siendo la extracción por lectura en un orden diferente a la introducción por lectura, determinándose el orden a partir de un conjunto de direcciones, con el efecto de que los símbolos de datos son desentrelazados desde las señales de sub-portadora OFDM adentro de la corriente de símbolos de salida. Una unidad de desmapeo se puede hacer funcionar para generar, a partir de los símbolos de datos de la corriente de símbolos de salida, bits de datos codificados por LDPC, entrelazados por paridad, mediante la conversión de cada uno de los símbolos de datos de la corriente de símbolos de salida que representa un símbolo de modulación de las señales de sub-portadora OFDM en bits de datos de acuerdo con un esquema de modulación. Un permutador inverso está adaptado para realizar un proceso de permutación inversa para efectuar una reversión de un proceso de permutación aplicado a los bits de datos codificados por LDPC, entrelazados por paridad, para permutar los bits de datos codificados por LDPC de manera que no se incorporan en el mismo símbolo una pluralidad de los bits de datos codificados por LDPC que corresponden a un valor de 1 en una fila arbitraria de una matriz de información que corresponde a bits de información de un código LDPC, que se usó para codificar los bits de datos. Un decodificador LDPC está adaptado para realizar una decodificación LDPC sobre los bits de datos codificados por LDPC sobre los que se ha realizado el proceso de permutación inversa para formar los bits de datos de salida. El desentrelazador de símbolos incluye un generador de direcciones que se puede hacer funcionar para generar el conjunto de direcciones, generándose una dirección para cada uno de los símbolos de datos recibido para indicar la señal de sub-portadora OFDM desde la que el símbolo de datos recibido se tiene que mapear adentro de la corriente de símbolos de salida. El generador de dirección comprende: un registro de desplazamiento de retroalimentación lineal que incluye un número predeterminado de niveles de registro y que es operable para generar una secuencia de bits pseudo-aleatoria de acuerdo con un polinomio generador;

un circuito de permutación operable para recibir el contenido de los niveles de registro de desplazamiento y para permutar los bits presentes en los niveles de registro de acuerdo con un código de permutación para formar una dirección de una de las sub-portadoras de OFDM, y

- 40 una unidad de control operable en combinación con un circuito de comprobación de dirección para regenerar una dirección cuando una dirección generada exceda de una dirección válida máxima predeterminada, y en el que:

la dirección válida máxima predeterminada es sustancialmente cuatro mil noventa y seis,

- 45 el registro de desplazamiento de retroalimentación lineal tiene once niveles de registro con un polinomio generador para el registro de desplazamiento de retroalimentación lineal de  $R'_i[10] = R'_{i-1}[0] \oplus R'_{i-1}[2]$ , y el orden de permutación forma una dirección de once bits  $R'_i[n]$  para el símbolo de datos  $i^{\text{ésimo}}$  del bit presente en el nivel de registro  $n^{\text{ésimo}}$   $R'_i[n]$  de acuerdo con la tabla:

|                      |    |    |   |   |   |   |   |   |   |   |   |

|----------------------|----|----|---|---|---|---|---|---|---|---|---|

| $R'_i[n]$ para $n =$ | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| $R'_i[n]$ para $n =$ | 7  | 10 | 5 | 8 | 1 | 2 | 4 | 9 | 0 | 3 | 6 |

En un ejemplo, en el que el símbolo de OFDM se genera de acuerdo con un modo de 4k, la dirección válida máxima predeterminada es sustancialmente cuatro mil noventa y seis, el registro de desplazamiento de retroalimentación lineal tiene once niveles de registro con un polinomio generador para el registro de desplazamiento de retroalimentación lineal que es  $R'_i[10]=R'_{i-1}[0]\oplus R'_{i-1}[2]$ , y el orden de permutación forma una dirección  $R'_i[n]$  de once bits para el símbolo de datos  $i^{\text{ésimo}}$  a partir del bit presente en el nivel de registro  $n^{\text{ésimo}}$   $R'_i[n]$  de acuerdo con la tabla:

|                      |    |   |   |   |   |   |   |   |   |   |   |

|----------------------|----|---|---|---|---|---|---|---|---|---|---|

| $R'_i[n]$ para $n =$ | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|----|---|---|---|---|---|---|---|---|---|---|

|                     |   |    |   |   |   |   |   |   |   |   |   |

|---------------------|---|----|---|---|---|---|---|---|---|---|---|

| $R_i[n]$ para $n =$ | 7 | 10 | 5 | 8 | 1 | 2 | 4 | 9 | 0 | 3 | 6 |

|---------------------|---|----|---|---|---|---|---|---|---|---|---|

En otro ejemplo, en el que el símbolo de OFDM se genera de acuerdo con un modo de 32k, la dirección válida máxima predeterminada es de aproximadamente treinta y dos mil, el registro de desplazamiento de retroalimentación lineal tiene catorce niveles de registro con un polinomio generador para el registro de desplazamiento de retroalimentación lineal que es  $R'_i[13] = R'_{i-1}[0] \oplus R'_{i-1}[1] \oplus R'_{i-1}[2] \oplus R'_{i-1}[12]$ , y el código de permutación forma, con un bit adicional, una dirección  $R'_i[n]$  de quince bits para el símbolo de datos  $i^{\text{ésimo}}$  a partir del bit presente en el nivel de registro  $n^{\text{ésimo}}$   $R'_i[n]$  de acuerdo con la tabla:

|                          |    |    |    |    |   |   |    |    |   |   |   |   |    |   |

|--------------------------|----|----|----|----|---|---|----|----|---|---|---|---|----|---|

| Posiciones de bit $R'_i$ | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5 | 4 | 3 | 2 | 1  | 0 |

| Posiciones de bit $R_i$  | 6  | 5  | 0  | 10 | 8 | 1 | 11 | 12 | 2 | 9 | 4 | 3 | 13 | 7 |

En otros modos, la dirección válida máxima, el número de niveles del registro de desplazamiento de retroalimentación lineal, el polinomio generador y el código de permutación pueden ser adaptados de acuerdo con el número predeterminado de señales de sub-portadora por símbolo de OFDM en cada modo.

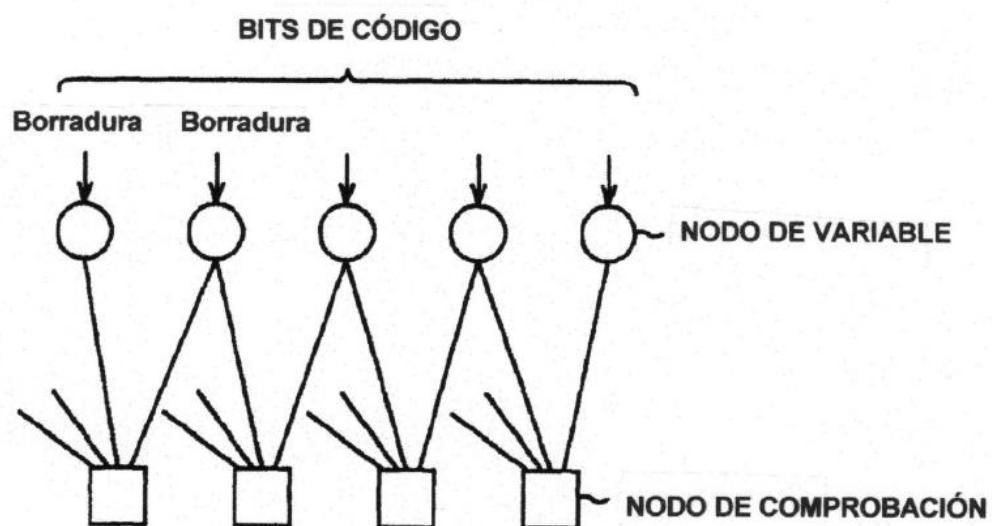

- 10 Las realizaciones de la presente invención incluyen un intercalador de bit que combina con un intercalador de símbolo para mejorar el rendimiento de un sistema de comunicación de OFMD, utilizando codificación de corrección de error de Comprobación de Paridad de Baja Densidad (LDPC). El intercalador de bits incluye un permutador para realizar, cuando dos o más bits de código de un código de Comprobación de Paridad de Baja Densidad (LPDC) son transmitidos y recibidos como un símbolo, un proceso de permutación que permuta los bits de código del código de LPDC de modo que una pluralidad de bits de código correspondientes a un valor de 1 en una fila arbitraria de una matriz de información correspondientes a bits de información del código de LPDC no son incorporados en el mismo símbolo.

- 15

El aparato de procesamiento de datos puede ser un dispositivo independiente y también puede ser un bloque interno incluido en un dispositivo, tal como un transmisor, o en otras realizaciones un receptor.

- 20 Los códigos de LDPC pueden proporcionar un comportamiento alto de corrección de error en trayectorias de comunicación, distintas de los canales Ruido Gaussiano Blanco Aditivo, que sea superior a códigos convolucionales o a códigos convolucionales Reed Solomon (RS) concatenados. Esto puede estar previsto en canales de comunicación que presenten errores de ráfaga que ocasionen borraduras. Así, existe una necesidad de proporcionar un método para incrementar la resistencia a los errores de ráfaga o borraduras mientras se conserva el comportamiento de las trayectorias de comunicación de AWGN.

- 25

La invención ha sido realizada en vista de las circunstancias anteriores y proporciona un aparato y un método de procesamiento de datos que puede incrementar la resistencia a los errores en bits de código de códigos de LDPC tales como los errores de ráfaga o las borraduras, combinando un intercalador de bits para los bits de datos codificados de LDPC con un intercalador de símbolo.

- 30 Es decir, de acuerdo con las realizaciones de la invención, la intercalación de paridad se realiza sobre un código de LDPC obtenido al realizar codificación de LDPC de acuerdo con una matriz de comprobación de paridad que incluye una matriz de paridad estructurada en forma gradual correspondiente a bits de paridad del código de LDPC de modo que los bits de código de LDPC son intercalados en diferentes posiciones de bits de paridad.

- 35 Se han previsto diversos modos operativos de un sistema de OFDM en los que encuentra aplicación la presente invención. Por ejemplo, con el fin de proporcionar un despliegue más disperso uniforme de transmisores de DVB dentro de una red de frecuencia única, se ha propuesto proporcionar el modo de 32k. Para implementar el modo de 32k, se debe proporcionar un intercalador de símbolo para mapear los símbolos de datos de entrada sobre las señales de sub-portadora del símbolo de OFDM.

- 40 Las realizaciones de la presente invención pueden proporcionar un aparato de procesamiento de datos operable como intercalador de símbolo para mapear símbolos de datos que han de ser comunicados sobre un símbolo de OFDM, que tenga aproximadamente treinta y dos mil señales de sub-portadora. En una realización, el número de señales de sub-portadora puede ser un valor comprendido sustancialmente entre veinticuatro mil y treinta y dos mil setecientos sesenta y ocho. Además, el símbolo de OFDM puede incluir sub-portadoras piloto, las cuales están dispuestas sobre un número de símbolos de sub-portadora piloto presentes en el símbolo de OFDM. Como tal, se puede proporcionar el modo de 32k, por ejemplo, para un estándar de DVB, tal como el DVB-72, DVB-Cable2, DVB-T o DVB-H.

- 45

El mapeo de símbolos de datos que van a ser transmitidos sobre las señales de sub-portadora de un símbolo de OFDM, donde el número de señales de sub-portadora es de aproximadamente treinta y dos mil, representa un problema técnico que requiere análisis de simulación y comprobación para establecer un polinomio generador apropiado para el registro de desplazamiento de retroalimentación lineal y el orden de permutación. Esto se debe a que el mapeo requiere que los símbolos sean intercalados sobre las señales de sub-portadora con el efecto de que los símbolos sucesivos procedentes de la corriente de datos estén separados en frecuencia mediante una cantidad

lo más grande posible con el fin de optimizar el comportamiento de los esquemas de codificación de corrección de error.

Como se explicará, se ha descubierto a partir de análisis de comportamiento de simulación que el polinomio generador para el registro de desplazamiento de retroalimentación lineal en combinación con el orden de circuito de permutación indicado anteriormente, proporciona un buen rendimiento. Además, al proporcionar una disposición que puede implementar generación de dirección para uno de entre el modo de 2k, el modo de 4k y el modo de 8k cambiando las derivaciones del polinomio generador para el registro de desplazamiento de retroalimentación lineal y para el orden de permutación, se puede proporcionar una implementación de bajo coste del intercalador de símbolo para el modo de 32k. Además, se puede cambiar un transmisor y un receptor entre el modo de 1k, el modo de 2k, el modo de 4k, el modo de 8k, el modo de 16k y el modo de 32k cambiando el polinomio generador y los órdenes de permutación. Esto puede ser efectuado en software (o mediante señalización incorporada), con lo que se proporciona una implementación flexible.

Diversos aspectos y características de la presente invención están definidos en las reivindicaciones anexas. Los aspectos adicionales de la invención incluyen un aparato de procesamiento de datos que se puede hacer funcionar para mapear símbolos recibidos desde un número predeterminado de señales de sub-portadora de un símbolo Multiplexado por División de Frecuencias Ortogonales (OFDM) adentro de una corriente de símbolos de datos, así como un receptor.

#### Breve descripción de los dibujos

Las realizaciones de la presente invención van a ser descritas ahora a título de ejemplo únicamente con referencia a los dibujos que se acompañan, en los que las partes iguales han sido dotadas de números de referencia correspondientes, y en los que:

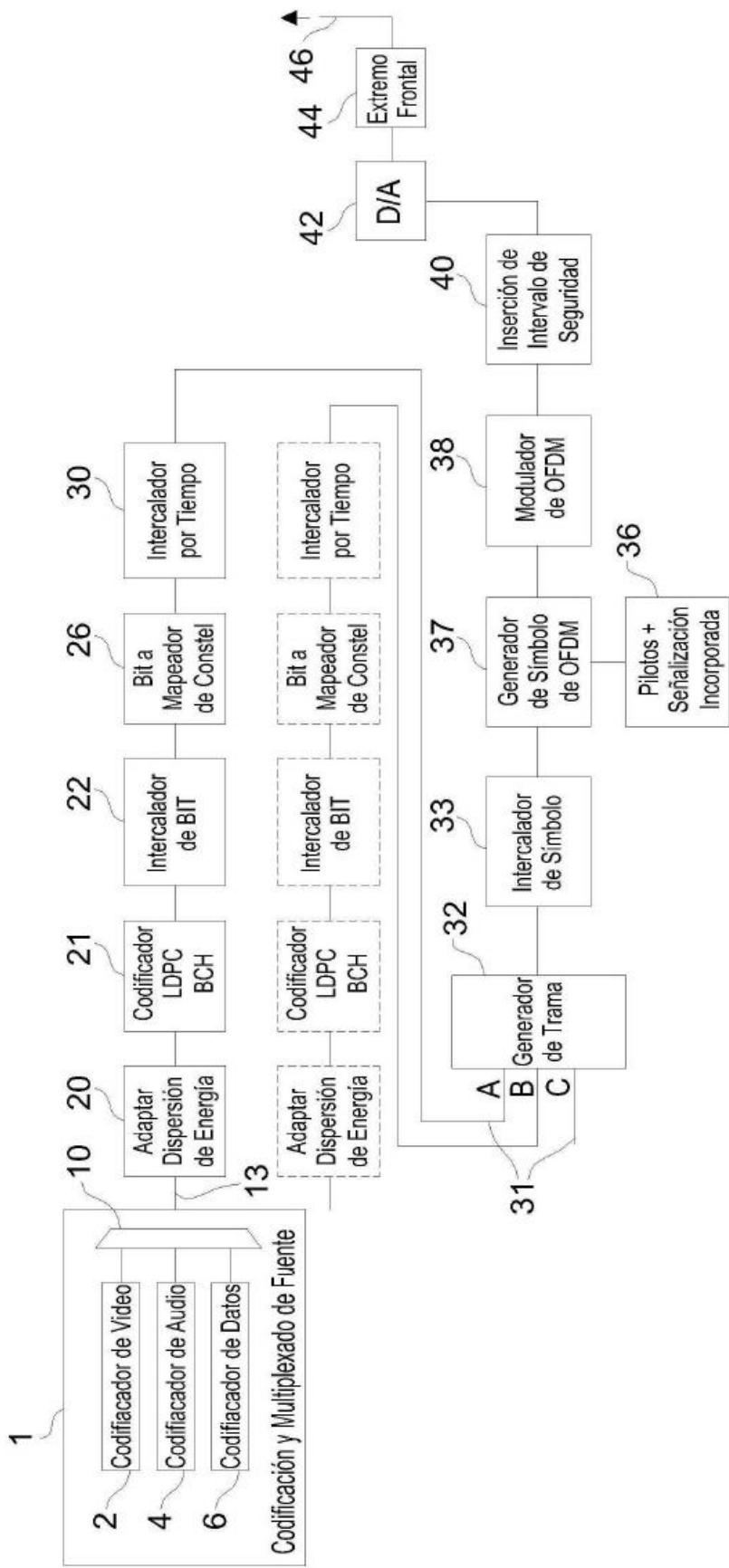

la figura 1 es un diagrama de bloques esquemático de un transmisor de OFDM codificado que puede ser usado, por ejemplo, con el estándar DVB-T2;

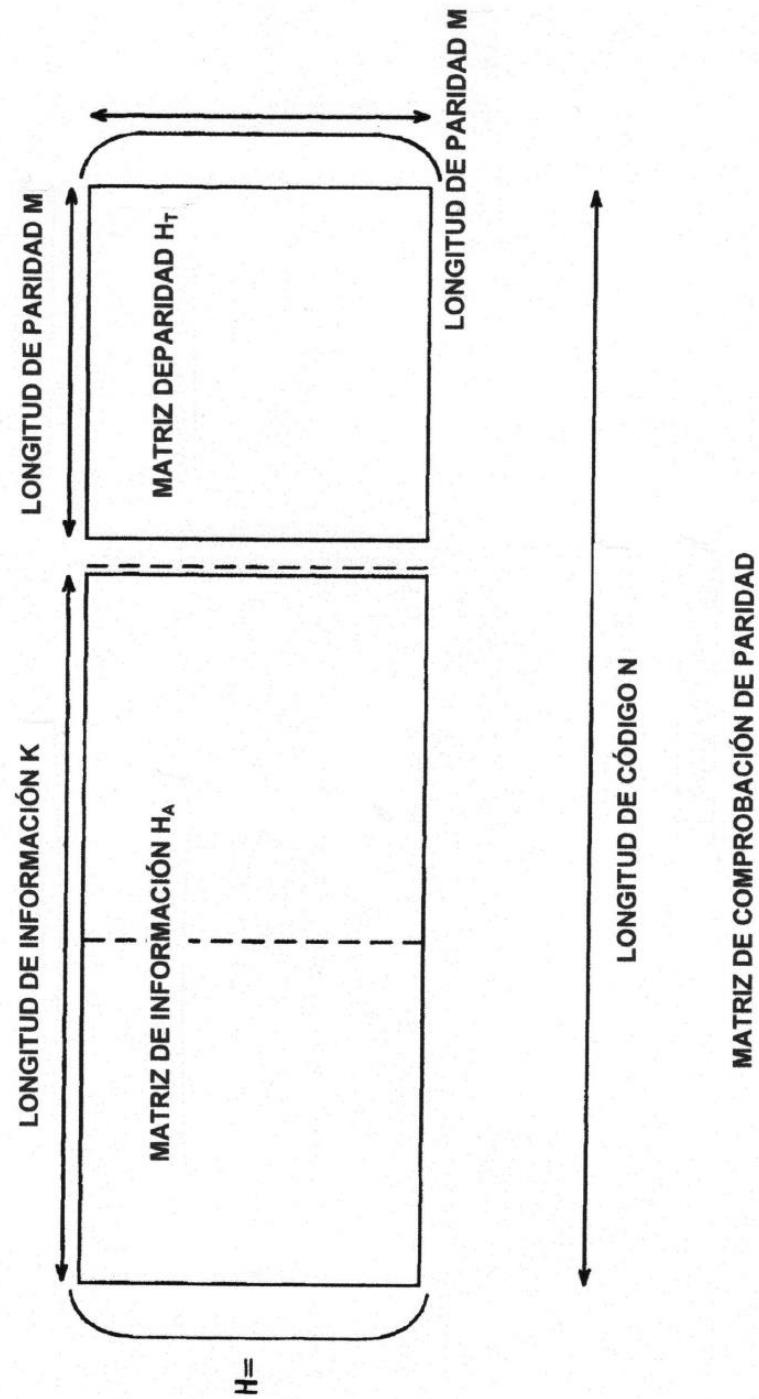

la figura 2 ilustra un ejemplo de matriz H de comprobación de paridad de un código de LDPC;

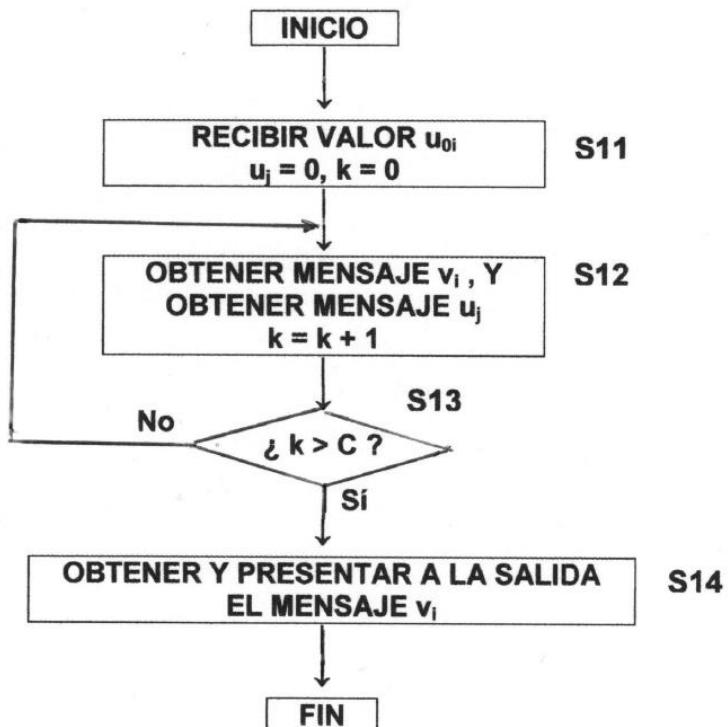

25 la figura 3 es un diagrama de flujo que ilustra un procedimiento para la descodificación de un código de LDPC;

la figura 4 ilustra un ejemplo de matriz de comprobación de paridad de un código de LDPC;

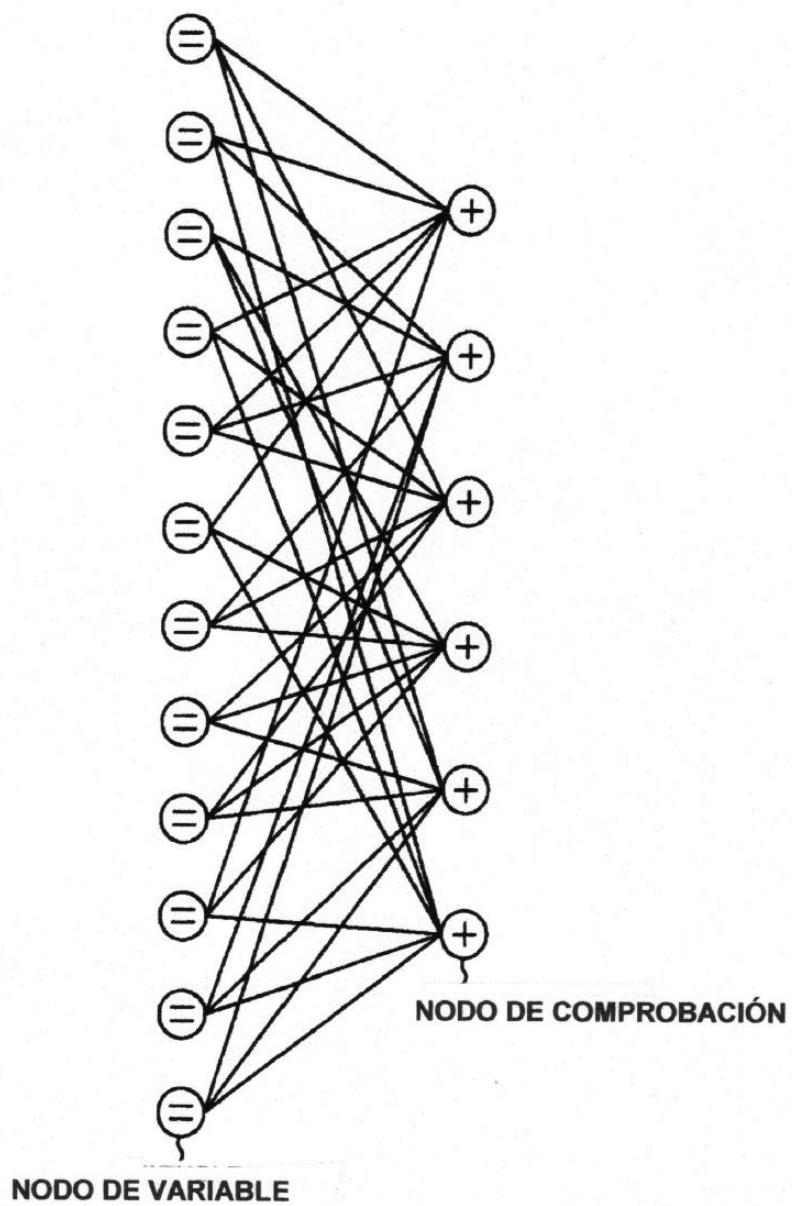

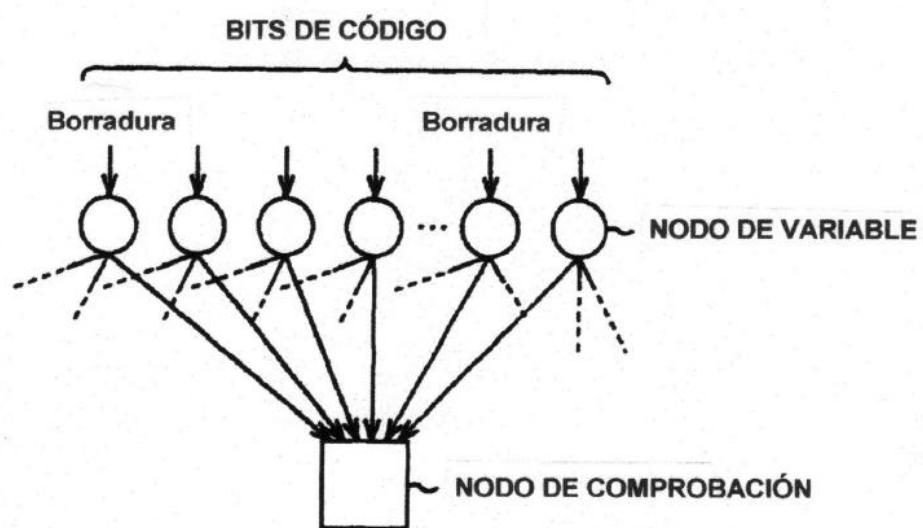

la figura 5 ilustra un gráfico de Tanner de una matriz de comprobación de paridad;

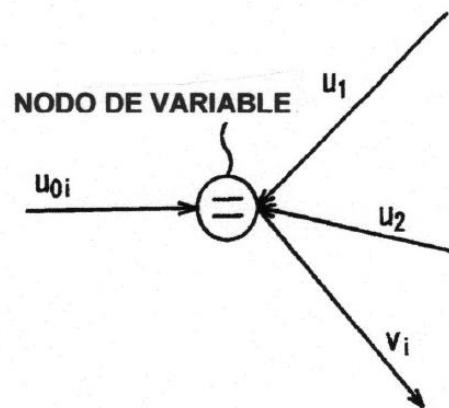

la figura 6 ilustra un nodo de variable;

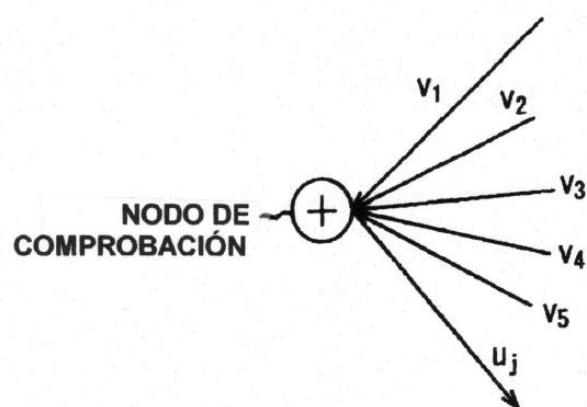

la figura 7 ilustra un nodo de comprobación;

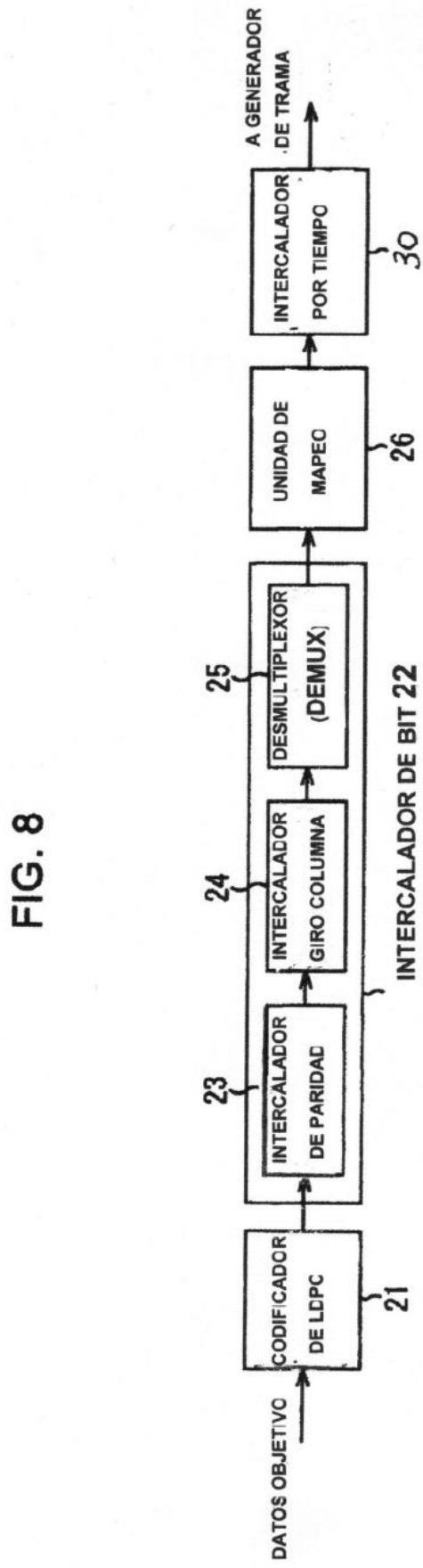

30 la figura 8 es un diagrama de bloques esquemático que ilustra un ejemplo de configuración de un transmisor;

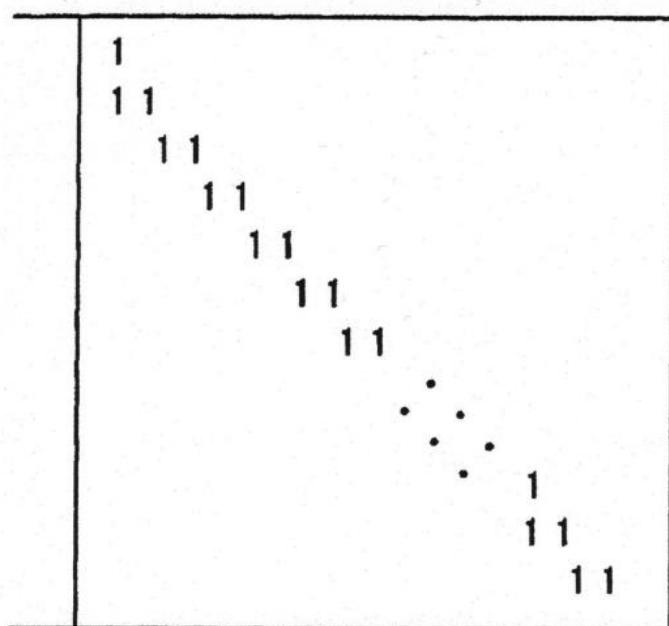

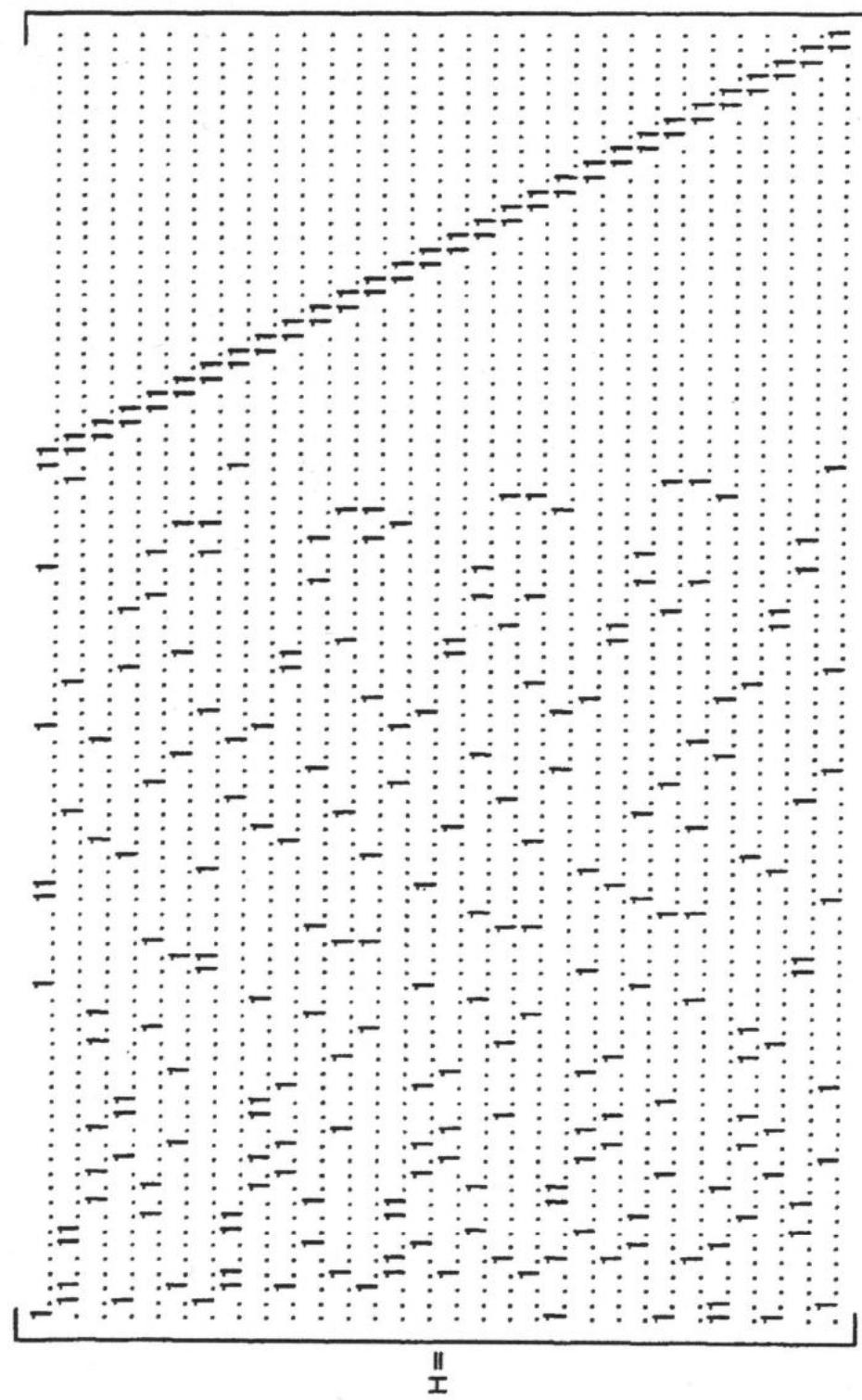

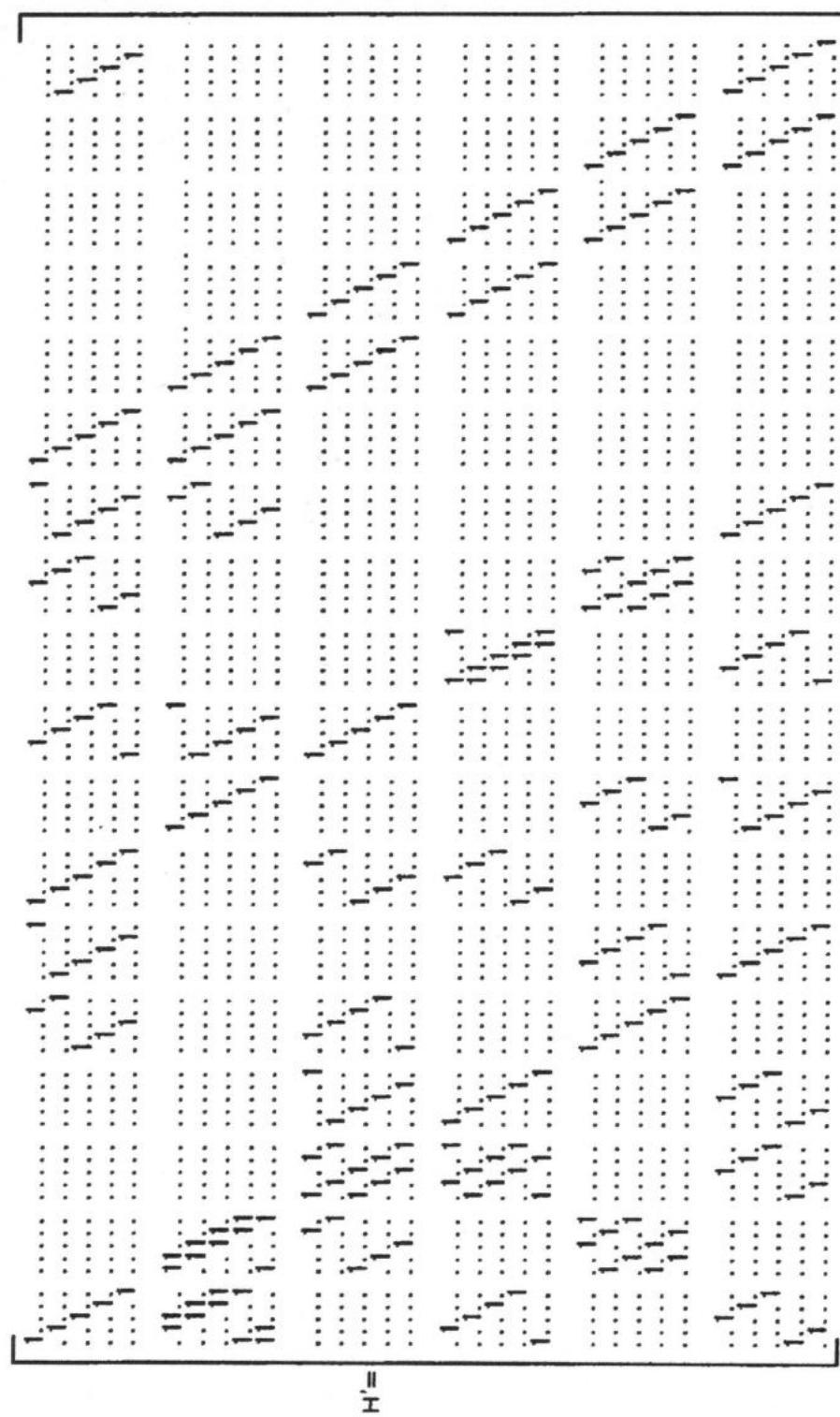

la figura 9 es una matriz de comprobación de paridad;

la figura 10 ilustra una matriz de paridad;

las figuras 11a y 11b ilustran una matriz de comprobación de paridad de un código de LDPC y pesos de columna definidos en la especificación DVB-S.2;

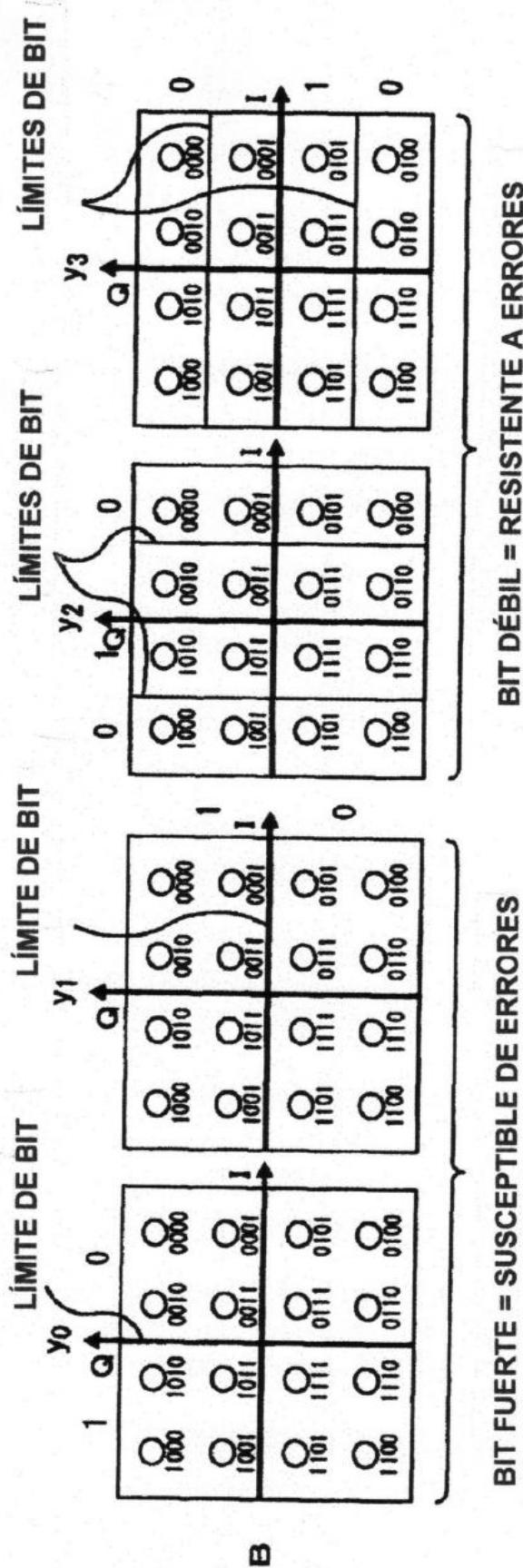

35 las figuras 12a y 12b ilustran una disposición de puntos de señal de 16QAM;

la figura 13 ilustra una disposición de puntos de señal de 64QAM;

la figura 14 ilustra una disposición de puntos de señal de 64QAM

la figura 15 ilustra una disposición de puntos de señal de 64QAM;

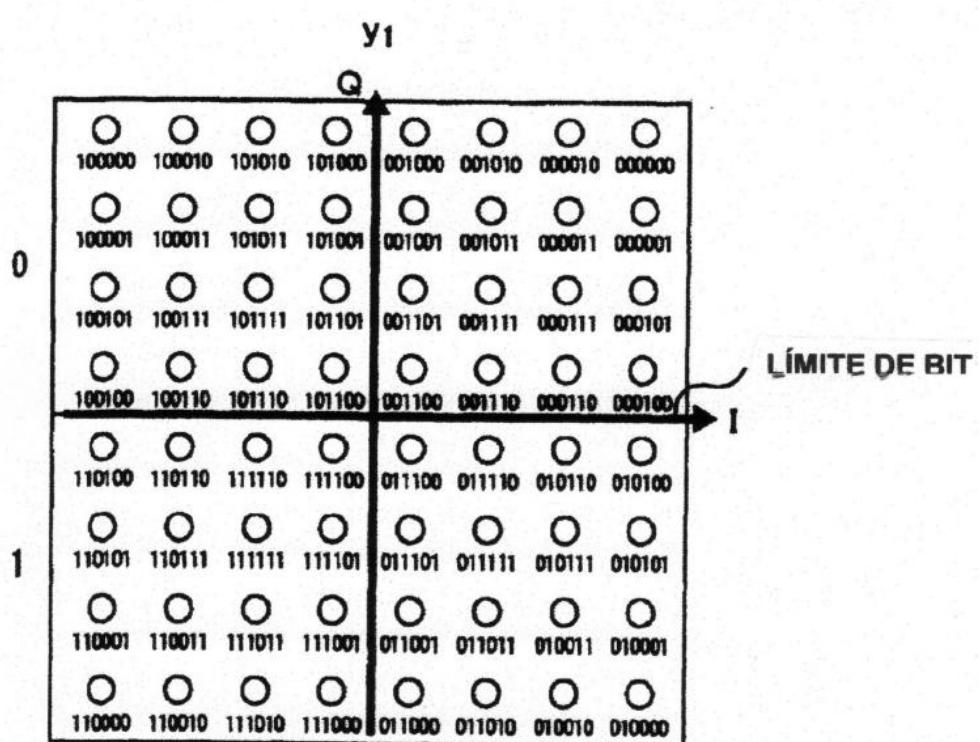

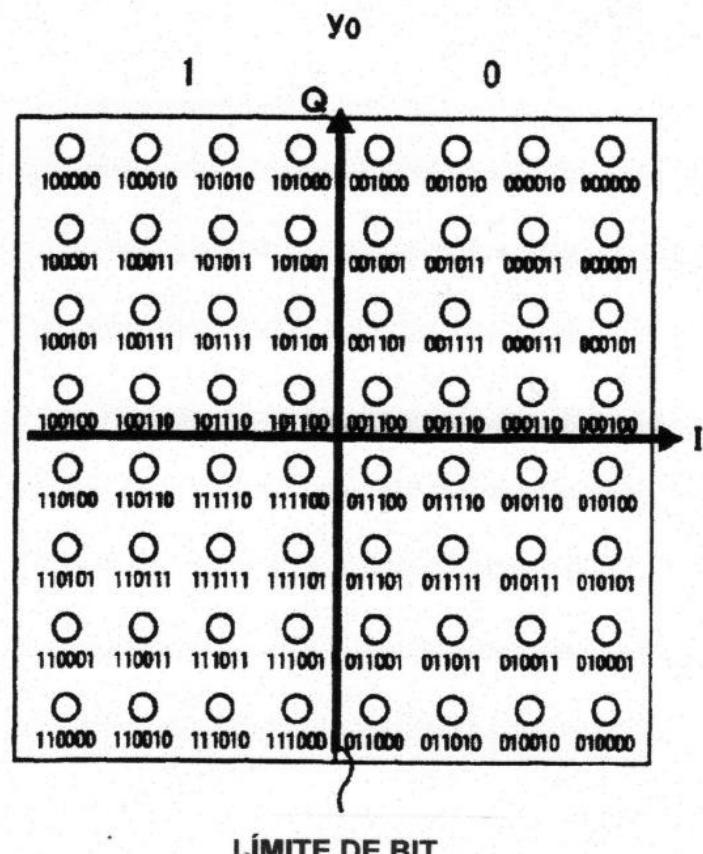

las figuras 16a a 16d ilustran la operación de un desmultiplexor 25;

40 las figuras 17a a 17d ilustran la operación del desmultiplexor 25;

la figura 18 ilustra un gráfico de Tanner para descodificar un código de LDPC;

las figuras 19a y 19b ilustran una matriz de paridad  $H_T$  que tiene una estructura de forma gradual y un gráfico de Tanner correspondiente a la matriz  $H_T$  de paridad;

45 la figura 20 ilustra una matriz  $H_T$  de paridad de una matriz H de comprobación de paridad correspondiente a un código de LDPC después de haber realizado intercalación de paridad sobre el código de LDPC;

- las figuras 21a y 21b ilustran una matriz de comprobación de paridad convertida;

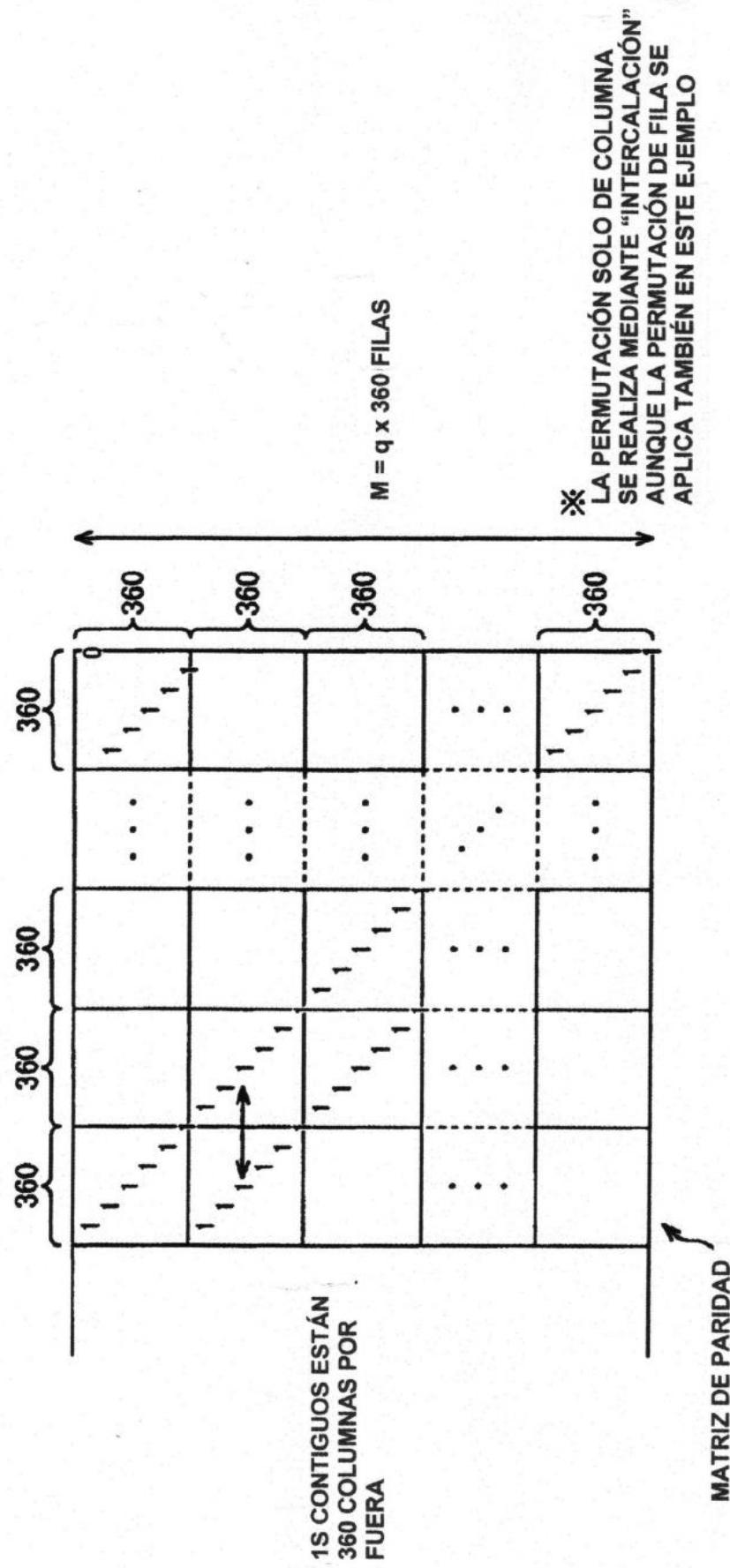

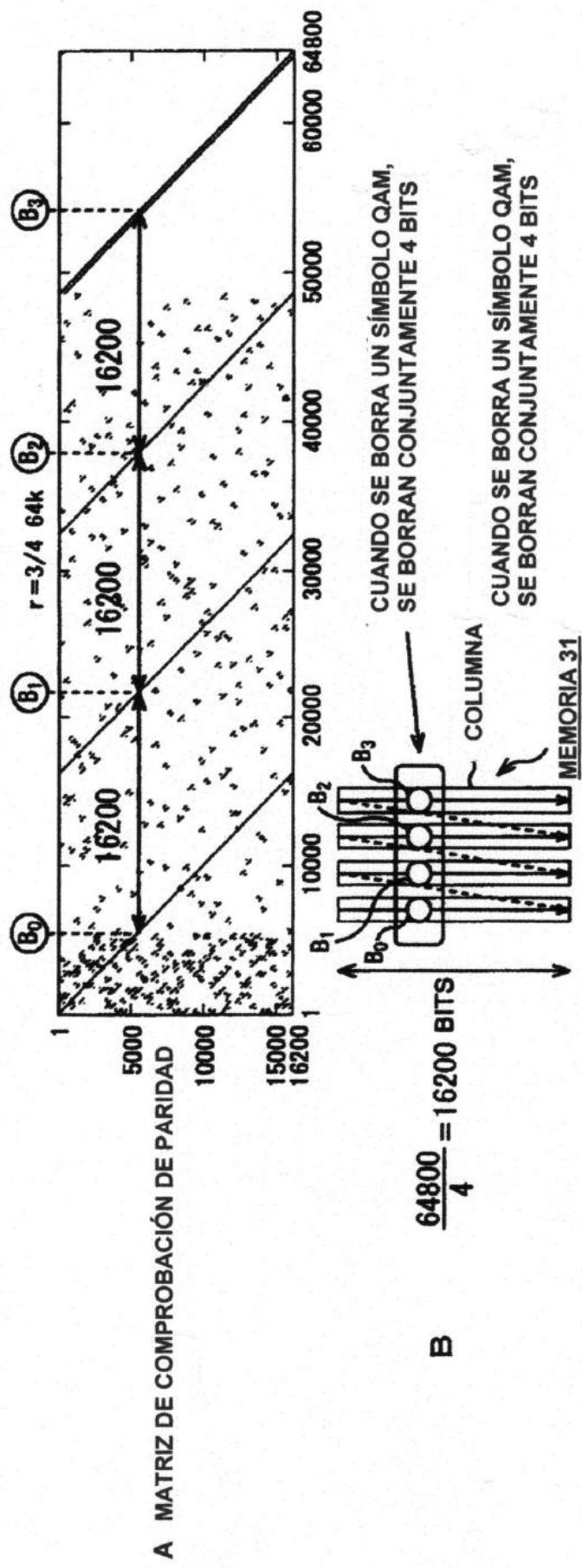

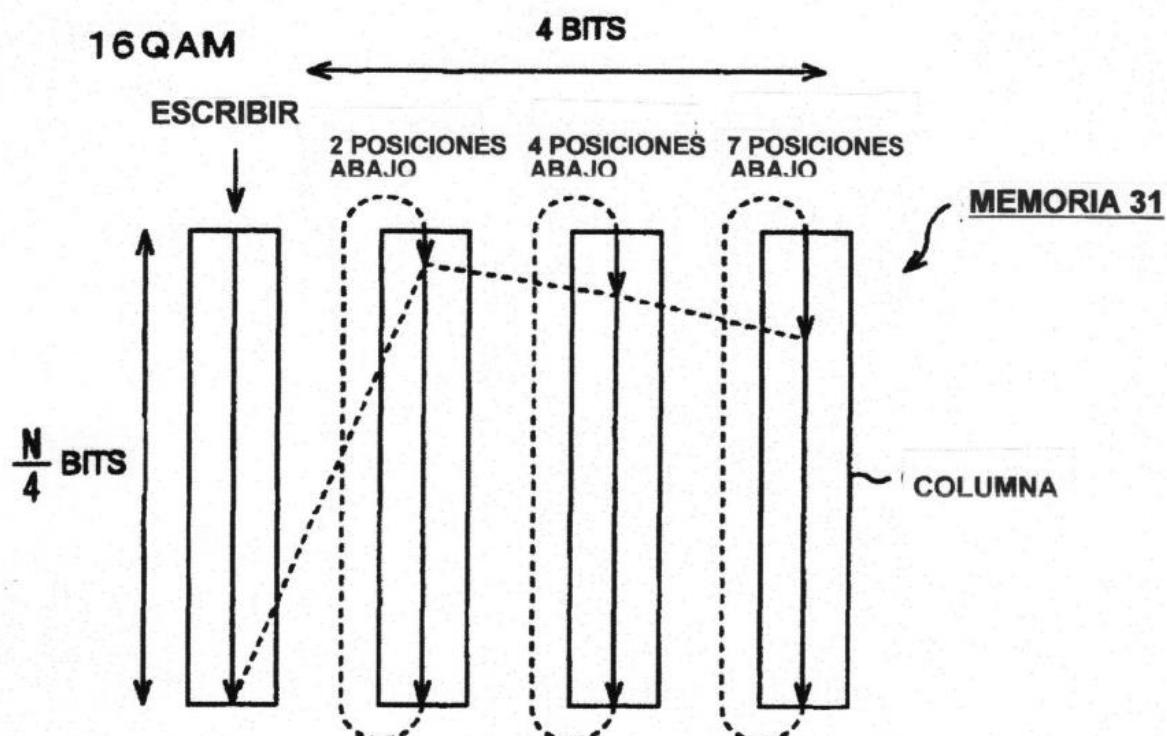

- la figura 22 ilustra la operación de un intercalador 24 por giro de columna;

- la figura 23 ilustra el número de columnas de una memoria 31 requeridas para intercalación por giro de columna y las direcciones de las posiciones de inicio de escritura;

- 5 la figura 24 ilustra el número de columnas de la memoria 31 requeridas para intercalación por giro de columna y las direcciones de las posiciones de inicio de escritura;

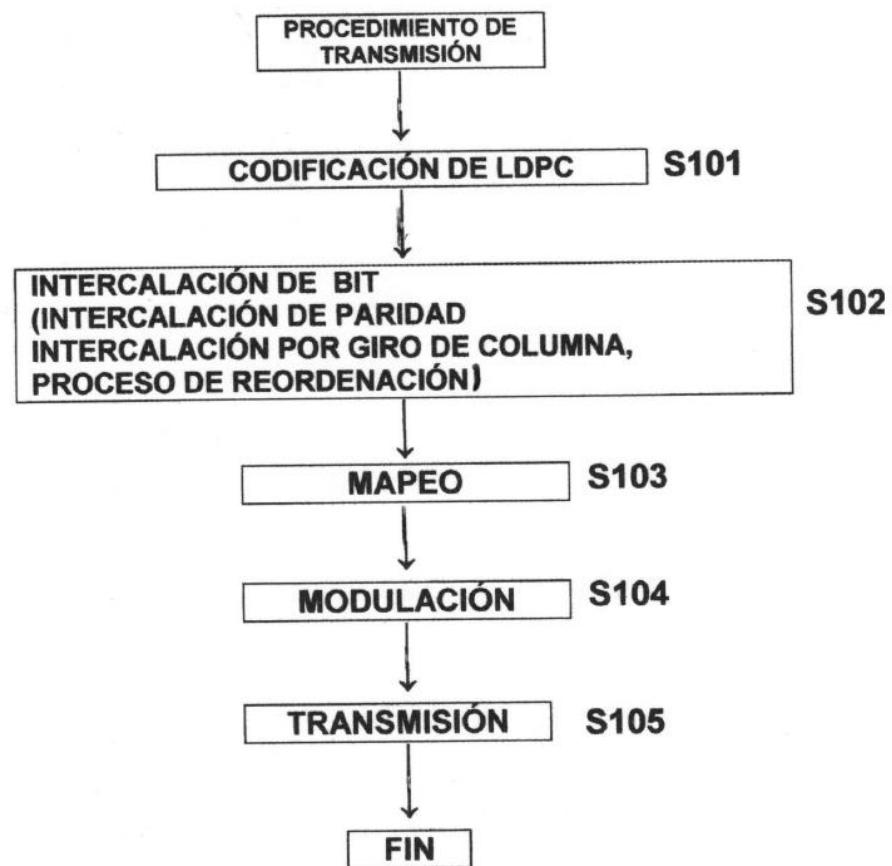

- la figura 25 es un diagrama de flujo que ilustra un procedimiento de transmisión;

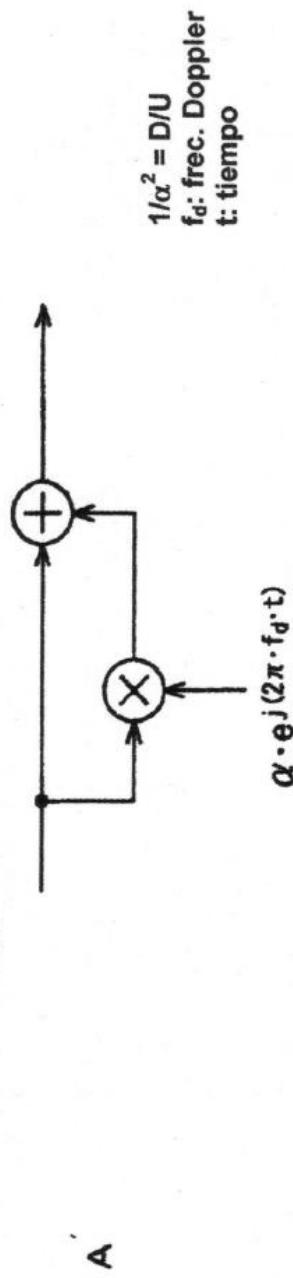

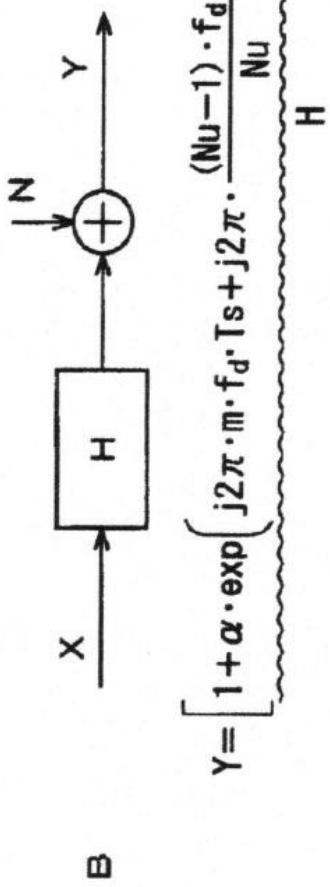

- las figuras 26a y 26b ilustran un modelo de trayectoria de comunicación empleada en simulaciones;

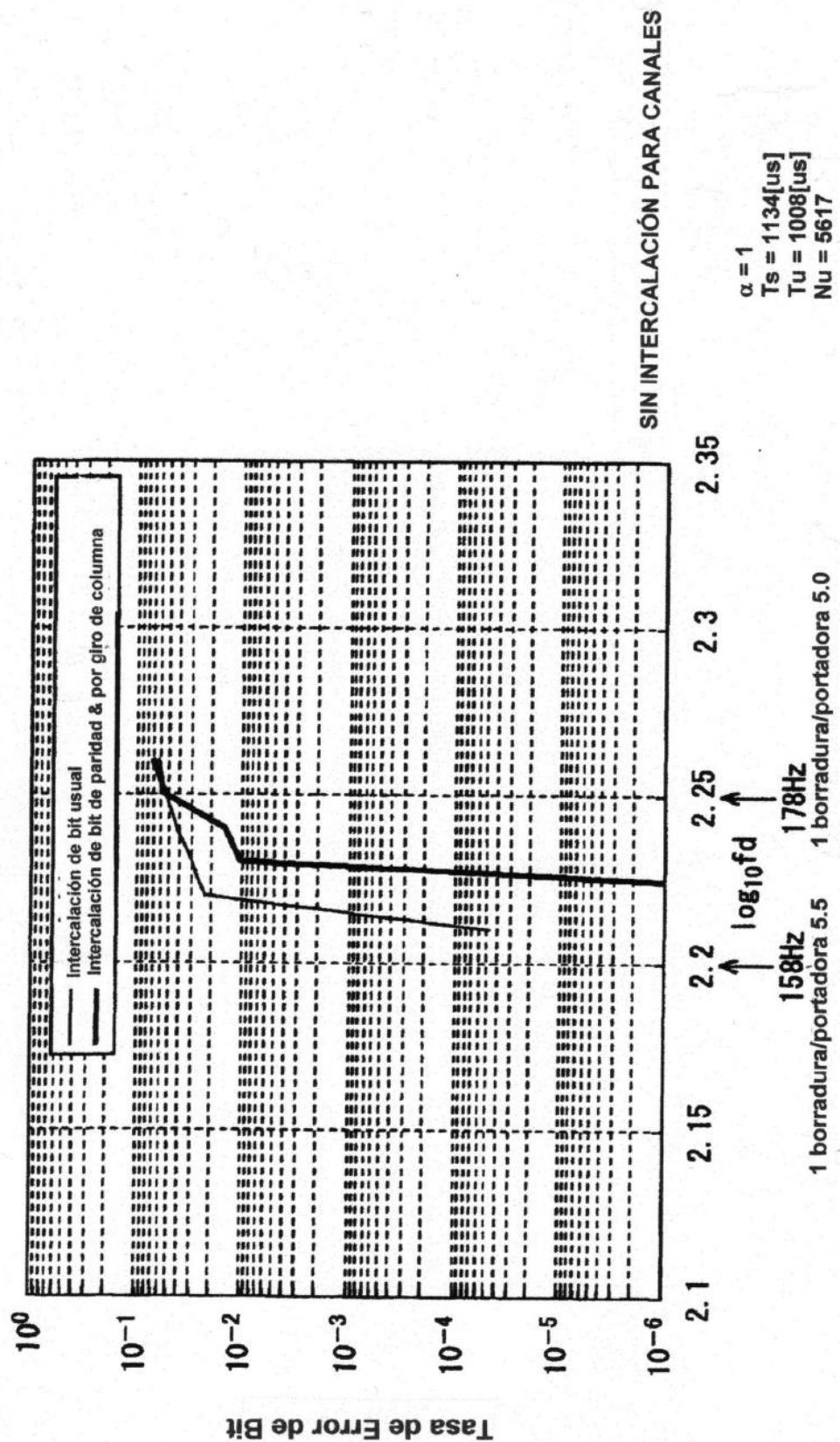

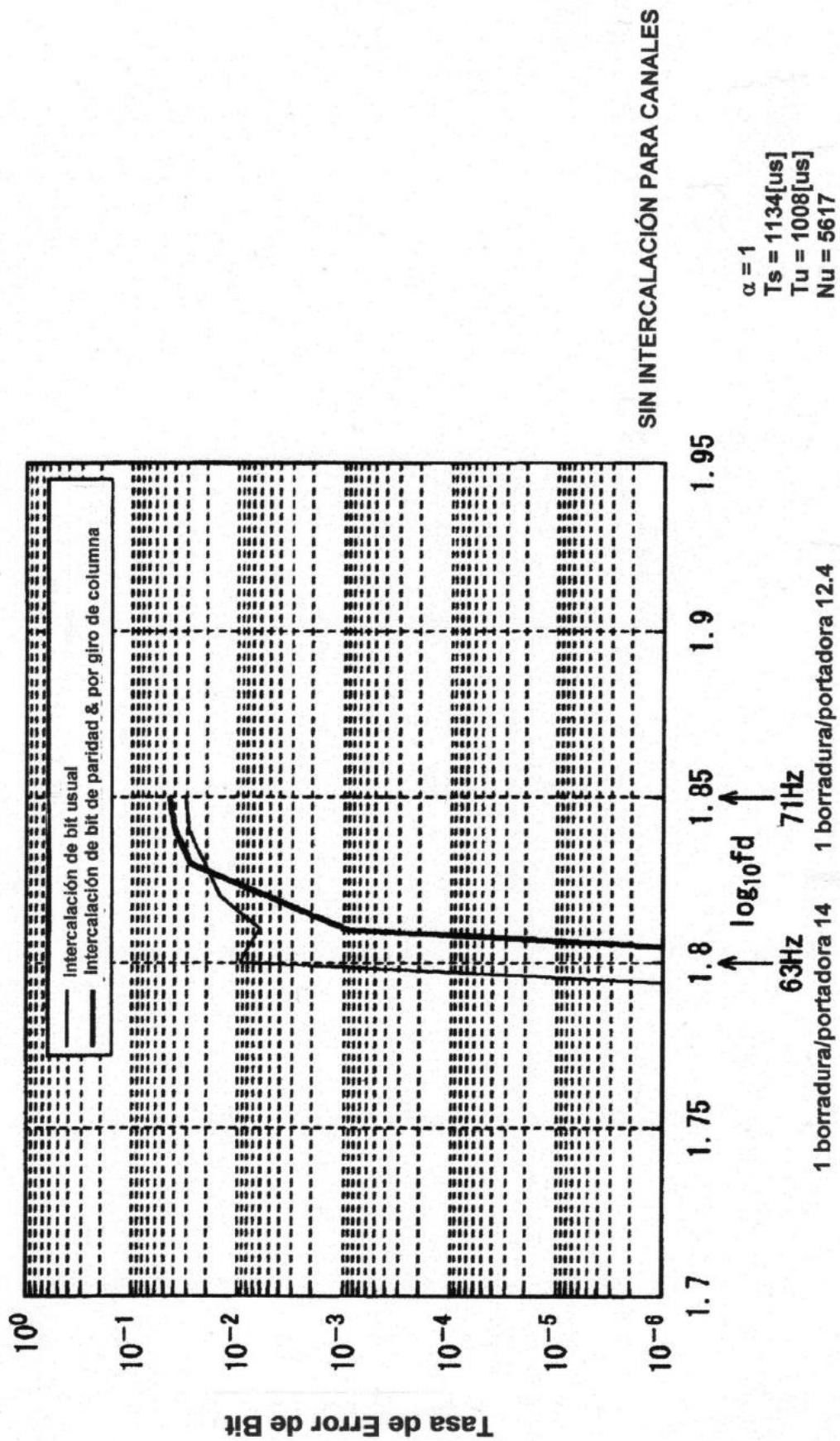

- la figura 27 ilustra relaciones entre frecuencias de Doppler  $f_d$  y tasas de error obtenidas a partir de simulaciones;

- 10 la figura 28 ilustra relaciones entre frecuencias de Doppler  $f_d$  y tasas de error obtenidas a partir de simulaciones;

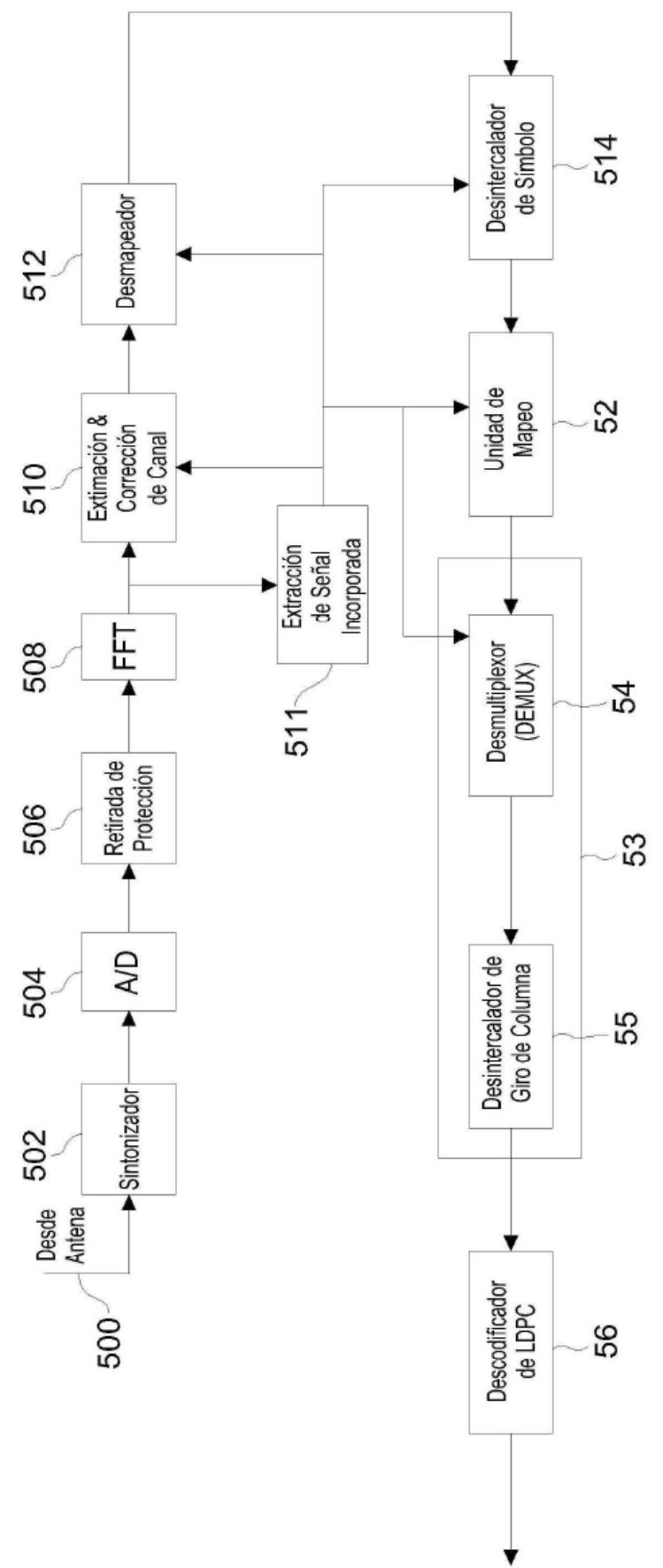

- la figura 29 es un diagrama de bloques esquemático de un receptor de OFDM codificado que puede ser usado, por ejemplo, con el estándar DVB-T2;

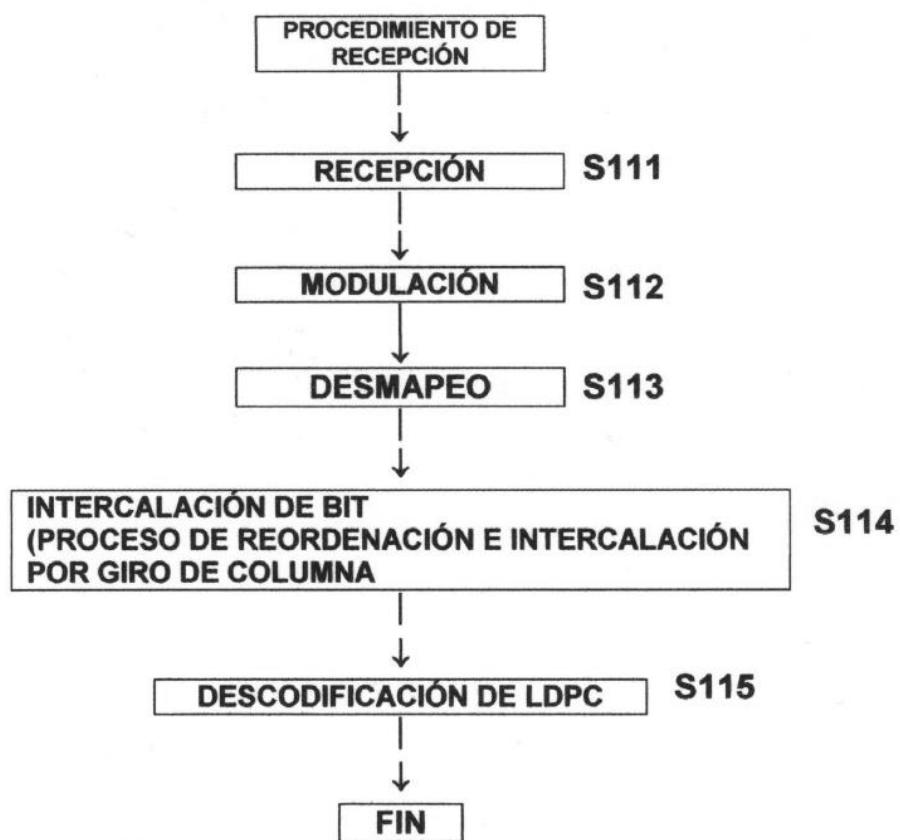

- la figura 30 es un diagrama de flujo que ilustra un procedimiento de recepción;

- la figura 31 ilustra un ejemplo de matriz de comprobación de paridad de un código de LPDC;

- 15 la figura 32 ilustra una matriz (matriz de comprobación de paridad convertida) obtenida al realizar permutación de fila y permutación de columna sobre la matriz de comprobación de paridad;

- la figura 33 ilustra la matriz de comprobación de paridad convertida dividida en matrices unidad de 5x5;

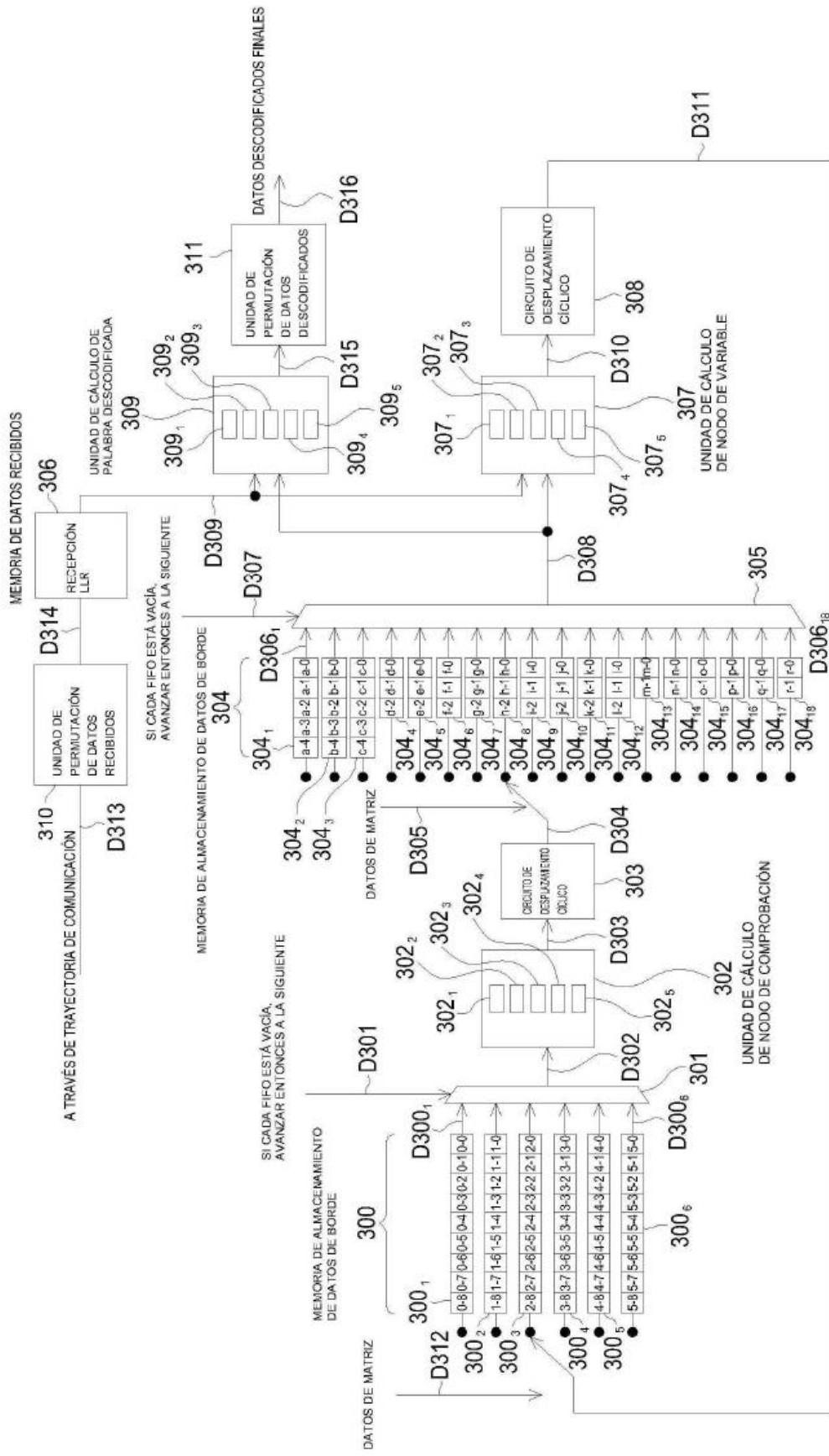

- la figura 34 es un diagrama de bloques que ilustra un ejemplo de configuración de un dispositivo de descodificación que realiza cálculos de nodos P en paralelo;

- 20 la figura 35 muestra un ejemplo de configuración de un descodificador 56 de LDPC;

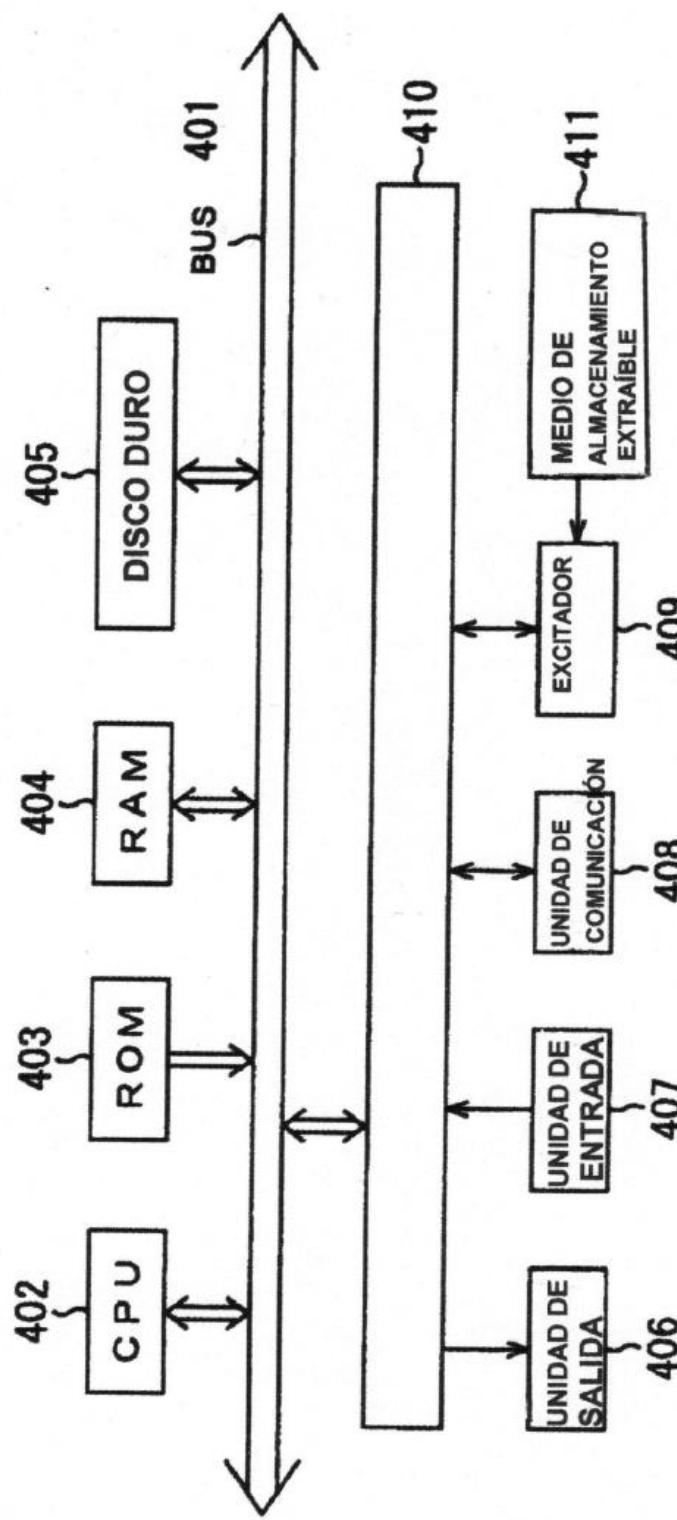

- la figura 36 es un diagrama de bloques que ilustra un ejemplo de configuración de una realización de un ordenador al que se aplica la invención;

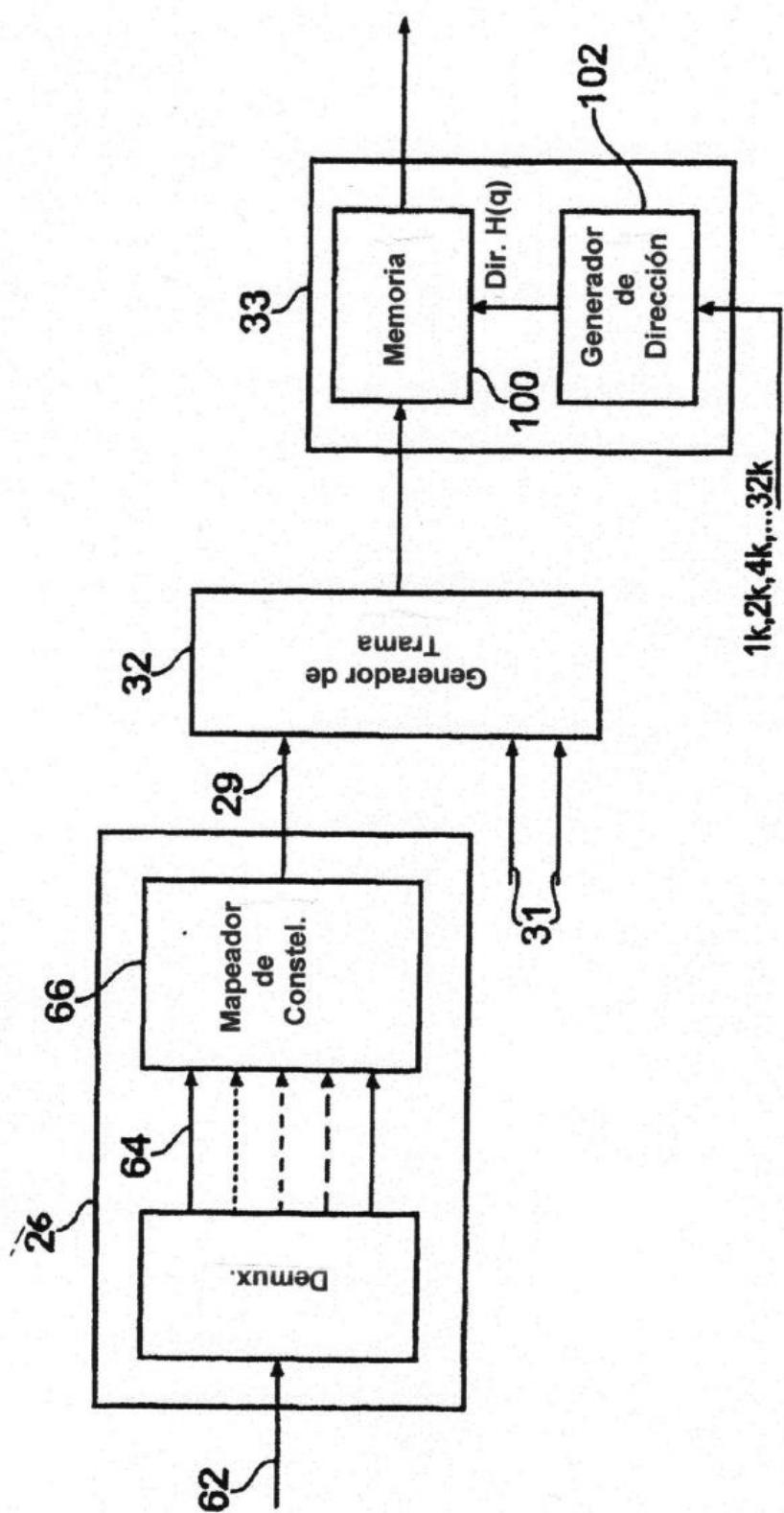

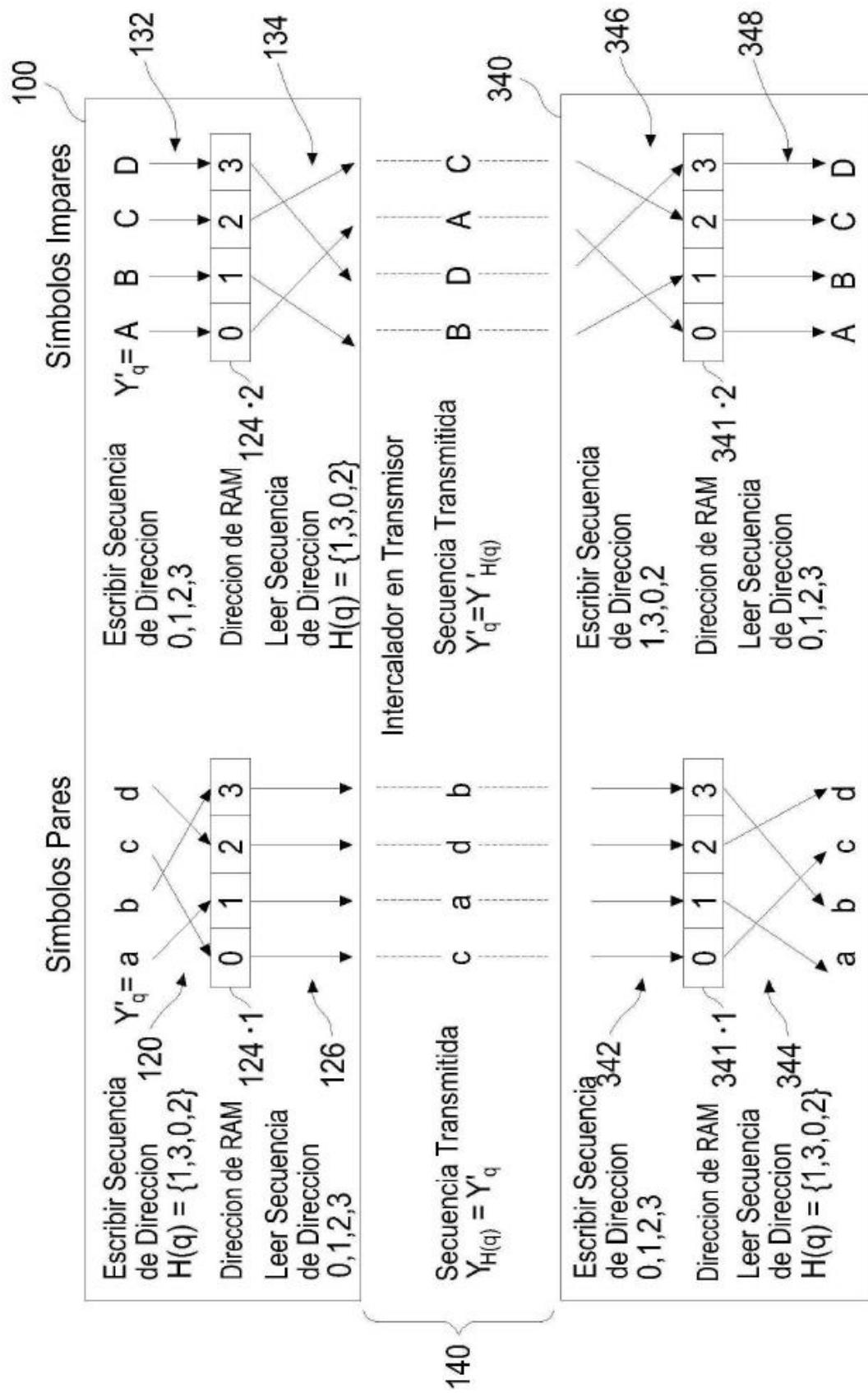

- la figura 37 es un diagrama de bloques de partes del transmisor mostrado en la figura 1 en el que un mapeador de símbolo y un generador de trama ilustran la operación de un intercalador;

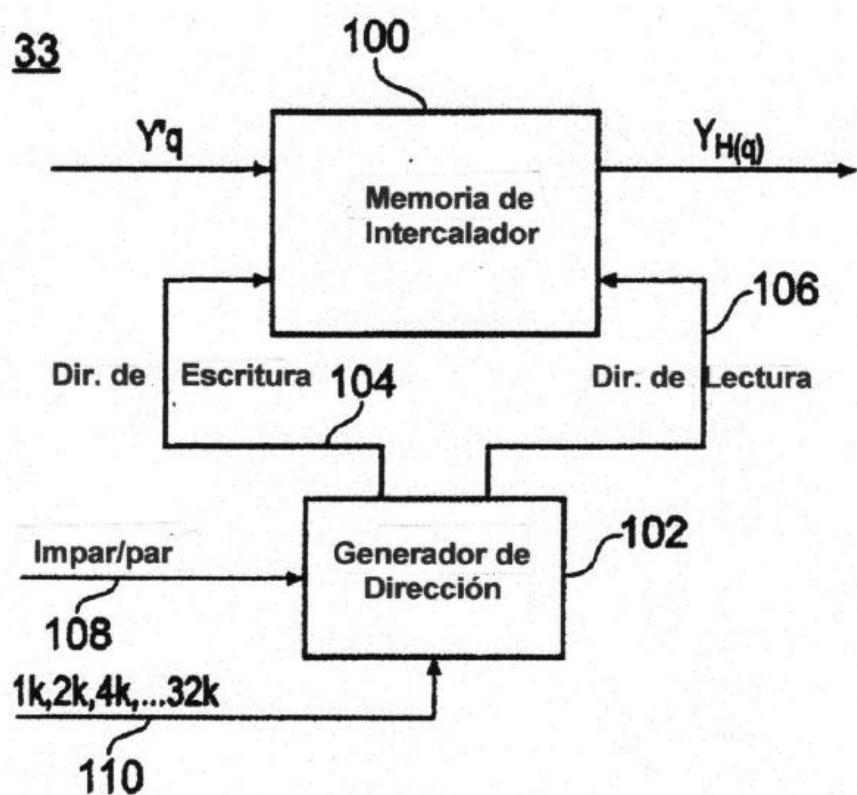

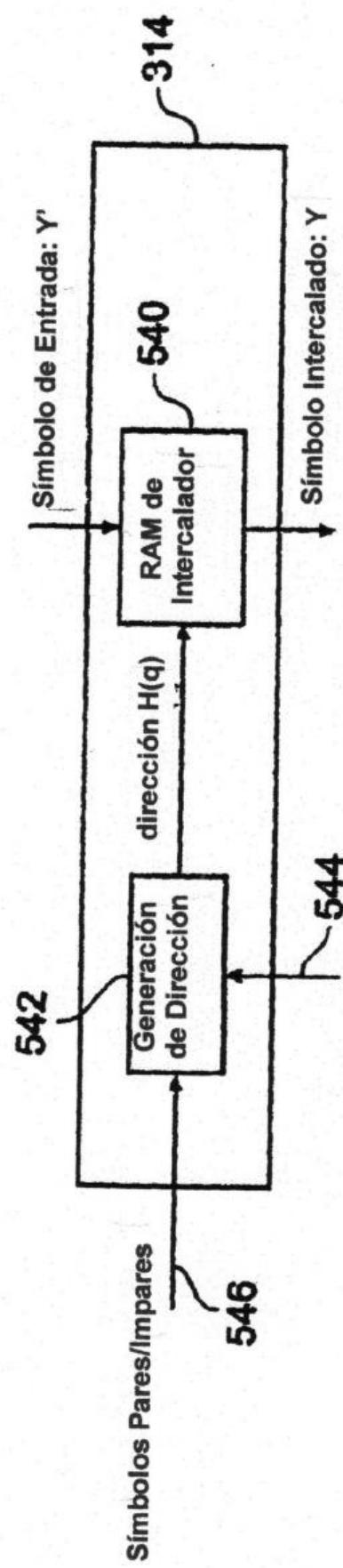

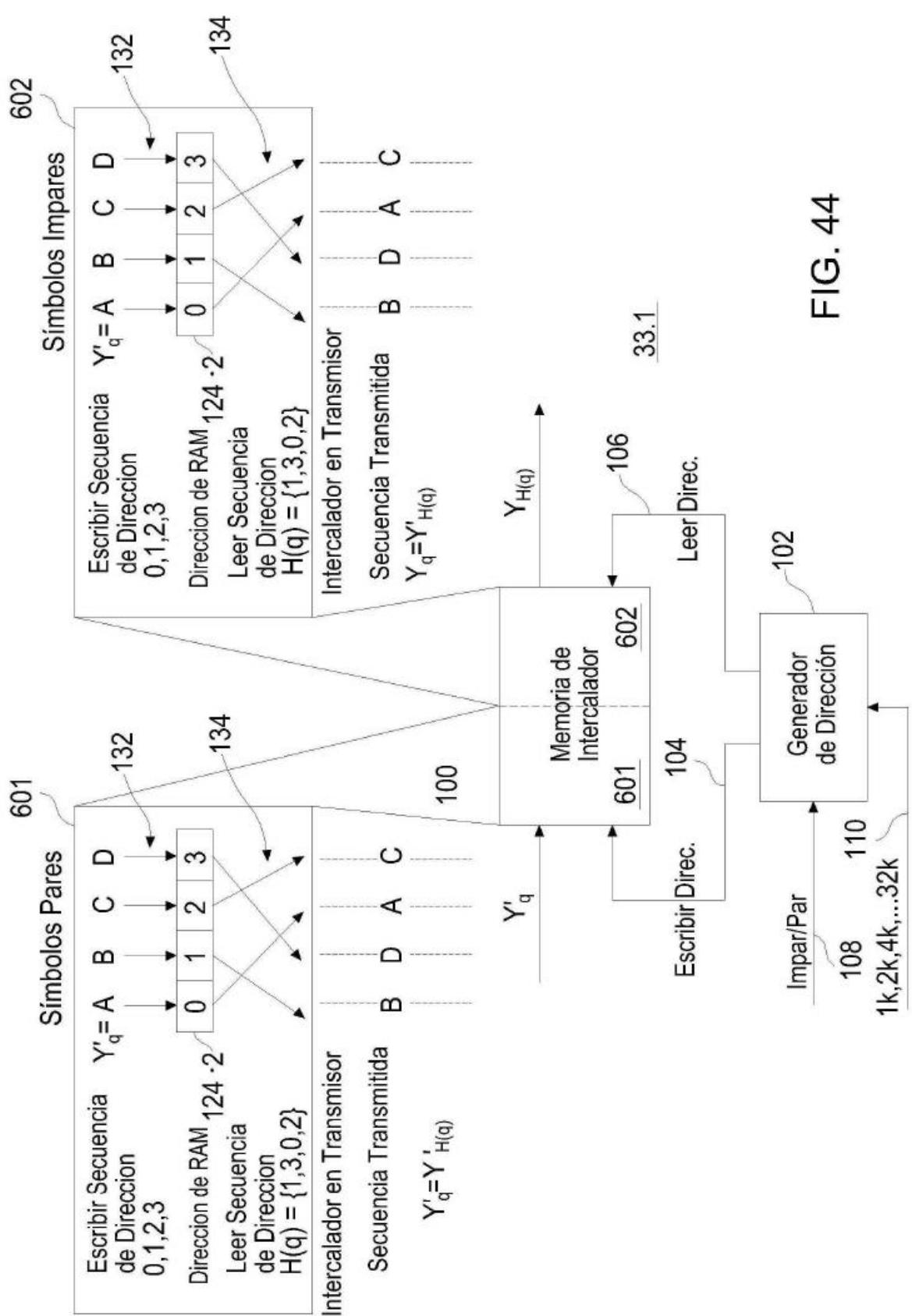

- 25 la figura 38 es un diagrama de bloques esquemático del intercalador de símbolo mostrado en la figura 37;

- la figura 39 es un diagrama de bloques esquemático de una memoria de intercalador mostrada en la figura 38, y del correspondiente símbolo desintercalador en el receptor;

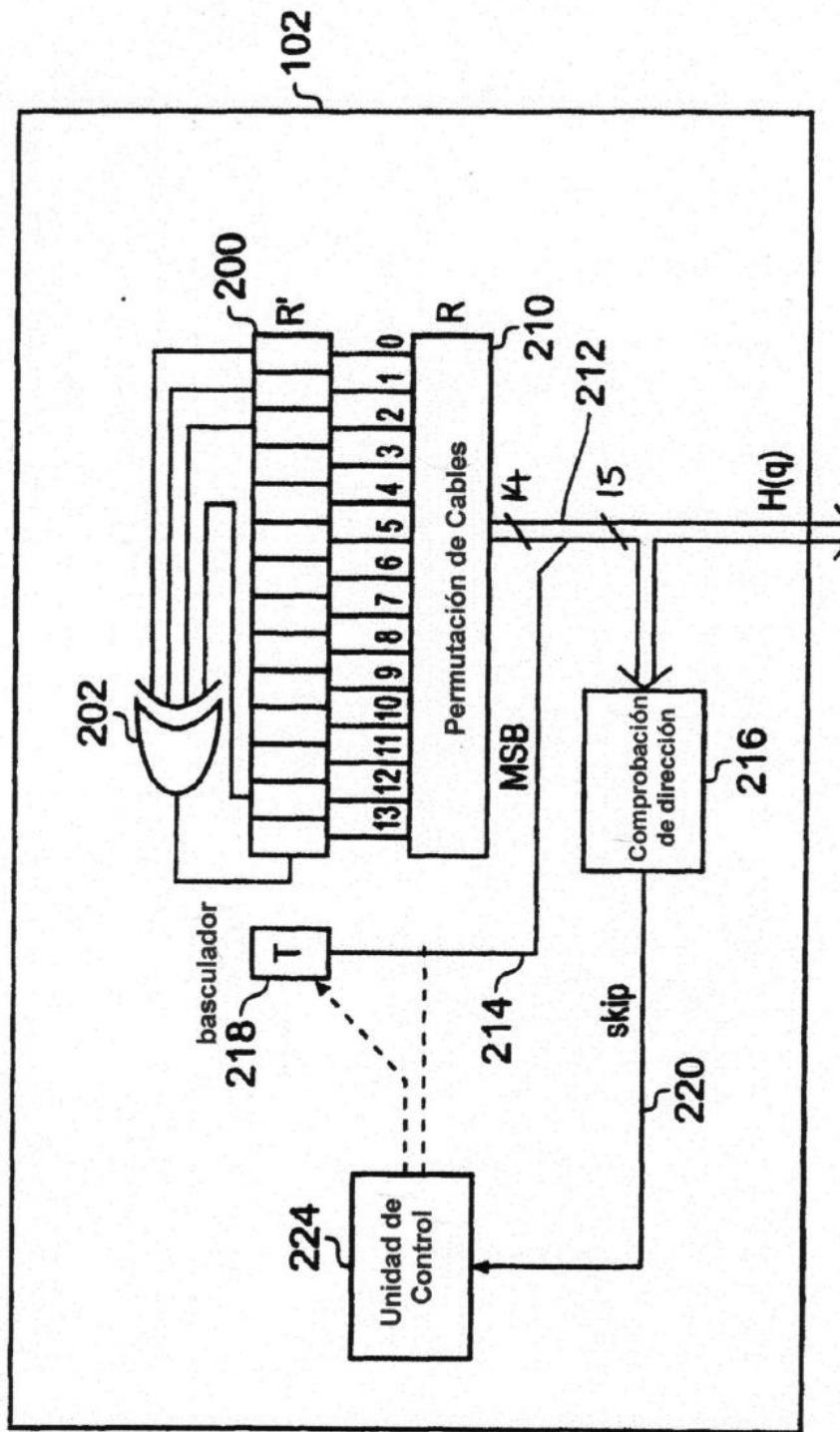

- la figura 40 es un diagrama esquemático de bloques del generador de dirección mostrado en la figura 38 para el modo de 32k;

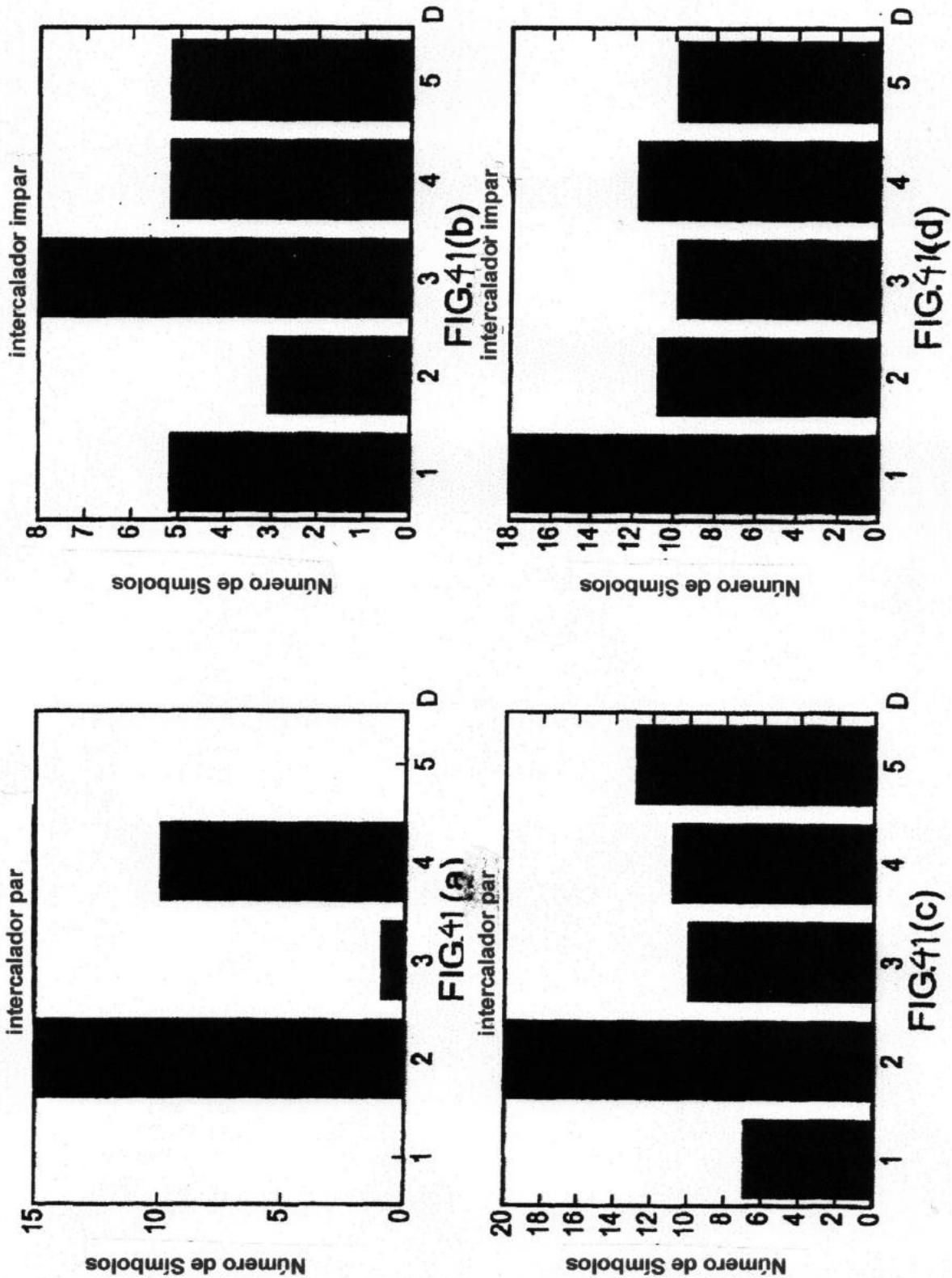

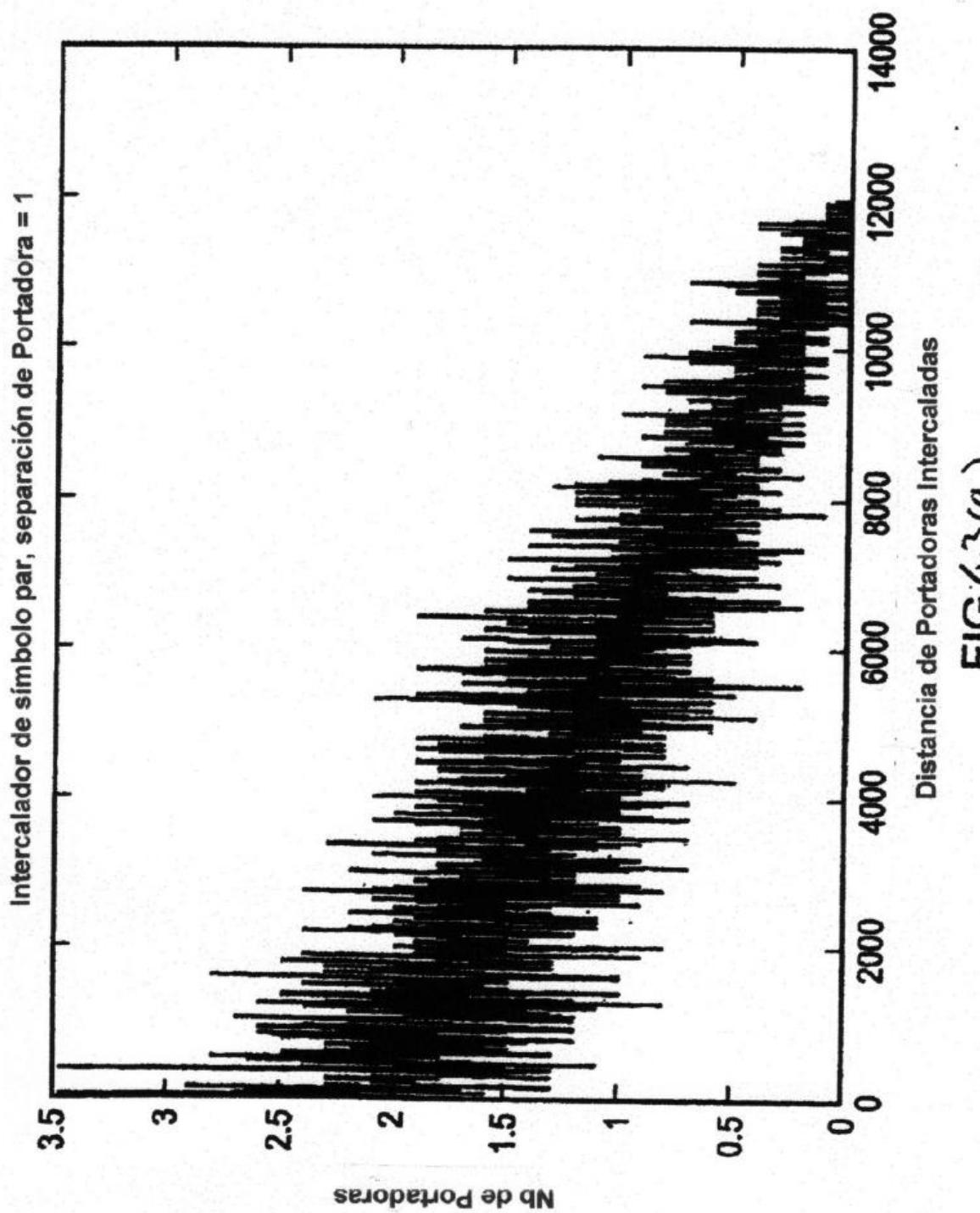

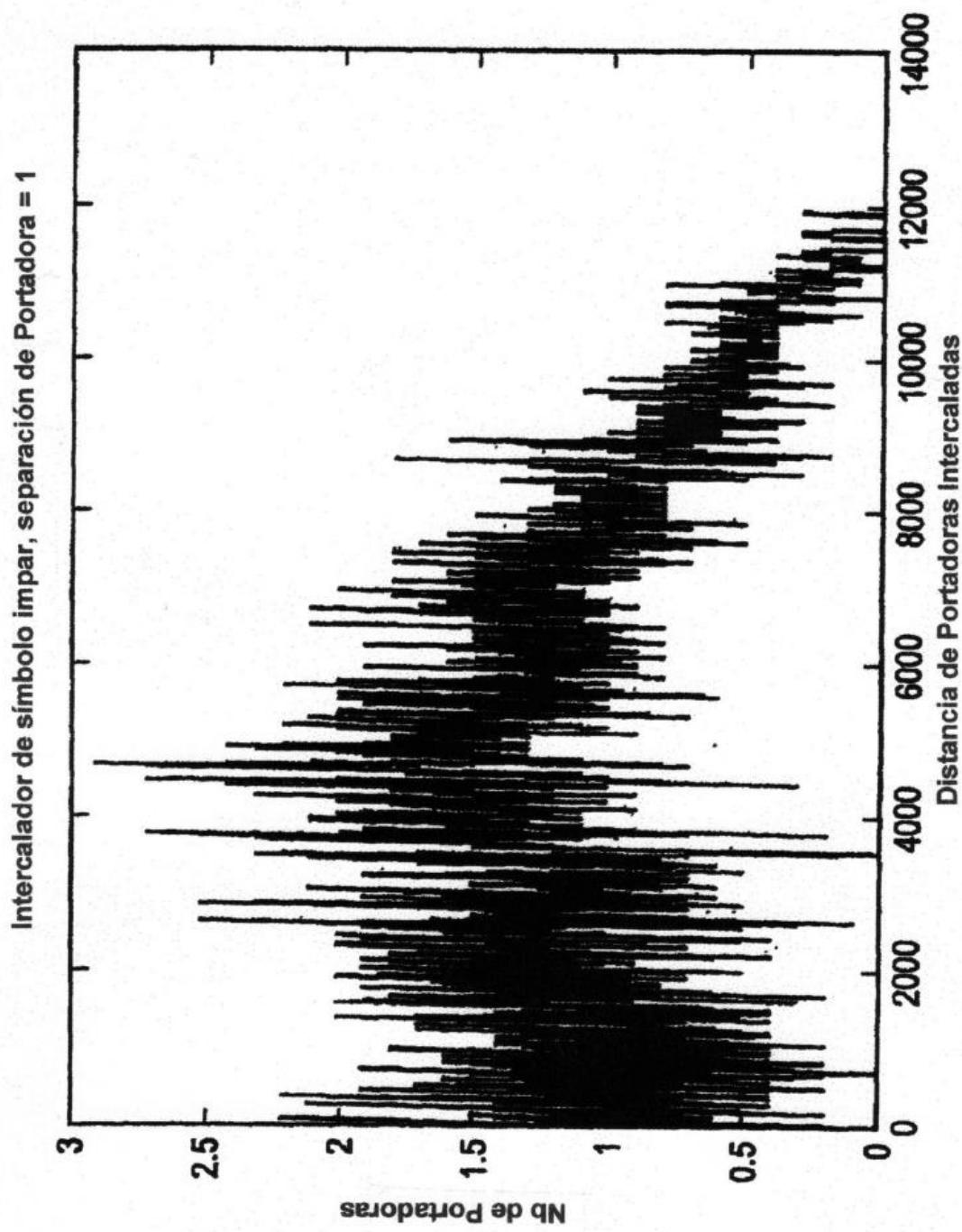

- 30 la figura 41(a) es un diagrama que ilustra los resultados para un intercalador que utiliza el generador de dirección mostrado en la figura 40 para símbolos pares, y la figura 41(b) es un diagrama que los ilustra resultados de simulación de diseño para símbolos impares, mientras que la figura 41(c) es un diagrama que ilustra resultados comparativos para un generador de dirección que utiliza un código de permutación diferente para símbolos pares, y la figura 41(d) es un diagrama correspondiente para símbolos impares.

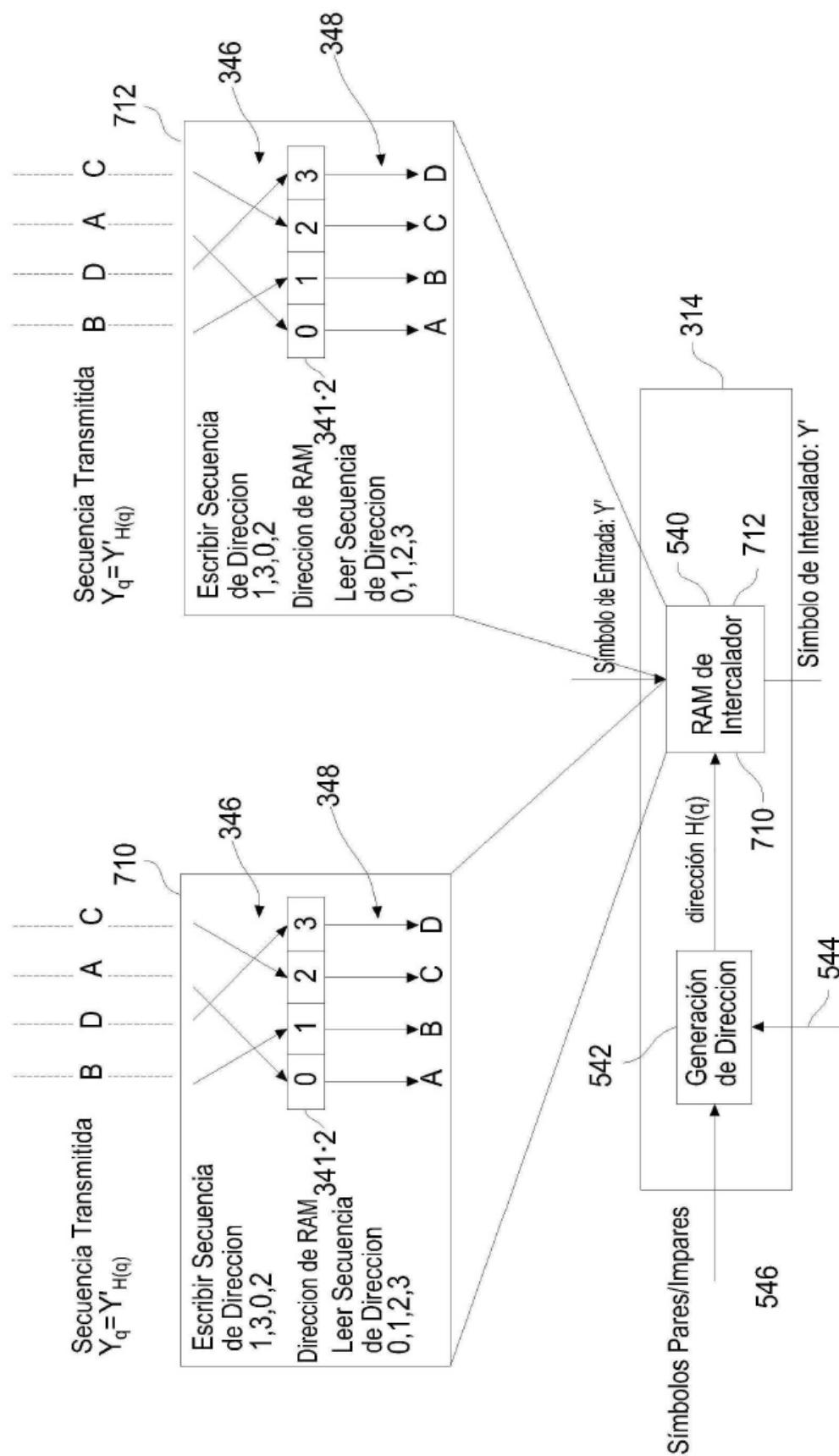

- 35 la figura 42 es un diagrama de bloques esquemático de un desintercalador de símbolo que aparece en la figura 29;

- la figura 43(a) es un diagrama que ilustra resultados para un intercalador que utiliza el generador de dirección mostrado en la figura 40 para símbolos de OFDM pares, y la figura 43(b) es un diagrama que ilustra resultados para símbolos de OFDM impares. Las figuras 44(a) y 44(b) muestran representaciones de la distancia a la salida del intercalador de sub-portadoras que eran adyacentes a la entrada del intercalador;

- 40 la figura 44 proporciona un diagrama de bloques esquemático del intercalador de símbolo mostrado en la figura 38, que ilustra un modo operativo en el que la intercalación se realiza de acuerdo con un modo de intercalación impar solamente; y

- la figura 45 proporciona un diagrama de bloques esquemático del desintercalador de símbolo mostrado en la figura 42, que ilustra el modo operativo en el que se realiza la intercalación de acuerdo con un modo de intercalación impar únicamente.

### Descripción de realizaciones preferidas

La figura 1 proporciona un ejemplo de diagrama de bloques de un transmisor de OFDM que puede ser usado, por ejemplo, para transmitir imágenes de video y señales de audio de acuerdo con el estándar DVB-T2. En la figura 1, una fuente de programa genera datos que van a ser transmitidos por el transmisor de OFDM. Un codificador 2 de video, un codificador 4 de audio y un codificador 6 de datos, generan video, audio y otros datos que van a ser transmitidos, los cuales son alimentados a un multiplexor 10 de programa. La salida del multiplexor 10 de programa forma una corriente multiplexada con otra información requerida para comunicar el video, el audio o los otros datos. El multiplexor 10 proporciona una corriente sobre un canal 13 de conexión. Pueden existir muchas corrientes multiplexadas de ese tipo que son alimentadas a diferentes ramas A, B, etc. Por simplicidad, solamente se va a describir la rama A.

Según se muestra en la figura 1, un transmisor 11 de OFDM recibe la corriente en un bloque 20 de adaptación de multiplexor y de dispersión de energía. El bloque 20 de adaptación de multiplexor y de dispersión de energía aleatoriza los datos y alimenta los datos apropiados a un codificador 21 de corrección de error adelantado que realiza codificación de corrección de error de la corriente. Un intercalador de bits 22 ha sido previsto para intercalar los bits de datos codificados que, para el ejemplo de DVB-T2, son la salida del codificador de LDPC. La salida del intercalador 22 de bits se alimenta en un bit a un mapeador 26 de constelación, el cual mapea grupos de bits en un punto de constelación, que va a ser usado para transportar los bits de datos codificados. Las salidas procedentes del bit en el mapeador 26 de constelación son etiquetas de punto de constelación que representan componentes reales e imaginarios. Las etiquetas de punto de constelación representan símbolos de datos formados a partir de dos o más bits dependiendo del esquema de modulación utilizado. Éstas serán mencionadas como células de datos. Estas células de datos se hacen pasar a través de un intercalador por tiempo 30 cuyo efecto es el de intercalar células de datos resultantes de múltiples palabras de código de LDPC. Las células de datos procedentes del intercalador por tiempo 30 son alimentadas a continuación a un generador 27 de modulación y trama, el cual mapea las células de datos sobre símbolos de modulación para su transmisión.

Las células de datos son recibidas en el interior de la unidad 27 de modulación por medio de un generador 32 de trama, con células de datos producidas por la rama B de la figura 1, a través de otros canales 31. El generador 32 de trama forma entonces muchas células de datos según secuencias que van a ser transportadas sobre símbolos de OFDM, donde un símbolo de OFDM comprende un número de células de datos, siendo cada célula de datos mapeada sobre una de las sub-portadoras. El número de sub-portadoras dependerá del modo de operación del sistema, el cual puede incluir uno de entre 1k, 2k, 4k, 8k, 16k o 32k, cada uno de los cuales proporciona un número diferente de sub-portadoras de acuerdo, por ejemplo, con la siguiente tabla:

| Modo | Sub-portadoras |

|------|----------------|

| 1k   | 756            |

| 2k   | 1512           |

| 4k   | 3024           |

| 8k   | 6048           |

| 16k  | 12096          |

| 32k  | 24192          |

### Número de sub-portadoras adaptadas a partir de DVB-T/H

Así, en un ejemplo, el número de sub-portadoras para el modo de 32k es de veinticuatro mil ciento noventa y dos. Para el sistema de DVB-T2, el número de sub-portadoras por símbolo de OFDM puede variar dependiendo del número de portadoras piloto y de otras portadoras reservadas. Así, en DVB-T2, a diferencia con DVB-T, el número de sub-portadoras para portar datos no es fijo. Los radiodifusores pueden seleccionar uno de los modos operativos de entre 1k, 2k, 4k, 8k, 16k, 32k, teniendo cada uno de ellos una gama de sub-portadoras para datos por símbolo de OFDM, siendo el máximo disponible para cada uno de estos modos de 1024, 2048, 4096, 8192, 16384, 32768, respectivamente. En DVB-T2 una trama de capa física está compuesta por muchos símbolos de OFDM. Tipicamente la trama empieza con uno o más símbolos de OFDM de preámbulo o P2, los cuales van seguidos a continuación por un número de símbolos de OFDM portadores de carga útil. El final de la trama de capa física está marcado por símbolos de cierre de trama. Para cada modo operativo, el número de sub-portadoras puede ser diferente para cada tipo de símbolo. Además, esto puede variar para cada uno de acuerdo a si se elige extensión de ancho de banda, si se ha habilitado reserva de tono y de acuerdo con el patrón de sub-portadora piloto que haya sido seleccionado. Como tal, una generalización a un número específico de sub-portadoras por símbolo de OFDM es difícil. Sin embargo, el intercalador de frecuencia para cada modo puede intercalar cualquier símbolo cuyo número de sub-portadoras sea más pequeño, o igual, que el número máximo disponible de sub-portadoras para el modo dado. Por ejemplo, en el modo de 1k, el intercalador podría trabajar para símbolos con un número de sub-portadoras que sea menor que, o igual a 1024, y para el modo de 16k, con un número de sub-portadoras que sea menor que, o igual a 16384.

- La secuencia de células de datos que va a ser portada en cada símbolo de OFDM se hace pasar a continuación al intercalador 33 de símbolo. El símbolo de OFDM es generado a continuación por un bloque 37 generador de símbolo de OFDM que introduce señales piloto y de sincronización desde un generador 36 de señal piloto e incorporada. Un modulador 38 de OFDM conforma a continuación el símbolo de OFDM en el dominio del tiempo, siendo alimentado a un procesador 40 de inserción de protección para generar un intervalo de seguridad entre símbolos, y a continuación a un convertidor digital a analógico, y finalmente a un amplificador de RF dentro de un extremo 44 frontal de RF para su difusión eventual por el transmisor de OFDM desde una antena 46.

- 5

Las realizaciones de la presente invención proporcionan un sistema de comunicación de OFDM que incluye un intercalador de bit para intercalar bits codificados con un codificador de LDPC en combinación con un intercalador de símbolo, el cual intercala símbolos que representan a los uno o más bits intercalados y codificados sobre las señales de sub-portadora de un símbolo de OFDM. Tanto el intercalador de bit como el intercalador de símbolo, de acuerdo con ejemplos de realización, van a ser descritos en los párrafos siguientes, empezando por el intercalador de bit, el cual se describe con codificación de LDPC.

#### Intercalador de bit para codificación de LDPC

#### 15 Códigos de corrección de errores de LDPC

Los códigos de LDPC tienen un alto comportamiento de corrección de error y han empezado recientemente a ser usados en esquemas de comunicación que incluyen radiodifusión digital por satélite tal como DVB-S.2, el cual ha entrado en uso en Europa (por ejemplo, véase DVB-S.2: ETSI EN 302 307 V1.1.2 (06-2006)). Aplicar códigos de LDPC a radiodifusión digital terrestre de próxima generación, está siendo también objeto de discusión.

20 Estudios recientes muestran que el rendimiento de los códigos de LDPC se aproxima al Límite de Shannon según se incrementa la longitud del código, de manera similar a los turbo códigos. Puesto que los códigos de LDPC tienen la propiedad de que la distancia mínima es proporcional a la longitud del código, los códigos de LDPC tienen las ventajas de que las características de probabilidad de error de bloque son excelentes y un piso de error, que es un fenómeno observado en asociación con características de descodificación de turbo códigos o similares, raramente ocurre.

25

Ahora se hará referencia en detalle a tales códigos de LDPC. Los códigos de LDPC son códigos lineales. Aunque los códigos de LDPC no son necesariamente binarios, la descripción que sigue se hará con referencia a códigos de LDPC binarios.

30 La característica más importante de los códigos de LDPC consiste en que una matriz de comprobación de paridad que define cada código de LDPC es una matriz de dispersión que tiene un número muy pequeño de elementos de "1", es decir que los elementos de la misma son en su mayor parte "0".

La figura 2 ilustra un ejemplo de matriz H de comprobación de paridad de un código de LDPC.

Cada columna de la matriz H de comprobación de paridad de la figura 2 tiene un peso de 3 (es decir, 3 elementos de "1") y cada fila tiene un peso de 6 (es decir, 6 elementos de "1").

35 La codificación basada en códigos de LDPC (es decir, codificación LDPC) se realiza, por ejemplo, calculando una matriz G de generación basada en una matriz H de comprobación de paridad y multiplicando la matriz G de generación por bits de información para generar una palabra clave (código de LDPC).

Específicamente, un codificador de LDPC calcula en primer lugar una matriz G de generación que satisface una ecuación  $GH^T = 0$  con una matriz transpuesta  $H^T$  de la matriz H de comprobación de paridad. Aquí, cuando la matriz 40 G de generación es una matriz K x N, el codificador multiplica la matriz G de generación por una secuencia de bit de información de K bits (vector u) para generar un palabra clave c (= uG) N bits. La palabra clave (código de LDPC) generada por el codificador es recibida por un lado de recepción a través de una trayectoria de comunicación.

45 El código de LDPC puede ser descodificado mediante un algoritmo de paso de mensaje propuesto por Gallager y denominado "algoritmo de descodificación probabilística". El algoritmo de paso de mensaje utiliza propagación creíble sobre un gráfico de Tanner que incluye nodos de variable (también conocidos como nodos de mensaje) y nodos de comprobación. En la descripción que sigue, cada uno de los nodos de variable y de los nodos de comprobación será mencionado simplemente como un "nodo" según sea apropiado.

La figura 3 ilustra un procedimiento para descodificar un código de LDPC.

50 En lo que sigue, un valor real que exprese, a modo de relación de probabilidad logarítmica, la probabilidad de que un bit de código  $i^{\text{ésimo}}$  de un código de LDPC (una palabra clave) recibido por un lado de recepción tenga un valor de "0", se menciona como valor  $u_{0i}$  recibido, según sea apropiado. Además, un mensaje de salida desde un nodo de comprobación se mencionada como  $u_i$  y un mensaje de salida desde un nodo de variable se menciona como  $v_i$ .

Un código de LDPC se descodifica de la siguiente manera. En primer lugar, según se muestra en la figura 3, en la etapa S11, se recibe un código de LDPC, se inicializa un mensaje  $u_i$  (mensaje de nodo de comprobación) en "0", y

una variable k, que es un valor entero como contador de un proceso iterativo, se inicializa en "0". A continuación, el procedimiento avanza hasta la etapa S12. En la etapa S12, se realiza un cálculo (cálculo de nodo de variable) representado por la ecuación (1) en base al valor  $u_{0i}$  recibido, obtenido por recepción del código de LDPC para obtener un mensaje  $v_i$  (mensaje de nodo de variable) y a continuación se realiza un cálculo (cálculo de nodo de comprobación) representado por la ecuación (2), en base al mensaje  $v_i$ , para obtener un mensaje  $u_j$ .

5

## ECUACIÓN 1

$$v_i = u_{0i} + \sum_{j=1}^{d_v-1} u_j \quad \dots (1)$$

## ECUACIÓN 2

$$\tanh\left(\frac{u_j}{2}\right) = \prod_{i=1}^{d_c-1} \tanh\left(\frac{v_i}{2}\right) \quad \dots (2)$$

10  $d_v$  y  $d_c$  en la ecuación (1) y en la ecuación (2) son parámetros seleccionables arbitrariamente que representan los números respectivos de 1s en dirección vertical (columna) y en dirección horizontal (fila) de la matriz H de comprobación de paridad. Por ejemplo,  $d_v = 3$  y  $d_c = 6$  en el caso de un código (3, 6).

15 Las gamas para cálculo respectivas en el cálculo de nodo de variable de la ecuación (1) y el cálculo de nodo de comprobación de la ecuación (2) van desde 1 hasta  $d_v-1$  y desde  $d_c-1$  puesto que un mensaje recibido desde un borde (es decir, una línea que conecta un nodo de variable con un nodo de comprobación, cada uno con el otro) que presenta a la salida el mensaje, es excluido de cada uno de los cálculos de las ecuaciones (1) y (2). Realmente, el cálculo de nodo de comprobación de la ecuación (2) se realiza utilizando recursivamente, según se muestra en la ecuación (4), una tabla creada previamente de una función  $R(v_1, v_2)$  mostrada en la ecuación (3) que se define como una salida con respecto a dos entradas  $v_1$  y  $v_2$ .

## 20 ECUACIÓN 3

$$x = 2\tanh^{-1} \{ \tanh(v_1/2) \tanh(v_2/2) \} = R(v_1, v_2) \quad \dots (3)$$

## ECUACIÓN 4

$$u_j = R(v_1, R(v_2, R(v_3, \dots R(v_{d_c-2}, v_{d_c-1}) \dots))) \quad \dots (4)$$

25 En la etapa S12, la variable k se incrementa en "1" y el procedimiento avanza hasta la etapa S13. En la etapa S13, se determina si la variable k es o no mayor que un número C predeterminado de iteraciones de descodificación. Si se determina en la etapa S13 que la variable k no es mayor que C, el procedimiento retorna a la etapa S12 para repetir el mismo proceso.

30 Si se determina en la etapa S13 que la variable k es mayor que C, el procedimiento avanza hasta la etapa S14 para realizar un cálculo representado por la ecuación (5) para obtener y presentar a la salida un mensaje  $v_i$  como resultado de la descodificación final. A continuación, termina el procedimiento de descodificación de código de LDPC.

## ECUACIÓN 5

$$v_i = u_{0i} + \sum_{j=1}^{d_v} u_j \quad \dots (5)$$

35 Aquí, a diferencia con el cálculo de nodo de variable de la ecuación (1), el cálculo de la ecuación (5) se realiza utilizando mensajes  $u_j$  procedentes de todos los bordes conectados al nodo de variable.

La figura 4 ilustra un ejemplo de matriz H de comprobación de paridad de un código de LDPC de (3, 6) con una tasa de código de 1/2 y una longitud de código de 12.

Al igual que con la matriz H de comprobación de paridad de la figura 2, la matriz H de comprobación de paridad de la figura 4 tiene un peso de columna de 3 y un peso de fila de 6.

La figura 5 ilustra un gráfico de Tanner de la matriz H de comprobación de paridad de la figura 4.

En la figura 5, “+” representa un nodo de comprobación y “=” representa un nodo de variable. Los nodos de comprobación y los nodos de variable corresponden a filas y columnas de la matriz H de comprobación de paridad, respectivamente. Cada línea de conexión entre un par de nodos de comprobación y de variable es un borde correspondiente a un elemento de “1” de la matriz H de comprobación de paridad.

Específicamente, cuando un elemento de la fila  $j^{\text{ésima}}$  y de la columna  $i^{\text{ésima}}$  de una matriz de comprobación de paridad es “1”, un nodo “=” de variable  $i^{\text{ésimo}}$  (contando desde la parte superior) y un nodo “+” de comprobación  $j^{\text{ésimo}}$  (contando desde la parte superior) están conectados a través de un borde en la figura 5. El borde indica que un bit de código correspondiente al nodo de variable tiene una restricción correspondiente al nodo de comprobación.

Un algoritmo de suma y producto, que es un algoritmo de descodificación de código de LDPC, realiza repetitivamente un cálculo de nodo de variable y un cálculo de nodo de comprobación.

La figura 6 ilustra un cálculo de nodo de variable realizado en un nodo de variable.

Un mensaje  $v_i$  correspondiente a un borde para el cálculo, se obtiene de acuerdo con el cálculo de nodo de variable de la ecuación (1), utilizando un valor  $u_{0i}$  recibido y mensajes  $u_1$  y  $u_2$  procedentes de los bordes restantes conectados al nodo de variable. Los mensajes correspondientes a otros bordes se obtienen de la misma manera.

La figura 7 ilustra un cálculo de nodo de comprobación realizado en un nodo de comprobación.

La ecuación (2) anterior para el cálculo de nodo de comprobación puede ser re-escrita como ecuación (6) utilizando una ecuación de relación de  $a \times b = \exp\{\ln(|a|) + \ln(|b|)\} \times \text{sign}(a) \times \text{sign}(b)$ , donde  $\text{sign}(x)$  es 1 cuando  $x > 0$ , y -1 cuando  $x < 0$ .

## 20 ECUACIÓN 6

$$\begin{aligned}

u_j &= 2\tanh^{-1}\left(\prod_{i=1}^{d_c-1} \tanh\left(\frac{v_i}{2}\right)\right) \\

&= 2\tanh^{-1}\left[\exp\left\{\sum_{i=1}^{d_c-1} \ln\left(\left|\tanh\left(\frac{v_i}{2}\right)\right|\right)\right\} \times \prod_{i=1}^{d_c-1} \text{sign}\left(\tanh\left(\frac{v_i}{2}\right)\right)\right] \\

&= 2\tanh^{-1}\left[\exp\left\{-\left(\sum_{i=1}^{d_c-1} -\ln\left(\tanh\left(\frac{|v_i|}{2}\right)\right)\right)\right\} \times \prod_{i=1}^{d_c-1} \text{sign}(v_i)\right] \quad \dots(6)

\end{aligned}$$

Adicionalmente, cuando se define una función  $\phi = \ln(\tanh(x/2))$  cuando  $x > 0$ , se satisface una ecuación  $\phi^{-1}(x) = 2\tanh^{-1}(e^{-x})$  y por lo tanto la ecuación (6) puede ser reorganizada como ecuación (7):

## ECUACIÓN 7

$$u_j = \phi^{-1}\left(\sum_{i=1}^{d_c-1} \phi(|v_i|)\right) \times \prod_{i=1}^{d_c-1} \text{sign}(v_i) \quad \dots(7)$$

En el nodo de comprobación, el cálculo de nodo de comprobación de la ecuación (2) se realiza de acuerdo con la ecuación (7).

Es decir, en el nodo de comprobación, se obtiene un mensaje  $u_j$  correspondiente a un borde para cálculo, de acuerdo con el cálculo de nodo de comprobación de la ecuación (7) utilizando mensajes  $v_1, v_2, v_3, v_4$  y  $v_5$  procedentes de los bordes restantes conectados al nodo de comprobación como se muestra en la figura 7. Otros mensajes correspondientes a otros bordes son obtenidos de la misma manera.

La función  $\phi(x)$  en la ecuación (7) puede ser expresada de tal modo que  $\phi(x) = \ln((e^x + 1)/(e^x - 1))$  y  $\phi^{-1}(x) = \phi^{-1}(x)$  cuando  $x > 0$ . Cuando las funciones  $\phi(x)$  y  $\phi^{-1}(x)$  están incorporadas en hardware, ambas pueden ser incorporadas utilizando la misma Tabla de Búsqueda Ascendente (LUT).

Aunque se sabe que los códigos de LDPC presentan un comportamiento muy alto en trayectorias de comunicación de Ruido Gaussiano Blanco Aditivo (AWGN), también se ha sabido en los últimos años que los códigos de LDPC tienen un alto rendimiento de corrección de error en otras trayectorias de comunicación, en comparación con códigos convolucionales o con códigos convolucionales de Reed Solomon (RS) concatenados en el pasado.

- 5 Es decir, cuando se elige un código que tiene un comportamiento excelente en una trayectoria de comunicación de AWGN, el código elegido muestra por lo general un excelente comportamiento en otras trayectorias de comunicación, superior a otros códigos.

Por ejemplo, puesto que se aplican códigos de LDPC a radiodifusión digital terrestre, se ha sugerido que los códigos de LPDC definidos en los esquemas de especificación y modulación de DVB-S.2 sean combinados y se proporcione un intercalador de bit que intercale bits de código de un código de LDPC entre un codificador de LDPC y un modulador para mejorar el rendimiento de códigos de LDPC en trayectorias de comunicación de AWGN.

10 Sin embargo, las borraduras o los errores de ráfaga que pueden ocurrir en las trayectorias de comunicación se supone que son ondas de superficie. Por ejemplo, en un sistema de Multiplexado por División de Frecuencia Ortogonal (OFDM), un símbolo específico puede ser borrado (es decir, llevado a potencia cero) debido al retardo de 15 un eco, lo cual es una trayectoria distinta de la trayectoria principal, en entornos multi-trayectoria en los que la Relación de Deseada respecto a Indeseada (D/U) es de 0 dB, de tal modo que la potencia de la trayectoria principal como potencia deseada es igual a la potencia de eco como potencia indeseada.

20 Cuando la D/U es de 0 dB, todos los símbolos de OFDM en un momento específico pueden ser también borrados (es decir, caer a potencia cero) debido a una frecuencia Doppler en una titilación que es una trayectoria de comunicación a la que ha sido añadido un eco con una frecuencia Doppler aplicada al mismo y que tiene un retardo de "0".

Adicionalmente, los errores de ráfaga pueden producirse debido a una potencia inestable o unas condiciones indeseadas del cableado que va desde las antenas hasta los receptores.

25 En la técnica relacionada, los códigos de corrección de error que tienen un comportamiento excelente en trayectorias de comunicación de AWGN, son también utilizados frecuentemente en trayectorias de comunicación en las que ocurren errores de ráfaga o borraduras según se ha descrito anteriormente.

30 Por otra parte, cuando se descodifica un código de LDPC, se calcula un nodo de variable correspondiente no sólo a una columna de una matriz H de comprobación de paridad sino también a un bit de código del código de LDPC de acuerdo con la ecuación (1), que incluye la adición de un bit de código (un valor  $u_{0i}$  recibido) de un código de LDPC según se muestra en la figura 6. Por lo tanto, la precisión del mensaje obtenido se reduce si se produce un error en 35 un bit de código utilizado en el cálculo de nodo de variable.

Adicionalmente, cuando se descodifica un código de LDPC, se calcula un nodo de comprobación de acuerdo con la ecuación (7) utilizando un mensaje obtenido en un nodo de variable conectado al nodo de comprobación. Por lo tanto, el rendimiento de descodificación se reduce si ocurre simultáneamente un error que incluya una borradura en 40 (una pluralidad de bits de código de LDPC correspondientes a) una pluralidad de nodos de variable conectados a cada uno de un gran número de nodos de comprobación.

Más específicamente, por ejemplo cuando dos o más nodos de variable conectados a un nodo de comprobación son 45 borrados simultáneamente, el nodo de comprobación devuelve un mensaje con una probabilidad de "0" que es igual a la probabilidad de "1" en cada nodo de variable conectado al nodo de comprobación. En este caso, el nodo de comprobación que devuelve el mensaje con iguales probabilidades de "0" y de "1" no contribuye a un proceso de descodificación que consiste en un conjunto de un cálculo de nodo de variable y un cálculo de nodo de comprobación. Esto incrementa el número de procesos de descodificación requeridos, reduciendo con ello el rendimiento de descodificación e incrementando el consumo de potencia de un receptor que realiza descodificación de código de LDPC.

50 De ese modo, existe una necesidad de proporcionar un método que incremente la resistencia a los errores de ráfaga o borraduras mientras se mantiene el rendimiento de las trayectorias de comunicación de AWGN.

En este punto, puede ser posible incrementar el rendimiento de descodificación si se proporciona un intercalador de bit que intercale bits de código de un código de LDPC entre un codificador de LDPC y un modulador para mejorar el rendimiento de códigos de LDPC en trayectorias de comunicación de AWGN según se ha descrito anteriormente, y 55 si el intercalador de bit está diseñado de modo que pueda realizar intercalación que reduzca la probabilidad de que ocurra un error simultáneamente en (una pluralidad de bits de código de un código de LDPC correspondiente a) una pluralidad de nodos de variable conectados a un nodo de comprobación.

La invención ha sido realizada en vista de las circunstancias anteriores y proporciona un aparato y un método de procesamiento de datos que pueden incrementar la resistencia a los errores en los bits de código de códigos de LDPC tales como errores de ráfaga o borraduras.

- Un aparato de procesamiento de datos para intercalar datos de acuerdo con una realización de la invención incluye un intercalador de paridad para realizar intercalación de paridad sobre un código de Comprobación de Paridad de Baja Densidad (LDPC) obtenido al realizar codificación de LDPC de acuerdo con una matriz de comprobación de paridad que incluye una matriz de paridad correspondiente a bits de paridad del código de LDPC, teniendo la matriz de paridad una estructura progresiva, de modo que se intercale un bit de paridad del código de LDPC en una posición de bit de paridad diferente.

- Un método de procesamiento para un aparato de procesamiento que intercala datos de acuerdo con una realización de la invención incluye la etapa de hacer que el aparato de procesamiento de datos realice intercalación de paridad en un código de Comprobación de Paridad de Baja Densidad (LDPC) obtenido al realizar codificación de LDPC de acuerdo con una matriz de comprobación de paridad que incluye una matriz de paridad correspondiente a bits de paridad del código de LDPC, teniendo la matriz de paridad una estructura gradual, de modo que se intercale un bit de paridad del código de LDPC en una posición de bit de paridad diferente.

- Es decir, de acuerdo con las realizaciones de la invención, la intercalación de paridad se lleva a cabo sobre un código de LDPC obtenido al realizar codificación de LDPC de acuerdo con una matriz de comprobación de paridad que incluye una matriz de paridad estructurada de forma gradual, correspondiente a bits de paridad del código de LDPC de modo que se intercalan bits de paridad del código de LDPC en posiciones de bit de paridad diferentes.

- El aparato de procesamiento de datos puede ser un dispositivo independiente y puede ser también un bloque interno incluido en un dispositivo.

- Explicación detallada de un intercalador de bit de ejemplo

- La figura 8 proporciona una representación más detallada de partes del transmisor mostrado en la figura 1, las cuales ilustran la operación del intercalador de bit. En particular, el codificador 21 de LDPC va a ser descrito a continuación. El codificador 21 de LDPC codifica los datos objetivo en un bit de datos codificados de LDPC que incluyen bits de información correspondientes a los datos objetivo de acuerdo con una matriz de comprobación de paridad, en la que una matriz de paridad correspondiente a bits de paridad del código de LDPC tiene una estructura gradual.

- Específicamente, el codificador 21 de LDPC codifica datos objetivo en un código de LDPC definido, por ejemplo, de acuerdo con la especificación DVB-S.2 y presenta a la salida el código de LDPC.

- El código de LDPC definido en la especificación DVB-S.2 es un código Acumulado de Repetición Irregular (IRA), y una matriz de paridad en una matriz de comprobación del código de LDPC tiene una estructura gradual. Detalles de la matriz de paridad y de la estructura gradual de la misma van a ser descritos en lo que sigue. Un ejemplo del código IRA se encuentra descrito en "Repetición Irregular-Códigos Acumulados", H. Jin, A. Khandekar, y R. J. McEliece, en Procedimientos de 2º Simposio Internacional sobre Turbo códigos y Tópicos Relacionados, pp. 1-8, Septiembre 2000.

- La salida de código de LDPC procedente del codificador 21 de LDPC se suministra al intercalador 22 de bit.

- El intercalador 22 de bit es un aparato de procesamiento de datos que intercala datos e incluye un intercalador 23 de paridad, un intercalador 24 por giro de columna, y un desmultiplexor 25.

- El intercalador 23 de paridad realiza intercalación de paridad sobre el código de LDPC procedente del codificador 21 de LDPC para intercalar bits de paridad del código de LDPC en posiciones de bit de paridad diferentes, y proporciona el código de LDPC de paridad intercalada al intercalador 24 por giro de columna.

- El intercalador 24 por giro de columna realiza intercalación por giro de columna sobre el código de LDPC procedente del intercalador 23 de paridad y a continuación proporciona el código de LDPC por giro de columna intercalado al desmultiplexor 25.

- De ese modo, el código de LDPC es transmitido después de que dos o más bits de código del código de LDPC hayan sido mapeados respecto a un símbolo ortogonalmente modulado por medio de la unidad 26 de mapeo que se describe en lo que sigue.

- El intercalador 24 por giro de columna realiza permutación (por ejemplo, intercalación por giro de columna que se describe a continuación) sobre los bits de código del código de LDPC recibido desde el intercalador 23 de paridad de tal modo que una pluralidad de bits de código del código de LDPC correspondiente a "1" en una fila arbitraria de la matriz de comprobación de paridad utilizada por el codificador 21 de LDPC no son mapeados respecto a un símbolo.

- El desmultiplexor 25 lleva a cabo un proceso de reordenación sobre el código de LDPC recibido desde el intercalador 24 por giro de columna de tal modo que son reordenadas las posiciones de dos o más bits de código del código de LDPC que van a ser mapeados en un símbolo, obteniendo un código de LDPC de resistencia incrementada respecto a un AWGN, y a continuación proporciona el código de LDPC obtenido a la unidad 26 de

mapeo.

La unidad de mapeo 26 mapea dos o más bits de código del código de LDPC procedente del desmultiplexor 25 en cada punto de señal que se determine de acuerdo con un esquema de modulación que el modulador 27 ortogonal utiliza para realizar modulación ortogonal (modulación multi-valor).

- 5 Más específicamente, la unidad 26 de mapeo convierte el código de LDPC procedente del desmultiplexor 25 en símbolos (valores de símbolo) representados por puntos de señal determinados de acuerdo con el esquema de modulación sobre un plano IQ (constelación IQ) definido con un eje I que representa I componentes de los mismos niveles que las portadoras, y Q ejes que representan Q componentes ortogonales a las portadoras.

10 El esquema de modulación que utiliza el transmisor de OFMD de la figura 1 utilizado para llevar a cabo modulación ortogonal incluye un esquema de modulación definido en la especificación DVB-T, ejemplos del cual incluyen Modulación por Desplazamiento de Fase en Cuadratura (QPSK), Modulación de Amplitud de Cuadratura 16 (16QAM), 64QAM, 256QAM, y 4096QAM. Uno de los esquemas de modulación que utiliza el modulador 27 ortogonal para llevar a cabo modulación ortogonal está preestablecido, por ejemplo, mediante operación por un operador que opera el transmisor de la figura 1. Ejemplos de otros esquemas de modulación que pueden usar el modulador 27 ortogonal para realizar modulación ortogonal incluyen Modulación de amplitud de Pulso 4 (4PAM).

15 El símbolo obtenido en la unidad 26 de mapeo es proporcionado al intercalador por tiempo, el cual puede intercalar diferentes palabras de código de LDPC sobre diferentes símbolos de OFMD. La salida del intercalador por tiempo 30 es alimentada a continuación al generador de trama de la figura 1. Las partes restantes del transmisor mostrado en la figura 1 realizan modulación ortogonal de las señales de sub-portadora del símbolo de OFMD recibido desde la unidad 26 de mapeo para producir una señal modulada y a continuación transmitir la señal modulada.

20 La figura 9 ilustra una matriz H de comprobación de paridad que utiliza el codificador 21 de LDPC de la figura 8 para codificación de LDPC.

25 La matriz H de comprobación de paridad tiene una estructura de Matriz de Generación de Baja Densidad (LDGM) y puede ser expresada mediante la ecuación “ $H = [H_A|H_T]$ ” que incluye una matriz  $H_A$  de información como componente izquierdo y una matriz  $H_T$  de paridad como componente derecho, donde la matriz  $H_A$  de información corresponde a bits de información entre los bits de código del código de LDPC, y la matriz  $H_T$  de paridad corresponde a bits de paridad.

30 Aquí, el número de bits de información y el número de bits de paridad entre bits de código de un código de LDPC (una palabra clave) se definen como una longitud de información de K y una longitud de paridad de M, y el número de los bits de código se define como una longitud de código N (= K + M).

La longitud K de información y la longitud M de paridad de un código de LDPC de una longitud de código N, se determinan en base a una tasa de código. De ese modo, la matriz H de comprobación de paridad es una matriz de M x N. Adicionalmente, la matriz  $H_A$  de información es una matriz de M x K y la matriz  $H_T$  de paridad es una matriz de M x M.

35 La figura 10 ilustra una matriz  $H_T$  de paridad de una matriz H de comprobación de paridad de un código de LDPC definido en la especificación DVB-S.2.

40 La matriz  $H_T$  de paridad de la matriz H de comprobación de paridad de un código de LDPC definida en la especificación DVB-S.2, tiene una estructura gradual tal que los elementos de “1” de la matriz  $H_T$  de paridad están dispuestos de una forma gradual según se muestra en la figura 10. La primera fila de la matriz H de comprobación de paridad tiene un peso de 1 y las restantes filas tienen un peso de 2. La última columna de la matriz H de comprobación de paridad tiene un peso de 1 y las restantes columnas tienen un peso de 2.

45 El código de LDPC de la matriz H de comprobación de paridad que tiene la matriz  $H_T$  de paridad de estructura gradual, puede ser generada fácilmente utilizando la matriz H de comprobación de paridad.

Más específicamente, supóngase que un vector de fila c representa un código (palabra clave) de LDPC y supóngase que  $C^T$  representa un vector columna obtenido por transposición del vector fila. Adicionalmente, supóngase que un vector fila A representa una parte de bit de información del vector fila c, el cual es el código de LDPC, y supóngase que un vector fila T represente una parte de bit de paridad del mismo.

50 En este caso, el vector fila c puede ser expresado mediante una ecuación “ $c = [A|T]$ ” que incluye un vector fila A como componente izquierdo y un vector fila T como componente derecho, donde el vector fila A corresponde a bits de información y el vector fila T corresponde a bits de paridad.

La matriz H de comprobación de paridad y el vector fila  $c = [A|T]$ , que corresponde al código de LDPC, necesitan satisfacer una ecuación “ $Hc^T = 0$ ”. De ese modo, el valor de cada elemento del vector fila T que corresponda a bits de paridad incluidos en el vector fila  $c = [A|T]$  puede ser obtenido secuencialmente estableciendo un elemento en cada fila del vector columna  $Hc^T$  en la ecuación “ $Hc^T = 0$ ” en cero por un orden que empieza desde el elemento de la

primera fila, cuando la matriz  $H_T$  de paridad en la matriz  $H = [H_A|H_T]$  de comprobación de paridad tiene una estructura gradual según se muestra en la figura 10.

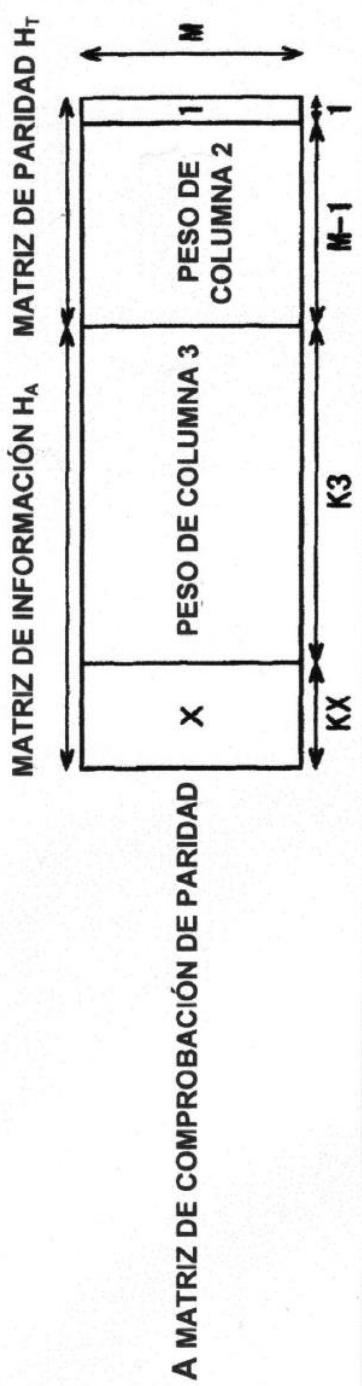

Las figuras 12a y 12b ilustran una matriz H de comprobación de paridad de un código de LDPC y pesos de columna definidos en la especificación DVB-S.2.

- 5 Es decir, la figura 11A ilustra una matriz H de comprobación de paridad de un código de LDPC definido en la especificación DVB-S.2.

Antes de que las columnas  $KX^{\text{ésimas}}$  de la matriz H de comprobación de paridad tengan un peso de columna de X, las siguientes columnas K3 tienen un peso de columna de 3, las siguientes columnas M-1 tienen un peso de columna de 2, y la última columna tiene un peso de columna de 1.

- 10 En este punto, la suma de los números de columnas "KX + K3 + M-1 + 1" es igual a una longitud de código de N.

En la especificación DVB-S.2, los números de columnas KX, K3 y M (longitud de paridad) y el peso de columna X se definen según se muestra en la figura 11B.

Es decir, la figura 11B ilustra los números de columnas KX, K3 y M, y el peso de columna X, para cada tasa de código de códigos de LDPC definidos en la especificación DVB-S.2.

- 15 Los códigos de LDPC con longitudes de código N respectivas de 64800 bits y 16200 bits, están definidos en la especificación DVB-S.2.

Adicionalmente, se definen 11 tasas nominales de 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9 y 9/10 para el código de LDPC cuya longitud de código N sea 64800, y se definen 10 tasas de código nominales de 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6 y 8/9 para el código de LDPC cuya longitud de código N sea 16200 bits según se ha mostrado en la figura 11B.

- 20 Para códigos de LDPC, se sabe que la tasa de error de un bit de código disminuye según se incrementa el peso de una columna correspondiente al bit de código en una matriz H de comprobación de paridad.

En el caso de una matriz H de comprobación de paridad definida en la especificación DVB-S.2 mostrada en las figuras 12a y 12b, el peso de una columna se incrementa según se reduce el número ordinal de la columna (es decir, según la columna está más cerca del extremo izquierdo de la matriz H de comprobación de paridad), y por lo tanto un bit de código de un código de LDPC correspondiente a la matriz H de comprobación de paridad es más robusto contra (resistente a) errores según disminuye el número ordinal del bit de código (es decir, el primer bit de código es el más resistente) y es más susceptible de errores según se incrementa el número ordinal del bit de código (es decir, el último bit de código es el más susceptible).

- 30 Las figuras 12A y 12B ilustran una disposición de (puntos de señal correspondientes a) 16 símbolos en un plano IQ en el caso de que se realice 16QAM en el modulador 27 ortogonal de la figura 8.

Es decir, la figura 13A ilustra símbolos de 16QAM.

En 16QAM, un símbolo representa 4 bits y se proporcionan 16 ( $= 2^4$ ) símbolos. Adicionalmente, 16 símbolos se encuentran dispuestos en un cuadrado de 4 x 4 símbolos en las direcciones I y Q, con centro en el origen del plano IQ.

En este punto, cuando  $y_0$ ,  $y_1$ ,  $y_2$  e  $y_3$  indican 4 bits representados por un símbolo de 16QAM, empezando secuencialmente desde el bit más significativo (MSB), la unidad 26 de mapeo de la figura 8 mapea bits de código de un código de LDPC respecto a un símbolo de 4 bits  $y_0$  a  $y_3$  correspondientes a 4 bits de código en el caso de que el esquema de modulación sea 16QAM.

- 40 La figura 13B muestra límites de bit de cuatro bits  $y_0$  a  $y_3$  representados por un símbolo de 16QAM.

En este caso, un límite de bit de un bit  $y_i$  ( $i = 0, 1, 2, 3$ , en las figuras 12A y 12B) es un límite entre símbolos con un bit  $y_i$  de "0" y símbolos con un bit  $y_i$  de "1".

Según se muestra en la figura 13B, un límite correspondiente al eje Q en el plano IQ que es el único límite de bit para el primer bit (es decir, el MSB)  $y_0$  de los cuatro bits  $y_0$  a  $y_3$  representados por un símbolo de 16QAM y un límite correspondiente al eje I en el plano IQ es el único límite de bit para el segundo bit (es decir, el segundo MSB)  $y_1$ .

Adicionalmente, dos límites, uno entre la primera y la segunda columnas de símbolos (contando desde el lado izquierdo) entre los símbolos de 4 x 4 y el otro entre la tercera y la cuarta columnas, son límites de bit para el tercer bit  $y_2$ .

Además, dos límites, uno entre la primera y la segunda filas de símbolos (contando desde la parte superior) entre símbolos de 4 x 4 y el otro entre la tercera y cuarta filas, son límites de bit para el cuarto bit  $y_3$ .

Cada bit  $y_i$  representado por un símbolo es más resistente a errores según se incrementa el número de símbolos distantes del límite de bit, y es más susceptible de errores según se incrementa el número de símbolos cerca del límite de bit.

- 5 Cuando un bit resistente a (robusto frente a) errores se menciona como "bit fuerte" y un bit susceptible a (sensible a) errores se menciona como "bit débil", el primer bit (es decir, el MSB)  $y_0$  y el segundo bit  $y_1$  son bits fuertes, y el tercer bit  $y_2$  y el cuarto bit  $y_3$  son bits débiles según se muestra en las figuras 1A y 12B.

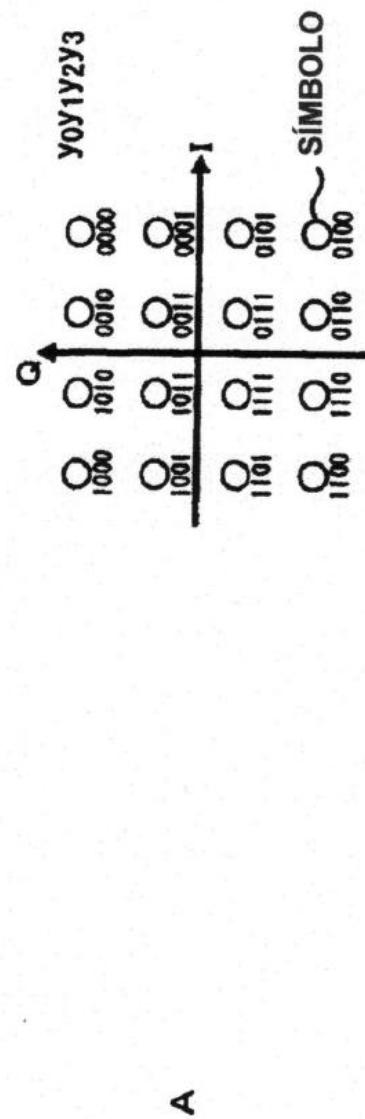

Las figuras 13 a 15 ilustran una disposición de (puntos de señal correspondientes a) 64 símbolos en un plano IQ en el caso de que se realice 64QAM en el modulador 27 ortogonal de la figura 8.

- 10 En 64QAM, un símbolo representa 4 bits y se proporcionan 64 ( $= 2^6$ ) símbolos. Adicionalmente, 64 símbolos están dispuestos en un cuadrado de 8 x 8 símbolos en las direcciones I y Q, con centro en el origen del plano IQ.

En este caso, cuando  $y_0$ ,  $y_1$ ,  $y_2$ ,  $y_3$ ,  $y_4$  e  $y_5$  indican 6 bits representados por un símbolo de 64QAM, empezando secuencialmente desde el bit más significativo (MSB), la unidad 26 de mapeo de la figura 8 mapea 6 bits de código de un código de LDPC respecto a un símbolo de 6 bits  $y_0$  a  $y_5$  correspondientes a los 6 bits de código en el caso de que el esquema de modulación sea 64QAM.

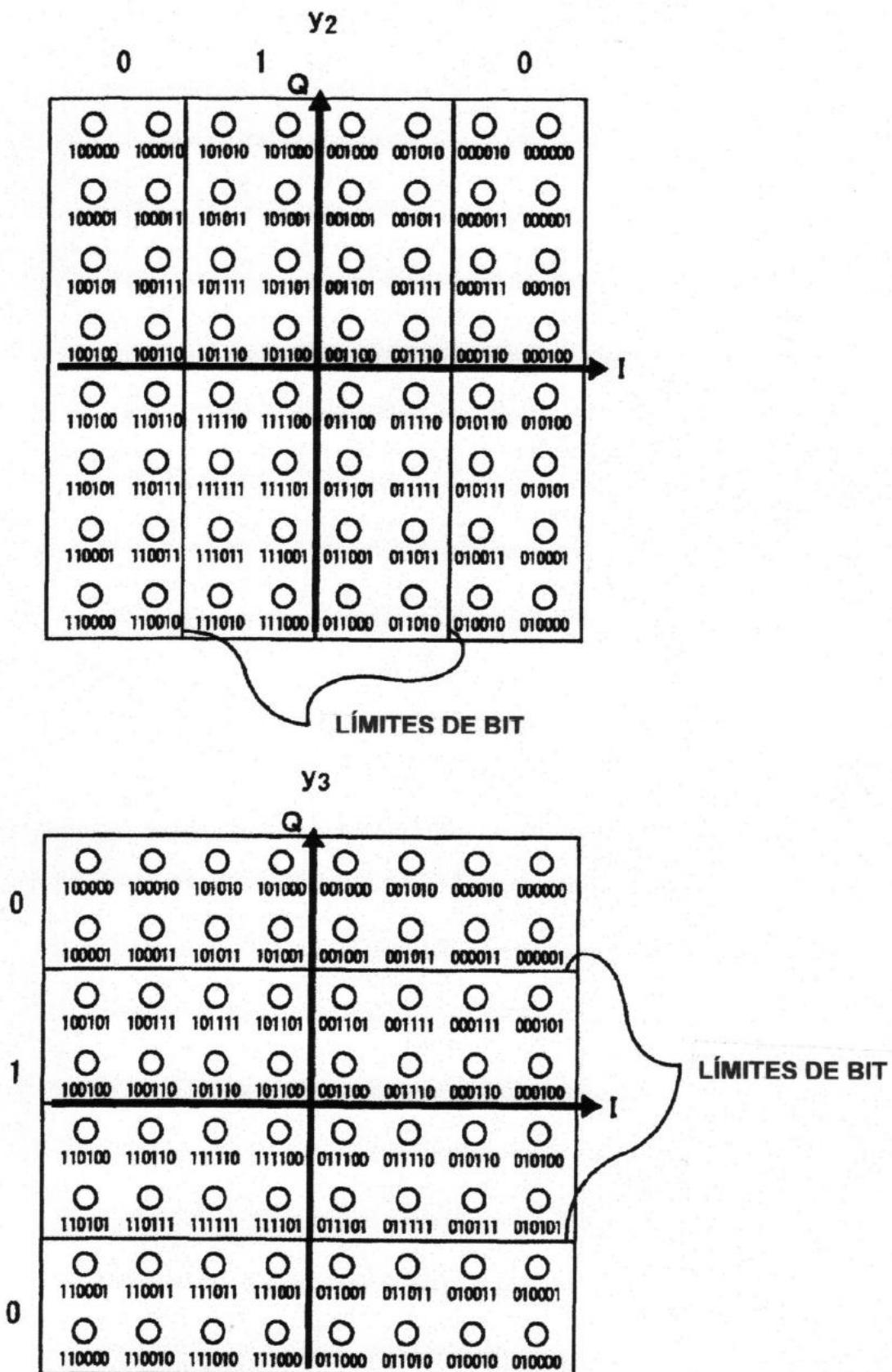

- 15 La figura 13 muestra límites de bit del primer y segundo bits  $y_0$  e  $y_1$  entre los 6 bits  $y_0$  a  $y_5$  representados por un símbolo de 64QAM, la figura 14 muestra límites de bit del tercer y cuarto bits  $y_2$  e  $y_3$ , y la figura 15 muestra límites de bit del quinto y sexto bits  $y_4$  e  $y_5$ .

- 20 Un límite de bit está presente para cada uno del primer y segundo bits  $y_0$  e  $y_1$  según se muestra en la figura 14. Dos límites de bit están presentes para cada uno del tercer y cuarto bits  $y_2$  e  $y_3$  mostrados en la figura 14, y cuatro límites de bit están presentes para cada uno del quinto y sexto bits  $y_4$  e  $y_5$  según se muestra en la figura 15.

En consecuencia, el primero y el segundo bits  $y_0$  e  $y_1$  entre los 6 bits  $y_0$  a  $y_5$  representados por un símbolo de 64QAM, son los más bits más fuertes, el tercero y el cuarto bits  $y_2$  e  $y_3$  son los segundos bits más fuertes, y el quinto y el sexto bits  $y_4$  e  $y_5$  son bits débiles.

- 25 A partir de las figuras 13, 14 y 15 se puede ver que, en el caso de bits de símbolos modulados ortogonalmente, los bits más significativos son bits fuertes, y los menos significativos son bits débiles.

La salida de código de LDPC desde el codificador 21 de LDPC de la figura 8 incluye bits de código susceptibles a error y bits de código resistentes a error según se ha descrito en lo que antecede con referencia a la figura 11.

Los bits de símbolos modulados ortogonalmente por el modulador 27 ortogonal incluyen bits fuertes y bits débiles según se ha descrito anteriormente con referencia a las figuras 12 a 15.

- 30 En consecuencia, cuando son mapeados bits de código susceptibles de error de un código de LDPC respecto a bits débiles de símbolos modulados ortogonalmente, se reduce la resistencia global a errores.

Por lo tanto, la invención sugiere un intercalador que intercale bits de código de un código de LDPC de modo que los bits de códigos susceptibles de error del código de LDPC sean mapeados respecto a bits fuertes de símbolos modulados ortogonalmente.

- 35 El desmultiplexor de la figura 8 realiza la función de ese intercalador.

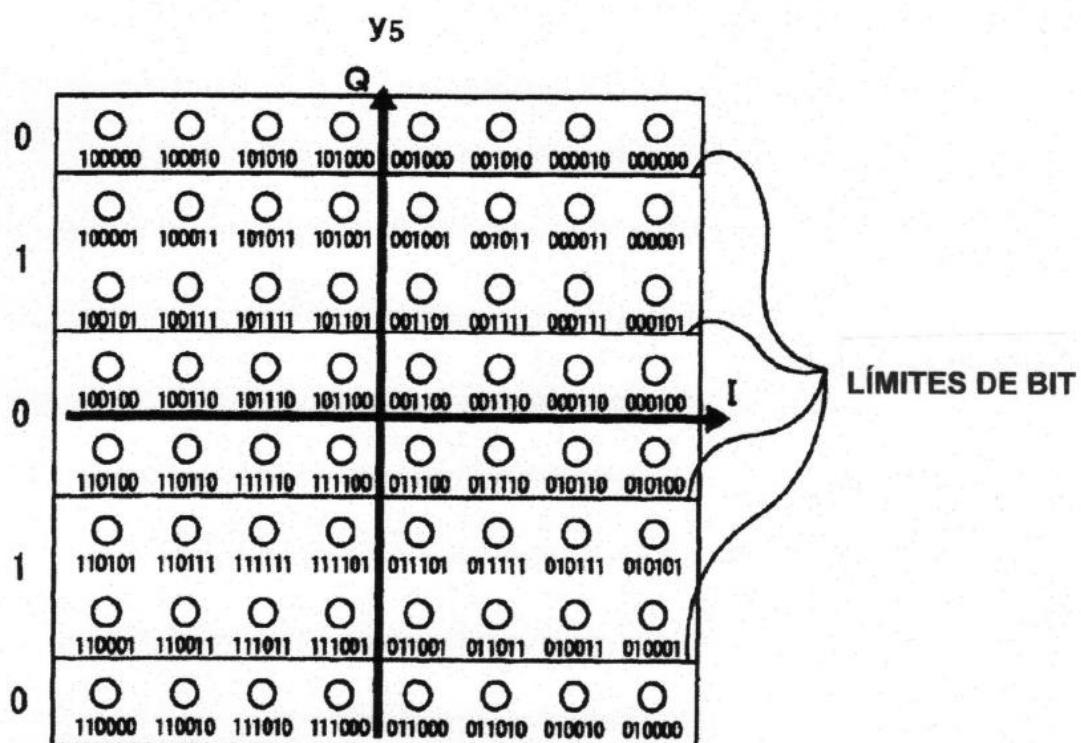

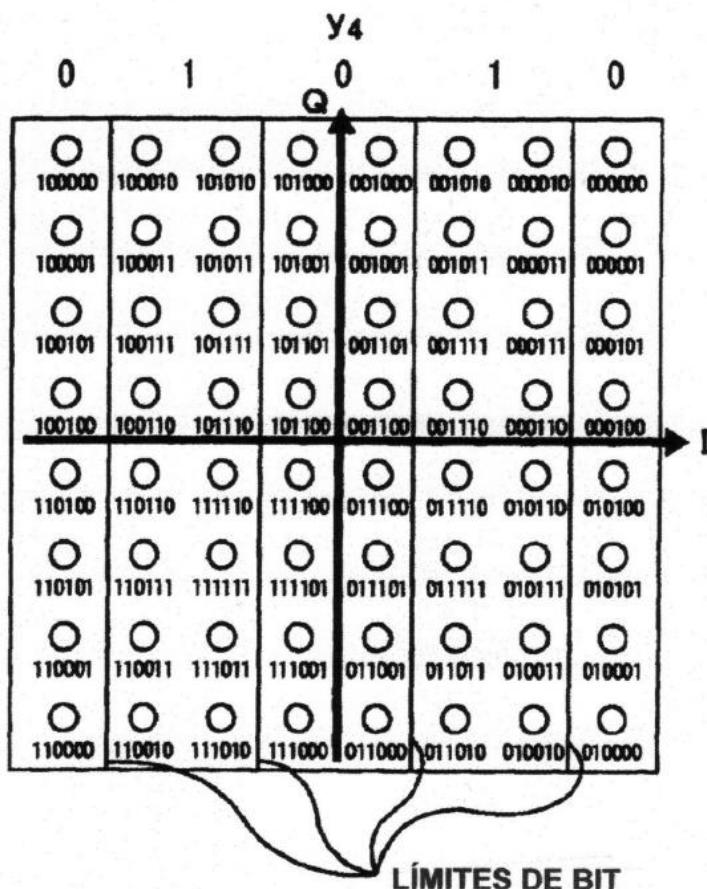

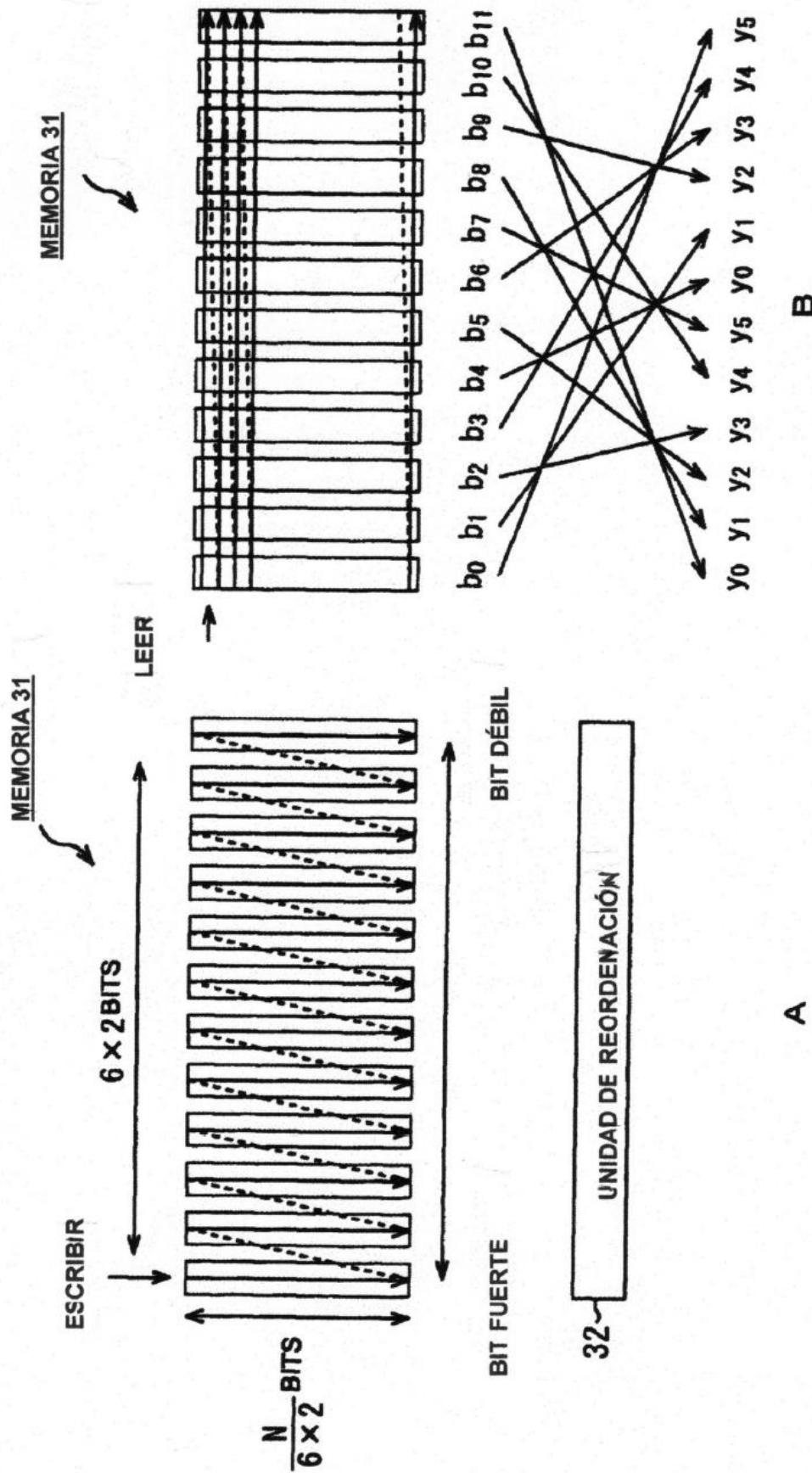

Las figuras 16A a 16D ilustran la operación del desmultiplexor 25 de la figura 8.

Específicamente, la figura 16A ilustra un ejemplo de configuración funcional del desmultiplexor 25.

- 40 El desmultiplexor 25 incluye una memoria 31 y una unidad 32 de reordenación. Se proporciona un código de LDPC a la memoria 31. La memoria 31 tiene una capacidad de almacenamiento para almacenar mb bits en la dirección de una fila (horizontal) y almacenar N/m bits en la dirección de una columna (vertical). Los bits del código de LDPC proporcionados a la memoria 31 son escritos en la dirección de una columna en la memoria 31 y son leídos en la dirección de una fila desde la memoria 31, y los bits de código leídos son proporcionados a la unidad 32 de reordenación.

- 45 En este caso, "m" representa el número de bits de código del código de LDPC mapeados en un símbolo y "b" representa un número entero específico positivo (es decir, un factor) por el que se multiplica "m" para obtener un múltiplo entero de "m". Adicionalmente, "N" (= longitud de información K + longitud de paridad M) representa la longitud de código del código de LDPC según se ha descrito con anterioridad.

La figura 16A ilustra un ejemplo de configuración del desmultiplexor 25 cuando el esquema de modulación es 64QAM. En consecuencia, el número de bits de código "m" de un código de LDPC mapeado en un símbolo es 6.

- 50 En la figura 16A, el factor "b" es 1 y por lo tanto la memoria 31 tiene una capacidad de almacenamiento de N/(6 x 1)

x (6 x 1) bits en las direcciones de columna y fila.

En lo que sigue, una región de almacenamiento de la memoria 31, que es un bit en la dirección de una fila y se extiende en la dirección de una columna, se menciona como columna según sea apropiado. En el ejemplo de la figura 16A, la memoria 31 incluye 6 (= 6 x 1) columnas.

- 5 El desmultiplexor 25 escribe bits de código del código de LDPC en la memoria 31 en la dirección de una columna desde la parte superior a la inferior de cada columna, empezando secuencialmente desde la columna más a la izquierda hasta la derecha.

Cuando los bits de código han escrito completamente de arriba abajo la columna más a la derecha, los bits de código son leídos desde la memoria 31 en la dirección de una fila, empezando secuencialmente desde la primera fila de todas las columnas de la memoria 31 en unidades de 6 bits (es decir, mb bits), y los bits de código leídos son proporcionados a la unidad 32 de reordenación.

- 10 La unidad 32 de reordenación reordena posiciones de 6 bits de código recibidos desde la memoria 31 y presenta a la salida los 6 bits reordenados como 6 bits  $y_0, y_1, y_2, y_3, y_4$  e  $y_5$  que representan un símbolo de 64 QAM.

15 Más específicamente, cuando los 6 bits de código leídos a partir de la memoria 31 en la dirección de una fila son indicados como  $b_0, b_1, b_2, b_3, b_4$  y  $b_5$  empezando secuencialmente desde el MSB, los bits de código que incluyen "y" que son adyacentes al bit " $b_5$ ", son bits de código susceptibles de error de acuerdo con la relación de peso de columna que se ha descrito anteriormente con referencia a la figura 11.

- 20 La unidad 32 de reordenación reordena posiciones de los 6 bits de código  $b_0$  a  $b_5$  recibidos desde la memoria 31 de tal modo que los bits de código susceptibles de error entre los 6 bits de código  $b_0$  a  $b_5$  procedentes de la memoria 31 son asignados a bits fuertes entre los 6 bits  $y_0$  a  $y_5$  que representan un símbolo de 64 QAM.

Varias compañías han sugerido una diversidad de métodos para reordenar los 6 bits de código  $b_0$  a  $b_5$  a partir de la memoria 31 y asignarlos a 6 bits  $y_0$  a  $y_5$  que representan un símbolo de 64 QAM, respectivamente.

La figura 16B ilustra un primer método de reordenación, la figura 16C ilustra un segundo método de reordenación y la figura 16D ilustra un tercer método de reordenación.

- 25 En las figuras 16B a 16D, una línea que conecta los bits  $b_i$  e  $y_j$  indica que un bit de código  $b_i$  está asignado a un bit de símbolo  $y_j$  (es decir, la posición del bit de código  $b_i$  se cambia a la del bit de símbolo  $y_j$ ), de manera similar a las figuras 17A y 17B que se describen más adelante.

Mientras que el primer método de reordenación de la figura 16B sugiere el uso de uno de los tres tipos de reordenación, el segundo método de reordenación de la figura 16C sugiere utilizar uno de dos tipos de reordenación.

- 30 El tercer método de reordenación de la figura 16D sugiere la selección y el uso secuencial de 6 tipos de reordenación.

Las figuras 17A y 17B ilustran un ejemplo de configuración de un desmultiplexor 25 y un cuarto método de reordenación en el caso de que el método de modulación sea 16QAM (de modo que el número de bits de código "m" de un código de LDPC mapeado respecto a un símbolo sea 6 como en la figura 16) y el factor "b" sea 2.

- 35 Cuando el factor "b" es 2, la memoria 31 tiene una capacidad de almacenamiento de  $n/(6 \times 2) \times (6 \times 2)$  bits en las direcciones de columna y fila, y tiene 12 (= 6 x 2) columnas.

La figura 17A ilustra el orden en el que los bits de código de un código de LDPC son escritos en la memoria 31.

El desmultiplexor 25 escribe bits de código en la memoria 31 en la dirección de una columna desde la parte superior hasta la inferior de cada columna, empezando secuencialmente desde la columna más a la izquierda hasta la derecha según se ha descrito anteriormente con referencia a la figura 16A.

Cuando los bits de código han sido escritos por completo de arriba abajo de la columna más a la derecha, los bits de código son leídos desde la memoria 31 en la dirección de una fila, secuencialmente a partir de la primera fila de todas las columnas de la memoria 31 en unidades de 12 bits (es decir, mb bits), y los bits de código leídos son proporcionados a la unidad 32 de reordenación.

- 45 La unidad 32 de reordenación reordena las posiciones de 12 bits de código recibidos desde la memoria 31 de acuerdo con el cuarto método de reordenación y presenta a la salida los 12 bits reordenados como 12 bits que representan dos símbolos (es decir, símbolos b) de 6aQAM, es decir, 6 bits  $y_0, y_1, y_2, y_3, y_4$  e  $y_5$  que representan un símbolo de 64QAM y 6 bits  $y_0, y_1, y_2, y_3, y_4$  e  $y_5$  que representan un símbolo de 64QAM y 6 bits  $y_0, y_1, y_2, y_3, y_4$  e  $y_5$  que representan el otro símbolo.

- 50 La figura 17B ilustra el cuarto método de reordenación realizado por la unidad 32 de reordenación de la figura 17A.

El óptimo de los métodos de reordenación, que minimiza tasas de error en las trayectorias de comunicación de AWGM, depende de la tasa de código de un código de LDPC o similar.

Ahora se va a describir cómo el intercalador de paridad 23 de la figura 8 realiza el intercalado de paridad con referencia a las figuras 18 a 20.

- 5 La figura 18 ilustra (parte de) un gráfico de Tanner de una matriz de comprobación de paridad de un código de LDPC.

Si ocurre un error, tal como una borradura, simultáneamente en dos o más nodos de variable conectados a (o dos o más bits de código correspondientes a) un nodo de comprobación, entonces el nodo de comprobación devuelve un mensaje con una probabilidad de "0" que es igual a la probabilidad de "1" a cada nodo de variable conectado al nodo de comprobación según se muestra en la figura 18. Por lo tanto, el rendimiento de descodificación se reduce si son borrados múltiples nodos de variable conectados al mismo nodo de comprobación.

Un código de LDPC definido en la especificación DVB-S.2, que es presentado a la salida por el codificador 21 de LDPC de la figura 8, es un código IRA y una matriz  $H_T$  de paridad de la matriz H de comprobación de paridad tiene una estructura gradual según se ha mostrado en la figura 11.

- 15 Las figuras 19A y 19B ilustran una matriz  $H_T$  de paridad que tiene una estructura gradual y un gráfico de Tanner que corresponde a la matriz  $H_T$  de paridad.

Es decir, la figura 19A ilustra una matriz  $H_T$  de paridad de estructura gradual, y la figura 19B ilustra un gráfico de Tanner correspondiente a la matriz  $H_T$  de paridad de la figura 19A.

- 20 Cuando la matriz  $H_T$  de paridad tiene una estructuras gradual, los nodos de variable cuyos mensajes son obtenidos utilizando bits de código adyacentes (bits de paridad) de un código de LDPC, correspondientes a columnas que incluyen elementos que tienen un valor de "1" en la matriz  $H_T$  de paridad, son conectados al mismo nodo de comprobación en el gráfico de Tanner de la matriz  $H_T$  de paridad.