# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 569 904

51 Int. Cl.:

G11C 16/22 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

- 96 Fecha de presentación y número de la solicitud europea: 27.10.2009 E 09748611 (2)

- (97) Fecha y número de publicación de la concesión europea: 23.03.2016 EP 2351042

- (54) Título: Prevención de protección frente a escritura permanente no intencionada en memoria no volátil

- (30) Prioridad:

29.10.2008 US 260188

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 13.05.2016

(73) Titular/es:

MICROCHIP TECHNOLOGY INCORPORATED (100.0%) 2355 West Chandler Boulevard Chandler, AZ 85224-6199, US

(72) Inventor/es:

MIETUS, DAVID FRANCIS; BEAUCHAMP, BRUCE EDWARD; ALEXANDER, SAMUEL y ABERRA, EZANA H.

(74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

#### **DESCRIPCIÓN**

Prevención de protección frente a escritura permanente no intencionada en memoria no volátil

#### Campo de la técnica

La presente divulgación se refiere a dispositivos de circuito integrado que tienen una memoria no volátil programable y, más en concreto, a una memoria no volátil programable capaz de una protección frente a escritura temporal y permanente.

#### **Antecedentes**

5

10

15

40

45

50

55

Los dispositivos de circuito integrado que tienen una memoria no volátil pueden almacenar parámetros de operación del dispositivo, programas de operación y/o datos fijos en la memoria no volátil. La memoria no volátil se puede proteger frente a escritura con el fin de evitar cambios no autorizados y/o involuntarios a los contenidos en la misma. Se encuentra disponible un número de medios para proteger frente a escritura la memoria no volátil y se hace referencia a los mismos, de forma colectiva en el presente documento, como "fusibles de protección frente a escritura". Se pueden implementar dos tipos de fusibles de protección frente a escritura con una memoria no volátil, a) un fusible de protección frente a escritura temporal que permite una función de desactivación por parte del usuario (deshabilitar protección frente a escritura), y b) un fusible de protección frente a escritura permanente que coloca de forma permanente la memoria no volátil en un modo protegido frente a escritura sin que el usuario sea capaz de desactivar la protección frente a escritura permanente. Por lo tanto, una vez que un dispositivo se ha programado y se ha protegido frente a escritura de forma permanente, el programa del dispositivo no se puede alterar a partir de entonces.

Por lo general, un dispositivo de circuito integrado tendrá una patilla (conexión externa) de función múltiple que se puede utilizar o bien para una operación normal del circuito integrado o bien para unas operaciones de programación en el mismo. La patilla de función múltiple se puede caracterizar además como que requiere diferentes niveles de tensión, por ejemplo, el uso de una tensión más alta que la tensión de operación para realizar una operación de programación semipermanente o permanente.

De acuerdo con la especificación de la organización *JEDEC Solid State Technology Association* para la memoria de solo lectura eléctricamente borrable y programable (EEPROM, *electrically erasable and programmable read only memory*) con Detección de Presencia Serie (SPD, *Serial Presence Detection*), cuando se intenta programar un fusible de protección frente a escritura temporal usando la instrucción de SWP (*software write protect*, protección frente a escritura de soporte lógico), si una tensión elevada, VHV, sobra la patilla de dirección A0 del dispositivo no se encuentra a una tensión lo bastante elevada para completar la instrucción de protección frente a escritura temporal (SWP), entonces el dispositivo hará que se establezca su fusible de protección frente a escritura permanente, por ejemplo, ejecutará la instrucción de protección frente a escritura de soporte lógico permanente (PSWP, *permanent software write protect*) en su lugar. Esto da como resultado que el dispositivo quede protegido frente a escritura de forma permanente, y requeriría que el dispositivo se sustituyera físicamente si se hubiera de implementar en el mismo un cambio y/o corrección de programa.

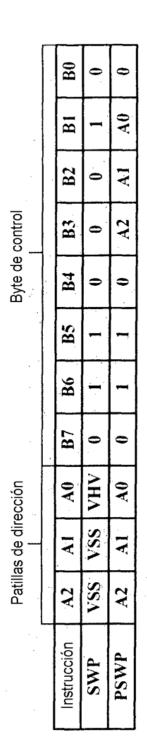

Haciendo referencia a la figura 5, se muestra una tabla de tensiones y niveles lógicos que están asociados con una conexión de entrada-salida de función múltiple externa de la tecnología anterior que se usa para realizar instrucciones de protección frente a escritura temporal (SWP) y de protección frente a escritura de soporte lógico permanente (PSWP). Cuando se intenta programar una protección frente a escritura (fusible) temporal usando la instrucción de SWP, si el nivel de VHV que se aplica a la conexión de entrada A0 es insuficiente, el dispositivo de circuito integrado programará de forma involuntaria la protección frente a escritura (fusible) permanente, es decir, ejecutará la instrucción de PSWP en su lugar. Esto hace que el dispositivo de circuito integrado quede protegido frente a escritura de forma permanente.

La nota técnica de Micron TN-04-42 "Memory Module Serial Presence Detect" de 2002, (disponible en http://www.micron.com/support/serial-presence-detect) divulga detalles adicionales acerca de la SWP y la PSWP de los dispositivos de EEPROM con SPD.

La solicitud internacional PCT WO2006/039075 con fecha 13 de abril de 2006 (Microchip Technology Incorporated/Simons) divulga una protección frente a escritura de una memoria no volátil incorporada en un dispositivo de C. I. usando una 'sobretensión' sobre una patilla de señal para establecer o desactivar un indicador de protección frente a escritura temporal.

#### **Sumario**

Por lo tanto, existe una necesidad de evitar que una operación de programación no deseada, por ejemplo, una protección frente a escritura permanente, tenga lugar de forma involuntaria debido a unas tolerancias de tensión marginales de las diversas funciones de programación. De acuerdo con las enseñanzas de la presente divulgación, se puede establecer un intervalo, por ejemplo, una "ventana", entre diferentes niveles de tensión que se usan para diferentes funciones de programación de un dispositivo de circuito integrado, implementando de este modo una zona

de protección ("zona segura") de no operación para facilitar la prevención de una operación de programación irreversible no intencionada, por ejemplo, una protección frente a escritura permanente. El presente objeto puede ser logrado por el dispositivo de circuito integrado y el procedimiento tal como se define en las reivindicaciones independientes. Se pueden lograr potenciaciones adicionales de acuerdo con las reivindicaciones dependientes.

De acuerdo con una realización a modo de ejemplo específica de la presente divulgación, un dispositivo de circuito integrado que tiene una memoria programable no volátil comprende: una memoria no volátil; una lógica de control de memoria y de programación acoplada a la memoria no volátil y adaptada para escribir datos en la memoria no volátil; por lo menos una conexión de entrada de función múltiple acoplada a la lógica de control de memoria y de programación, en el que la por lo menos una entrada de función múltiple se usa para habilitar una protección frente a escritura de los datos escritos en la memoria no volátil; en el que la protección frente a escritura comprende una protección frente a escritura permanente cuando una tensión sobre la por lo menos una entrada de función múltiple es menor que un primer valor de tensión, y una protección frente a escritura temporal cuando la tensión sobre la por lo menos una entrada de función múltiple es mayor que un segundo valor de tensión, siendo el segundo valor de tensión mayor que el primer valor de tensión; y en el que la protección frente a escritura no se puede habilitar cuando la tensión sobre la por lo menos una entrada de función múltiple es igual a o mayor que el primer valor de tensión y menor que o igual al segundo valor de tensión.

De acuerdo con otra realización a modo de ejemplo específica de la presente divulgación, un procedimiento para evitar una protección frente a escritura permanente no intencionada de una memoria programable no volátil en un dispositivo de circuito integrado comprende: comparar una tensión sobre una entrada de una conexión de entrada de función múltiple de un dispositivo de circuito integrado con un primer y un segundo valores de tensión, en el que el segundo valor de tensión es mayor que el primer valor de tensión; si la tensión sobre la entrada de la conexión de entrada de función múltiple es menor que el primer valor de tensión, entonces permitir una protección frente a escritura permanente de una memoria programable en el dispositivo de circuito integrado; si la tensión sobre la entrada de la conexión de entrada de función múltiple es mayor que el segundo valor de tensión, entonces permitir una protección frente a escritura temporal de la memoria programable en el dispositivo de circuito integrado; y si la tensión sobre la entrada de la conexión de entrada de función múltiple es igual a o mayor que el primer valor de tensión y menor que o igual a la segunda tensión, entonces no permitir una protección frente a escritura de la memoria programable.

#### Breve descripción de los dibujos

20

25

35

40

55

30 Se puede adquirir una comprensión más completa de la presente divulgación al hacer referencia a la siguiente descripción tomada junto con los dibujos adjuntos, en los que:

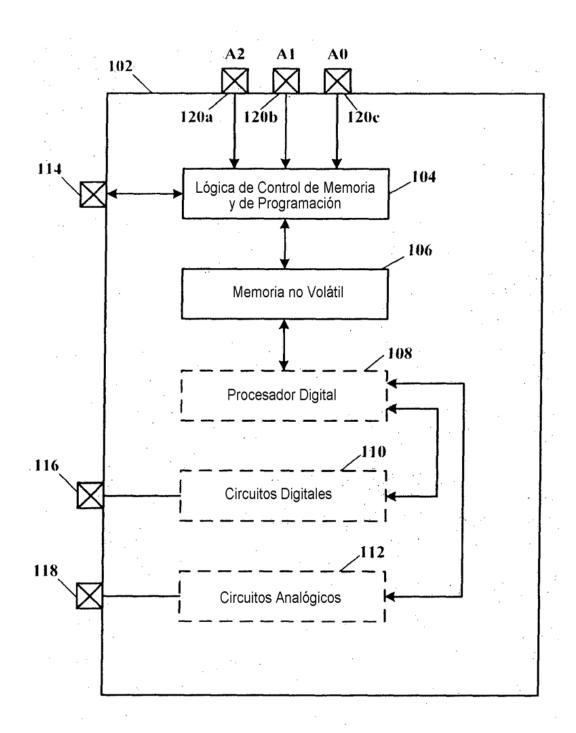

la figura 1 es un diagrama de bloques esquemático de un dispositivo de circuito integrado que tiene por lo menos una conexión de entrada-salida de función múltiple externa en un paquete de circuito integrado;

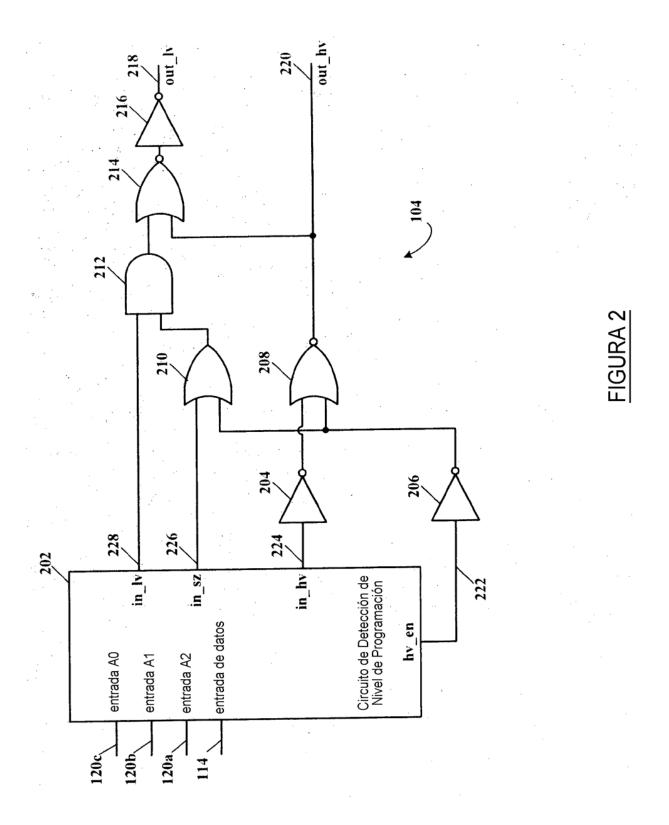

la figura 2 es un diagrama esquemático de un circuito lógico para implementar una ventana no operativa para la por lo menos una conexión de función múltiple externa, de acuerdo con una realización a modo de ejemplo específica de la presente divulgación;

la figura 3 son unas tablas de relaciones de diversas entradas de nivel de tensión y salidas lógicas del circuito que se muestra en la figura 2, de acuerdo con las enseñanzas de la presente divulgación;

la figura 4 es una tabla de tensiones y niveles lógicos que están asociados con el dispositivo de circuito integrado de la figura 1 y el circuito que se muestra en la figura 2, de acuerdo con las enseñanzas de la presente divulgación; y

la figura 5 es una tabla de tensiones y niveles lógicos que están asociados con una conexión de entrada-salida de función múltiple externa de la tecnología anterior que se usa para realizar instrucciones de protección frente a escritura temporal (SWP) y de protección frente a escritura de soporte lógico permanente (PSWP).

A pesar de que la presente divulgación es susceptible de diversas modificaciones y formas alternativas, unas realizaciones a modo de ejemplo específicas de la misma se han mostrado en los dibujos y se describen con detalle en el presente documento. Se debería entender, no obstante, que la descripción en el presente documento de unas realizaciones a modo de ejemplo específicas no tiene por objeto limitar la divulgación a las formas particulares que se divulgan en el presente documento sino que, por el contrario, la presente divulgación es para cubrir todas las modificaciones y equivalentes tal como son definidos por las reivindicaciones adjuntas.

#### Descripción detallada

Haciendo referencia a continuación al dibujo, los detalles de unas realizaciones a modo de ejemplo específicas se ilustran de forma esquemática. Elementos semejantes en los dibujos se representarán mediante números semejantes, y elementos similares se representarán mediante números semejantes con un sufijo en letra minúscula diferente.

## ES 2 569 904 T3

Haciendo referencia a la figura 1, se muestra un diagrama de bloques esquemático de un dispositivo de circuito integrado que tiene por lo menos una conexión de entrada-salida de función múltiple externa en un paquete de circuito integrado. El dispositivo de circuito integrado 102 comprende una lógica de control de memoria y de programación 104, una memoria no volátil 106 y unas conexiones externas, por ejemplo, las conexiones 114 y 120 y otras. Por lo menos una de las conexiones externas, por ejemplo, la conexión 120c, puede ser una conexión de entrada, de salida o de entrada-salida de función múltiple. De acuerdo con las enseñanzas de la presente divulgación, la por lo menos una conexión de función múltiple puede tener unas funciones primaria y secundaria, tal como, por ejemplo pero sin limitarse a, una entrada o entradas de selección de dirección (primaria); y una protección frente a escritura de memoria no volátil, tanto temporal como permanente (secundaria), por ejemplo, para establecer unos "fusibles" para una protección borrable y no borrable de los contenidos de programa de la memoria no volátil 106

10

40

El dispositivo de circuito integrado 102 puede comprender además un procesador digital 108, unos circuitos digitales 110 y/o unos circuitos analógicos 112. Unas conexiones de entrada y/o de salida externas 116 y 118 están acopladas a los circuitos digitales 110 y los circuitos analógicos 112, respectivamente.

- Haciendo referencia a la figura 2, se muestra un diagrama esquemático de un circuito lógico para implementar una ventana no operativa para la por lo menos una conexión de función múltiple externa, de acuerdo con una realización a modo de ejemplo específica de la presente divulgación. Las conexiones externas 114, 120a, 120b y 120c tienen una función secundaria que se puede usar junto con la programación y la protección frente a escritura de la memoria no volátil programada 106. Las puertas lógicas combinacionales 204 216 son representativas de una realización a modo de ejemplo específica, de acuerdo con las enseñanzas de la presente divulgación, y se contempla y se encuentra dentro del alcance de la presente divulgación que se pueda usar cualquier diseño lógico tal como sería inmediatamente evidente a un experto en el diseño de lógica digital y que tenga el beneficio de la presente divulgación.

- Haciendo referencia a la figura 3, se muestran unas tablas de relaciones de diversas entradas de nivel de tensión y salidas lógicas del circuito que se muestra en la figura 2, de acuerdo con las enseñanzas de la presente divulgación. Por razones ilustrativas, se divulgan unos valores de tensión VIH, mín = 0,7 \* Vdd; VIL, máx = 0,3 \* Vdd; VIH, máx = Vdd + 0,5 voltios; VHH, mín = 7 voltios; y Vdd es la tensión de fuente de alimentación. Se contempla y se encuentra dentro del alcance de la presente divulgación que se puedan usar otros valores de tensión y sus relaciones y que se encuentren dentro del alcance y de la intención de la presente divulgación.

- 30 En la tabla 3(a), cuando la línea de señal hv\_en 222 se encuentra a un nivel lógico "0", la línea de señal out\_hv 220 se encuentra siempre a un nivel lógico "0" para todos los valores de tensión que se aplican a la entrada A0 de función múltiple (la conexión 120c). La línea de señal out\_lv 218 sigue la línea de señal en\_lv 228 como encontrándose a un nivel lógico "1" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es mayor que o igual a VIH, mín; y a un nivel lógico "0" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es menor que o igual a VIL, máx.

- En la tabla 3(b), cuando la línea de señal hv\_en 222 se encuentra a un nivel lógico "1", la línea de señal en\_lv 228 se encuentra a un nivel lógico "1" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es mayor que o igual a VIH, mín; y a un nivel lógico "0" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es menor que o igual a VIL, máx. La línea de señal en\_sz (de zona segura) 226 se encontrará a un nivel lógico "1" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es menor que VIH, máx, y a un nivel lógico "0" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es mayor que o igual a VIH, máx. La línea de señal en\_hv 224 se encontrará a un nivel lógico "1" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es mayor que o igual a VHH, mín, y a un nivel lógico "0" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es menor que VHH, mín,

- La línea de señal out\_lv 218 se encontrará a un nivel lógico "0" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es menor que o igual a VIL, máx; o menor que VHH, mín, y mayor que o igual a VIH, máx. La línea de señal out\_lv 218 se encontrará a un nivel lógico "1" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es mayor que VHH, mín; o menor que VIH, máx, y mayor que o igual a VIH, mín.

- La línea de señal out\_hv 220 se encontrará a un nivel lógico "1" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es mayor que o igual a VHH, mín; y a un nivel lógico "0" cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es menor que VHH, mín. El uso de las líneas de señal 222, 224, 226 y 228 combinadas con las puertas lógicas 204 216 crean la "zona segura" en la que se inhibe toda forma de protección frente a escritura. La zona segura será, de acuerdo con la presente realización a modo de ejemplo específica, cuando la tensión sobre la entrada A0 de función múltiple (la entrada 120c) sea menor que VHH, mín; pero mayor que o igual a VIH, máx.

Haciendo referencia a la figura 4, se muestra una tabla de tensiones y niveles lógicos que están asociados con el dispositivo de circuito integrado de la figura 1 y el circuito que se muestra en la figura 2, de acuerdo con las enseñanzas de la presente divulgación. La lógica anteriormente mencionada de la figura 2 crea de ese modo una zona segura entre VHH, mín; y VIH, máx; en la cual no puede tener lugar ni una protección frente a escritura de

## ES 2 569 904 T3

memoria temporal (SWP) ni una protección frente a escritura de memoria permanente (PSWP). Cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es mayor que VHH, mín; puede tener lugar una protección frente a escritura de memoria temporal (SWP) y, cuando la tensión sobre la entrada A0 de función múltiple (la conexión 120c) es menor que VIH, máx; puede tener lugar una protección frente a escritura de memoria permanente (PSWP). Por lo tanto, no puede tener lugar de forma accidental una protección frente a escritura de memoria permanente (PSWP) involuntaria, de acuerdo con las enseñanzas de la presente divulgación.

5

10

A pesar de que se han mostrado, se han descrito y se definen unas realizaciones de la presente divulgación por referencia a unas realizaciones a modo de ejemplo de la divulgación, tales referencias no implican una limitación a la divulgación, y no se ha de inferir limitación alguna de este tipo. La materia objeto que se divulga es capaz de considerables modificaciones, alteraciones y equivalentes en cuanto a su forma y función, tal como se les ocurrirá a los expertos en la materia pertinente y que tengan el beneficio de la presente divulgación.

#### **REIVINDICACIONES**

- 1. Un dispositivo de circuito integrado que tiene una memoria programable no volátil, que comprende:

- una memoria no volátil (106);

una lógica de control de memoria y de programación (104) acoplada a la memoria no volátil (106) y adaptada para escribir datos en la memoria no volátil (106), en el que dicha lógica de control de memoria y de programación (104) se puede operar para determinar si se va a realizar una función de protección frente a escritura a partir de señales digitales suministradas a al menos una conexión de entrada (120a..c, 114);

al menos una conexión de entrada de función múltiple (120c; A0) acoplada a la lógica de control de memoria y de programación (104), en el que la al menos una conexión de entrada de función múltiple (120c; A0) se usa para distinguir entre una protección frente a escritura permanente y una temporal de los datos escritos en la memoria no volátil;

en el que

5

10

15

20

35

40

la protección frente a escritura permanente está habilitada cuando una tensión en la al menos una conexión de entrada de función múltiple (120c; A0) es menor que un primer valor de tensión, y

la protección frente a escritura temporal está habilitada cuando la tensión en la al menos una conexión de entrada de función múltiple (120c; A0) es mayor que un segundo valor de tensión, siendo el segundo valor de tensión mayor que el primer valor de tensión; y

en el que la protección frente a escritura no se puede habilitar cuando la tensión en la al menos una conexión de entrada de función múltiple (120c; A0) es igual a o mayor que el primer valor de tensión y menor que o igual al segundo valor de tensión.

- 2. El dispositivo de circuito integrado, de acuerdo con la reivindicación 1, en el que el primer valor de tensión es sustancialmente igual a aproximadamente medio voltio más que una tensión de fuente de alimentación.

- 3. El dispositivo de circuito integrado, de acuerdo con la reivindicación 1, en el que el segundo valor de tensión es sustancialmente igual a aproximadamente 4,8 voltios más que una tensión de fuente de alimentación.

- 4. El dispositivo de circuito integrado, de acuerdo con la reivindicación 1, en el que el segundo valor de tensión es sustancialmente igual a aproximadamente siete voltios.

- 5. El dispositivo de circuito integrado, de acuerdo con la reivindicación 1, en el que la protección frente a escritura permanente comprende programar un fusible de protección frente a escritura permanente.

- 6. El dispositivo de circuito integrado, de acuerdo con la reivindicación 1, en el que la protección frente a escritura temporal comprende programar un fusible de protección frente a escritura temporal.

- 7. El dispositivo de circuito integrado, de acuerdo con la reivindicación 1, en el que la lógica de control de memoria y de programación comprende:

un circuito de detección de nivel de programación (202), en el que el circuito de detección de nivel de programación determina cuándo

la tensión en la al menos una conexión de entrada de función múltiple (120a) es menor que el primer valor de tensión.

la tensión en la al menos una conexión de entrada de función múltiple (120c; A0) es igual a o mayor que el primer valor de tensión y menor que o igual a la segunda tensión, y

la tensión en la al menos una conexión de entrada de función múltiple (120c; A0) es mayor que la segunda tensión; y

una lógica (204..216) para permitir la protección frente a escritura permanente, no permitir la protección frente a escritura permanente y la temporal y permitir la protección frente a escritura temporal dependiendo de la tensión en la al menos una conexión de entrada de función múltiple (120c; A0).

- 45 8. El dispositivo de circuito integrado, de acuerdo con la reivindicación 1, que comprende además un procesador digital (108) acoplado a la memoria no volátil.

- 9. El dispositivo de circuito integrado, de acuerdo con la reivindicación 8, que comprende además unos circuitos digitales (110) acoplados al procesador digital (108) y al menos una conexión de entrada-salida digital (116).

- 10. El dispositivo de circuito integrado, de acuerdo con la reivindicación 8, que comprende además unos circuitos analógicos (112) acoplados al procesador digital (108) y al menos una conexión de entrada-salida analógica (118).

- 11. El dispositivo de circuito integrado, de acuerdo con la reivindicación 1, en el que un byte de control (B0..B7) se usa para determinar si se va a realizar una protección frente a escritura.

- 12. El dispositivo de circuito integrado, de acuerdo con la reivindicación 11, en el que por lo menos un bit (B3) de dicho byte de control (B0..B7) se compara con una tensión aplicada a dicha conexión de entrada de función múltiple (120c; A0).

- 13. Un procedimiento para evitar una protección frente a escritura permanente no intencionada de una memoria programable no volátil en un dispositivo de circuito integrado, comprendiendo dicho procedimiento:

- determinar si se va a realizar una función de protección frente a escritura a partir de unas señales lógicas aplicadas a una pluralidad de conexiones de entrada (120a..c, 114) de un dispositivo de circuito integrado (102); comparar una tensión en una entrada de una conexión de entrada de función múltiple (120c; A0) del dispositivo de circuito integrado (102) con un primer y un segundo valor de tensión, en el que el segundo valor de tensión es mayor que el primer valor de tensión:

- si la tensión en la entrada de la conexión de entrada de función múltiple (120c; A0) es menor que el primer valor de tensión, entonces permitir una protección frente a escritura permanente de una memoria programable en el dispositivo de circuito integrado (102);

- si la tensión en la entrada de la conexión de entrada de función múltiple (120c; A0) es mayor que el segundo valor de tensión, entonces permitir una protección frente a escritura temporal de la memoria programable en el dispositivo de circuito integrado (102); y

10

15

- si la tensión en la entrada de la conexión de entrada de función múltiple (120c; A0) es igual a o mayor que el primer valor de tensión y menor que o igual a la segunda tensión, entonces no permitir una protección frente a escritura de la memoria programable (106).

- 20 14. El procedimiento de acuerdo con la reivindicación 13, en el que un byte de control (B0..B7) se usa para determinar si se va a realizar una protección frente a escritura.

- 15. El procedimiento de acuerdo con la reivindicación 14, en el que por lo menos un bit (B3) de dicho byte de control (B0..B7) se compara con una tensión aplicada a dicha conexión de entrada de función múltiple (120c; A0).

FIGURA 1

# FIGURA 3

|                        | 1   | atillas d | Patillas de direccion |    |    |    | Byte de control | control |    |    |    |

|------------------------|-----|-----------|-----------------------|----|----|----|-----------------|---------|----|----|----|

|                        |     |           |                       |    |    |    |                 |         |    |    |    |

| Instrucción            | A2  | AI        | Α0                    | B7 | B6 | BS | B4              | B3      | B2 | Bl | B0 |

| SWP                    | NSS | NSS       | > VHH min             | 0  | -  | _  | 0               | 0       | 0  | 1  | 0  |

| Operación sin fusible> | NSS | NSS.      | Zona segura           | 0  | -  | -  | 0               | 0       | 0  | -  | 0  |

| PSWP                   | A2  | A1        | < VIH máx             | 0  | -  | -  | 0               | A2      | Al | A0 | 0  |

|                        |     |           |                       |    |    |    |                 |         |    |    |    |

|                        |     |           |                       |    |    |    |                 |         |    |    |    |

|                        |     |           |                       |    |    |    |                 |         |    |    |    |

|                        |     |           |                       |    |    |    |                 |         |    |    |    |

|                        |     |           |                       |    |    |    |                 |         |    |    |    |

|                        |     |           |                       |    |    |    |                 |         |    |    |    |

FIGURA 4

| Símbolo | Parámetro              | Condición de prueba   | Min | Máx | Unidades |

|---------|------------------------|-----------------------|-----|-----|----------|

| VHV     | tensión elevada de SA0 | $VHV-VDDSD \ge 4,8 V$ | 7   | 10  | ^        |

FIGURA 5 (Tecnología Anterior)