# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 575 095

51 Int. Cl.:

**G06F 13/16** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

96 Fecha de presentación y número de la solicitud europea: 16.11.2012 E 12808934 (9)

(97) Fecha y número de publicación de la concesión europea: 06.04.2016 EP 2780813

(54) Título: Memoria configurada para proporcionar acceso simultáneo de lectura / escritura a múltiples bancos

(30) Prioridad:

16.11.2011 US 201113297771

Fecha de publicación y mención en BOPI de la traducción de la patente: **24.06.2016**

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121, US

(72) Inventor/es:

TERZIOGLU, ESIN y PARK, DONGKYU

74) Agente/Representante:

FORTEA LAGUNA, Juan José

## **DESCRIPCIÓN**

Memoria configurada para proporcionar acceso simultáneo de lectura / escritura a múltiples bancos

#### 5 Campo de divulgación

La presente invención está orientada a una memoria de ordenador que permite el acceso simultáneo de lectura y de escritura a distintos bancos de una memoria de múltiples bancos y a un procedimiento de provisión de tal acceso y más específicamente, a una memoria de ordenador que permite el acceso simultáneo de lectura y de escritura a distintos bancos de una memoria de múltiples bancos enviando una instrucción que incluye una ubicación de memoria y una indicación de una operación a realizar en la ubicación de memoria y hacia un procedimiento de provisión de tal acceso.

#### **Antecedentes**

10

20

25

30

35

40

60

65

La memoria convencional de puerto único incluye generalmente un conjunto único de direcciones y un control único. Por lo tanto, solamente un dispositivo puede acceder a la misma a la vez: puede ser realizada una única operación de lectura o una única operación de escritura, pero ambos tipos de operación no pueden ser realizados al mismo tiempo.

Cuando es deseable proporcionar acceso simultáneo de lectura y de escritura a una memoria, puede ser usada una memoria de dos puertos o una memoria de múltiples puertos. Por ejemplo, puede hacerse un acceso de lectura mediante un puerto de la memoria, mientras que se hace un acceso de escritura mediante el otro puerto. Las memorias convencionales de dos puertos o de múltiples puertos, sin embargo, incluyen generalmente más transistores que las memorias de puerto único y por tanto ocupan más espacio en un chip que las memorias de puerto único. Cuando no se requiere el acceso a la misma ubicación (o cuando puede estar prohibido), pueden usarse memorias distintas; sin embargo, hay también una penalización en el área asociada al uso de memorias distintas pues muchos de los circuitos periféricos para una de las memorias están duplicados para la otra memoria. La necesidad de lectura y de escritura simultáneas debe por tanto ser sopesada con respecto a la penalización en que se incurre para el espacio y las memorias de puerto dual o de múltiples puertos son seleccionadas en general solamente cuando la necesidad del acceso simultáneo sobrepasa las penalizaciones de área y de filtración asociadas con las mismas. Sería deseable por lo tanto proporcionar una memoria que tenga capacidades simultáneas de lectura y escritura que mejore las memorias convencionales de puerto dual o de múltiples puertos.

Se reclama atención al documento CA 2 239 426 A1 que describe un sistema de memoria compartido, que comprende una pluralidad de bancos de memoria y una pluralidad de unidades de procesamiento. Cada unidad de procesamiento tiene dirección de memoria y buses de datos y genera una señal de comando para solicitar un acceso a memoria compartida. El sistema emplea al menos una estructura de conmutación de bus que comprende al menos un conmutador de bus de compuerta de pasaje. La estructura de conmutación de bus tiene un retardo de propagación despreciable y se usa para conectar la dirección de memoria y los buses de datos de cada unidad de procesamiento con cada banco de memoria. Un controlador de memoria compartida recibe la señal de solicitud de acceso a memoria asociada a cada unidad de procesamiento. El controlador de memoria compartida controla la estructura de conmutación de bus y cada banco de memoria a fin de permitir que distintas unidades de procesamiento accedan a cada banco de memoria simultáneamente y asíncronamente.

#### Sumario

45

De acuerdo con la presente invención se proporciona un procedimiento y una memoria, según lo enunciado, respectivamente, en las reivindicaciones independientes. Las realizaciones preferidas de la invención están descritas en las reivindicaciones dependientes.

Una realización ejemplar de la invención comprende un procedimiento que incluye proporcionar una memoria de múltiples bancos que tiene al menos bancos de memoria primero y segundo, donde cada uno de los bancos de memoria primero y segundo incluye una pluralidad de elementos de memoria de puerto único y proporcionar controladores locales primero y segundo para controlar operaciones de lectura y escritura en los bancos de memoria primero y segundo. El procedimiento también incluye proporcionar un controlador global para enviar instrucciones de lectura y escritura a los controladores locales primero y segundo y enviar una instrucción de lectura al primer controlador local y enviar una instrucción de escritura al segundo controlador local al mismo tiempo.

Otra realización incluye una memoria con al menos bancos primero y segundo de elementos de memoria de puerto único, un primer controlador local adaptado para enviar instrucciones de lectura y escritura al primer banco de memoria, un segundo controlador local adaptado para enviar instrucciones de lectura y escritura al segundo banco de memoria y un controlador global en comunicación con los controladores locales primero y segundo. El controlador global está configurado para recibir direcciones de memoria primera y segunda y una primera indicación de una operación a realizar en la primera dirección de memoria y una segunda indicación de una operación a realizar en la segunda dirección de memoria y para instruir al primer controlador local para realizar la primera operación indicada en la primera dirección de memoria y para instruir al segundo controlador local para realizar la segunda operación indicada en la segunda dirección de memoria al mismo tiempo.

Una realización adicional comprende un procedimiento que incluye proporcionar una memoria de múltiples bancos con al menos bancos de memoria primero y segundo, proporcionar al menos controladores primero y segundo adaptados para controlar las operaciones de lectura y escritura en al menos dichos bancos de memoria primero y segundo y proporcionar un controlador global en comunicación con al menos dichos controladores primero y segundo. El procedimiento también incluye proporcionar al controlador global una primera instrucción que comprende una primera dirección de memoria y una primera operación a realizar en la primera dirección de memoria y una segunda dirección de memoria. El controlador global instruye al primer controlador local para realizar la primera operación en la primera dirección de memoria y al segundo controlador local para realizar la segunda operación en la segunda dirección de memoria.

Otra realización más comprende un dispositivo que incluye una memoria de múltiples bancos que tiene al menos bancos de memoria primero y segundo y al menos controladores primero y segundo adaptados para controlar operaciones de lectura y de escritura en al menos dichos bancos de memoria primero y segundo. El dispositivo también incluye un controlador global en comunicación con al menos dichos controladores locales primero y segundo y el controlador está configurado para recibir una primera instrucción que comprende una primera dirección de memoria y una primera operación a realizar en la primera dirección de memoria y una segunda instrucción que comprende una segunda dirección de memoria y una segunda operación a realizar en la segunda dirección de memoria. El controlador global también está configurado para instruir al primer controlador local para realizar la primera operación en la primera dirección de memoria y para instruir al segundo controlador local para realizar la segunda operación en la segunda dirección de memoria.

Otra realización comprende una memoria que tiene una disposición de elementos de memoria, una disposición de controladores locales adaptada para enviar instrucciones de lectura y de escritura a la disposición de elementos de memoria y una disposición de controladores globales en comunicación con la disposición de controladores locales. La disposición de controladores globales está configurada para recibir direcciones de memoria primera y segunda y una primera indicación de una operación a realizar en una primera dirección de memoria y una segunda indicación de una operación a realizar en una segunda dirección de memoria y para instruir a la disposición de controladores locales para realizar la primera operación indicada en la primera dirección de memoria y la segunda operación indicada en la segunda dirección de memoria al mismo tiempo.

Una realización adicional comprende un procedimiento que incluye etapas para proporcionar una memoria de múltiples bancos con al menos bancos de memoria primero y segundo, comprendiendo cada uno de los bancos de memoria primero y segundo una pluralidad de elementos de memoria de puerto único y etapas para proporcionar controladores locales primero y segundo para controlar operaciones de lectura y de escritura en al menos dichos bancos de memoria primero y segundo. El procedimiento también incluye etapas para proporcionar un controlador global para enviar instrucciones de lectura y de escritura a los controladores locales primero y segundo y etapas para enviar una instrucción de lectura al primer controlador local y enviar una instrucción de escritura al segundo controlador local al mismo tiempo.

## 40 Breve descripción de los dibujos

10

15

20

25

30

35

55

60

65

Los dibujos adjuntos se presentan para ayudar en la descripción de las realizaciones de la invención y se proporcionan únicamente para la ilustración de las realizaciones y no la limitación de las mismas.

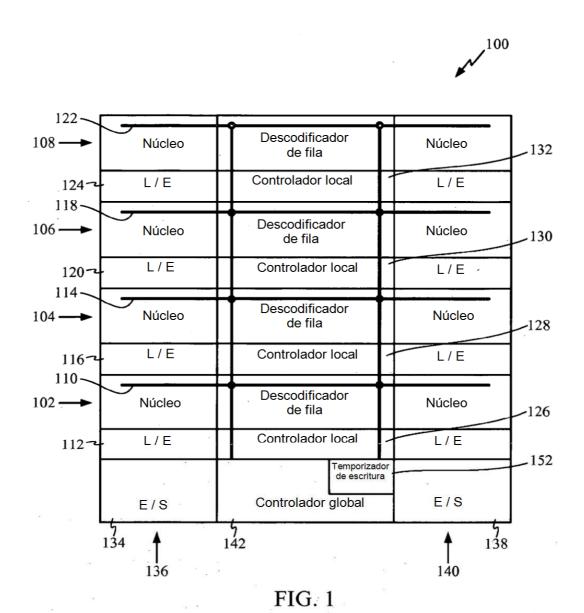

45 La FIG. 1 es un diagrama esquemático de circuitos que ilustra una memoria de acuerdo a una primera realización.

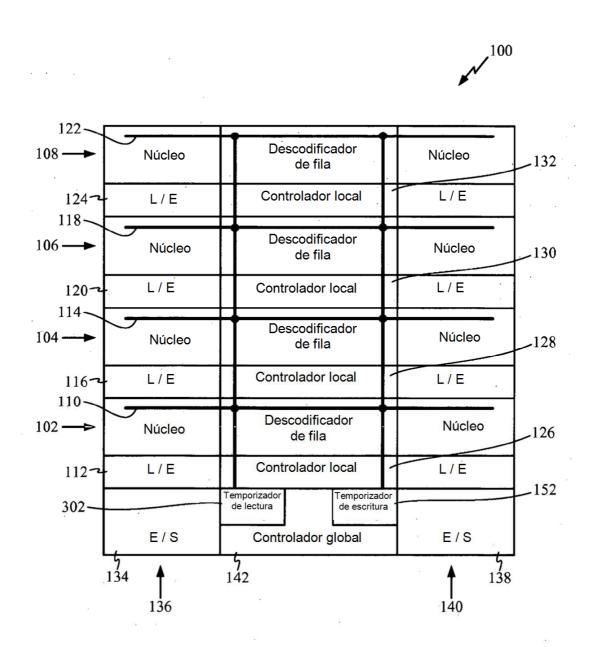

La FIG. 2 es un diagrama esquemático de circuitos que ilustra una memoria de acuerdo a una segunda realización.

La FIG. 3 es una representación esquemática de dos instrucciones a procesar por parte de la memoria de la FIG. 1 o la FIG. 2.

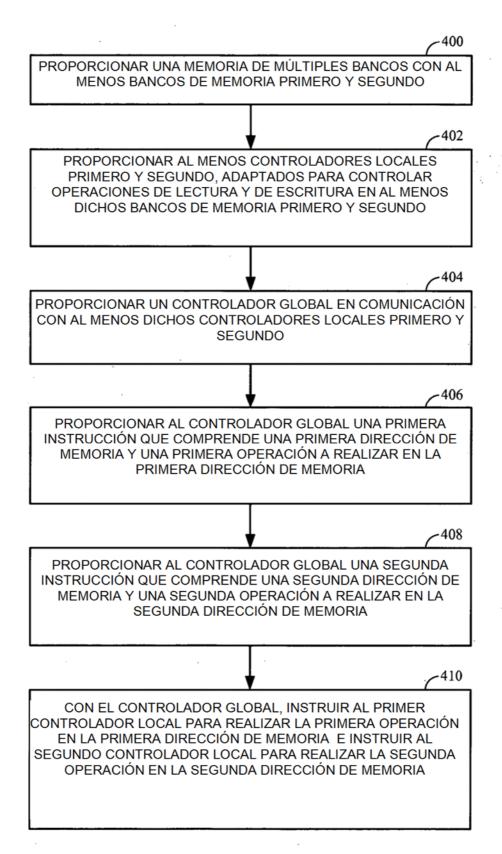

La FIG. 4 es un gráfico de fluio que ilustra un procedimiento de acuerdo a una realización.

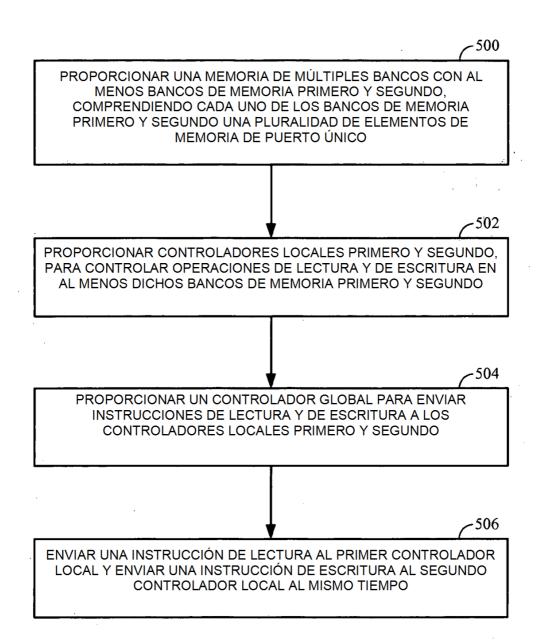

La FIG. 5 es un gráfico de flujo que ilustra un procedimiento de acuerdo a otra realización.

## Descripción detallada

Los aspectos de la invención están divulgados en la siguiente descripción y los dibujos relacionados, orientados a realizaciones específicas de la invención. Pueden ser ideadas realizaciones alternativas sin apartarse del ámbito de la invención. Adicionalmente, elementos bien conocidos de la invención no serán descritos en detalle o serán omitidos a fin de no oscurecer los detalles relevantes de la invención.

La palabra "ejemplar" se usa en la presente memoria para significar "que sirve como un ejemplo, caso o ilustración". Cualquier realización descrita en la presente memoria como "ejemplar" no ha de ser necesariamente interpretada como preferida o ventajosa con respecto a otras realizaciones. Análogamente, el término "realizaciones de la invención" no requiere que todas las realizaciones de la invención incluyan la característica, ventaja o modalidad de funcionamiento

## expuesta.

10

15

20

La terminología usada en la presente memoria es con el fin de describir realizaciones específicas solamente y no está concebida para ser limitadora de las realizaciones de la invención. Según se usan en la presente memoria, las formas singulares "un", "uno" y "el" están concebidas para incluir asimismo las formas plurales, a menos que el contexto indique claramente lo contrario. Se entenderá además que los términos "comprende", "comprendiendo", "incluye" y / o "incluyendo", cuando se usan en la presente memoria, especifican la presencia de las características, etapas, operaciones, elementos y / o componentes indicados, pero no impiden la presencia o el agregado de uno o más de otras características, otros enteros, otras etapas, otras operaciones, otros elementos, otros componentes y / o de grupos de los mismos.

Además, muchas realizaciones están descritas en términos de secuencias de acciones a realizar, por ejemplo, por parte de elementos de un dispositivo informático. Se reconocerá que diversas acciones descritas en la presente memoria pueden ser realizadas por circuitos específicos (p. ej., circuitos integrados específicos de la aplicación (ASIC)), por instrucciones de programa ejecutadas por uno o más procesadores, o por una combinación de ambos. Adicionalmente, estas secuencias de acciones descritas en la presente memoria pueden ser consideradas como realizadas enteramente dentro de cualquier forma de medio de almacenamiento legible por ordenador, que tenga almacenado en el mismo un correspondiente conjunto de instrucciones de ordenador que, al ejecutarse, provocarían que un procesador asociado realizara la funcionalidad descrita en la presente memoria. Por tanto, los diversos aspectos de la invención pueden ser realizados en un cierto número de formas distintas, todas las cuales han sido contempladas para que estén dentro del ámbito del asunto en cuestión reivindicado. Además, para cada una de las realizaciones descritas en la presente memoria, la forma correspondiente de realizaciones cualesquiera de ese tipo puede ser descrita en la presente memoria, por ejemplo, como "lógica configurada para" realizar la acción descrita.

25 La Figura 1 ilustra una memoria de múltiples bancos 100 de acuerdo a una primera realización que incluye un primer banco de memoria 102, un segundo banco de memoria 104, un tercer banco de memoria 106 y un cuarto banco de memoria 108, entendiéndose que las realizaciones con más o menos bancos de memoria también están dentro del ámbito de esta divulgación. Cada uno de los bancos de memoria primero a cuarto 102, 104, 106, 108 incluye una línea de palabras y los circuitos asociados de lectura / escritura que permiten que las operaciones de lectura y escritura sean 30 realizadas en ese banco de memoria. Los circuitos de lectura / escritura incluyen, por ejemplo, un amplificador de detección (no ilustrado) y un controlador de escritura (no ilustrado). Específicamente, el primer banco de memoria 102 incluye una línea de palabras 110 y circuitos de lectura / escritura 112, el segundo banco de memoria 104 incluye una línea de palabras 114 y circuitos de lectura / escritura 116, el tercer banco de memoria 106 incluye una línea de palabras 118 y circuitos de lectura / escritura 120 y el cuarto banco de memoria 108 incluye una línea de palabras 122 y circuitos 35 de lectura / escritura 124. Un controlador local también está asociado a cada uno de los bancos de memoria primero a cuarto 102, 104, 106, 108. Específicamente, el primer banco de memoria 102 incluye un primer controlador local 126, el segundo banco de memoria 104 incluye un segundo controlador local 128, el tercer banco de memoria 106 incluye un tercer controlador local 130 y el cuarto banco de memoria 108 incluye un cuarto controlador local 132. Los primeros circuitos de Entrada / Salida 134 están asociados a los elementos de memoria en una primera columna de memoria 136 40 y los segundos circuitos de Entrada / Salida 138 están asociados a los elementos de memoria en una segunda columna de memoria 140 y los circuitos de Entrada / Salida primero y segundo 134, 138, permiten que los datos sean escritos en y leídos de, los elementos de memoria en la primera columna de memoria 136 y la segunda columna de memoria 140, respectivamente.

45 Un controlador global 142 está configurado para recibir pares de instrucciones, incluyendo cada instrucción una indicación de una operación a realizar y una identificación de una dirección de memoria en la que ha de realizarse la instrucción. La indicación, por ejemplo, puede comprender una parte de la dirección de memoria recibida y / o ser transmitida simultáneamente con la dirección de memoria. La Figura 2 ilustra las instrucciones representativas primera y segunda 144, 146, cada una de las cuales incluye una primera parte 148 que identifica una operación a realizar y una 50 segunda parte 150 que identifica una dirección de memoria en la que la operación ha de ser realizada. La primera parte 148 de la primera instrucción 144 incluye una "e" de "escritura" y la segunda parte 150 de la primera instrucción 144 incluye una dirección de memoria a ser escrita. En este ejemplo, el "1" en la dirección indica que el elemento de memoria al que se accede está en el primer banco de memoria 102 y el "5" identifica el elemento de memoria. La primera parte 148 de la segunda instrucción 146 incluye una "l" de "lectura" y la segunda parte 150 de la segunda instrucción 146 incluye una dirección de memoria a leer. Én este ejemplo, el "2" en la dirección indica que el elemento de memoria al que 55 se accede está en el segundo banco de memoria 104 y que se ha de acceder a una ubicación "8". Si bien "l" y "e" se usan para indicar "lectura" y "escritura", respectivamente, la parte identificativa de la instrucción será probablemente un valor numérico que pueda ser interpretado por el controlador global 142 como una instrucción bien de lectura o bien de escritura. Análogamente, las direcciones de memoria en las segundas partes 150 de las instrucciones primera y segunda 144, 146 serán proporcionadas de manera que puedan ser inmediatamente procesadas por el controlador global. 60

La memoria de múltiples bancos 100 incluye trayectos separados de lectura y de escritura y por tanto puede realizar operaciones de lectura y escritura al mismo tiempo, mientras las operaciones estén siendo realizadas en bancos distintos de los bancos de memoria primero a cuarto 102, 104, 106, 108. El controlador global 142 está configurado para enviar dos instrucciones a dos controladores distintos entre los controladores locales primero a cuarto 126, 128, 130, 132 al mismo tiempo y siempre que una operación sea una operación de lectura y la otra sea una operación de escritura, las

## ES 2 575 095 T3

operaciones pueden ejecutarse simultáneamente sin ninguna interferencia en los trayectos de datos de salida. Los elementos de memoria de puerto dual y de múltiples puertos permiten el acceso simultáneo a un elemento de memoria dado pero son más complejos y ocupan más espacio. En casos donde no se requiere el acceso simultáneo al mismo elemento de memoria, muchas de las ventajas de la memoria de puerto dual y de múltiples puertos pueden ser obtenidas usando elementos de memoria de puerto único y la presente divulgación. Según se usan en la presente memoria, "simultáneamente", "concurrentemente" y "al mismo tiempo" significan que operaciones de lectura y de escritura están teniendo lugar al mismo tiempo. Estas operaciones, sin embargo, pueden, pero no necesariamente deben, comenzar o acabar en precisamente el mismo instante. En efecto, según la memoria, se requieren generalmente distintos lapsos de tiempo para que ocurran las operaciones de lectura y de escritura e incluso si comienzan aproximadamente al mismo tiempo, una de estas operaciones terminará generalmente antes que la otra.

Es deseable que el sistema que accede a la memoria de múltiples bancos 100 sea configurado para evitar enviar solicitudes conflictivas de acceso a memoria a la memoria de múltiples bancos 100. Es decir, el sistema debería garantizar que los pares de solicitudes de acceso de lectura y de escritura que son enviados a la memoria de múltiples bancos 100 estén siempre dirigidos a bancos distintos de los bancos de memoria primero a cuarto 102, 104, 106, 108. La memoria de múltiples bancos 100 puede ser configurada, sin embargo, para gestionar situaciones en que dos instrucciones recibidas son bien dos instrucciones de lectura o bien dos instrucciones de escritura o instrucciones para leer y / o escribir en el mismo banco de memoria. En tal caso, el controlador global 142 puede ser configurado para dar prioridad a una de las instrucciones sobre la otra o para ignorar ambas instrucciones y evitar así el conflicto.

20

25

30

10

15

Como se ha indicado anteriormente, las instrucciones de lectura y de escritura para un dispositivo de memoria dado requieren habitualmente distintos lapsos para ser ejecutadas. Para los fines de la exposición, se supone que realizar una operación de escritura en la memoria de múltiples bancos 100 requiere más tiempo que realizar una operación de lectura. Sin embargo, para otras memorias, un acceso de lectura puede tomar más tiempo que un acceso de escritura. Para ayudar a asegurar que el controlador global 142 no comience otra operación de lectura o de escritura antes de que se acabe una operación actual, el controlador global 142 incluye un temporizador de escritura 152. El temporizador de escritura 152 controla el intervalo en el que el controlador global 142 envía instrucciones a los controladores locales primero a cuarto 126, 128, 130, 132 y no permite que las instrucciones de lectura o de escritura sean enviadas hasta que el temporizador de escritura 152 se haya agotado indicando que ha pasado un tiempo predeterminado. Debido a que en esta realización se supone que las operaciones de escritura requieren más tiempo que las operaciones de lectura, las operaciones de lectura habrán acabado necesariamente en el momento en que se agote el temporizador de escritura 152. La memoria de múltiples bancos 100 es por tanto un elemento de memoria auto-temporizado que no es dependiente de un reloj del sistema para determinar la temporización del acceso a memoria.

En funcionamiento, la primera instrucción 144 y la segunda instrucción 146 son recibidas en el controlador global 142. La primera instrucción 144 incluye una "l" y una dirección en el primer banco de memoria 102. La segunda instrucción incluye una "e" y una dirección en el segundo banco de memoria 104. El controlador global 142 envía así una instrucción al primer controlador local 126 en el primer banco de memoria 102 para realizar una operación de lectura en la ubicación de memoria indicada y de manera esencialmente simultánea, envía una instrucción de escritura al segundo controlador local 128 del segundo banco de memoria 104 para realizar una operación de escritura en la ubicación indicada. La lectura y escritura efectiva de los datos es realizada de manera convencional, aunque, a diferencia de las memorias convencionales, es realizada al mismo o esencialmente al mismo tiempo en los dos bancos de memoria distintos. Cuando se agota el temporizador de escritura 152, un segundo par de direcciones de memoria es recibido por el

45

50

controlador global 142 y el proceso continúa.

Una segunda realización está ilustrada en la Figura 3, en la que los elementos comunes con la primera realización están identificados con iguales números de referencia. En la Figura 3, el controlador global 142 incluye un temporizador de lectura 302 además del temporizador de escritura 152 de la primera realización. El temporizador de lectura 302 permite a la memoria 100 determinar independientemente cuándo se completan las operaciones de lectura y de escritura y emprender por tanto las acciones adecuadas en base a los tiempos efectivos de terminación. Por ejemplo, si se determina usando el temporizador 302 que ha terminado una operación de lectura, puede ser posible comenzar la precarga adecuada de una línea de bits de lectura sin esperar a que se complete la operación de escritura.

La memoria 100 proporciona por tanto la ventaja de permitir operaciones simultáneas de lectura y de escritura en distintos bancos de memoria de una memoria de múltiples bancos, que está formada por elementos de memoria de puerto único. Esto brinda muchas de las ventajas de la memoria de puerto dual o múltiples puertos y permite las operaciones simultáneas de lectura y de escritura mientras se impidan las operaciones simultáneas en el mismo banco de memoria.

60 Las memorias de acuerdo a las realizaciones divulgadas pueden estar formadas o integradas en uno o más troqueles semiconductores y / o en diversos dispositivos, incluyendo, sin limitación, un equipo de sobremesa, un reproductor de música, un reproductor de vídeo, una unidad de entretenimiento, un dispositivo de navegación, un dispositivo de comunicaciones, un asistente digital personal (PDA), una unidad de datos de ubicación fija y un ordenador.

Un procedimiento de acuerdo con una realización se ilustra en la Figura 4 e incluye un bloque 400 de provisión de una memoria de múltiples bancos que tiene al menos bancos de memoria primero y segundo, un bloque 402 de provisión de

# ES 2 575 095 T3

al menos controladores locales primero y segundo adaptados para controlar operaciones de lectura y de escritura en al menos dichos bancos de memoria primero y segundo, un bloque 404 de provisión de un controlador global en comunicación con al menos dichos controladores locales primero y segundo, un bloque 406 de provisión al controlador global de una primera instrucción que comprende una primera dirección de memoria y una primera operación a realizar en la primera dirección de memoria, un bloque 408 de provisión al controlador global de una segunda instrucción que comprende una segunda dirección de memoria y una segunda operación a realizar en la segunda dirección de memoria y un bloque 410 del controlador global que instruye al primer controlador local para realizar la primera operación en la primera dirección de memoria y que instruye al segundo controlador local para realizar la segunda operación en la segunda dirección de memoria.

10

15

Otro procedimiento de acuerdo a una realización adicional está ilustrado en la Figura 5 e incluye un bloque 500 de provisión de una memoria de múltiples bancos que tiene al menos bancos de memoria primero y segundo, comprendiendo cada uno de los bancos de memoria primero y segundo una pluralidad de elementos de memoria de puerto único, un bloque 502 de provisión de controladores locales primero y segundo para controlar operaciones de lectura y de escritura en al menos dichos bancos de memoria primero y segundo, un bloque 504 de provisión de un controlador global para enviar instrucciones de lectura y de escritura a los controladores locales primero y segundo y un bloque 506 de envío de una instrucción de lectura al primer controlador local y de envío de una instrucción de escritura al segundo controlador local al mismo tiempo.

20

Los expertos en la técnica apreciarán que la información y las señales pueden ser representadas usando cualquiera entre una amplia variedad de distintas tecnologías y técnicas. Por ejemplo, los datos, las instrucciones, los comandos, la información, las señales, los bits, los símbolos y los chips que puedan ser mencionados en toda la extensión de la descripción anterior pueden ser representados por voltajes, corrientes, ondas electromagnéticas, campos o partículas magnéticos, campos o partículas ópticos, o cualquier combinación de los mismos.

25

30

Además, los expertos en la técnica apreciarán que los diversos bloques lógicos ilustrativos, módulos, circuitos y etapas de algoritmo descritos con relación a las realizaciones divulgadas en la presente memoria pueden ser implementados como hardware electrónico, software de ordenador o combinaciones de ambos. Para ilustrar claramente esta intercambiabilidad del hardware y del software, diversos componentes ilustrativos, bloques, módulos, circuitos y etapas han sido descritos en lo que antecede en general en términos de su funcionalidad. Si tal funcionalidad es implementada como hardware o software depende de la aplicación específica y de las restricciones de diseño impuestas sobre el sistema global. Los artesanos expertos pueden implementar la funcionalidad descrita de manera variable para cada aplicación específica, pero tales decisiones de implementación no deberían ser interpretadas como causantes de un alejamiento del ámbito de la presente invención.

35

40

Los procedimientos, secuencias y / o algoritmos descritos con relación a las realizaciones divulgadas en la presente memoria pueden ser realizados directamente en hardware, en un módulo de software ejecutado por un procesador o en una combinación de los dos. Un módulo de software puede residir en memoria RAM, memoria flash, memoria ROM, memoria EPROM, registros, un disco rígido, un disco extraíble, un CD-ROM o cualquier otra forma de medio de almacenamiento conocido en la técnica. Un medio de almacenamiento ejemplar está acoplado con el procesador de modo que el procesador pueda leer información de y escribir información en, el medio de almacenamiento. Como alternativa, el medio de almacenamiento puede estar integrado en el procesador.

45

Si bien la divulgación precedente muestra realizaciones ilustrativas de la invención, debería observarse que diversos cambios y modificaciones podrían ser hechos en la presente memoria sin apartarse del ámbito de la invención según lo definido por las reivindicaciones adjuntas. Las funciones, etapas y / o acciones de las reivindicaciones de procedimiento de acuerdo con las realizaciones de la invención descrita en la presente memoria no necesariamente deben ser realizadas en ningún orden específico. Además, aunque los elementos de la invención pueden ser descritos o reivindicados en singular, está contemplado el plural a menos que se indique explícitamente la limitación al singular.

50

## REIVINDICACIONES

1. Un procedimiento, que comprende:

10

15

45

- proporcionar una memoria de múltiples bancos, con al menos bancos de memoria primero y segundo;

- 5 proporcionar al menos controladores locales primero y segundo adaptados para controlar operaciones de lectura y de escritura en al menos dichos bancos de memoria primero y segundo;

- proporcionar un controlador global en comunicación con al menos dichos controladores locales primero y segundo;

- proporcionar al controlador global una primera instrucción que comprende una primera dirección de memoria y una primera operación a realizar en la primera dirección de memoria;

- proporcionar al controlador global una segunda instrucción que comprende una segunda dirección de memoria y una segunda operación a realizar en la segunda dirección de memoria;

- instruir, usando el controlador global, al primer controlador local para realizar la primera operación en la primera dirección de memoria e instruir al segundo controlador local para realizar la segunda operación en la segunda dirección de memoria; y

- controlar, usando un temporizador en el controlador global, un intervalo en el que el controlador global envía las instrucciones primera y segunda a los controladores locales primero y segundo.

- 2. El procedimiento de la reivindicación 1, en el que el controlador global instruye al segundo controlador local para realizar la segunda operación en la segunda dirección de memoria antes de que haya acabado la primera operación.

- 3. El procedimiento de la reivindicación 1, en el que el controlador global instruye al primer controlador local para realizar la primera operación en la primera dirección de memoria y al segundo controlador local para realizar la segunda operación en la segunda dirección de memoria al mismo tiempo.

- 4. El procedimiento de la reivindicación 3, que incluye además proporcionar trayectos separados de lectura y de escritura, para cada uno de al menos dichos bancos de memoria primero y segundo.

- 30 5. El procedimiento de la reivindicación 3, en el que cada uno de dichos bancos de memoria primero y segundo comprende una pluralidad de elementos de memoria de puerto único.

- 6. El procedimiento de la reivindicación 3, en el que la segunda operación es distinta a la primera operación.

- 35 7. El procedimiento de la reivindicación 6, en el que la primera operación comprende una entre una operación de lectura y una operación de escritura y en el que la segunda operación comprende la otra operación entre la operación de lectura y la operación de escritura.

- 8. El procedimiento de la reivindicación 7, que incluye además impedir que el controlador global instruya al primer controlador local para realizar la primera operación si una operación anterior de lectura o una operación anterior de escritura está aún en marcha.

- El procedimiento de la reivindicación 7, que incluye además determinar si ha pasado o no un tiempo predeterminado desde el envío de la primera instrucción al primer controlador local antes de enviar una instrucción posterior al primer controlador local.

- El procedimiento de la reivindicación 1, que incluye además integrar la memoria de múltiples bancos en al menos un troquel semiconductor.

- 11. El procedimiento de la reivindicación 1, que incluye además integrar la memoria de múltiples bancos en un dispositivo seleccionado entre el grupo que consiste en un equipo de sobremesa, un reproductor de música, un reproductor de vídeo, una unidad de entretenimiento, un dispositivo de navegación, un dispositivo de comunicaciones, un asistente digital personal (PDA), una unidad de datos de ubicación fija y un ordenador.

- 55 12. Una memoria, que comprende:

- medios de elementos de memoria;

- medios de controlador local, adaptados para enviar instrucciones de lectura y escritura a los medios de elementos de memoria:

- medios de controlador global en comunicación con los medios de controlador local;

- en la que los medios de controlador global están configurados para recibir direcciones de memoria primera y segunda y una primera indicación de una operación a realizar en una primera dirección de memoria en los medios de elementos de memoria y una segunda indicación de una operación a realizar en una segunda dirección de memoria en los medios de elementos de memoria y para instruir a los medios de controlador local para realizar la primera operación indicada en la primera dirección de memoria y la segunda operación indicada en la segunda dirección de memoria al mismo tiempo: y

- un temporizador en los medios de controlador global, en el que el temporizador está configurado para controlar un

# ES 2 575 095 T3

intervalo en el que los medios de controlador global envían instrucciones a los controladores locales primero y segundo.

- 13. La memoria de la reivindicación 12, en la que los medios de elementos de memoria comprenden primeros medios de banco de memoria y segundos medios de banco de memoria y en el que los medios de controlador local comprenden primeros medios de controlador local y segundos medios de controlador local y en el que la primera dirección de memoria está situada en los primeros medios de banco de memoria y la segunda dirección de memoria está situada en los segundos medios de banco de memoria y en el que la primera operación indicada es distinta a la segunda operación indicada.

- 14. La memoria de la reivindicación 13, en la que la primera operación indicada comprende una operación de lectura y la segunda operación indicada comprende una operación de escritura y en la que los primeros medios de controlador local ejecuta la operación de lectura mientras que los segundos medios de controlador local ejecuta la operación de escritura.

15

148 150 144 E, 1, 5 146 L, 2, 8 FIG. 2

FIG. 3

FIG. 4

FIG. 5