# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 597 079

51 Int. CI.:

H04B 1/40 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

86) Fecha de presentación y número de la solicitud internacional: 31.10.2012 PCT/CN2012/083855

(87) Fecha y número de publicación internacional: 08.05.2014 WO14067100

(96) Fecha de presentación y número de la solicitud europea: 31.10.2012 E 12887608 (3)

(97) Fecha y número de publicación de la concesión europea: 27.07.2016 EP 2906000

(54) Título: Transmisor, receptor y método de recepción/transmisión de radiofrecuencia

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 13.01.2017

(73) Titular/es:

HUAWEI TECHNOLOGIES CO., LTD. (100.0%) Huawei Administration Building, Bantian, Longgang District Shenzhen, Guangdong 518129, CN

(72) Inventor/es:

LUO, XUN y MA, JUN

(74) Agente/Representante:

LEHMANN NOVO, María Isabel

#### **DESCRIPCIÓN**

Transmisor, receptor y método de recepción/transmisión de radiofrecuencia.

#### Campo técnico

La presente invención se refiere al campo de las tecnologías de comunicaciones por radio y, en particular, a un transmisor, un receptor, y un método para recibir y transmitir una señal de radiofrecuencia.

#### Antecedentes

5

10

35

40

45

En un sistema de comunicaciones existente, un chip de banda base y un circuito de radiofrecuencia deben trabajar, normalmente, en colaboración, donde el circuito de radiofrecuencia es, en general, responsable de transmitir o recibir una señal de radiofrecuencia, y el chip de banda base es, en general, responsable de llevar a cabo un procesamiento en la señal de radiofrecuencia; por ejemplo, en un transmisor, el chip de banda base puede codificar una señal de audio dentro de una señal de radiofrecuencia que se transmitirá y, en un receptor, el chip de banda base puede decodificar una señal de radiofrecuencia recibida dentro de una señal de audio. Además, el chip de banda base tiene también una función de procesamiento de señal, como, por ejemplo, codificar/decodificar información de domicilio, información de texto, e información de imagen.

- El chip de banda base tiene además una función importante que es llevar a cabo, mediante el uso de una serie de algoritmos complejos, el procesamiento como, por ejemplo, la recuperación de la onda portadora o generación de la onda portadora en una señal que atraviesa un circuito de radiofrecuencia, para corregir un error de una señal, asegurando, de esta manera, la exactitud de una señal de radiofrecuencia que trasmite/recibe el circuito de radiofrecuencia. Un ejemplo se describe a continuación:

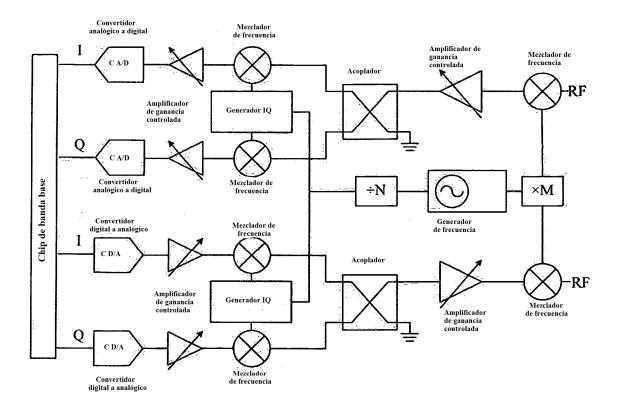

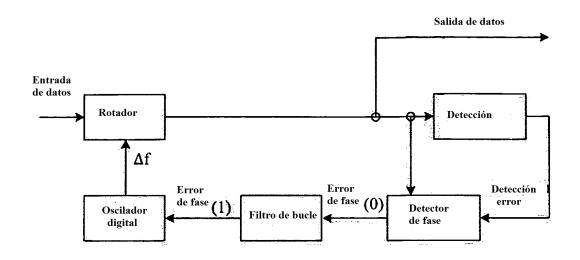

- Según se muestra en la Figura 1a, la cual es una arquitectura de circuito de radiofrecuencia de la técnica anterior, un receptor y un transmisor se integran de forma conjunta y se conectan a un mismo chip de banda base, de modo tal que el chip de banda base lleva a cabo el procesamiento como, por ejemplo, la recuperación de la onda portadora o generación de la onda portadora en una señal que atraviesa el receptor y el transmisor. Por ejemplo, según se muestra en la Figura 1b, la cual es un procedimiento de procesamiento general para llevar a cabo la recuperación de la onda portadora en una señal por parte de un chip de banda base, donde el chip de banda base obtiene un error de fase según un error que obtiene el detector de fase llevando a cabo la detección, y luego de llevar a cabo el procesamiento según los algoritmos correspondientes usando un filtro de bucle y un oscilador digital, emite una señal de fase de error corregido. La solicitud de patente CN101662822 es un ejemplo de un transceptor de comunicaciones por radio equipado con una unidad de procesamiento de señal de banda base.

#### 30 Problemas de la técnica anterior:

Con el fin de mejorar la eficiencia de funcionamiento de un receptor/transmisor, se debe mejorar la eficiencia espectral de un circuito de radiofrecuencia; una de las principales maneras de mejorar la eficiencia espectral es mejorar un modo de modulación. Sin embargo, después de haber mejorado el modo de modulación, por ejemplo, 64QAM (Modulación de Amplitud en Cuadratura, Modulación de Amplitud en Cuadratura) mejora a 1024QAM, un chip de banda base también requiere componentes adicionales para asegurar el funcionamiento apropiado de las funciones como, por ejemplo, la recuperación de la onda portadora o generación de la onda portadora. Además, en la técnica anterior, con el fin de asegurar que el chip de banda base funcione correctamente en un modo de alta modulación, la única solución viable es integrar más componentes en el chip de banda base; por ejemplo, el chip de banda base requiere 2<sup>6</sup> circuitos puerta en un escenario 64QAM, y requiere 2<sup>10</sup> circuitos puerta en un escenario 1024AQAM. Además, en un escenario como, por ejemplo, 2048QAM o 4096QAM, el número de circuitos puerta requerido aumenta de manera exponencial, el cual no se puede implementar en la fabricación industrial. Además, con el fin de ejecutar en el modo de alta modulación, los componentes que deben aumentarse en un chip de banda base no son solo los circuitos puerta; otros componentes dentro del chip de banda base también necesitan aumentar de manera exponencial, lo cual causa un coste enorme; además, el consumo de energía del chip de banda base durante la ejecución es también muy alto debido al aumento de los componentes.

Ello hace que el chip de banda base y el circuito de radiofrecuencia requieran un coste muy alto para llevar a cabo la recuperación de la onda portadora o generación de la onda portadora en el modo de alta modulación en la técnica anterior.

#### Compendio

Las realizaciones de la presente invención proveen un transmisor, un receptor, y un método para recibir y transmitir una señal de radiofrecuencia, lo cual permite llevar a cabo la recuperación de la onda portadora o generación de la onda portadora en un extremo frontal de un circuito de radiofrecuencia, de modo tal que un chip de banda base ya no necesita asumir funciones de recuperación de la onda portadora o generación de la onda portadora, reduciendo, de esta manera, el coste de funcionamiento del chip de banda base.

Con el fin de lograr los objetivos anteriores, las realizaciones de la presente invención usan las siguientes soluciones técnicas:

Según un aspecto, una realización de la presente invención provee un receptor, que incluye:

10

15

25

30

45

una antena de recepción, un módulo de conversión de frecuencia de extremo frontal, un discriminador de amplitud, 5 un generador de código de amplitud, y un corrector de matriz de error binario, donde

el módulo de conversión de frecuencia de extremo frontal obtiene una señal de radiofrecuencia desde la antena de recepción; y el módulo de conversión de frecuencia de extremo frontal convierte la señal de radiofrecuencia obtenida en una señal analógica de frecuencia intermedia, y luego envía la señal analógica de frecuencia intermedia al discriminador de amplitud, donde el módulo de conversión de frecuencia de extremo frontal incluye un amplificador de bajo nivel de ruido, un mezclador de frecuencia de conversión descendente, y un amplificador de ganancia controlada;

el discriminador de amplitud se conecta al módulo de conversión de frecuencia de extremo frontal; y el discriminador de amplitud genera una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal, y luego envía la primera señal por impulso de amplitud de señal al generador de código de amplitud;

el generador de código de amplitud se conecta al discriminador de amplitud; y el generador de código de amplitud convierte la primera señal por impulso de amplitud de señal en un primer código digital de amplitud, y luego envía el primer código digital de amplitud de señal al corrector de matriz de error binario;

el corrector de matriz de error binario se conecta al discriminador de amplitud; y el corrector de matriz de error binario genera una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y luego envía la señal de control de corrección de amplitud al discriminador de amplitud;

el discriminador de amplitud corrige la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal; y

el generador de código de amplitud convierte la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, de modo tal que el receptor usa el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora. Además, el receptor incluye un detector de fase y un generador de código de fase, donde

el detector de fase se conecta al módulo de conversión de frecuencia de extremo frontal; y el detector de fase genera una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal, y luego envía la primera señal por impulso de fase de señal al generador de código de fase;

el generador de código de fase se conecta al detector de fase; y el generador de código de fase convierte la primera señal por impulso de fase de señal en el primer código digital de fase de señal, y luego envía el primer código digital de fase de señal al corrector de matriz de error binario:

el corrector de matriz de error binario se conecta al detector de fase; y el corrector de matriz de error binario genera una señal de control de corrección de fase según el primer código digital de fase de señal, y luego envía la señal de control de corrección de fase al detector de fase;

el detector de fase corrige la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal; y

40 el generador de código de fase convierte la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal, de modo tal que el receptor usa el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

Según otro aspecto, una realización de la presente invención provee un transmisor, que incluye:

un mezclador de frecuencia de conversión descendente, un discriminador de amplitud, un generador de código de amplitud, un corrector de matriz de error binario, y un generador de frecuencia de oscilador local, donde

el mezclador de frecuencia de conversión descendente se conecta al generador de frecuencia de oscilador local, y convierte una señal de radiofrecuencia a enviarse que se obtiene del generador de frecuencia de oscilador local en una señal analógica de frecuencia intermedia, y luego envía la señal analógica de frecuencia intermedia al discriminador de amplitud;

el discriminador de amplitud se conecta al mezclador de frecuencia de conversión descendente, y el discriminador de amplitud genera una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia enviada por el mezclador de frecuencia de conversión descendente, y luego envía la primera señal por impulso de amplitud de señal al generador de código de amplitud;

- el generador de código de amplitud se conecta al discriminador de amplitud; y el generador de código de amplitud convierte la primera señal por impulso de amplitud de señal en un primer código digital de amplitud de señal, y luego envía el primer código digital de amplitud de señal al corrector de matriz de error binario;

- el corrector de matriz de error binario se conecta al discriminador de amplitud; y el corrector de matriz de error binario genera una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y luego envía la señal de control de corrección de amplitud al discriminador de amplitud;

- el discriminador de amplitud corrige la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal; y

- el generador de código de amplitud convierte la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, de modo tal que el receptor usa el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora.

- Además, el transmisor también incluye un detector de fase y un generador de código de fase, donde

- el detector de fase se conecta al mezclador de frecuencia de conversión descendente; y el detector de fase genera una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia enviada por el mezclador de frecuencia de conversión descendente, y luego envía la primera señal por impulso de fase de señal al generador de código de fase;

- el generador de código de fase se conecta al detector de fase; y el generador de código de fase convierte la primera señal por impulso de fase de señal en el primer código digital de fase de señal, y luego envía el primer código digital de fase de señal al corrector de matriz de error binario;

- el corrector de matriz de error binario se conecta al detector de fase; y el corrector de matriz de error binario genera una señal de control de corrección de fase según el primer código digital de fase de señal, y luego envía la señal de control de corrección de fase al detector de fase;

- el detector de fase corrige la primera señal por impulso de fase de señal según la señal de control de corrección de fase para generar una segunda señal por impulso de fase de señal; y

- 30 el generador de código de fase convierte la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal, de modo tal que el receptor usa el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

- Según otro aspecto, una realización de la presente invención provee un método para recibir una señal de radiofrecuencia, que incluye:

- recibir, mediante un receptor, una señal de radiofrecuencia, y convertir una señal de radiofrecuencia obtenida en una señal analógica de frecuencia intermedia;

- generar una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia;

- convertir la primera señal por impulso de amplitud de señal en un primer código digital de amplitud de señal;

- generar una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y corregir la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal; y

- convertir la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, y usar el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora.

- 45 Además, el método también incluye:

10

15

- generar una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia;

- convertir la primera señal por impulso de fase de señal en un primer código digital de fase de señal;

generar una señal de control de corrección de fase según el primer código digital de fase de señal, y corregir la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal; y

convertir la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal, y usar el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la portadora o generación de la portadora.

Según otro aspecto, una realización de la presente invención provee un método para transmitir una señal de radiofrecuencia, que incluye:

convertir, mediante un transmisor, una señal de radiofrecuencia a enviarse en una señal analógica de frecuencia intermedia;

generar una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia;

convertir la primera señal por impulso de amplitud de señal en un primer código digital de amplitud de señal;

generar una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y corregir la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal; y

convertir la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, de modo tal que el transmisor usa el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la portadora o generación de la onda portadora.

Además, el método también incluye:

5

10

15

30

35

45

20 generar una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia;

convertir la primera señal por impulso de fase de señal en un primer código digital de fase de señal;

generar una señal de control de corrección de fase según el primer código digital de fase de señal, y corregir la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal; y

convertir la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal, de modo tal que el transmisor usa el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

En el transmisor, el receptor, y el método para recibir y transmitir una señal de radiofrecuencia provista por las realizaciones de la presente invención, una función de recuperación de la onda portadora o generación de la onda portadora se puede implementar en una porción del circuito de radiofrecuencia del receptor; en comparación con la técnica anterior, un chip de banda base ya no necesita llevar a cabo la recuperación de la onda portadora o generación de la onda portadora, en especial, no necesita asumir funciones como, por ejemplo, la supresión de la desviación de frecuencia y la supresión de ruido de fase relacionadas con la recuperación de la onda portadora y con el consumo de recursos informáticos, simplificando, de esta manera, las funciones del chip de banda base, reduciendo el consumo de energía del chip de banda base; además, dado que el chip de banda base ya no necesita asumir funciones que requieren la ejecución de procedimientos informáticos complejos, como, por ejemplo, la recuperación de la onda portadora o generación de la onda portadora, la complejidad de la técnica y la dificultad del diseño para fabricar el chip de banda base se reducen, lo cual reduce directamente el coste de fabricación del chip de banda base.

40 Breve descripción de las figuras

Con el fin de describir las soluciones técnicas en las realizaciones de la presente invención de forma más clara, a continuación se introducen brevemente los dibujos que la acompañan y que se requieren para describir las realizaciones. De manera aparente, los dibujos que se acompañan en la siguiente descripción muestran simplemente algunas realizaciones de la presente invención, y una persona con experiencia normal en la técnica podrá derivar otros dibujos a partir de dichos dibujos que la acompañan sin esfuerzos creativos.

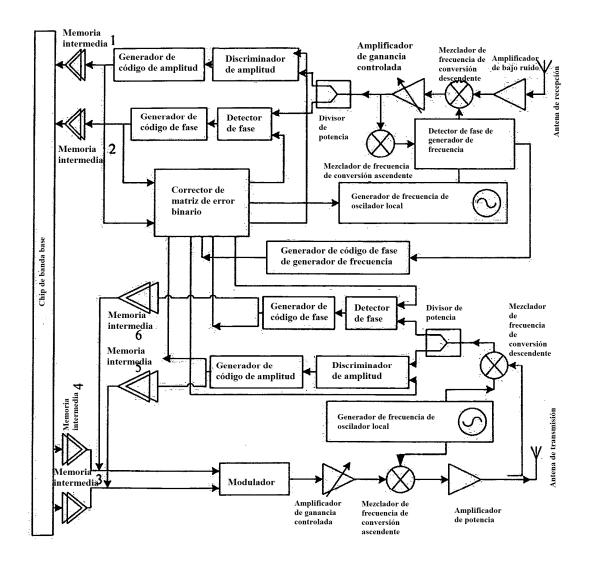

La Figura 1a es un diagrama estructural esquemático de un transceptor de la técnica anterior;

La Figura 1b es un diagrama esquemático de un flujo de trabajo de un chip de banda base de la técnica anterior;

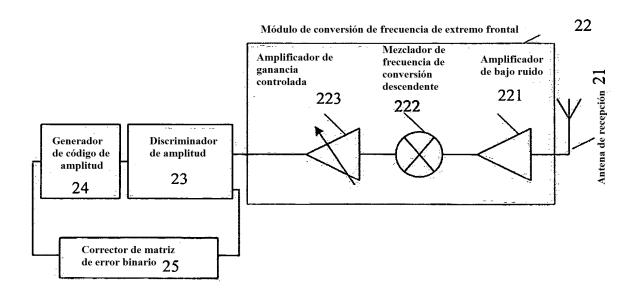

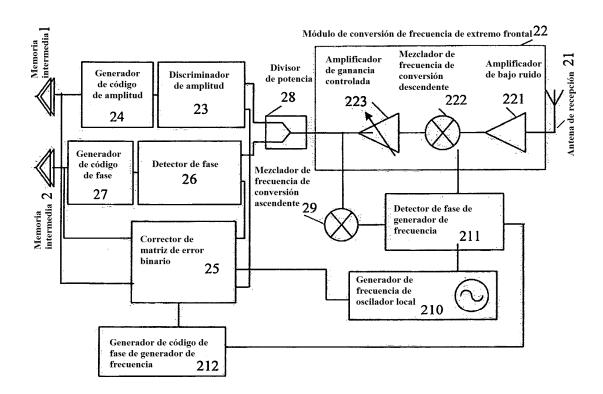

La Figura 2a es un diagrama estructural esquemático de un receptor según la realización 1 de la presente invención;

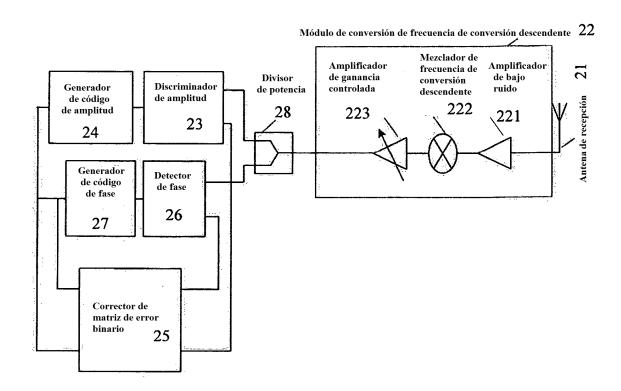

- La Figura 2b es otro diagrama estructural esquemático de un receptor según la realización 1 de la presente invención:

- La Figura 2c es otro diagrama estructural esquemático de un receptor según la realización 1 de la presente invención:

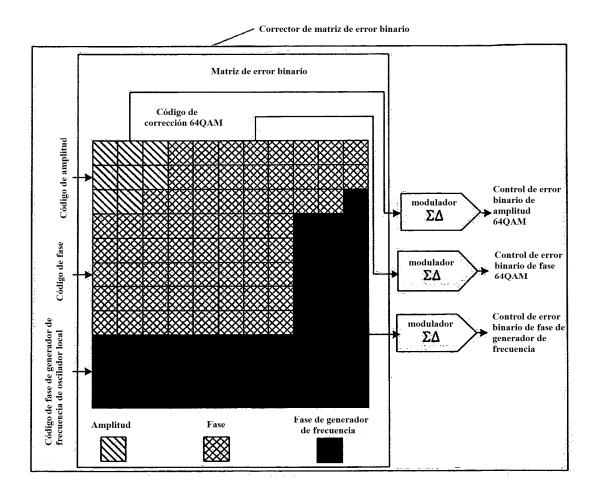

- 5 La Figura 2d es un diagrama esquemático de un ejemplo específico según la realización 1 de la presente invención;

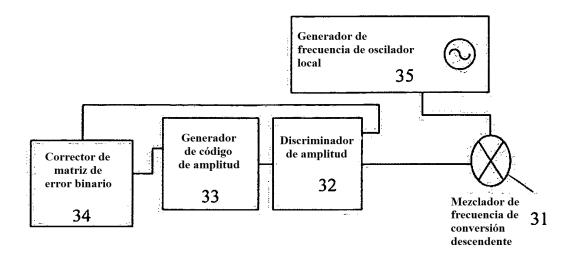

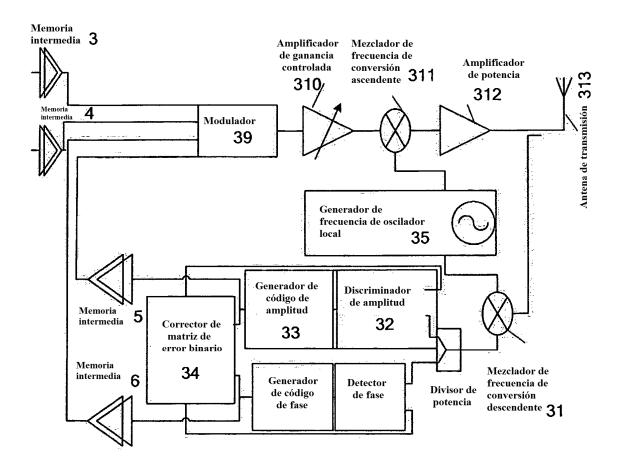

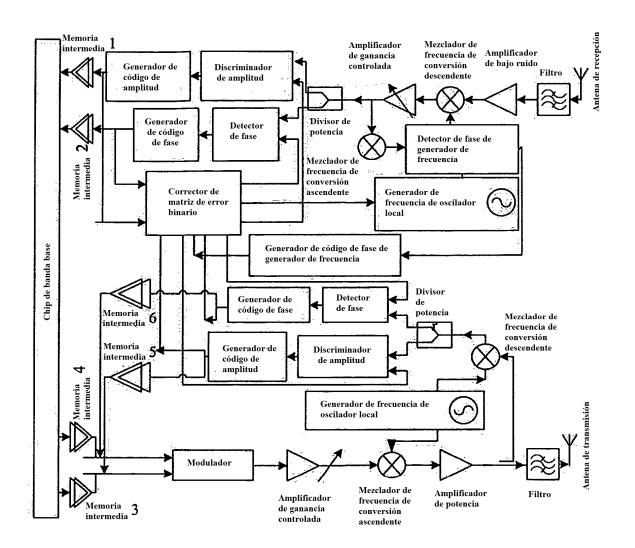

- La Figura 3a es un diagrama estructural esquemático de un transmisor según la realización 2 de la presente invención:

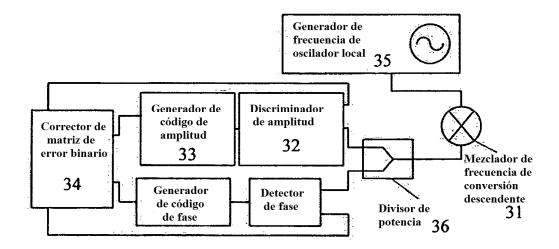

- La Figura 3b es otro diagrama estructural esquemático de un transmisor según la realización 2 de la presente invención;

- 10 La Figura 3c es otro diagrama estructural esquemático de un transmisor según la realización 2 de la presente invención;

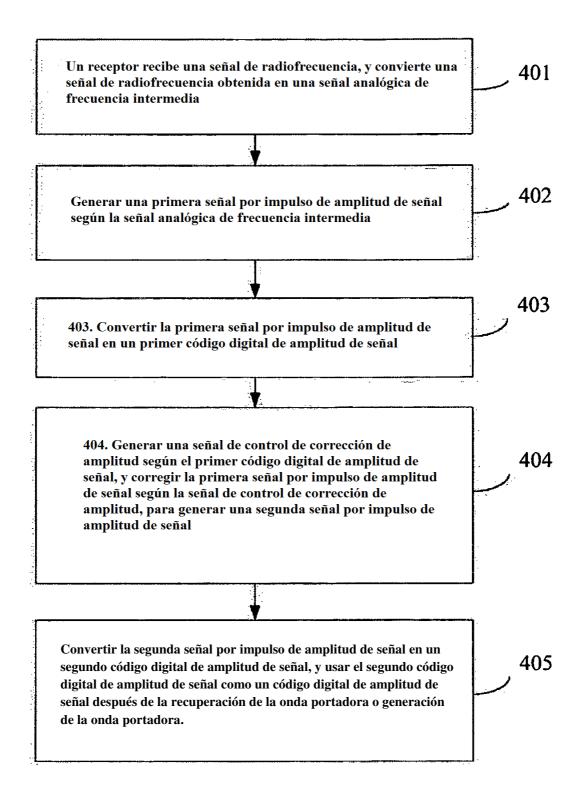

- La Figura 4a es un diagrama de flujo de un método para recibir una señal de radiofrecuencia según la realización 3 de la presente invención;

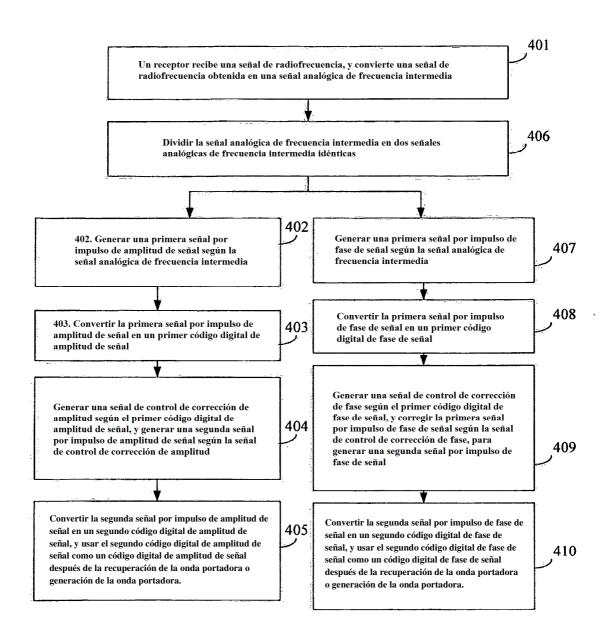

- La Figura 4b es otro diagrama de flujo de un método para recibir una señal de radiofrecuencia según la realización 3 de la presente invención;

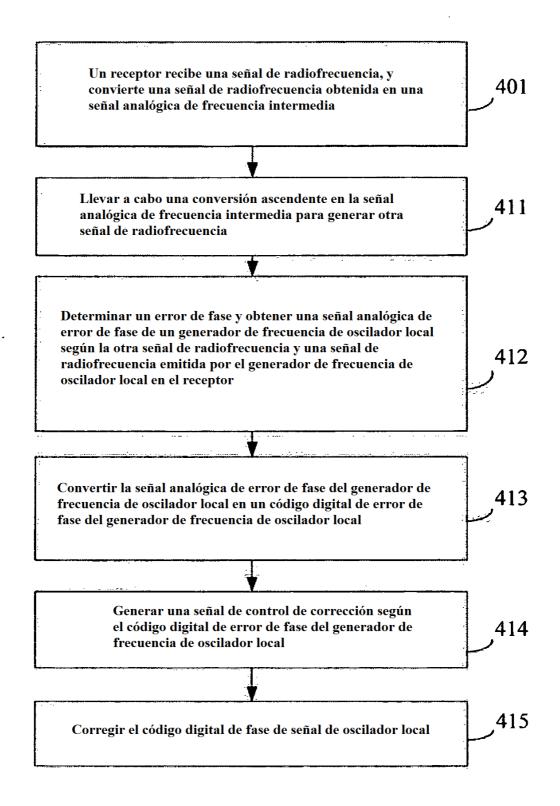

- La Figura 4c es otro diagrama de flujo de un método para recibir una señal de radiofrecuencia según la realización 3 de la presente invención;

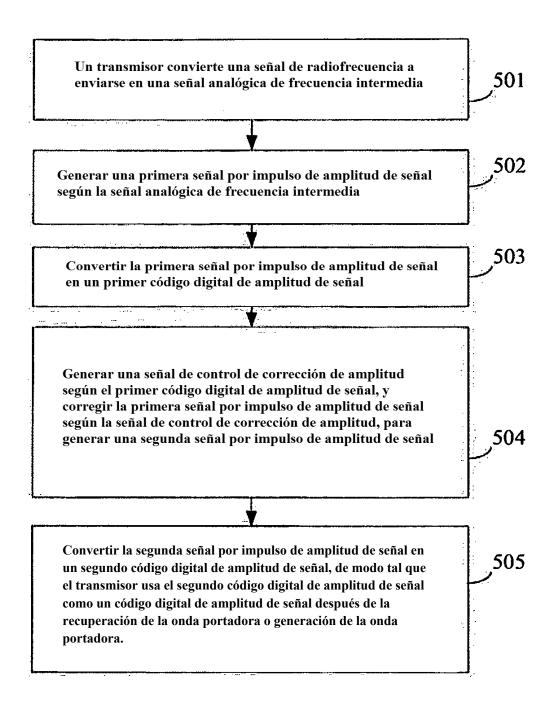

- La Figura 5a es un diagrama de flujo de un método para transmitir una señal de radiofrecuencia según la realización 4 de la presente invención;

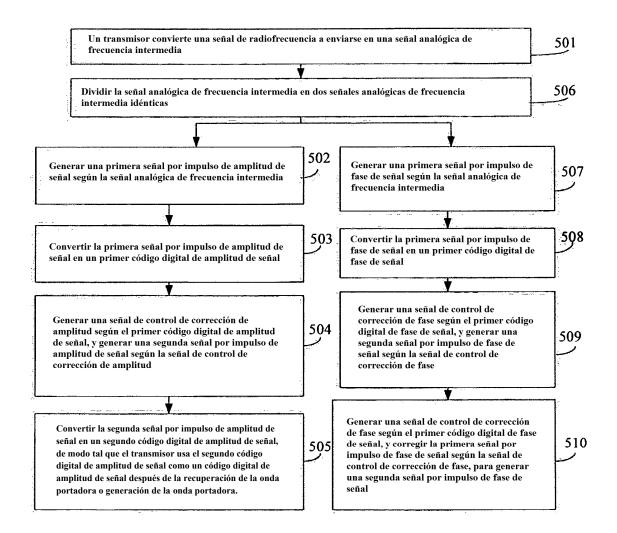

- La Figura 5b es otro diagrama de flujo de un método para transmitir una señal de radiofrecuencia según la realización 4 de la presente invención;

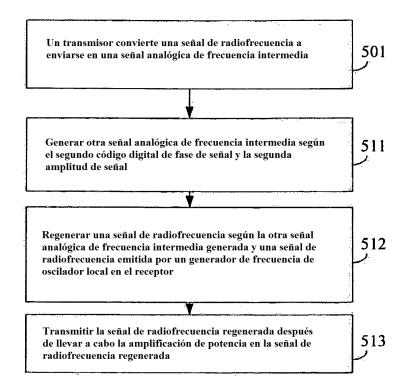

- La Figura 5c es otro diagrama de flujo de un método para transmitir una señal de radiofrecuencia según la realización 4 de la presente invención;

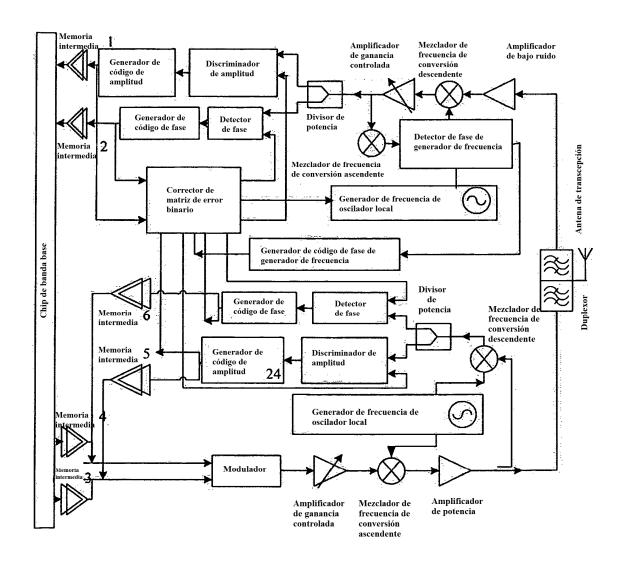

- La Figura 6a es un diagrama estructural esquemático de un sistema para recibir y transmitir una señal de radiofrecuencia según la Realización 5 de la presente invención;

- La Figura 6b es un diagrama estructural esquemático de un ejemplo específico de un circuito de radiofrecuencia según la presente invención;

- La Figura 6c es un diagrama estructural esquemático de un ejemplo específico de otro circuito de radiofrecuencia según la presente invención; y

- La Figura 6d es un diagrama estructural esquemático de un ejemplo específico de otro circuito de radiofrecuencia según la presente invención.

- Descripción de las realizaciones

- A continuación se describen de forma clara y completa las soluciones técnicas en las realizaciones de la presente invención con referencia a los dibujos que la acompañan en las realizaciones de la presente invención.

- De manera aparente, las realizaciones descritas son, meramente, una parte de, y no todas, las realizaciones de la presente invención. Todas las otras realizaciones que una persona con experiencia normal en la técnica obtenga según las realizaciones de la presente invención sin esfuerzos creativos estarán comprendidas dentro del alcance de protección de la presente invención.

- Con el fin de aclarar aún más las ventajas de las soluciones técnicas de la presente invención, a continuación se describe la presente invención en detalle con referencia a los dibujos que la acompañan y a las realizaciones.

# Realización 1

45

Un receptor según la presente realización incluye una antena de recepción, un módulo de conversión de frecuencia de extremo frontal, un discriminador de amplitud, un generador de código de amplitud, un corrector de matriz de error binario, un divisor de potencia, un mezclador de frecuencia de conversión ascendente, un generador de frecuencia de oscilador local, y un generador de código de fase de generador de frecuencia.

El módulo de conversión de frecuencia de extremo frontal se configura para obtener una señal de radiofrecuencia desde la antena de recepción, convertir la señal de radiofrecuencia obtenida en una señal analógica de frecuencia intermedia, y luego enviar la señal analógica de frecuencia intermedia al discriminador de amplitud, donde el módulo de conversión de frecuencia de extremo frontal incluye un amplificador de bajo ruido, un mezclador de frecuencia de conversión descendente, y un amplificador de ganancia controlada.

5

30

El discriminador de amplitud se conecta al módulo de conversión de frecuencia de extremo frontal, y se configura para generar una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal, y luego enviar la primera señal por impulso de amplitud de señal al generador de código de amplitud.

- El generador de código de amplitud se conecta al discriminador de amplitud, y se configura para convertir la primera señal por impulso de amplitud de señal como una señal por impulso en un primer código digital de amplitud de señal como una señal digital, y luego enviar el primer código digital de amplitud de señal al corrector de matriz de error binario, donde el generador de código de amplitud es un codificador configurado para convertir una señal por impulso en una señal digital.

- El corrector de matriz de error binario se conecta al discriminador de amplitud y al generador de código de amplitud, y se configura para generar una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y luego enviar la señal de control de corrección de amplitud al discriminador de amplitud.

- El discriminador de amplitud se configura para corregir la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal.

- El generador de código de amplitud se configura además para convertir la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, de modo tal que el receptor usa el segundo código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora. Además, un detector de fase se conecta al módulo de conversión de frecuencia de extremo frontal, y se configura para generar una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal, y luego enviar la primera señal por impulso de fase de señal a un generador de código de fase.

- El generador de código de fase se conecta al detector de fase, y se configura para convertir la primera señal por impulso de fase de señal como una señal por impulso en un primer código digital de fase de señal como una señal digital, y luego enviar el primer código digital de fase de señal al corrector de matriz de error binario, donde el generador de código de fase es un codificador configurado para convertir una señal por impulso en una señal digital.

- El corrector de matriz de error binario se conecta al detector de fase y al generador de código de fase, y se configura para generar una señal de control de corrección de fase según el primer código digital de fase de señal, y luego enviar la señal de control de corrección de fase al detector de fase.

- El detector de fase se configura para corregir la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal.

- El generador de código de fase se configura además para convertir la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal, de modo tal que el receptor usa el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

- El divisor de potencia se conecta al módulo de conversión de frecuencia de extremo frontal, al discriminador de amplitud, y al detector de fase, y se configura para recibir la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal, dividir la señal analógica de frecuencia intermedia en dos señales analógicas de frecuencia intermedia idénticas, y luego enviar las dos señales analógicas de frecuencia intermedia idénticas al discriminador de amplitud y al detector de fase, respectivamente, de modo tal que el discriminador de amplitud genera la primera señal por impulso de amplitud de señal según una de las señales analógicas de frecuencia intermedia enviada por el divisor de potencia, y el detector de fase genera la primera señal por impulso de fase de señal según la otra de las señales analógicas de frecuencia intermedia enviada por el divisor de potencia.

- El mezclador de frecuencia de conversión ascendente se conecta al módulo de conversión de frecuencia de extremo frontal, y se configura para llevar a cabo la conversión ascendente en la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal, para generar otra señal de radiofrecuencia.

- El detector de fase de generador de frecuencia se conecta al generador de frecuencia de oscilador local y al mezclador de frecuencia de conversión ascendente, y se configura para determinar un error de fase y obtener una señal analógica de error de fase del generador de frecuencia de oscilador local según la señal de radiofrecuencia

generada por el mezclador de frecuencia de conversión ascendente y una señal de radiofrecuencia emitida por el generador de frecuencia de oscilador local.

El generador de código de fase de generador de frecuencia se conecta al detector de fase de generador de frecuencia, y se configura para recibir la señal analógica de error de fase del generador de frecuencia de oscilador local, y convertir la señal analógica de error de fase del generador de frecuencia de oscilador local en un código digital de error de fase del generador de frecuencia de oscilador local.

5

15

20

30

40

45

50

El corrector de matriz de error binario se conecta al generador de código de fase de generador de frecuencia, y se configura para recibir el código digital de error de fase del generador de frecuencia de oscilador local, y generar una señal de control de corrección según el código digital de error de fase del generador de frecuencia de oscilador local.

El generador de frecuencia de oscilador local se conecta al corrector de matriz de error binario, y se configura para recibir la señal de control de corrección enviada por el corrector de matriz de error binario, y corregir un código digital de fase de señal de oscilador local según la señal de control de corrección.

El mezclador de frecuencia de conversión ascendente se conecta al amplificador de ganancia controlada en el módulo de conversión de frecuencia de extremo frontal, y el mezclador de frecuencia de conversión descendente en el módulo de conversión de frecuencia de extremo frontal se conecta al detector de fase de generador de frecuencia.

De manera específica, en la presente realización, tal como se muestra en la Figura 2a, un receptor puede incluir una antena de recepción 21, un módulo de conversión de frecuencia de extremo frontal 22, un discriminador de amplitud 23, un generador de código de amplitud 24, y un corrector de matriz de error binario 25. El módulo de conversión de frecuencia de extremo frontal 22 obtiene una señal de radiofrecuencia desde la antena de recepción 21; y el módulo de conversión de frecuencia de extremo frontal 22 convierte la señal de radiofrecuencia obtenida en una señal analógica de frecuencia intermedia, y luego envía la señal analógica de frecuencia intermedia al discriminador de amplitud 23.

El módulo de conversión de frecuencia de extremo frontal 22 incluye un amplificador de bajo ruido 221, un mezclador de frecuencia de conversión descendente 222, y un amplificador de ganancia controlada 223.

El discriminador de amplitud 23 se conecta al módulo de conversión de frecuencia de extremo frontal 22; y el discriminador de amplitud 23 genera una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal 22, y luego envía la primera señal por impulso de amplitud de señal al generador de código de amplitud 24.

El generador de código de amplitud 24 se conecta al discriminador de amplitud 23; y el generador de código de amplitud 24 convierte la primera señal por impulso de amplitud de señal en un primer código digital de amplitud de señal, y luego envía el primer código digital de amplitud de señal al corrector de matriz de error binario 25.

El corrector de matriz de error binario 25 se conecta al discriminador de amplitud 23; el corrector de matriz de error binario 25 genera una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y luego envía la señal de control de corrección de amplitud al discriminador de amplitud 23.

35 El discriminador de amplitud 23 corrige la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal.

El generador de código de amplitud 24 convierte la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, de modo tal que el receptor usa el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora.

En esta realización de la presente invención, el corrector de matriz de error binario puede llevar a cabo la corrección del error binario en un error de un código digital generado en un transmisor/el receptor. El error del código digital en el receptor se genera, principalmente, por razones que incluyen: en un enlace de hardware de un transmisor que lleva a cabo la comunicación de datos con el receptor, se origina una desviación para una cierta probabilidad durante la transmisión de una señal eléctrica, de modo tal que se origina un error en un código digital que genera el receptor según una señal recibida; un error se origina en un proceso de transmisión espacial de comunicaciones por radio; y en un enlace de hardware del receptor, se origina una desviación para una cierta probabilidad durante la transmisión de una señal eléctrica, de modo tal que se origina, principalmente, por razones que incluyen: en un enlace de hardware del transmisor, se origina una desviación para una cierta probabilidad durante la transmisión de una señal eléctrica, de modo tal que se origina una cierta probabilidad durante la transmisión de una señal eléctrica, de modo tal que se origina un error en un código digital en el transmisión de una señal eléctrica, de modo tal que se origina un error en un código digital en el transmisión de una señal eléctrica, de modo tal que se origina un error en un código digital en el transmisión de una señal eléctrica, de modo tal que se origina un error en un código digital en el transmisión de una señal eléctrica, de modo tal que se origina un error en un código digital en el transmisión de una señal eléctrica, de modo tal que se origina un error en un código digital en el transmisión.

Se puede observar que los correctores de matriz de error binario en el receptor y el transmisor pueden ser el mismo. Un ejemplo se describe a continuación:

Una fuente de código estándar, por ejemplo, una fuente de código estándar QAM en un protocolo, que se ha formulado en un protocolo de comunicaciones, como, por ejemplo, una matriz de error binario digital de amplitud de señal estándar, una matriz de error binario digital de fase de generador de frecuencia, se pueden prealmacenar en el corrector de matriz de error binario. Una persona experta puede prealmacenar la fuente de código en el corrector de matriz de error binario, de modo tal que el corrector de matriz de error binario compara los datos estándar con el código digital de amplitud de señal, el código digital de fase de señal, y el código digital de fase de generador de frecuencia que recibe el receptor o que genera el transmisor, y emite un error binario digital de amplitud de señal, un error binario digital de fase de generador de frecuencia.

El error binario digital de amplitud de señal, el error binario digital de fase de señal, y el error binario digital de fase de generador de frecuencia pueden suscitarse de múltiples formas; por ejemplo, los caracteres del segmento A en un código digital de amplitud de señal estándar prealmacenado son 1010, y los caracteres del segmento A en un código digital de amplitud de señal analizados por el receptor según una señal de radiofrecuencia recibida son 1011, por consiguiente, el corrector de matriz de error binario puede obtener un error binario digital de amplitud de señal llevando a cabo una simple suma o resta binaria, es decir, 1011 - 1010 = 1.

Además, puede haber múltiples procesos en los cuales el corrector de matriz de error binario analiza un código digital de amplitud de señal, un código digital de fase de señal, y un código digital de error de fase del generador de frecuencia de oscilador local, y obtiene una señal de control de corrección correspondiente. A continuación se describen soluciones a modo de ejemplo utilizando un ejemplo.

La Figura 2d muestra un proceso en el cual un corrector de matriz de error binario en un circuito de radiofrecuencia de un receptor o un transmisor analiza un código digital de amplitud de señal, un código digital de fase de señal, y un código digital de error de fase del generador de frecuencia de oscilador local en un escenario 64QAM. Los cuadrados marcados con barras oblicuas indican fuentes de código estándar correspondientes al código digital de amplitud de señal, los cuadrados marcados con cuadrículas indican fuentes de código estándar correspondientes al código digital de fase de señal, y los cuadrados totalmente marcados en negro indican fuentes de código estándar correspondientes al código digital de error de fase del generador de frecuencia de oscilador local; dichas fuentes de código estándar pueden ser fuentes de código estándar QAM prealmacenadas en el corrector de matriz de error binario, y dichas fuentes de código estándar QAM se han descrito en protocolos existentes, de modo tal que una persona experta puede aprender dichas fuentes de código estándar QAM a partir de los protocolos directamente.

Cuando el código digital de amplitud de señal en un circuito de radiofrecuencia se transfiere al corrector de matriz de error binario, el corrector de matriz de error binario puede, usando un medio técnico existente, por ejemplo, usando un comparador, comparar el código digital de amplitud de señal en el circuito de radiofrecuencia con un código digital de amplitud de señal en la fuente de código QAM estándar; es decir, el corrector de matriz de error binario puede comparar el código digital de amplitud de señal en el circuito de radiofrecuencia con los datos correspondientes a los cuadrados marcados con barras oblicuas que se muestran en la Figura 2d; obtener una diferencia entre ellos llevando a cabo una simple suma o resta binaria; y luego emitir una señal analógica de control de corrección de amplitud de señal correspondiente según la diferencia obtenida usando un modulador ΣΔ.

Después de la transferencia de la señal analógica de control de corrección de amplitud de señal emitida por el corrector de matriz de error binario al discriminador de amplitud, el discriminador de amplitud puede corregir un código digital de amplitud de señal según la señal analógica de control de corrección de amplitud de señal.

40

45

Además, el proceso de error binario precedente se puede repetir muchas veces, con el fin de asegurar que el código digital de amplitud de señal sea correcto.

De manera similar, el corrector de matriz de error binario puede procesar el código digital de fase de señal y el código digital de error de fase del generador de frecuencia de oscilador local usando el proceso anterior. Es decir, en esta realización de la presente invención, el corrector de matriz de error binario puede corregir un código digital de amplitud de señal, un código digital de fase de señal, y un código digital de error de fase del generador de frecuencia de oscilador local en un receptor, un transmisor, o un transceptor (por ejemplo, el circuito de radiofrecuencia que integra las funciones de recepción y transmisión que se muestran en la Figura 6b, la Figura 6c, o la Figura 6d) usando el proceso anterior.

Se puede observar además que en la presente realización, el anterior proceso de corrección de error binario puede ser aplicable a todos los escenarios de 1024QAM, 2048QAM, 4096QAM, y similares, para implementar la recuperación de la onda portadora o generación de la onda portadora en los escenarios de 1024QAM, 2048QAM, 4096QAM, y similares; y una estructura de un circuito de radiofrecuencia no cambia, y se puede fabricar usando dispositivos de producción industrial existentes.

Además, el receptor según la presente realización puede, tal y como se muestra en la Figura 2b, incluir además un detector de fase 26, un generador de código de fase 27, y un divisor de potencia 28.

El detector de fase 26 se conecta al módulo de conversión de frecuencia de extremo frontal 22, y se configura para generar una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal 22, y luego enviar la primera señal por impulso de fase de señal al generador de código de fase 27.

- El generador de código de fase 27 se conecta al detector de fase 26, y se configura para convertir la primera señal por impulso de fase de señal como una señal por impulso en un primer código digital de fase de señal como una señal digital, y luego enviar el primer código digital de fase de señal al corrector de matriz de error binario 25, donde el generador de código de fase 27 es un codificador configurado para convertir una señal por impulso en una señal digital.

- El corrector de matriz de error binario 25 se conecta al detector de fase 26 y al generador de código de fase 27, y se configura para generar una señal de control de corrección de fase según el primer código digital de fase de señal, y luego enviar la señal de control de corrección de fase al detector de fase 26.

- El detector de fase 26 se configura para corregir la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal.

- El generador de código de fase 27 se configura además para convertir la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal, de modo tal que el receptor usa el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

- El divisor de potencia 28 se conecta al módulo de conversión de frecuencia de extremo frontal 22, al discriminador de amplitud 23, y al detector de fase 26, y se configura para recibir la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal 22, dividir la señal analógica de frecuencia intermedia en dos señales analógicas de frecuencia intermedia idénticas, y luego enviar las dos señales analógicas de frecuencia intermedia idénticas, y luego enviar las dos señales analógicas de frecuencia intermedia emplitud 23 y al detector de fase 26, respectivamente, de modo tal que el discriminador de amplitud 23 genera la primera señal por impulso de amplitud de señal según una de las señales analógicas de frecuencia intermedia enviada por el divisor de potencia 28, y el detector de fase 26 genera la primera señal por impulso de fase de señal según la otra de las señales analógicas de frecuencia intermedia enviada por el divisor de potencia 28.

- De manera específica, en la presente realización, el detector de fase 26 se conecta al módulo de conversión de frecuencia de extremo frontal 22; y el detector de fase 26 genera la primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal 22, y luego envía la primera señal por impulso de fase de señal al generador de código de fase 27.

- El generador de código de fase 27 se conecta al detector de fase 26; y el generador de código de fase 27 convierte la primera señal por impulso de fase de señal en el primer código digital de fase de señal, y luego envía el primer código digital de fase de señal al corrector de matriz de error binario 25.

- El corrector de matriz de error binario 25 se conecta al detector de fase 26; y el corrector de matriz de error binario 25 genera la señal de control de corrección de fase según el primer código digital de fase de señal, y luego envía la señal de control de corrección de fase al detector de fase 26.

- El detector de fase 26 corrige la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal.

- 40 El generador de código de fase 27 convierte la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal, de modo tal que el receptor usa el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

- El divisor de potencia 28 se conecta al módulo de conversión de frecuencia de extremo frontal 22, al discriminador de amplitud 23, y al detector de fase 26; y el divisor de potencia 28 recibe la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal 22, divide la señal analógica de frecuencia intermedia en dos señales analógicas de frecuencia intermedia idénticas, y luego envía las dos señales analógicas de frecuencia intermedia idénticas al discriminador de amplitud 23 y al detector de fase 26, respectivamente, de modo tal que el discriminador de amplitud 23 genera la primera señal por impulso de amplitud de señal según una de las señales analógicas de frecuencia intermedia, y el detector de fase 26 genera la primera señal por impulso de fase de señal según la otra de las señales analógicas de frecuencia intermedia.

- Además, el receptor según la presente realización puede, tal y como se muestra en la Figura 2c, incluir además un mezclador de frecuencia de conversión ascendente 29, un generador de frecuencia de oscilador local 210, un detector de fase de generador de frecuencia 211, y un generador de código de fase de generador de frecuencia 212.

El mezclador de frecuencia de conversión ascendente 29 se conecta al módulo de conversión de frecuencia de extremo frontal 22; y el mezclador de frecuencia de conversión ascendente 29 lleva a cabo la conversión ascendente en la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal 22, para generar otra señal de radiofrecuencia.

- El detector de fase de generador de frecuencia 211 se conecta al generador de frecuencia de oscilador local 210 y al mezclador de frecuencia de conversión ascendente 29; y el detector de fase de generador de frecuencia 211 determina un error de fase y obtiene una señal analógica de error de fase del generador de frecuencia de oscilador local 210 según la señal de radiofrecuencia generada por el mezclador de frecuencia de conversión ascendente 29 y una señal de radiofrecuencia emitida por el generador de frecuencia de oscilador local 210.

- El generador de código de fase de generador de frecuencia 212 se conecta al detector de fase de generador de frecuencia 211; y el generador de código de fase de generador de frecuencia 212 recibe la señal analógica de error de fase del generador de frecuencia de oscilador local 210, y convierte la señal analógica de error de fase del generador de frecuencia de oscilador local 210 en un código digital de error de fase del generador de frecuencia de oscilador local.

- El corrector de matriz de error binario 25 se conecta al generador de código de fase de generador de frecuencia 212; y el corrector de matriz de error binario 25 recibe el código digital de error de fase del generador de frecuencia de oscilador local, y genera una señal de control de corrección según el código digital de error de fase del generador de frecuencia de oscilador local.

- El generador de frecuencia de oscilador local 210 se conecta al corrector de matriz de error binario 25; y el generador de frecuencia de oscilador local 210 recibe la señal de control de corrección enviada por el corrector de matriz de error binario 25, y corrige el código digital de fase de señal de oscilador local según la señal de control de corrección.

- El mezclador de frecuencia de conversión ascendente 29 se conecta al amplificador de ganancia controlada en el módulo de conversión de frecuencia de extremo frontal 22.

- Se puede observar que, en el transmisor que se muestra en la Figura 2c, una memoria intermedia 1 y una memoria intermedia 2 en la Figura 2c se configuran para almacenar el código digital de amplitud de señal y el código digital de fase emitidos por el generador de código de amplitud 24 y el generador de código de fase 27, y sincronizar y actualizar el código digital de amplitud de señal y el código digital de fase almacenados; se puede observar que una manera específica de implementación para sincronizar y actualizar los datos almacenados (por ejemplo, el código digital de amplitud de señal y código digital de fase en la presente realización) por parte de la memoria intermedia puede ser cualquier manera que sea conocida por una persona experta en la técnica.

Análisis de los efectos beneficiosos de la presente realización:

En esta realización de la presente invención, los componentes como, por ejemplo, un corrector de matriz de error binario, un discriminador de amplitud, un detector de fase, un generador de código de amplitud, y un generador de código de fase se añaden a un extremo frontal de un circuito de radiofrecuencia de un receptor, de modo tal que el receptor/un transmisor puedan comparar, usando el corrector de matriz de error binario, un código digital de amplitud de señal, un código digital de fase de señal, y un código digital de fase de generador de frecuencia en el circuito de radiofrecuencia con una fuente de código estándar prealmacenada en el corrector de fase de señal, y corregir el código digital de amplitud de señal, el código digital de fase de señal, y el código digital de fase de generador de frecuencia en el circuito de radiofrecuencia, llevando a cabo, de esta manera, la recuperación de la onda portadora o generación de la onda portadora en el circuito de radiofrecuencia.

En comparación con la técnica anterior, un chip de banda base ya no necesita llevar a cabo la recuperación de la onda portadora o generación de la onda portadora, en especial, no necesita asumir funciones como, por ejemplo, la supresión de la desviación de frecuencia y la supresión de ruido de fase relacionadas con la recuperación de la onda portadora y con el consumo de recursos informáticos, simplificando, de esta manera, las funciones del chip de banda base, reduciendo el consumo de energía del chip de banda base; además, dado que el chip de banda base ya no necesita asumir funciones que requieren la ejecución de procedimientos informáticos complejos, como, por ejemplo, la recuperación de la onda portadora o generación de la onda portadora, la complejidad de la técnica y la dificultad del diseño para fabricar el chip de banda base se reducen, lo cual reduce directamente el coste de fabricación del chip de banda base, reduciendo además, de esta manera, el coste de funcionamiento/uso del chip de banda base.

# Realización 2

35

40

45

50

Un transmisor según la presente realización incluye un mezclador de frecuencia de conversión descendente, un discriminador de amplitud, un generador de código de amplitud, un corrector de matriz de error binario, un generador de frecuencia de oscilador local, un detector de fase, un generador de código de fase, un divisor de potencia, un

modulador, un amplificador de ganancia controlada, un mezclador de frecuencia de conversión ascendente, un amplificador de potencia, y una antena de transmisión.

El mezclador de frecuencia de conversión descendente se conecta al generador de frecuencia de oscilador local, y se configura para convertir una señal de radiofrecuencia a enviarse que se obtiene del generador de frecuencia de oscilador local en una señal analógica de frecuencia intermedia, y luego enviar la señal analógica de frecuencia intermedia al discriminador de amplitud.

5

10

15

25

35

45

50

El discriminador de amplitud se conecta al mezclador de frecuencia de conversión descendente, y se configura para generar una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia enviada por el mezclador de frecuencia de conversión descendente, y luego enviar la primera señal por impulso de amplitud de señal al generador de código de amplitud.

El generador de código de amplitud se conecta al discriminador de amplitud, y se configura para convertir la primera señal por impulso de amplitud de señal como una señal por impulso en un primer código digital de amplitud de señal como una señal digital, y luego enviar el primer código digital de amplitud de señal al corrector de matriz de error binario, donde el generador de código de amplitud es un codificador configurado para convertir una señal por impulso en una señal digital.

El corrector de matriz de error binario se conecta al discriminador de amplitud y al generador de código de amplitud, y se configura para generar una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y luego enviar la señal de control de corrección de amplitud al discriminador de amplitud.

El discriminador de amplitud se configura además para corregir la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal.

El generador de código de amplitud se configura además para convertir la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, de modo tal que el transmisor usa el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora.

Además, el detector de fase se conecta al mezclador de frecuencia de conversión descendente, y se configura para generar una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia enviada por el mezclador de frecuencia de conversión descendente, y luego enviar la primera señal por impulso de fase de señal al generador de código de fase.

30 El generador de código de fase se conecta al detector de fase, y se configura para convertir la primera señal por impulso de fase de señal como una señal por impulso en un primer código digital de fase de señal como una señal digital, y luego enviar el primer código digital de fase de señal al corrector de matriz de error binario, donde el generador de código de fase es un codificador configurado para convertir una señal por impulso en una señal digital.

El corrector de matriz de error binario se conecta al detector de fase y al generador de código de fase, y se configura además para generar una señal de control de corrección de fase según el primer código digital de fase de señal, y luego enviar la señal de control de corrección de fase al detector de fase.

El detector de fase se configura para corregir la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal.

El generador de código de fase se configura además para convertir la segunda señal por impulso de fase de señal 40 en un segundo código digital de fase de señal, de modo tal que el transmisor usa el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

El divisor de potencia se conecta al mezclador de frecuencia de conversión descendente, al discriminador de amplitud, y al detector de fase, y se configura para recibir la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal, dividir la señal analógica de frecuencia intermedia en dos señales analógicas de frecuencia intermedia idénticas, y luego enviar las dos señales analógicas de frecuencia intermedia idénticas al discriminador de amplitud y al detector de fase, respectivamente, de modo tal que el discriminador de amplitud genera la primera señal por impulso de amplitud de señal según una de las señales analógicas de frecuencia intermedia enviada por el divisor de potencia, y el detector de fase genera la primera señal por impulso de fase de señal según la otra de las señales analógicas de frecuencia intermedia enviada por el divisor de potencia.

El modulador se conecta al generador de código de fase y al generador de código de amplitud, y se configura para generar otra señal analógica de frecuencia intermedia según el segundo código digital de fase de señal y el segundo código digital de amplitud de señal.

El mezclador de frecuencia de conversión ascendente se conecta al generador de frecuencia de oscilador local y al modulador, y se configura para regenerar una señal de radiofrecuencia según la señal analógica de frecuencia intermedia generada por el modulador y la señal de radiofrecuencia emitida por el generador de frecuencia de oscilador local, y enviar la señal de radiofrecuencia regenerada al amplificador de potencia.

La antena de transmisión se conecta al amplificador de potencia, y se configura para transmitir la señal de radiofrecuencia regenerada que ha procesado el amplificador de potencia, donde el amplificador de potencia se conecta al mezclador de frecuencia de conversión ascendente.

10

20

45

50

De manera específica, en la presente realización, tal y como se muestra en la Figura 3a, un transmisor puede incluir un mezclador de frecuencia de conversión descendente 31, un discriminador de amplitud 32, un generador de código de amplitud 33, un corrector de matriz de error binario 34, y un generador de frecuencia de oscilador local 35.

El mezclador de frecuencia de conversión descendente 31 se conecta al generador de frecuencia de oscilador local 35, y convierte una señal de radiofrecuencia a enviarse que se obtiene del generador de frecuencia de oscilador local 35 en una señal analógica de frecuencia intermedia, y luego envía la señal analógica de frecuencia intermedia al discriminador de amplitud 32.

El discriminador de amplitud 32 se conecta al mezclador de frecuencia de conversión descendente 31; y el discriminador de amplitud 32 genera una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia enviada por el mezclador de frecuencia de conversión descendente 31, y luego envía la primera señal por impulso de amplitud de señal al generador de código de amplitud 33.

El generador de código de amplitud 33 se conecta al discriminador de amplitud 32; y el generador de código de amplitud 33 convierte la primera señal por impulso de amplitud de señal en un primer código digital de amplitud de señal al corrector de matriz de error binario 34.

El corrector de matriz de error binario 34 se conecta al discriminador de amplitud 32; y el corrector de matriz de error binario 34 genera una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y luego envía la señal de control de corrección de amplitud al discriminador de amplitud 32.

El discriminador de amplitud 32 corrige la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal.

30 El generador de código de amplitud 33 convierte la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, de modo tal que el transmisor usa el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora.

Además, el transmisor según la presente realización puede, tal y como se muestra en la Figura 3b, incluir un divisor de potencia 36, un detector de fase 37, y un generador de código de fase 38.

El detector de fase 37 se conecta al mezclador de frecuencia de conversión descendente 31; y el detector de fase 37 genera la primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia enviada por el mezclador de frecuencia de conversión descendente 31, y luego envía la primera señal por impulso de fase de señal al generador de código de fase 38.

40 El generador de código de fase 38 se conecta al detector de fase 37; y el generador de código de fase 38 convierte la primera señal por impulso de fase de señal en el primer código digital de fase de señal, y luego envía el primer código digital de fase de señal al corrector de matriz de error binario 34.

El corrector de matriz de error binario 34 se conecta al detector de fase 37; y el corrector de matriz de error binario 34 genera la señal de control de corrección de fase según el primer código digital de fase de señal, y luego envía la señal de control de corrección de fase al detector de fase 37.

El detector de fase 37 corrige la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal.

El generador de código de fase 38 convierte la segunda señal por impulso de fase de señal en el segundo código digital de fase de señal, de modo tal que el transmisor usa el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

El divisor de potencia 36 se conecta al mezclador de frecuencia de conversión descendente 31, al discriminador de amplitud 32, y al detector de fase 37; y el divisor de potencia 36 recibe la señal analógica de frecuencia intermedia enviada por el módulo de conversión de frecuencia de extremo frontal, divide la señal analógica de frecuencia intermedia en dos señales analógicas de frecuencia intermedia idénticas, y luego envía las dos señales analógicas de frecuencia intermedia idénticas al discriminador de amplitud 32 y al detector de fase 37, respectivamente, de modo tal que el discriminador de amplitud 32 genera la primera señal por impulso de amplitud de señal según una de las señales analógicas de frecuencia intermedia, y el detector de fase 37 genera la primera señal por impulso de fase de señal según la otra de las señales analógicas de frecuencia intermedia.

Además, el transmisor según la presente realización puede, tal y como se muestra en la Figura 3c, incluir un modulador 39, un amplificador de ganancia controlada 310, un mezclador de frecuencia de conversión ascendente 311, un amplificador de potencia 312, y una antena de transmisión 313.

El modulador 30 se conecta al generador de código de fase 38 y al generador de código de amplitud 33; y el modulador 30 genera otra señal analógica de frecuencia intermedia según el segundo código digital de fase de señal y el segundo código digital de amplitud de señal.

- El mezclador de frecuencia de conversión ascendente 311 se conecta al generador de frecuencia de oscilador local 35 y al modulador 39; y el mezclador de frecuencia de conversión ascendente 311 regenera una señal de radiofrecuencia según la señal analógica de frecuencia intermedia generada por el modulador 39 y la señal de radiofrecuencia emitida por el generador de frecuencia de oscilador local 35, y envía la señal de radiofrecuencia regenerada al amplificador de potencia 312.

- La antena de transmisión 313 se conecta al amplificador de potencia 312; el amplificador de potencia 312 se conecta al mezclador de frecuencia de conversión ascendente 311; y la antena de transmisión 313 transmite la señal de radiofrecuencia regenerada que ha procesado el amplificador de potencia 312.

Se puede observar que las funciones y las formas de ejecución de una memoria intermedia 5 y una memoria intermedia 6 en la Figura 3c son las mismas que las de la memoria intermedia 1 y la memoria intermedia 2 en la Figura 2c, ambas sincronizan y actualizan un código digital de amplitud de señal y un código digital de fase almacenados.

Se puede observar además que una memoria intermedia 3 y una memoria intermedia 4 se incluyen en la Figura 3c, y pueden recibir y almacenar una señal enviada por el chip de banda base, y transferir la señal almacenada al modulador 39. Este medio de transmisión de señal y manera de procesamiento de señal del chip de banda base  $\rightarrow$  la memoria intermedia 3/memoria intermedia 4  $\rightarrow$  el modulador 39 puede ser una manera conocida por una persona experta en la técnica.

Se utiliza un medio técnico existente.

30

45

50

Análisis de los efectos beneficiosos de la presente realización:

En esta realización de la presente invención, los componentes como, por ejemplo, un corrector de matriz de error binario, un discriminador de amplitud, un detector de fase, un generador de código de amplitud, y un generador de código de fase se añaden a un extremo frontal de un circuito de radiofrecuencia de un transmisor, de modo tal que un receptor/el transmisor pueden comparar, usando el corrector de matriz de error binario, un código digital de amplitud de señal, un código digital de fase de señal, y un código digital de fase de generador de frecuencia en el circuito de radiofrecuencia con una fuente de código estándar prealmacenada en el corrector de matriz de error binario, y corregir el código digital de amplitud de señal, el código digital de fase de señal, y el código digital de fase de generador de frecuencia en el circuito de radiofrecuencia, llevando a cabo, de esta manera, la recuperación de la onda portadora o generación de la onda portadora en el circuito de radiofrecuencia.

En comparación con la técnica anterior, un chip de banda base ya no necesita llevar a cabo la recuperación de la onda portadora o generación de la onda portadora, en especial, no necesita asumir funciones como, por ejemplo, la supresión de la desviación de frecuencia y la supresión de ruido de fase relacionadas con la recuperación de la onda portadora y con el consumo de recursos informáticos, simplificando, de esta manera, las funciones del chip de banda base, reduciendo el consumo de energía del chip de banda base; además, dado que el chip de banda base ya no necesita asumir funciones que requieren la ejecución de procedimientos informáticos complejos, como, por ejemplo, la recuperación de la onda portadora o generación de la onda portadora, la complejidad de la técnica y la dificultad del diseño para fabricar el chip de banda base se reducen, lo cual reduce directamente el coste de fabricación del chip de banda base, reduciendo además, de esta manera, el coste de funcionamiento/uso del chip de banda base.

#### Realización 3

Esta realización de la presente invención provee un método para recibir una señal de radiofrecuencia, el cual lleva a cabo un receptor. Según se muestra en la Figura 4a, el método incluye:

- 401. Un receptor recibe una señal de radiofrecuencia, y convierte una señal de radiofrecuencia obtenida en una señal analógica de frecuencia intermedia.

- 402. Generar una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia.

- 403. Convertir la primera señal por impulso de amplitud de señal en un primer código digital de amplitud de señal.

- 404. Generar una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y corregir la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal.

- 405. Convertir la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, y usar el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora. En una forma paralela, tal y como se muestra en la Figura 4b, el método para recibir una señal de radiofrecuencia que se provee mediante la presente realización puede incluir además:

- 406. El receptor divide la señal analógica de frecuencia intermedia en dos señales analógicas de frecuencia intermedia idénticas.

- 15 407. Generar una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia.

- 408. Convertir la primera señal por impulso de fase de señal en un primer código digital de fase de señal.

- 409. Generar una señal de control de corrección de fase según el primer código digital de fase de señal, y corregir la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal.

- 410. Convertir la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal, y usar el segundo código digital de fase de señal como un código digital de fase de señal después de la recuperación de la onda portadora o generación de la onda portadora.

- Además, tal y como se muestra en la Figura 4c, el método para recibir una señal de radiofrecuencia provisto por la presente realización incluye:

- 411. El receptor lleva a cabo la conversión ascendente en la señal analógica de frecuencia intermedia para generar otra señal de frecuencia.

- 412. Determinar un error de fase y obtener una señal analógica de error de fase de un generador de frecuencia de oscilador local según la otra señal de radiofrecuencia y una señal de radiofrecuencia emitida por el generador de frecuencia de oscilador local en el receptor.

- 413. Convertir la señal analógica de error de fase del generador de frecuencia de oscilador local en un código digital de error de fase del generador de frecuencia de oscilador local.

- 414. Generar una señal de control de corrección según el código digital de error de fase del generador de frecuencia de oscilador local.

- 415. Corregir el código digital de fase de señal de oscilador local según la señal de control de corrección.

- En la presente realización, una función de recuperación de la onda portadora o generación de la onda portadora se puede implementar en una porción del circuito de radiofrecuencia de un receptor; en comparación con la técnica anterior, un chip de banda base ya no necesita llevar a cabo la recuperación de la onda portadora o generación de la onda portadora, en especial, no necesita asumir funciones como, por ejemplo, la supresión de la desviación de frecuencia y la supresión de ruido de fase relacionadas con la recuperación de la onda portadora y con el consumo

- de recursos informáticos, simplificando, de esta manera, las funciones del chip de banda base, reduciendo el consumo de energía del chip de banda base; además, dado que el chip de banda base ya no necesita asumir funciones que requieren la ejecución de procedimientos informáticos complejos, como, por ejemplo, la recuperación de la onda portadora o generación de la onda portadora, la complejidad de la técnica y la dificultad del diseño para fabricar el chip de banda base se reducen, lo cual reduce directamente el coste de fabricación del chip de banda

- 45 base, reduciendo además, de esta manera, el coste de funcionamiento/uso del chip de banda base.

#### Realización 4

10

Esta realización de la presente invención provee un método para transmitir una señal de radiofrecuencia, el cual lleva a cabo un transmisor. Tal y como se muestra en la Figura 5a, el método incluye:

- 501. Un transmisor convierte una señal de radiofrecuencia a enviarse en una señal analógica de frecuencia intermedia.

- 502. Generar una primera señal por impulso de amplitud de señal según la señal analógica de frecuencia intermedia.

- 503. Convertir la primera señal por impulso de amplitud de señal en un primer código digital de amplitud de señal.

- 5 504. Generar una señal de control de corrección de amplitud según el primer código digital de amplitud de señal, y corregir la primera señal por impulso de amplitud de señal según la señal de control de corrección de amplitud, para generar una segunda señal por impulso de amplitud de señal.

- 505. Convertir la segunda señal por impulso de amplitud de señal en un segundo código digital de amplitud de señal, de modo tal que el transmisor usa el segundo código digital de amplitud de señal como un código digital de amplitud de señal después de la recuperación de la onda portadora o generación de la onda portadora.

En una forma paralela, tal y como se muestra en la Figura 5b, el método para transmitir una señal de radiofrecuencia provisto por la presente realización, después de la conversión de una señal de radiofrecuencia a enviarse en una señal analógica de frecuencia intermedia, incluye además:

- 506. El transmisor divide la señal analógica de frecuencia intermedia en dos señales analógicas de frecuencia intermedia idénticas.

- 507. Generar una primera señal por impulso de fase de señal según la señal analógica de frecuencia intermedia.

- 508. Convertir la primera señal por impulso de fase de señal en un primer código digital de fase de señal.

- 509. Generar una señal de control de corrección de fase según el primer código digital de fase de señal, y corregir la primera señal por impulso de fase de señal según la señal de control de corrección de fase, para generar una segunda señal por impulso de fase de señal.

- 510. Convertir la segunda señal por impulso de fase de señal en un segundo código digital de fase de señal.

Además, tal y como se muestra en la Figura 5c, el método para transmitir una señal de radiofrecuencia provisto por la presente realización incluye además:

- 511. El transmisor genera otra señal analógica de frecuencia intermedia según el segundo código digital de fase de señal y el segundo código digital de amplitud de señal.

- 512. Regenerar una señal de radiofrecuencia según la otra señal analógica de frecuencia intermedia generada y una señal de radiofrecuencia emitida por un generador de frecuencia de oscilador local en el transmisor.

- 513. Transmitir la señal de radiofrecuencia regenerada después de llevar a cabo la amplificación de potencia en la señal de radiofrecuencia regenerada.

- En la presente realización, una función de la recuperación de la onda portadora o generación de la onda portadora se puede implementar en una porción del circuito de radiofrecuencia de un transmisor; en comparación con la técnica anterior, un chip de banda base ya no necesita llevar a cabo la recuperación de la onda portadora o generación de la onda portadora, en especial, no necesita asumir funciones como, por ejemplo, la supresión de la desviación de frecuencia y la supresión de ruido de fase relacionadas con la recuperación de la onda portadora y con el consumo de recursos informáticos, simplificando, de esta manera, las funciones del chip de banda base, reduciendo el consumo de energía del chip de banda base; además, dado que el chip de banda base ya no necesita asumir funciones que requieren la ejecución de procedimientos informáticos complejos, como, por ejemplo, la recuperación de la onda portadora o generación de la onda portadora, la complejidad de la técnica y la dificultad del diseño para fabricar el chip de banda base se reducen, lo cual reduce directamente el coste de fabricación del chip de banda base, reduciendo además, de esta manera, el coste de funcionamiento/uso del chip de banda base.

#### Realización 5

10

Esta realización de la presente invención provee un sistema para recibir y transmitir una señal de radiofrecuencia, el cual, tal y como se muestra en la Figura 6a, incluye:

un receptor 61 y un transmisor 62.

45 El sistema para recibir y transmitir una señal de radiofrecuencia según la presente realización incluye el receptor según la Realización 1 y el transmisor según la Realización 2.

En la presente realización, el receptor 61 y el transmisor 62 pueden recibir y transmitir una señal de radiofrecuencia usando una red radio, donde una manera de implementación específica puede ser cualquier manera conocida por una persona experta en la técnica.

Se puede observar que un extremo del sistema para recibir y transmitir una señal de radiofrecuencia según la presente realización puede tener funciones tanto del receptor como del transmisor; es decir, el receptor según la Realización 1 y el transmisor según la Realización 2 se integran en un mismo circuito de radiofrecuencia; además, una persona experta en la técnica puede, usando un medio técnico común, permitir que un corrector de matriz de error binario asuma funciones tanto del transmisor como del receptor, de modo tal que un circuito de radiofrecuencia tenga funciones tanto del receptor según la Realización 1 como del transmisor según la Realización 2, por ejemplo, tal y como se muestra en la Figura 6b:

5

10

40

45

Los circuitos de radiofrecuencia del transmisor y receptor se integran de forma conjunta, y comparten un corrector de matriz de error binario; además, una manera específica de llevar a cabo la recuperación de la onda portadora o generación de la onda portadora por parte del circuito de radiofrecuencia que se muestra en la Figura 6b y se conecta al chip de banda base puede ser la misma que la de realizaciones anteriores.