# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 605 491

51 Int. Cl.:

**H03M 1/08** (2006.01) **H03M 1/12** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 26.03.2013 PCT/EP2013/056397

(87) Fecha y número de publicación internacional: 03.10.2013 WO2013144142

(96) Fecha de presentación y número de la solicitud europea: 26.03.2013 E 13713831 (9)

(97) Fecha y número de publicación de la concesión europea: 27.07.2016 EP 2831998

(54) Título: Atenuación de una anomalía de fase en una señal de salida de convertidor analógico-digital

(30) Prioridad:

30.03.2012 EP 12275035

Fecha de publicación y mención en BOPI de la traducción de la patente: 14.03.2017

(73) Titular/es:

AIRBUS DEFENCE AND SPACE LIMITED (100.0%) Gunnels Wood Road Stevenage, Hertfordshire SG1 2AS, GB

(72) Inventor/es:

FARRUGIA, LEWIS; GIBSON, MARK y PEARSON, RYAN

(74) Agente/Representante:

PONS ARIÑO, Ángel

# **DESCRIPCIÓN**

Atenuación de una anomalía de fase en una señal de salida de convertidor analógico-digital.

## 5 Campo de la invención

La presente invención se refiere a la atenuación de una anomalía de fase en una señal de salida de convertidor analógico-digital (ADC). Más en particular, la presente invención se refiere a la obtención de información acerca de un nivel estimado de interferencia entre una salida del ADC y una entrada del ADC debida a cada una de una pluralidad de palabras de código basándose en los valores lógicos de bits en la palabra de código, y la corrección de los valores I y Q obtenidos a partir de la señal de salida de ADC basándose en la información obtenida.

#### Antecedentes de la invención

15 Los satélites de comunicaciones que reciben señales analógicas, por ejemplo procedentes de un transmisor con base en tierra o procedentes de otro satélite, pueden estar dispuestos para convertir las señales analógicas dentro del dominio digital para procesamiento a bordo. La señal analógica recibida es convertida usando un convertidor analógico-digital (ADC), que mide el nivel de señal, por ejemplo el voltaje o la corriente, en un momento particular y produce una palabra de código que representa el nivel señal medido. Por lo tanto, la señal digital producida por el 20 ADC comprende una secuencia de palabras de código que representan la variación en el nivel de señal recibida a lo largo del tiempo.

También, en las aplicaciones de procesamiento de señal puede ser necesario medir con exactitud el ángulo de fase de la señal que es procesada. Por ejemplo, cuando se usan esquemas de modulación de amplitud en cuadratura (QAM), la separación angular entre distintos símbolos referidos al origen de la constelación disminuye a medida que se incrementa el orden de modulación. Por lo tanto, es deseable una medición exacta del ángulo de fase para asegurar que los símbolos pueden distinguirse con fiabilidad. Pueden estar presentes errores en la señal tal como se recibe, por ejemplo como ruido gaussiano, o pueden ser introducidos por diversos componentes antes del procesador de señal digital (DSP). En el caso de la conversión de una señal analógica a una digital mediante un 30 ADC, pueden introducirse errores sistemáticos por parte del propio ADC. Por ejemplo, se sabe que los ADC pueden adolecer de efectos de no linealidad integral (INL) y no linealidad diferencial (DNL) que reducen la gama dinámica para la cual puede usarse el ADC.

El documento US2004164889 describe un módulo digitalizador que comprende un convertidor AD para muestrear un par de señales analógicas para convertir señales analógicas en señales digitales. Una unidad calculadora de componente de frecuencia de oblicuidad calcula una componente de frecuencia de oblicuidad que representa un error de fase de cada frecuencia de una señal digital que corresponde a otra señal digital. Una unidad correctora de componente de frecuencia corrige la componente de frecuencia de oblicuidad basándose en la frecuencia de oblicuidad. El aparato corrige un error de la sincronización de la muestra con la cual un par de señales analógicas es convertido en señales digitales mediante un proceso digital de modo que puede prevenirse un deterioro de calidad de señal durante la digitalización de un par de señales analógicas.

La invención se realiza en este contexto.

## 45 Resumen de la invención

De acuerdo con la presente invención, se proporciona un procedimiento de atenuación de una anomalía de fase en una señal de salida de convertidor analógico-digital ADC, comprendiendo el procedimiento recibir una pluralidad de palabras de código producidas por el ADC, obtener para cada una de la pluralidad de palabras de código información acerca de un nivel estimado de interferencia entre una salida del ADC y una entrada del ADC debida a la palabra de código, basándose en los valores lógicos de bits en la palabra de código, obtener correcciones en fase I y en cuadratura Q del nivel estimado de interferencia basándose en la información obtenida, y aplicar las correcciones I y Q a los valores I y Q obtenidos a partir de la señal de salida de ADC.

55 Obtener información acerca del nivel estimado de interferencia para cada palabra de código puede comprender obtener la información basándose en el peso de Hamming de la palabra de código.

Obtener información acerca del nivel estimado de interferencia para cada palabra de código puede comprender obtener una suma de dígitos ponderada de la palabra de código multiplicando cada bit de la palabra de código por

un factor de ponderación predeterminado para ese bit y sumando los bits ponderados, y obtener la información acerca del nivel estimado de interferencia basándose en la suma de dígitos ponderada.

Obtener información acerca del nivel estimado de interferencia para cada palabra de código puede comprender además comparar cada bit de la palabra de código con cada bit correspondiente de la palabra de código precedente producida por el ADC, para determinar el número de transiciones de bit 0 a 1 y el número de transiciones de bit 1 a 0 con respecto a la palabra de código precedente, y obtener la información acerca del nivel estimado de interferencia basándose en el número de transiciones de bit 0 a 1, el número de transiciones de bit 1 a 0, y el número de bits establecidos en 1 en la palabra de código actual.

Obtener información acerca del nivel estimado de interferencia para cada palabra de código puede comprender además almacenar información de suma de dígitos acerca del número de bits establecidos en 1 en cada una de la pluralidad de palabras de código, y obtener la información acerca del nivel estimado de interferencia debida a la palabra de código actual basándose en la información de suma de dígitos almacenada.

15

30

El nivel estimado de interferencia para cada palabra de código puede comprender un valor que representa un nivel relativo de interferencia debida a la palabra de código, de modo que una pluralidad de dichos valores obtenidos para la pluralidad de palabras de código define una señal interferente estimada, donde los valores de I y Q pueden obtenerse cambiando la escala y rotando la fase de la señal interferente estimada de acuerdo con un parámetro de 20 cambio de escala de amplitud predeterminado y un parámetro de rotación de fase predeterminado.

El procedimiento puede comprender además correlacionar la señal de salida de ADC con una primera señal de referencia para obtener los valores I y Q a partir de la señal de salida de ADC, donde la rotación de fase de la señal interferente estimada puede comprender generar una segunda señal de referencia con la fase rotada con respecto a la primera señal de referencia en un ángulo determinado por el parámetro de rotación de fase predeterminado, y correlacionar la señal interferente estimada con la segunda señal de referencia.

Las correcciones I y Q pueden obtenerse basándose en el resultado de correlación de correlacionar la señal interferente estimada con la segunda señal de referencia.

De acuerdo con la presente invención, se proporciona un aparato para atenuar una anomalía de fase en una señal de salida de convertidor analógico-digital ADC, comprendiendo el aparato un medio para recibir una pluralidad de palabras de código producidas por el ADC y obtener, para cada una de la pluralidad de palabras de código, información acerca de un nivel estimado de interferencia entre una salida del ADC y una entrada del ADC debida a 35 la palabra de código, basándose en los valores lógicos de bits en la palabra de código, un medio para obtener correcciones en fase I y en cuadratura Q del nivel estimado de interferencia basándose en la información obtenida, y un medio para aplicar las correcciones I y Q a los valores I y Q obtenidos a partir de la señal de salida de ADC.

El medio para obtener la información acerca de un nivel estimado de interferencia puede ser un calculador de peso 40 de Hamming.

El medio para obtener la información acerca de un nivel estimado de interferencia puede estar dispuesto para obtener, para cada palabra de código, una suma de dígitos ponderada de la palabra de código multiplicando cada bit de la palabra de código por un factor de ponderación predeterminado para ese bit y sumar los bits ponderados, y obtener la información acerca del nivel estimado de interferencia basándose en la suma de dígitos ponderada.

El medio para obtener la información acerca de un nivel estimado de interferencia puede estar dispuesto además para comparar, para cada palabra de código, cada bit de la palabra de código con cada bit correspondiente de la palabra de código precedente producida por el ADC, para determinar el número de transiciones de bit 0 a 1 y el número de transiciones de bit 1 a 0 con respecto a la palabra de código precedente, y obtener la información acerca del nivel estimado de interferencia basándose en el número de transiciones de bit 0 a 1, y el número de bits establecidos en 1 en la palabra de código actual.

El medio para obtener la información acerca de un nivel estimado de interferencia puede estar dispuesto además para almacenar información de suma de dígitos acerca del número de bits establecidos en 1 en cada una de la pluralidad de palabras de código, y obtener la información acerca del nivel estimado de interferencia debida a cada palabra de código basándose en la información de suma de dígitos almacenada.

La información acerca de un nivel estimado de interferencia puede comprender un valor que representa un nivel

relativo de interferencia debida a la palabra de código, de modo que una pluralidad de dichos valores obtenidos para la pluralidad de palabras de código define una señal interferente estimada, y el medio para obtener las correcciones I y Q puede comprender un medio para cambio de escala y un medio para rotación de fase de la señal interferente estimada de acuerdo con un parámetro de cambio de escala de amplitud predeterminado y un parámetro de rotación de fase predeterminado.

El aparato puede comprender un generador de señal de referencia dispuesto para generar una primera señal de referencia y una segunda señal de referencia con la fase rotada con respecto a la primera señal de referencia en un ángulo determinado por el parámetro de rotación de fase predeterminado, y un primer correlador dispuesto para correlacionar la señal de salida de ADC con la primera señal de referencia para obtener los valores I y Q a partir de la señal de salida de ADC, donde el medio para cambio de escala y rotación de fase de la señal interferente estimada puede incluir un segundo correlador dispuesto para correlacionar la señal interferente estimada con la segunda señal de referencia, para aplicar la rotación de fase a la señal interferente estimada.

# 15 Breve descripción de los dibujos

A continuación se describirán realizaciones de la presente invención, únicamente a título de ejemplo, con referencia a los dibujos adjuntos, en los cuales:

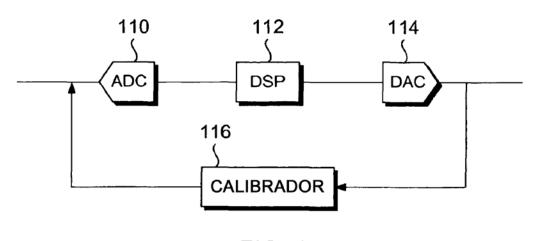

- 20 la figura 1 ilustra un sistema de procesamiento de señal para uso en un satélite de comunicaciones;

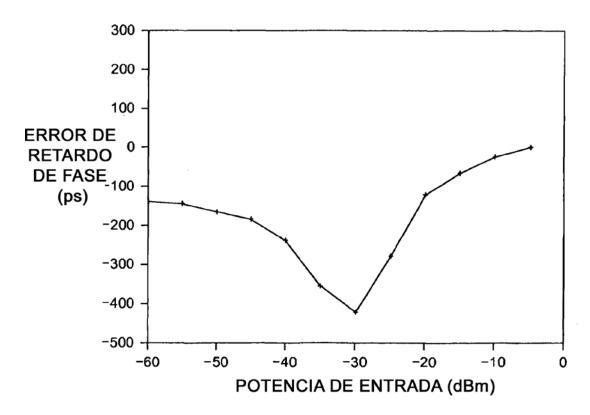

- la figura 2 es un gráfico que traza el error de retardo de fase frente a la potencia de la señal de entrada para el sistema de la fig. 1;

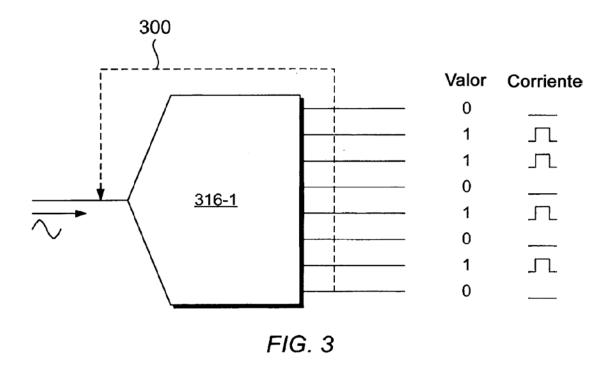

- la figura 3 ilustra la interferencia digital-analógica en la señal de salida de un ADC;

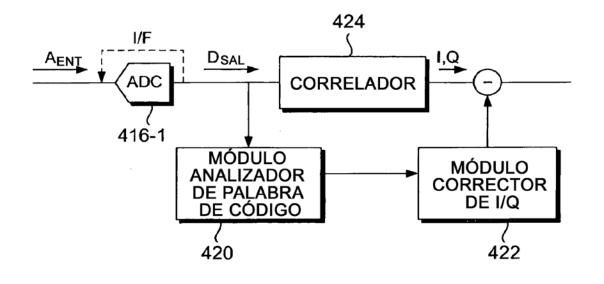

- la figura 4 ilustra un aparato para atenuar una anomalía de fase en la señal de salida de un ADC, de acuerdo con 25 una realización de la presente invención;

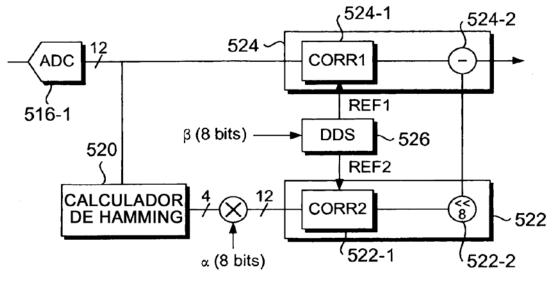

- la figura 5 ilustra un aparato para atenuar una anomalía de fase en un sistema para medir el ángulo de fase, de acuerdo con una realización de la presente invención;

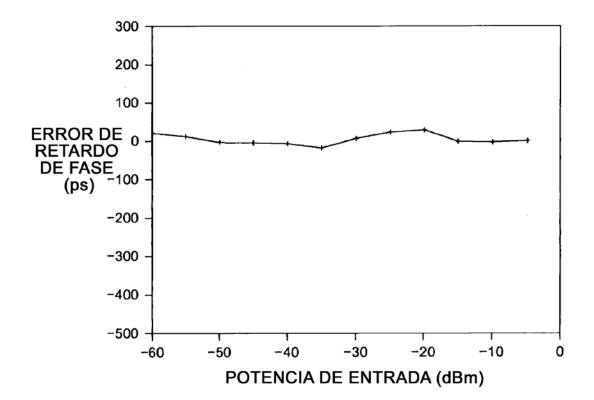

- la figura 6 es un gráfico que traza el error de retardo de fase frente a la potencia de la señal de entrada para el sistema de la fig. 5; y

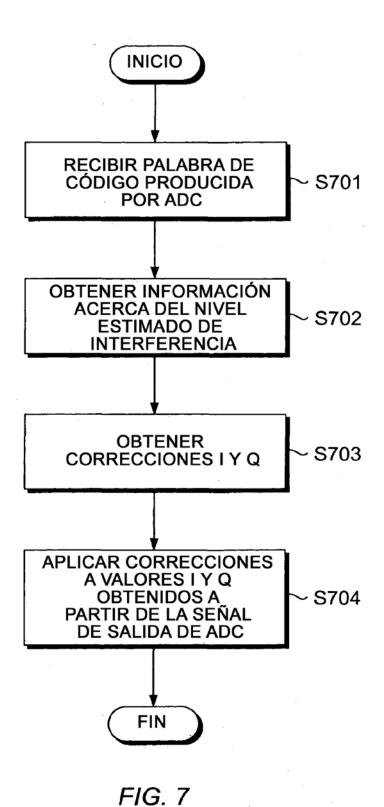

- 30 la figura 7 ilustra un procedimiento para atenuar una anomalía de fase en una señal de salida de ADC, de acuerdo con una realización de la presente invención.

# Descripción detallada

- 35 Haciendo referencia a continuación a la fig. 1, se ilustra un sistema de procesamiento de señal para uso en un satélite de comunicaciones. El sistema comprende un ADC (110), un DSP (112) conectado a la salida del ADC (110), y un convertidor digital-analógico (DAC) (114) conectado a la salida del DSP (112). Una señal analógica es introducida en el ADC (110) y convertida en una señal digital, la cual es procesada entonces por el DSP (112). La señal digital procesada es convertida entonces de nuevo al dominio analógico por el DAC (114).

- Tal como se muestra en la fig. 1, en la presente realización se usa un calibrador de DSP (116) para comprobar si la fase de la señal se conserva correctamente a través de las transiciones de analógico a digital y de vuelta a analógico. El calibrador de DSP (116) opera inyectando una señal de referencia conocida en la entrada del ADC (110), a una frecuencia escogida para no interferir con otras frecuencias presentes en la señal de entrada que es procesada. El calibrador de DSP (116) reconvierte la salida analógica del DAC (114) de vuelta a una representación digital usando su propio ADC, es decir un ADC adicional incluido en el calibrador (116), y luego correlaciona esta señal con sus propias señales de referencia digitales I, Q digitales locales, de las cuales se mide un ángulo de fase. La medición del ángulo de fase conduce a un retardo de fase por interferencia sistemática, dada la frecuencia conocida de las señales de referencia. Por lo tanto, el calibrador de DSP (116) puede comparar la señal de referencia en la salida del DAC (114) con la señal de referencia de entrada para determinar si la fase de la señal de referencia se ha conservado o si se han introducido errores de fase.

- La figura 2 es un gráfico que traza el error de retardo de fase frente a la potencia de la señal de entrada para el sistema de la fig. 1. El error de retardo de fase se mide en picosegundos (ps) y la potencia de la señal de entrada se mide en decibelios referidos a un milivatio (dBm). El error de retardo de fase es el error inherente en las mediciones obtenidas por el calibrador de DSP (116) para una señal de referencia que comprende un tono constante a 9,80 megahercios (MHz). Tal como se muestra en la fig. 2, a bajas potencias de señal de entrada se infieren errores de retardo de fase de hasta varios cientos de ps como resultado de que la fase sea medida incorrectamente por el correlador, con el resultado de que el ángulo de fase es medido incorrectamente por el correlador en el calibrador de

DSP (116). Las investigaciones llevadas a cabo por los inventores han revelado que la fuente de esta anomalía de retardo de fase a bajas potencias de señal es la interferencia digital-analógica entre la salida de ADC y la entrada de ADC en el calibrador (116). Específicamente, diferentes palabras de código de salida pueden interferir de manera diferente con la señal analógica de entrada, dependiendo de los niveles de voltaje en cada palabra de código.

La interferencia digital-analógica en el ADC (316-1) del calibrador de DSP (116) de la fig. 1 se ilustra esquemáticamente en la fig. 3. Existe una vía de fuga (300) entre el bus de salida de ADC y la entrada de ADC, lo que significa que la señal de entrada puede verse influenciada por los niveles de corriente en la palabra de código que es producida actualmente por el ADC (316-1). Tal vía de fuga puede estar presente en cualquier ADC 10 convencional ya que en la práctica la entrada y la salida no están aisladas perfectamente, lo que significa que todavía puede producirse una anomalía de retardo de fase independientemente del tipo de ADC usado en el calibrador (116).

En más detalle, tal como se muestra en la fig. 3 el bus de salida de ADC incluye una pluralidad de líneas de salida dispuestas cada una para transportar un bit de la palabra de código producida. En el presente ejemplo el ADC (316-1) es un ADC de 8 bits, pero la presente invención se puede aplicar en general a ADC de cualquier resolución. Como los principios de funcionamiento de los ADC son bien conocidos, aquí no se proporcionará una descripción detallada. Tal como se muestra en la fig. 3, el nivel de corriente en cada una de las líneas de salida depende de si ese bit de la palabra de código que es producida actualmente está establecido en 0 o 1, es decir, si el voltaje está establecido en 20 bajo o alto. Específicamente, cuando el voltaje de un bit está establecido en alto, que representa un valor binario de 1, circula una corriente más alta en la línea de señal que transporta ese bit que en una línea de señal que transporta un valor binario de 0. La corriente de salida más alta será obtenida cuando todos los bits de la palabra de código producida están establecidos en 1, y la corriente de salida más baja será obtenida cuando todos los bits de la palabra de código producida están establecidos en 0. Por lo tanto, la fuerza de la interferencia digital-analógica en cualquier momento dependerá del número de bits establecidos en 1 en la palabra de código que es producida actualmente por el ADC (316-1). Es decir, la interferencia será más fuerte cuando más bits están establecidos en 1 porque la corriente de salida media será más alta.

El experto en la materia comprenderá que aunque los niveles de corriente ejemplares mostrados en la fig. 3 corresponden a un protocolo eléctrico particular, en el cual un nivel de voltaje alto representa un valor de 1 y un nivel de voltaje bajo representa un valor de 0, la presente invención no está limitada a su uso con tales protocolos. En otras realizaciones pueden usarse otros protocolos eléctricos, por ejemplo el nivel de corriente tanto en ambos estados 1 y 0 puede ser el mismo, cambiando sólo la dirección de la corriente. En cualquier caso, independientemente del protocolo particular usado puede suponerse que el nivel de interferencia varía de acuerdo con los valores lógicos de los bits en la palabra de código, por ejemplo el número de bits establecidos en 1, y/o el número de transiciones de 1 a 0 y de 0 a 1 en relación con la palabra de código precedente, es decir la diferencia entre valores lógicos de bits en la palabra de código actual y los valores lógicos de bits correspondientes en la palabra de código precedente. En términos generales, las realizaciones de la presente invención pueden estimar el nivel de interferencia debida a una palabra de código basándose en valores lógicos de bits en la palabra de código.

Haciendo referencia ahora a la fig. 4, se ilustra un aparato para atenuar una anomalía de fase en la señal de salida de un ADC, de acuerdo con una realización de la presente invención. El aparato comprende un módulo analizador de palabra de código (420) para analizar una palabra de código producida por un ADC (416-1), un correlador (424) para obtener valores I y Q a partir de la señal de salida de ADC, y un módulo corrector de I/Q (422) para obtener 45 correcciones en fase (I) y en cuadratura (Q) que han de aplicarse a los valores I y Q obtenidos a partir de la señal de salida de ADC.

En más detalle, el módulo analizador de palabra de código (420) está dispuesto para recibir una palabra de código producida por el ADC (416-1), y obtener información acerca de un nivel esperado de interferencia entre la salida y la entrada de ADC debida a esa palabra de código. Tal como se describe anteriormente, el nivel de interferencia analógica-digital causada por una palabra de código que es producida por un ADC puede verse influenciado por la corriente media en las líneas de señal de salida y/o el número de transiciones de bit entre palabras de código consecutivas. En general, el módulo analizador de palabra de código (420) puede estar dispuesto para obtener la información acerca del nivel esperado de interferencia basándose en los valores lógicos de los bits en la palabra de código. Por ejemplo, puede determinarse durante las pruebas que para un tipo particular de ADC, el nivel de interferencia está influenciado fuertemente por la corriente media, la cual depende ella misma del número de bits establecidos en 1 en la palabra de código. Por lo tanto, en este caso el modulo analizador de palabra de código (420) puede estar dispuesto para obtener información acerca del número de bits establecidos en 1 en la palabra de código recibida. Aquí, la información acerca del número de bits establecidos en 1 puede adoptar diversas formas.

Por ejemplo, en una realización la información puede ser simplemente el número total de bits establecidos en 1, es decir, el peso de Hamming de la palabra de código. El peso de Hamming es la suma de dígitos de un número binario, y también puede denominarse el "recuento de población" o la "suma lateral". Por ejemplo, el peso de Hamming de un número binario de 8 bits puede ser cualquier número entero entre 0 (es decir, todos los bits establecidos en 0) y 8 (es decir, todos los bits establecidos en 1). En el ejemplo de la fig. 3, la palabra de código producida 01101010 tiene un peso de Hamming de 4 (0+1+1+0+1+0+1+0).

En otras realizaciones pueden usarse otras estrategias. Por ejemplo, en lugar de usar el peso de Hamming, el módulo analizador de palabra de código (420) puede estar dispuesto para obtener una suma de dígitos ponderada de la palabra de código recibida, multiplicando cada valor de bit (es decir, 1 o 0) por un factor de ponderación predeterminado correspondiente para ese bit, y sumando los bits ponderados. Este procedimiento puede tener en cuenta el hecho de que no todas las líneas de señal de salida del ADC pueden interferir igualmente con la entrada de ADC. Por ejemplo, el acoplamiento entre cualquier línea de señal dada y la entrada puede verse influenciado por la distribución física de las trazas dentro del ADC. A los bits transmitidos por las líneas que interfieren más fuertemente se les puede dar una ponderación más alta que a los bits transmitidos por las líneas que interfieren menos fuertemente. Los factores de ponderación pueden diferir para diferentes diseños de ADC, y pueden determinarse durante la configuración y calibración del sistema.

Estimando el nivel de interferencia basándose en el número de bits establecidos en 1, por ejemplo basándose en el peso de Hammming o una suma de dígitos ponderada, el aparato puede dar cuenta de la interferencia digitalanalógica debida a efectos estáticos, específicamente las corrientes de bus de ADC. Dependiendo del diseño del ADC, en algunos casos la interferencia también puede verse influenciada por efectos dinámicos tales como las transiciones de bus de ADC, es decir, si un bit particular cambia de 1 a 0 o de 0 a 1 en palabras de código consecutivas. Para dar cuenta de estos efectos dinámicos, en algunas realizaciones el analizador de palabra de código (420) puede estar dispuesto para comparar cada bit de la palabra de código con cada bit correspondiente de la palabra de código precedente producida por el ADC, para determinar el número de transiciones de bit 0 a 1 y el número de transiciones de bit 1 a 0 con respecto a la palabra de código precedente. La información acerca del nivel esperado de interferencia puede obtenerse entonces basándose en el número de transiciones así como el número de bits establecidos en 1 en la palabra de código actual. Además, en algunas realizaciones puede calcularse una suma ponderada del número de transiciones, similar a la suma de dígitos ponderada de la palabra de código. Esto puede dar cuenta del hecho de que las transiciones en una línea particular del bus de ADC pueden interferir más fuertemente con la entrada de ADC que las transiciones en otra línea del bus de ADC.

En otra realización más, puede almacenarse información acerca del número de bits establecidos en 1 para cada una de una secuencia de palabras de código producidas por el ADC. El analizador de palabra de código (420) puede usar entonces esta información almacenada, por ejemplo para calcular una derivada del peso de Hamming o de la suma de dígitos ponderada con respecto al tiempo, por ejemplo una derivada de primer orden o de segundo orden. La derivada puede tenerse en cuenta cuando se estima el nivel de interferencia, para dar cuenta de los efectos de orden superior. En algunas realizaciones, en lugar de calcular directamente la derivada puede usarse la primera, segunda, tercera, etc., diferencia como aproximación numérica a la primera, segunda, tercera, etc. derivada. Aquí, la diferencia finita se usa como aproximación a la derivada matemática verdadera porque la variable en cuestión, es decir el peso de Hamming o la suma de dígitos ponderada, no es una variable continua sino que, en cambio, cambia discontinuamente entre un número limitado de valores discretos.

- 45 Para estimar el nivel de interferencia y obtener las correcciones I y Q, son posibles diversas soluciones. A continuación se describirá en detalle una solución ejemplar con referencia a la fig. 5, que ilustra un aparato para atenuar una anomalía de fase en la señal de salida de un ADC, de acuerdo con una realización de la presente invención.

- 50 En esencia, la estrategia adoptada en la fig. 5 es estimar la fase y amplitud de una señal interferente digitalanalógica. Esto se hace estableciendo el nivel de señal en cualquier momento basándose en valores lógicos de los

bits en la palabra de código actual, por ejemplo el peso de Hamming, la suma de dígitos ponderada, y/o el número

de transiciones de bit 1 a 0 y 0 a 1 en relación con la palabra de código precedente. En la presente realización se

usa el peso de Hamming, y está provisto un módulo calculador de peso de Hamming 520 para calcular el peso de

55 Hamming de una señal digital producida por un ADC (516-1). Tal como se muestra en la fig. 5, el ADC (516-1) en la

presente realización es un ADC de 12 bits. El peso de Hamming de una palabra de código de 12 bits puede adoptar

un valor entero entre 0 y 12, y tal módulo calculador de peso de Hamming (520) está provisto de un bus de salida de

4 bits para transmitir cualquier valor entre 0 y 12 en forma binaria.

La salida del módulo calculador de peso de Hamming (520) se usa, en esencia, como una representación normalizada del nivel de interferencia debida a esa palabra de código particular con respecto a otras palabras de código. La salida del módulo calculador de peso de Hamming (520) a lo largo de un periodo prolongado, durante el cual son producidas y procesadas una pluralidad de palabras de código, puede considerarse como que proporciona un modelo de la señala interferente estimada, en el cual el nivel de señal de la señal interferente estimada en cualquier momento viene dado por el peso de Hamming de la palabra de código actual. La amplitud de la señal interferente estimada, es decir la salida del módulo calculador de peso de Hamming (520), es entonces cambiada de escala para proporcionar una indicación cuantificada del nivel de interferencia entre la salida y la entrada de ADC debida a la palabra de código actual. Para lograr esto, la salida del módulo calculador de peso de Hamming (520) es multiplicada por un parámetro de cambio de escala de amplitud predeterminado α. En la presente realización, α está provisto como un número de 8 bits, de modo que es obtenida una señal interferente estimada cambiada de escala de 12 bits.

A continuación, la señal cambiada de escala es enviada a un segundo correlador (522), que es similar al primer correlador (524) usado para obtener valores I y Q de la señal digital original (es decir, sin corregir) producida por el ADC (516-1). Aquí, se aplica una rotación de fase constante a la señal cambiada de escala para dar cuenta del hecho de que la palabra de código que interfiere con la señal de entrada analógica corresponde a un valor anterior de la señal, en lugar del valor actual de la señal de entrada. Esto surge porque existe una latencia asociada con la conversión analógica a digital en el ADC (516-1), que por ejemplo puede incluir un circuito y conducto de muestreo y retención.

En más detalle, la rotación de fase puede aplicarse directamente a la señal cambiada de escala, o puede aplicarse indirectamente correlacionando la señal cambiada de escala con una señal de referencia con rotación de fase. Estos dos procedimientos son matemáticamente equivalentes, pero en la presente realización se prefiere la segunda 25 opción ya que el segundo correlador (522) también puede usarse para obtener las correcciones I y Q. Por lo tanto, en la presente realización, se aplica la rotación de fase generando dos señales de referencia con una diferencia de fase de β, y proporcionando cada señal de referencia a uno diferente de los correladores (522), (524). Específicamente, el valor de β, que en la presente realización es un número de 8 bits, es introducido en un generador de señal de referencia (526). El generador señal de referencia (526) genera una primera señal de referencia (REF1) que ha de ser enviada al primer correlador (524), y una segunda señal de referencia (REF2) que ha de ser enviada al segundo correlador (522). En la presente realización, REF1 es generada basándose en la ecuación:

$$REF1(t) = e^{i\omega t}$$

35

mientras que REF2 es generada basándose en la ecuación:

REF2(t) =

$$e^{i(\omega t + \beta)}$$

40 donde β es un parámetro de rotación de fase predeterminado. Estas son meramente ejemplares, y en otras realizaciones pueden usarse otras estrategias para generar señales de referencia con la diferencia de fase necesaria.

Los valores de α y β pueden determinarse empíricamente durante la calibración del sistema, probando diferentes valores para determinar cuál ofrece la reducción más efectiva en la anomalía de retardo de fase. Por consiguiente, no es necesario el conocimiento del mecanismo de interferencia real o la estructura interna del ADC (516-1). La optimización de parámetro de α y β puede obtenerse, por lo tanto, fuera de línea, es decir antes de que el sistema sea puesto en uso, y después de ello puede suponerse que es invariante en el tiempo. En algunas realizaciones, sin embargo, puede estar provisto un medio para realizar periódicamente la recalibración para actualizar los valores de σ y β, con el fin de dar cuenta de efectos tales como el envejecimiento de los componentes del sistema. Además, en la presente realización se ha supuesto que pueden ignorarse la no linealidad integral (INL) y la no linealidad diferencial (DNL) del ADC (516-1), pero en algunas realizaciones puede no ser así. Si los efectos de la INL y la DNL no son insignificantes, α y β dependerán de la amplitud. Podría darse cuenta de esto determinando diferentes valores de α y β que han de usarse para diferentes amplitudes.

55

Después de aplicar la rotación, es obtenida una estimación cuantificada del nivel de interferencia presente actualmente en la señal de salida de ADC. Además, como resultado de la correlación, son obtenidos valores en fase (I) y en cuadratura (Q) de la señal interferente estimada. Estos valores (I) y (Q) pueden usarse como correcciones que han de aplicarse a los valores I y Q de la señal de salida, que son obtenidos por el primer correlador (524). Por

lo tanto, el ruido de fase en la señal de salida puede reducirse restando las correcciones I y Q obtenidas de los valores I y Q originales de la señal de salida de ADC.

Tal como se muestra en la fig. 5, en la presente realización el segundo correlador (522) incluye una parte de 5 correlación (522-1) para realizar la correlación con la segunda señal de referencia (REF2), y una parte de desplazamiento de bits (522-2) para realizar una función de cambio de escala de desplazamiento de bits sobre el resultado de la correlación. La parte de desplazamiento de bits (522-2) está dispuesta para ocuparse de los resultados acumulados de la parte de correlación (522-1), y por tanto opera a una velocidad más lenta que la parte correlacionadora (522-1). La parte de desplazamiento de bits (522-2) realiza una función de cambio de escala de 10 desplazamiento de bits para compensar el crecimiento de bits después de la multiplicación por α. Igualmente, el primer correlador (524) incluye una parte de correlación (524-1) y una parte de sustracción (524-2), estando dispuesta la parte de sustracción para operar a la misma velocidad más lenta que la parte de desplazamiento de bits (522-2) del segundo correlador (522). En la presente realización las dos partes correlacionadoras (522-1), (524-1) operan a 48 MHz y la parte de desplazamiento de bits (522-2) y la parte sustractora (524-2) operan a 10 MHz, pero 15 estas frecuencias son sólo ejemplares y pueden usarse otras frecuencias.

La figura 6 es un gráfico que traza el error de retardo de fase frente a la potencia de la señal de entrada para el sistema de la fig.5, en el cual se ha reducido la anomalía de fase debida a interferencia digital-analógica. Como en la fig. 2, la fig. 6 el error de retardo de fase se mide en picosegundos (ps) y la potencia de la señal de entrada se mide en decibelios referidos a un milivatio (dBm). Se obtienen mediciones de error de retardo de fase para una señal de referencia que comprende un tono constante a 9,80 megahercios (MHz). Por comparación con la fig. 2, puede verse que el sistema de la fig. 5 puede reducir sustancialmente el error de retardo de fase incluso a bajas potencias de señal de entrada.

- 25 Haciendo referencia ahora a la fig. 7, se ilustra un procedimiento para atenuar una anomalía de fase en una señal de salida de ADC, de acuerdo con una realización de la presente invención. En la etapa (S701), se recibe una palabra de código producida por un ADC. Después, en la etapa (S702), se obtiene información acerca de un nivel estimado de interferencia entre la salida y la entrada de ADC debida a la palabra de código, basándose en los valores lógicos de bits en la palabra de código. Aquí, son posibles diversas estrategias, tal como se describe anteriormente. Por ejemplo, la información puede ser simplemente el peso de Hamming de la palabra de código o podría ser una suma de dígitos ponderada, y también podría tener en cuenta factores tales como las transiciones de bit de una palabra de código a la siguiente.

- Después, en la etapa (S703), se obtienen correcciones I y Q basándose en la información obtenida. Por ejemplo, 35 una señal de peso de Hamming puede ser correlacionada con una señal de referencia tal como se describe anteriormente con referencia a la fig. 5. Por último, en la etapa (S704), las correcciones obtenidas se aplican a los valores I y Q obtenidos de la señal de salida de ADC, para atenuar la anomalía de fase que surge debido la interferencia digital-analógica en el ADC.

- 40 Aunque la presente invención se ha descrito en relación con la medición de ángulo de fase, un experto en la materia apreciará que las realizaciones de la presente invención puede encontrar uso en general en cualquier aplicación de procesamiento de señal digital donde sea deseable atenuar el efecto de la anomalía de fase que surge debido a la interferencia digital-analógica en un ADC.

- 45 Aunque anteriormente se han descrito ciertas realizaciones de la presente invención, el experto en la materia comprenderá que son posibles muchas variaciones y modificaciones sin apartarse del ámbito de la invención tal como se define en las reivindicaciones adjuntas.

# **REIVINDICACIONES**

- 1. Un procedimiento de atenuación de una anomalía de fase en una señal de salida de convertidor analógico-digital ADC, comprendiendo el procedimiento:

- recibir una pluralidad de palabras de código producidas por el ADC; obtener, para cada una de la pluralidad de palabras de código, información acerca de un nivel estimado de interferencia entre una salida del ADC y una entrada del ADC debida a la palabra de código basándose en los valores lógicos de bits en la palabra de código;

- 10 obtener correcciones en fase I y en cuadratura Q del nivel estimado de interferencia basándose en la información obtenida; y

- aplicar las correcciones I y Q a valores I y Q obtenidos a partir de la señal de salida de ADC.

- 2. El procedimiento de acuerdo con la reivindicación 1, donde obtener información acerca del nivel 15 estimado de interferencia para cada palabra de código comprende obtener la información basándose en el peso de Hamming de la palabra de código.

- 3. El procedimiento de acuerdo con la reivindicación 1, donde obtener información acerca del nivel estimado de interferencia para cada palabra de código comprende:

- obtener una suma de dígitos ponderada de la palabra de código multiplicando cada bit de la palabra de código por un factor de ponderación predeterminado para ese bit y sumando los bits ponderados; y obtener la información acerca del nivel estimado de interferencia basándose en la suma de dígitos ponderada.

- 25 4. El procedimiento de acuerdo con una cualquiera de las reivindicaciones anteriores, donde obtener información acerca del nivel estimado de interferencia para cada palabra de código comprende además:

- comparar cada bit de la palabra de código con cada bit correspondiente de la palabra de código precedente producida por el ADC, para determinar el número de transiciones de bit 0 a 1 y el número de transiciones de bit 1 a 0 30 con respecto a la palabra de código precedente; y

- obtener la información acerca del nivel estimado de interferencia basándose en el número de transiciones de bit 0 a 1, el número de transiciones de bit 1 a 0, y el número de bits establecidos en 1 en la palabra de código actual.

- 5. El procedimiento de acuerdo con una cualquiera de las reivindicaciones precedentes, donde obtener 35 información acerca del nivel estimado de interferencia para cada palabra de código comprende además:

- almacenar información de suma de dígitos acerca del número de bits establecidos en 1 en cada una de la pluralidad de palabras de código; y

- obtener la información acerca del nivel estimado de interferencia debida a la palabra de código actual basándose en 40 la información de suma de dígitos almacenada.

- 6. El procedimiento de acuerdo con una cualquiera de las reivindicaciones precedentes, donde la información acerca del nivel estimado de interferencia para cada palabra de código comprende un valor que representa un nivel relativo de interferencia debida a la palabra de código, de modo que una pluralidad de dichos 45 valores obtenidos para la pluralidad de palabras de código define una señal interferente estimada, y

- donde la correcciones I y Q son obtenidas cambiando la escala y rotando la fase de la señal interferente estimada de acuerdo con un parámetro de cambio de escala de amplitud predeterminado y un parámetro de rotación de fase predeterminado.

- 50 7. El procedimiento de acuerdo con la reivindicación 6, que comprende además:

- correlacionar la señal de salida de ADC con una primera señal de referencia para obtener los valores I y Q a partir de la señal de salida de ADC,

- donde la rotación de fase de la señal interferente estimada comprende generar una segunda señal de referencia con 55 la fase rotada con respecto a la primera señal de referencia en un ángulo determinado por el parámetro de rotación de fase predeterminado, y correlacionar la señal interferente estimada con la segunda señal de referencia.

- 8. El procedimiento de acuerdo con la reivindicación 7, donde las correcciones I y Q son obtenidas basándose en el resultado de correlación de correlacionar la señal interferente estimada con la segunda señal de

referencia.

- 9. Aparato para atenuar una anomalía de fase en una señal de salida de convertidor analógico-digital ADC, comprendiendo el aparato:

- un medio (420; 520) para recibir una pluralidad de palabras de código producidas por el ADC y obtener, para cada una de la pluralidad de palabras de código, información acerca de un nivel estimado de interferencia entre una salida del ADC y una entrada del ADC debida a la palabra de código, basándose en los valores lógicos de bits en la palabra de código;

- 10 un medio (422; 522) para obtener correcciones en fase I y en cuadratura Q del nivel estimado de interferencia basándose en la información obtenida; y un medio (524-2) para aplicar las correcciones I y Q a los valores I y Q obtenidos a partir de la señal de salida de ADC.

- 15 10. El aparato de acuerdo con la reivindicación 9, donde el medio para obtener la información acerca de un nivel estimado de interferencia es un calculador de peso de Hamming (520).

- 11. El aparato de acuerdo con la reivindicación 9, donde el medio para obtener la información acerca de un nivel estimado de interferencia está dispuesto para obtener, para cada palabra de código, una suma de dígitos ponderada de la palabra de código multiplicando cada bit de la palabra de código por un factor de ponderación predeterminado para ese bit y sumar los bits ponderados, y obtener la información acerca del nivel estimado de interferencia basándose en la suma de dígitos ponderada.

- 12. El aparato de acuerdo con la reivindicación 9, 10 u 11, donde el medio para obtener la información acerca de un nivel estimado de interferencia está dispuesto además para comparar, para cada palabra de código, cada bit de la palabra de código con cada bit correspondiente de la palabra de código precedente producida por el ADC (416-1; 516-1), para determinar el número de transiciones de bit 0 a 1 y el número de transiciones de bit 1 a 0 con respecto a la palabra de código precedente, y obtener la información acerca del nivel estimado de interferencia basándose en el número de transiciones de bit 0 a 1, el número de transiciones de bit 1 a 0, y el número de bits 30 establecidos en 1 en la palabra de código actual.

- 13. El aparato de acuerdo con una cualquiera de las reivindicaciones 9 a 12, donde el medio para obtener la información acerca de un nivel estimado de interferencia está dispuesto además para almacenar información de suma de dígitos acerca del número de bits establecidos en 1 en cada una de la pluralidad de palabras de código, y obtener la información acerca del nivel estimado de interferencia para cada palabra de código basándose en la información de suma de dígitos almacenada.

- 14. El aparato de acuerdo con una cualquiera de las reivindicaciones 9 a 13, donde la información acerca de un nivel estimado de interferencia comprende un valor que representa un nivel relativo de interferencia debida a 40 la palabra de código, de modo que una pluralidad de dichos valores obtenidos para la pluralidad de palabras de código define una señal interferente estimada, y

donde el medio para obtener las correcciones I y Q comprende un medio para cambio de escala y un medio (522-1) para rotación de fase de la señal interferente estimada de acuerdo con un parámetro de cambio de escala de amplitud predeterminado y un parámetro de rotación de fase predeterminado.

15. El aparato de acuerdo con la reivindicación 14, que comprende:

un generador de señal de referencia (526) dispuesto para generar una primera señal de referencia (REF1) y una segunda señal de referencia (REF2) con la fase rotada con respecto a la primera señal de referencia en un ángulo 50 determinado por el parámetro de rotación de fase predeterminado; y

un primer correlador (524-1) dispuesto para correlacionar la señal de salida de ADC con la primera señal de referencia para obtener los valores I y Q a partir de la señal de salida de ADC,

donde el medio para cambio de escala y rotación de fase de la señal interferente estimada incluye un segundo 55 correlador (522-1) dispuesto para correlacionar la señal interferente estimada con la segunda señal de referencia, para aplicar la rotación de fase a la señal interferente estimada.

FIG. 1

FIG. 2

FIG. 4

FIG. 5

FIG. 6

14