# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 606 299

21) Número de solicitud: 201531213

(51) Int. Cl.:

**G06F 3/14** (2006.01) **G06F 13/00** (2006.01)

(12)

### PATENTE DE INVENCIÓN

В1

(22) Fecha de presentación:

21.08.2015

(43) Fecha de publicación de la solicitud:

23.03.2017

Fecha de concesión:

02.01.2018

(45) Fecha de publicación de la concesión:

09.01.2018

(56) Se remite a la solicitud internacional:

PCT/ES2016/070511

(73) Titular/es:

UNIVERSIDAD DE VALLADOLID (100.0%) CTT-OTRI. CASA DEL ESTUDIANTE C/ REAL DE BURGOS, S/№ 47001 VALLADOLID (Valladolid) ES

(72) Inventor/es:

HERNÁNDEZ MANGAS, Jesús Manuel y ARIAS ÁLVAREZ, Jesús

(74) Agente/Representante:

**UNGRÍA LÓPEZ, Javier**

54 Título: SISTEMA Y PROCEDIMIENTO DE GENERACIÓN DE IMÁGENES EN PANTALLAS TFT

#### (57) Resumen:

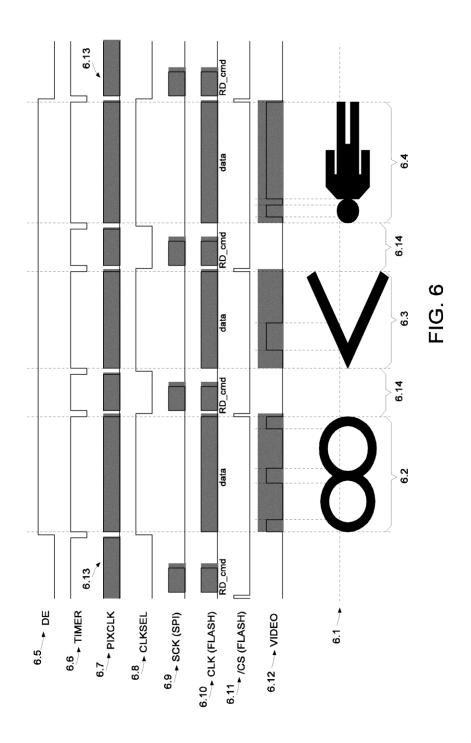

Sistema y método de generación de imágenes en pantallas TFT que comprende unas memorias flash (1.3) con interfaz serie donde se almacenan unos caracteres a ser mostrados y un microcontrolador (1.2), donde el microcontrolador (1.2) comprende un módulo temporizador (1.22) que genera una señal proporcional a una señal de reloj programable; un puerto de interfaz de periféricos serie (1.23) para gestionar las memorias flash; unos pines de entrada/salida de propósito general (1.24) para habilitar la escritura en la pantalla TFT; y donde el sistema está configurado para transmitir los caracteres almacenados en las memorias flash directamente a la pantalla TFT sin interposición de memorias RAM o de controladores TFT.

FIG. 1

# **DESCRIPCIÓN**

# SISTEMA Y PROCEDIMIENTO DE GENERACIÓN DE IMÁGENES EN PANTALLAS TFT

5

10

## **OBJETO DE LA INVENCIÓN**

La presente invención se refiere a un novedoso sistema y un procedimiento de generación de imágenes en pantallas TFT (pantalla de transistores de películas finas) en el que caracteres o figuras predeterminadas y prealmacenadas se transfieren de forma directa desde una memoria no volátil de tipo flash serie a la pantalla TFT. Preferentemente, la invención se ha previsto para pantallas TFT de bajo coste en el que las capacidades computacionales de la electrónica asociada a la pantalla son limitadas.

15

La solución aquí descrita permite utilizar microcontroladores de propósito general evitando la necesidad de integrar controladores específicos de pantallas TFT y memorias RAM internas o externas. Adicionalmente, los requisitos de memoria en el microcontrolador de propósito general son mínimos ya que se limitan a un breve conjunto de punteros en lugar de a los propios datos de vídeo relativos a las imágenes a mostrar en la pantalla TFT.

La invención se encuadra en el campo técnico de los sistemas electrónicos para la visualización de contenidos, más concretamente en el relacionado con pantallas TFT.

25

30

20

# **ANTECEDENTES DE LA INVENCIÓN**

Las pantallas y paneles indicadores electrónicos convencionales de bajo coste suelen estar basados en dispositivos LCD (*Pantallas de cristal líquido*) segmentados de tipo pasivo que no incluyen ninguna electrónica integrada y donde sus terminales se conectan directamente a los electrodos del LCD. La electrónica de control de la propia pantalla LCD es de bajo coste ya que la memoria de vídeo que incorpora se limita a un bit por segmento. Este tipo de pantallas presentan una serie de inconvenientes entre los que están:

- Mala estética: los caracteres alfanuméricos tienen formas artificiosas dado que se descomponen en un conjunto común de segmentos poligonales. La separación entre los segmentos es claramente visible.

- Mal contraste: cuando el número de segmentos es elevado (>40) se recurre a su multiplexado mediante el uso de dos o más backplanes lo que reduce el contraste y puede requerir un ajuste manual mediante potenciómetros.

10

15

20

25

30

Imagen monocroma: los problemas de contraste excluyen la posibilidad de representar imágenes de colores variables. Mediante técnicas como el LCD de campo secuencial consistente en cambiar el color de la retroiluminación del LCD de forma sincronizada con el refresco de los segmentos se consiguen simular hasta 16 colores (US7502004 B2, CN1680994 A, US7557787 B2).

Otra tecnología de visualización son las pantallas TFT (US8937691 B2) en las que a cada segmento (pixel) se puede aplicar una tensión concreta de forma individual gracias a la electrónica de conmutación incluida en la propia pantalla basada en transistores MOSFET de silicio amorfo, que dan nombre a esta tecnología. Este tipo de pantallas presentan una calidad de imagen muy superior a las pantallas LCD. Los píxeles son de tamaños inferiores al milímetro con tres componentes de color, rojo, verde y azul, que pueden elegirse entre una paleta de al menos 64 niveles de forma individual para cada pixel, y con resoluciones que rondan el millón de píxeles incluso para pantallas de dimensiones reducidas. Además tienen un coste bastante reducido.

Sin embargo, estas pantallas TFT requieren una electrónica de control (interna o externa al microcontrolador) que permita el almacenamiento de datos (memoria RAM interna o externa) y que genere un refresco de datos periódico hacia la pantalla TFT. Los documentos WO2003021566 A1, CN204178686 U y CN102945658 A describen diversos controladores de TFT. La tecnología TFT implica que incluso en pantallas pequeñas el volumen de datos a transferir sea considerable. Por ejemplo, en una pantalla de 480x272 pixeles, se necesitan 391.680 bytes que se deben transferir a la pantalla al menos cada 20 milisegundos para evitar parpadeos en la imagen. Estas cantidades de memoria superan ampliamente la capacidad de las memorias internas de los microcontroladores de propósito general actuales, lo que obliga a incorporar en las pantallas TFT controladores para memorias dinámicas externas además de periféricos de interfaz (controladores TFT) para la pantalla que se encargue del

refresco periódico de la misma.

Los sistemas de generación de imágenes para pantallas TFT convencionales cambian la imagen visualizada de forma indirecta: primero escriben en el área de memoria RAM de video destinada al refresco del video, y después el controlador TFT (periférico de interfaz) transferirá esos datos a la pantalla en los sucesivos ciclos de refresco. El carácter gráfico de las imágenes representadas se traduce en un notable volumen de datos que hay que modificar en la memoria RAM de video cuando se cambian áreas grandes de la imagen, lo que resulta en una respuesta lenta ante los cambios. Este aspecto no suele ser relevante en los equipos informáticos de sobremesa pues disponen de grandes anchos de banda en sus memorias y mucha potencia de cálculo. Pero en los microcontroladores que integran este tipo de pantallas TFT para aplicaciones específicas, como por ejemplo los indicadores de posición en ascensores, paneles indicadores de carretera, etc, estos recursos suelen estar mucho más limitados. Con procesadores como el LPC2478, con frecuencia de reloj inferior a los 100MHz, memorias RAM y/o Flash internas por debajo del Mbyte y DRAM externa de 32 o 16 bit de anchura de datos, los cambios en la memoria de vídeo suelen superar ampliamente la duración de un ciclo de refresco de la pantalla, creando una sensación visual de falsa persistencia de la imagen.

20

25

5

10

15

También conviene destacar que en las pantallas y paneles indicadores electrónicos convencionales de bajo coste, las imágenes que se muestran no son por lo general arbitrarias sino combinaciones de figuras predefinidas tales como caracteres alfanuméricos de diversos tamaños e iconos fijos. Estos elementos han de almacenarse en la memoria no volátil del sistema desde la que se transfieren a la memoria RAM de vídeo cuando se desean representar en la pantalla, de modo que se tiene la misma información ocupando espacio en dos memorias distintas.

30

Por tanto, el problema técnico que se plantea es la visualización en pantallas TFT de caracteres o figuras predeterminadas mediante un sistema de generación de imágenes que implique una reducción de componentes y por tanto de coste económico y una reducción de la potencia de cálculo necesaria para hacerlo, con respecto a las soluciones actualmente existentes.

# **DESCRIPCIÓN DE LA INVENCIÓN**

Con el objeto de solventar los problemas expuestos anteriormente, la presente invención describe un sistema y un procedimiento de generación de imágenes en pantallas TFT en el que figuras predeterminadas y previamente almacenadas en memorias no volátiles de tipo flash serie se transfieren de forma directa a la pantalla TFT. Esto permite utilizar microcontroladores de propósito general sin controlador de TFT ni memorias RAM internas o externas.

5

25

- Así, un primer objeto de la presente invención es un sistema de generación de imágenes en pantallas TFT que comprende una pantalla TFT, al menos una memoria flash con interfaz serie donde se almacenan unos caracteres a ser mostrados en la pantalla TFT y un microcontrolador. Dependiendo del tipo de caracteres que se vayan a mostrar o de las necesidades de color de los mismos, se hará necesario una única o varias memorias flash conectadas en paralelo para almacenar los diferentes caracteres que se vayan a mostrar. Nótese que a lo largo del presente documento cuando se dice "caracteres" se refiere a imágenes, letras, números, iconos o figuras predefinidas, que pueden tener tamaños y formas muy dispares. La capacidad de las memorias flash determinará la forma, tamaño y cantidad de caracteres que se almacenen. Estas memorias flash con interfaz serie son memorias externas a la pantalla TFT y al microcontrolador. El microcontrolador comprende:

- un módulo temporizador configurado para generar una señal de anchura proporcional a un número de ciclos de una señal de reloj. El número de ciclos de la señal de reloj será programable dependiendo de las particularidades de la pantalla TFT y de la electrónica asociada así como del tipo de carácter que vaya a mostrarse. Cada ciclo de esta señal generada por el módulo temporizador se corresponde a un pixel de la pantalla TFT. Además la señal de reloj será síncrona con el reloj interno del microcontrolador. Esta señal controlará el número de ciclos de reloj que se aplica a las memorias flash durante la lectura de datos:

- un puerto de interfaz de periféricos serie configurado para gestionar la al menos una memoria flash. Este puerto generará las señales que habilitarán la lectura en las memorias flash;

- unos pines de entrada/salida de propósito general configurados para habilitar la escritura en la pantalla TFT. También estarán configurados para gestionar la

selección de las memorias flash serie, el multiplexado de la señal de reloj de las memorias flash serie, y la selección del color de la imagen en las realizaciones con una profundidad de color de 1 bit por pixel;

donde el sistema adicionalmente comprende unos medios de generación de una señal de entrada de reloj de la pantalla TFT a partir de la señal generada por el módulo temporizador y de la señal de reloj y un conmutador que selecciona una señal de reloj de la al menos una memoria flash entre la señal de entrada del reloj de la pantalla TFT y una señal de reloj del puerto de interfaz de periféricos serie, de manera que los caracteres en la al menos una memoria flash se transmiten directamente a la pantalla TFT.

Dado que se emplean microcontroladores de propósito general (no específicamente diseñados para la gestión de pantallas TFT) se carece también de un periférico de interfaz TFT específico. Esto implica la necesidad de generar las señales de control tanto de la pantalla TFT como de las memorias flash mediante el microcontrolador empleando los periféricos habituales integrados en los mismos: temporizadores y puertos serie síncronos que ayudan a reducir la carga computacional en la CPU del microcontrolador, dejando aún un porcentaje apreciable del tiempo de CPU disponible para ejecutar el código principal de la aplicación.

20

5

10

15

En una realización particular de la invención, el sistema comprende un reloj interno para la generación de la señal de reloj. Este reloj interno proporciona, generalmente, una onda cuadrada de frecuencia fija. Esta señal también puede ser proporcionada desde un reloj externo al sistema.

25

En otra realización particular de la invención, el módulo temporizador comprende tener una salida activa seleccionada entre una salida por comparación y una salida con modulación por ancho de pulsos por donde se genera la señal de anchura proporcional a la señal de reloj.

30

En otra realización particular de la invención, la al menos una única memoria flash con interfaz serie es una memoria de interfaz periférica (SPI) conectada en serie al microcontrolador.

En otra realización particular de la invención, la al menos una memoria flash con interfaz serie es una memoria de interfaz serial cuádruple (SQI, "Serial Quad Interface"), que es capaz de leer 4 bits de datos por cada ciclo de reloj.

5 En otra realización particular de la invención, la al menos una memoria flash con interfaz serie del sistema son dos memorias de interfaz serial cuádruple (SQI) conectadas en paralelo.

En otra realización particular de la invención, el sistema comprende un módulo de asignación de color conectado a la al menos una memoria flash para asignar colores a los caracteres mostrados en la pantalla TFT.

En otra realización particular de la invención, para el caso de disponer de una única memoria de interfaz periférica (SPI) conectada en serie al microcontrolador, el módulo de asignación de color comprende 4 puertas AND. Cada una de las puertas AND tiene una primera entrada común conectada a una salida de vídeo de la memoria SPI en serie y adicionalmente una segunda entrada. Cada segunda entrada de cada puerta AND está conectada, respectivamente, a uno de los pines de entrada/salida de propósito general, de forma que el módulo de asignación de color está configurado para generar caracteres monocromos con fondo negro.

15

20

25

30

En otra realización particular de la invención, para el caso de disponer de una única memoria de interfaz periférica (SPI) conectada en serie al microcontrolador, el módulo de asignación de color comprende un multiplexor cuádruple con una entrada conectada a una salida de video de la memoria SPI, 4 primeras entradas conectadas respectivamente a 4 pines de entrada/salida de propósito general para asignar un color a cada carácter y 4 segundas entradas conectadas respectivamente a 4 pines de entrada/salida de propósito general para asignar un color a un fondo. De este modo, el módulo de asignación de color está configurado para generar caracteres monocromos con fondo monocromo.

En otra realización particular de la invención, cuando se dispone de una única memoria SQI, dicha memoria tiene 4 salidas de video conectadas directamente a unas entradas de video de la pantalla TFT de forma que el sistema está configurado para

generar caracteres con profundidades de color de 4 bits por pixel.

5

10

15

20

25

30

En otra realización particular de la invención, cuando se dispone de dos memorias SQI conectadas en paralelo, cada memoria tiene 4 salidas de video conectadas directamente a unas entradas de video de la pantalla TFT, estando el sistema configurado para generar caracteres con profundidades de color de 8 bits por pixel.

Opcionalmente, también se ha previsto la interconexión de más de dos memorias SQI en paralelo para aumentar la profundidad de color de la imagen generada, aunque profundidades de 8 bits por pixel proporcionan una calidad de imagen en fotografías más que aceptable (los caracteres podrían ser fotos).

Un segundo objeto de la presente invención es un procedimiento de generación de imágenes en pantallas TFT que hace uso del sistema descrito anteriormente. Dicho procedimiento comprende las siguientes etapas:

- generar en el módulo temporizador una señal de anchura proporcional a un número programable de ciclos de una señal reloj;

- activar un modo escritura de la pantalla TFT mediante uno de los pines de entrada salida de propósito general del microcontrolador durante una duración de una parte visible de una línea de caracteres;

- generar una señal de entrada de reloj de la pantalla TFT a partir de la señal generada por el módulo temporizador y de la señal de reloj;

- -seleccionar mediante un conmutador una señal entre la señal de entrada del reloj de la pantalla TFT y una señal de reloj del puerto de interfaz de periféricos serie, donde la señal seleccionada es la señal de entrada de reloj de la al menos una memoria flash; y,

- enviar desde la al menos una memoria flash un carácter de la línea de caracteres directamente a la pantalla TFT cuando el conmutador seleccione la señal de entrada de reloj de la pantalla TFT y la señal de entrada de reloj de la pantalla TFT esté activa.

En una realización particular, el método además asigna color a los caracteres mostrados en la pantalla TFT mediante el módulo de asignación de color.

En otra realización particular, el método envía un número de pulsos de reloj entre dos ciclos activos de la señal de entrada de reloj de la pantalla TFT para marcar un comienzo de una nueva línea de caracteres.

5 En otra realización particular, cuando el conmutador selecciona la señal de reloj del puerto de interfaz de periféricos serie, el procedimiento comprende enviar comandos de lectura a la al menos una memoria flash.

Así, la solución aquí descrita presenta las siguientes ventajas con respecto a otras soluciones existentes:

- los requisitos de memoria en el microcontrolador son mínimos pues se limitan a un breve conjunto de punteros en lugar de a los propios datos de vídeo. El cambio en el valor de dichos punteros se traducirá inmediatamente en la representación de una imagen distinta, sin que transcurra más tiempo que el de un único ciclo de refresco:

15

20

30

- no se hace necesaria la existencia de un controlador específico de la pantalla

TFT ni de memorias RAM internas ni externas lo que simplifica la implementación del sistema reduciendo el número de componentes y por ende de su coste económico;

- la transmisión de los caracteres desde las memorias flash hasta la pantalla TFT se hace de forma directa desde la salida de video de las memorias hacia las entradas de video la pantalla (entradas RGB) o mediante la interposición de puertas lógicas o multiplexores muy simples, lo que reduce muy significativamente las necesidades de memoria del sistema; y,

- se evitan duplicidades de memorias al no hacerse necesario incluir memorias 25 RAM.

#### **BREVE DESCRIPCIÓN DE LAS FIGURAS**

Para complementar la descripción que se está realizando y con objeto de ayudar a una mejor comprensión de las características de la invención, se acompaña como parte integrante de dicha descripción, un juego de dibujos en donde con carácter ilustrativo y no limitativo, se ha representado lo siguiente:

Figura 1.- Muestra el diagrama de bloques de un ejemplo de realización del sistema de

generación de imágenes en pantallas TFT.

5

10

15

20

25

30

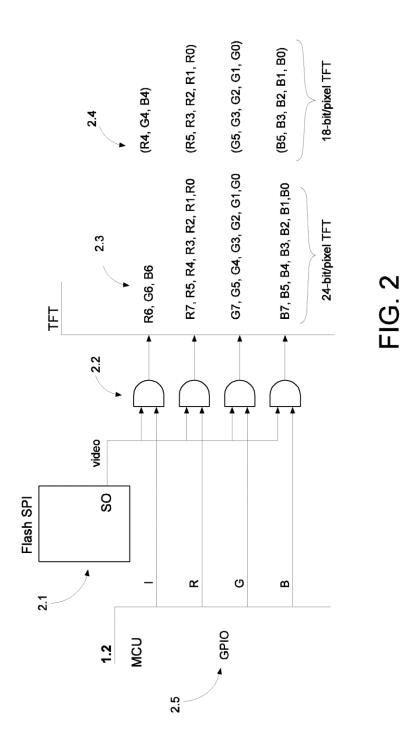

Figura 2.- Muestra el diagrama de bloques de un ejemplo de realización del módulo de asignación de color para la representación de caracteres con una profundidad de 1 bit por pixel, con 16 colores posibles para el primer plano y fondo negro.

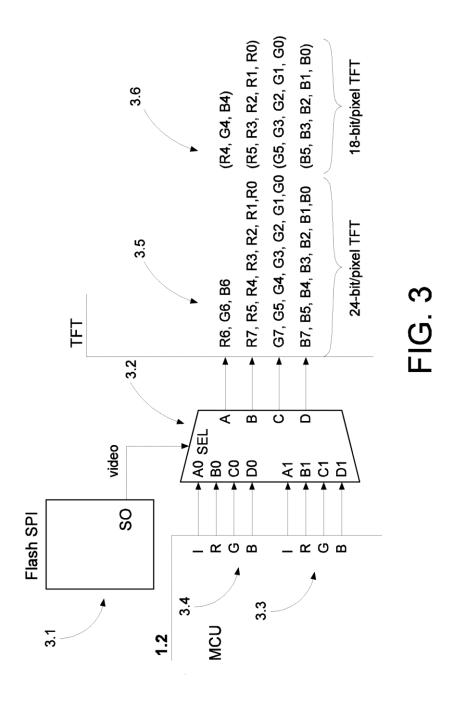

Figura 3.- Muestra el diagrama de bloques de un ejemplo de realización del módulo de asignación de color para la representación de caracteres con una profundidad de 1 bit por pixel, 16 colores posibles para el primer plano y fondo de color seleccionable entre 16 colores.

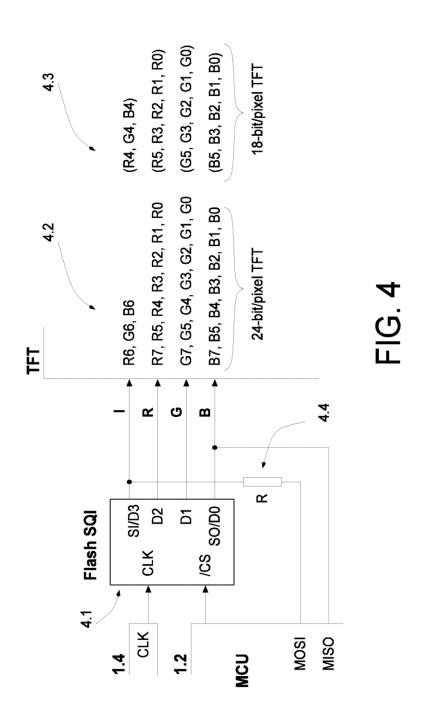

Figura 4.- Muestra el diagrama de bloques de un ejemplo de realización del módulo de asignación de color para la representación de caracteres con una profundidad de 4 bits por pixel. La memoria flash tiene una interfaz de entrada/salida serial cuádruple (SQI) con un ancho de datos seleccionable por comando de 1 o 4 bits.

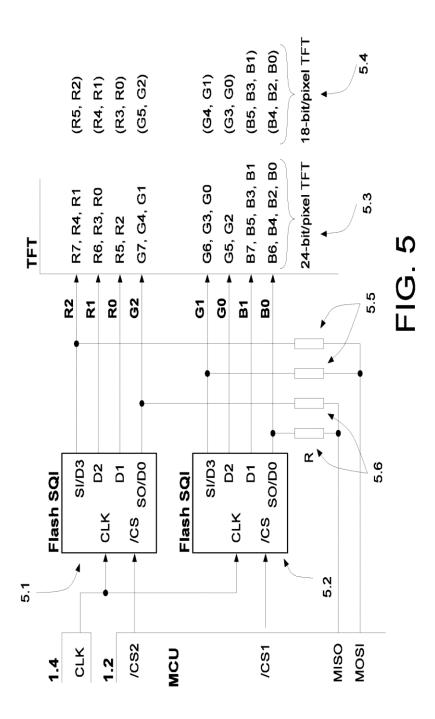

Figura 5.- Muestra el diagrama de bloques de un ejemplo de realización del módulo de asignación de color para una profundidad de 8 bit por pixel. Las dos memorias flash tienen una interfaz de entrada/salida serial cuádruple (SQI) con un ancho de datos seleccionable por comando de 1 o 4 bits.

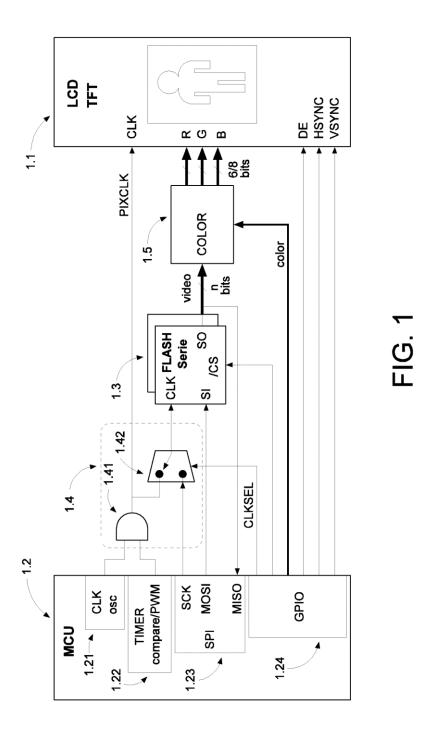

Figura 6.- Muestra un cronograma de un ejemplo de realización del proceso de generación de imágenes en una pantalla TFT mostrando la forma de las distintas señales de control generadas para la transmisión de una línea de video desde las memorias flash hasta la pantalla TFT.

#### DESCRIPCIÓN DE VARIOS EJEMPLOS DE REALIZACIÓN DE LA INVENCIÓN

Seguidamente se realiza, con carácter ilustrativo y no limitativo, una descripción de varios ejemplos de realización de la invención, haciendo referencia a la numeración adoptada en las figuras.

La figura 1 es el diagrama de bloques de un ejemplo de realización del sistema de generación de imágenes en pantallas TFT en el que se muestran los principales

componentes del citado sistema y el modo en que se conectan entre sí. Dichos componentes son: la pantalla TFT (1.1), el microcontrolador (1.2) de propósito general, los periféricos integrados (1.21-1.24) en el microcontrolador (1.2), una pluralidad de memorias Flash serie (1.3) con la información gráfica (caracteres) almacenada, la lógica de generación de reloj (1.4) para la generación de las señales de reloj de la pantalla (1.1) y de las memorias (1.3) y la lógica de generación del color (1.5) que dependerá de la profundidad de color deseada. A su vez, los periféricos integrados en el microcontrolador son: un generador de reloj (1.21), un temporizador (1.22), un puerto serie SPI (1.23) y pines de entrada y salida de propósito general GPIO (1.24).

10

15

20

25

5

De manera más específica, el sistema de la figura 1 muestra la pantalla TFT (1.1) con sus señales de interfaz típicas. Las pantallas TFT son dispositivos síncronos, con una entrada de reloj (CLK) por la que se recibe una señal de reloj (PIXCLK) que gobierna su máquina de estados interna. No es por lo tanto necesario seguir una temporización rigurosa durante el refresco de la pantalla, siempre y cuando el cómputo total de pulsos de reloj sea correcto y el tiempo total del refresco no sea demasiado grande y de lugar a parpadeo. Además las pantallas TFT disponen de una entrada de validación de datos (DE) y dos entradas de sincronismo, horizontal (HSYNC) y vertical (VSYNC), si bien en muchos casos estas dos últimas señales son opcionales ya que se generan internamente a partir de la señal DE. Estas entradas DE, HSYNC y VSYNC se controlan desde los pines de entrada y salida de propósito general GPIO (1.24). El resto de entradas de la pantalla TFT (1.1) son las entradas de video de la pantalla correspondientes a los bits con el nivel de cada componente de color (R: rojo, G: verde, B: azul) codificado como un número binario de 8 o de 6 bits. El ancho de bit dependerá del modelo concreto de pantalla TFT (1.1). Dichas entradas RGB se conectarán directamente a las salidas específicas de las propias memorias flash serie (1.3) o bien por interposición de puertas lógicas, multiplexores o demultiplexores, entre otros, que conforman la lógica de generación del color (1.5).

30

El otro componente básico del sistema es el microcontrolador (1.2), del que sólo se han representado los subsistemas implicados en la generación de las imágenes hacia la pantalla TFT (1.1), pero que dispondría de subsistemas adicionales para la gestión de otros aspectos relacionados con el control de la pantalla TFT como por ejemplo interfaces de comunicación serie (CAN/LIN/RS485/USB,...) o temporizadores para la

10

15

20

25

30

generación de señales acústicas, etc. En esta realización particular, el microcontrolador dispone de los siguientes periféricos:

- un generador de reloj (1.21) que permita obtener en un pin una señal cuadrada (CLKosc) de una frecuencia compatible con la pantalla, (en el orden de las decenas de megahercios, proporcional con el número total de pixeles de la pantalla). Muchos microcontroladores modernos generan su señal de reloj internamente y pueden dirigirla a un pin si se configuran adecuadamente. Si el microcontrolador no dispusiera de un generador de reloj interno aún se puede generar dicha señal de reloj externamente y aplicarla tanto a la lógica de generación de reloj (1.4) como al propio microcontrolador (1.2).

- un modulo temporizador (1.22) con al menos una salida activa por comparación o con modo PWM ("Modulación por ancho de pulsos"). Este periférico se usará para generar un pulso correspondiente a un número programable de ciclos de la señal cuadrada del generador de reloj (CLKosc). Se realiza una función de tipo AND lógico, mediante una puerta AND (1.41), entre este pulso y la señal de reloj (CLKosc), obteniendo con ello un tren de un número preciso de pulsos en la entrada de reloj de la pantalla (PIXCLK). Si la señal DE está activa cada uno de estos pulsos introducirá los datos de un pixel en la pantalla, mientras que si DE está inactiva los pulsos se corresponden con los tiempos de retrazado horizontal o vertical de la pantalla.

- una o varias memorias Flash con interfaz serie (1.3). El tipo, número, y capacidad de dichas memorias va a depender de la profundidad de color de las imágenes generadas así como de la cantidad total de objetos gráficos que deben almacenar y de sus respectivos tamaños en pixeles. Para los tipos de aplicaciones previstas se ha considerado unas profundidades de color de 1, 4 u 8 bits por pixel (aunque se podrían conseguir mayor profundidades de color conectando más memorias SQI en paralelo, por ejemplo con 3 memorias SQI se conseguirían profundidades de 12 bits por pixel):

- o en el caso de 1 bit/pixel se hace uso de una única memoria de tipo SPI;

- en el caso de 4 bits por pixel la memoria ha de ser SQI para poder obtener de forma simultánea los 4 bits con la información de color del pixel; y,

- en el caso de 8 bits por pixel se usan dos memorias de tipo SQI conectadas en paralelo.

Todas estas memorias tienen la característica de poder presentar un nuevo

25

30

dato en la salida e incrementar su contador de direcciones de forma automática por cada pulso de reloj que reciben (cada pulso positivo de la señal PIXCLK), necesitando tan solo de un comando inicial proveniente del puerto serie SPI (1.23) que indique la operación de lectura (ciclo activo de la señal MOSI) y la dirección inicial de la memoria a partir de la cual se leerán los datos. Otro aspecto destacado de este tipo de memorias es que sus terminales son siempre los mismos, independientemente de su capacidad, lo que permite elegir el dispositivo que mejor se ajuste a las necesidades de la aplicación sin necesidad de rediseñar la electrónica del sistema.

- 10 una lógica de generación de reloj (1.4) que comprende un conmutador (1.42) para seleccionar la señal de reloj de entrada de las memorias Flash (1.3) entre la señal SCK proveniente de puerto serie SPI (1.23) y la señal PIXCLK correspondiente a la señal de reloj de la pantalla TFT previamente generada en la puerta AND (1.41). La señal SCK se seleccionará mientras se envían a la 15 memoria los comandos de lectura a través del puerto serie SPI (1.23), pasando a continuación a seleccionarse la señal PIXCLK para el envío de los caracteres a la pantalla (1.1) a través de las correspondientes salidas de video de las memorias flash (1.3). De este modo, una vez iniciada la lectura de la memora Flash los datos pasan de forma automática a la pantalla sin necesidad de 20 intervención directa desde la CPU del microcontrolador. La señal SCK también deberá seleccionarse cuando se programe el contenido de las memorias flash desde el microcontrolador o cuando se lean datos de la memoria que sean relevantes para el microcontrolador pero no para la generación de imágenes.

- Un bloque de lógica relacionado con la generación de color (1.5) Este bloque depende de la profundidad de color deseada, pudiendo tener las siguientes implementaciones:

- Profundidad de color de 1 bit por pixel y color de fondo negro. La figura 2 muestra una implementación particular de este bloque de asignación de color (1.5) para esta profundidad de color. Esta es la implementación más básica del bloque (1.5) y tan solo requiere de 4 puertas AND (2.2), de modo que el pixel tendrá el color seleccionado mediante los 4 pines I, R, G, y B de salida de propósito general GPIO (2.5) cuando desde la salida de video (SO) de la memoria flash SPI (2.1) salga un nivel lógico de 1, o color negro en caso contrario. Obsérvese que aunque las imágenes almacenadas en la

memoria flash son monocromas, su color se puede variar dependiendo de su posición en la pantalla, de modo que podemos visualizar simultáneamente hasta 16 colores distintos. Según la pantalla TFT elegida el conexionado será (2.3) para una TFT con una resolución de 24 bit/pixel o (2.4) para un TFT con una resolución de 18 bit/pixel. Así en una realización particular (se pueden elegir conexionados diferentes que den como resultado paletas de colores distintas) para la generación de imágenes con una profundidad de color de 1 bit por pixel y color de fondo negro, los colores obtenidos pueden ser:

| 10 |      |                 |

|----|------|-----------------|

|    | IRGB | COLOR           |

|    |      |                 |

|    | 0000 | Negro           |

|    | 0001 | Azul oscuro     |

| 15 | 0010 | Verde oscuro    |

|    | 0011 | Cyan oscuro     |

|    | 0100 | Rojo oscuro     |

|    | 0101 | Magenta oscuro  |

|    | 0110 | Amarillo oscuro |

| 20 | 0111 | Gris claro      |

|    | 1000 | Gris oscuro     |

|    | 1001 | Azul claro      |

|    | 1010 | Verde claro     |

|    | 1011 | Cyan claro      |

| 25 | 1100 | Rojo claro      |

|    | 1101 | Magenta claro   |

|    | 1110 | Amarillo claro  |

|    | 1111 | Blanco          |

|    |      |                 |

Profundidad de color de 1 bit por pixel y color de fondo seleccionable. La figura 3 muestra una implementación particular de este bloque de asignación de color (1.5) para esta profundidad de color. En este caso se emplea un multiplexor cuádruple (3.2), 4 pines I, R, G, y B de salida de propósito general GPIO (3.3) para la asignación del color de los caracteres de primer plano y otros 4 pines I, R, G, y B de salida de propósito general GPIO (3.4) para la asignación del color de fondo. Según la pantalla TFT elegida el

10

15

20

25

30

conexionado será (3.5) para una TFT con una resolución de 24 bit/pixel o (3.6) para una TFT con una resolución de 18 bit/pixel.

- Profundidad de color de 4 bits por pixel. La figura 4 muestra una implementación particular de este bloque de asignación de color (1.5) para esta profundidad de color. En este caso los datos de video provienen de una memoria de tipo SQI (4.1) y son de 4 bits, de modo que se pueden conectar directamente a las entradas de video de la pantalla TFT. Según la pantalla TFT elegida el conexionado será (4.2) para un TFT con una resolución de 24 bit/pixel o (4.3) para un TFT con una resolución de 18 bit/pixel. Se requiere una resistencia (4.4) conectada entre la salida MOSI del microcontrolador y la salida SI de la memoria (4.1) ya que al pasar la memoria SQI (4.1) al modo de 4 bits el pin SI deja de ser de entrada para ser de salida, lo que provocaría un conflicto con la salida MOSI del microcontrolador. En esta implementación cada pixel puede tener hasta 16 colores diferentes.

- o Profundidad de color de 8 bits por pixel. La figura 5 muestra una implementación particular de este bloque de asignación de color (1.5) para esta profundidad de color. En este caso se emplean dos memorias Flash SQI (5.1 y 5.2) conectadas en paralelo que proporcionan un total de 8 bits por pixel cuya señal de reloj procede de la lógica de reloj (1.4) descrita anteriormente. La asignación de colores responde a un modo RGB332 (con 3 bits para las componentes roja (R0, R1, R2) y verde (G0, G1, G2) y 2 bits para la componente azul (B0, B1)). Cada pixel puede tener 256 colores diferentes. Las resistencias (5.5) conectadas entre la salida MOSI del micro controlador y las entradas SI de las memorias (4.1) son necesarias para mitigar los posibles conflictos lógicos entre los pines de salida SI/D3 de ambas memorias durante la fase de lectura de datos de 4 bits (función D3), así como con el pin MOSI del microcontrolador. De igual modo las resistencias (5.6) entre la entrada MISO y las salidas SO de las memorias (4.1) son necesarias para mitigar los posibles conflictos lógicos entre los pines de salida SO/D0 de ambas memorias durante la fase de lectura de datos de 4 bits (función D0). Según la pantalla TFT elegida el conexionado podría ser (5.3) para una TFT con una resolución de 24 bit/pixel o (5.4) para una TFT con una resolución de 18 bit/pixel.

10

15

20

25

30

La figura 6 muestra un ejemplo de realización de un cronograma con las señales de control que se implementan para la generación de las imágenes en las pantallas TFT. Este ejemplo de realización muestra el cronograma temporal correspondiente al refresco de una única línea (6.1) en una pantalla TFT del tipo "sólo DE, sin HSYNC ni VSYNC". Dicha línea (6.1) comprende el envío de 3 caracteres ("∞" (6.2), "<" (6.3), v un icono representando un hombre (6.4)) de las memorias flash serie donde se almacenan a la pantalla TFT. En primer lugar, la señal DE (6.5) generada por uno de los pines de salida GPIO (1.24) se activa durante la duración de la parte visible de la línea para habilitar la escritura en la pantalla TFT. Simultáneamente el módulo temporizador genera la señal TIMER (6.6) correspondiente la anchura de un número programable de ciclos de la señal de reloj. Así, una vez el conmutador selecciona como entrada de reloj de las memorias flash serie la señal PIXCLK (6.7) se procede al envío de los caracteres (6.2, 6.3, 6.4) de la línea (6.1), enviándose un carácter por cada ciclo alto de la señal CLKSEL (6.8). Cada uno de los ciclos altos de la señal PIXCLK (6.7) comprende una pluralidad de pulsos, de manera que en cada pulso se transmite un pixel de los caracteres (6.2, 6.3, 6.4) de la línea (6.1) que se van a mostrar por pantalla.

El reloj del puerto SPI se emplea para enviar comandos de lectura a la memoria Flash, lo que supone enviar un total de 32 o 40 pulsos de reloj con el byte de comando, 3 bytes de dirección y un posible byte de relleno. PIXCLK (6.7) se utiliza en la posterior fase de lectura de datos, de forma que el contenido de la memoria Flash se transfiere a la pantalla de forma directa, sin la intervención de la CPU del microcontrolador. Por lo tanto, a cada envío de un carácter (6.2, 6.3, 6.4) desde las memorias a la pantalla le precede un tren de pulsos de la señal de reloj SCK (6.9) del puerto serie SPI para el comando de lectura del carácter a enviar, por lo que el conmutador seleccionara una señal entre PIXCLK (6.7) y SCK (SPI) (6.9) de forma alterna para primero enviar el comando de lectura del carácter (RD-cmd) y luego enviar los datos (data) del carácter a la pantalla. De este modo se obtiene la señal de reloj compuesta, CLK (FLASH) (6.10), en la entrada de reloj de las memorias Flash.

Adicionalmente, el sistema envía, entre cada dos líneas, un cierto número de pulsos de reloj (6.13), dependiente del modelo de pantalla, que señalizan el comienzo de una nueva línea. Un número mayor de pulsos con la señal DE en bajo señalizaría el

comienzo del cuadro de imagen o retrazado vertical (no representado en la Fig. 6).

5

10

15

El número total de pulsos de reloj generados en la señal PIXCLK (6.7) se controla mediante la salida del temporizador TIMER (6.6), mientras que CLKSEL (6.8) indica si a la memoria Flash llega la señal de reloj SCK del puerto SPI (6.9) o la señal PIXCLK (6.7). También conviene destacar que las señales PIXCLK (6.7) y SCK (SPI) (6.9) se pueden generar simultáneamente si la señal CLKSEL (6.8) está inactiva, lo que puede resultar de utilidad para reducir los tiempos muertos de PIXCLK y así aumentar la frecuencia de refresco de la pantalla. En particular esta posibilidad se puede aprovechar en los tiempos de retrazado o si en la imagen tenemos huecos grandes (6.14) entre los caracteres (6.2, 6.3, 6.4).

Las memorias Flash tienen una entrada adicional, /CS (6.11), que debe estar en nivel bajo durante la ejecución de los comandos de lectura del carácter (RD-cmd) los comandos de envío de datos (data) de la señal CLK (6.10) y en la que un flanco de bajada señaliza el primer bit de los citados comandos. En la Fig. 6 se muestra la evolución temporal de dicha señal, que sólo se pone en nivel alto de forma breve antes del envío de un nuevo comando de lectura a las memorias Flash.

La señal VIDEO (6.12) se obtiene en las salidas de las memorias Flash, y en el ejemplo de la Fig. 6 es de un solo bit, lo que generará imágenes monocromas (bloques de generación de color como los mostrados en las Fig. 2 o Fig. 3). La señal de VIDEO (6.12) puede tener un valor arbitrario durante la lectura de los caracteres, acorde con los datos programados en las memorias Flash, si bien en la Fig. 6 se muestra superpuesta la traza correspondiente a la línea de vídeo (6.1) particular de este ejemplo.

#### **REIVINDICACIONES**

- 1. Sistema de generación de imágenes en pantallas TFT, caracterizado porque comprende una pantalla TFT, al menos una memoria flash con interfaz serie donde se almacenan unos caracteres a ser mostrados en la pantalla TFT y un microcontrolador, donde el microcontrolador comprende:

- un módulo temporizador configurado para generar una señal proporcional a un número programable de ciclos de una señal de reloj;

- -un puerto de interfaz de periféricos serie configurado para gestionar la al

10 menos una memoria flash;

- unos pines de entrada/salida de propósito general configurados para habilitar una escritura en la pantalla TFT;

donde el sistema adicionalmente comprende unos medios de generación de una señal de entrada de reloj de la pantalla TFT a partir de la señal generada por el módulo temporizador y de la señal de reloj y un conmutador que selecciona una señal de reloj de la al menos una memoria flash entre la señal de entrada del reloj de la pantalla TFT y una señal de reloj del puerto de interfaz de periféricos serie, de manera que los caracteres en la al menos una memoria flash se transmiten directamente a la pantalla TFT.

20

30

15

- 2. Sistema de generación de imágenes en pantallas TFT, según la reivindicación 1, que comprende un reloj interno para la generación de la señal de reloj.

- 3.- Sistema de generación de imágenes en pantallas TFT, según la reivindicación 1,

donde el módulo temporizador comprende una salida activa seleccionada entre una salida por comparación y una salida con modulación por ancho de pulsos.

- 4.- Sistema de generación de imágenes en pantallas TFT, según la reivindicación 1, donde la al menos una memoria flash con interfaz serie es una memoria de interfaz periférica en serie.

- 5.- Sistema de generación de imágenes en pantallas TFT, según la reivindicación 1, donde la al menos una memoria flash con interfaz serie es una memoria de entrada/salida serial cuádruple.

- 6.- Sistema de generación de imágenes en pantallas TFT, según la reivindicación 1, donde la al menos una memoria flash con interfaz serie son dos memorias de entrada/salida serial cuádruple conectadas en paralelo.

- 7.- Sistema de generación de imágenes en pantallas TFT, según una cualquiera de las reivindicaciones anteriores, que comprende un módulo de asignación de color conectado a la al menos una memoria flash para asignar colores a los caracteres mostrados en la pantalla TFT.

- 8.- Sistema de generación de imágenes en pantallas TFT, según las reivindicaciones 4 y 7, donde el módulo de asignación de color comprende 4 puertas AND, cada puerta AND teniendo una primera entrada común conectada a una salida de vídeo de la memoria de interfaz periférica en serie y una segunda entrada, donde la segunda entrada de cada puerta AND está conectada, respectivamente, a uno de los pines de entrada/salida de propósito general, de forma que el módulo de asignación de color está configurado para generar caracteres monocromos con fondo negro.

- 9.- Sistema de generación de imágenes en pantallas TFT, según las reivindicaciones 4 y 7, donde el módulo de asignación de color comprende un multiplexor cuádruple con una entrada conectada a una salida de video de la memoria de interfaz periférica en serie, 4 primeras entradas conectadas respectivamente a 4 pines de entrada/salida de propósito general para asignar un color a cada carácter y 4 segundas entradas conectadas respectivamente a 4 pines de entrada/salida de propósito general para asignar un color a un fondo, de forma que el módulo de asignación de color está configurado para generar caracteres monocromos con fondo monocromo.

25

- 10.- Sistema de generación de imágenes en pantallas TFT, según la reivindicación 5, donde la una memoria de entrada/salida serial cuádruple tiene 4 salidas de imagen conectadas directamente a unas entradas de imagen de la pantalla TFT, estando el sistema configurado para generar caracteres con profundidades de color de 4 bits por pixel.

- 11.- Sistema de generación de imágenes en pantallas TFT, según la reivindicación 6, donde cada una memoria de entrada/salida serial cuádruple tiene 4 salidas de imagen

conectadas directamente a unas entradas de imagen de la pantalla TFT, estando el sistema configurado en un modo RGB 332 para generar caracteres con profundidades de color de 8 bits por pixel.

- 5 12.- Procedimiento de generación de imágenes en pantallas TFT que hace uso del sistema descrito en una cualquiera de las reivindicaciones anteriores, caracterizado porque comprende las etapas de:

- generar en el módulo temporizador una señal proporcional a un número programable de ciclos de la señal reloj;

- activar un modo escritura de la pantalla TFT mediante uno de los pines de entrada salida de propósito general del microcontrolador durante una duración de una parte visible de una línea de caracteres;

10

20

- generar una señal de entrada de reloj de la pantalla TFT a partir de la señal generada por el módulo temporizador y de la señal de reloj;

- -seleccionar mediante un conmutador una señal entre la señal de entrada del reloj de la pantalla TFT y una señal de reloj del puerto de interfaz de periféricos serie, donde la señal seleccionada es la señal de entrada de reloj de la al menos una memoria flash; y,

- enviar desde la al menos una memoria flash un carácter de la línea de caracteres directamente a la pantalla TFT cuando el conmutador seleccione la señal de entrada de reloj de la pantalla TFT y la señal de entrada de reloj de la pantalla TFT esté activa.

- 13.- Procedimiento de generación de imágenes en pantallas TFT, según la

25 reivindicación 12, donde comprende asignar color a los caracteres mostrados en la pantalla TFT.

- 14.- Procedimiento de generación de imágenes en pantallas TFT, según la reivindicación 12, que comprende enviar un número de pulsos de reloj entre dos ciclos activos de la señal de entrada de reloj de la pantalla TFT para marcar un comienzo de una nueva línea de caracteres.

- 15.- Procedimiento de generación de imágenes en pantallas TFT, según la reivindicación 12, que cuando el conmutador selecciona la señal de reloj del puerto de

# ES 2 606 299 B1

interfaz de periféricos serie, el procedimiento comprende enviar comandos de lectura a la al menos una memoria flash.

22