# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 607 934

51 Int. Cl.:

H04J 3/06 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 03.01.2008 PCT/CN2008/070017

(87) Fecha y número de publicación internacional: 07.08.2008 WO08092390

(96) Fecha de presentación y número de la solicitud europea: 03.01.2008 E 08700043 (6)

(97) Fecha y número de publicación de la concesión europea: 28.09.2016 EP 2127216

(54) Título: Reutilización del ancho de banda en un flujo de datos multiplexados

(30) Prioridad:

26.01.2007 US 886833 P 16.04.2007 US 735604

Fecha de publicación y mención en BOPI de la traducción de la patente: **04.04.2017**

(73) Titular/es:

HUAWEI TECHNOLOGIES CO., LTD. (100.0%) HUAWEI ADMINISTRATION BUILDING BANTIAN LONGGANG DISTRICT SHENZHEN, GUANGDONG PROVINCE 518129, CN

(72) Inventor/es:

FOURCAND, SERGE, FRANCOIS

(74) Agente/Representante:

**LEHMANN NOVO, María Isabel**

#### **DESCRIPCIÓN**

Reutilización del ancho de banda en un flujo de datos multiplexados

#### 5 CAMPO DE LA INVENCIÓN

15

45

50

55

60

65

La presente invención se refiere, en general, a tecnologías de comunicaciones de redes y en particular, a un método y componentes de red para reutilizar el ancho de banda en un flujo de datos multiplexados.

#### 10 ANTECEDENTES DE LA INVENCIÓN

Ethernet es el protocolo preferido para numerosos tipos de redes puesto que es flexible, descentralizado y escalable. Ethernet es flexible por cuanto que permite que paquetes de datos de tamaños variables sean transmitidos a través de diferentes tipos de medios utilizando varios nodos que tienen cada uno diferentes velocidades de transmisión. Ethernet es descentralizado por cuanto que permite que los dispositivos extremos transmitan y reciban datos sin supervisión o intervención de un servidor centralizado o parte interviniente. Además, Ethernet es escalable por cuanto que puede ponerse en práctica tanto en redes a pequeña escala como en redes a gran escala. Estas ventajas hacen de Ethernet una opción preferida para distribución de datos en numerosas redes informáticas.

Lamentablemente, Ethernet tiene algunos inconvenientes. Cuando los paquetes de Ethernet se transmiten a través de la red, los paquetes de Ethernet tienen que contender con otro tráfico que es transmitido a través de los mismos enlaces o a través de los mismos nodos. El tráfico contencioso no solamente incluye paquetes vinculados para el mismo destino, sino también paquetes vinculados para otros destinos que se transmiten a través del mismo enlace o a través del mismo nodo que el paquete de Ethernet. La contención produce ráfagas y fluctuaciones en los nodos dentro de la red. Algunos de estos problemas pueden resolverse utilizando un procedimiento de arbitraje de recursos y memorias intermedias en los nodos, y asignando prioridad a los paquetes en datos de alta prioridad y datos de baja prioridad. Sin embargo, estas soluciones aumentan la complejidad de la red, incrementan el retardo y menoscaban las ventajas inherentes de Ethernet.

Los inconvenientes antes citados son parte de la razón por la que Ethernet no ha sido ampliamente puesta en práctica en redes que transmiten datos multiplexados por división de tiempo (TDM). Más concretamente, Ethernet no proporciona una Calidad de Servicio (QoS) suficiente para cumplir los requisitos estrictos sobre fluctuaciones y pérdida de datos para el tráfico vocal en la red telefónica conmutada pública (PSTN) y otras redes TDM. En cambio, el tráfico de TDM se transmite por redes altamente sincronizadas, tales como redes ópticas síncronas (SONET) y redes de jerarquía digital síncrona (SDH). Varias mejoras de Ethernet, tales como emulación de circuitos, transporte central del proveedor y los denominados pseudo-circuitos, han sido propuestas para resolver los inconvenientes de las fluctuaciones y pérdida de datos, pero dichas mejoras no consiguen acoplar la flexibilidad de Ethernet con los estrictos requisitos de QoS en las redes TDM. En consecuencia, existe una necesidad de un protocolo de Ethernet mejorado que sea flexible, fácil de poner en práctica, soporte los requisitos de QoS de las redes TDM y sea compatible con la tecnología existente.

El documento EP 1655885 A1 da a conocer un método de puesta en práctica para un terminal videofónico, que se refiere a un método de transmisión en comunicación multimedia, que incluye: en primer lugar, establecer un canal de voz de red PSTN desde un terminal videofónico a otro terminal en conformidad con el modo de marcación telefónica normal de la red PSTN; reiniciando luego la función videofónica; después de que la información digital, tal como una dirección IP, fuera modulada a señal analógica por el dispositivo terminal siendo la señal transmitida en el canal vocal de PSTN para completar el proceso interactivo de dirección IP; un dispositivo terminal inicia una llamada automática a través de la red IP, utilizando una dirección IP obtenida, y estableciendo luego un tráfico de comunicación videofónica sobre la base de la red IP, esto es, datos multimedia, tales como voz, datos de vídeo, se transmitieron a través de la red de protocolo de Internet IP. Adoptando el método anterior, un usuario puede establecer un proceso de comunicación multimedia videofónica sobre la base de la red IP en conformidad con el modo de marcación telefónica de la red PSTN común, y realizando una función videofónica simple y de amplia aceptación por el usuario; la invención da a conocer también un método de puesta en práctica en el que un terminal videofónico y un terminal videofónico IP simple llaman a dicho terminal videofónico.

El documento WO 02/099578 A2 da a conocer un sistema del tipo punto a punto para conectar una tarjeta de línea a una tarjeta de conmutación utilizando una velocidad de transmisión medida en gigabits por segundo. En conformidad con otro aspecto de la idea inventiva, un método de transmisión de tráfico incluye las operaciones siguientes: la tarjeta de línea transmite tráfico en varias tramas en una denominada supertrama y dentro de cada trama transmite tráfico por intermedio de varios canales, transmitiendo cada canal datos multiplexados por división de tiempo o datos en paquetes, dentro de al menos un canal que transmite un paquete de longitud fija que comprende una cabecera y datos, y dentro del paquete de longitud fija transmite también bits que identifican la posición de una trama que contiene la longitud fija dentro de la supertrama y en donde los bits que acaban de describirse están situados entre una cabecera del paquete de longitud fija y datos dentro del paquete de longitud fija. Como alternativa, un método del tipo anteriormente descrito puede transmitir, o no, los bits anteriormente descritos para identificar la posición de la trama dentro de la supertrama. En este método alternativo, la tarjeta de línea transmite, dentro de la cabecera,

una combinación de bits que incluyen un identificador de flujo, un mapa de enrutamiento que identifica al menos una unidad de línea de destino y una señal que indica la llegada de otro paquete de longitud fija en una cola de espera en la unidad de línea. Otro método alternativo puede transmitir, o no, los bits anteriormente descritos y en cambio, transmitir un byte de sobrecarga utilizado para indicar un estado de configuración, y la tarjeta de línea cambia un bit en dicho byte de sobrecarga en respuesta a una señal que indica la eliminación próxima de la tarjeta de línea.

El documento US 6999479 B1 da a conocer un aparato que comprende uno o más nodos. El aparato puede configurarse para transportar uno o más paquetes dentro de una trama. Los unos o más nodos pueden configurarse para añadir y/o eliminar al menos uno de entre los uno o más paquetes desde la trama.

#### SUMARIO DE LA INVENCIÓN

5

10

15

20

35

40

45

En un aspecto de la idea inventiva, la presente invención incluye un componente de red que comprende un procesador configurado para comunicar una trama dentro de una ventana de sincronización, en donde la trama comprende un mapa de intervalos temporales que indica una pluralidad de tipos de datos transmitidos en una pluralidad de intervalos temporales, y en donde cada intervalo temporal es asignado para transmitir uno de los tipos de datos; identificar un intervalo temporal inactivo que se asigna para transmitir un primer tipo de datos en conformidad con una indicación incluida en el intervalo temporal para identificar si los intervalos temporales son intervalos temporales activos o intervalos temporales inactivos; e insertar un segundo tipo de datos en el intervalo temporal inactivo; en donde el segundo tipo de datos es parte de un flujo del segundo tipo de datos y en donde el procesador está configurado, además, para identificar un intervalo temporal activo que sigue al intervalo temporal inactivo, siendo el intervalo temporal activo asignado para transmitir el primer tipo de datos; e interrumpir el flujo del segundo tipo de datos insertando el primer tipo de datos en el intervalo temporal activo.

En otro aspecto de la idea inventiva, la presente invención incluye un método que comprende la recepción de un flujo de datos que incluye una pluralidad de intervalos temporales, en donde cada intervalo temporal es asignado para transmitir uno de entre una pluralidad de tipos de datos según se indica por un mapa de intervalos temporales; y determinar si uno de los intervalos temporales asignados para transmitir un primer tipo de datos contiene un segundo tipo de datos en conformidad con una indicación contenida en el intervalo temporal para indicar si los intervalos temporales son intervalos temporales activos o intervalos temporales inactivos; en donde el segundo tipo de datos es parte de un flujo del segmento de trama consecutiva, y el método comprende, además: identificar un intervalo temporal activo que sigue a uno de los intervalos temporales inactivos, siendo el intervalo temporal activo asignado para transmitir el primer tipo de datos; e interrumpir el flujo del segundo tipo de datos insertando el primer tipo de datos en el intervalo temporal activo.

En un tercero aspecto de la idea inventiva, el procesador está configurado, además, para comunicar un flujo de datos que comprende una sección asignada para transmitir datos de alta prioridad, determinar si una parte de la sección no está transmitiendo los datos de alta prioridad y reutilizar la parte de la sección para transmitir datos de baja prioridad a la determinación de que la parte de la sección no está transmitiendo los datos de alta prioridad.

Con las soluciones dadas a conocer por las formas de realización de la presente invención, es posible transmitir datos de alta prioridad a través de una red en una manera determinística y sin contención, con lo que se cumplen los requisitos de calidad de servicio QoS de la red PSTN. Estas y otras características operativas se entenderán con mayor claridad a partir de la descripción detallada siguiente haciendo referencia a los dibujos adjuntos y a las reivindicaciones.

#### BREVE DESCRIPCIÓN DE LOS DIBUJOS

Para un entendimiento más completo de la presente invención y sus ventajas, se hace referencia a continuación a la descripción siguiente tomada en conjunción con los dibujos adjuntos, en los que las referencias numéricas similares representan partes similares.

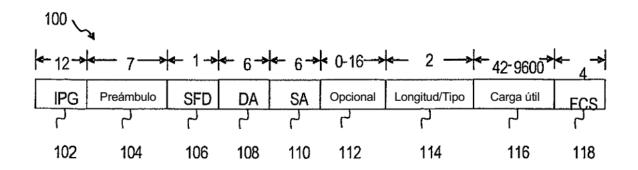

La Figura 1 es una ilustración de una forma de realización de una trama MAC de Ethernet.

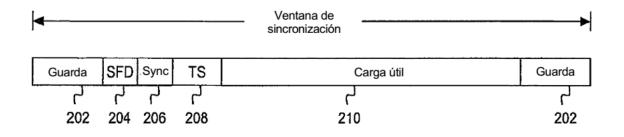

La Figura 2A es una ilustración de una forma de realización de una trama H-TDM.

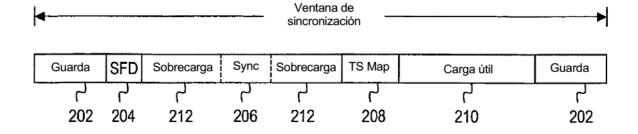

La Figura 2B es una ilustración de otra forma de realización de una trama H-TDM.

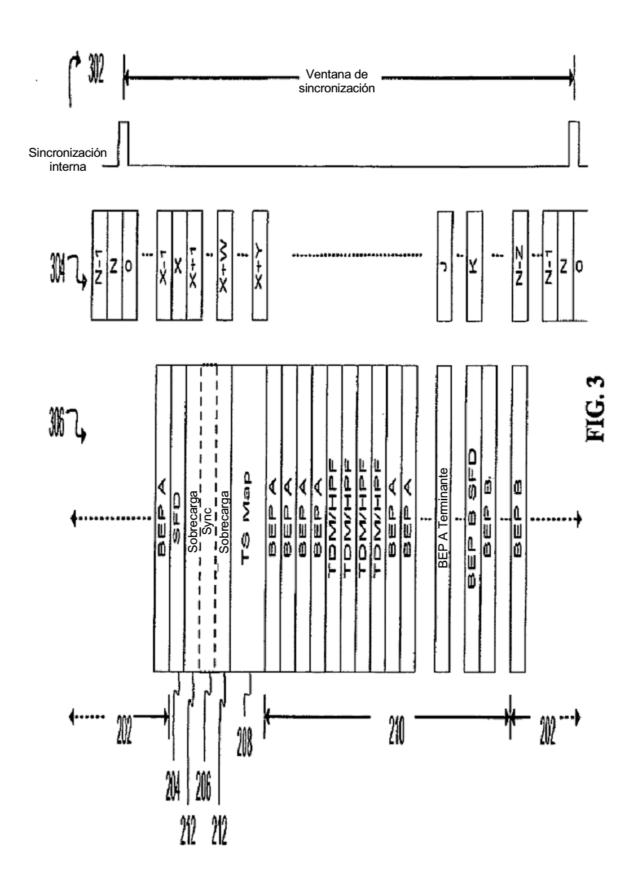

La Figura 3 es una ilustración de una forma de realización de una disposición de intervalos temporales de la trama 60 H-TDM.

La Figura 4 es una ilustración de una forma de realización de una codificación de reutilización de ancho de banda para intervalos temporales de flujo de alta prioridad.

La Figura 5 es una ilustración de una forma de realización de una pluralidad de intervalos temporales que comunican datos de flujo de alta prioridad.

La Figura 6 es una ilustración de una forma de realización de un flujo de datos que reutiliza el ancho de banda en intervalos temporales de flujo de alta prioridad inactivos.

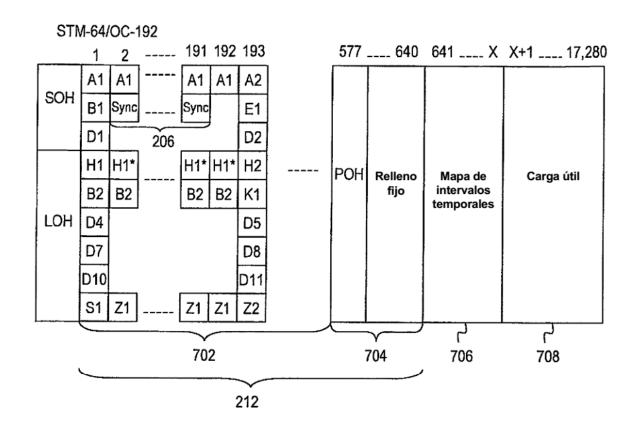

5 La Figura 7 es una ilustración de una forma de realización de una trama H-TDM en una trama STM-64/OC-192.

La Figura 8A es una ilustración de una forma de realización de un mapa de intervalos temporales.

La Figura 8B es una ilustración de otra forma de realización del mapa de intervalos temporales.

10

25

55

60

65

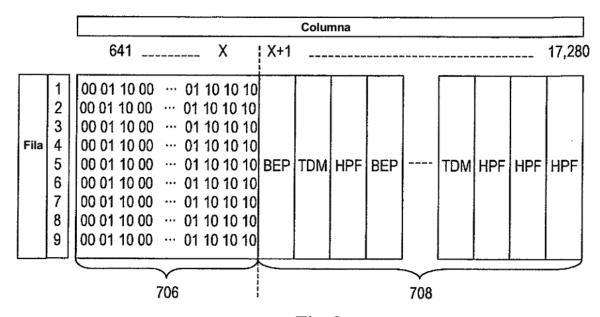

La Figura 9 es una ilustración de una forma de realización de un mapa de intervalos temporales y la carga útil en la trama STM-64/OC-192.

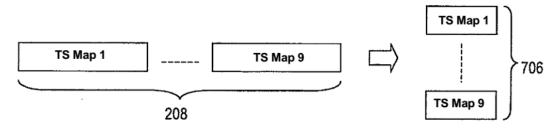

La Figura 10A es una ilustración de una forma de realización del proceso de comunicación del mapa de intervalos temporales mediante una interfaz Ethernet y una interfaz SONET/SDH.

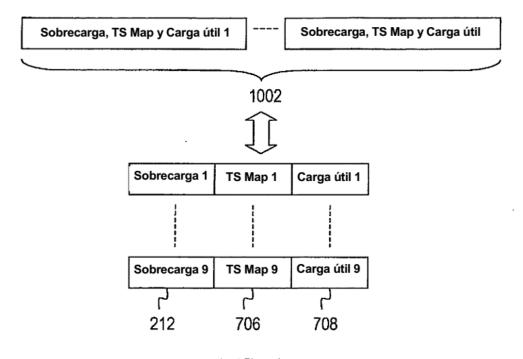

La Figura 10B es una ilustración de otra forma de realización del proceso de comunicación de la trama H-TDM por intermedio de una interfaz Ethernet y una interfaz SONET/SDH.

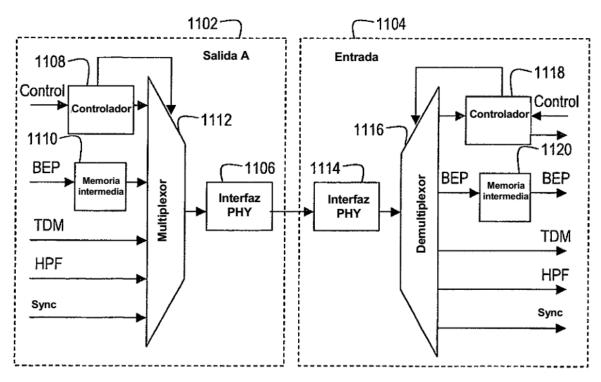

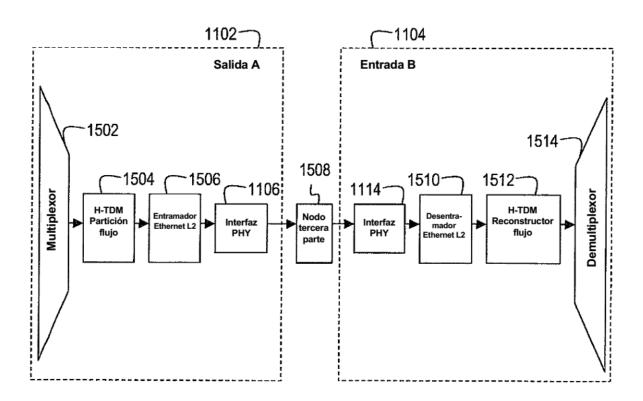

La Figura 11 es una ilustración de una forma de realización de un diagrama de bloques funcionales del puerto de salida y del puerto de entrada de dos nodos.

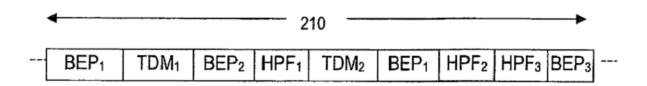

La Figura 12 es una ilustración de una forma de realización de una carga útil con múltiples instancias de cada tipo de tráfico.

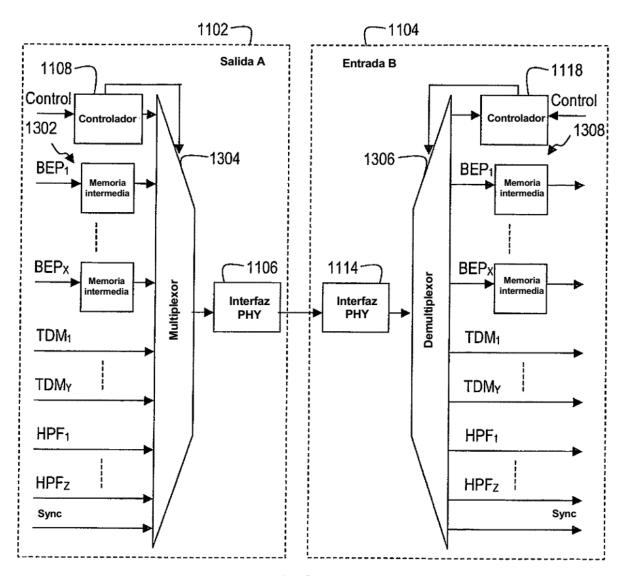

La Figura 13 es una ilustración de otra forma de realización de un diagrama de bloques funcionales del puerto de salida y del puerto de entrada de dos nodos.

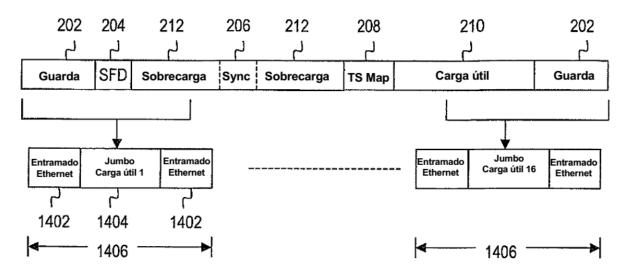

La Figura 14 es una ilustración de una forma de realización del proceso de encapsulación de la trama H-TDM dentro de una pluralidad de paquetes de Ethernet.

de un diagrama de bloques funcionales del puerto de salida y del puerto de entrada de dos nodos.

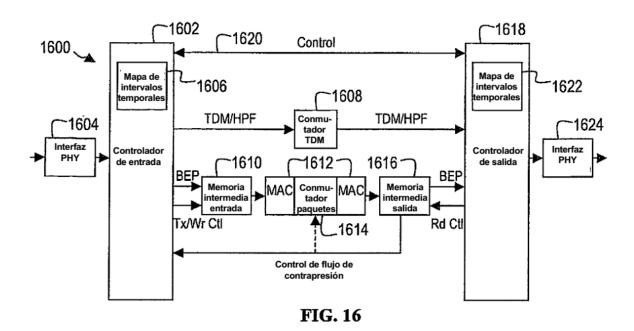

La Figura 16 es una ilustración de otra forma de realización de un diagrama de bloques funcionales para la comunicación de la trama H-TDM dentro de un nodo.

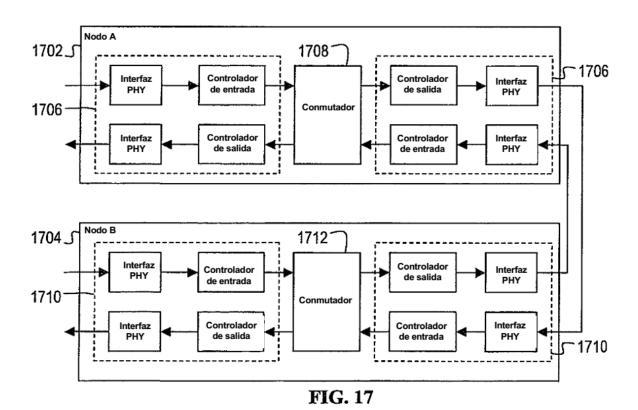

La Figura 17 es una ilustración de una forma de realización de dos nodos.

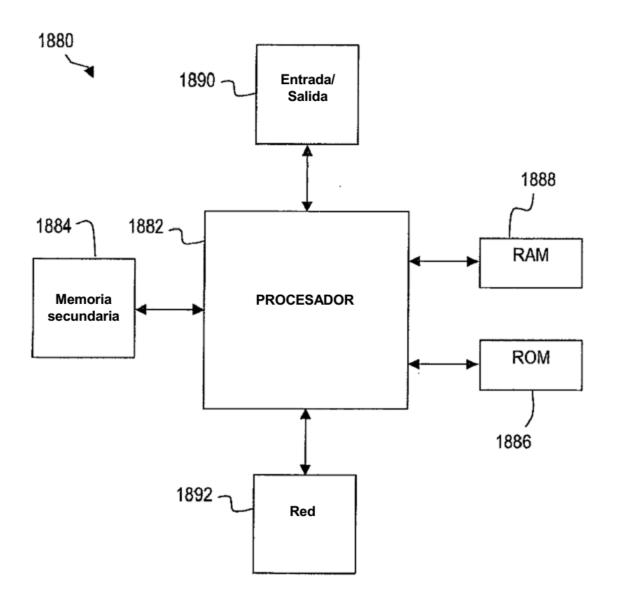

La Figura 18 es una ilustración de una forma de realización de un sistema informático de uso general adecuado para poner en práctica las diversas formas de realización de la presente invención.

#### DESCRIPCIÓN DETALLADA DE LAS FORMAS DE REALIZACIÓN

Debe entenderse, desde el principio, que aunque se dan a conocer, a continuación, una puesta en práctica ilustrativa de una o más formas de realización, el sistema y/o métodos dados a conocer pueden ponerse en práctica utilizando cualquier número de técnicas, sean actualmente conocidas o en existencia. La presente invención no debe, en forma alguna, limitarse a las formas de realización ilustrativas, dibujos y técnicas que se ilustran a continuación, incluyendo los ejemplos de diseños y puestas en práctica ilustradas y descritas en esta descripción, sino que pueden modificarse dentro del alcance de lo establecido en las reivindicaciones adjuntas junto con su gama completa de equivalentes.

A continuación se da a conocer un modo operativo en el que se multiplexan diferentes tipos de datos utilizando un sistema de intervalos temporales síncronos superpuestos, que se refiere aquí como un modo operativo de multiplexación por división de tiempo de Huawei (H-TDM). El sistema de intervalos temporales síncronos superpuestos puede ser datos de marcas temporales multiplexadas por división de tiempo, datos de control y datos de carga útil en intervalos temporales dimensionados en octetos dentro de una ventana de sincronización predefinida. Los datos de carga útil pueden incluir una pluralidad de tipos de datos, tales como datos multiplexados por división de tiempo (TDM), datos de flujo de alto rendimiento (HPF) y datos de paquetes del mejor esfuerzo (BEP). Cuando múltiples tipos de datos se incluyen en la carga útil, un mapa de intervalos temporales puede indicar el tipo y la localización de los diferentes tipos de datos. El sistema de intervalos temporales síncronos superpuestos puede permitir que datos de alta prioridad sean transmitidos por intermedio de una red en una manera determinística y sin contención, con lo que se cumplen los requisitos de calidad de servicio QoS de la red PSTN. El sistema de intervalos temporales síncronos superpuestos favorece también el uso eficiente del ancho de banda permitiendo que datos de baja prioridad utilicen intervalos temporales que están asignados a datos de alta prioridad cuando los datos de alta prioridad están en condición inactiva. El sistema de intervalos temporales síncronos superpuestos permite también un mapeado de correspondencia eficiente de datos entre nodos Ethernet y nodos SONET o SDH.

Se da a conocer, además, una arquitectura de circuito que multiplexa una pluralidad de fuentes de datos en el sistema de intervalos temporales síncronos superpuestos. La arquitectura del circuito proporciona una memorización intermedia específica de la prioridad, de modo que los datos de baja prioridad puedan memorizarse en los nodos mientras los datos de alta prioridad pasan a través de los nodos sin ser memorizados. La arquitectura del circuito proporciona también un control de flujo de contrapresión para mantener una capacidad óptima de las memorias intermedias en los nodos.

La Figura 1 ilustra una forma de realización de un paquete Ethernet 100. El paquete 100 se inicia con un preámbulo 104, que puede ser aproximadamente siete octetos de una configuración repetida, tal como "10101010". El preámbulo 104 puede permitir a los circuitos de señalización de capa física (PLS) de un nodo alcanzar la sincronización de régimen estacionario con la temporización del paquete. El preámbulo 104 puede ir seguido por un delimitador de inicio de tramas (SFD) 106, que puede ser un octeto único con la configuración "10101011" y puede utilizarse para indicar el inicio del paquete 100. La dirección de destino (DA) 108 puede especificar la dirección del nodo de destino para el que está previsto el paquete 100 y puede ser aproximadamente seis octetos. La dirección origen (SA) 110 puede especificar la dirección del nodo origen a partir del cual tiene origen el paquete 100 y puede ser aproximadamente seis octetos. El paquete 100 puede contener una pluralidad de octetos opcionales 112 que se utilizan para asociar el paquete 100 con un identificador de protocolo de tipo (TPID) y/o un identificador de red de área local virtual (VID). A modo de ejemplo, hasta aproximadamente dieciséis octetos pueden utilizarse para asociar el paquete 100 con un TPID y un VID, a modo de ejemplo, según se describe en la norma IEEE 802.1Q.

El paquete 100 continúa con un campo de longitud/tipo 114, que puede especificar la longitud de la carga útil 116 y el protocolo Ethernet que se utiliza, y puede ser aproximadamente dos octetos. La carga útil 116 puede ser un campo de magnitud variable que transmite una carga útil de datos. Aunque la carga útil 116 puede contener cualquier cantidad de datos, en formas de realización específicas, la carga útil 116 puede contener desde aproximadamente 42 octetos a aproximadamente 1500 octetos en paquetes estándar y puede contener desde aproximadamente 9000 octetos a aproximadamente 12000 octetos en paquetes denominados jumbo. La secuencia de control de tramas (FCS) 118 puede utilizarse para detección de errores y puede ser un campo de cuatro octetos que contiene un valor de control de concordancia cíclica (CRC) calculado utilizando los contenidos del paquete 100. Aunque no sea parte del paquete 100, el intervalo entre paquetes (IPG) 102 pueden ser datos o caracteres inactivos que separan los paquetes 100. El IPG 102 puede contener aproximadamente doce octetos de caracteres de control inactivos, aunque cualquier cantidad de datos o caracteres inactivos puede utilizarse en el IPG 102.

La Figura 2A ilustra una forma de realización del sistema de intervalos temporales síncronos superpuestos del modo operativo H-TDM. Más concretamente, la Figura 2A ilustra un sistema de intervalos temporales síncronos superpuestos dentro de una ventana de sincronización que tiene un periodo predefinido, tal como aproximadamente 125 µs. El sistema de intervalos temporales síncronos superpuestos comprende un delimitador de inicio de trama (SFD) 204, una marca temporal de sincronización (Sync) 206, un mapa de intervalos temporales (TS Map) 208 y una carga útil 210. El delimitador SFD 204 puede delimitar un inicio de la trama H-TDM y puede ser un símbolo de control Ethernet reservado, tal como el símbolo de control /K28.1/. Como reconocerán los expertos en esta técnica, el símbolo de control /K28.1/ incluye una coma que puede utilizarse para permitir la sincronización de símbolos de 8 bits/10 bits (8B/10B) cuando el sistema de intervalos temporales síncronos superpuestos se comunica sobre medios de soporte codificados de 8B/10B. En una forma de realización, el delimitador SFD 204 puede especificar también la magnitud de la trama H-TDM. La marca temporal Sync 206 sigue el delimitador SFD 204 y puede utilizarse para iniciar las ventanas de sincronización, para sincronizar las ventanas de sincronización y para alinear en fase las ventanas de sincronización entre dos nodos. Una descripción detallada de Sync 206, el proceso de frecuencia-sincronización y el proceso de alineación de fases se encuentra en el documento de la Solicitud de Patente de Estados Unidos número de serie 11/735,590 titulado "Sincronización de reloj de red de intervalos entre paquetes".

El sistema de intervalos temporales síncronos superpuestos puede continuar con el TS Map 208, que puede especificar el tipo y la localización de los datos en la carga útil 210. En una forma de realización, los intervalos temporales individuales en la carga útil 210 pueden asignarse al tráfico de TDM, HPF y BEP, en conformidad con un modelo predefinido. A modo de ejemplo, el primer millar de intervalos temporales puede asignarse al tráfico de TDM, los cinco mil intervalos temporales subsiguientes pueden asignarse al tráfico de HPF y los tres mil intervalos temporales subsiguientes pueden asignarse al tráfico de BEP. En dicha forma de realización, el TS Map 208 puede omitirse de la trama H-TDM si los nodos tienen conocimiento del modelo predefinido. Como alternativa, el TS Map 208 puede indicar la asignación de cada intervalo temporal en la carga útil 210 como un intervalo temporal de TDM, HPF o BEP. Utilizando el TS Map 208 el tráfico de TDM, HPF y de BEP puede intercalarse dinámicamente dentro de un sistema de intervalos temporales síncronos superpuestos.

Algunos intervalos temporales al principio y/o final de la ventana de sincronización pueden ser parte de un intervalo de guarda 202. Los intervalos de guarda 202 permiten a la trama H-TDM entrar en flotación dentro de la ventana de sincronización. Más concretamente, la localización de SFD 204 en relación con el inicio de la ventana de sincronización puede variar entre ventanas de sincronización. En consecuencia, el intervalo de guarda 202 al principio de la ventana de sincronización puede ser el mismo o de un tamaño diferente del que tiene el intervalo de guarda 202 al final de la ventana de sincronización, y la magnitud de los intervalos de guarda 202 en una ventana de

sincronización puede variar respecto al tamaño de los intervalos de guarda 202 en otras ventanas de sincronización. Dicha forma de realización puede ser ventajosa puesto que la integridad del SFD 204, Sync 206, TS Map 208 y los datos en la carga útil 210 se mantienen si cualesquiera de los datos en los intervalos de guarda 202 es objeto de eliminación, corrupción, pérdida o resultan de cualquier otro modo ilegibles, a modo de ejemplo, debido a las tolerancias de reloj u otros factores no determinísticos. En algunas formas de realización, el intervalo de guarda 202 puede transmitir datos de BEP de baja prioridad. Como alternativa, el intervalo de guarda 202 puede rellenarse con ceros o puede contener caracteres inactivos.

5

35

40

55

60

65

Aunque la ventana de sincronización puede ser de cualquier duración, existen ventajas particulares para utilizar una 10 ventana de sincronización con un periodo de aproximadamente 125 µs. Más concretamente, sincronizando los sistemas de intervalos temporales síncronos superpuestos a una ventana de sincronización de 125 us se permite la interoperabilidad de los nodos Ethernet con la red PSTN, SONET, SDH y otras redes TDM. En consecuencia, cuando el sistema de intervalos temporales síncronos superpuestos tiene una ventana de 125 µs, la sobrecarga de transporte de SONET/SDH puede añadirse al formato del sistema de intervalos temporales síncronos superpuestos. 15 La Figura 2B ilustra un sistema de intervalos temporales síncronos superpuestos que contiene una sobrecarga de transporte de SONET/SDH 212. La sobrecarga de transporte de SONET/SDH 212 permite que los datos contenidos en la carga útil 210 sean objeto de un mapeado de puesta en correspondencia eficiente entre redes Ethernet y las redes SONET/SDH utilizadas por la PSTN. La sobrecarga de transporte de SONET/SDH 212 se ilustra como circundante de Sync 206 puesto que el Sync 206 puede insertarse en octetos indefinidos de la sobrecarga de 20 transporte de SONET/SDH 212. Una descripción detallada del mapeado de correspondencia de las tramas H-TDM entre el formato Ethernet y el formato SONET/SDH puede encontrarse en las solicitudes de patente provisionales antes citadas.

El sistema de intervalos temporales síncronos superpuestos puede permitir a la trama H-TDM transportar una diversidad de tipos de datos. Cuando la ventana de sincronización tiene un periodo de aproximadamente 125 µs y cada intervalo temporal contiene un octeto de datos, cada uno de los intervalos temporales en el sistema de intervalos temporales síncronos superpuestos representa un canal único con aproximadamente 64 kilobits por segundo (Kbps) de ancho de banda. Estos canales proporcionan un ancho de banda suficiente para contener una conversación vocal compatible con la red PSTN. De este modo, los canales vocales que se transmiten en una trama H-TDM pueden referirse como datos TDM.

El sistema de intervalos temporales síncronos superpuestos proporciona también una granularidad de la magnitud de octetos que soporta la comunicación de otro tráfico con requisitos estrictos de calidad de servicio QoS, referidos en esta descripción como datos de HPF. En una forma de realización, los datos HPF pueden requerir una cantidad determinística de ancho de banda. Ejemplos de tráfico de HPF incluyen vídeo, audio y otro tráfico multimedia. Al tráfico de HPF se le pueden asignar múltiples canales con granularidad de octeto único en conformidad con los requisitos de ancho de banda del tráfico de HPF. Dicho de otro modo, cada canal asignado a un HPF aumenta el ancho de banda asignado al HPF en 64 Kbps. A modo de ejemplo, a un tráfico de HPF de vídeo en flujo continuo de baja resolución que requiere aproximadamente 256 Kbps de ancho de banda se le puede asignar aproximadamente cuatro canales desde la trama H-TDM. De modo similar, a un HPF que requiere aproximadamente 3.2 megabits por segundo (Mbps) de ancho de banda se le puede asignar aproximadamente cincuenta canales desde la trama H-TDM. En una forma de realización, a los HPFs puede asignarse un ancho de banda en granularidad de 576 Kbps para estar en correspondencia con una columna completa de una trama SONET/SDH.

Además de asignarse para transmitir datos de TDM y HPF, los intervalos temporales en la carga útil 210 pueden asignarse para transmitir datos BEP. Los datos BEP pueden incluir datos de paquetes Ethernet de baja prioridad, cargas descendentes de datos, exploración de la web, o cualesquiera otros datos de baja prioridad. En una forma de realización, cualesquiera intervalos temporales en la carga útil 210 que no estén asignados como intervalos temporales de TDM o de HPF se asignan automáticamente como intervalos temporales de BEP. En otra forma de realización, al menos una parte de los intervalos temporales son asignados como intervalos temporales de BEP para garantizar que al menos algunos datos de BEP estén contenidos en cada trama H-TDM.

Mientras que la asignación de ancho de banda puede realizarse según se describió con anterioridad para flujos de datos de tasa binaria constante (CBR), los flujos de datos de tasa binaria variable (VBR) presentan un reto operativo adicional. En una forma de realización, los flujos de datos de VBR pueden asignarse en ancho de banda en conformidad con una magnitud máxima de ancho de banda que puede utilizar los flujos de datos de VBR. Se considera un caso en donde el VBR HPF puede ser un flujo de datos de vídeo codificados del denominado Grupo de Expertos de Imágenes Animadas (MPEG). El formato del MPEG puede codificar datos de vídeo de modo que se necesite menos ancho de banda para visualizar escenas con pocos cambios o movimiento, y se necesite más ancho de banda para visualizar escenas con numerosos cambios o movimiento. En tal caso, a un HPF que soporta los datos de vídeo codificados de MPEG se le puede asignar una cantidad suficiente de intervalos temporales para transportar la magnitud máxima de ancho de banda que requerirá el flujo de datos de vídeo codificados de MPEG. Durante escenas operativas en donde menos de la cantidad máxima de ancho de banda se esté utilizando para comunicar el flujo de datos de vídeo codificado de MPEG, el ancho de banda no utilizado puede reutilizarse por otros tipos de datos, según se describe en detalle a continuación.

La Figura 3 ilustra una disposición más detallada del sistema de intervalos temporales síncronos superpuestos que se ilustra en la Figura 2A. La Figura 3 contiene tres filas de información: una señal de sincronización interna 302 que delimita la ventana de sincronización, una línea de tiempo 304 que enumera cada intervalo temporal y un descriptor 306 que describe los datos que pueden contenerse dentro de cada intervalo temporal. La señal de sincronización interna 302 puede corresponder a la ventana de sincronización establecida cuando se inician los modos operativos H-TDM o sincronizados de Huawei (H-Sync) según se describe en la solicitud de patente de Estados Unidos número 11/735,590 titulada "Sincronización de reloj de red de intervalos entre paquetes".

La ventana de sincronización puede iniciarse en el intervalo temporal 0. Los intervalos temporales 0 a X inclusive representan los intervalos de guarda 202 y por ello, el descriptor 306 indica que el tráfico de BEP puede transportarse durante estos intervalos temporales. Más concretamente, el intervalo temporal X-1 incluye una primer parte de un primer BEP, identificado como BEP A. En el intervalo temporal X BEP A puede interrumpirse por SFD 204 que puede delimitar el inicio de la trama H-TDM. Si la trama H-TDM incluye una sobrecarga de SONET/SDH 212, según se ilustra en la Figura 2B, en tal caso la sobrecarga de SONET/SDH 212 y Sync 206 se comunican posteriormente a SFD 202, p.ej., en los intervalos temporales X+1 a X+W inclusive. En una forma de realización, al menos un octeto inactivo o un octeto de sobrecarga de transporte de SONET/SDH 212 puede insertarse entre los intervalos temporales X+1 y X+W. Dichos octetos permiten un mapeado de correspondencia eficiente de Sync 206 para una trama de SONET/SDH, de modo que el Sync 206 se alinee con las columnas de la trama SONET/SDH. El TS Map 208 puede seguir el intervalo temporal X+W y puede indicar el tipo y la localización de los intervalos temporales HPF, TDM y/o BEP en la carga útil 210. El TS Map 208 puede extenderse a través del intervalo temporal X+Y

La carga útil 210 de la trama H-TDM sigue al intervalo temporal X+Y. La carga útil 210 puede contener una segunda parte de BEP A, que puede interrumpirse por uno o más intervalos temporales de datos TDM o HPF. A la terminación de los intervalos temporales TDM o HPF, BEP A puede continuar hasta que BEP A termine en el intervalo temporal J. Siguiendo a un IPG o siguiendo inmediatamente al final de BEP A, un segundo BEP identificado como BEP B puede iniciarse en el intervalo temporal K y los intervalos temporales restantes. La trama H-TDM puede finalizar en el intervalo temporal N; sin embargo BEP B puede continuar en el intervalo de guarda 202 y quizás en el intervalo de guarda 202 de la ventana de sincronización subsiguiente. De este modo, la transmisión de un BEP no finaliza necesariamente al final de la trama H-TDM o al final de la ventana de sincronización, sino que, en cambio, finaliza cuando el BEP está completo o cuando se interrumpe por el SFD 204 subsiguiente.

25

30

35

40

45

50

55

60

65

Mientras la disposición de intervalos temporales ilustrada en la Figura 3 comunica dos BEPs, cualquier cantidad de datos de BEP puede comunicarse dentro de la ventana de sincronización. A modo de ejemplo, la ventana de sincronización puede no contener ningún dato BEP, parte de un BEP, exactamente un BEP o múltiples BEPs. Además, mientras que la Figura 3 ilustra que los datos BEP se interrumpen solamente una vez debido a una serie de intervalos temporales TDM y/o HPF, los expertos en esta técnica apreciarán que los datos de BEP pueden interrumpirse cualquier número de veces por cualquier número de intervalos temporales TDM o HPF, o mediante intervalos temporales asignados a una diferente instancia operativa de datos de BEP, según se describe a continuación.

En una forma de realización, el ancho de banda de los intervalos temporales asignados para transmitir datos de alta prioridad puede reutilizarse cuando un intervalo temporal de alta prioridad está inactivo. Más concretamente, cuando los intervalos temporales asignados a HPF o TDM no están siendo utilizados o son de cualquier otro modo inactivos, los intervalos temporales pueden transmitir datos BEP de baja prioridad. Según se ilustra en la Figura 4, cada intervalo temporal asignado para transmitir datos de alta prioridad, tales como HPF, puede codificarse de modo que un primer bit sea un bit de control y los bits restantes transporten datos. El bit de control puede indicar si el intervalo temporal HPF es activo o inactivo. A modo de ejemplo, cuando el bit de control tiene un valor "1", el intervalo temporal de HPF puede estar activo y los datos contenidos en el intervalo temporal HPF pueden ser datos de HPF. Cuando el bit de control tiene un valor "0", el intervalo temporal HPF puede estar inactivo y los bits de datos pueden reutilizarse para transmitir otros tipos de datos tales como datos BEP. Los intervalos temporales TDM no utilizados o no asignados pueden reutilizarse también por los datos de BEP.

La Figura 5 ilustra un ejemplo de un flujo de datos de HPF dentro de tres intervalos temporales HPF activos que utilizan la codificación ilustrada en la Figura 4. Según se ilustra en un primer intervalo temporal HPF, el intervalo temporal HPF 1, el bit de control se establece a "1" con el fin de indicar que el intervalo temporal HPF 1 está activo. Si los datos de HPF se comunican en secciones de la magnitud de octetos, en tal caso, los primeros siete bits de un primer octeto de HPF se colocan en los siete bits de datos del intervalo temporal HPF 1. Además, un segundo intervalo temporal HPF, el intervalo temporal HPF 2, tiene similarmente el bit de control establecido a "1" y el último bit del primer octeto de HPF y los seis primeros bits del siguiente octeto de HPF se colocan en los siete bits de datos del intervalo temporal HPF 3, tiene el bit de control establecido a "1" y los dos últimos bits del segundo octeto de HPF y los cinco primeros bits del tercer octeto de HPF se colocan en los siete bits de datos del intervalo temporal HPF 3. Los expertos en esta técnica apreciarán que, aunque los datos de HPF se describen como estando divididos en secciones del tamaño de octetos, se considera que los datos de HPF pueden configurarse alternativamente y colocarse en los intervalos temporales de HPF activos. A modo de ejemplo, los datos de HPF pueden comunicarse en incrementos de siete bits de modo que

cada intervalo temporal activo se comunique completamente cada incremento de siete bits.

5

10

15

20

25

40

45

50

55

60

La Figura 6 ilustra un flujo de datos transportado en tres columnas de una trama SONET/SDH que se asignan para transmitir datos HPF. Cada una de las columnas X, X+1 y X+2 incluyen datos organizados en ocho bits, del bit 0 al bit 7 inclusive, y nueve filas, de fila 1 a fila 9 inclusive. Tal como los expertos en esta técnica reconocerán, los datos se transportan desde la trama SONET/SDH, sobre una base de fila por fila, de modo que los bits 0 a 7 inclusive de las columnas X, X+1 y X+2 se comunican en serie para la fila 1, luego para la fila 2 y así sucesivamente. En consecuencia, los datos que no estén completados en una columna continuarán en la columna siguiente. A modo de ejemplo, la primera fila de las columnas X y X+1 tiene el bit de control establecido a "1" para indicar que están activas, y transportarán los datos indicados en TS Map 208, p.ej., datos HPF. La columna X+1 comunica un final de los datos de HPF y por ello, los bits 4 a bit 7 inclusive de la columna X+1 pueden rellenarse con ceros o hacerse inactivos posteriormente a la terminación de los datos de HPF.

Por el contrario, la columna X+2 tiene el bit de control establecido a "0" para indicar que el intervalo temporal asignado a los datos HPF está inactivo, y en consecuencia, el bit 1 al bit 7 inclusive de la columna X+2 pueden utilizarse para soportados datos de BEP. De modo similar, cada una de las columnas X, X+1 y X+2 están inactivas en las filas 2 y 3, y la columna X está inactiva en la Figura 4 y de este modo, dichas áreas pueden utilizarse para el transporte de datos de BEP. Los datos de BEP pueden incluir el inicio de un nuevo BEP, el final de un BEP o datos inactivos entre BEPs. Además, los datos de BEP contenidos en los intervalos temporales HPF inactivos pueden incluir datos de BEP que están situados en cualquier lugar en el sistema de intervalos temporales síncronos superpuestos. A modo de ejemplo, los datos BEP pueden incluir datos procedentes de un BEP anterior, tal como un BEP que estaba localizado en una banda de guarda o en la carga útil antes de los intervalos temporales de HPF.

Según se ilustra en la fila 4 de la columna X+1, se inicia un nuevo HPF y las filas restantes pueden estar activas y contener el nuevo HPF. Los datos del nuevo HPF no esperan a que se complete el BEP, sino que, en cambio, interrumpen el BEP tan pronto como se reciba el HPF. De este modo, el ancho de banda asignado para el transporte de datos de alta prioridad en intervalos temporales de HPF puede reutilizarse dinámicamente por el BEP sin ningún retardo para los datos de HPF.

La Figura 7 ilustra una disposición general del sistema de intervalos temporales síncronos superpuestos dentro de una trama STM-64/OC-192 de SONET/SDH. La trama STM-64/OC-192 incluye 576 columnas de sobrecarga de transporte 702 organizadas en tres filas de sobrecarga de sección (SOH) y seis filas de sobrecarga de líneas (LOH). La trama STM-64/OC-192 incluye también 64 columnas de una sobrecarga de ruta (POH) y relleno fijo 704 y 16640 columnas de carga útil de trama la STM-64/OC-192. La sobrecarga de transporte 702, POH, y el relleno fijo 704 constituyen colectivamente la sobrecarga de SONET/SDH 212 anteriormente descrita. El TS Map 208 y la carga útil 210 pueden disponerse en la carga útil de la trama STM-64/OC-192 de modo que TS Map 208 esté alineada con la columna 671 por intermedio de la columna X en una primera zona 706 de la carga útil de la trama STM-64/OC-192, y la carga útil 210 está alineada con la columna X+1 por intermedio de la columna 17280 en una segunda zona 708 de la carga útil de la trama STM-64/OC-192.

En una forma de realización, Sync 206 puede incluirse dentro de la sobrecarga de transporte 702. Más concretamente, Sync 206 puede situarse dentro de una pluralidad de octetos no definidos en la segunda fila en la sobrecarga de transporte 702. Aunque Sync 206 se ilustra en una posición en octetos no definidos particulares, p.ej., en cualquier lugar en las columnas 2 a 191 inclusive de la segunda fila, los expertos en esta técnica apreciarán que Sync 206 puede comunicarse en cualesquiera otros octetos no definidos de la sobrecarga de transporte 702. Como alternativa, Sync 206 puede comunicarse en las primeras dos columnas de la carga útil de la trama STM-64/OC-192, p.ej., las columnas X+1 y X+2. En dicha forma de realización, la primera mitad de Sync 206 puede situarse en la primera columna y la segunda mitad de Sync 206 puede situarse en la segunda columna.

La Figura 8A ilustra una forma de realización de TS Map 208. TS Map 208 puede estar constituido por una configuración de bits, en donde el valor de cada bits indica si un intervalo temporal se asigna, o no, para transmitir datos de alta prioridad o datos de baja prioridad. Más concretamente, los intervalos temporales asignados a datos de baja prioridad pueden incluir datos de BEP y los intervalos temporales asignados para soportar datos de alta prioridad pueden soportar datos de HPF o TDM. Un bit en TS Map 208 con un valor de "0" puede significar que se asigna un intervalo temporal particular para transportar datos de baja prioridad. De modo similar, un bit en TS Map 208 con un valor de "1" corresponde con un intervalo temporal que se asigna para transportar datos de alta prioridad. Además, las posiciones relativas de los bits en TS Map 208 corresponden con las posiciones relativas de intervalos temporales en la carga útil 210. A modo de ejemplo, el primer bit en TS Map 208 corresponde con el primer intervalo temporal en la carga útil 210 y el último bit en TS Map 208 corresponde con el último intervalo temporal en la carga útil 210. De este modo, si TS Map 208 incluye una configuración de bits con los valores "00110", en tal caso, los primero y segundo intervalos temporales serían asignados para transportar datos de baja prioridad, los tercero y cuarto intervalos temporales se asignarían para transportar datos de alta prioridad y el quinto intervalo temporal sería asignado para transportar datos de baja prioridad.

La Figura 8B ilustra otra forma de realización de TS Map 208. De modo similar a la forma de realización ilustrada en la Figura 8A, TS Map 208 puede estar constituido por una configuración de bits. Sin embargo, en esta forma de

realización, cada par de bits indica la asignación de un intervalo temporal para transportar datos de BEP, HPF o TDM. Un par de bits con un valor de "00" corresponde con un intervalo temporal que se asigna para transportar datos BEP. Un par de bits con un valor de "01" corresponde con un intervalo temporal que se asigna para transportar datos TDM. Un par de bits con un valor de "10" corresponde con un intervalo temporal que se asigna para transportar datos HPF. El valor "11" es un tipo de datos no definidos en esta forma de realización y puede reservarse para otros tipos de datos. Como se indicó anteriormente, las posiciones relativas de los pares de bits en TS Map 208 corresponden con las posiciones relativas de intervalos temporales en la carga útil. A modo de ejemplo, el primer par de bits en TS Map 208 corresponde con el primer intervalo temporal en la carga útil 210 y el último par de bits en TS Map 208 corresponde con el último intervalo temporal en la carga útil 210. De este modo, si TS Map 208 incluye una configuración de bits con los valores "00 10 01 00", en tal caso, el primer intervalo temporal se asigna para transportar datos HPF, el tercer intervalo temporal se asigna para transportar datos BEP.

10

15

20

25

30

35

55

60

65

Aunque valores particulares se describen como estando asociados con uno de los tres tipos de tráfico, los expertos en esta técnica reconocerán que otros pares de valor y tipo de tráfico son posibles. A modo de ejemplo, TS Map 208 puede utilizar el valor "01" para designar un tráfico de BEP y el valor "00" para designar un tráfico de TDM. Además, aunque TS Map 208 en esta forma de realización asigna cada intervalo temporal como siendo un intervalo temporal para transportar uno de entre datos de BEP, HPF o TDM, en otras formas de realización se pueden utilizar otras designaciones. A modo de ejemplo, la designación del tipo de tráfico puede corresponder con diferentes niveles de calidad de servicio QoS. En este caso, los intervalos temporales pueden designarse como transportando tráfico para datos vocales, datos de vídeo, datos de mejor esfuerzo o datos de antecedentes. Asimismo, mientras que uno o dos bits pueden utilizarse para indicar la asignación de un tipo de tráfico en cada intervalo temporal en la carga útil 210, más bits pueden utilizarse en TS Map 208. A modo de ejemplo, si se utilizaron tres bits para TS Map 208, en tal caso, pueden indicarse un mayor número de tipos de tráfico. En particular, con tres bits, ocho tipos de tráfico pueden diferenciarse dentro de TS Map 208.

La Figura 9 ilustra una forma de realización en donde los tipos de datos en la carga útil están alineados en columnas. Más concretamente, TS Map 208 puede organizarse dentro de la primera zona 706 de modo que cada columna de la carga útil 708 sea asignada para transportar uno de entre datos de HPF, TDM o BEP. Cuando cada columna de la carga útil 708 transporta uno de los tipos de datos, cada una de las filas de TS Map 208 en la primera zona 706 es idéntica. Es decir, TS Map 208 es esencialmente una configuración de bits que indica la asignación de cada columna de la carga útil 708 y que tiene una replicación para cada una de las nueve filas de la trama STM-64/OC-192. En dicha forma de realización, pueden omitirse ocho filas de TS Map 208 y la fila restante única de TS Map 208 puede utilizarse para determinar los tipos de datos asignados a los intervalos temporales para todas las nueve filas. Sin embargo, los expertos en esta técnica apreciarán que aunque cada columna puede asignarse para transportar uno de los tipos de datos, el contenido de los datos transportados en cada fila puede diferir de la asignación, a modo de ejemplo, debido a la reutilización del ancho de banda antes citada y/o establecimiento de prioridad dentro de los tipos de datos.

Cada entrada en la trama STM-64/OC-192 puede contener un octeto de datos, en donde una entrada se define como la intersección de una columna y una fila. En consecuencia, cada entrada en TS Map 706 proporciona la asignación del tipo de datos para cuatro columnas en la carga útil 708 cuando el formato de TS Map 208 en la Figura 8B se utiliza a este respecto. Según se ilustra en la Figura 9, la columna 641 puede contener un TS Map 208 con la configuración de bits "00 01 10 00", y la columna X puede contener un TS Map 208 con la configuración de bits "01 10 10 10". De este modo, la configuración de bits en la columna 641 indica que la primera columna de la carga útil 708, columna X+1, se asigna para transportar datos de BEP, la columna X+2 se asigna para transportar datos de TDM la columna X+3 se asigna para transportar datos de HPF y la columna X+4 se asigna para transportar datos de BEP. De modo similar, la configuración de bits en la columna X indica que la columna 17277 de la carga útil 708 se asigna para transportar datos de TDM y las columnas 17278 a 17280 se asignan para transportar datos de HPF.

La trama STM-64/OC-192 puede transportarse en serie mediante una interfaz de SONET/SDH sobre una base de fila por fila. Más concretamente, la primera fila de las columnas 1 a 17280 inclusive puede transportarse antes de transportar la segunda fila de las columnas 1 a 17280 inclusive. En consecuencia, el flujo de datos en serie que transporta la trama STM-64/OC-192 incluye nueve secciones, en donde cada sección contiene partes de la sobrecarga de transporte 212, el TS Map 704 y la carga útil 708. Por el contrario, la sobrecarga de transporte 212, el TS Map 208 y la carga útil 210 se suelen comunicar en secciones distintas mediante una interfaz de Ethernet, según se ilustra en las Figuras 2A y 2B. Es decir, cada una de la sobrecarga de transporte 212, TS Map 208 y la carga útil 210 de la trama H-TDM puede comunicarse en su integridad mediante la interfaz Ethernet antes de la comunicación de la sección siguiente. En consecuencia, cuando se comunica la trama H-TDM por intermedio de una interfaz Ethernet y posteriormente, se comunica la trama H-TDM mediante una interfaz de SONET/SDH, cada sección de la trama Ethernet puede necesitar un mapeado de puesta en correspondencia en un conjunto de columnas correspondiente en una trama de SONET/SDH. Lo inverso puede ser verdadero cuando se convierte la trama H-TDM desde un formato de SONET/SDH a un formato Ethernet.

Según se ilustra en la Figura 10A, cuando TS Map 208 se transporta mediante una interfaz de Ethernet, TS Map 208

puede visualizarse como nueve secciones idénticas que se comunican en serie. Para el mapeado de correspondencia del TS Map 208 con una trama SONET/SDH, el TS Map 208 puede memorizarse y distribuirse para cada fila de la trama SONET/SDH sobre una base de sección por sección. Un procesamiento similar puede ocurrir para las secciones de la sobrecarga de transporte 212 y la carga útil 210 de la trama H-TDM.

La Figura 10B ilustra una disposición alternativa para la trama H-TDM. Más concretamente, la trama H-TDM puede organizarse de modo que la sobrecarga de transporte 212, el TS Map 208, y la carga útil 210 estén dispuestos en nueve secciones consecutivas 1002 con cada sección incluyendo una parte de la sobrecarga 212, el TS Map 208 y la carga útil 210. Organizando la trama H-TDM de esta manera, el contenido de la trama H-TDM puede transportarse idénticamente mediante interfaces Ethernet y mediante interfaces SONET/SDH. Aunque lo que antecede describe una de las dificultades de transporte de la trama H-TDM mediante interfaces SONET/SDH e interfaces Ethernet, pueden considerarse muchos otros factores y disposiciones. Las solicitudes de patente provisionales antes citadas proporcionan una descripción detallada del proceso de mapeado de puesta en correspondencia de la trama H-TDM entre interfaces Ethernet y SONET/SDH.

La Figura 11 ilustra un ejemplo de un diagrama de bloques funcionales de los puertos de salida y entrada de dos nodos. Un puerto de salida 1102 de un nodo A está en comunicación con un puerto de entrada 1104 de un nodo B y transporta el sistema de intervalos temporales síncronos superpuestos de H-TDM por intermedio de interfaces de capa física (PHY). El puerto de salida 1102 está configurado para recibir datos de BEP, HPF y TDM así como datos de sincronización, p.ej., el Sync 206 y datos de control. Los datos de control incluyen la sobrecarga de transporte 212, el TS Map 208 y cualquier dato de control adicional, tal como SFD 204, requerido para transportar el sistema de intervalos temporales síncronos superpuestos de H-TDM por intermedio de una interfaz PHY de salida 1106. Un controlador 1108 utiliza los datos de control para multiplexar los diversos flujos de datos, según se describe a continuación. Una memoria intermedia 1110 puede memorizar los datos de BEP hasta que los datos de BEP se necesiten por un multiplexor de salida 1112. El multiplexor de salida 1112 multiplexa los datos procedentes del controlador 1108 y de la memoria intermedia 1110 con los datos de HPF, los datos de TDM y los datos de sincronización. Más concretamente, el multiplexor de salida 1112 selecciona datos desde una de las entradas para cada octeto dentro de la ventana de sincronización. A la selección de una entrada, el multiplexor de salida 1112 comunica los datos recibidos en la entrada seleccionada para la interfaz PHY de salida 1106 para el transporte a través de un medio de comunicación.

El controlador 1108 da instrucciones al multiplexor de salida 1112 para seleccionar cada una de las entrada/salida en conformidad con TS Map 208. A modo de ejemplo, dentro de los intervalos de guarda 202 del sistema de intervalos temporales síncronos superpuestos de H-TDM, el controlador 1108 da instrucciones al multiplexor de salida 1112 para seleccionar los datos BEP procedentes de la memoria intermedia 1110. A la recepción de SFD 204, el controlador 1108 da instrucciones al multiplexor de salida 1112 para aceptar una parte de la sobrecarga de transporte 212 procedente del controlador 1118 y luego, aceptar el Sync 206 procedente de la entrada de sincronización. A la terminación de Sync 206, el controlador 1108 da instrucciones al multiplexor de salida 1112 para aceptar el resto de la sobrecarga de transporte 212 y el TS Map 208 desde el controlador 1108. A la terminación de la sobrecarga de transporte 212 y del TS Map 208, el controlador da instrucciones al multiplexor de salida 1112 para aceptar los datos de TDM, los datos de HPF y los datos de BEP en conformidad con el TS Map 208. Por último, a la terminación de la carga útil 210, el controlador 1108 da instrucciones al multiplexor de salida 1112 para aceptar los datos BEP procedentes de la memoria intermedia 1110, p.ej., para el transporte durante el intervalo de guardia 202.

El puerto de entrada 1104 del nodo B está configurado para recibir los datos transportados mediante el medio de comunicación en una interfaz PHY de entrada 1114. La interfaz PHY de entrada 1114 reenvía los datos a un demultiplexor de entrada 1116, que demultiplexa el flujo de datos. El demultiplexor de entrada 1116 reenvía también los datos a un controlador 1118, una memoria intermedia 1120, una salida de datos TDM, una salida de datos HPF o una salida de sincronización según las instrucciones dadas por el controlador 1118. La memoria intermedia 1120 puede configurarse para memorizar los datos de BEP recibidos desde el demultiplexor de entrada 1116. El controlador 1118 puede controlar el demultiplexor de entrada 1116 utilizando la información de control recibida desde el demultiplexor de entrada 1116 y/o desde otros componentes en el nodo B. Como parte del control el controlador 1118 utiliza el TS Map 208 recibido por intermedio de la interfaz PHY de entrada 1114 para controlar la operación de demultiplexación del flujo de datos.

De modo similar al controlador 1108, el controlador 1118 da instrucciones al demultiplexor de entrada 1116 para reenviar los datos recibidos a las salidas en conformidad con el TS Map 208. A modo de ejemplo, dentro de los intervalos de guarda 202 del sistema de intervalos temporales síncronos superpuestos de H-TDM, el controlador 1118 da instrucciones al demultiplexor de entrada 1116 para enviar los datos de BEP recibidos a la memoria intermedia 1120. Cuando se recibe el SFD 204, el controlador 1118 da instrucciones al demultiplexor de entrada 1116 para enviar los datos recibidos al controlador 1118. En una forma de realización alternativa, el demultiplexor de entrada 1116 puede contener una lógica que reconoce el SFD 204 de modo que los datos recibidos se envíen al controlador 1118 sin necesidad de ninguna instrucción del controlador 1118. Si los datos recibidos después de SFD 204 incluyen una parte de la sobrecarga de transporte 212, el demultiplexor de entrada 1116 envía dichos datos al controlador 1118. El demultiplexor de entrada 1116 envía luego el Sync 206 a la salida de sincronización. Posteriormente al Sync 206 el demultiplexor de entrada 1116 puede enviar el resto de la sobrecarga de transporte

212 y el TS Map 208 al controlador 1118. El controlador 1118 puede utilizar, entonces, el TS Map 208 recibido para dar instrucciones al demultiplexor de entrada 1116 para distribuir los datos recibidos a la salida de datos de TDM, la salida de datos de HPF y la memoria intermedia 1120. Por último, a la terminación de la carga útil 210, el controlador 1118 da instrucciones, de nuevo, al demultiplexor de entrada 1116 para enviar los datos de BEP recibidos durante el intervalo de guarda 202 a la memoria intermedia 1120.

El puerto de salida 1102 y el puerto de entrada 1104 pueden ponerse en práctica, cada uno de ellos, como parte de una interfaz de comunicaciones entre dos nodos. En una forma de realización, el puerto de salida 1102 y el puerto de entrada 1104 pueden ponerse en práctica cada uno de ellos como parte de una tarjeta de línea que soporta comunicaciones de redes básicas. Además, aunque solamente el puerto de salida 1102 del nodo A y el puerto de entrada 1104 del nodo B se ilustran, comunicaciones en dúplex completo pueden soportarse por cada uno de los nodos A y B incluyendo un puerto de entrada en el nodo A y un puerto de salida en el nodo B. En tal caso, además del puerto de salida 1102 del nodo A y del puerto de entrada 1104 del nodo B que se comunican entre sí, un puerto de salida del nodo B y un puerto de entrada del nodo A pueden comunicarse también entre sí.

Aunque la carga útil 210 anteriormente descrita solamente contiene una instancia operativa de cada tipo de tráfico, la carga útil 210 puede contener también múltiples instancias operativas de cada tipo de tráfico, según se ilustra en la Figura 12. Más concretamente, la Figura 12 ilustra parte de una carga útil 210 que incluye una pluralidad de instancias operativas de datos de BEP, una pluralidad de instancias de datos de TDM y una pluralidad de instancias de datos de HPF. Además, aunque cada instancia pueda ser un conjunto completo de datos, se considera que cada instancia operativa no puede completarse antes de proseguir con otra instancia. A modo de ejemplo, la Figura 12 ilustra tres instancias de datos de BEP, BEP1, BEP2 y BEP3, que pueden representar datos procedentes de tres cargas útiles Ethernet separadas. BEP1 puede no completarse necesariamente antes del inicio de TDM1. De forma análoga, BEP2 puede seguir TDM1 incluso cuando BEP1 pueda no estar completa. De este modo, los intervalos temporales siguientes de la Figura 12 pueden contener la terminación de BEP1, BEP 2 y BEP3.

La Figura 13 ilustra una modificación del diagrama de bloques funcionales de la Figura 11. Más concretamente, la Figura 11 ilustra puertos de salida y de entrada modificados que transportan múltiples instancias de cada tipo de datos en el sistema de intervalos temporales síncronos superpuestos de H-TDM por intermedio de interfaces PHY. Según se ilustra en la Figura 13, el puerto de salida 1102 del nodo A incluye la interfaz PHY de salida 1106 y el controlador 1108 según se describió con anterioridad. El puerto de salida 1102 ha sido modificado de modo que múltiples instancias de datos de BEP, de HPF y TDM puedan recibirse. A modo de ejemplo, los datos de BEP pueden incluir instancias BEP1 a BEPX inclusive, los datos de TDM pueden incluir instancias de TDM1 a TDMY inclusive, y los datos de HPF pueden incluir instancias de HPF1 a HPFZ inclusive. Estas diversas instancias pueden multiplexarse según se describió con anterioridad.

Según se ilustra en la Figura 13, cada instancia de datos de BEP puede ser objeto de entrada a una de entre una pluralidad de memorias intermedias 1302. Aunque cada una de las instancias de datos de BEP se ilustran como siendo una entrada en memorias intermedias separadas 1302, se considera que las memorias intermedias 1302 pueden ponerse en práctica como una memoria única con cada instancia de datos de BEP permitida para la escritura de datos para diferentes gamas de direcciones de la memoria, o de cualquier otro modo, dividir, de forma lógica, la memoria para proporcionar las memorias intermedias 1302. Las salidas de la memoria intermedia, las otras instancias de datos, los datos de control y los datos de sincronización se alimentan a un multiplexor de salida 1304, que multiplexa las diversas entradas en conformidad con TS Map 208. En esta forma de realización, TS Map 208 puede modificarse respecto a la forma de realización ilustrada en la Figura 8B para incluir más bits, de modo que cada tipo de datos pueda incluir múltiples instancias. A modo de ejemplo, con tres bits para cada intervalo temporal en la carga útil 210, puede existir hasta cuatro instancias de datos de BEP, dos instancias de datos de TDM y dos instancias de datos de HPF en el TS Map 208.

El puerto de entrada 1104 del nodo B incluye la interfaz PHY de entrada 1114 y el controlador 1118 según se describió con anterioridad. El puerto de entrada 1104 ha sido modificado para incluir un demultiplexor de entrada 1306 que reenvía los datos demultiplexados a las diversas salidas en conformidad con el TS Map 208. El puerto de entrada 1104 ha sido modificado, además, para incluir una pluralidad de memorias intermedias de salida 1308 que pueden ponerse en práctica de forma similar a las memorias intermedias 1302 según se describió con anterioridad.

Cuando los puertos de salida y de entrada contienen múltiples instancias de un tipo de datos, las instancias dentro del tipo de datos pueden tener una prioridad establecida de modo que las instancias individuales se traten de forma distinta. A modo de ejemplo, si existen dos instancias de BEP, BEP1 y BEP2, entonces BEP1 puede tener una prioridad superior a BEP2 de modo que se transporten todos los datos de BEP1, p.ej., en las bandas de guarda, los intervalos temporales de BEP y los intervalos temporales de HPF inactivos antes de que se transporte cualquiera de los datos de BEP2. Como alternativa, puede crearse una política operativa que favorezca a los datos de BEP1 sobre los datos de BEP2 en la selección del transporte, pero que permita que se transporten algunos datos de BEP2 en cada trama incluso cuando no se hayan transportado la totalidad de los datos de BEP1. Prioridades y políticas operativas similares pueden crearse también para los datos de TDM y de HPF, si fuera deseable.

Aunque el sistema de intervalos temporales síncronos superpuestos de H-TDM permite la comunicación de datos de

TDM y de datos de BEP por intermedio de las interfaces de comunicaciones Ethernet, el sistema de intervalos temporales síncronos superpuestos de H-TDM no puede ser compatible hacia atrás con algunos nodos Ethernet en la capa de control de acceso al soporte (MAC) o la capa 2 de OSI. En tal caso, un modo operativo de Huawei jumbo (H-JUMBO) puede dividir el sistema de intervalos temporales síncronos superpuestos de H-TDM en una pluralidad de secciones y encapsular cada sección con el entramado de la capa 2 de Ethernet. Al hacer esta operación, el modo operativo H-JUMBO permite el transporte de cargas útiles de H-TDM a través de nodos Ethernet que no soportan el sistema de intervalos temporales síncronos superpuestos de H-TDM.

5

35

40

45

50

55

60

65

La Figura 14 ilustra un ejemplo del sistema de intervalos temporales síncronos superpuestos de H-TDM dividido utilizando el modo operativo H-JUMBO. Según se describió con anterioridad, el modo operativo H-JUMBO divide el sistema de intervalos temporales síncronos superpuestos en secciones que se encapsulan en tramas Ethernet. Las secciones pueden no estar necesariamente en correspondencia con cualquier contenido particular dentro del sistema de intervalos temporales síncronos superpuestos, sino que, en cambio, pueden seleccionarse sobre la base de la cantidad de los octetos. Aunque las secciones puedan contener cualquier cantidad de datos, en formas de realización específicas, las secciones pueden contener desde aproximadamente 42 octetos a aproximadamente 1500 octetos en paquetes estándar y pueden contener más de 1500 octetos, p.ej., desde aproximadamente 9000 a aproximadamente 12000 octetos en paquetes jumbo. En una forma de realización específica, las tramas de jumbo Ethernet con una carga útil de aproximadamente 9600 octetos se utilizan en el modo operativo H-JUMBO.

Según se ilustra en la Figura 14, cada división del sistema de intervalos temporales síncronos superpuestos de H-TDM puede insertarse una carga útil jumbo 1404 que puede encapsularse dentro del entramado de la capa 2 de Ethernet 1402. El entramado de la capa 2 de Ethernet 1406 con una parte del sistema de intervalos temporales síncronos superpuestos de H-TDM a través de uno o más nodos Ethernet estándar. Con la carga útil de aproximadamente 9600 octetos para cada una de las tramas jumbo Ethernet 506, el sistema de intervalos temporales síncronos superpuestos de H-TDM puede encapsularse dentro de aproximadamente dieciséis tramas de jumbo Ethernet 1406. El modo operativo de H-JUMBO permite el transporte transparente de cargas útiles de H-TDM a través de redes Ethernet que no soportan el modo operativo H-TDM. En una forma de realización, VIDs opcionales y/o TPIDs pueden incluirse en las tramas de jumbo Ethernet 1406 para prestar asistencia en el reordenamiento de los paquetes recibidos. En otra forma de realización, las tramas jumbo Ethernet 506 pueden transportarse en serie para garantizar un ordenamiento adecuado.

La Figura 15 ilustra otra modificación del diagrama de bloques funcionales de la Figura 11. Más concretamente, la Figura 15 ilustra puertos de salida y de entrada modificados que transportan el sistema de intervalos temporales síncronos superpuestos de H-TDM en conformidad con el modo operativo H-JUMBO. El puerto de salida 1102 del nodo A incluye la interfaz PHY de salida 1106 y un multiplexor 1502, que es similar al multiplexor 1112 y al multiplexor 1304 anteriormente descritos. Sin embargo, el puerto de salida 1102 ha sido modificado de modo que el sistema de intervalos temporales síncronos superpuestos de H-TDM pueda dividirse mediante una partición de flujo H-TDM 1504. Cada una de las particiones puede ser objeto de salida desde la partición del flujo H-TDM 1504 a un entramador de capa 2 de Ethernet 1506. El entramador de capa 2 de Ethernet 1506 encapsula cada partición en una trama MAC de Ethernet. El entramador de capa 2 de Ethernet 1506 proporciona, a la salida, un flujo de datos compatible con la capa 2 de Ethernet. El flujo de datos compatible con la capa 2 de Ethernet. El flujo de datos compatible con la capa 2 de Ethernet puede transportarse por intermedio de la interfaz PHY 1106 mediante al menos un nodo Ethernet de terceros 1508 que puede ser un conmutador, un enrutador o un puente. El nodo Ethernet de terceros 1508 puede comunicar, entonces, el flujo de datos compatible con Ethernet capa 2 a la interfaz PHY de Ethernet 1114 en el puerto de entrada 1104.

En el nodo B, el puerto de entrada 1104 incluye la interfaz PHY de salida 1114 y un demultiplexor 1514, que pueden ser similares al demultiplexor 1116 y al demultiplexor 1306 anteriormente descritos. Sin embargo, el puerto de entrada 1104 ha sido modificado de modo que el flujo de datos compatible con Ethernet capa 2 recibido pueda ser objeto de entrada a un desentramador de Ethernet capa 2 1510 para extraer cada partición del sistema de intervalos temporales síncronos superpuestos de H-TDM. Las particiones extraídas del sistema de intervalos temporales síncronos superpuestos de H-TDM pueden ser luego objeto de entrada a un reconstructor de flujos de H-TDM 1512 que reconstruye el sistema de intervalos temporales síncronos superpuestos de H-TDM. El sistema de intervalos temporales síncronos superpuestos de H-TDM reconstruido puede aplicarse luego a la entrada del demultiplexor 1512 y proseguir en la forma anteriormente descrita.

Las Figuras 11, 13 y 15 describen cómo el sistema de intervalos temporales síncronos superpuestos de H-TDM puede comunicarse entre nodos entre nodos mediante interfaces de capa física. Por el contrario, la Figura 16 es un diagrama de bloques funcionales de algunos de los componentes internos de un nodo 1600. Más concretamente, la Figura 16 ilustra una sub-capa de reconciliación entre las capas PHY y MAC existentes que transportan el sistema de intervalos temporales síncronos superpuestos de H-TDM por intermedio del nodo 1600. Dicha forma de realización puede utilizar TDM estándar y la conmutación de paquetes, y no puede modificar los componentes de PHY y MAC ya existentes. Los expertos en esta técnica apreciarán que aunque la Figura 16 ilustra un solo puerto con un solo puerto de entrada y un puerto de salida, el nodo 1600 puede tener una pluralidad de puertos de entrada y una pluralidad de puertos de entrada y que la estructura de conmutación puede encaminar los diversos tipos de datos entre los puertos de entrada y los puertos de salida.

Según se ilustra en la Figura 16, un controlador de entrada 1602 puede recibir un flujo de datos por intermedio de una interfaz PHY 1604 y separar el tráfico de HPF y el tráfico de TDM con respecto al tráfico de paquetes de BEP. El controlador de entrada 1602 puede incluir uno de los demultiplexores de entrada 1306 o 1116 y otros circuitos o lógica que permitan al controlador de entrada 1602 comunicar el sistema de intervalos temporales síncronos superpuestos de H-TDM por intermedio del nodo 1600. El controlador de entrada 1602 puede mantener una copia del TS Map 208 en una memoria 1606, tal como en el controlador 1118 anteriormente descrito. El controlador de entrada 1602 puede enviar los datos de TDM y de HPF directamente a un conmutador de TDM 1608 que enruta los datos a los diversos puertos de salida. Por el contrario, los datos de BEP pueden enviarse a una memoria intermedia de entrada 1610, que puede ser similar a la memoria intermedia 1120 y las memorias intermedias 1308 anteriormente descritas.

5

10

15

20

25

30

35

40

45

50

55

60

65

El controlador de entrada 1602 puede dar instrucciones a la memoria intermedia de entrada 1610 para memorizar datos de BEP que se reciben desde el controlador de entrada 1602 en la memoria intermedia de entrada 1610. El controlador de entrada 1602 puede también dar instrucciones a la memoria intermedia de entrada 1610 para enviar datos desde la memoria intermedia de entrada 1610 a la lógica de MAC 1612. La memoria intermedia de entrada 1610 puede operar como una memoria de tipo 'primero en entrar, primero en salir' (FIFO), de modo que los datos de BEP se conmuten a través del nodo 1600 en el orden en que sean recibidos. La memoria intermedia de entrada 1610 puede memorizar el tráfico de BEP en ruta a un conmutador de paquetes 1614 mientras se atenúan y ocultan las interrupciones y retardos que se causan por la multiplexación de múltiples tipos de datos en el sistema de intervalos temporales síncronos superpuestos de túnel H-TDM. En una forma de realización, la memoria intermedia de entrada 1610 puede memorizar los datos de BEP al menos hasta que se haya recibido un paquete completo. En otra forma de realización, los datos de BEP memorizados en la memoria intermedia de entrada pueden comenzar a conmutarse antes de la recepción de un paquete completo. Para el tráfico de BEP de atajo operativo, el retardo del paquete de entrada debido a la memoria intermedia de entrada 1610 puede minimizarse si se conoce la longitud del paquete puesto que el número de interrupciones de intervalos temporales es siempre determinístico. Además, la memoria intermedia de entrada puede soportar un tráfico de atajo operativo calculando la cantidad mínima de tiempo en que se memoriza un paquete antes de que pueda iniciar la transmisión del paquete a un conmutador de paquetes 1614 puesto que el número de intervalos temporales en uso es conocido para el controlador de entrada debido a la memorización del TS Map 208 en la memoria 1606. Dicha forma de realización elimina la posibilidad de necesitar datos antes de que estén disponibles, que una condición conocida como de sub-ejecución.

La lógica de MAC 1612 proporciona los datos de BEP al conmutador de paquetes 1614 de modo que los datos de BEP puedan conmutarse a través del nodo 1600. En otras formas de realización, la lógica de MAC 1612 puede ponerse en práctica como lógica de Ethernet MAC o cualquier otra lógica conocida para los expertos en esta técnica. Después de conmutarse por el conmutador de paquetes 1614, los datos de BEP se proporcionan a una segunda lógica MAC 1612 y posteriormente, se memorizan en una memoria intermedia de salida 1616. La memoria intermedia de salida 1616 puede memorizar los datos de paquetes BEP para atenuar los retardos en el tráfico de paquetes causado por la inserción del tráfico de HPF y de TDM en el flujo de datos de salida. Aunque el conmutador TDM 1608 y el conmutador de paquetes 1614 se ilustran como estructuras de conmutación separadas, pueden combinarse en una estructura de conmutación unificada. Varias arquitecturas para proporcionar controladores de entrada y de salida que se comunican a través de una estructura de conmutación unificada se detallan en las solicitudes provisionales antes citadas.

Para HPFs que sean datos de paquetes de alta prioridad, el HPF puede comunicarse al conmutador de paquetes 1614 para el transporte a través del nodo 1600. En este caso, los datos de paquetes de alta prioridad pueden enviarse directamente a la primera lógica de MAC 1612 mediante el conmutador de paquetes 1614 y ser objeto de salida desde la segunda lógica MAC 1612 sin ser memorizados en la memoria intermedia de entrada 1610 o la memoria intermedia de salida 1616. En una forma de realización alternativa, los datos de paquetes de alta prioridad pueden proporcionarse a una memoria intermedia de entrada y de salida separadas que se utilizan exclusivamente para proporcionar datos de paquetes de alta prioridad a y desde el conmutador de paquetes 1614. Además en la alternativa, los paquetes de alta prioridad pueden tener su propia estructura de conmutación y pueden no encaminarse a través de cualesquiera memorias intermedias. En otra forma de realización, todos los datos de HPF se conmutan utilizando el conmutador de TDM 1608 haciendo caso omiso de si los datos son datos de paquetes de alta prioridad o no lo son. Utilizando estas formas de realización, los datos de paquetes de alta prioridad que los datos de BEP de más baja prioridad.

El controlador de salida 1618 puede recibir información de control, tal como el TS Map 208 y el Sync 206, desde el controlador de entrada 1602 por intermedio de un canal de control 1620. Más concretamente, el controlador de salida 1618 mantiene una copia del TS Map 208 en una memoria 1622 de modo que el controlador de salida 1618 conozca cómo multiplexar tráfico de TDM, de HPF y BEP con el TS Map 208 y el Sync 206. El controlador de salida 1618 proporciona también datos de control a la memoria intermedia de salida 1616 de modo que los datos de BEP puedan eliminarse de la memoria intermedia de salida 1616 cuando sea necesario en conformidad con el TS Map 208 memorizado en la memoria 1622. De modo similar, el controlador de salida 1618 recibe datos de TDM y de HPF procedentes del conmutador TDM 1608 y reenvía los datos de TDM y de HPF al flujo de datos de salida en conformidad con el TS Map 208 memorizado en la memoria 1622. A la recepción de varios tipos de tráfico desde el conmutador de TDM 1608 y la memoria intermedia de salida 1616, un controlador de salida 1618 multiplexa el tráfico

con información de control y temporización, tal como el TS Map 208 y el Sync 206 y transmite los datos multiplexados por intermedio de una interfaz PHY 1624. El controlador de salida 1618 puede incluir uno de entre el multiplexor de salida 1112 o 1304 u otros circuitos o lógica que permitan al controlador de salida 1618 enviar el sistema de intervalos temporales síncronos superpuestos de H-TDM por intermedio de la interfaz PHY 1624.

5

10

15

20

25

30

35

50

55

El controlador de salida 1618 puede proporcionar también un control de flujo de contrapresión a la memoria intermedia de salida 1616, con lo que se controla el flujo de tráfico desde el conmutador de paquetes 1614 a la memoria intermedia de salida 1616. El control de flujo de contrapresión proporciona un mecanismo mediante el cual el flujo de datos de BEP puede ajustarse sin que ello afecte al flujo de datos de TDM y de HPF. En una forma de realización, la memoria intermedia de salida 1616 puede suministrar el control del flujo de contrapresión al controlador de entrada 1602. El controlador de entrada 1602 puede proporcionar entonces instrucciones a la memoria intermedia de entrada 1610 para variar el flujo de datos de BEP enviados al conmutador de paquetes 1614. En una forma de realización alternativa, el control del flujo de contrapresión puede suministrarse directamente al conmutador de paquetes 1614, según se ilustra por la línea de trazados, con lo que se controla el flujo de contrapresión puede estar conforme a la norma IEEE 802.3x, que se incorpora aquí por referencia como si se reprodujera en su integridad.

El controlador de salida 1618 puede suministrar un control de flujo de contrapresión para aumentar o disminuir el flujo de tráfico. A modo de ejemplo, cuando los datos de BEP en la memoria intermedia de salida 1616 alcanza un umbral de capacidad superior, el controlador de salida 1618 puede proporcionar un control de flujo de contrapresión para disminuir el flujo de tráfico desde el conmutador de paquetes 1614 de modo que los datos no sean objeto de sobreescritura en la memoria intermedia de salida 1616. De modo similar, cuando los datos de BEP en la memoria intermedia de salida 1616 alcanzan un umbral de capacidad más bajo, el controlador de salida 1618 puede proporcionar un control de flujo de contrapresión para aumentar el flujo de tráfico desde el conmutador de paquetes 1614, de modo que la memoria intermedia de salida 1616 pueda mantener una cantidad mínima de datos de BEP.

Cuando el controlador de entrada 1602 recibe el control de flujo de contrapresión, el controlador de entrada puede proporcionar instrucciones a la memoria intermedia de entrada 1610 para aumentar o disminuir una cantidad de datos de BEP que se envía al conmutador de paquetes 1614. A modo de ejemplo, si el control de flujo de contrapresión demanda una reducción en el flujo de tráfico desde el conmutador de paquetes 1614, en tal caso, el controlador de entrada 1602 puede dar instrucciones a la memoria intermedia de entrada 1610 para disminuir la cantidad de datos de BEP enviados al conmutador de paquetes 1614. En algunas situaciones operativas, el controlador de entrada puede dar instrucciones a la memoria intermedia de entrada 1610 para interrumpir el envío de todos los datos de BEP al conmutador de paquetes 1614. De modo similar, si el control de flujo de contrapresión demanda un aumento en el flujo de tráfico procedente del conmutador de paquetes 1614, en tal caso, el controlador de entrada 1602 puede dar instrucciones a la memoria intermedia de entrada 1610 para aumentar la cantidad de datos de BEP enviados al conmutador de paquetes 1614.