# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

①Número de publicación: 2 610 187

(21) Número de solicitud: 201531371

(51) Int. Cl.:

H01L 21/06 (2006.01)

(12)

#### PATENTE DE INVENCIÓN

B1

22) Fecha de presentación:

25.09.2015

(43) Fecha de publicación de la solicitud:

26.04.2017

Fecha de concesión:

31.01.2018

(45) Fecha de publicación de la concesión:

07.02.2018

(56) Se remite a la solicitud internacional:

PCT/ES2016/070662

(73) Titular/es:

CONSEJO SUPERIOR DE INVESTIGACIONES CIENTÍFICAS (CSIC) (100.0%) C/ Serrano, nº 117 28006 Madrid (Madrid) ES

(72) Inventor/es:

ULLÁN COMES, Miguel; FERNÉNDEZ MARTÍNEZ, Pablo; HIDALGO VILLENA, Salvador; FLORES GUAL, David y GIULIO VILLANI, Enrico

(74) Agente/Representante:

PONS ARIÑO, Ángel

54 Título: TRANSISTOR TIPO JFET Y MÉTODO DE OBTENCIÓN DEL MISMO

(57) Resumen:

Se detalla un dispositivo semiconductor correspondiente a un transistor tipo JFET que presenta una disposición multicapa de varios materiales, dando como resulta de esa disposición un dispositivo transistor tipo JFET vertical; es decir que la corriente fluye desde la parte superior del chip (fuente) hacia la parte inferior (drenador), atravesando todo el bloque de silicio, mientras que en un segundo aspecto de la invención se tiene un método para la fabricación del dispositivo JFET del primer aspecto; método que hace uso de la técnica de procesamiento DRIE (Deep reactive-ion etching).

#### TRANSISTOR TIPO JFET Y MÉTODO DE OBTENCIÓN DEL MISMO

### **DESCRIPCIÓN**

#### 5 **OBJETO DE LA INVENCIÓN**

15

20

25

30

El objeto de la invención se enmarca en el campo de los dispositivos semiconductores y sus procesos de fabricación.

Más concretamente el objeto de la invención va dirigido a un dispositivo transistor tipo JFET y a un método de obtención del mismo.

#### **ANTECEDENTES DE LA INVENCIÓN**

Los dispositivos electrónicos conocidos como JFET (*Junction Field-Effect Transistor*, en español transistor de efecto de campo de juntura o unión) son circuitos basados en el efecto de campo eléctrico cuyos valores de entrada son tensiones eléctricas, en concreto la tensión entre terminales S (fuente) y G (puerta), VGS. Según este valor de entrada VGS, la salida del transistor tipo JFET presentará una curva característica que se simplifica definiendo en ella tres zonas con ecuaciones definidas: corte, óhmica y saturación.

Físicamente, un transistor tipo JFET de los denominados "canal P" está formado por una pastilla de semiconductor tipo P en cuyos extremos se sitúan dos terminales de salida (drenador y fuente) flanqueada por dos regiones con dopaje de tipo N en las que se conectan dos terminales conectados entre sí (puerta). Al aplicar una tensión positiva VGS entre puerta y fuente, las zonas N crean a su alrededor sendas zonas en las que el paso de electrones (corriente ID) queda cortado, llamadas zonas de exclusión. Cuando esta VGS sobrepasa un valor determinado, las zonas de exclusión se extienden hasta tal punto que el paso de electrones ID entre fuente y drenador queda completamente cortado. A ese valor de VGS se le denomina Vp. Para un JFET "canal N" las zonas p y n se invierten, y las VGS y Vp son negativas, cortándose la corriente para tensiones menores que Vp (negativas).

Así, según el valor de VGS se definen dos primeras zonas; una activa para tensiones menores que Vp y una zona de corte para tensiones mayores que Vp. Los distintos valores de la ID en función de la VGS vienen dados por una gráfica o ecuación denominada ecuación de entrada.

5

En la zona activa, al permitirse el paso de corriente, el transistor dará una salida en el circuito que viene definida por la propia corriente de drenador (ID) y la tensión entre el drenador y la fuente VDS. A la gráfica o ecuación que relaciona estás dos variables se le denomina ecuación de salida, y en ella es donde se distinguen las dos zonas de funcionamiento de activa: óhmica y saturación.

10

Este tipo de dispositivos son conocidos, a la par que aquellos procedimientos de obtención de los mismos; en este sentido se tiene conocimiento de diversos documentos como el US8068321B2 en el que se detalla un JFET convencional para la protección contra sobretensiones (protección contra picos de tensión no deseados) de un convertidor DC / DC de baja tensión. No obstante, el dispositivo es un interruptor normalmente apagado (Normally-off) que sólo se activa cuando tiene que proteger el sistema principal soportando la corriente no deseada y donde la conducción se basa en electrones y la tecnología se basa en un substrato N+ inicial sobre el que se crece una capa epitaxial N- delgada. A continuación, se realizan implantes para crear la puerta (boro) y la fuente (fósforo).

20

25

15

Asimismo en el documento US6251716B1se describe un JFET con baja resistencia y alta velocidad de conmutación en dispositivos de alta corriente (100 A en chips de gran área). Sin embargo, la capacidad en tensión está limitada por el espesor de la capa N epitaxial. Además, la citada alta velocidad de conmutación no se puede lograr si se requiere una capacidad de alta tensión y la conducción se basa en electrones y la tecnología se basa en un substrato N+ inicial, sobre el quese hace crecer una capa delgada N- epitaxial, para a continuación crear las múltiples puertas (boro) y la región de drenador (fósforo).

30

US8310007B2 detalla una integración monolítica de un transistor tipo NMOS lateral y un transistor tipo NMOS vertical, para implementar un tramo de un convertidor de fase. El funcionamiento en conducción está determinado por la configuración de las capas epitaxiales N y P crecidas en la parte superior del sustrato N+. La puerta del NMOS

vertical se crea con una trinchera más profunda que la de capa eitaxial superior tipo P, finalmente se incluye un aislamiento N+.

En el documento US6380569B1 se describe un dispositivo JFET convencional de alta potencia y alta tensión, aunque en funcionamiento normalmente en apagado y basado en substratos N+ / N- convencionales. Además, una trinchera, que incluye un óxido de puerta y el necesario material de relleno conductor, controla la región JFET. De hecho, presenta difusiones de tipo P en la parte inferior de la trinchera para evitar una ruptura prematura. El dispositivo se dirige a aplicaciones de potencia, donde la velocidad de conmutación no es crucial pero donde se requiere una alta capacidad de corriente.

5

10

15

20

25

30

Finalmente, se tiene que en el documento US20090075435A1 se detalla un dispositivo JFET que se basa en el uso de una región aislante creada en el sustrato, en una zona cercana a su superficie. Se trata esencialmente de un SOI JFET y como consecuencia de ello, la fuente, drenador y electrodos de puerta tienen que ser colocado en el mismo lado del sustrato, dando lugar a un voltaje bajo y la capacidad actual. Las tecnologías de proceso que se describen en US20090075435A1 se basan en la capa de aislante y difieren entre ellas en la forma en que se crea la capa superior de semiconductores y dopado. En todos los casos, se crea una trinchera poco profunda y se llena de polisilicio; la sección transversal del JFET propuesto en US20090075435A1 se basa en corrientes de electrones y su topología es tal que el JFET propuesto en US20090075435A1 proporciona una velocidad de conmutación extremadamente rápida y de bajo nivel parasitario; es decir está diseñado para aplicaciones de alta frecuencia y de baja tensión.

Un dispositivo electrónico que es utilizado ampliamente por los circuitos de distribución de potencia es el interruptor. Muchos de los interruptores del estado del arte utilizados en campos de aplicación estándar no son válidos para aplicaciones de alta radiación, ya que fallan bajo exposición a la radiación. A la vista de lo anterior se tiene que una de las preocupaciones de electrónica de potencia de hoy en día es la búsqueda de circuitos apropiados y dispositivos para la distribución de potencia en sistemas que sean capaces de operar en entornos con presencia de radiación, que es perjudicial.

#### **DESCRIPCIÓN DE LA INVENCIÓN**

5

10

15

20

25

30

En un primer aspecto de la invención se tiene un dispositivo JFET vertical, es decir que la corriente fluye desde la parte superior del chip (fuente) hacia la parte inferior (drenador), atravesando todo el bloque de silicio, mientras que en un segundo aspecto de la invención se tiene un método para la fabricación del dispositivo JFET del primer aspecto; método que hace uso de la técnica de procesamiento DRIE (Deep reactive-ion etching). Mediante el uso de la técnica DRIE, se producen una serie de taladros ciegos que definen una trinchera o más si se requiere, profunda en un bloque de material semiconductor tipo P, trinchera que luego se puede rellenar con una capa conductora de tipo A (P o N). Estas trinchera está configurada preferentemente con una sección circular o poligonal, y define un cuerpo (como por ejemplo un toroide de sección circular o elíptica) que encierra un volumen de semiconductor de tipo B (N o P) trinchera; es decir, visto en planta, el polígono o círculo definido en la superficie del bloque por las paredes de la trinchera es de un material de tipo B (N o P) mientras que al rellenar el taladro ciego/ trinchera con un material conductor de tipo A (P o N) la trinchera actúa como puerta del dispositivo transistor, mientras que la parte de semiconductor del bloque encerrado entre las paredes de la trinchera (los citados círculos o polígonos vistos en planta) será la parte activa intrínseca del transistor JFET, denominada canal. A continuación se procede a crear un contacto de fuente y un contacto de drenador. El contacto de fuente se crea en la parte superior de la superficie del bloque semiconductor y contacto de drenador se crea en la parte inferior del bloque semiconductor de manera que se obtiene un dispositivo transistor JFET de deplexión o empobrecimiento, con una configuración vertical.

El transistor JFET opera como una resistencia con el tamaño del volumen de conducción intrínseco en aquellas situaciones en las que se encuentra en la región lineal cercana a cero o bajos voltajes en la entrada y baja polarización fuente-drenador. En estas situaciones se procede a incrementar la polarización fuente-drenador de tal manera que se produce un incremento de voltaje en el canal y una caída de tensión en el volumen de conducción intrínseca. El volumen de tensión en la parte inferior del canal se agota progresivamente hasta alcanza una tensión de "estrangulamiento" en la que el volumen de tensión en la parte inferior está completamente agotado y la corriente se satura. Por otro lado, si se aumenta la tensión de puerta invirtiendo la unión PN formada con el semiconductor intrínseco, el volumen de tensión del canal se ve cada vez más empobrecido, hasta que esté totalmente vacío en un valor de *Voff* en particular, y

consecuentemente no hay conducción de corriente en el canal.

En una realización del primer aspecto de la invención, el canal es de silicio tipo P, y las trincheras están llenas de un material tipo N como puede ser polisilicio el cual puede encontrarse altamente dopado. De esta manera, el dispositivo puede ser utilizado como un interruptor de potencia resistente a la radiación en aplicaciones de distribución de potencia. El silicio de tipo P no se invierte (a tipo N) por efecto el daño por desplazamiento de la radiación no ionizante, lo que hace que el sustrato sea más resistente para este tipo de radiación. Por otra parte, los únicos óxidos presentes en el dispositivo están en su superficie, lo que hace que el dispositivo sea más robusto frente a los daños por radiación ionizante debido a su configuración vertical. Adiacionalmente, el radio del canal intrínseco se puede reducir hasta obtener una tensión de corte baja que permita el uso de un circuito de control de baja potencia realizado con un proceso CMOS sub-micrónico (DSM) CMOS, lo que hace que el sistema completo sea aún más resistente a la radiación, ya que los procesos DSM son intrínsicamente más resistentes a la radiación. De esta manera, el dispositivo puede ser utilizado como un interruptor de potencia en aplicaciones de distribución de energía en entornos sometidos a alta radiación.

Entre los posibles usos del transistor tipo JFET del primer aspecto de la invención u obtenible mediante el método del segundo aspecto de la invención se tiene el uso como interruptor o como interruptor rad-hard (los denominados *switch* o *switch rad-hard*).

#### **DESCRIPCIÓN DE LOS DIBUJOS**

25

30

5

10

15

20

Para complementar la descripción que se está realizando y con objeto de ayudar a una mejor comprensión de las características de la invención, de acuerdo con un ejemplo preferente de realización práctica de la misma, se acompaña como parte integrante de dicha descripción, un juego de dibujos en donde con carácter ilustrativo y no limitativo, se ha representado lo siguiente:

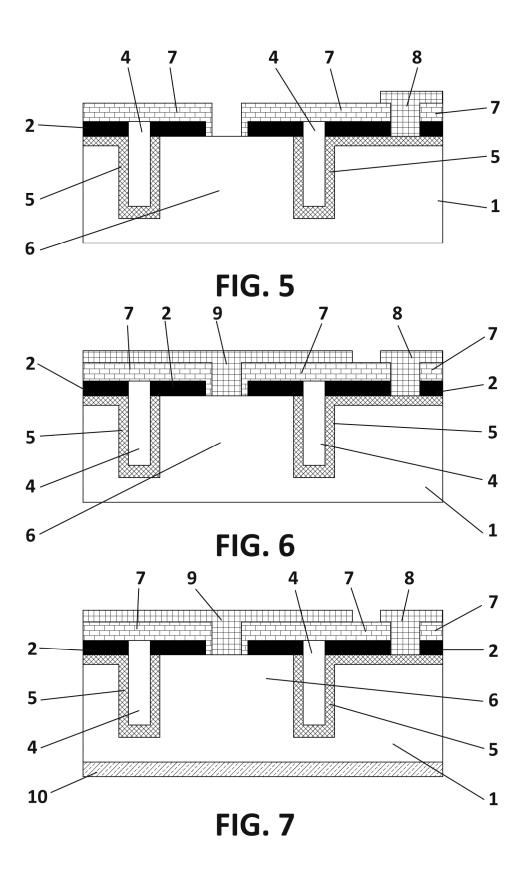

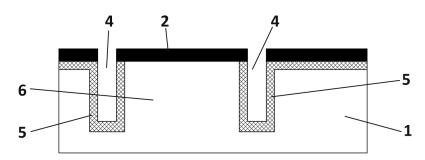

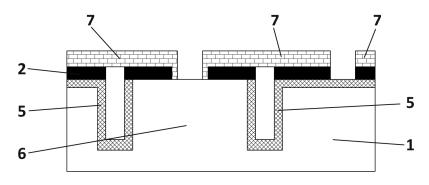

Figuras 1-7.- Muestran una serie de vistas en sección representativas de una realización alternativa del proceso de obtención del dispositivo transistor tipo JFET.

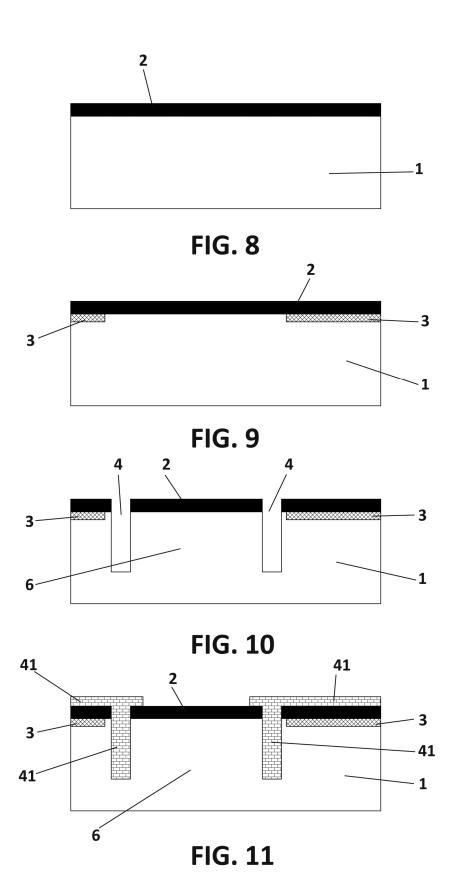

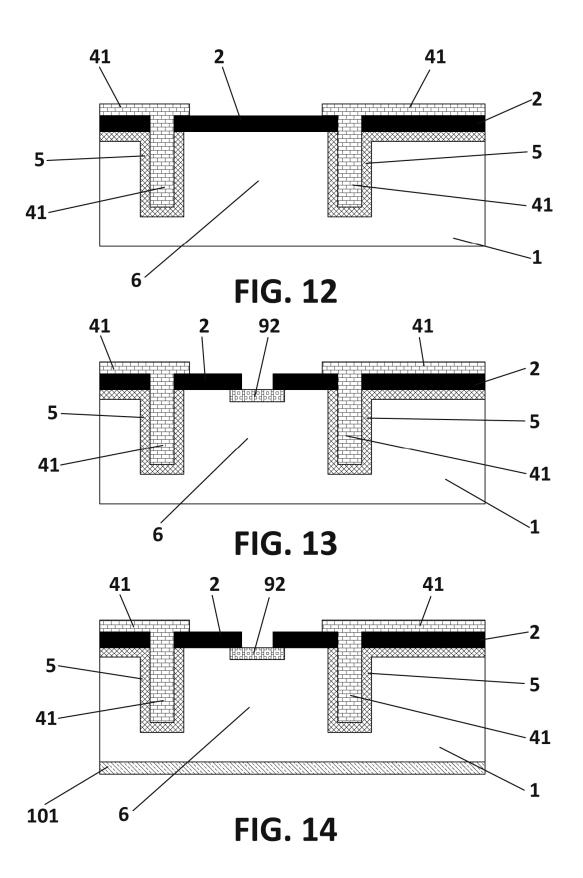

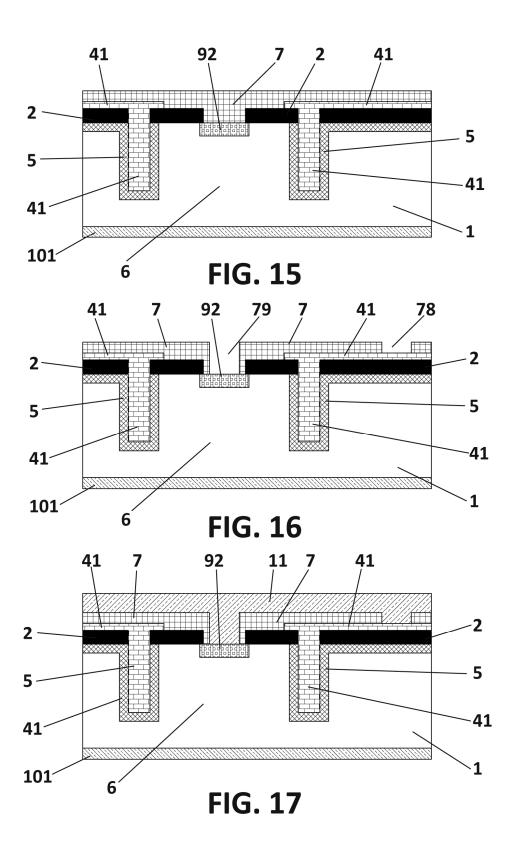

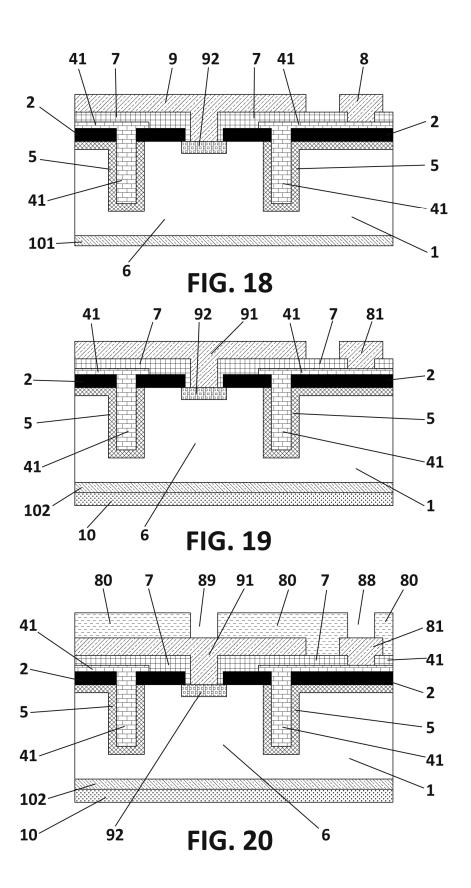

Figuras 8-20.- Muestran una serie de vistas en sección representativas de una realización preferente del proceso de obtención del dispositivo transistor tipo JFET.

#### REALIZACIÓN PREFERENTE DE LA INVENCIÓN

5

10

15

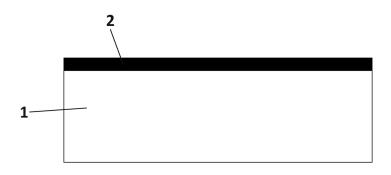

En un ejemplo de realización de la invención se tiene que el segundo aspecto de la misma relacionado con el método de obtención del dispositivo transistor JFET, también referido a lo largo de este ejemplo como dispositivo o simplemente transistor, del primer aspecto de la invención se inicia, en una realización preferente de la invención mostrada en las figuras 8 a 20, se tiene que el segundo aspecto de la misma relacionado con el método de obtención del transistor JFET del primer aspecto de la invención se inicia, tal y como se observa en la figura 8 con un material de partida, un bloque (1) que es un semiconductor tipo P con alta resistividad o, alternativamente, una oblea (1) de semiconductor tipo P con muy baja resistividad sobre la cual se ha realizado un crecimiento epitaxial de una capa de Si con alta resistividad, capa crecida que tiene un espesor de alrededor de 100 micras; para posteriormente llevar a cabo una limpieza (RCA o equivalente), y un crecimiento de una primera capa de dieléctrico (2), como puede ser óxido de silicio, mediante procesos térmicos para pasivar la superficie de Si.

20

25

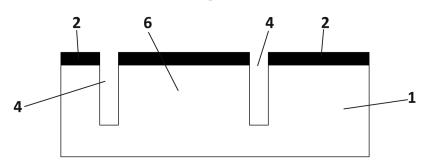

A continuación se realiza un proceso de realización de un patrón sobre la primera capa de dieléctrico (2) junto con una implementación selectiva de elementos dopantes (3) de tipo N cuando el bloque (1) es de un semiconductor tipo P y viceversa con dopantes (3) tipo P cuando el semiconductor del bloque (1) es tipo N,para posteriormente proceder a un proceso térmico para conformar el resultado que se aprecia en la figura 9. En una posible realización alternativa se puede proceder a crecer o depositar una capa protectora sobre aquellas zonas que han sido dopadas capa protectora que es de un material como puede ser un óxido de silicio.

30

A continuación, se procede a depositar una capa de metal que, una vez definida según el patrón correspondiente, hará de máscara selectiva para el posterior grabado profundo de silicio, realizando un taladro ciego creando una trinchera (4), menor de 5 micras de anchura, practicada en la primera capa de dieléctrico (2) y que llega hasta el interior del bloque (1) de material semiconductor, hasta una profundidad de alrededor de 80 micras, taladro ciego que es en forma de corona con sección circular o, alternativamente, con

sección poligonal, de tal manera que un canal (6) de material semiconductor del bloque (1) queda definido en el interior de la trinchera (4). Posteriormente se graba el metal que ha servido de máscara, retirándolo completamente, para obtener una sección como en la figura 10. Alternativamente se puede usar otro material diferente, como óxido de silicio, para hacer de máscara del grabado profundo.

En una realización preferente del segundo aspecto la invención que es la que se muestra en las figuras 8 a 20 se procede a rellenar la trinchera (4) realizada en el bloque (1) con polisilicio dopado conductor (41) cuyo dopaje es tipo P ó N según sea necesario en función del tipo de semiconductor del bloque (1) siendo el dopaje del tipo contrario al del semiconductor del bloque (1); cubriendo además parte de la superficie del óxido de silicio como se ve en la figura 11. Posteriormente se realiza un proceso térmico para extender los dopantes tipo desde el polisilicio dopado hacia las paredes de la trinchera definiendo de este modo una puerta (5) del transistor tipo JFET de la invención como se ve en la figura 12.

En una posible realización alternativa del segundo aspecto de la invención que se muestra en las figuras 1 a 7, se realiza un dopaje de las paredes de la trinchera (4) mediante difusión térmica de dopantes, y posteriormente se puede rellenar la trinchera con otro material conductor diferente del polisilicio o con un material aislante.

20

25

5

10

15

En cualquiera de las posibles realizaciones se lleva a cabo a continuación un proceso de grabado selectivo de la primera capa de dieléctrico (2) en una zona específica en el centro del canal, para realizar una implementación selectiva de elementos dopantes de tipo P ó N según sea necesario, ver explicación anterior, sólo en las zonas donde se ha grabado la primera capa de dieléctrico (2) es decir el óxido de silicio, para posteriormente proceder a un proceso térmico para conformar el resultado que se aprecia en la figura 13, definiendo una fuente (92) del transistor.

30

A continuación se realiza un proceso implementación selectiva de elementos dopantes de P ó N según sea necesario en el dorso del bloque (1) para posteriormente proceder a un proceso térmico para conformar el resultado que se aprecia en la figura 14, definiendo un drenador (101) del transistor.

A continuación se realiza un crecimiento o, alternativamente depósito, de una segunda

#### ES 2 610 187 B1

capa de dieléctrico (7) que puede ser óxido de silicio, mediante procesos térmicos para hacer la función de capa aislante entre capas conductoras, como se puede apreciar en la figura 15.

A continuación se realiza un grabado selectivo de esta segunda capa de dieléctrico (7) en zonas específicas para la apertura de respectivas ventanas de contacto (78,79) a la puerta (5) y a la fuente (92) del transistor como se ve en la figura 16.

10

15

20

25

30

Es decir en aquellas realizaciones en las que el bloque (1) es de semiconductor tipo N, el dopaje del conductor (41) que define la puerta (5), es de tipo P y a su vez, el de los elementos que definen el drenador (101) y la fuente (92), deben ser tipo N y viceversa.

A continuación se deposita una primera capa material conductor (11) en toda la superficie como se ve en la figura 17, que contacta la puerta (5) y la fuente (92) del transistor. Posteriormente esta capa de metal se graba selectivamente en zonas específicas para definir y separar eléctricamente un contacto de puerta (81) y un contacto de fuente (91) del transistor como se ve en la figura 18.

En una posible realización alternativa se tiene que el contacto de puerta (81) y el contacto de fuente (91) no se obtienen mediante una separación de la primera capa de material conductor (11) sino que se obtienen mediante deposición de una primera capa de material conductor eléctrico de baja resistividad (8) que cubre al menos parcialmente la puerta (5) y contacta la puerta (5) definiendo un contacto de puerta (81), y de una segunda capa de material conductor eléctrico de baja resistividad (9) que cubre al menos parcialmente el canal (6) por su parte superior definiendo el contacto de fuente (91).

A continuación se deposita una tercera capa de material conductor eléctrico de baja resistividad (10) que cubre al menos parcialmente el canal (6) por su parte inferior en el dorso del bloque (1) como se ve en la figura 19, que contacta el drenador (101) del dispositivo y define el contacto de drenador (102) del dispositivo.

A continuación, y con el propósito de llevar a cabo una pasivación y aislamiento, se deposita una capa de pasivación (80), la cual comprende una capa de óxido de silicio de la capa de pasivación y una capa de nitruro de silicio de la capa de pasivación,

## ES 2 610 187 B1

cubriendo completamente los contactos (81,91), y la segunda capa de dielectrico (7) allá donde se encuentre expuesta. Esta capa de pasivación (80) se graba posteriormente de forma selectiva para abrir ventanas de contacto (88,89) al contacto de puerta (81) y al contacto de fuente (91) del dispositivo como se ve en la figura 20.

#### REIVINDICACIONES

- 1.- Transistor tipo JFET que comprende un bloque (1) de material semiconductor P ó N, estando el transistor tipo JFET caracterizado por que comprende:

- una primera capa de dieléctrico (2) que cubre al menos parcialmente una superficie del bloque (1),

- una trinchera (4) practicada en la capa de dieléctrico (2) y que llega hasta el interior del bloque (1) de material semiconductor de tal manera que un canal (6) de material semiconductor del bloque (1) queda definido en el interior de la trinchera (4), donde la pared interna de la trinchera (4) comprende un material semiconductor dopado de tipo contrario a aquel del material semiconductor del bloque (1) definiendo de este modo la puerta (5) del transistor tipo JFET,

- una segunda capa de dieléctrico (7) que cubre al menos parcialmente la superficie del bloque (1) y la primera capa de dieléctrico (2),

- una primera capa de material conductor eléctrico de baja resistividad (8) que cubre al menos parcialmente la puerta (5), y contacta la puerta (5) definiendo un contacto de puerta (81),

- una segunda capa de material conductor eléctrico de baja resistividad (9) que cubre al menos parcialmente el canal (6) por su parte superior definiendo un contacto de fuente (91), y

- una tercera capa de material conductor eléctrico de baja resistividad (10) que cubre al menos parcialmente el canal (6) por su parte inferior definiendo un contacto de drenador (101).

- 2.- Transistor tipo JFET según reivindicación 1 caracterizado por que la trinchera (4) que presentan una sección de corona poligonal o circular.

- 3.- Transistor tipo JFET según reivindicación 1 ó 2 caracterizado por que las la trinchera(4) tiene una profundidad menor que el grosor del bloque (1).

- 4.- Transistor tipo JFET según una cualquiera de las realizaciones 1 a 3 caracterizado por que el canal es de silicio, y las trinchera (4) están llenas de polisilicio.

- 5.- Transistor tipo JFET según reivindicación 1 caracterizado por que la capa de

5

10

15

20

dieléctrico (7) es de un material que se selecciona de entre dióxido de silicio y nitruro de silicio.

- 6.- Transistor tipo JFET según reivindicación 1 caracterizado por que las trincheras (4) presentan su eje longitudinal ortogonal al plano longitudinal del bloque (1).

- 7.- Transistor tipo JFET según reivindicación 1 caracterizado por que adicionalmente comprende al menos una capa de pasivación (80) que cubre al menos parcialmente la capa de dieléctrico (7) y al menos una de las capas de material conductor eléctrico de baja resistividad (8,9,10).

- 8.- Transistor tipo JFET según reivindicación 1 caracterizado por que la capa de pasivación (80) comprende una capa de óxido de silicio de la capa de pasivación y una capa de nitruro de silicio de la capa de pasivación.

- 9.- Método de obtención de un transistor JFET, método caracterizado por que comprende:

- i. crecer una primera capa de dieléctrico (2) sobre una superficie del bloque (1),

- ii. estampar la primera capa de dieléctrico (2),

- iii. dopar al menos una zona de la superficie del bloque (1) a través de la primera capa de dieléctrico (2) con dopantes (3) de tipo inverso a aquel del bloque (1),

- iv. aplicar un tratamiento térmico de recocido al resultado del paso anterior,

- v. realizar un taladro ciego con forma de corona de sección circular o poligonal sobre la primera capa de dieléctrico (2), taladro ciego que llega hasta una zona interior del bloque (1) y define la trinchera (4),

- vi. depositar una capa de polisilicio dopado conductor (41) cubriendo al menos parcialmente la capa de dieléctrico (2) y la trinchera (4) cubriendo el interior de las paredes de ésta mientras deja expuesta parte de la primera capa de dieléctrico (2),

- vii. realizar un proceso térmico para extender los dopantes tipo N desde el polisilicio dopado de la hacia las paredes de la trinchera (4) definiendo de este modo la puerta (5) del dispositivo,

- viii. practicar al menos un grabado selectivo en la primera capa de dieléctrico (2) definiendo una ventana que expone la superficie del bloque (1) en el centro del

10

5

25

30

- canal (6), para realizar una implementación selectiva de elementos dopantes de sólo en las zonas donde se ha grabado el óxido de silicio, para posteriormente proceder a un proceso térmico, definiendo una fuente (92),

- ix. realizar un proceso implementación selectiva de elementos dopantes en el dorso del bloque (1) para posteriormente proceder a un proceso térmico definiendo el drenador (101) del dispositivo,

5

10

15

20

25

- x. depositar una capa de dieléctrico (7) sobre la capa de polisilicio dopado conductor (41) dopado con un tipo de semiconductor inverso a aquel del bloque (1), de tal manera que cubre dicha capa de polisilicio dopado conductor (41) y el resto de la superficie,

- xi. realizar un grabado selectivo de esta capa de dieléctrico (7) en zonas específicas para la apertura de ventanas (78,79) de contacto a la puerta (5) y a la fuente (92),

- xii. depositar una primera capa material conductor (11), que contacta la puerta (5) y la fuente (92) del transistor,

- xiii. grabar selectivamente la capa de material conductor (11) en zonas específicas para definir y separar eléctricamente un contacto de puerta (81) y un contacto de fuente (91) del transistor,

- xiv. depositar una tercera capa de material conductor eléctrico de baja resistividad (10) que cubre al menos parcialmente el canal (6) por su parte inferior en el dorso del bloque (1), que contacta el drenador (101) del dispositivo y define el contacto de drenador (102) del dispositivo,

- xv. depositar una capa de pasivación (80) la cual comprende una capa de óxido de silicio de la capa de pasivación y una capa de nitruro de silicio de la capa de pasivación, cubriendo completamente los contactos (81,91), y la segunda capa de dielectrico (7) allá donde se encuentre expuesta, y

- xvi. grabar la capa de pasivación (80) de forma selectiva para abrir ventanas de contacto (88,89) al contacto de puerta (81) y al contacto de fuente (91).

- 10.- Método según reivindicación 9 caracterizado por que el contacto de puerta (81) y el contacto de fuente (91) se definen mediante deposición de una primera capa de material conductor eléctrico de baja resistividad (8) que cubre al menos parcialmente la puerta (5) y contacta la puerta (5) definiendo un contacto de puerta (81), y de una segunda capa de material conductor eléctrico de baja resistividad (9) que cubre al menos parcialmente el

#### ES 2 610 187 B1

canal (6) por su parte superior.

5

- 11.- Método según reivindicación 9 caracterizado por que adicionalmente comprende depositar una capa protectora de óxido de silicio sobre la zona una zona de la primera capa de dieléctrico (2) que ha sido dopada en el paso ii.

- 12.- Método según reivindicación 9 caracterizado por que la trinchera (4) tiene un grosor no mayor de 5 micras.

- 13.- Método según reivindicación 9 caracterizado por que la trinchera (4) tiene una profundidad no mayor de entre 60 y 100 micras.

- 14.- Uso del transistor tipo JFET descrito en una cualquiera de las reivindicaciones 1 a 8 u obtenible mediante el método descrito en una cualquiera de las reivindicaciones 9 a 13 como interruptor.

FIG. 1

FIG. 2

FIG. 3

FIG. 4