# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

(1) Número de publicación: 2 610 384

61 Int. Cl.:

**G01N 27/74** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 29.08.2014 PCT/EP2014/068443

(87) Fecha y número de publicación internacional: 05.03.2015 WO15028642

(96) Fecha de presentación y número de la solicitud europea: 29.08.2014 E 14780768 (9)

(97) Fecha y número de publicación de la concesión europea: 12.10.2016 EP 2929341

(54) Título: Plataforma de biodetección escalable y de alto rendimiento

(30) Prioridad:

30.08.2013 PT 10713813

Fecha de publicación y mención en BOPI de la traducción de la patente: **27.04.2017**

(73) Titular/es:

MAGNOMICS, SA (100.0%) Parque Tecnógico de Cantanhede, Núcleo 04, lote 2, 3060-197 Cantanhede, PT

(72) Inventor/es:

GERMANO, JOSE ANTONIO HENRIQUES KUAN Y PIEDADE, MOISES SIMOES

74 Agente/Representante:

**ISERN JARA, Jorge**

## **DESCRIPCIÓN**

Plataforma de biodetección escalable y de alto rendimiento

#### 5 Campo técnico

15

La presente divulgación se refiere en general a análisis biológico; y en particular a plataformas de biodetección de alto desempeño multi-canal escalables, que pueden hacer análisis biológico de alto rendimiento.

#### 10 Antecedentes de la técnica

Los métodos de análisis biológico convencionales se están sustituyendo gradualmente por dispositivos de punto de cuidado basados en biochip sofisticados y compactos. Estos dispositivos de punto de cuidado basados en biochip realizan análisis de sangre o glucosa comunes a una fracción del coste de métodos de análisis biológicos convencionales. También, los dispositivos de punto de cuidado basados en biochip típicamente requieren tiempo de análisis mucho más corto en comparación con métodos de análisis biológico convencionales. Dado el alto potencial de estas tecnologías de punto de cuidado basadas en biochip, la investigación en métodos de biodetección y en los propios biochips, ha crecido significativamente en la última década.

- A partir de la investigación continuada en métodos de biodetección, se han hecho posibles métodos de análisis biológico nuevos y más eficientes, proporcionando una herramienta valiosa para varias aplicaciones, en concreto, pero sin limitación: diagnósticos clínicos, forenses, veterinarios, industria alimentaria, agricultura y detección de drogas.

- LOPES P ET AL: "Measuring and Extraction of Biological Information on New Handheld Biochip-Based Microsystem", IEEE TRANSACTIONS ON INSTRUMENTATION AND MEASUREMENT, IEEE SERVICE CENTER, PISCATAWAY, NJ, US, vol. 59, n. º 1, 1 de enero de 2010 (01-01-2010), páginas 56-62, ISSN: 0018-945.6, DOI: 10:1109/TIM.2008.2003321 propone técnicas para la extracción de información biológica en un microsistema basado en biochip portátil desarrollado recientemente. El microsistema está basado en un biochip de matriz magnetoresistiva compuesto de un número de sitios de detección. Se presentan experimentos con el sistema en una configuración para detectar señales biológicas reales.

#### Divulgación de la invención

35 De acuerdo con aspectos de la presente divulgación, se proporciona un sistema de detección biológica. El sistema de detección biológica está caracterizado por un biochip y una plataforma de biodetección. El biochip tiene al menos dos bloques de sensores, teniendo cada bloque de sensores un canal de adquisición de señal que es accesible independientemente de manera que cada bloque de sensores puede leerse en paralelo. La plataforma de biodetección tiene circuitería de accionamiento para accionar cada bloque de sensores del biochip. En una 40 implementación ejemplar, la misma o diferentes señales de accionamiento pueden aplicarse a cada bloque de sensores del biochip. También, la plataforma de biodetección tiene adicionalmente un conjunto de interfaces de adquisición dispuestas de manera que una interfaz de adquisición selecta está acoplada a un correspondiente canal de adquisición de señal del biochip. La plataforma de biodetección también tiene un conjunto de coprocesadores de manera que un coprocesador selecto está asociado de manera inequívoca con una correspondiente de las interfaces de adquisición. Aún además, la plataforma de biodetección tiene un controlador central que controla la 45 circuitería de accionamiento. El controlador central también interconecta con el conjunto de interfaces de adquisición. Aún además, el controlador central interconecta con el conjunto de coprocesadores para leer datos desde el biochip. Además, la plataforma de biodetección puede proporcionar una interfaz de usuario directa, una interfaz remota o combinación de las mismas.

#### Breve descripción de los dibujos

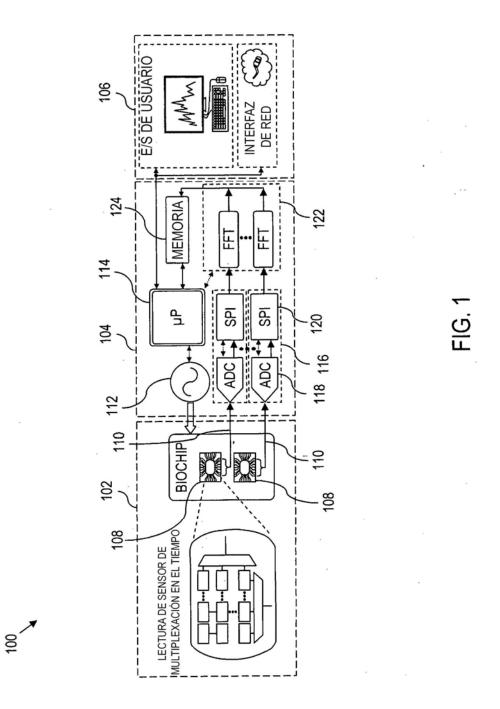

La Figura 1 es una representación esquemática de un sistema para análisis biológico que integra un biochip y una plataforma de biodetección embebida, de acuerdo con aspectos de la presente divulgación;

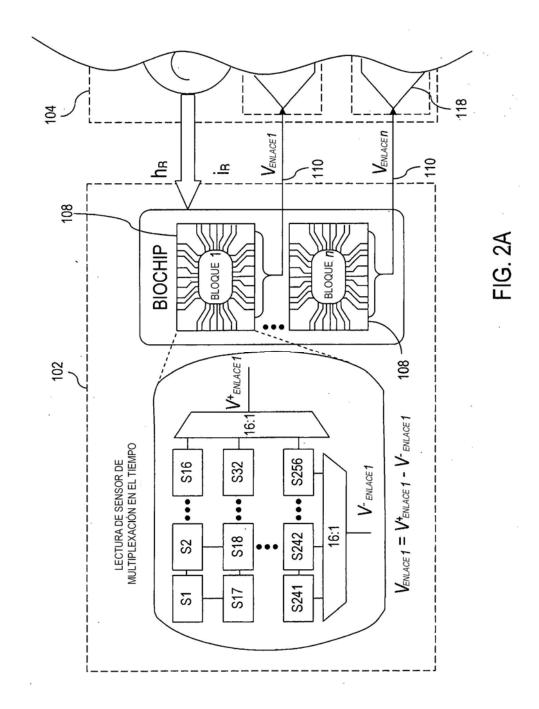

- La Figura 2A es una representación esquemática de vista en despiece de un biochip del sistema para análisis biológico ilustrado en la Figura 1;

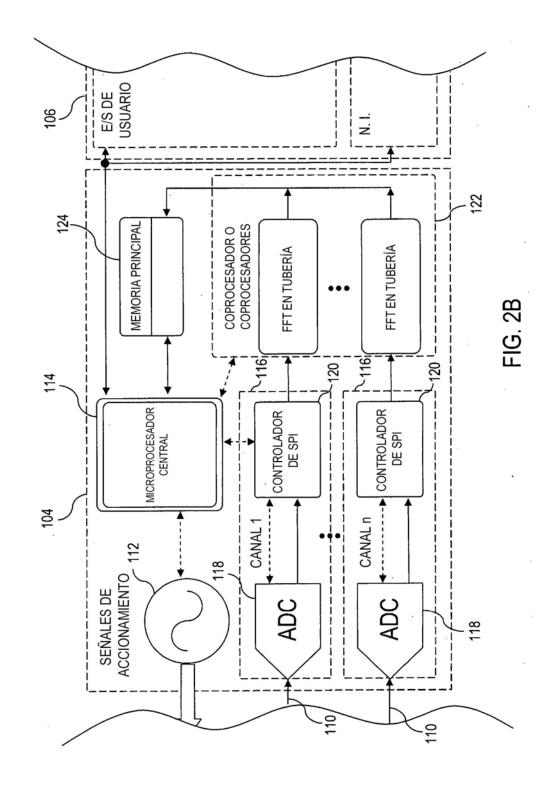

- La Figura 2B es una representación esquemática de vista en despiece de una plataforma de biodetección del sistema para análisis biológico ilustrado en la Figura 1;

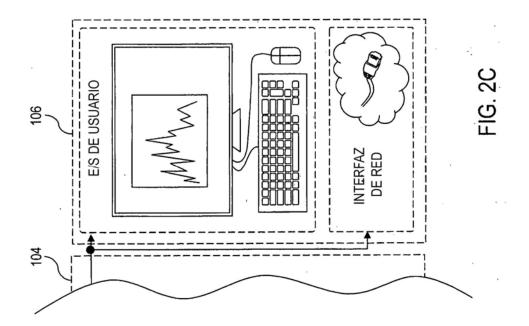

- La Figura 2C es una representación esquemática de vista en despiece de una interfaz del sistema para análisis biológico ilustrado en la Figura 1;

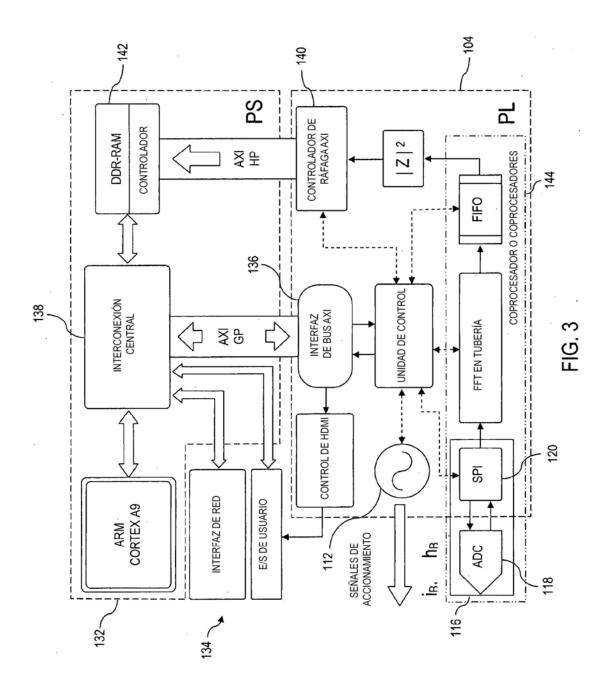

- La Figura 3 es un diagrama de bloques de una plataforma de biodetección, de acuerdo con aspectos de la presente divulgación en el presente documento; y

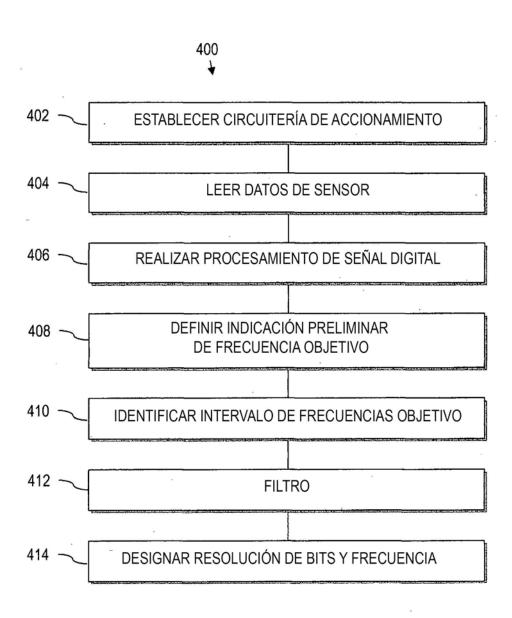

- La Figura 4 es un método de operación de un sistema de detección biológica que tiene un biochip y una plataforma de biodetección.

65

60

50

55

#### Modos para llevar a cabo la invención

De acuerdo con la presente invención, se utiliza un sistema para implementar plataformas de biodetección de alto desempeño multi-canal escalables, que pueden hacer análisis biológico de alto rendimiento. Por ejemplo, los aspectos de la presente divulgación hallan uso en aplicaciones tales como generación de perfiles de expresión génica, donde miles de biosensores analizan una muestra dada en paralelo. En este sentido, la plataforma de biodetección descrita en el presente documento, integra las necesidades computacionales y de complejidad del sistema de detección electrónico, en sistemas embebidos portátiles e independientes con capacidades computacionales adecuadas para tales análisis de alto rendimiento.

10

15

20

25

35

40

45

50

55

60

65

5

De acuerdo con aspectos de la presente divulgación, se proporcionan sistemas para entregar la potencia computacional requerida mediante tecnología de biochip avanzada, y parar permitir adquisición y procesamiento simultáneos a altas tasas de muestreo, a través de una arquitectura de adquisición y procesamiento de alto desempeño y configurable. Por ejemplo, como se describirá en mayor detalle en el presente documento, se proporciona una plataforma de biodetección, que usa múltiples coprocesadores especializados que realizan filtrado de señal basado en la Transformación Rápida de Fourier (FFT), así como otros algoritmos de corrección complejos. Un procesador especializado adicional se usa para sintetizar las señales de estímulos para los sensores, y se proporciona un procesador central para controlar la totalidad del sistema. Con este enfoque, se proporciona un sistema embebido completamente autónomo, que posibilita operación de la plataforma independiente, proporcionando por lo tanto flexibilidad y usabilidad aumentadas.

## SISTEMA DE DETECCIÓN BIOLÓGICA

Haciendo referencia ahora a los dibujos, y en particular, a la Figura 1, se ilustra un sistema de detección biológica 100 en forma esquemática, que puede realizar análisis biológico de acuerdo con aspectos de la presente divulgación. En general, el sistema de detección biológica 100 incluye un biochip 102 y una plataforma de biodetección 104.

El sistema de detección biológica 100 también se integra con una interfaz 106 para proporcionar una solución de laboratorio en un chip completa. La interfaz 106 puede incluir por ejemplo, periféricos de interfaz de usuario local (tales como un teclado, ratón, pantalla, etc.), una interfaz remota, o una combinación de los mismos, que pueden intercambiar datos con la electrónica de la plataforma de biodetección 104.

Haciendo referencia en general a la Figura 1 y a la Figura 2A, el biochip 102 (por ejemplo, un biochip magnetoresistivo) incluye uno o más "bloques" 108 de sensores. Por ejemplo, como se ilustra, hay *n* bloques de sensores donde *n* es cualquier número entero mayor que cero. De esta manera, los bloques particulares se referencian como 108-1, 108-2, ..., 108-*n*, etc. Cada bloque 108 de sensores tiene un canal de adquisición de señal 110 que puede ser accesible independientemente de manera que cada bloque 108 de sensores puede leerse en paralelo, como se describirá en mayor detalle en el presente documento. Los sensores de biochip (por ejemplo, los bloques 108 de sensores) consiguen una alta sensibilidad, alta Relación de Señal a Ruido (SNR) y alto rango dinámico cuando se usan en conjunto con la plataforma de biodetección 104 descrita en el presente documento.

Como se ilustra mejor a la izquierda del biochip 102, una vista en despiece (del bloque 108-1 a modo de ejemplo) ilustra que cada bloque 108 incluye una pluralidad de sensores. Cada uno de la pluralidad de sensores puede ser de un tipo diverso (por ejemplo magnético, temperatura). A modo de ilustración, y no a modo de limitación, hay 256 sensores en cada bloque 108, dispuestos en una matriz de 16 filas y 16 columnas. De acuerdo con aspectos de la presente divulgación, se requieren más de 256 sensores para muchas aplicaciones importantes (por ejemplo, generación de perfiles de expresión génica). Para tratar este requisito, el biochip ilustrativo 102 combina CMOS con tecnologías de fabricación de película fina para proporcionar el número requerido de sensores en un pequeño paquete de biochip. Por lo tanto, por ejemplo, un biochip 102 con por encima de 1.000 sensores se realiza implementando *n*=4 bloques 108, cada uno con 256 sensores. Sin embargo, en la práctica, cada bloque 108 puede tener cualquier número de sensores en su matriz. Por ejemplo, cada bloque 108 puede incluir 16 sensores o más en ciertas implementaciones ilustrativas.

En ciertas implementaciones ilustrativas, cada bloque 108 del biochip 102 puede tener un único canal de adquisición. Cada canal de adquisición (o bloque de los mismos sensores) puede incluir circuitería de acondicionamiento de señal integrada en chip, y circuitería de lectura necesaria para tratar y acceder a los sensores individuales de un bloque correspondiente 108. Por ejemplo, usando una técnica de lectura de sensor, tal como Multiplexación por División en el Tiempo (TDM), un dispositivo de control puede tratar cada uno de los biosensores (256 biosensores en el ejemplo anterior) a través de ese único canal. Por ejemplo, cada sensor puede leerse individualmente usando técnicas de lectura de multiplexación en el tiempo, tal como usando un primer multiplexor ("multiplexor de fila") para seleccionar una fila deseada, y un segundo multiplexor ("multiplexor de columna") para seleccionar una columna deseada. El sensor que se lee a través del canal de adquisición de señal es por lo tanto el sensor en la intersección de la fila seleccionada por el multiplexor de fila y la columna seleccionada por el multiplexor de columna. En una implementación ilustrativa, el biochip 102 está caracterizado por tener cada bloque de sensores una matriz de al menos 16 sensores y un multiplexor de división en el tiempo correspondiente para leer sensores

individuales desde un bloque correspondiente. Además, en implementaciones prácticas, puesto que hay múltiples bloques 108 de sensores, el biochip 102 puede proporcionar una capacidad de multi-canal que incluye hasta, y/o en exceso de 1000 sensores en ciertas implementaciones ejemplares.

Haciendo referencia ahora a la Figura 1 y a la Figura 2B, la plataforma de biodetección 104 incluye en general, circuitería de accionamiento 112 que genera la señal o señales de accionamiento necesarias para el biochip correspondiente 102. Más particularmente, la plataforma de biodetección 104 incluye circuitería de accionamiento 112 para controlar cada bloque 108 de sensores del biochip 102. En este sentido, la manera en la que las señales de accionamiento desde la plataforma de biodetección 104 se acoplan al biochip 102 dependerá de la implementación particular del biochip 102. Sin embargo, a modo de ejemplo, la circuitería de accionamiento puede incluir circuitería para generar corrientes de polarización y campos magnéticos oscilantes que se aplican a los sensores del biochip 102.

Por ejemplo, la circuitería de accionamiento 112 puede incluir un único circuito con múltiples salidas. Como alternativa, la circuitería de accionamiento puede incluir múltiples circuitos independientes, por ejemplo, un circuito independiente para cada bloque 108 del biochip correspondiente 102. Aún además, el uno o más circuitos que componen la circuitería de accionamiento 112 pueden estar basados en software, basados en hardware, o una combinación de los anteriores. En este sentido, las señales de accionamiento pueden ser completa o parcialmente programables, controlarse por puntos de ajuste, parámetros u otras variables de programa, hacerse ajustables mediante señales de accionamiento, por ejemplo, programadas mediante tensiones de control u otras señales de control, etc.

15

20

25

30

35

Como se ilustra, la circuitería de accionamiento 112 se controla mediante un procesador central 114. Por lo tanto por ejemplo, en una implementación ilustrativa, la circuitería de accionamiento 112 se controla mediante el procesador central 114 para tener una frecuencia ajustable. Además, el procesador central 122 puede controlar la circuitería de accionamiento para generar formas y amplitudes de señal arbitraria. Por ejemplo, la circuitería de accionamiento 112 puede utilizar Sintetizadores Digitales Directos (DDS) que pueden combinarse con generadores de señal arbitraria desplegados en una estructura reconfigurable, que se controlan mediante el procesador central 114, para proporcionar las señales correctas al biochip correspondiente 102.

La plataforma de biodetección 104 incluye también múltiples (por ejemplo, un conjunto de) interfaces de adquisición 116. Como se ilustra, la plataforma de biodetección 104 incluye n interfaces de adquisición 116 donde n es cualquier número entero mayor que cero. En el ejemplo ilustrado, una interfaz de adquisición selecta 116 está acoplada a un correspondiente canal de adquisición de señal 110 de cada bloque 108 del biochip 102. Por lo tanto, cuando el biochip 102 tiene 4 bloques 108, teniendo cada bloque un único canal de adquisición de señal 110, la correspondiente plataforma de biodetección 104 incluye 4 interfaces de adquisición 116, cada interfaz de adquisición 116 conectada a un único correspondiente de los canales de adquisición de señal de biochip 110.

En la representación esquemática ilustrativa, cada interfaz de adquisición 116 incluye un convertidor 118, por ejemplo, un convertidor de analógico a digital, que recibe la señal desde su correspondiente canal de adquisición de señal 110. El convertidor de analógico a digital convierte la señal de sensor en una representación digital que puede procesarse adicionalmente, como se describirá en mayor detalle en el presente documento. Como un ejemplo ilustrativo, una interfaz de adquisición 116 está configurada para medir datos de sensor desde el correspondiente canal de adquisición de señal 110 a una frecuencia de enlace específica o banda de frecuencia que se determina mediante la modulación inducida por el campo magnético, la corriente de polarización, la respuesta del sensor a estas señales de CA, y el ruido y diafonía del sistema. Por ejemplo, cada convertidor de analógico a digital 118 puede tener una frecuencia de muestreo de al menos 1 kHz y al menos resolución de 12 bits para conseguir el muestreo deseado.

La salida del convertidor de analógico a digital 118 se acopla a un controlador 120, por ejemplo, un controlador de interfaz periférica en serie. Cada interfaz de adquisición 116 puede incluir también circuitería de acondicionamiento de señal según sea necesaria para interconectar con las señales analógicas desde el biosensor 102. Los controladores 120 se controlan cada uno mediante el procesador central 114.

Además, en una implementación ejemplar, cada controlador 120 se acopla a un coprocesador correspondiente 122. De esta manera, cada controlador 120 transporta información desde su correspondiente convertidor de analógico a digital 118 a su correspondiente coprocesador 122. Por lo tanto, la plataforma de biodetección 104 ilustrada incluye un conjunto de coprocesadores 122 (por ejemplo, *n* coprocesadores donde *n* es cualquier número entero mayor que cero) de manera que un coprocesador selecto 122 está asociado de manera inequívoca con una correspondiente de las interfaces de adquisición 116. En implementaciones alternativas, no hay necesidad de que haya una correspondencia uno o a uno entre las interfaces de adquisición 116 y los coprocesadores 122. Por ejemplo, puede haber un único coprocesador 122 para todos los canales (interfaces de adquisición 116). También, puede utilizarse un único coprocesador 122 para dar servicio a un subconjunto de interfaces de adquisición 116.

Cada coprocesador especializado 122 realiza procesamiento digital, por ejemplo, filtrado de señal basado en la Transformada Rápida de Fourier (FFT) en los datos desde la correspondiente interfaz de adquisición. Cada

coprocesador 122 puede también/como alternativa realizar otros algoritmos de corrección complejos, por ejemplo, un algoritmo de corrección complejo que incluye un filtro Kalman. Aún además, cada coprocesador 122 puede usarse para implementar un controlador de temperatura, un modulador y demodulador complejo, etc. Los coprocesadores 122 comunican también con el procesador central 114, que controla la plataforma de biodetección 104.

De esta manera, para leer datos desde el biochip, el procesador central 114 de la plataforma de biodetección 104 controla la circuitería de accionamiento 112. El procesador central 114 también interconecta con el conjunto de interfaces de adquisición 116 (por ejemplo, mediante los controladores 120). Aún además, el procesador central 114 interconecta con el conjunto de coprocesadores 122. También, el procesador central 114, un coprocesador especializado 122 u otro procesador (no mostrado) pueden utilizarse para sintetizar las señales de estímulos para los datos leídos desde los sensores del biochip 102.

La plataforma de biodetección 104 ilustrada incluye adicionalmente una memoria principal 124. La memoria principal puede acoplarse al procesador central 114 y/o a uno o más de los coprocesadores 122. Por ejemplo, el procesador central 114 y los coprocesadores 122 pueden compartir la memoria principal 124. En este sentido, la memoria principal 124 puede usarse para almacenar programación, información de control, información de calibración, datos, etc. Como tal, en ciertas aplicaciones, un dispositivo de procesamiento informático (por ejemplo, ordenador personal u ordenador de servidor) no necesita estar conectado a la plataforma de biodetección 104 para que el sistema sea operacional. Esto permite, por ejemplo, uso independiente flexible. A un tiempo adecuado, la plataforma de biodetección 104 puede acoplarse al dispositivo de procesamiento informático, por ejemplo, para descargar datos de señal recopilados, etc.

En este sentido, la plataforma de biodetección 104 incluye circuitería electrónica para tratar el biochip 102, para accionar señales de control y para acondicionar y obtener las señales de biochip. Las señales obtenidas se procesan mediante un conjunto de coprocesadores 122 y se transmiten al procesador central 114, por ejemplo, que ejecuta software que funciona como un analizador digital donde, a través de la interfaz 106, por ejemplo, una interfaz de usuario gráfica convencional, el experimento se controla mediante el operador o analista. La plataforma de biodetección 104 proporciona múltiples canales de adquisición de señal 110 que operan a una alta tasa de muestreo, produciendo por lo tanto un alto volumen de datos. Como tal, la plataforma de biodetección 104 también incluye la potencia de cálculo necesaria que se requiere para manejar el volumen de datos.

Haciendo referencia a la Figura 1 y a la Figura 2C, la interfaz 106 puede comprender un monitor, teclado, ratón u otros periféricos informáticos, una interfaz de usuario gráfica, interfaz de red, etc. En una implementación ilustrativa, el sistema de detección biológica incluye una plataforma de biodetección implementada en dos componentes, incluyendo un componente de lógica programable y un componente de sistema de procesamiento, en el que la circuitería de accionamiento 112 (por ejemplo, sintetizador de señal de accionamiento), los coprocesadores 122 y las interfaces de adquisición 116 se implementan en el componente de lógica programable, y el procesador central 114 y la memoria principal 124 se implementan en el sistema de procesamiento.

El procesador central 114 puede comunicar adicionalmente a través de una red, que proporciona enlaces de comunicaciones entre diversos dispositivos de procesamiento, y puede soportarse por componentes de interconexión en red que interconectan los dispositivos de procesamiento, incluyendo por ejemplo, encaminadores, concentradores, cortafuegos, interfaces de red, enlaces de comunicaciones alámbricas o inalámbricas e interconexiones correspondientes, estaciones celulares y tecnologías de conversión celular correspondientes, por ejemplo, para convertir entre celular y tcp/ip, etc. Además, la red o redes pueden comprender conexiones usando una o más redes internas, redes externas, redes de área local (LAN), redes de área extensa (WAN), redes inalámbricas (WIFI), internet, incluyendo la red informática mundial, celular y/u otras disposiciones para posibilitar la comunicación entre los dispositivos de procesamiento, en tiempo real o de otra manera, por ejemplo, mediante desfase temporal, procesamiento en lotes, etc.

# Implementación de ejemplo

5

10

15

20

25

30

35

40

45

50

65

Con referencia a la Figura 1, y a las Figuras 2A-2C en general, un ensayo de laboratorio comienza etiquetando dianas biológicas bajo análisis con Partículas Magnéticas (MP). A continuación, una corriente de polarización,  $i_B$ , y una señal de campo magnético oscilante,  $h_B$ , se aplican a los sensores del biochip 102, por ejemplo, mediante la circuitería de accionamiento 112 de la plataforma de biodetección 104. Tras reconocimiento y lavado biomolecular, los sensores detectan los campos marginales creados por las MP que se han capturado mediante sondas biológicas colocadas por encima de los sensores. La información biológica se extrae a continuación midiendo las variaciones de la señal de tensión de sensor,  $v_{enlace}$ .

Para reducir el coste y complejidad del sistema, los sensores de cada bloque 108 se miden usando Multiplexación por División en el Tiempo (pueden aplicarse como alternativa otras técnicas de modulación y multiplexación). Puesto que alcanzar un bajo nivel de ruido típicamente requiere un alto número de muestras por sensor, los tiempos de lectura de biochip pueden ser lentos, por ejemplo, aproximadamente 4 minutos. Tal reconocimiento biomolecular a una baja velocidad, puede ser aceptable para ciertos biochips. Sin embargo, tal reconocimiento lento no cambia de

escala cuando el número de sensores crece a 1000 o más. Para evitar los problemas de velocidades lentas, el biochip 102 está organizado en grupos de sensores, por ejemplo, 256 elementos de sensores por bloque 108, y cada sensor está multiplexado en tiempo en su correspondiente bloque, como se ha indicado anteriormente. Con este enfoque, el tiempo de lectura total se restringe al número de sensores en cada grupo, ya que el procesamiento se realiza en paralelo. Por lo tanto el tamaño del biochip puede cambiarse de escala sin aumentar el tiempo de lectura global. Sin embargo, esto impone recursos de hardware significativos en la electrónica de la plataforma. Cada grupo 108 del biochip 102 se sirve por una interfaz de canal de adquisición especializada 116 de la plataforma de biodetección 104, por ejemplo, que comprende circuitos de acondicionamiento de señal y un Convertidor de Analógico a Digital (ADC) 118. Adicionalmente, los datos desde cada canal se procesan en paralelo, para permitir la observación de la evolución del ensayo en tiempo real.

Deben considerarse también características adicionales del biochip. De acuerdo con una implementación ejemplar, para evitar el efecto de bajo ruido de frecuencia y maximizar la SNR obtenida, las señales aplicadas desde la circuitería de accionamiento 112, por ejemplo, las señales aplicadas son y  $h_B$  en las figuras, incluyen un componente de CA. En consecuencia,  $v_{enlace}$  se mide a una frecuencia de enlace específica,  $f_{enlace}$ , que se determina mediante la modulación inducida por el campo magnético  $h_B$  { $f_2$ }, la corriente de polarización  $i_B$  { $f_1$ }, la respuesta del sensor a estas señales de CA, y el ruido y diafonía del sistema. En cada bloque de sensor pueden aplicarse múltiples frecuencias de modulación tanto en el campo magnético como en la corriente de polarización.

Debido a la complejidad de la tecnología del biochip y de la circuitería que acciona y mide los sensores, puede no 20 ser fácil determinar una buena estimación a priori de la frecuencia a la que la SNR es máxima. Para optimizar la sensibilidad biológica,  $f_{enlace}$  debería adaptarse en tiempo real, cambiando las frecuencias de  $i_B$  y/o  $h_B$ . Sin embargo, esto introduce la dificultad añadida de determinar la amplitud de señal a una frecuencia desconocida. De acuerdo con aspectos ilustrativos de la divulgación en el presente documento, un método flexible y manejable es usar una FFT de la señal obtenida en cada uno de los más de 1000 sensores, para calcular la amplitud de la señal venlace a la 25 frecuencia  $f_{enlace}$ . Aunque esto asegura una buena adaptabilidad, este enfoque puede requerir una frecuencia de muestreo de al menos 50 kHz y una resolución de frecuencia tan baja como 1 Hz, para una resolución de 24 bits en cada sensor. Es decir, los aspectos de la presente invención pueden funcionar adecuadamente, por ejemplo, con una frecuencia de muestreo de al menos 1 kHz y al menos una resolución de 12 bits. Sin embargo, esto impone 30 grandes requisitos de memoria y hardware, que restringen la escalabilidad del sistema. Adicionalmente, pueden implementarse otros algoritmos de corrección complejos mediante cada coprocesador 122, en concreto pero sin limitación: corrección de desviación, controlador de temperatura, filtros Kalman, modulador y/o demodulador complejo (por ejemplo espectro ensanchado).

# **ARQUITECTURA**

5

10

15

35

40

45

50

55

60

65

El rendimiento computacional requerido por la plataforma de biodetección 104 para asegurar la resolución y fiabilidad de ensayos de bio-reconocimiento puede conseguirse optimizando la arquitectura de los procesadores y aumentando el paralelismo aprovechado con el uso de estructuras multi-núcleo. Sin embargo, sería insuficiente tratar exclusivamente las limitaciones de desempeño, puesto que el cuello de botella puede surgir también en los canales de comunicación, tal como el de los circuitos de adquisición a la unidad de procesamiento. Adicionalmente, debido a la complejidad significativa de los algoritmos subyacentes, la unidad de procesamiento debe poder almacenar y manipular grandes conjuntos de datos, haciendo claro que un ancho de banda de memoria alto y capacidad son necesarios para aprovechar completamente las capacidades de procesamiento mejoradas.

Como se describe más completamente en el presente documento, la arquitectura para satisfacer los requisitos de la plataforma de biodetección de alto rendimiento se representa en la Figura 1. En general, cuando se implementa la plataforma de biodetección 104, puede seleccionarse una interfaz en serie de alta velocidad para proporcionar una comunicación rápida entre los ADC 118 y el conjunto de coprocesadores especializados 122 (por ejemplo, núcleos) donde se manejan las tareas más computacionalmente intensivas. Todos los componentes, incluyendo el generador de las señales de estímulos, están configurados mediante un procesador central 114, por ejemplo, también denominado en el presente documento como un Procesador de Fin General (GPP) que, aparte de actuar como el controlador de sistema principal, también puede realizar cálculos auxiliares en los datos requeridos y tareas de interfaz de usuario así como tareas de comunicación. El procesador central 114 comparte su memoria principal 124 con los coprocesadores 122. Una interfaz de usuario, controlada a través del procesador central 114, se prefiere realizar a través de la interfaz 106 que incluye un conjunto de dispositivos de E/S, tal como los periféricos de entrada usados para controlar el experimento y una pantalla en la que se presentan los resultados al usuario. Se incluye también una interfaz de red, controlada a través del procesador central 114, que permite que se transfieran los datos procesados a una base de datos externa, fácilmente disponible para otros usuarios.

## Procesador central y memoria principal

El procesador central 114, por ejemplo, el GPP, es un dispositivo adecuado para configurar los varios componentes de sistema y por lo tanto el procesador central 114 desempeña un papel clave en facilitar la integración del sistema. En ciertas implementaciones ilustrativas, el soporte de Sistema Operativo (SO) es necesario, para beneficiarse de los paquetes de software disponibles que proporcionan funcionalidades de gestión de sistema complejas e interfaces

de alto nivel para la E/S convencional y periféricos de memoria. Un subsistema de interconexión procesador-memoria (subsistema que interconecta el procesador central 114 a la memoria principal 124) puede equiparse con canales de DMA (o equivalentes), que permiten al procesador central 114 comunicar con periféricos de flujo continuo en un espacio de memoria compartido.

#### Interfaz de sensor de alto rendimiento

5

10

15

20

25

30

35

40

55

60

65

Cada canal de adquisición está enlazado a un grupo de sensor de biochip 108 y alimenta directamente un coprocesador especializado 122 con los datos muestreados mediante el ADC 118. En una implementación ejemplar, puesto que cada ADC 118 puede operar a una velocidad máxima de 96 Mbit/s, la ausencia de un canal de datos de alta velocidad comprometería gravemente el rendimiento global. En la implementación ejemplar, se eligió Señalización Diferencial de Baja Tensión (LVDS) como una solución rentable y tolerante a ruido para conseguir altas velocidades de transmisión. En la parte superior de esta capa física, se utiliza un protocolo de bus de Interfaz de Periféricos en Serie (SPI) 118, para proporcionar capacidades de configuración y direccionamiento basándose en un controlador maestro/esclavo de SPI.

#### Coprocesadores especializados

Los coprocesadores especializados 122 son responsables de medir la amplitud de la señal de enlace de los sensores,  $v_{enlace}$ , desde el biosensor 102, a una frecuencia específica. Esta señal se estima usando un enfoque de FFT de aumento junto con otros algoritmos de procesamiento complejo como los filtros Kalman que mejoran la precisión de datos global. En una primera etapa, se realiza una FFT con una resolución de baja frecuencia, y usando un subconjunto de sensores en el mismo canal. Esto proporciona una identificación basta y preliminar de la mejor frecuencia  $f_{enlace}$  para medir la  $v_{enlace}$ , mientras mantiene los recursos de hardware y consumo de potencia a niveles tolerables. Después de identificar el intervalo *fenlace*, se realiza filtrado de paso banda y demodulación de señal, para desplazar la frecuencia de interés hasta la banda base. Esto permite el cálculo de múltiples FFT (una por canal) con una resolución de bits y frecuencia superior, mientras limita aún los recursos requeridos. También, para aumentar la relación de señal a ruido y conseguir escalabilidad del sistema, el procedimiento de aumento puede realizarse tantas veces como se requiera. Los demoduladores complejos (por ejemplo espectro ensanchado) pueden implementarse también en los coprocesadores para conseguir una capacidad de multiplexación superior.

Debido a la complejidad computacional implicada, se considera un dispositivo de campo de matriz de puertas programables (FPGA) reconfigurable como una tecnología adecuada para adaptar la infraestructura multi-núcleo de coprocesadores de FFT especializados, filtros y demoduladores 122. Un FPGA combina el nivel de alto desempeño requerido, mientras confiere aún la flexibilidad para cambiar o actualizar los algoritmos de procesamiento adoptados. En particular, pueden almacenarse múltiples configuraciones en memoria para cada nivel de aumento. En tiempo de ejecución, el usuario empieza observando el espectro de señal basta del subconjunto inicial de sensores. A continuación, se selecciona la frecuencia de demodulación y banda de espectro más favorables. Esto activará la reconfiguración del FPGA y el despliegue de los coprocesadores especializados en hardware, configurados con la frecuencia de demodulación objetivo. En este punto, el usuario puede observar la señal de enlace para cada sensor.

## Periféricos de E/S e interfaz de usuario

Se utiliza un conjunto de periféricos de E/S 106 para hacer la plataforma de biodetección 104 un sistema de análisis y diagnóstico independiente. Estos módulos no permiten únicamente que el usuario tenga control total del experimento, sino que también ofrecen los medios de visualización para fines de interpretación clínica. El conjunto convencional de periféricos informáticos (es decir teclado USB / panel de pantalla táctil y monitor HDMI) se utiliza típicamente como interfaces para la plataforma de biodetección 104 para mejorar la experiencia de usabilidad.

#### 50 Generador de señal de estímulo

Haciendo referencia ahora a la Figura 3, se ilustra una porción del sistema de detección biológica 100 de la Figura 1. En particular, la Figura 3 ilustra una vista parcial de la plataforma de biodetección 104. Por ejemplo, únicamente se ilustra una interfaz de adquisición de señal 116 por conveniencia de ilustración y análisis. También, el biochip 102 y los dispositivos de interfaz 106 se han omitido por conveniencia de análisis.

Las señales de CA de referencia deben suministrarse mediante el generador de accionamiento 112 a los biosensores del biochip 102, para producir una respuesta medible (por ejemplo,  $i_B$  y  $h_B$  analizadas anteriormente). La amplitud, forma e intervalos de frecuencia de estos estímulos están parcialmente restringidos por la tecnología del biochip considerada. Sin embargo, el nivel de ruido al que están expuestas las mediciones es inversamente proporcional a la frecuencia de estas señales. Por lo tanto la precisión de los resultados está fuertemente restringida por este parámetro. Como consecuencia, un componente generador de frecuencia variable y configurable de la circuitería de accionamiento 112, que puede ajustarse y parametrizarse por el procesador central 114 (por ejemplo, GPP), asegura la adaptabilidad de la plataforma de biodetección 104 a múltiples generaciones del biochip 102. Los generadores de señal requeridos pueden implementarse usando Sintetizadores Digitales Directos (DDS) desplegados en una estructura reconfigurable, que pueden combinarse con hardware adicional en la estructura

reconfigurable para conseguir modulación compleja como espectro ensanchado, y controlarse por el procesador central 114.

#### Implementación ejemplar

5

En una realización ejemplar de funcionamiento, se utilizó una Plataforma de Procesamiento Extensible Xilinx Zynq 7000 para crear la plataforma de biodetección 104 como un sistema embebido. Este Sistema en un Chip (SoC) particular incluye una estructura reconfigurable del estado de la técnica y ofrece la mayoría de las características requeridas por el sistema descrito más completamente con respecto a las Figuras 1-3.

10

15

20

#### Arquitectura SoC de Zyng

La SoC de Zyng integra dos módulos independientes en el mismo chip: un Sistema de Procesamiento (PS), que presenta un procesador 132, por ejemplo, un procesador ARM Cortex-A9 de doble núcleo, y Lógica Programable (PL), que consiste en la estructura reconfigurable compatible con FPGA Xilinx 7-Series. Además de los procesadores ARM y el controlador de memoria DDR asociado, el PS también integra una colección de interfaces de comunicación convencionales en la industria 134 (Gigabit Ethernet, USB, I2C y SPI). En tiempo de arranque, el PS configura la PL por medio del Puerto de Acceso de Configuración del Procesador (PCAP) e inicializa los relojes de sistema. A través del PCAP, el procesador ARM puede aprovechar las capacidades de reconfiguración parcial dinámicas accionadas por software de la estructura reconfigurable, promocionando por lo tanto un uso adaptado y optimizado de la parte reconfigurable de este SoC.

La interconexión PS-PL puede conseguirse usando una interfaz, por ejemplo, el protocolo de bus de Interfaz extensible Avanzada (AXI), a través de cualquiera de los puertos de conectividad proporcionados, en concreto, el de 25 Fin General (AXI-GP), Alto Desempeño (AXI-HP), y Puerto de Coherencia Acelerador (AXI-ACP). Por ejemplo, como se ilustra, dos interfaces AXI-GP maestras y dos esclavas 136 conectan la PL a una interconexión central de PS 138, permitiendo datos de bajo rendimiento y trasferencias de control. Cuando se requiere alto rendimiento, una interfaz separada 140, por ejemplo, una interfaz AXI-HP, se conecta directamente a la memoria principal 142. En esta interfaz 140, las operaciones de lectura y escritura se arbitran por una FIFO de 1 kB asíncrona con un ancho de 30 datos configurable de 32 o 64 bits. La interfaz de AXI-ACP conecta la PL directamente a la Unidad de Control de Sondeo (SCU), para asegurar coherencia de datos en la caché compartida L2 de los procesadores ARM. Todos

35

## Implementación

40

hardware.

Aunque el procesador ARM en el PS se usa para controlar la plataforma, la estructura reconfigurable en la PL se usa para implementar los coprocesadores especializados y para soportar la interfaz con el biochip. La capa de software de base que se ejecuta en el PS se implementa en una implementación ejemplar, usando el SO GNU/Linux Linaro Ubuntu, que proporciona herramientas optimizadas y paquetes de software para SoC de ARM. Adoptando este SO, el PS proporciona una interfaz rica para usuario usando el conjunto existente de periféricos informáticos.

estos puertos pueden activarse y configurarse individualmente. En el lado de la PL, estas interfaces se implementan usando la lógica reconfigurable existente, teniendo por lo tanto un coste asociado en términos de recursos de

45

La Figura 3 representa el diagrama de bloques de la arquitectura implementada, considerando un único canal 116. Corresponde a la fase de aumento inicial, donde se calcula una FFT a través de un pequeño subconjunto de sensores desde un único canal de adquisición para determinar la frecuencia de enlace, fenlace que maximiza la relación de señal a ruido. En la implementación multi-canal, donde canales paralelos leen información biológica de más de 1000 sensores, el canal de coprocesador 1X en la Figura 3 se replica según sea necesario, de acuerdo con los bloques 108/canales de adquisición 116 del biochip 102.

50

55

Varias interfaces AXI conectan la estructura reconfigurable al procesador ARM y a la memoria principal asociada, ya sea para control o para transferencias de datos de alto rendimiento. Siguiendo la estrategia de diseño comúnmente adoptada en periféricos basados en DMA, cada coprocesador diseñado proporciona una interfaz esclava para fines de configuración, junto con un controlador maestro que escribe en el bus de memoria compartida. La coherencia de datos entre los coprocesadores especializados y el GPP se consigue usando una región contigua en la memoria principal, marcada como que no puede almacenarse en caché y excluida de la gestión de memoria del sistema. El SO puede leer esta región de memoria volviendo a mapear la región en el espacio de direcciones virtual del núcleo, permitiendo por lo tanto que se acceda fácilmente mediante un controlador de dispositivo personalizado.

60

65

# Coprocesador FFT

En una implementación ilustrativa, los coprocesadores de FFT (por ejemplo, el coprocesador 122) en la PL están basados en el núcleo Xilinx FFT IP v7.1, y adoptan una operación en tubería para producir una salida por ciclo de reloj en un esquema de procesamiento basado en flujo. Los núcleos están configurados para recibir entradas reales de punto fijo de 24 bits, aunque se usa una precisión superior dentro de los núcleos para reducir la propagación de error numérica entre etapas intermedias. Adicionalmente, los bloques de DSP embebidos se usan en los cálculos en mariposa para permitir un mejor equilibrio en el uso de DSP/BRAM en la estructura reconfigurable disponible. Es necesaria una cantidad significativa de BRAM para almacenamiento de datos y factor de fase cuando se calculan las FFT con una alta cantidad de puntos. Sin embargo, la adopción del enfoque de aumento permite que los requisitos de memoria total por canal se mantengan en niveles razonables. En todos los niveles de aumento, las señales de bits de reseteo e inicio síncronas se obtienen desde un registro de control, que permite una operación completamente controlada mediante el PS. También, puesto que el algoritmo de procesamiento de señal considerado requiere el cuadrado de la salida compleja de FFT, se introduce un bloque de cuadrado adicional en la salida de FIFO.

### 10 Flujo continuo de datos e interfaz de PL-PS

5

15

20

60

65

En una implementación ilustrativa, la comunicación entre los varios bloques lógicos en la estructura reconfigurable y el GPP de ARM se asegura mediante canales de control y datos específicamente definidos. Siguiendo un enfoque de E/S de memoria mapeada, un conjunto de registros de control se hacen disponibles para los programas que se ejecutan en el ARM, proporcionando funcionalidades de activación de banderas de reseteo e inicio de software convenientes. Estos registros se colocan en un bus AXI, masterizado mediante la CPU a través de un puerto de interfaz AXI-GP. Se usa un puerto AXI-HP para transferir las tramas de salida de FFT directamente a la memoria principal, donde pueden accederse posteriormente mediante la CPU. Puesto que esta región de memoria compartida es contigua y no se gestiona directamente por el núcleo de SO (como se ha explicado anteriormente), se usa un Controlador Maestro de Ráfagas AXI para proporcionar estos canales de coprocesamiento 144 con un acceso a memoria directo. Esta solución proporciona un desempeño de transferencia de datos equivalente a un motor de DMA convencional, pero reduce los requisitos de hardware aproximadamente 7 veces.

Cuando se considera el procesamiento multicanal, la arquitectura en la Figura 3 se expande para incorporar tantos bloques de coprocesamiento como el número de canales, por ejemplo, bloques 108/canales de adquisición 116 del biochip 102 (canal de coprocesamiento 144 etiquetado con recuadro de línea discontinua en la parte inferior de la Figura 3). Los bloques de coprocesamiento se conectan a continuación al puerto AXI-HP, que proporciona un canal de comunicación entre los coprocesadores y la memoria principal que puede soportar transferencias de datos de hasta 1,2 GBytes/s (estimación). Esto está muy por encima de los 72 KBits/s tasa de bits del ADC en ciertas aplicaciones de biosensor. Incluso considerando que se requieren tasas de bits superiores para la plataforma de biodetección desvelada, este ancho de banda es suficiente para soportar múltiples canales (los biochips 102 comprenden 4 canales), y aún proporciona suficientes recursos para expansiones futuras. Sin embargo, debería observarse que debe asegurarse una transmisión de datos continua para conseguir un rendimiento de 1,2 GBytes/s. Para garantizar este requisito, se usa una memoria FIFO de dominio de reloj dual para implementar un puente entre los canales de procesamiento de FFT y el bus AXI-HP conectado a la memoria principal.

#### E/S de sistema e interfaz de usuario

En una implementación ilustrativa, se soportan dos interfaces diferentes por la plataforma de biodetección: i) una interconexión basada en SPI con cada ADC de canal y con generador de estímulos, ii) la interfaz con el operador humano. Las conexiones al ADC de biodetección con el generador de estímulos pueden conseguirse mediante una implementación de núcleo de código abierto del protocolo SPI, disponible en OpenCores.org. La selección de este núcleo particular tiene en cuenta sus características particulares en términos de versatilidad y eficacia de recursos.

Haciendo referencia en general a la Figura 1, a la Figura 2C, y a la Figura 3, en una implementación ilustrativa, la interfaz 106, por ejemplo, interfaz de usuario gráfica, se consigue usando un puerto de gráficos HDMI y un teclado USB, panel táctil USB u otra interfaz adecuada. Aunque ya existe una interfaz HDMI en la plataforma Zynq, el controlador tiene que implementarse en la estructura reconfigurable. El módulo de controlador se obtuvo a partir de un diseño de referencia que se dirige a una interfaz de salida de HDMI, junto con los bloques de flujo continuo físicos y de datos requeridos para manejar flujos de vídeo de DMA. Estos motores de DMA están conectados a dos puertos AXI-HP separados, que les posibilita recoger directamente datos de vídeo desde la memoria principal. La lógica de control de HDMI (también en el lado de PL), está conectada a una interfaz de AXI-GP y está mapeada en el espacio de memoria del SO, permitiendo el uso de controladores de dispositivo de software existentes.

# 55 Calibración de método de un sistema de detección biológica

Haciendo referencia a la Figura 4, puede usarse un método 400 de operación de un sistema de detección biológica que tiene un biochip, por ejemplo, para calibrar señales de circuitería de accionamiento para la mejor relación de señal a ruido, estableciendo circuitería de accionamiento para generar un conjunto de señales de accionamiento y leyendo datos de sensor desde un biochip. El método puede realizar procesamiento digital, con una resolución de frecuencia baja en los datos de sensor extraídos desde el biochip, usando un subconjunto de sensores que acceden a un canal de adquisición de señal común del biochip. El método puede usar el resultado del procesamiento digital con una resolución de frecuencia baja para definir, en una indicación preliminar de una frecuencia objetivo para medir unos datos de sensor emitidos desde el canal de adquisición de señal, e identificando un intervalo o banda de frecuencias objetivo. Además aún, el método puede realizar filtrado y demodulación de señal para desplazar una frecuencia (banda) de interés del intervalo identificado de frecuencias objetivo hasta una banda base y puede

designar, una resolución de bits y frecuencia desde la banda base que maximiza la relación de señal a ruido de los datos leídos desde el canal de adquisición de señal.

El método puede realizar demodulación donde los datos de sensor extraídos desde el biochip resultan de usar técnicas de modulación. Realizar procesamiento digital puede conseguirse realizando una transformada rápida de Fourier con una resolución de frecuencia baja en datos de sensor extraídos desde el biochip, usando un subconjunto de sensores que acceden a un canal de adquisición de señal común del biochip. Incluyendo los algoritmos de corrección complejos al menos uno de: puede usarse un filtro Kalman, compensación de desvío y un controlador de temperatura, en el resultado de la transformada de Fourier.

#### Resultados experimentales

Para evaluar apropiadamente la arquitectura multi-canal escalable, se obtuvieron resultados experimentales usando un ZedBoard que presenta un Zynq XC7Z020, uno de los SoC de Zynq más pequeños y menos exigentes en potencia, y se sintetizaron y mapearon usando las herramientas de desarrollo Xilinx 14.3. El análisis presentado empieza considerando una implementación de arquitectura de único canal con el núcleo de FFT más grande permitido, que se usa para determinar, con máxima precisión, la región de frecuencia de enlace de los biosensores. Se presentan resultados experimentales en la Tabla 1 y muestran que el tamaño de FFT (64 k muestras) está limitado por la cantidad de bloques de RAM disponibles en la PL. Adicionalmente, los resultados muestran que los recursos requeridos por la estructura restante corresponden a únicamente el 33,5 % de las LUT disponibles, únicamente 8 BRAM y 19 DSP. A partir de esto, puede concluirse que la mayoría de los recursos de hardware de PL se hicieron disponibles para usarse por el canal o canales de coprocesamiento.

Tabla 1. Recursos de sistema para una FFT de 64 K de único canal

| Componente                     |       | (53200)  |     | M (140)  | DSP48 (220) |          |

|--------------------------------|-------|----------|-----|----------|-------------|----------|

| Núcleo de FFT 64 k             | 7157  | (13,5 %) | 106 | (75,7 %) | 103         | (46,8 %) |

| Módulo de cuadratura           | 149   | (0,3 %)  | 0   | -        | 16          | (7,2 %)  |

| Señales de accionamiento (DDS) | 174   | (0,3 %)  | 2   | (1,4 %)  | 3           | (1,4 %)  |

| Agrupador AXI                  | 572   | (1,1 %)  | 0   | -        | 0           | -        |

| SPI maestro                    | 131   | (0,2 %)  | 0   | -        | 0           | -        |

| Sistema principal              | 13857 | (26,0 %) | 6   | (4,3 %)  | 0           | -        |

| Sistema total                  | 25097 | (47,2 %) | 114 | (82,1 %) | 122         | (55,4 %) |

25

30

5

10

15

20

Para evaluar la escalabilidad y adaptabilidad de la arquitectura al caso cuando se realiza aumento y se requieren múltiples canales, se generaron flujos de bits con núcleos de FFT más pequeños y el número de canales se maximizó equilibrando el uso de DSP, BRAM y LUT. La Tabla 2 presenta los recursos usados mediante un único canal de coprocesamiento 144, considerando las FFT con número creciente de puntos, y el número máximo de canales de coprocesamiento 144 soportado en la PL. Debería indicarse que para la FFT de 1 k, 2 k y 4 k el número máximo de canales está restringido por el número de elementos de DSP48 disponible; para FFT mayores la limitación radica en las BRAM. También, en la FFT de 32 k, para soportar 2 canales, algunos bloques de RAM se implementaron usando LUT.

35

Tabla 2. Requisitos de hardware de canal de coprocesamiento.

| Tabla 2: Requisites de haraware de sanar de sopresseamiente: |                                  |        |            |        |             |        |                |  |  |  |

|--------------------------------------------------------------|----------------------------------|--------|------------|--------|-------------|--------|----------------|--|--|--|

| Tamaño de FFT (N. º                                          | Recursos de hardware (por canal) |        |            |        |             |        | N. º máximo de |  |  |  |

| de muestras)                                                 | LUT (53200)                      |        | BRAM (140) |        | DSP48 (220) |        | canales        |  |  |  |

| 1024                                                         | 3686                             | (7 %)  | 8          | (6 %)  | 24          | (11 %) | 8              |  |  |  |

| 2048                                                         | 4375                             | (8 %)  | 11         | (8 %)  | 31          | (14 %) | 6              |  |  |  |

| 4096                                                         | 4765                             | (9 %)  | 14         | (10 %) | 31          | (14 %) | 6              |  |  |  |

| 16384                                                        | 7201                             | (14 %) | 28         | (20 %) | 40          | (18 %) | 4              |  |  |  |

| 32768                                                        | 7916                             | (15 %) | 55         | (39 %) | 49          | (22 %) | 2              |  |  |  |

| 65536                                                        | 7254                             | (14 %) | 106        | (76 %) | 103         | (47 %) | 1              |  |  |  |

Los resultados presentados sugieren que es posible conseguir un sistema de procesamiento multicanal compuesto de 8 canales de FFT de 1024 puntos. Por lo tanto, con hasta 256 biosensores por canal, puede procesarse un total de 2.048 biosensores y el tiempo de barrido se reduce en un factor de 8. Puede conseguirse multiplexación adicional

usando otras técnicas de modulación complejas como múltiples portadoras o espectro ensanchado. Esto demuestra la adaptabilidad del sistema propuesto para procesamiento multicanal, mientras mantiene la cantidad requerida de recursos de hardware compatibles con este SoC de Zynq de nivel de básico. Los núcleos de FFT pueden operar por encima de 180 MHz, produciendo 1 muestra de salida por ciclo de reloj. Considerando que el sistema debe soportar una tasa de muestreo de ADC de hasta 4 Msps, que corresponde a los convertidores de alta resolución del estado de la técnica, esto sugiere que los núcleos de FFT no imponen ninguna limitación al rendimiento de análisis de señal.

Por otra parte, el AXI-HP permite una tasa de transferencia máxima estimada de 1,2 GBytes/s, aunque, para un ancho de datos de 32 bits, el núcleo de FFT emite una tasa de bits de como máximo 128 Mbit/s. Por lo tanto, el ancho de banda de AXI-HP no limita la operación del sistema, soportando múltiples canales de adquisición. Considerando que el biochip desarrollado presenta 4 bloques de sensores (1024 sensores), la tasa de bits podría aún aumentarse si se hacen disponibles ADC más rápidos.

A partir de estos resultados, puede concluirse que la arquitectura del presente documento, mapeada en un SoC de Zynq, proporciona los recursos computacionales requeridos para implementar una plataforma de biodetección completamente embebida y de alto desempeño. Adicionalmente, el prototipo implementado también demuestra que puede obtenerse una plataforma escalable y adaptable con las capacidades de reconfiguración existentes, que puede adaptarse a biochips con recuento de sensores superior y diferentes necesidades computacionales.

#### Miscelánea

5

20

25

30

35

40

45

50

De acuerdo con aspectos de la presente divulgación, se proporcionan sistemas para entregar la potencia computacional requerida mediante tecnología de biochip avanzada, y para permitir adquisición y procesamiento simultáneos a altas tasas de muestreo, a través de una arquitectura de adquisición y procesamiento de alto desempeño y configurable. Por ejemplo, como se describe en mayor detalle en el presente documento, se proporciona una plataforma de biodetección, que usa múltiples coprocesadores especializados que realizan filtrado de señal basado en la Transformada Rápida de Fourier (FFT), así como otros algoritmos de corrección y modulación/multiplexación complejos. Un procesador especializado adicional se usa para sintetizar las señales de estímulos para los sensores, y se proporciona un procesador central para controlar la totalidad del sistema. Con este enfoque, se proporciona un sistema embebido completamente autónomo, que posibilita operación independiente de la plataforma, proporcionando por lo tanto flexibilidad y usabilidad aumentada.

De esta manera, se consideran nuevos biochips de alta densidad como soluciones altamente prometedoras para numerosas aplicaciones, donde se requiere análisis de alto rendimiento. Sin embargo, las plataformas electrónicas existentes no pueden obtener y procesar la cantidad superior de datos producidos. La arquitectura multi-canal y de alto rendimiento escalable en el presente documento cumple las necesidades para obtener y procesar esta cantidad de datos superior, por ejemplo, cuando se implementa en un único SoC de Zynq. Por ejemplo, incluso cuando se usa uno de los Zynq más pequeños, los resultados experimentales demuestran que el sistema soporta 8 veces más sensores y más de 1000 veces frecuencia de muestreo superior que la generación anterior de la plataforma de biodetección. Aprovechando las características reconfigurables de este SoC, los resultados también sugieren que la plataforma elegida permite implementar un sistema escalable que soporta coprocesadores con tamaños de FFT configurables, posibilitando medición de señal optimizada y ajustable para cada biochip, sin sacrificar eficacia en uso de recursos de hardware, permitiendo que se expanda el sistema desarrollado para tratar con los requisitos de los biochips futuros.

La terminología usada en el presente documento es para el fin de describir realizaciones particulares únicamente y no se pretende para limitar la invención. Como se usa en el presente documento, las formas singulares "un", "una" y "el", "la" se pretende que incluyan las formas plurales también, a menos que el contexto lo indique claramente de otra manera. Se entenderá adicionalmente que los términos "comprende" y/o "que comprende", cuando se usan en esta memoria descriptiva, especifican la presencia de características, enteros, etapas, operaciones, elementos, y/o componentes, establecidos pero no excluyen la presencia o adición de una o más otras características, enteros, etapas, operaciones, elementos, componentes, y/o grupos de los mismos.

#### **REIVINDICACIONES**

- 1. Un sistema de detección biológica (100), que comprende:

- un biochip (102) que tiene al menos dos bloques (108) de sensores, teniendo cada bloque de sensores un canal de adquisición de señal (110) que es accesible independientemente de manera que cada bloque de sensores puede leerse en paralelo; y

una plataforma de biodetección (104) que tiene:

desde el biochip.

30

40

55

60

- circuitería de accionamiento (112) para controlar cada bloque (108) de sensores del biochip; un conjunto de interfaces de adquisición (116) dispuestas de manera que una interfaz de adquisición selecta (116) está acoplada a un correspondiente canal de adquisición de señal (110); caracterizado por un conjunto de coprocesadores (122) de manera que un coprocesador selecto está asociado de manera inequívoca con una correspondiente de las interfaces de adquisición (116); y un procesador central (114) que controla la circuitería de accionamiento (112), interconecta con el conjunto de interfaces de adquisición (116) e interconecta con el conjunto de coprocesadores (122), para leer datos

- 2. El sistema de detección biológica de la reivindicación 1, en el que el biochip está caracterizado adicionalmente por:

tener cada bloque de sensores una matriz de al menos 16 sensores y un correspondiente multiplexor de división en el tiempo para leer sensores individuales desde un bloque correspondiente.

3. El sistema de detección biológica de acuerdo con cualquiera de las reivindicaciones anteriores, en el que el conjunto de interfaces de adquisición está caracterizado adicionalmente por:

un convertidor de analógico a digital (118) y un controlador (120), donde el controlador transporta información desde el convertidor de analógico a digital a su correspondiente coprocesador.

- 4. El sistema de detección biológica de la reivindicación 3, en el que el convertidor de analógico a digital tiene una frecuencia de muestreo de al menos 1 kHz y resolución de al menos 12 bits.

- 5. El sistema de detección biológica de acuerdo con cualquier reivindicación anterior, en el que cada coprocesador está caracterizado por:

una configuración que realiza al menos uno de:

- filtrado de señal basado en Transformación Rápida de Fourier (FFT) en los datos desde su correspondiente interfaz de adquisición;

- un algoritmo de corrección complejo que incluye un filtro Kalman,

- un controlador de temperatura; y

- un modulador y demodulador complejo.

- 45 6. El sistema de detección biológica de acuerdo con cualquier reivindicación anterior, caracterizado adicionalmente

una memoria principal que se comparte por el procesador central y cada uno de los coprocesadores.

- 50 7. El sistema de detección biológica de acuerdo con cualquier reivindicación anterior, en el que la circuitería de accionamiento está caracterizada adicionalmente por:

- circuitería para generar corrientes de polarización y campos magnéticos oscilantes que se aplican a los sensores del biochip.

- 8. El sistema de detección biológica de acuerdo con cualquier reivindicación anterior, caracterizado por:

- la circuitería de accionamiento está acoplada al procesador central de manera que un generador de señal de la circuitería de accionamiento está controlado por el procesador central para tener una frecuencia ajustable y puede generar también formas y amplitudes de señales arbitrarias.

- 9. El sistema de detección biológica de acuerdo con cualquier reivindicación anterior, en el que la circuitería de accionamiento está caracterizada por:

- Sintetizadores Digitales Directos (DDS) que pueden configurarse con generadores de señales arbitrarias desplegados en una estructura reconfigurable, que se controlan mediante el procesador central.

- 10. El sistema de detección biológica de acuerdo con cualquiera de las reivindicaciones anteriores, en el que una interfaz de adquisición está configurada para medir datos de sensor desde el correspondiente canal de adquisición de señal a una frecuencia de enlace o banda de frecuencia específica que se determina mediante la modulación inducida por el campo magnético, la corriente de polarización, la respuesta del sensor a estas señales de CA y el ruido y diafonía del sistema.

- 11. El sistema de detección biológica de acuerdo con cualquiera de las reivindicaciones anteriores, caracterizado por:

- la plataforma de biodetección implementada en dos componentes, incluyendo un componente de lógica programable y un componente de sistema de procesamiento, en el que la circuitería de accionamiento, los coprocesadores y las interfaces de adquisición se implementan en el componente de lógica programable, y el procesador central y la memoria principal se implementan en el sistema de procesamiento.

5

14

FIG. 4