# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 617 303

51 Int. Cl.:

**G06F 9/54** (2006.01) **G06F 9/38** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

86 Fecha de presentación y número de la solicitud internacional: 19.09.2011 PCT/US2011/052196

(87) Fecha y número de publicación internacional: 29.03.2012 WO2012040121

(96) Fecha de presentación y número de la solicitud europea: 19.09.2011 E 11764399 (9)

(97) Fecha y número de publicación de la concesión europea: 23.11.2016 EP 2619666

(54) Título: Técnicas de comunicación entre procesadores en una plataforma informática de múltiples procesadores

(30) Prioridad:

16.09.2011 US 201113235266 20.09.2010 US 384571 P 04.08.2011 US 201161515182 P 16.09.2011 US 201113235236

Fecha de publicación y mención en BOPI de la traducción de la patente: 16.06.2017

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121-1714, US

(72) Inventor/es:

BOURD, ALEXEI, V.; SHARP, COLIN, CHRISTOPHER; GARCIA GARCIA, DAVID, RIGEL y ZHANG, CHIHONG

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

#### **DESCRIPCIÓN**

Técnicas de comunicación entre procesadores en una plataforma informática de múltiples procesadores.

#### 5 Campo técnico

La divulgación se refiere a plataformas informáticas y, más particularmente, a plataformas informáticas que incluyen múltiples procesadores

#### 10 Antecedentes

15

20

25

30

35

40

45

50

55

60

65

Las plataformas informáticas que incluyen múltiples procesadores se utilizan para mejorar el rendimiento de las aplicaciones que tienen requisitos de alta intensidad de cálculo y/o requisitos de alto caudal de datos. Una plataforma informática de múltiples procesadores puede incluir una unidad de procesamiento central (CPU) de propósito general que puede actuar como un dispositivo anfitrión y uno o más dispositivos informáticos que la CPU anfitriona puede utilizar para descargar las prestaciones de tareas intensivas en cálculo, mejorando así el rendimiento de todo el sistema. En algunos casos, uno o más dispositivos informáticos pueden ser diseñados específicamente para procesar ciertos tipos de tareas más eficientemente que la CPU anfitriona, lo cual puede proporcionar mejoras adicionales de rendimiento para el sistema en general. Por ejemplo, los uno o más dispositivos informáticos pueden ser diseñados específicamente para ejecutar algoritmos paralelos más eficazmente que la CPU anfitriona

Un tipo de dispositivo informático que se puede utilizar en un sistema informático de múltiples procesadores es una unidad de procesamiento de gráficos (GPU). Tradicionalmente, las GPU incluían hardware de función fija que estaba diseñado específicamente para la representación en tiempo real de gráficos en 3 dimensiones (3D) para un dispositivo de visualización, pero no era habitualmente programable, es decir, un programa compilado no se podía descargar a la GPU y ejecutar en la GPU. Más recientemente, sin embargo, con el desarrollo de unidades de sombreado programables, gran parte de la arquitectura de la GPU se ha desplazado a una arquitectura programable que incluye muchos elementos de procesamiento en paralelo. La arquitectura programable permite que la GPU facilite la ejecución, no solo de las operaciones de gráficos, sino también de tareas de cálculo de propósito general de una manera sumamente paralela.

El uso de una GPU para ejecutar tareas de cálculo específicas sin gráficos, de propósito general, puede denominarse en el presente documento cálculo de propósito general en unidades de procesamiento de gráficos (GPGPU) o, de forma alternativa, cálculo de GPU. En algunos casos, las GPU puede dejar disponibles interfaces de programación de aplicaciones (API), que no son específicas para gráficos, facilitando de esta manera la programación de la GPU para la ejecución de tareas de cálculo de propósito general. Las tareas de cálculo de GPU pueden incluir tareas que son intensivas en cálculos y/o que incluyen un alto grado de paralelismo, por ejemplo, cálculos matriciales, cálculos de procesamiento de señales, algoritmos estadísticos, aplicaciones de modelado molecular, aplicaciones financieras, formación de imágenes médicas, aplicaciones de criptoanálisis, etc.

Una GPU es solo un tipo de dispositivo informático que se puede utilizar en una plataforma informática de múltiples procesadores, y también pueden utilizarse otros tipos de dispositivos informáticos además o en lugar de una GPU. Por ejemplo, entre otros tipos de dispositivos informáticos que pueden utilizarse en una plataforma informática de múltiples procesadores se incluyen, por ejemplo, una CPU adicional, un procesador de señales digitales (DSP), un procesador Motor de Banda Ancha Celular (Cell / BE) o cualquier otro tipo de unidad de procesamiento.

Una plataforma informática de múltiples procesadores con múltiples dispositivos informáticos puede ser una plataforma homogénea o una plataforma heterogénea. En una plataforma homogénea, todos los dispositivos informáticos comparten una arquitectura común del conjunto de instrucciones (ISA). Por el contrario, una plataforma heterogénea puede incluir dos o más dispositivos informáticos con diferentes ISA. En general, los diferentes tipos de dispositivos informáticos pueden tener diferentes ISA, y diferentes marcas de dispositivos informáticos del mismo tipo también puede tener diferentes ISA.

El rendimiento de una plataforma informática de múltiples procesadores puede mejorarse aún más mediante la utilización de dispositivos informáticos de múltiples núcleos y/o dispositivos informáticos de muchos núcleos. Un ejemplo de un dispositivo informático de múltiples núcleos es la GPU que se ha descrito anteriormente, que contiene una unidad de sombreado programable que tiene una pluralidad de núcleos de procesamiento. Las CPU, sin embargo, también pueden diseñarse para incluir múltiples núcleos de procesamiento. En general, cualquier chip o troquel que incluye múltiples núcleos de procesamiento puede considerarse como un procesador de múltiples núcleos. Un núcleo de procesamiento puede referirse a una unidad de procesamiento que es capaz de ejecutar una instrucción en un determinado conjunto de datos. Por ejemplo, una sola unidad lógica y aritmética (ALU) o un procesador vectorial dentro de una GPU puede considerarse como un núcleo de procesamiento. Los procesadores de muchos núcleos se refieren en general a los procesadores de múltiples núcleos que tienen un número relativamente alto de núcleos, por ejemplo, superior a diez núcleos y, por lo general, están diseñados utilizando técnicas diferentes a las que se utilizan para diseñar procesadores de múltiples núcleos con un número menor de

núcleos. Los procesadores de múltiples núcleos proporcionan una mejora del rendimiento al permitir que un programa de software se ejecute en paralelo, por ejemplo, al mismo tiempo, en varios núcleos en un único chip.

Un modelo de programación en paralelo se refiere a un modelo de programación que está diseñado para permitir que un programa se ejecute al mismo tiempo en múltiples núcleos de procesamiento. El programa puede ser un programa de múltiples hilos, en cuyo caso, un solo hilo puede funcionar en cada núcleo de procesamiento. En algunos ejemplos, un único dispositivo informático puede incluir la totalidad de los núcleos de procesamiento utilizados para ejecutar el programa. En otros ejemplos, algunos de los núcleos de procesamiento utilizados para ejecutar el programa pueden estar situados en diferentes dispositivos informáticos del mismo tipo o de un tipo diferente.

Se puede utilizar una interfaz de programación de aplicaciones (API) del modelo de programación en paralelo, de plataforma informática heterogénea, para múltiples plataformas y múltiples proveedores, para proporcionar una especificación de lenguaje común para la programación en paralelo de una plataforma informática heterogénea, de múltiples núcleos, que incluye diferentes tipos de dispositivos informáticos potencialmente fabricados por diferentes proveedores que implementan diferentes ISA. El Lenguaje Informático Abierto (OpenCL<sup>TM</sup>) es un ejemplo de una API de programación en paralelo, de plataforma informática heterogénea, de múltiples plataformas y múltiples proveedores. Tales API pueden estar diseñadas para permitir un procesamiento de datos más generalizado en una GPU. Por ejemplo, más allá de la exposición de las capacidades del subsistema de sombreado ampliado mediante un lenguaje informático, estas API pueden generalizar el flujo de datos y los trayectos de control hacia la GPU de una manera específica sin gráficos. Actualmente, sin embargo, los conjuntos de instrucciones proporcionados por tales API se basan en la arquitectura de hardware de una GPU y, por lo tanto, están limitadas a la funcionalidad que es compatible con arquitecturas de GPU existentes.

El documento US 6618759 se refiere a las operaciones de gráficos tridimensionales en un entorno en red que tiene un anfitrión cliente y un anfitrión principal. El anfitrión cliente es capaz de emitir comandos de OpenGL para ser ejecutados por un anfitrión principal de forma inmediata. La patente divulga el almacenamiento en memoria caché de comandos de gráficos en modalidad inmediata, en particular, proporcionando dos tipos de comandos de gráficos en modalidad inmediata, un tipo de paquete de tamaño completo que incluye un campo de código de memoria caché, un campo de índice de tabla y un campo de datos correspondiente al comando, y un tipo de paquete truncado que incluye solo el campo de código de memoria caché y el campo de índice de tabla. En el caso de que el comando ya haya sido almacenado dentro del servidor principal, solo el paquete truncado se envía al anfitrión servidor y el anfitrión servidor es capaz de ejecutar el comando recuperando el campo de datos previamente almacenado en respuesta al índice de tabla suministrado en el paquete truncado.

#### Sumario

5

10

15

20

35

40

45

60

65

Esta divulgación describe las técnicas de comunicación que pueden utilizarse dentro de una plataforma informática de múltiples procesadores. Las técnicas pueden, en algunos ejemplos, proporcionar interfaces de software que pueden utilizarse para prestar soporte al paso de mensajes dentro de una plataforma informática de múltiples procesadores que inicia las tareas utilizando las colas de comandos. Las técnicas pueden, en ejemplos adicionales, proporcionar interfaces de software que pueden utilizarse para la comunicación entre procesadores de memoria compartida dentro de una plataforma informática de múltiples procesadores. En ejemplos adicionales, las técnicas pueden proporcionar una unidad de procesamiento de gráficos (GPU), que incluye hardware para prestar soporte al paso de mensajes y/o a la comunicación de memoria compartida entre la GPU y una CPU anfitriona.

De acuerdo con un primer aspecto de la presente invención, se proporciona un aparato que comprende:

medios para colocar una pluralidad de comandos en una cola de comandos en respuesta a la recepción de una o más instrucciones de puesta en cola desde un proceso que se está ejecutando en un dispositivo anfitrión, incluyendo la pluralidad de comandos un primer comando que instruye al dispositivo anfitrión para transferir datos entre un primer espacio de memoria asociado con el dispositivo anfitrión y un segundo espacio de memoria asociado con una unidad de procesamiento de gráficos (GPU), incluyendo la pluralidad de comandos, además, un segundo comando que instruye al dispositivo anfitrión para iniciar la ejecución de una tarea en la GPU; y

medios para hacer pasar uno o más mensajes entre el proceso que se está ejecutando en el dispositivo anfitrión y una tarea que se está ejecutando en la GPU, mientras la tarea se está ejecutando en la GPU, y en respuesta a la recepción de una o más instrucciones de paso de mensajes desde el proceso que se está ejecutando en el dispositivo anfitrión.

De acuerdo con un segundo aspecto de la presente invención, se proporciona un procedimiento que comprende:

la colocación, con una interfaz de cola de comandos que se está ejecutando en uno o más procesadores de un dispositivo anfitrión, de una pluralidad de comandos en una cola de comandos, en respuesta a la recepción de una o más instrucciones de puesta en cola desde un proceso que se está ejecutando en el dispositivo anfitrión, incluyendo la pluralidad de comandos un primer comando que instruye al dispositivo anfitrión para transferir datos entre un

primer espacio de memoria asociado con el dispositivo anfitrión y un segundo espacio de memoria asociado con una unidad de procesamiento de gráficos (GPU), incluyendo la pluralidad de comandos, además, un segundo comando que instruye al dispositivo anfitrión para iniciar la ejecución de una tarea en la GPU; y

- el paso, con una interfaz de paso de mensajes que se está ejecutando en los uno o más procesadores del dispositivo anfitrión, de uno o más mensajes entre el proceso que se está ejecutando en el dispositivo anfitrión y una tarea que se está ejecutando en la GPU, mientras la tarea se está ejecutando en la GPU, y en respuesta a la recepción de una o más instrucciones de paso de mensajes desde el proceso en ejecución en el dispositivo anfitrión.

- De acuerdo con un tercer aspecto de la presente invención, se proporciona un medio legible por ordenador que comprende instrucciones para hacer que uno o más procesadores lleven a cabo el procedimiento de acuerdo con el segundo aspecto de la presente invención.

#### Breve descripción de los dibujos

15

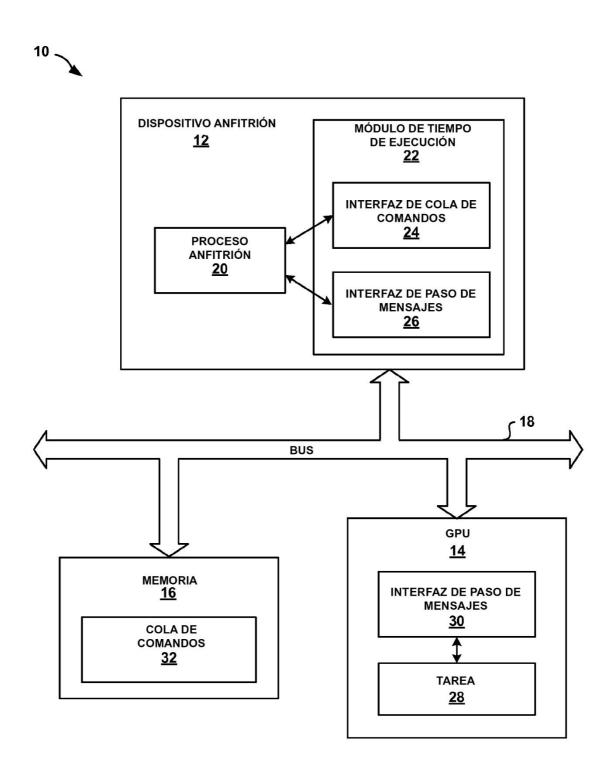

- La FIG. 1 es un diagrama de bloques que ilustra un sistema informático ejemplar que puede utilizarse para llevar a cabo técnicas de paso de mensajes de acuerdo con esta divulgación.

- La FIG. 2 es un diagrama de bloques que ilustra una GPU ejemplar que puede utilizarse en el sistema informático de la FIG. 1 de acuerdo con esta divulgación.

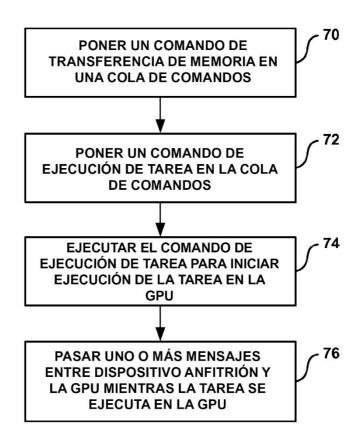

- La FIG. 3 es un diagrama de flujo que ilustra una técnica ejemplar para el paso de mensajes en un entorno de plataforma de múltiples procesadores de acuerdo con esta divulgación.

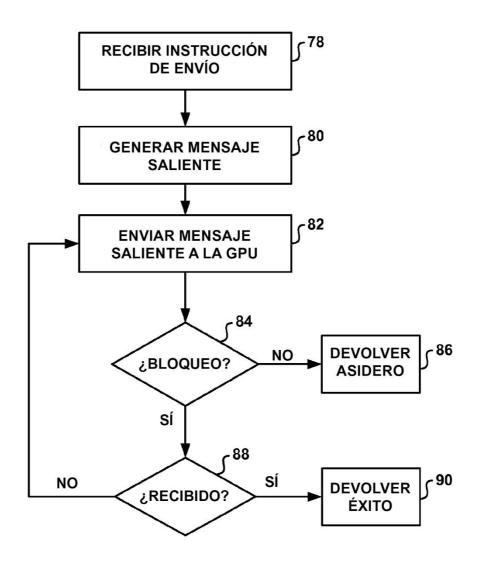

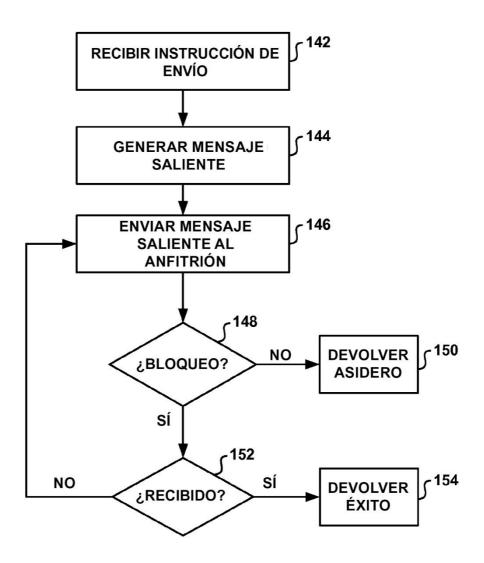

- La FIG. 4 es un diagrama de flujo que ilustra una técnica ejemplar para la ejecución de una instrucción de envío emitida por un proceso que se está ejecutando en un dispositivo anfitrión, de acuerdo con esta divulgación.

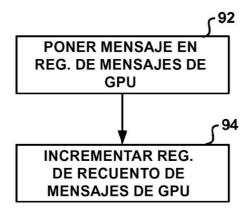

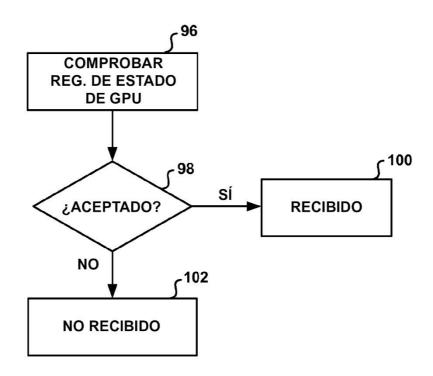

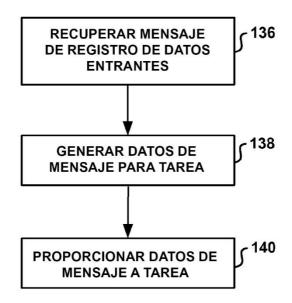

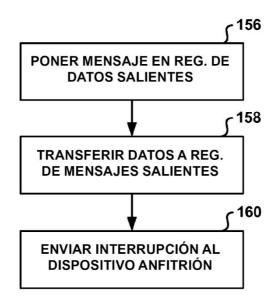

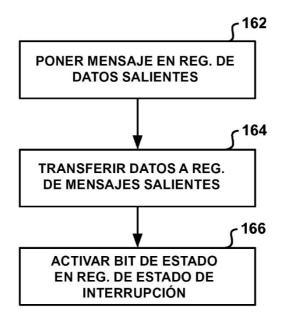

- Las FIGs. 5 y 6 son diagramas de flujo que ilustran técnicas ejemplares que pueden utilizarse para implementar partes de la técnica ilustrada en la FIG. 4 de acuerdo con esta divulgación.

30

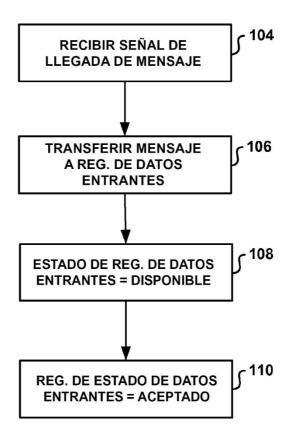

- La FIG. 7 es un diagrama de flujo que ilustra una técnica ejemplar para el procesamiento de un mensaje recibido en un dispositivo informático, por ejemplo, una GPU, de acuerdo con esta divulgación.

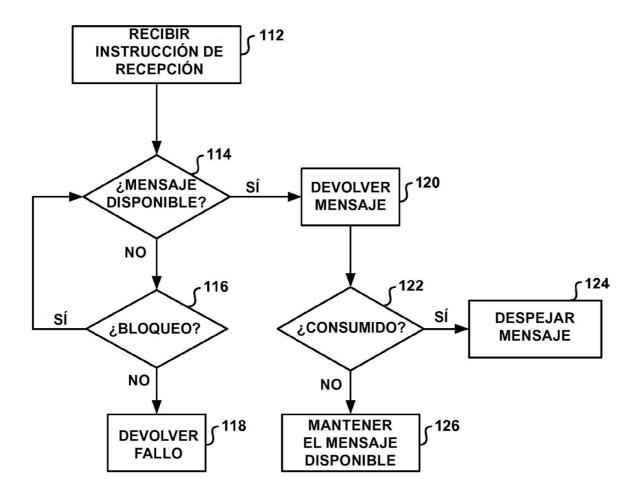

- La FIG. 8 es un diagrama de flujo que ilustra una técnica ejemplar para la ejecución de una instrucción de recepción emitida por una tarea que se está ejecutando en un dispositivo informático, por ejemplo, una GPU, de acuerdo con esta divulgación.

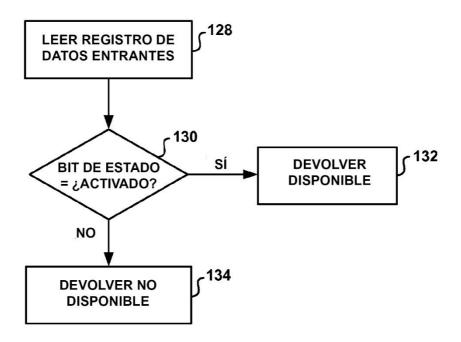

- Las FIGs. 9 y 10 son diagramas de flujo que ilustran técnicas ejemplares que pueden utilizarse para implementar partes de la técnica ilustrada en la FIG. 8 de acuerdo con esta divulgación.

40

- La FIG. 11 es un diagrama de flujo que ilustra una técnica ejemplar para la ejecución de una instrucción de envío emitida por un proceso que se está ejecutando en un dispositivo informático, por ejemplo, una GPU, de acuerdo con esta divulgación.

- Las FIGs. 12 y 13 son diagramas de flujo que ilustran técnicas ejemplares que pueden utilizarse para implementar partes de la técnica ilustrada en la FIG. 11 de acuerdo con esta divulgación.

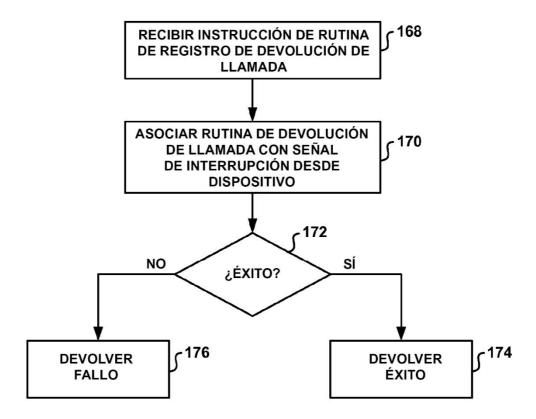

- La FIG. 14 es un diagrama de flujo que ilustra una técnica ejemplar para la ejecución de una instrucción de registro de rutina de devolución de llamada, emitida por un proceso que se está ejecutando en un dispositivo anfitrión, de acuerdo con esta divulgación.

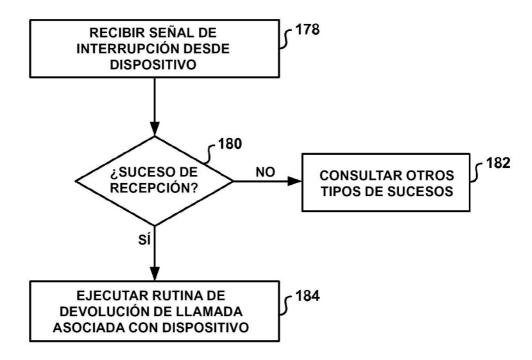

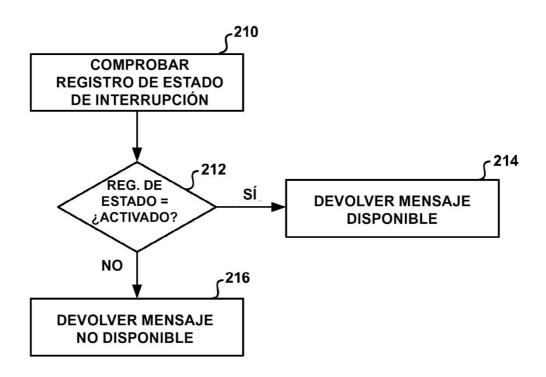

- La FIG. 15 es un diagrama de flujo que ilustra una técnica ejemplar para el procesamiento de una interrupción recibida desde un dispositivo informático de acuerdo con esta divulgación.

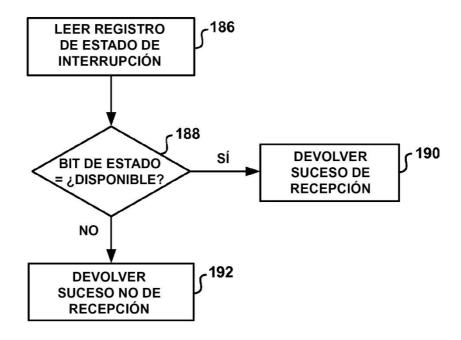

- Las FIGs. 16 y 17 son diagramas de flujo que ilustran técnicas ejemplares que pueden utilizarse para implementar partes de la técnica ilustrada en la FIG. 15 de acuerdo con esta divulgación.

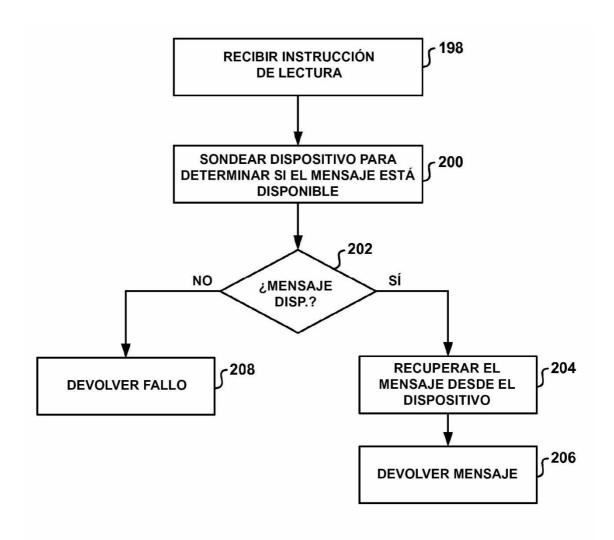

- La FIG. 18 es un diagrama de flujo que ilustra una técnica ejemplar para la ejecución de una instrucción de lectura emitida por un proceso que se está ejecutando en un dispositivo anfitrión, de acuerdo con esta divulgación.

60

- La FIG. 19 es un diagrama de flujo que ilustra una técnica ejemplar que puede utilizarse para implementar partes de la técnica ilustrada en la FIG. 18 de acuerdo con esta divulgación.

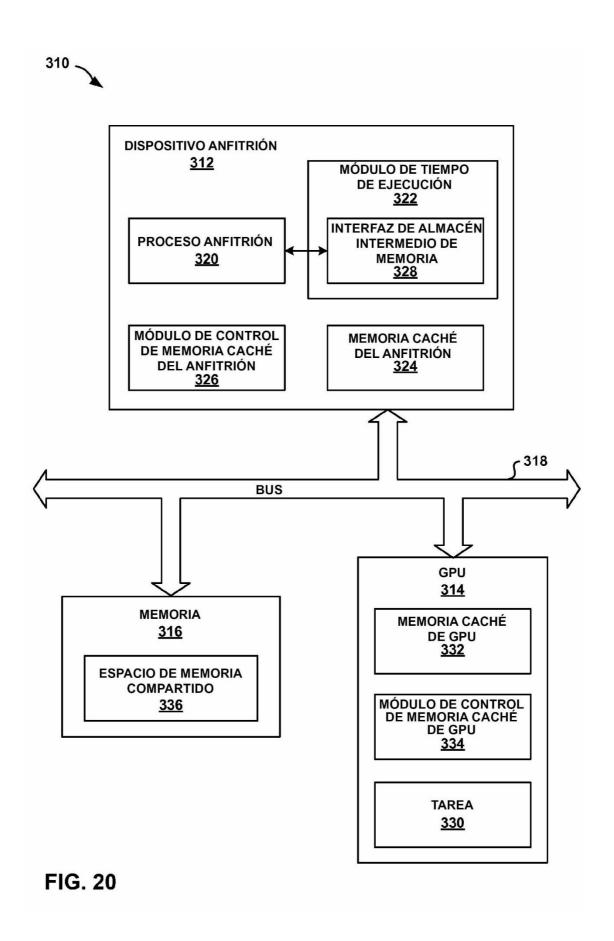

- La FIG. 20 es un diagrama de bloques que ilustra un sistema informático ejemplar que puede facilitar el uso de objetos de memoria inmediata de acuerdo con esta divulgación.

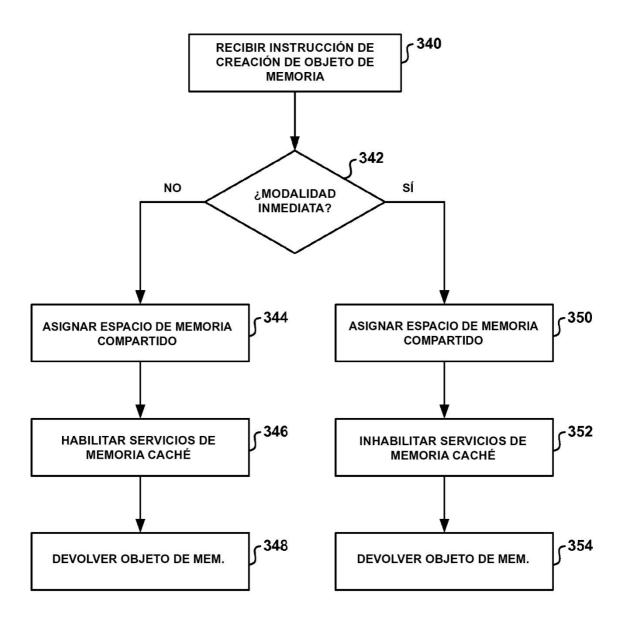

La FIG. 21 es un diagrama de flujo que ilustra una técnica ejemplar para la ejecución de una instrucción de creación de objetos de memoria emitida por un proceso que se está ejecutando en un dispositivo anfitrión, de acuerdo con esta divulgación.

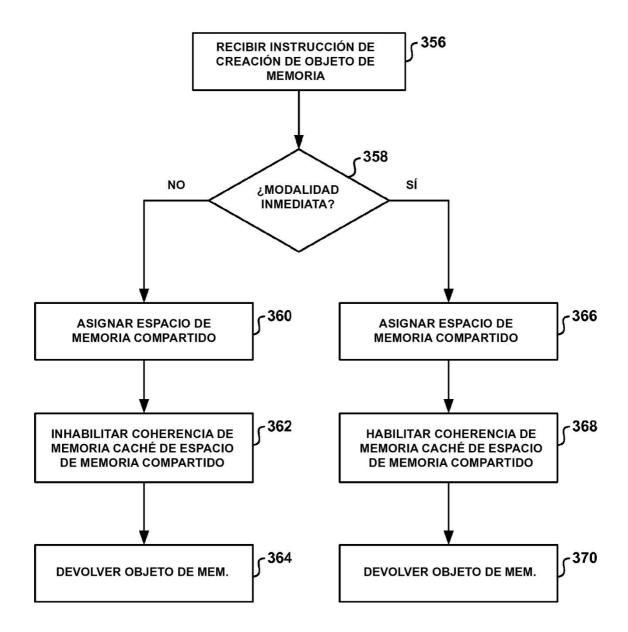

- La FIG. 22 es un diagrama de flujo que ilustra otra técnica ejemplar para la ejecución de una instrucción de creación de objetos de memoria emitida por un proceso que se está ejecutando en un dispositivo anfitrión, de acuerdo con esta divulgación.

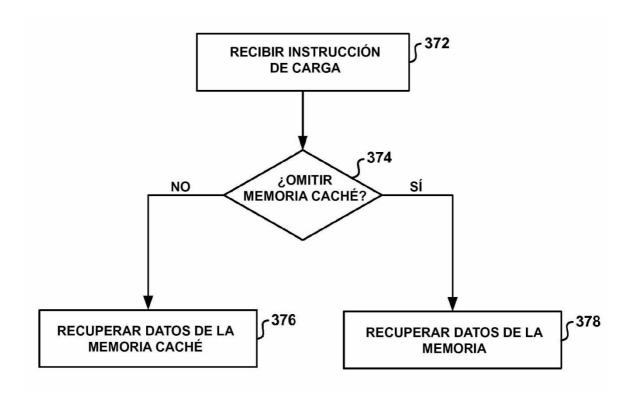

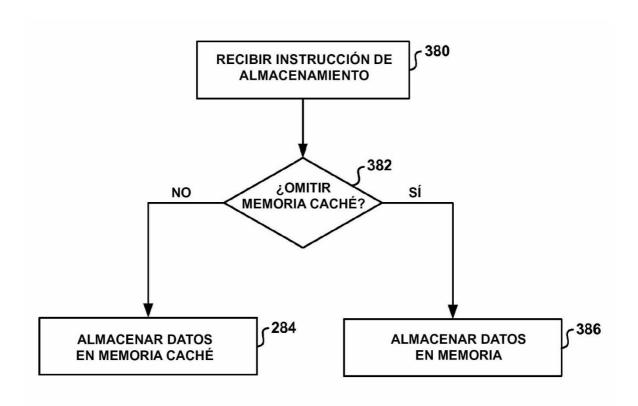

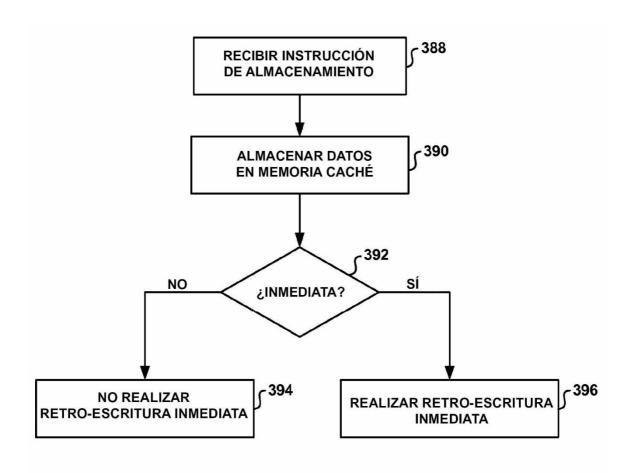

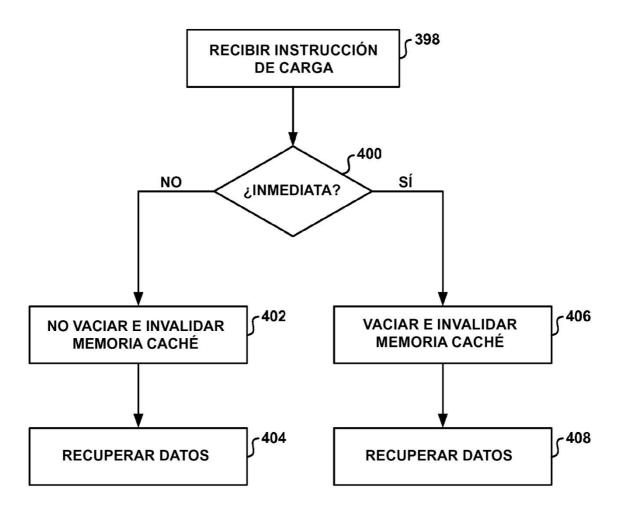

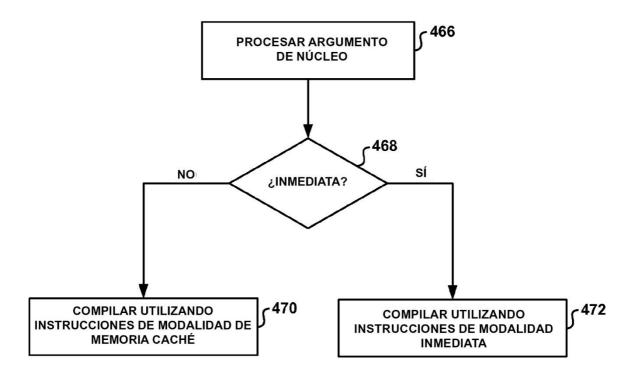

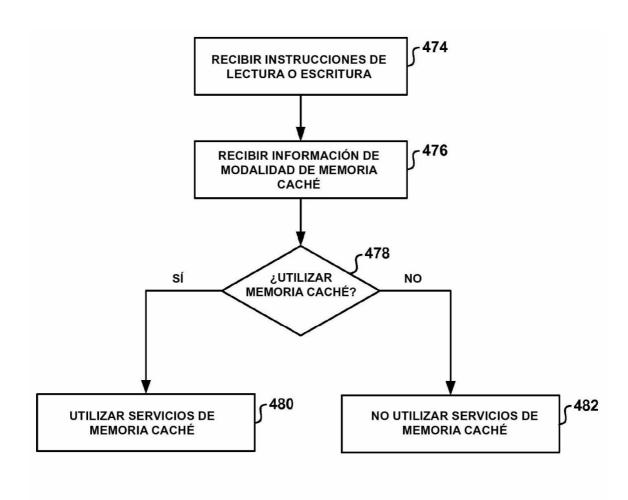

- Las FIGs. 23 a 26 son diagramas de flujo que ilustran técnicas ejemplares para el procesamiento de instrucciones en modalidad de memoria caché y en modalidad inmediata, de acuerdo con esta divulgación.

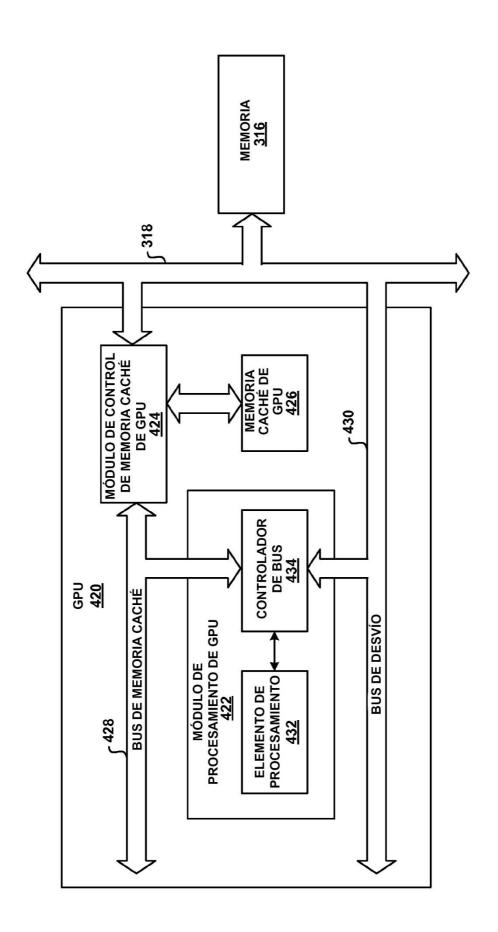

- La FIG. 27 es un diagrama de bloques que ilustra una GPU ejemplar que puede utilizarse en el sistema informático de la FIG. 20 de acuerdo con esta divulgación.

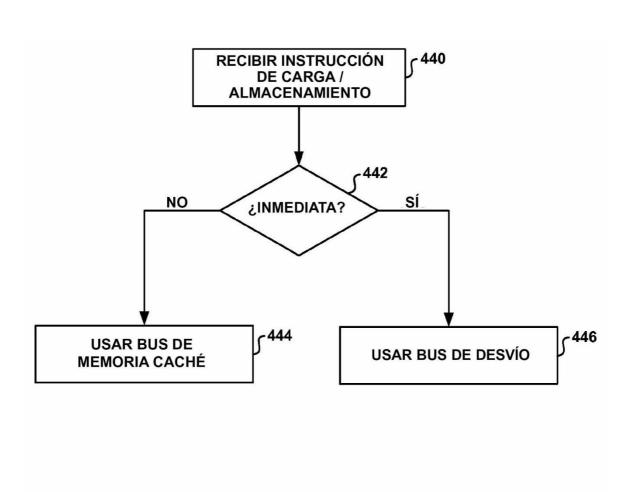

- La FIG. 28 es un diagrama de flujo que ilustra una técnica ejemplar para el procesamiento de instrucciones en modalidad de memoria caché y en modalidad inmediata de acuerdo con esta divulgación.

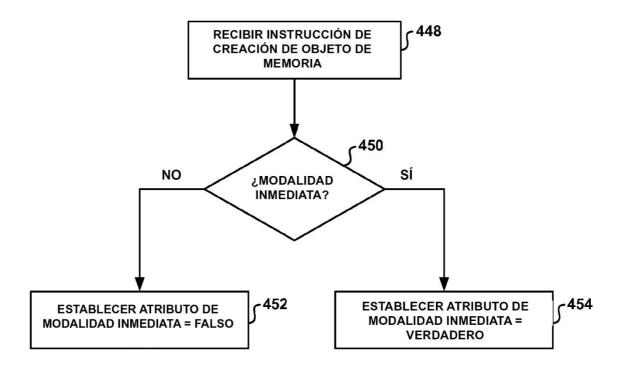

- La FIG. 29 es un diagrama de flujo que ilustra otra técnica ejemplar para la ejecución de una instrucción de creación de objetos de memoria emitida por un proceso que se está ejecutando en un dispositivo anfitrión, de acuerdo con esta divulgación.

- La FIG. 30 es un diagrama de flujo que ilustra cómo una GPU puede procesar una secuencia de instrucciones compiladas de acuerdo con una primera técnica de compilación de acuerdo con esta divulgación.

- La FIG. 31 es un diagrama de flujo que ilustra una técnica ejemplar para la compilación de código fuente para una tarea de acuerdo con esta divulgación.

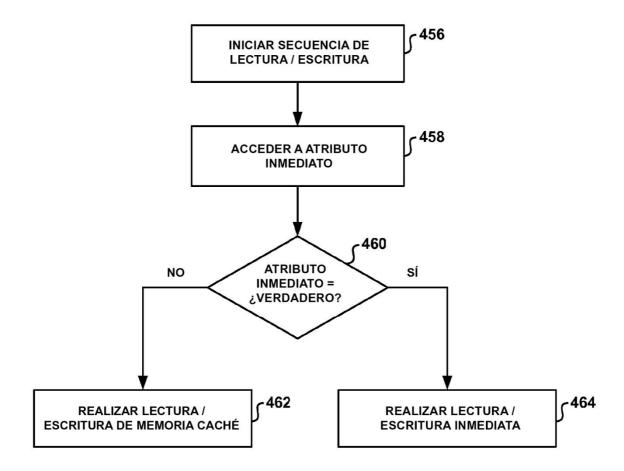

- La FIG. 32 es un diagrama de flujo que ilustra una técnica ejemplar que puede ser utilizada por una GPU para utilizar selectivamente los servicios de almacenamiento en memoria caché de acuerdo con esta divulgación.

#### Descripción detallada

30

35

40

45

50

55

60

Esta divulgación describe las técnicas de comunicación que pueden utilizarse dentro de una plataforma informática de múltiples procesadores. Las técnicas pueden, en algunos ejemplos, proporcionar interfaces de software que pueden utilizarse para prestar soporte al paso de mensajes dentro de una plataforma informática de múltiples procesadores que inicia las tareas utilizando las colas de comandos. Las técnicas pueden, en ejemplos adicionales, proporcionar interfaces de software que pueden utilizarse para la comunicación entre procesadores de memoria compartida dentro de una plataforma informática de múltiples procesadores. En ejemplos adicionales, las técnicas pueden proporcionar una unidad de procesamiento de gráficos (GPU) que incluye hardware para prestar soporte al paso de mensajes y/o a la comunicación de memoria compartida entre la GPU y una CPU anfitriona.

En los últimos años, los procesadores que fueron diseñados originalmente para el procesamiento de gráficos tridimensionales en tiempo real, por ejemplo, una unidad de procesamiento de gráficos (GPU), se generalizaron para realizar tareas de cálculo de propósito general (GPGPU). El valor de las GPGPU se ha demostrado en parte por la adopción de estándares para toda la industria, tales como, por ejemplo, el estándar Lenguaje Informático Abierto (OpenCL™). OpenCL es un ejemplo de una API de programación en paralelo de plataforma informática heterogénea, de múltiples plataformas y múltiples proveedores, que puede utilizarse para ejecutar programas que tienen paralelismo a nivel de tareas y/o paralelismo a nivel de datos sobre una plataforma informática de múltiples procesadores. La API está diseñada específicamente para permitir el procesamiento de datos más generalizado en una GPU, generalizando las vías de flujo de datos y de control de la GPU de manera específica sin gráficos. Una limitación de este enfoque es la granularidad gruesa de la comunicación de datos entre la CPU anfitriona y los dispositivos informáticos, por ejemplo, una GPU.

- Por ejemplo, la API de OpenCL proporciona una interfaz de cola de comandos que presta soporte a la granularidad a nivel de tareas de la comunicación entre un dispositivo anfitrión y uno o más dispositivos informáticos. Cada cola de comandos en general mantiene los comandos que serán ejecutados por un dispositivo informático específico. Un proceso anfitrión que se está ejecutando en un dispositivo anfitrión puede transferir datos entre el espacio de memoria del anfitrión y el espacio de memoria del dispositivo, mediante la colocación de un comando en la cola de comandos que instruye al dispositivo anfitrión para realizar la transferencia de memoria. De forma similar, el proceso anfitrión puede hacer que una tarea empiece a ejecutarse en un dispositivo informático mediante la colocación de un comando en la cola de comandos, instruyendo al dispositivo anfitrión para ejecutar una tarea en el dispositivo informático.

- La interfaz de cola de comandos puede configurarse para proporcionar la ejecución de comandos en orden o la ejecución de comandos de forma desordenada. Cuando la interfaz de cola de comandos está configurada para proporcionar la ejecución de comandos en orden, la interfaz de cola de comandos garantiza que los comandos se

ejecutarán en el orden en que los comandos se colocaron en la cola de comandos y que la ejecución de un comando posterior no comenzará hasta que el comando anterior haya finalizado su ejecución. Por lo tanto, cuando el proceso anfitrión coloca un comando en la cola de comandos para ejecutar una tarea, la cola de comandos espera a que la tarea complete la ejecución antes de ejecutar comandos adicionales cualesquiera que pueden ser colocados posteriormente en la cola de comandos.

En una configuración sencilla que implica una CPU anfitriona y una GPU y una cola de comandos en orden, un sistema de comunicación entre la CPU anfitriona y la GPU puede implicar las siguientes operaciones: (1) la CPU anfitriona prepara los datos y los coloca en la memoria accesible para la GPU; (2) la CPU anfitriona ordena a la GPU que ejecute una tarea; (3) la CPU anfitriona espera a que la GPU termine la ejecución de la tarea; y (4) la CPU anfitriona copia los datos desde la memoria accesible para la GPU a la memoria del anfitrión. En una configuración de este tipo, todos los datos necesarios para la ejecución de una tarea en la GPU se transfieren a la memoria accesible para la GPU antes del inicio de la ejecución de la tarea, y los datos producidos por la tarea que se está ejecutando en la GPU no están disponibles para la CPU anfitriona hasta después de que la tarea que se está ejecutando en la GPU complete su ejecución. Esta tosquedad en el intercambio de datos entre una CPU anfitriona y una GPU puede impedir las implementaciones efectivas de muchas operaciones útiles para aplicaciones basadas en paralelo, tales como, por ejemplo, la transmisión de mensajes entre procesos entre un proceso que se está ejecutando en el dispositivo anfitrión y una tarea que se está ejecutando en la GPU. Tales mensajes pueden ser útiles, por ejemplo, para permitir que una tarea que se está ejecutando en la GPU tenga la capacidad de ejecutar una llamada a procedimiento remoto (RPC) en la CPU anfitriona.

Cuando la interfaz de cola de comandos está configurada para proporcionar la ejecución desordenada de los comandos, el proceso anfitrión no es capaz de controlar cuándo, durante la ejecución de una tarea en particular, se llevará a cabo la ejecución de un comando en particular. Como tal, el modo de ejecución desordenada para la cola de comandos tampoco permite eficazmente la implementación del paso de mensajes entre procesos, entre un proceso que se está ejecutando en el dispositivo anfitrión y una tarea que se está ejecutando en la GPU.

Con respecto al modelo de memoria utilizada en OpenCL, la API define las denominadas memorias intermedias globales del CL y las imágenes globales del CL que pueden utilizarse para la compartición de datos entre una CPU anfitriona y una GPU o para compartir datos entre múltiples dispositivos informáticos de OpenCL. Sin embargo, la CPU y la GPU no pueden leer o escribir en una memoria intermedia al mismo tiempo. Habitualmente, una CPU prepara una o más memorias intermedias que contienen datos de origen y pasa las memorias intermedias a la GPU para su procesamiento. La GPU o bien modifica estas memorias intermedias o pone resultados en otras memorias intermedias que también fueron asignadas por software ejecutándose en la CPU a priori con el propósito de recibir las modificaciones de datos de GPU.

Aunque los objetos de memoria en OpenCL actualmente permiten utilizar una región del espacio de memoria del anfitrión para almacenar los datos de memoria intermedia utilizados por un dispositivo informático, la especificación permite que los dispositivos informáticos almacenen en memoria caché estos datos para la ejecución más eficaz de una tarea. El dispositivo anfitrión, en general, no es capaz de invalidar inmediatamente la memoria caché del dispositivo informático que se utiliza para almacenar en memoria caché los datos de memoria intermedia. Por lo tanto, incluso si el dispositivo anfitrión fuera a sobrescribir ciertos datos de memoria intermedia almacenados en el espacio de memoria del anfitrión, no hay garantía de que la memoria caché en el dispositivo informático se actualice con el fin de proporcionar al dispositivo informático acceso inmediato a los datos modificados. Además, dado que los resultados de los cálculos realizados por el dispositivo informático se pueden almacenar en la memoria caché del dispositivo informático, el proceso anfitrión que se está ejecutando en el dispositivo anfitrión no es capaz de leer ningún resultado parcial de la memoria intermedia, debido a que tales datos pueden ser inválidos debido a nuevos datos almacenados en la memoria caché del dispositivo informático. Por lo tanto, el modelo de gestión de memoria en OpenCL no permite inmediatamente compartir datos en proceso mediante una memoria compartida.

Las técnicas descritas en esta divulgación pueden utilizarse, en algunos ejemplos, para superar una o más de las limitaciones anteriormente mencionadas de la API de OpenCL. Por ejemplo, las técnicas de esta divulgación pueden proporcionar interfaces de software que se pueden utilizar para prestar soporte al paso de mensajes entre procesos dentro de una plataforma informática de múltiples procesadores que inicia las tareas utilizando colas de comandos de granularidad a nivel de tareas. Como otro ejemplo, las técnicas de esta divulgación pueden proporcionar interfaces de software que pueden utilizarse para prestar soporte al intercambio de datos en proceso mediante una memoria compartida dentro de una plataforma informática de múltiples procesadores.

En algunos ejemplos, las técnicas de esta divulgación pueden proporcionar una arquitectura de hardware de GPU que facilite el paso de mensajes a nivel de software. Por ejemplo, las técnicas de esta divulgación pueden proporcionar una arquitectura de hardware de GPU que está configurada para prestar soporte a la ejecución de instrucciones de paso de mensajes a nivel de software. En otros ejemplos, las técnicas de la presente divulgación pueden proporcionar una arquitectura de hardware de GPU que facilita la comunicación de memoria compartida entre la GPU y una CPU anfitriona. Por ejemplo, las técnicas de esta divulgación pueden proporcionar una arquitectura de hardware de GPU que está configurada para habilitar e inhabilitar de forma selectiva servicios de almacenamiento en memoria caché para un espacio de memoria compartida y/o para habilitar e inhabilitar de forma

selectiva un mecanismo de coherencia de memoria caché para un espacio de memoria compartida.

5

10

35

40

45

50

55

60

65

De acuerdo con un primer aspecto de esta divulgación, se proporciona una interfaz de paso de mensajes que facilita la ejecución de instrucciones de paso de mensajes entre un dispositivo anfitrión y uno o más dispositivos informáticos durante la ejecución de una tarea por el dispositivo informático. El paso de mensajes puede referirse a una forma de comunicación entre procesos, y potencialmente entre dispositivos, en la que cada uno de los procesos que se están comunicando realiza conjuntos complementarios de operaciones para pasar con éxito un mensaje. Por ejemplo, cada uno de los procesos que se comunica de acuerdo con un protocolo de paso de mensajes puede poner en práctica una operación de envío y una operación de recepción. Las técnicas de paso de mensajes en la presente divulgación pueden permitir que una CPU y un dispositivo informático, por ejemplo, una GPU, se pasen mensajes entre sí durante la ejecución de una tarea en el dispositivo informático. De esta manera, una plataforma informática de múltiples procesadores que implementa un esquema de comunicación de cola de comandos de granularidad a nivel de tareas puede ser capaz de facilitar la comunicación entre procesos y/o entre dispositivos.

- En algunos ejemplos, las técnicas de paso de mensajes descritas en esta divulgación pueden denominarse técnicas de "señalización de fuera de banda" debido a que las técnicas pueden utilizar una interfaz distinta a la interfaz de cola de comandos, que se utiliza habitualmente en OpenCL para la comunicación entre un dispositivo anfitrión y un dispositivo informático, tal como, por ejemplo, una GPU. En otras palabras, las técnicas de esta divulgación pueden incluir una nueva interfaz de comunicación fuera de banda que está lógicamente separada de la interfaz de cola de comandos dentro de banda, incluida dentro de OpenCL. La interfaz de comunicación fuera de banda puede no estar sujeta a la misma granularidad a nivel de tareas a la que está sujeta la interfaz de cola de comandos, proporcionando de ese modo una solución a una o más de las limitaciones descritas anteriormente con respecto a la granularidad a nivel de tareas de la cola de comandos.

- Los mensajes transferidos entre la CPU y la GPU de acuerdo con las técnicas de esta divulgación pueden ser de cualquier tipo de mensaje. Ejemplos de diferentes tipos de mensajes incluyen señales, solicitudes de asignación de memoria, solicitudes de des-asignación de memoria, mensajes de notificación, mensajes de sincronización, mensajes de invocación a procedimiento remoto (por ejemplo, mensajes que son parte de una llamada a procedimiento remoto (RPC)), paquetes de datos, mensajes de informes, mensajes de mecanismo de afirmación y mensajes de registro.

En el actual paradigma de OpenCL, todas las peticiones de una CPU anfitriona a una GPU se ponen en colas de comandos de OpenCL y se envían luego a la GPU. En particular, una aplicación podría poner en la cola de comandos un gran número de ejecuciones del núcleo y operaciones de memoria intermedia. Mientras tanto, si la primera tarea puesta en cola, por ejemplo, una ejecución del núcleo, necesita, por ejemplo, solicitar la asignación de memoria adicional de una CPU, surgen varios problemas. En primer lugar, ¿cómo notifica la GPU a la CPU desde el interior de un núcleo en ejecución que necesita que se produzca la asignación de memoria? En segundo lugar, ¿cómo notificar la CPU a la GPU la finalización de la asignación de memoria y de la dirección del bloque de memoria recién asignado? Las técnicas de interfaz de paso de mensajes de esta divulgación, sin embargo, pueden ser capaces de resolver estos problemas al permitir que uno o más mensajes que contienen las notificaciones y la información descritos anteriormente se pasen entre la CPU y la GPU.

Las técnicas de señalización fuera de banda de esta divulgación pueden utilizarse, en algunos ejemplos, para implementar la señalización entre una CPU anfitriona y uno o más dispositivos informáticos, por ejemplo, dispositivos informáticos de OpenCL. La señalización fuera de banda puede proporcionar rápidas notificaciones de fuera de banda, por ejemplo, utilizando un mecanismo de entrega solicitada o no solicitada. En algunos ejemplos, las técnicas de señalización fuera de banda pueden llevar cantidades relativamente pequeñas de datos.

De acuerdo con un segundo aspecto de esta divulgación, se proporciona una GPU que es capaz de enviar mensajes a, y recibir mensajes desde, los procesos que se están ejecutando en procesadores distintos a la GPU. Por ejemplo, una GPU puede incluir hardware que está configurado para implementar una o más operaciones para enviar y recibir mensajes. En algunos ejemplos, una GPU diseñada de acuerdo con esta divulgación puede incluir uno o más registros accesibles por anfitrión, configurados para el almacenamiento de información de estado y de datos, asociada con un protocolo de paso de mensajes. Los uno o más registros pueden estar configurados para facilitar el paso de mensajes entre una tarea que se está ejecutando en la GPU y un proceso que se está ejecutando en un dispositivo distinto a la GPU. En ejemplos adicionales, el bloque de procesamiento de la ALU de la GPU (por ejemplo, una unidad de sombreado programable) puede estar acoplado comunicativamente a los registros accesibles por anfitrión para enviar y recibir mensajes mediante los registros accesibles por anfitrión. La GPU también puede diseñarse para incluir varios mecanismos de sondeo y/o interrupción para implementar técnicas de paso de mensajes, síncronas y/o asíncronas.

De acuerdo con un tercer aspecto de esta divulgación, se proporciona una interfaz de memoria intermedia que permite crear objetos de memoria inmediata. Los objetos de memoria inmediata se pueden usar para implementar un espacio de memoria compartida no almacenable en memoria caché y/o un espacio de memoria compartida coherente con memoria caché, con el fin de compartir datos entre un proceso que se está ejecutando en un dispositivo anfitrión y una tarea que se está ejecutando en un dispositivo informático, mientras la tarea se está

ejecutando en el dispositivo informático. El espacio de memoria compartida puede ser un espacio de memoria que sea accesible tanto por el dispositivo anfitrión como por un dispositivo informático, por ejemplo, una GPU, durante la ejecución de una tarea por el dispositivo informático. Un espacio de memoria compartida no almacenable en memoria caché, como se usa en el presente documento, puede referirse a un espacio de memoria compartida para el cual una o más memorias caché correspondientes en el dispositivo anfitrión y/o el dispositivo informático, o ambos, están inhabilitadas para el espacio de memoria. Un espacio de memoria compartida coherente con memoria caché, como se usa en el presente documento, puede referirse a un espacio de memoria compartida donde se utilizan técnicas de coherencia de caché de memoria compartida para mantener la coherencia de memoria caché dentro de una o más memorias caché correspondientes en uno entre el dispositivo anfitrión y/o el dispositivo informático, o en ambos. El espacio de memoria compartida no almacenable en memoria caché y el espacio de memoria compartida coherente con memoria caché pueden permitir la compartición de datos en cualquier momento. Los objetos de memoria inmediata pueden, en algunos ejemplos, implementarse como una memoria compartida volátil no almacenable en memoria caché y/o como una memoria compartida volátil coherente con memoria caché para el dispositivo anfitrión y el dispositivo informático.

En algunos ejemplos, los objetos de memoria inmediata de esta divulgación pueden estar integrados dentro de una API de programación en paralelo, de plataforma informática heterogénea, de múltiples plataformas y múltiples proveedores, que incluye un esquema de gestión de memoria de objetos de memoria. Por ejemplo, los objetos de memoria inmediatos pueden estar integrados en OpenCL como un atributo adicional de los objetos de memoria de OpenCL, por ejemplo, objetos de memoria intermedia de OpenCL o los objetos de imagen de OpenCL. En tales ejemplos, los objetos de memoria inmediatos se pueden crear mediante la modificación de las funciones de creación de objetos de memoria para incluir un parámetro o indicador que especifica si el objeto de memoria resultante creado por la llamada a la función debería ser un objeto de memoria de modalidad estándar o un objeto de memoria de modalidad inmediata. De esta manera, las técnicas de esta divulgación pueden permitir a los sistemas informáticos de múltiples procesadores que implementan las API que incluyen esquemas de gestión de memoria de objetos de memoria, tales como OpenCL, poner en práctica el intercambio de datos en proceso mediante un espacio de memoria compartida que no esté sujeto a problemas de coherencia de memoria caché.

En ejemplos adicionales, los objetos de memoria inmediata de esta divulgación pueden utilizarse para el intercambio de datos en desarrollo entre una CPU anfitriona y un dispositivo informático de OpenCL o entre diferentes dispositivos informáticos de OpenCL. En ejemplos adicionales, los objetos de memoria inmediatos pueden contener marcadores de sincronización interna. En ejemplos adicionales, los objetos de memoria inmediatos se pueden usar junto con las señales fuera de banda para la sincronización.

De acuerdo con un cuarto aspecto de esta divulgación, se proporciona una GPU que incluye una memoria caché

correspondiente a un espacio de memoria compartida, que puede inhabilitarse de forma selectiva para determinados espacios de direcciones de memoria con el fin de proporcionar un espacio de memoria compartida no almacenable en memoria caché. Por ejemplo, la GPU puede habilitar e inhabilitar de forma selectiva los servicios de memoria caché proporcionados por una caché asociada con un espacio de memoria compartida, en respuesta a la recepción de información que especifica si se deberían utilizar los servicios de almacenamiento en memoria caché para la ejecución de operaciones de lectura y/o escritura con respecto al espacio de memoria compartida. En algunos ejemplos, la información que especifica si se deberían utilizar los servicios de almacenamiento en memoria caché para la ejecución de modalidad de almacenamiento en memoria caché o una instrucción de modalidad inmediata que especifica si debería utilizarse una modalidad de memoria caché o una modalidad inmediata para ejecutar la instrucción particular. En ejemplos adicionales, la información que especifica si se deberían utilizar los servicios de almacenamiento en memoria caché para la ejecución de las operaciones de lectura y/o escritura con respecto al espacio de memoria compartida puede ser un atributo de objeto de memoria en modalidad inmediata que especifica si una modalidad inmediata está habilitada para el objeto de memoria.

En ejemplos adicionales, las técnicas de esta divulgación pueden proporcionar una GPU que incluye una modalidad de coherencia con memoria caché que puede habilitarse selectivamente para proporcionar un espacio de memoria compartida coherente con memoria caché. En algunos ejemplos, la GPU puede habilitar selectivamente una modalidad de coherencia de memoria caché para una parte de la memoria caché correspondiente al espacio de memoria compartida, en base a una o más instrucciones recibidas desde un dispositivo anfitrión. El dispositivo anfitrión puede emitir una o más instrucciones a la GPU para habilitar selectivamente la modalidad de coherencia de memoria caché del espacio de memoria compartida para la parte de la memoria caché correspondiente al espacio de memoria compartida tras la asignación del espacio de memoria compartida por el dispositivo anfitrión, en base a un parámetro de modalidad inmediata especificado por un proceso anfitrión.

Las técnicas de señalización fuera de banda y de almacenamiento inmediato en memoria intermedia de esta divulgación pueden proporcionar un acoplamiento de tareas más minucioso entre una CPU anfitriona y la GPU, o entre dos dispositivos informáticos de OpenCL, en comparación con lo que de otra manera se podría obtener utilizando solamente la interfaz de cola de comandos de OpenCL. Las técnicas de esta divulgación pueden permitir que una plataforma informática de múltiples procesadores lleve a cabo una diversidad de operaciones con el fin de asistir en la ejecución eficaz de programas en paralelo y/o de múltiples hilos. Por ejemplo, las técnicas de esta

divulgación pueden permitir que una tarea que está ejecutándose en una GPU lance una RPC. Como otro ejemplo, las técnicas de esta divulgación pueden permitir que una tarea que se está ejecutando en la GPU lance, mediante la CPU, otra tarea de GPU. Como un ejemplo adicional, las técnicas de esta divulgación pueden permitir que una tarea que se está ejecutando en la GPU emita solicitudes de gestión de recursos, tales como, por ejemplo, las solicitudes de asignación de memoria y/o de des-asignación de memoria, a la CPU y/o al controlador que se está ejecutando en la CPU. Como otro ejemplo más, las técnicas de esta divulgación pueden permitir que una tarea de que se está ejecutando en la GPU lleve a cabo comprobaciones de estado y el paso general de mensajes a una CPU, tal como, por ejemplo, la implementación de un mecanismo de afirmación, informes de progreso y/o registro de diagnóstico.

- La FIG. 1 es un diagrama de bloques que ilustra un sistema informático ejemplar 10 de acuerdo con esta divulgación. El sistema informático 10 está configurado para procesar una o más aplicaciones de software en múltiples dispositivos de procesamiento. En algunos ejemplos, las una o más aplicaciones de software pueden incluir un proceso anfitrión, y el sistema informático 10 puede estar configurado para ejecutar el proceso anfitrión y para distribuir la ejecución de una o más tareas iniciadas por el proceso anfitrión en otros dispositivos informáticos dentro del sistema informático 10. En ejemplos adicionales, el proceso anfitrión y/o las tareas ejecutadas por el sistema informático 10 pueden ser programados de acuerdo con un modelo de programación en paralelo. Por ejemplo, las aplicaciones pueden incluir instrucciones que están diseñadas para aprovechar el paralelismo a nivel de tareas y/o el paralelismo a nivel de datos de los sistemas de hardware subyacentes.

- El sistema informático 10 puede ser un ordenador personal, un ordenador de sobremesa, un ordenador portátil, una estación de trabajo de ordenador, una consola o plataforma de videojuegos, un teléfono móvil, tal como, por ejemplo, un teléfono celular o por satélite, un teléfono móvil, un teléfono fijo, un teléfono de Internet, un dispositivo portátil como un dispositivo de videojuegos portátil o un asistente digital personal (PDA), un reproductor de medios digitales, tal como un reproductor personal de música, un reproductor de vídeo, un dispositivo de visualización, o un televisor, un decodificador de televisión, un servidor, un dispositivo de red intermedio, un ordenador central o cualquier otro tipo de dispositivo que procese información.

El sistema informático 10 incluye un dispositivo anfitrión 12, una unidad de procesamiento de gráficos (GPU) 14, una memoria 16 y una red 18 de interconexión. El dispositivo anfitrión 12 está configurado para proporcionar una plataforma para la ejecución de un proceso anfitrión y un módulo de tiempo de ejecución para una API de plataforma informática de múltiples procesadores. Habitualmente, el dispositivo anfitrión 12 es una CPU de propósito general, aunque el dispositivo anfitrión 12 puede ser cualquier tipo de dispositivo capaz de ejecutar programas. El dispositivo anfitrión 12 está acoplado comunicativamente a la GPU 14 y a la memoria 16 a través de la red de interconexión 18. El dispositivo anfitrión 12 incluye un proceso anfitrión 20 y un módulo de tiempo de ejecución 22, cada uno de los cuales se puede ejecutar en cualquier combinación de uno o más procesadores programables.

El proceso anfitrión 20 incluye un conjunto de instrucciones que forman un programa de software para su ejecución en la plataforma de sistema informático del sistema informático 10. El programa de software puede estar diseñado para realizar una o más tareas específicas para un usuario final. Tales tareas pueden, en algunos ejemplos, implicar algoritmos intensivos en cálculo que pueden explotar los múltiples dispositivos de procesamiento y las arquitecturas paralelas proporcionadas por el sistema informático 10.

40

45

50

55

60

65

El módulo de tiempo de ejecución 22 puede ser un módulo de software que se está ejecutando en el dispositivo anfitrión 12 que implementa una o más interfaces configuradas para dar servicio a una o más de las instrucciones contenidas en el proceso anfitrión 20. Las interfaces implementadas por el módulo de tiempo de ejecución 22 incluyen una interfaz de cola de comandos 24 y una interfaz de paso de mensajes de anfitrión 26. En algunos ejemplos, el módulo de tiempo de ejecución 22 puede implementar una o más interfaces contenidas dentro de una API estándar del sistema de múltiples procesadores, además de las interfaces descritas en esta divulgación. En algunos ejemplos, la API estándar puede ser una API de plataforma informática heterogénea, una API de múltiples plataformas, una API de múltiples proveedores, una API de programación en paralelo, una API de programación en paralelo a nivel de tareas y/o una API de programación en paralelo a nivel de datos. En otros ejemplos, la API estándar puede ser la API de OpenCL. En dichos ejemplos, el módulo de tiempo de ejecución 22 puede estar diseñado para estar en conformidad con una o más de las especificaciones de OpenCL. En ejemplos adicionales, el módulo de tiempo de ejecución 22 puede implementarse como parte de, o ser, un programa controlador, por ejemplo, un controlador de GPU.

La interfaz de cola de comandos 24 está configurada para recibir una o más instrucciones de puesta en cola desde el proceso anfitrión 20 y para ejecutar las funciones especificadas por las instrucciones recibidas. En algunos ejemplos, la interfaz de cola de comandos 24 puede estar diseñada de acuerdo con la especificación de OpenCL. Por ejemplo, la interfaz de cola de comandos 24 puede implementar una o más de las instrucciones de puesta en cola especificadas en la especificación de OpenCL para interactuar con las colas de comandos.

De acuerdo con esta divulgación, la interfaz de paso de mensajes de anfitrión 26 está configurada para recibir una o más instrucciones de paso de mensajes desde el proceso anfitrión 20 y para ejecutar las funciones especificadas por las instrucciones recibidas. En algunos ejemplos, la interfaz de paso de mensajes del anfitrión 26 puede implementarse como una extensión para una API estándar existente, tal como, por ejemplo, la API de OpenCL. En

ejemplos adicionales, la interfaz de paso de mensajes de anfitrión 26 se puede integrar en una API estándar existente, tal como, por ejemplo, la API de OpenCL.

La GPU 14 está configurada para ejecutar una o más tareas en respuesta a las instrucciones recibidas desde el dispositivo anfitrión 12. La GPU 14 puede ser cualquier tipo de GPU que incluya uno o más elementos de procesamiento programables. Por ejemplo, la GPU 14 puede incluir una o más unidades de sombreado programables que están configuradas para ejecutar una pluralidad de instancias de ejecución para una tarea en paralelo. Las unidades de sombreado programables pueden incluir una unidad de sombreado de vértices, una unidad de sombreado de fragmentos, una unidad de sombreado de geometría y/o una unidad de sombreado unificada. La GPU 14 está acoplada comunicativamente al dispositivo anfitrión 12 y a la memoria 16 a través de la red de interconexión 18. La GPU 14 incluye una tarea 28 y una interfaz de paso de mensajes de dispositivo 30. La tarea 28 y la interfaz de paso de mensajes de dispositivo 30 se puede ejecutar en cualquier combinación de uno o más elementos de procesamiento programables.

5

10

35

40

45

50

La tarea 28 comprende un conjunto de instrucciones que forman una tarea para la ejecución en un dispositivo informático en el sistema informático 10. En algunos ejemplos, el conjunto de instrucciones para la tarea 28 puede definirse en el proceso anfitrión 20 y, en algunos casos, compilarse mediante instrucciones incluidas en el proceso anfitrión 20 que se están ejecutando en el dispositivo anfitrión 12. En otros ejemplos, la tarea 28 puede ser un programa de núcleo que tiene múltiples instancias de ejecución que se están ejecutando en la GPU 14 en paralelo.

En dichos ejemplos, el proceso anfitrión 20 puede definir un espacio de índices para el núcleo que correlaciona instancias de ejecución del núcleo con respectivos elementos de procesamiento para la ejecución de las instancias de ejecución del núcleo, y la GPU 14 puede ejecutar las múltiples instancias de ejecución de núcleo para la tarea 28 de acuerdo con el espacio de índices definido para el núcleo.

De acuerdo con esta divulgación, la interfaz de paso de mensajes de dispositivo 30 está configurada para recibir una o más instrucciones de paso de mensajes desde el proceso anfitrión 20 y para ejecutar las funciones especificadas por las instrucciones recibidas. En algunos ejemplos, la interfaz de paso de mensajes de dispositivo 30 puede implementarse como una extensión de una API estándar existente. Por ejemplo, la API estándar puede ser una API de dispositivo informático estándar, tal como, por ejemplo, la API de C de OpenCL. En ejemplos adicionales, la interfaz de paso de mensajes de dispositivo 30 puede estar integrada en una API estándar existente, tal como, por ejemplo, la API de C de OpenCL.

La memoria 16 está configurada para almacenar datos para su uso por uno entre el dispositivo anfitrión 12 y la GPU 14, o ambos. La memoria 16 puede incluir cualquier combinación de una o más memorias o dispositivos de almacenamiento, volátiles o no volátiles, tales como, por ejemplo, memoria de acceso aleatorio (RAM), RAM estática (SRAM), RAM dinámica (DRAM), memoria de solo lectura (ROM), ROM borrable y programable (EPROM), ROM borrable y programable eléctricamente (EEPROM), memoria flash, un medio magnético de almacenamiento de datos o un medio de almacenamiento óptico. La memoria 16 está acoplada comunicativamente a un dispositivo anfitrión 12 y a la GPU 14 a través de la red de interconexión 18. La memoria 16 incluye la cola de comandos 32.

La cola de comandos 32 puede ser una estructura de datos implementada en la memoria 16 que almacena y recupera los comandos recibidos desde la interfaz de cola de comandos 24. En algunos ejemplos, la cola de comandos 32 puede ser una memoria intermedia que almacena los comandos en un orden particular para su ejecución.

La red de interconexión 18 está configurada para facilitar la comunicación entre el dispositivo anfitrión 12, la GPU 14 y la memoria 16. La red de interconexión 18 puede ser cualquier tipo de red de interconexión conocida en la técnica. En el sistema informático ejemplar 10 de la FIG. 1, la red de interconexión 18 es un bus. El bus puede incluir una o más de cualquiera entre una variedad de estructuras de bus, tales como, por ejemplo, un bus de tercera generación (por ejemplo, un bus HyperTransport o un bus InfiniBand), un bus de segunda generación (por ejemplo, un bus de Puerto de Gráficos Avanzado, un bus Expreso de Interconexión de Componentes Periféricos (PCIe) o un bus de Interfaz Extensible Avanzada (AXI)) o cualquier otro tipo de bus. La red de interconexión 18 está acoplada al dispositivo anfitrión 12, la GPU 14 y la memoria 16.

Las estructuras y funcionalidades de los componentes en el sistema informático 10 se describirán ahora con más detalle. Como se ha expuesto anteriormente, el proceso anfitrión 20 incluye un conjunto de instrucciones. El conjunto de instrucciones puede incluir, por ejemplo, una o más instrucciones de puesta en cola, y una o más instrucciones de paso de mensajes de anfitrión. En ejemplos adicionales, el conjunto de instrucciones puede incluir instrucciones que especifican las tareas o núcleos que se tienen que ejecutar en la GPU 14, instrucciones que crean las colas de comandos y asocian las colas de comando con determinados dispositivos, instrucciones que compilan y vinculan programas, instrucciones que configuran parámetros de núcleo, instrucciones que definen espacios de índices, instrucciones que definen un contexto de dispositivo y otras instrucciones que prestan soporte a la funcionalidad proporcionada por el proceso anfitrión 20.

65 El proceso anfitrión 20 puede interactuar con la interfaz de cola de comandos 24 mediante la emisión de una o más instrucciones de puesta en cola para la interfaz de cola de comandos 24, que instruyen a la interfaz de cola de

comandos 24 para colocar uno o más comandos en la cola de comandos 32. Las una o más instrucciones de puesta en cola pueden incluir instrucciones de puesta en cola de transferencias de memoria, que instruyen a la interfaz de cola de comandos 24 para poner en cola un comando de transferencia de memoria en la cola de comandos 32. Por ejemplo, las una o más instrucciones de puesta en cola pueden incluir una instrucción para poner en cola un comando que instruye al dispositivo anfitrión 12, por ejemplo, el módulo de tiempo de ejecución 22 que se ejecuta en el dispositivo anfitrión 12, para transferir datos entre un espacio de memoria asociado con el dispositivo anfitrión 12 y un espacio de memoria asociado con la GPU 14.

Un espacio de memoria puede estar asociado con el dispositivo anfitrión 12, si el espacio de memoria es accesible por el dispositivo anfitrión 12 durante la ejecución del proceso anfitrión 20 por el dispositivo anfitrión 12. De manera similar, un espacio de memoria puede estar asociado con la GPU 14 si el espacio de memoria es accesible por la GPU 14 durante la ejecución de la tarea 28 por la GPU 14. El espacio de memoria asociado con el dispositivo anfitrión 12 puede denominarse en la presente memoria espacio de memoria del anfitrión, y el espacio de memoria asociado con la GPU 14 puede denominarse en la presente memoria espacio de memoria del dispositivo. En algunos ejemplos, la memoria 16 puede incluir partes tanto del espacio de memoria del anfitrión como del espacio de memoria del dispositivo. En otros ejemplos, las partes de uno entre el espacio de memoria del anfitrión y el espacio de memoria del dispositivo, o ambos, pueden estar situadas en otros uno o más dispositivos de memoria que no se muestran en el sistema informático 10 de la FIG. 1.

En algunos ejemplos, el comando que instruye al dispositivo anfitrión 12 para transferir datos entre un espacio de memoria asociado con el dispositivo anfitrión 12 y un espacio de memoria asociado con la GPU 14 puede ser un comando que instruya al módulo de tiempo de ejecución 22 para transferir los datos almacenados en una parte del espacio de memoria del anfitrión a un objeto de memoria intermedia asignado en el espacio de memoria del dispositivo. La instrucción emitida por el proceso anfitrión 20 para poner en cola un comando de este tipo puede denominarse en el presente documento una instrucción de puesta en cola de escritura de memoria intermedia. En algunos casos, la instrucción de puesta en cola de memoria intermedia de escritura puede adoptar la forma de la función clEnqueueWriteBujfer () especificada por la especificación de API de OpenCL.

En ejemplos adicionales, el comando que instruye al dispositivo anfitrión 12 para transferir datos entre un espacio de memoria asociado con el dispositivo anfitrión 12 y un espacio de memoria asociado con la GPU 14 puede ser un comando que instruye al módulo de tiempo de ejecución 22 para transferir los datos almacenados en un objeto de memoria intermedia, asignado en el espacio de memoria del dispositivo, a una parte del espacio de memoria del anfitrión. La instrucción emitida por el proceso anfitrión 20 para poner en cola un comando de este tipo puede denominarse en el presente documento una instrucción de puesta en cola de lectura de memoria intermedia. En algunos casos, la instrucción de puesta en cola de lectura de memoria intermedia puede tomar la forma de la función clEnqueueReadBujfer() especificada por la especificación de API de OpenCL.

40

45

50

55

Las una o más instrucciones de puesta en cola también pueden incluir instrucciones de puesta en cola de ejecución de tareas que instruyen a la interfaz de cola de comandos 24 para poner en cola un comando de ejecución de tareas en la cola de comandos 32. Por ejemplo, las una o más instrucciones de puesta en cola pueden incluir una instrucción para poner en cola un comando que instruye a un dispositivo anfitrión 12, por ejemplo, el módulo de tiempo de ejecución 22 que se ejecuta en el dispositivo anfitrión 12, para ejecutar una tarea en la GPU 14. En algunos ejemplos, el comando para ejecutar la tarea puede ser un comando para ejecutar múltiples instancias de ejecución de la tarea en una pluralidad de elementos de procesamiento en la GPU 14 en paralelo. Por ejemplo, la tarea puede ser el núcleo, y el proceso anfitrión 20 puede definir un espacio de índices para el núcleo que correlaciona instancias de ejecución del núcleo con los respectivos elementos de procesamiento en la GPU 14 para la ejecución de las instancias de ejecución del núcleo. En un ejemplo de ese tipo, el comando para ejecutar una tarea puede ser un comando para ejecutar un núcleo en la GPU 14 de acuerdo con un espacio de índices definido para la GPU 14. En algunos casos, una instrucción de puesta en cola de ejecución de tareas puede tomar la forma de la función *clEnqueueNDRangeKernel* () especificada por la API de OpenCL.

De acuerdo con esta divulgación, el proceso anfitrión 20 también puede interactuar con la interfaz de paso de mensajes del anfitrión 26, emitiendo una o más instrucciones de paso de mensajes del anfitrión a la interfaz de paso de mensajes del anfitrión 26, instruyendo a la interfaz de paso de mensajes del anfitrión 26 para pasar uno o más mensajes entre el proceso anfitrión 20 que se está ejecutando en el dispositivo anfitrión 12 y la tarea 28 que se está ejecutando en la GPU 14. Las instrucciones de paso de mensajes del anfitrión pueden ser ejecutadas por el dispositivo anfitrión 12.

Las instrucciones de paso de mensajes del anfitrión pueden, en algunos ejemplos, incluir una instrucción de envío que instruye al dispositivo anfitrión 12 para enviar los datos especificados a un dispositivo especificado. Por ejemplo, la instrucción de envío puede instruir a la interfaz de paso de mensajes del anfitrión 26 para enviar un mensaje desde el proceso anfitrión 20 que se está ejecutando en el dispositivo anfitrión 12 a la tarea 28 que se está ejecutando en la GPU 14. En algunos ejemplos, la instrucción de envío puede incluir un primer parámetro de entrada que especifica un dispositivo particular al cual debería enviarse el mensaje y un segundo parámetro de entrada que especifica el contenido del mensaje a enviar.

La instrucción de envío puede ser o bien una instrucción de envío bloqueante o una instrucción de envío no bloqueante. La instrucción de envío puede incluir, en algunos ejemplos, un tercer parámetro de entrada que especifica si la instrucción de envío es una instrucción de envío bloqueante o una instrucción de envío no bloqueante. Una instrucción de envío bloqueante puede esperar hasta que se haya completado la operación de envío antes de volver al proceso de llamada, por ejemplo, el proceso anfitrión 20 que se está ejecutando en el dispositivo anfitrión 12. Una instrucción de envío no bloqueante puede volver al proceso de llamada sin tener que esperar hasta que se complete la operación de envío. Por ejemplo, la instrucción de envío no bloqueante puede devolver un asidero a la operación de envío particular, que posteriormente puede ser consultado por el proceso de llamada para determinar si la operación de envío se ha realizado con éxito. Una operación de envío no bloqueante puede fallar y, en el caso de fallo, el proceso de llamada puede tener que emitir de nuevo la instrucción de envío para volver a intentar la operación de envío.

En algunos ejemplos, la interfaz para la instrucción de envío puede adoptar la forma siguiente:

donde clEnviarDatosFueraDeBanda es el identificador de instrucción, cl\_dispositivo \*identificador\_dispositivo es un parámetro de entrada que especifica un dispositivo de OpenCL particular al cual debería enviarse el mensaje, int datos\_OOB es un parámetro de entrada que especifica el contenido del mensaje a enviar, y bool bloqueante es un parámetro de entrada que especifica si la instrucción es una instrucción de envío bloqueante o una instrucción de envío no bloqueante. En el caso de una instrucción bloqueante, la instrucción puede devolver un parámetro indicativo de si se completó con éxito la operación de envío. En el caso de una instrucción no bloqueante, la instrucción puede devolver un parámetro de asidero para la posterior consulta de estado por el proceso de llamada.

Las instrucciones de paso de mensajes del anfitrión pueden, en algunos ejemplos, incluir una instrucción de registro de rutina de devolución de llamada que instruye al dispositivo anfitrión 12 para registrar una devolución de llamada para recibir datos desde un dispositivo especificado de forma asincrónica. Por ejemplo, la instrucción de registro de rutina de devolución de llamada puede instruir a la interfaz de paso de mensajes del anfitrión 26 para invocar una rutina de devolución de llamada en respuesta a la recepción de una señal desde la GPU 14 que indica que la tarea que se está ejecutando en la GPU 14 ha enviado un mensaje al proceso anfitrión 20. La instrucción de registro de rutina de devolución de llamada puede incluir un primer parámetro de entrada que especifica un dispositivo concreto para el que se debería registrar una rutina de devolución de llamada y un segundo parámetro de entrada que especifica la ubicación de la memoria de la rutina de devolución de llamada.

En algunos ejemplos, la interfaz para la instrucción de registro de rutina de devolución de llamada puede adoptar la forma siguiente:

clRegistrarDevoluciónDeLlamadaDeDatosFueraDeBanda( cl\_dispositivo \*identificador\_dispositivo, void(\*) (int) punteroDevoluciónDeLlamada)

donde clRegistrarDevoluciónDeLlamadaDeDatosFueraDeBanda es el identificador de instrucción, cl\_dispositivo \*identificador\_dispositivo es un parámetro de entrada que especifica un dispositivo de OpenCL particular al cual debería enviarse el mensaje, y void(\*) (int) punteroDevoluciónDeLlamada es un parámetro de entrada que especifica la ubicación de la memoria de la rutina de devolución de llamada. La instrucción de registro de rutina de devolución de llamada puede devolver un parámetro indicativo de si se completó con éxito la operación de registro de rutina de devolución de llamada.

Las instrucciones de paso de mensajes del anfitrión pueden, en algunos ejemplos, incluir una instrucción de sondeo que instruye al dispositivo anfitrión 12 para intentar leer datos de un dispositivo especificado. Por ejemplo, la instrucción de sondeo puede instruir a la interfaz de paso de mensajes del anfitrión 26 para sondear la GPU 14 para obtener información de estado de mensaje, indicativa de si la tarea 28 que se está ejecutando en la GPU 14 ha enviado un mensaje. La instrucción de sondeo puede incluir un parámetro de entrada que especifica un dispositivo en particular a sondear y un parámetro de salida que especifica los datos obtenidos, si los hubiera, como resultado del sondeo.

60 En algunos ejemplos, la interfaz para la instrucción de sondeo puede adoptar la forma siguiente:

clIntentarLecturaDeDatosFueraDeBanda( cl\_dispositivo \*identificador\_dispositivo, int \*datos\_OOB)

65

55

5

10

30

35

40

donde ClIntentarLecturaDeDatosFueraDeBanda es el identificador de instrucción, cl\_dispositivo

\*identificador\_dispositivo es un parámetro de entrada que especifica un dispositivo de OpenCL particular a ser sondeado, e int \*datos\_OOB es un parámetro de salida que especifica los datos obtenidos, si los hubiera, como resultado del sondeo. La instrucción de sondeo puede devolver un parámetro indicativo de si se obtuvieron datos con éxito en la operación de sondeo.

5

10

De forma similar al proceso anfitrión 20, la tarea 28 puede incluir una o más instrucciones de paso de mensajes de dispositivo que son ejecutadas por un dispositivo informático. Las instrucciones de paso de mensajes de dispositivo pueden incluir una instrucción de envío que instruye a un dispositivo informático para enviar los datos especificados al dispositivo anfitrión 12. Por ejemplo, la instrucción de envío puede instruir a la GPU 14 para enviar un mensaje desde la tarea 28 que se está ejecutando en la GPU 14 al proceso anfitrión 20 que se está ejecutando en el dispositivo anfitrión 12.

La instrucción de envío puede ser o bien una instrucción de envío bloqueante o una instrucción de envío no bloqueante. La instrucción de envío puede incluir, en algunos ejemplos, un primer parámetro de entrada que especifica si la instrucción de envío es una instrucción de envío bloqueante o una instrucción de envío no bloqueante. Una instrucción de envío bloqueante puede detener el proceso de llamada, por ejemplo, la tarea 28 que se está ejecutando en la GPU 14, y esperar a que la operación de envío se complete antes de volver al proceso de llamada. Una instrucción de envío no bloqueante puede volver al proceso de llamada sin tener que esperar hasta que se complete la operación de envío. Por ejemplo, la instrucción de envío no bloqueante puede devolver un asidero a la operación de envío particular, que posteriormente puede ser consultado por el proceso de llamada para determinar si la operación de envío se ha realizado con éxito. Una operación de envío no bloqueante puede fallar y, en el caso de fallo, el proceso de llamada puede tener que emitir de nuevo la instrucción de envío para volver a intentar la operación de envío. La instrucción de envío puede incluir un segundo parámetro de entrada que

25

En algunos ejemplos, la interfaz para la instrucción de envío puede adoptar la forma siguiente:

especifica el contenido del mensaje a ser enviado al dispositivo anfitrión.

enviar\_datosoob (

bool bloqueante,

int datos)

30

35

donde enviar\_datosoob es el identificador de instrucción, bool bloqueante es un parámetro de entrada que especifica si la instrucción es una instrucción de envío bloqueante o una instrucción de envío no bloqueante, e int datos es un parámetro de entrada que especifica el contenido del mensaje a enviar. En el caso de una instrucción bloqueante, la instrucción puede devolver un parámetro indicativo de si se completó con éxito la operación de envío. En el caso de una instrucción no bloqueante, la instrucción puede devolver un parámetro de asidero para la posterior consulta de estado por el proceso de llamada.

40

Las instrucciones de paso de mensajes de dispositivo pueden, en algunos ejemplos, incluir una instrucción de recepción que instruye a un dispositivo informático para recibir datos desde el dispositivo anfitrión 12. Por ejemplo, la instrucción de recepción puede instruir a la GPU 14, por ejemplo, a la interfaz de paso de mensajes de dispositivo 30, para proporcionar a la tarea 28 que se está ejecutando en la GPU 14 un mensaje enviado a la tarea 28 desde el proceso anfitrión 20 que se está ejecutando en el dispositivo anfitrión 12, si está disponible. Una instrucción de este tipo puede utilizarse para prestar soporte a un mecanismo de sondeo.

45

50

55

La instrucción de recepción puede ser o una instrucción de recepción bloqueante o una instrucción de recepción no bloqueante. La instrucción de recepción puede incluir, en algunos ejemplos, un parámetro de entrada que especifica si la instrucción de recepción es una instrucción de recepción bloqueante o una instrucción de recepción no bloqueante. Una instrucción de recepción bloqueante puede detener el proceso de llamada, por ejemplo, la tarea 28 que se está ejecutando en la GPU 14, y esperar hasta que un mensaje esté disponible antes de volver al proceso de llamada. Una instrucción de recepción no bloqueante puede volver al proceso de llamada sin esperar hasta que un mensaje esté disponible. Por ejemplo, si un mensaje está disponible, la instrucción de recepción no bloqueante puede devolver el mensaje. Sin embargo, si un mensaje no está disponible, la instrucción de recepción no bloqueante puede fallar. En caso de fallo, el proceso de llamada puede tener que emitir de nuevo la instrucción de recepción para volver a intentar la operación de recepción. La instrucción puede incluir recibir un parámetro de salida que especifica los datos obtenidos, si los hubiera, como resultado de la operación de recepción.

En algunos ejemplos, la interfaz para la instrucción de recepción puede adoptar la forma siguiente:

60 recibir\_datosoob ( bool bloqueante, int datos)

65

donde recibir\_datosoob es el identificador de instrucción, bool bloqueante es un parámetro de entrada que especifica si la instrucción es una instrucción de recepción bloqueante o una instrucción de recepción no bloqueante, e int datos es un parámetro de salida que especifica los datos obtenidos, si los hubiera, como resultado de la operación

de recepción. La instrucción puede devolver un parámetro indicativo de si se completó con éxito la operación de recepción.

La interfaz de cola de comandos 24 está configurada para poner los comandos en la cola de comandos 32. Por ejemplo, la interfaz de cola de comandos 24 puede recibir una o más instrucciones de puesta en cola desde el proceso anfitrión 20, y colocar uno o más comandos en la cola de comandos 32 en respuesta a la recepción de una o más instrucciones de puesta en cola del proceso anfitrión 20. Las una o más instrucciones de puesta en cola pueden incluir instrucciones de puesta en cola de ejecuciones de tareas e instrucciones de puesta en cola de transferencias de datos que instruyen a la interfaz de cola de comandos 24 para poner en cola, respectivamente, los comandos de ejecución de tareas y los comandos de transferencia de datos.

La interfaz de cola de comandos 24 también está configurada para ejecutar los comandos almacenados en la cola de comandos 32. Para los comandos de transferencia de datos, la interfaz de cola de comandos 24 puede transferir datos entre el espacio de memoria del anfitrión y el espacio de memoria del dispositivo. Por ejemplo, para un comando de memoria intermedia de escritura, la interfaz de cola de comandos 24 puede transferir los datos almacenados en una parte del espacio de memoria del anfitrión a un objeto de memoria intermedia asignado en el espacio de memoria del dispositivo. Como otro ejemplo, para un comando de memoria intermedia de lectura, la interfaz de cola de comandos 24 puede transferir los datos almacenados en un objeto de memoria intermedia asignado en el espacio de memoria del dispositivo a una parte del espacio de memoria del anfitrión. El espacio de memoria del dispositivo puede corresponder a un dispositivo al cual está asociada la cola de comandos 32.

Para los comandos de ejecución de tareas, la interfaz de cola de comandos 24 puede provocar el inicio de la ejecución de la tarea en un dispositivo asociado con una cola de comandos. Por ejemplo, en el ejemplo de la FIG. 1, la cola de comandos 32 está asociada con la GPU 14 dentro del contexto de módulo de tiempo de ejecución 22. Por lo tanto, cuando se está ejecutando un comando de ejecución de tareas, la interfaz de cola de comandos 24 puede hacer que una tarea empiece a ejecutarse en la GPU 14. En algunos ejemplos, la interfaz de cola de comandos 24 puede hacer que la tarea empiece a ejecutarse en la GPU 14 mediante la colocación de uno o más comandos en una cola de comandos local contenida dentro de la GPU 14. En otros ejemplos, la interfaz de cola de comandos 24 puede hacer que la tarea empiece a ejecutarse en la GPU 14 mediante el envío de una o más instrucciones a la GPU 14, instruyendo a la GPU 14 para comenzar la ejecución de la tarea. La interfaz de cola de comandos 24 puede utilizar la red de interconexión 18 para comunicarse con la GPU 14, la memoria 16 y los espacios de memoria del anfitrión y del dispositivo.

En algunos ejemplos, la interfaz de cola de comandos 24 puede ejecutar los comandos en orden. En dichos ejemplos, si un primer comando se pone en cola antes de un segundo comando, la ejecución del segundo comando comienza después de que el primer comando haya finalizado su ejecución. En ejemplos adicionales, la interfaz de cola de comandos 24 puede ejecutar los comandos de forma desordenada. En dichos ejemplos, si un primer comando se pone en cola antes de un segundo comando, la ejecución del segundo comando no necesariamente empieza después de que el primer comando haya finalizado su ejecución.

La interfaz de paso de mensajes del anfitrión 26 está configurada para ejecutar una o más instrucciones de paso de mensajes recibidas desde el proceso anfitrión 20. Por ejemplo, en respuesta a la recepción de una o más instrucciones de paso de mensajes desde el proceso anfitrión 20, la interfaz de paso de mensajes del anfitrión 26 puede pasar uno o más mensajes entre el proceso anfitrión 20 que se están ejecutando en el dispositivo anfitrión 12 y la tarea 28 que se está ejecutando en la GPU 14 mientras la tarea 28 se está ejecutando en la GPU 14. En algunos ejemplos, la interfaz de paso de mensajes del anfitrión 26 puede ejecutar una o más instrucciones de paso de mensajes sin colocar ningún comando en cola de comandos 32.

De acuerdo con un primer ejemplo, en respuesta a la recepción de una instrucción de envío desde el proceso anfitrión 20, la interfaz de paso de mensajes del anfitrión 26 puede enviar un mensaje desde el proceso anfitrión 20 a la tarea 28 mientras la tarea 28 se está ejecutando en la GPU 14. Por ejemplo, la interfaz de paso de mensajes del anfitrión 26 puede componer un mensaje saliente en base a los datos de mensajes contenidos dentro de la instrucción de envío, y transferir el mensaje saliente, a través de la red de interconexión 18, a un dispositivo especificado en la instrucción de envío, por ejemplo, la GPU 14, para su entrega a una tarea que se está ejecutando en el dispositivo especificado, por ejemplo, la tarea 28.

De acuerdo con un segundo ejemplo, en respuesta a la recepción de una instrucción de registro de rutina de devolución de llamada del proceso anfitrión 20, la interfaz de paso de mensajes del anfitrión 26 puede asociar la rutina de devolución de llamada especificada en la instrucción con una señal desde el dispositivo especificado en la instrucción, por ejemplo, la GPU 14, lo cual indica que la tarea, por ejemplo, la tarea 28, que se está ejecutando en el dispositivo especificado ha enviado un mensaje. En algunos ejemplos, la señal desde el dispositivo puede ser una señal de interrupción. La señal de interrupción, en algunos ejemplos, puede administrarse mediante una línea de señal de interrupción dedicada. En respuesta a la recepción de la señal desde el dispositivo especificado que indica que la tarea que se está ejecutando en el dispositivo ha enviado un mensaje, la interfaz de paso de mensajes del anfitrión 26 puede iniciar la ejecución de la rutina de devolución de llamada especificada en la instrucción de registro de rutina de devolución de llamada. La rutina de devolución de llamada puede obtener el mensaje enviado por la

tarea, por ejemplo, la tarea 28, desde el dispositivo especificado, por ejemplo, la GPU 14, y devolver el mensaje al proceso anfitrión 20 para su posterior procesamiento.

De acuerdo con un tercer ejemplo, en respuesta a la recepción de una instrucción de sondeo, la interfaz de paso de mensajes del anfitrión 26 puede sondear el dispositivo especificado en la instrucción, por ejemplo, la GPU 14, para obtener información sobre el estado del mensaje. La interfaz de paso de mensajes del anfitrión 26 puede utilizar la red de interconexión 18 u otra vía de comunicación basada en hardware para sondear el dispositivo. Si la información de estado de mensaje indica que una tarea, por ejemplo, la tarea 28, que se está ejecutando en el dispositivo especificado, por ejemplo, la GPU 14, ha enviado el mensaje, la interfaz de paso de mensajes del anfitrión 26 puede obtener el mensaje desde el dispositivo especificado y devolver el mensaje al proceso anfitrión 20 para su posterior procesamiento.

5

10

15

20

25

30

35

60

La interfaz de paso de mensajes de dispositivo 30 está configurada para ejecutar una o más instrucciones de paso de mensajes de dispositivo recibidas desde la tarea 28. Por ejemplo, en respuesta a la recepción de una o más instrucciones de paso de mensajes de dispositivo desde la tarea 28, la interfaz de paso de mensajes de dispositivo 30 puede pasar uno o más mensajes entre la tarea 28 que se está ejecutando en la GPU 14 y el proceso anfitrión 20 que se está ejecutando en el dispositivo anfitrión 12 mientras la tarea 28 se está ejecutando en la GPU 14.

De acuerdo con un primer ejemplo, en respuesta a la recepción de una instrucción de envío, la interfaz de paso de mensajes de dispositivo 30 puede enviar un mensaje desde la tarea 28 que se está ejecutando en la GPU 14 al proceso anfitrión 20 que se está ejecutando en el dispositivo anfitrión 12. Por ejemplo, la interfaz de paso de mensajes de dispositivo 30 puede componer un mensaje saliente sobre la base de datos de mensajes contenidos dentro de la instrucción de envío, y transferir el mensaje saliente, a través de la red de interconexión 18, al dispositivo anfitrión 12 para su entrega al proceso anfitrión 20.