# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 624 798

51 Int. Cl.:

H04B 10/114 (2013.01) H04B 10/116 (2013.01) H04L 25/49 (2006.01) H05B 37/02 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 14.07.2008 PCT/IB2008/052819

(87) Fecha y número de publicación internacional: 22.01.2009 WO09010916

96 Fecha de presentación y número de la solicitud europea: 14.07.2008 E 08789294 (9)

97 Fecha y número de publicación de la concesión europea: 22.02.2017 EP 2172083

54) Título: Manejo de una fuente de luz

(30) Prioridad:

16.07.2007 EP 07112524

Fecha de publicación y mención en BOPI de la traducción de la patente: 17.07.2017

(73) Titular/es:

PHILIPS LIGHTING HOLDING B.V. (100.0%) HIGH TECH CAMPUS 5 5656 AE EINDHOVEN, NL

(72) Inventor/es:

BAGGEN, CONSTANT, P., M., J.; HEKSTRA, ANDRIES, P. y LINNARTZ, JOHAN, P., M., G.

(74) Agente/Representante:

**ISERN JARA, Jorge**

### **DESCRIPCIÓN**

Manejo de una fuente de luz

#### 5 CAMPO DE LA INVENCIÓN

10

50

55

60

La presente invención se relaciona en general con métodos y dispositivos para manejar fuentes de luz, más particularmente LED. En una realización particular, la invención se relaciona con un método para manejar una pluralidad de LED de tal manera que un detector que reciba luz de dicha pluralidad de LED puede reconocer la contribución de cada LED individual.

#### ANTECEDENTES DE LA INVENCIÓN

Un reciente desarrollo en el campo de iluminación se relaciona con el control de color y el control de brillo de fuentes de luz. Aunque esta tecnología puede en principio ser aplicada a varios tipos de fuentes de luz, los LED son utilizados mayormente para este propósito. Ya que el control del color y el control del brillo de los LED es conocido per se, solo será suficiente aquí una breve explicación.

Los LED se han desarrollado para generar luz de color única. Con una fuente de luz que comprende tres LED de colores mutuamente diferentes, es posible generar una mezcla de luz que tiene un punto de color en un espacio de color dentro de un triángulo el cual los puntos de las esquinas se definen mediante los colores LED individuales. La ubicación de este punto de color puede variar al variar las intensidades promedio relativas de las contribuciones de luz individuales. El brillo puede variar al variar las intensidades de las contribuciones de luz individuales en la misma proporción, manteniendo unas intensidades relativas promedio constantes. Se hace notar que una fuente de luz puede realmente comprender múltiples LED de uno y el mismo color con el fin de incrementar la salida de luz para ese color. Una fuente de luz de este tipo comprende en general un manejador que tiene una entrada para recibir una señal de control, que indica el color y el brillo requeridos y, y que tiene salidas para manejar los LED individuales. Sobre la base de la señal de control recibida, tal manejador determina como manejar las fuentes de luz individuales.

Básicamente, el control del color y el control del brillo de una fuente de luz se basan en el control de intensidad de los LED constituyentes. Por lo tanto, en lo que sigue la presente invención será específicamente explicada para el control de intensidad de los LED manteniendo en mente que la presente invención es más generalmente aplicable al control de intensidad de las fuentes de luz.

35 Explicado de manera breve, un LED es manejado al hacer que la corriente eléctrica fluya a través del LED. Es posible utilizar una fuente de voltaje, pero, en vista del hecho de que la salida de luz es proporcional a la corriente, es más adecuado utilizar una fuente de corriente. La manera más directa para variar la salida de luz sería variar el nivel de corriente. Cambiar el nivel de corriente, sin embargo, no es adecuado, solo por razón de que el color de salida puede depender del nivel de corriente. Por lo tanto, es práctica común aplicar un control de ciclo de trabajo. 40 En tal caso, el LED es PRENDIDO y APAGADO a una cierta frecuencia de conmutación. En el estado APAGADO, la corriente de LED cero o casi cero, y el LED no produce luz o al menos no produce sustancialmente luz. En el estado PRENDIDO, la corriente del LED mantiene sustancialmente constante, así la salida de luz se mantiene sustancialmente constante. El periodo de repetición del patrón PRENDIDO/APAGADO se indica como periodo de corriente. La proporción de la duración de PRENDIDO y el periodo de corriente se indica como el ciclo de trabajo. El 45 ciclo de trabajo determina la corriente promedio de la lámpara y de esta manera la salida promedio de luz. La frecuencia de conmutación es un parámetro de diseño, el cual no debe ser seleccionado demasiado bajo con el fin de evitar un parpadeo visible, y que también no se debe seleccionar demasiado alto con el fin de evitar demasiadas pérdidas por conmutación, mientras que además la frecuencia de conmutación debe estar dentro del ancho de banda de la combinación manejador/LED. Se debe notar que manteniendo la corriente de la lámpara a un nivel fijo,

la salida de luz promedio está a un máximo cuando el ciclo de trabajo es igual a 1 (es decir, 100%)

En un desarrollo más reciente, un sistema de iluminación comprende una pluralidad de LED distribuido sobre un espacio, tal como una habitación. Es posible que todos los LED se manejen de la misma manera, de tal manera que las condiciones de color y brillo sean las mismas en toda la habitación. Sin embargo, sería deseable poder establecer independientemente las condiciones de color y brillo en diferentes secciones de la habitación. Un sistema de control para tal sistema de iluminación puede comprender un sensor de luz, que se puede ubicar en una cierta ubicación, generando una señal que representa las condiciones de color y brillo locales, y un controlador central puede corregir las señales de control para los LED del sistema de iluminación de tal manera que se cumplan las condiciones locales requeridas de color y brillo en la ubicación del sensor. Para tal operación, el sistema de control requiere saber cuáles LED contribuyen a la iluminación en esa ubicación, y en qué proporción. Con el fin de posibilitar la determinación de la identidad de los LED que contribuyen a la iluminación en el sitio del sensor, sería deseable que la salida de luz de un LD específico contenga un código que identifique ese LED específico.

Incorporar tal código en la salida de luz se puede hacer mediante la modulación de la amplitud de la corriente LED del estado PRENDIDO, pero, como se mencionó anteriormente, se prefiere que la corriente de LED en el estado PRENDIDO se mantenga constante.

Otro método para incorporar tal código en la salida de luz es conmutar el encendido o el PRENDIDO y APAGADO de los LED en un cierto patrón, el patrón define una serie de "0" y "1" de un código binario. Ahora, el problema surge sobre como la conmutación del ciclo de trabajo puede ser adecuadamente combinada con la conmutación codificada, especialmente de tal manera que el código no interfiera con la función de iluminación.

El documento WO02/13490 divulga sistemas de configuración automática y métodos para iluminar y otras aplicaciones en donde el componente de iluminación se puede utilizar tanto para iluminación como para comunicación. El documento WO02/13490 divulga que los LED se pueden modular a través de un número de técnicas, una de las cuales es la modulación de ancho de pulso (PWM), una técnica que puede suministrar, a través de pulsos de ancho variable, una manera de controlar la intensidad de los LED como las ve el ojo. Una técnica alternativa para modular los LED divulgados involucra variar las técnicas de amplitud de pulso. Existen muchos métodos para controlar los LED.

En un sistema de iluminación como se describió anteriormente WO02/13490 es decir, que comprende una pluralidad de LED distribuidos en un espacio, es posible que el espaciamiento entre los LED sea tal que un sensor recibiría solamente luz de un LED a la vez. Sin embargo, es posible también y en casos con iluminación sustancialmente homogénea que sea muy probable, que un sensor único (foto detector) recibiría luz de dos o más LED simultáneamente. En el caso de la conmutación codificada, el sensor recibiría dos o más señales codificadas al mismo tiempo, que interferirían la una con la otra. Así, surge el problema de efectuar la conmutación codificada de tal manera que las señales individuales de los LED individuales puedan ser distinguidas de manera confiable.

De otro lado, la presente invención no necesariamente se relaciona con una pluralidad de los LED. Aún en un sistema de iluminación que comprende solo un LED único, puede ser deseable combinar el control de ciclo de trabajo para las variaciones de color y/o brillo con conmutación codificada para comunicación de datos. Aparte de transmitir un código de identificación, es deseable utilizar la iluminación en una habitación para la comunicación de datos a uno (o más) usuarios en la habitación. Por ejemplo, los datos comunicados de esta manera pueden contener información de audio y/o video. Para tales aplicaciones, sería deseable una velocidad de datos muy alta.

### 30 RESUMEN DE LA INVENCIÓN

5

10

25

35

50

55

Se debe notar que la conmutación del ciclo de trabajo de los LED con el fin de variar la salida de la luz es conocida per se, pero sin emitir datos. Se debe además notar que la conmutación codificada de los LED con el fin de emitir datos es conocida per se, pero sin las variaciones del ciclo de trabajo para variar la intensidad de luz.

Un objetivo de la presente invención es suministrar un método para manejar un LED de tal manera que la conmutación del ciclo de trabajo pueda ser adecuadamente combinada con la conmutación codificada sin que el uno afecte el otro.

- 40 Un objetivo adicional de la presente invención es suministrar un método para manejar un LED con una combinación de conmutación codificada y control de ciclo de trabajo de tal manera que el espectro de señal contenga solo una contribución pequeña de señales de baja frecuencia, no considerando el componente de CD, con el fin de evitar parpadeo visible.

- 45 Un objetivo adicional de la presente invención es suministrar un método para manejar un LED con una combinación de conmutación codificada y control de ciclo de trabajo de tal manera que se logre una alta velocidad de datos.

Un objetivo adicional de la presente invención es suministrar un método para manejar un LED con una combinación de conmutación codificada y control de ciclo de trabajo de tal manera que en el caso de los múltiples LED, se puedan distinguir fácilmente las señales individuales de los LED individuales.

Elaboraciones ventajosas adicionales se mencionan en las reivindicaciones dependientes.

# BREVE DESCRIPCIÓN DE LOS DIBUJOS

Estos y otros aspectos, características y ventajas de la presente invención se explicarán adicionalmente mediante la siguiente descripción de una o más de las realizaciones preferidas con referencia a los dibujos, en los cuales los mismos numerales de referencia indican las mismas partes o similares, y en las cuales:

- 60 La Figura 1 es un diagrama de bloque que ilustra esquemáticamente un sistema de iluminación;

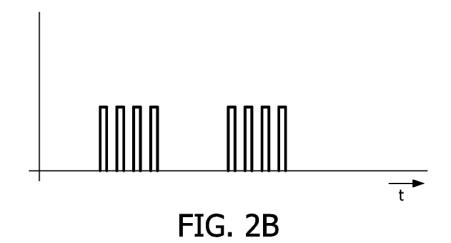

- La Figura 2B es un diagrama de tiempo esquemático que muestra una señal de datos pulsante para comunicar un código;

- 65 La Figura 2C es un diagrama de tiempo esquemático que ilustra una modulación bifase;

### ES 2 624 798 T3

- La Figura 3A es un diagrama esquemático de tiempo que ilustra una realización de una señal de manejo de acuerdo con la presente invención;

- La Figura 3B es un diagrama esquemático de tiempo que ilustra una realización de una señal de manejo de acuerdo a la presente invención;

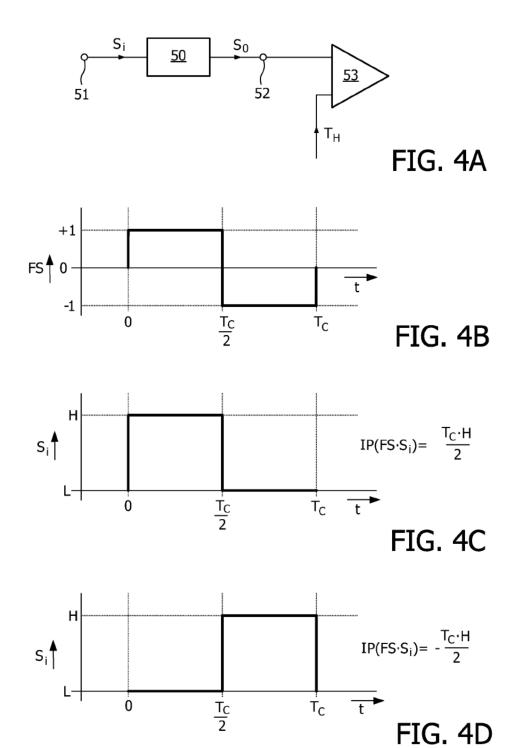

- La Figura 4A es un diagrama de bloque para ilustrar un filtro de case;

- La Figura 4B es un diagrama esquemático de tiempo que ilustra una forma de onda preprogramada de ejemplo (forma de filtro) del filtro que casa;

- La Figura 4C es un diagrama esquemático de tiempo de una señal de ejemplo a ser analizada por el filtro que casa de la Figura 4A, para ilustrar la operación del filtro que casa;

- La Figura 4D es un diagrama esquemático de tiempo de una señal de ejemplo a ser analizada por el filtro que casa de la Figura 4A, para ilustrar la operación del filtro que casa:

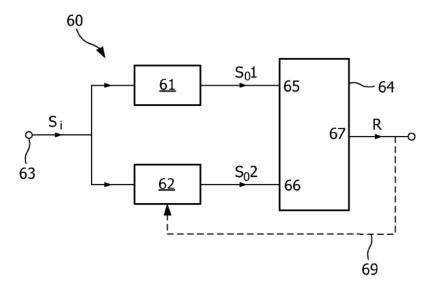

- La Figura 5A es un diagrama de bloque que ilustra esquemáticamente un circuito decodificante de señal;

- La Figura 5B es un diagrama esquemático de tiempo comparable con la Figura 4B, que ilustra una forma de onda preprogramada de ejemplo (forma de filtro) de un filtro que casa del circuito decodificante de señal;

- Las Figuras 5C-D son gráficas para ilustrar la operación del circuito de señal decodificante de la Figura 5A;

- La Figura 6A es un diagrama esquemático de tiempo que ilustra una realización de la señal de manejo de acuerdo con la presente invención;

- La Figura 6B es un diagrama esquemático de tiempo que ilustra una realización de la señal de manejo de acuerdo con la presente invención;

- La Figura 7 es una gráfica que muestra la velocidad de datos como una función del ciclo de trabajo;

- La Figura 8 es un diagrama de bloque que ilustra un maneiador de LED de la presente invención:

- La Figura 9 es un diagrama esquemático de tiempo que ilustra una forma de banda preprogramada de ejemplo (forma de filtro) de un filtro que casa;

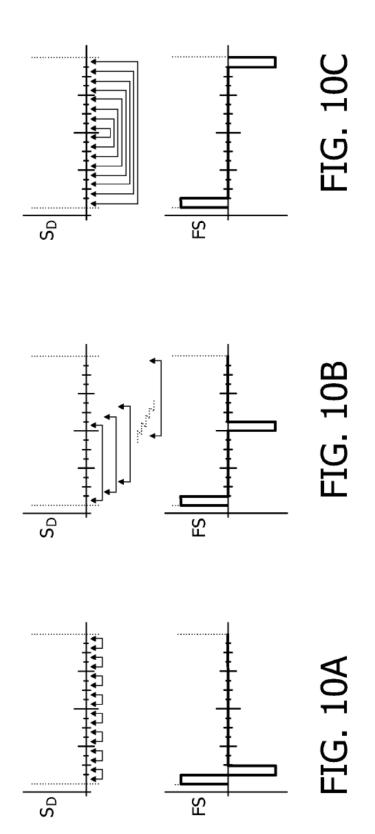

- Las Figuras 10A-C ilustran esquemáticamente diferentes métodos para segmentos de celda pareados;

- 40 La Figura 11A es un diagrama de bloque que ilustra esquemáticamente una realización de un dispositivo para recibir y decodificar luz;

- La Figura 11B es un diagrama esquemático de tiempo que ilustra una forma de banda preprogramada de ejemplo (forma de filtro) de un filtro que casa;

- La Figura 12A es un diagrama esquemático de tiempo que ilustra una realización de una señal de acuerdo con la presente invención;

- La Figura 12B es un diagrama esquemático de tiempo que ilustra una forma de onda preprogramada de ejemplo (forma de filtro) de un filtro que casa adecuado para la combinación con la señal de manejo de f;

- La Figura 13A es un diagrama esquemático de tiempo que ilustra una realización de la señal de manejo de acuerdo con la presente invención;

- La Figura 13B es un diagrama esquemático de tiempo que ilustra una forma de onda preprogramada de ejemplo (forma de filtro) de un filtro que casa adecuado para la combinación con la señal de manejo de la Figura 13A;

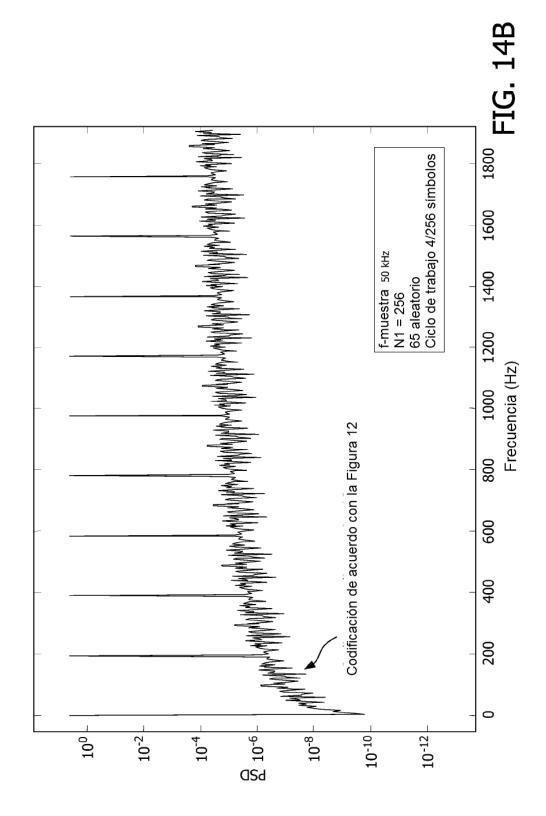

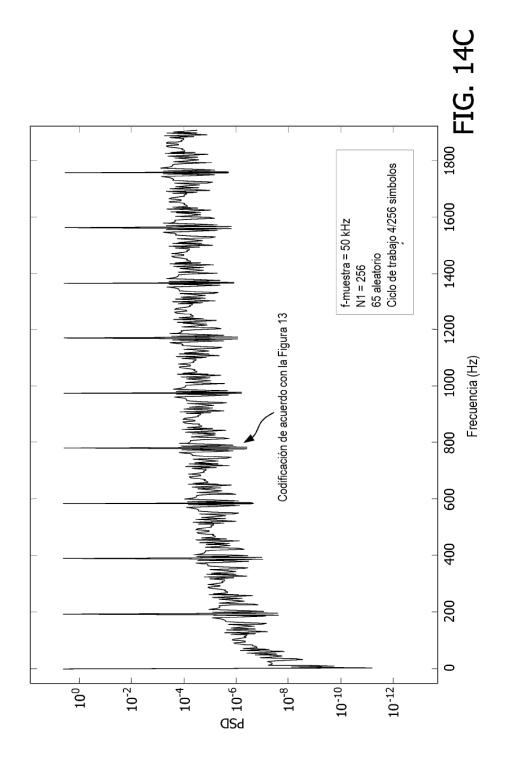

- Las Figuras 14A-C son gráficas que ilustran el contenido espectral de diferentes señales de manejo;

- 60 La Figura 15A es un diagrama esquemático de tiempo que ilustra una realización de una señal de manejo de acuerdo con la presente invención;

- La Figura 15B es un diagrama esquemático de tiempo que ilustra una forma de onda preprogramada de ejemplo (forma de filtro) de un filtro que casa adecuado para la combinación con la señal de manejo de la Figura 15A;

65

30

## ES 2 624 798 T3

La Figura 15C es un diagrama esquemático de tiempo que ilustra una forma de onda preprogramada de ejemplo (forma de filtro) de un filtro que casa adecuado para la combinación con la señal de impulsión de la Figura 15A;

La Figura 15D es un diagrama esquemático de tiempo que ilustra una realización de una señal de manejo de acuerdo con la presente invención;

La Figura 16A es un diagrama esquemático de tiempo que ilustra las formas de onda preprogramadas de ejemplo (formas de filtro) de los filtros que casan;

10 La Figura 16B es un diagrama esquemático de bloque de un circuito de determinación;

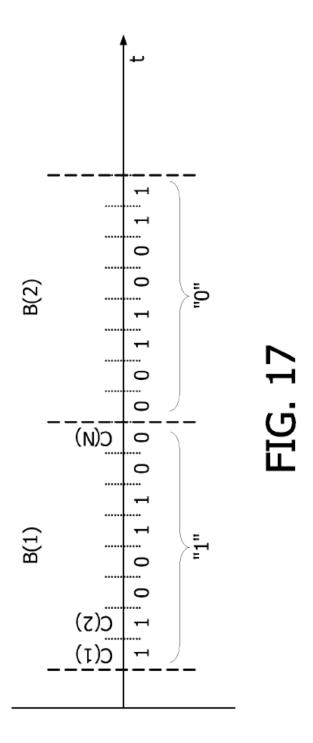

La Figura 17 es un diagrama esquemático de tiempo que ilustra las celdas de tiempo agrupadas para definir un bloque de tiempo;

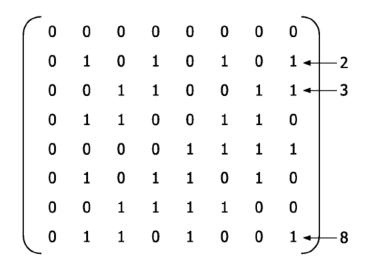

15 La Figura 18A muestra una matriz Hadamard de orden 8;

La Figura 18B muestra una matriz de contraseña derivada de la matriz Hadamard de la Figura 18A;

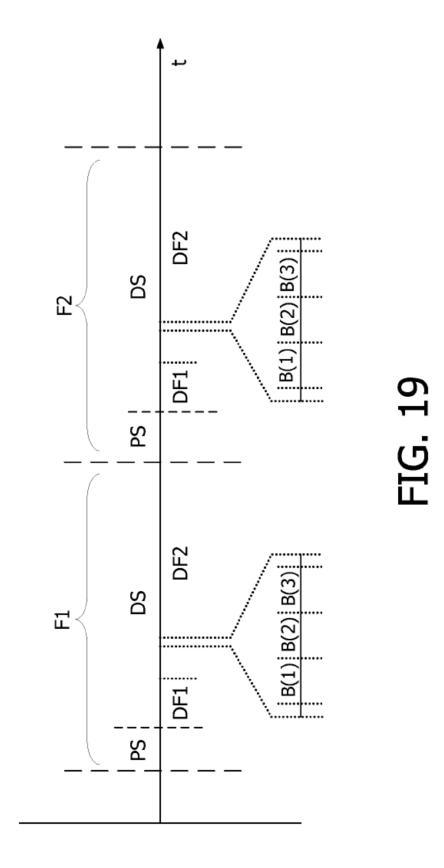

La Figura 19 es un diagrama esquemático de tiempo que ilustra los marcos de tiempo con un preámbulo y una pluralidad de bloques de tiempo.

### DESCRIPCIÓN DETALLADA DE LA INVENCIÓN

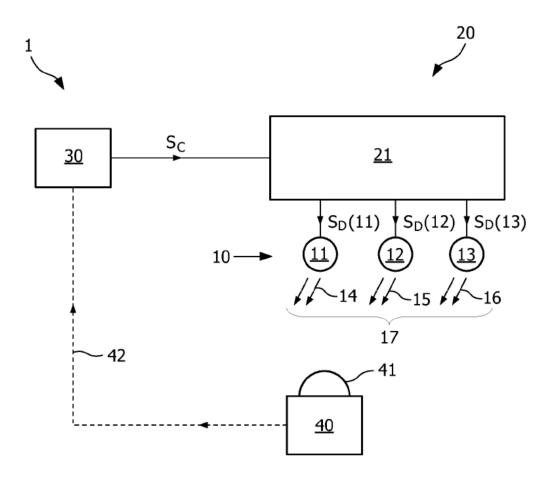

- La Figura 1 es un diagrama de bloque que ilustra esquemáticamente un sistema 1 de iluminación que muestra una realización de la presente invención por vía de ejemplo. El sistema 1 de iluminación comprende al menos una unidad 20 de iluminación. Se debe notar que el sistema 1 de iluminación puede comprender una pluralidad de unidades 20 de iluminación, pero la figura solo muestra una unidad 20 de iluminación.

- La unidad 20 de iluminación comprende una fuente 10 de luz. Se debe notar que la unidad 20 de iluminación puede comprender una pluralidad de fuentes de luz, pero la figura solo muestra una fuente 10 de luz. En este ejemplo, la fuente 10 de luz comprende tres LED, 11, 12, 13, para generar luz 14, 15, 16, respectivamente, de colores mutuamente diferentes, por ejemplo rojo, verde, azul, de tal manera que la salida 17 combinada de la luz de esta fuente 10 de luz puede tener un punto de color variable. Se debe notar que, para incrementar la salida de luz, la fuente 10 de luz puede comprender una pluralidad de LED que tienen mutuamente el mismo color. Se debe notar adicionalmente que la fuente 10 de luz puede comprender solo un LED único, si el LED único es capaz de variación de color en sí mismo o si no se requiere la variación de color, o la fuente 10 de luz puede comprender más de tres LED de colores mutuamente diferentes.

- La unidad 20 de iluminación comprende además un manejador 21 de fuente que genera señales de manejo adecuadas S<sub>D</sub>(11), S<sub>D</sub>(12), S<sub>D</sub>(13), para la fuente 10 de luz de tal manera que se logra la salida de luz requerida. Los requisitos de la salida de luz incluyen color y brillo. Las señales S<sub>C</sub> de comando para comunicar el color y brillos requeridos al manejador 21 de la fuente se generan mediante un controlador 30 central, que también genera tales señales de control para otras unidades de iluminación si están presentes. Se debe notar que, en el caso del sistema 1 de iluminación este solo comprende una unidad 20 de iluminación, el manejador 21 de fuente y el controlador 30 central pueden estar integrados.

- La figura muestra además un dispositivo 40 de recepción que comprende un sensor 41 de luz. En una realización particular, el dispositivo 40 de recepción se puede diseñar para comunicar al controlador 30 central información con relación a la luz recibida, o a través de un enlace alambrado o inalámbrico, como se indica mediante el numeral 42 de referencia, tal como para suministrar un ciclo de retroalimentación para el controlador 30 central de tal manera que este puede adaptar sus señales de control. Esto aplica particularmente en relación con el control del color y el brillo.

- Como se explicará con más detalle posteriormente, la salida 17 de luz de la fuente 10 de luz contiene datos codificados. Estos datos codificados pueden identificar fuentes 10 de luz individuales en un sistema 1 de iluminación multifuente, o pueden identificar los LED 11, 12, 13, individuales de tal manera que el controlador 30 central pueda detectar que LED contribuye a la luz recibida mediante el dispositivo 40 de recepción y este puede adaptar adecuadamente su señal S<sub>C</sub> de comando para esa fuente 10 de luz especifica.

- También es posible que los datos codificados contengan información de audio y/o video, y que el dispositivo 40 de recepción sea un reproductor de audio y/o video (en cuyo caso el enlace 42 de retroalimentación puede estar ausente)

- Ya que los LED, manejadores para los LED, controladores para controlar los manejadores, y sensores de luz para recibir la luz son conocidos per se, se omite una descripción general detallada del diseño y funcionamiento de los mismos.

En lo anterior, el control de la fuente 10 de luz se ha descrito con vista a un control de color. Una fuente de luz que comprende dos o más LED monocolor, el control de color involucra realmente el control de intensidad de los LED individuales. La idea básica de la presente invención no está restringida al control de color en un sistema multicolor, sino que también es aplicable al control del brillo en un sistema de color único, aun en un sistema LED único. Por lo tanto, en lo que sigue el enfoque de la explicación se concentrará en el tema del manejo de un LED único.

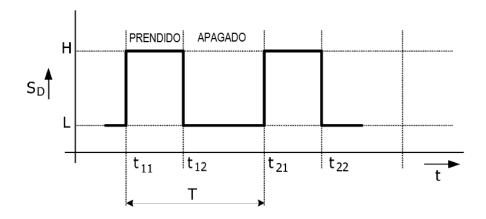

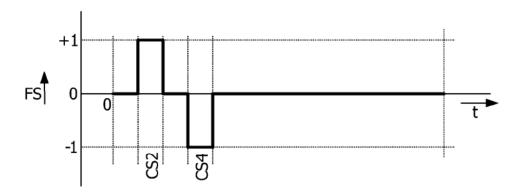

La Figura 2A es un diagrama de tiempo de una señal  $S_D$  de manejo para un LED. El eje horizontal representa el tiempo, el eje vertical representa el valor de la señal  $S_D$  de manejo. Se puede ver que las señales  $S_D$  de manejo solo puede tomar dos valores, que se indican L (bajo) y H (alto). Cuando quiera que la señal  $S_D$  de manejo sea baja, la corriente del LED es sustancialmente cero y el LED está sustancialmente APAGADO. Cuando quiera que la señal  $S_D$  de manejo es alta, la corriente del LED tiene un valor constante predeterminado y el LED esta PRENDIDO. Así, la forma de la curva que representa la señal  $S_D$  de manejo también representa la corriente LED y la salida de la luz como una función del tiempo.

Normalmente, la señal  $S_D$  de manejo es una señal periódica que tiene un periodo T de  $t_{11}$  a  $t_{21}$ . En el ejemplo de la Figura 2A, la señal  $S_D$  de manejo va ALTO en el tiempo  $t_{11}$  y va BAJO en el tiempo  $t_{12}$ , lo que define una duración de  $t_{prendido} = t_{12}$ - $t_{11}$  y una duración de APAGADO  $T_{apagado} = t_{21}$ - $t_{12}$ . Un ciclo de trabajo  $\Delta$  se define como la proporción de la duración de PRENDIDO  $t_{prendido}$  en relación con el periodo T de señal de acuerdo  $\Delta$  =  $t_{prendido}$  /T. Calculada en escala de tiempo mucho mayor que el periodo T, una corriente de lámpara promedio y una salida de luz promedio son proporcionales al sitio de trabajo  $\Delta$ . Así, el control de brillo de un LED se puede efectuar al variar el ciclo de trabajo  $\Delta$ , es decir, el tiempo  $t_{12}$ , asumiendo que el periodo T de la señal se mantenga constante. Sin importar el brillo, la corriente (si fluye) siempre tendrá el mismo valor, que se puede ajustar de tal manera que la eficiencia y/o el color del LED sea óptimo.

Se debe notar que la sucesión rápida de la conmutación APAGADO/PRENDIDO del LED puede resultar en un parpadeo notable si la frecuencia de conmutación es demasiado baja. En la práctica, la frecuencia de conmutación se puede seleccionar en el rango de kHz o mayor para evitar este problema. De otro lado, el proceso de conmutación en sí mismo toma tiempo y consume energía, de tal manera que la frecuencia de conmutación puede no seleccionarse demasiada alta.

Con el propósito de comunicar un código, este es generalmente conocido per se para modular la luz. Por ejemplo, un controlador remoto infrarrojo emite luz que es modulada o rápidamente conmutada PRENDIDO/APAGADO, de tal manera que la salida de la luz como una función del tiempo muestre una rápida sucesión de pulsos de luz, como se ilustra en la Figura 2B. En estos pulsos, la información se puede codificar de varias maneras: por ejemplo, la modulación del ancho de pulso o la modulación de la distancia de pulso son posibilidades.

También se conoce per se modular la amplitud de la salida de la luz de una lámpara que está continuamente PRENDIDA, con el fin de poder detectar en cual posición se ubica un detector. Un esquema de detección simple incluiría una pluralidad de lámparas, cada una siendo modulada con una frecuencia física especifica. Así, la frecuencia desmodulada de una señal de salida del detector de luz correspondería a la frecuencia de modulación de la lámpara cuya luz es recibida y de esta manera indicaría la identidad de la lámpara emisora. Para información de distribución, sería posible que la modulación de la amplitud se efectué con una señal de audio, de tal manera que la señal desmodulada se pueda reproducir con un parlante, como en un sistema de radio. Típicamente, la intensidad de la luz promedio de tal lámpara permanezca constante a una mayor escala de tiempo que la frecuencia de modulación. Si se requiere control de brillo (atenuación), este se efectúa típicamente de manera análoga al cambio del nivel de corriente de la lámpara.

Se debe notar además que en el campo de comunicaciones de señales digitales, se conoce el uso de la modulación bifase para determinar la diferencia entre un lógico "1" y un lógico "0". Esto se ilustra esquemáticamente en la Figura 2C. Una señal S digital puede tomar dos valores de señal L y H. La señal S se subdivide en las celdas C1, C2, C3 de señal de igual duración, cada celda representa un bit de código. Cada celda se divide en dos segmentos de igual duración. Dentro de una celda, la señal S es ALTA en el primer segmento y BAJA en el segundo segmento, indicada como HL (ver celdas C1 y C2), o viceversa, indicada como LH (ver celda C3). Las dos posibilidades HL y LH definen un lógico "1" y un lógico "0", respectivamente.

Sin embargo, si esta técnica conocida se incorporara en un sistema de iluminación como se describió anteriormente, debe ser claro que el ciclo de trabajo de la salida de luz requeriría siempre ser igual a 50%.

Además, en esta técnica conocida, cada celda contiene un bit de datos, es decir, un "0" o un "1".

La presente invención está destinada a combinar la comunicación digital y el control de ciclo de trabajo en una señal, de tal manera que el ciclo de trabajo se puede controlar completamente de manera independiente de los datos digitales.

65

5

10

15

20

25

30

35

40

Además, la presente invención está destinada a suministrar un método para procesar una señal de luz recibida de tal manera que los datos digitales y el ciclo de trabajo se puedan determinar confiablemente e independientemente el uno del otro.

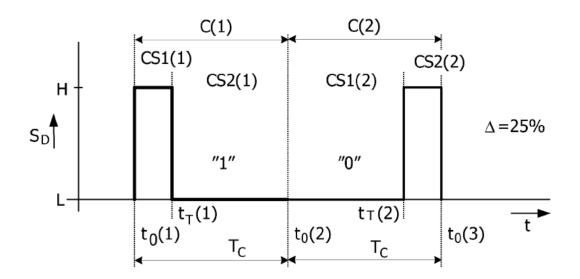

- La Figura 3A es una gráfica, comparable con la Figura 2C, de una señal S<sub>D</sub> de manejo propuesta mediante la presente invención. De nuevo, la señal se divide en celdas de tiempo, indicadas como C(1), C(2), etc., cada celda de tiempo representa un bit digital. Las celdas tienen duración T<sub>C</sub> mutuamente igual la cual se puede determinar mediante una señal de reloj (no mostrada por motivos de simplicidad). De nuevo, cada celda C(i) de tiempo se subdivide en dos segmentos CS1(i), CS2(i) de celda consecutiva. De nuevo, la señal S<sub>D</sub> puede tener dos valores H y L de señal solamente, y el valor de señal en el segundo segmento CS2(i) de celda siempre es el opuesto al valor de señal en el primer segmento CS1(i) de celda. El segmento de celda que tiene valor H se indicará como el segmento H mientras que el otro segmento se indicará como segmento L. Así, el primer segmento CS1(i) de celda es H mientras que el segundo segmento SC2(i) de celda es L, lo que aplica a la primera celda C(1) en la Figura 3A, o el segundo segmento CS2(i) de celda es H mientras que el primer segmento CS1(i) de celda es L, lo que aplica a la segunda celda C(2) en la Figura 3A. El valor de la primera celda C(1) se indicara como HL, mientras que el valor de la segunda celda C(2) se indicará como LH. Estos dos diferentes valores definen un digital 0 y un digital 1, respectivamente, siendo irrelevante si HL indica a 0 y LH indica a 1 o al contrario.

- En la Figura 3A, la primera celda C(1) inicia en  $t_0(1)$  y la segunda celda C(2) inicia en  $t_0(2)$ , de tal manera que la duración  $T_C$  de la celda es igual a  $t_0(2)$ - $t_0(1)$ . El tiempo de transición entre dos segmentos CS1(i), CS2(i) de celda consecutivos se indica como  $t_T(i)$ . En cada celda C(i), la duración t1(i) del primer segmento CS1(i) de celda es igual a  $t_T(i)$ - $t_T(i)$  mientras que la duración t2(i) del segundo segmento CS2(i) de celda es igual a  $t_0(i)$ - $t_T(i)$ . En cada celda C(i), un ciclo de trabajo  $\Delta(i)$  se define como la proporción de la duración del segmento H a la duración  $T_C$  de la celda. Así, en el caso de la primera celda C(1) el ciclo de trabajo  $\Delta(1)$  =  $t_T(1)/T_C$  aplica, mientras que en el caso de la segunda celda C(2) el ciclo de trabajo  $\Delta(2)$  =  $t_T(2)/T_C$  aplica).

Así, la señal contiene datos así como también información del ciclo de trabajo

55

60

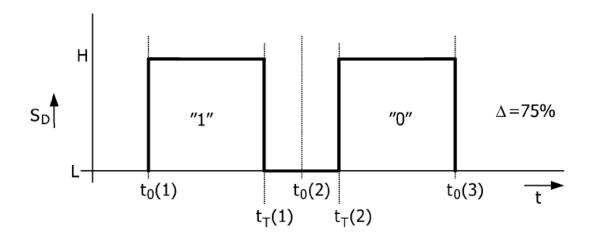

- En la Figura 3A, el ciclo de trabajo de la señal es menor de 50%, a saber, aproximadamente igual a 25%. La Figura 3B es comparable a la Figura 3A, pero ahora el ciclo de trabajo de la señal es mayor del 50%, a saber, aproximadamente igual al 75%. De nuevo, los bits digitales "0" y "1" están claramente definidos mediante el valor HL y LH de la celda, respectivamente.

- De la explicación anterior, debe ser claro que el ciclo de trabajo de la señal (y así la intensidad promedio de la luz emitida) pueden variar durante un gran rango sin afectar el contenido de datos, mientras que al contrario el contenido de datos se puede seleccionar libremente sin afectar el ciclo de trabajo (y la intensidad promedio). En otras palabras, el contenido de datos y el ciclo de trabajo (o la intensidad promedio) son independientes el uno del otro.

- 40 Se debe notar que, en la anterior explicación, la duración t1 de los primeros segmentos CS1 de celda no es constante: la duración de los segmentos H es constante, pero tal segmento puede ser el primer segmento de celda o el segundo segmento de celda, dependiendo de si los datos de celda son "1" o "0". Otra manera de describir lo anterior seria al decir que cada celda contiene la combinación de un segmento H de una duración tH especificada y un segmento L de una duración tL = tT-tH, especificada, en donde tH y tL son constantes, y en donde el segmento H es el primer segmento o el segmento L es el primer segmento. Aún otra manera de describir lo anterior seria al decir que cada celda se subdivide en TRES segmentos: un primer segmentó de una duración tx<Tc, un segundo segmento de duración Tc-2tx, y un tercer segmento de duración tx, en donde el primer segmento es un segmento H y el tercer segmento es un segmento L para los datos "1" de celda o viceversa para los datos "0" de celda, y en donde el segundo segmento es H o L dependiendo del ciclo de trabajo que es más del 50% o menos del 50% sin influenciar los datos de la celda.</p>

- Las señales ilustradas en las Figuras 3A-B son las señales  $S_D$  de manejo que manejan el LED, pero debe ser claro que la salida de la luz del LED sigue la misma curva, y también que la señal de salida del sensor 41 que recibe la salida de la luz seguirá básicamente la misma curva, aunque quizás con algún ruido y/o interferencia causado por los alrededores, por ejemplo, por otras fuentes de luz. Un aspecto adicional en la presente invención se relaciona con el problema de analizar la señal recibida, es decir, la señal de salida del sensor. En la explicación que sigue, se asume que la señal de salida del sensor 41 se comunica al controlador 30 central (enlace 42 de retroalimentación), y que el controlador 30 central de un lado es diseñado para decodificar el contenido de datos de la señal y de otro lado es diseñado para medir la intensidad pico de la luz tal como es recibida por el sensor. Alternativamente, por ejemplo, un decodificador separado se podría suministrar en el dispositivo 40 de recepción.

- Para analizar la señal de detección, la presente invención propone utilizar filtros de case. Los filtros de case para analizar señales digitales son conocidos per se. Básicamente, tal filtro contiene una forma de onda preprogramada, y esta correlaciona la señal recibida a ser analizada con la forma de onda preprogramada; Su señal de salida tiene un valor que indica la cantidad de correlación entre la señal recibida y la forma de onda preprogramada. Este valor de correlación de salida indica que tanta señal recibida corresponde a la forma de onda preprogramada del filtro. De

comparar este valor de correlación de salida con un umbral, se puede tomar una decisión SI/NO de si o no la señal recibida contiene la forma de onda preprogramada del filtro. Esta operación será brevemente explicada con referencia a las Figuras 4A-D, donde la forma de onda preprogramada será brevemente indicada como "forma de filtro" FS.

5

10

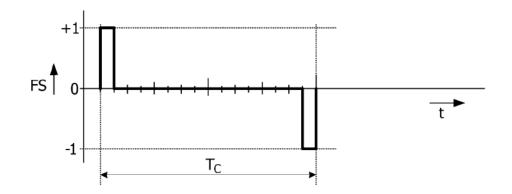

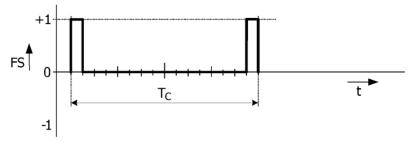

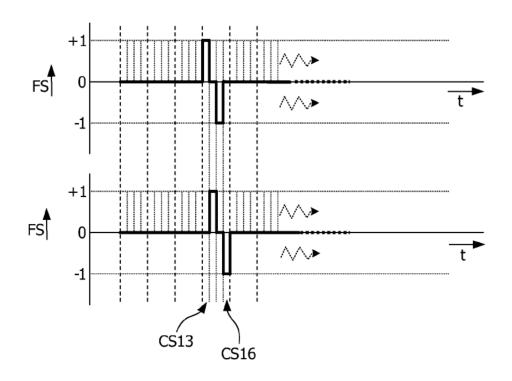

La Figura 4A muestra esquemáticamente un filtro 50 de case, que tiene una entrada 51 para recibir una señal Si de entrada a ser analizada, y que tiene una salida 52 para suministrar una señal S0 de salida. La señal Si de entrada a ser analizada es una señal con celdas de tiempo predeterminadas que tienen una duración Tc de celda. El filtro 50 está destinado a analizar las señales moduladas bifase tal como se explicó con referencia a la Figura 2C, y tiene una forma FS de filtro ilustrada en la Figura 4B, que tiene un valor +1 de tiempo t=0 a 0.5 TC y un valor -1 de tiempo t=0.5 Tc a Tc. El filtro 50 se diseña para calcular su señal S0 de salida de acuerdo a una operación S0 = IP(FS Si), del producto interno, que se define como tomando el producto FS(t)-Si(t) para cada valor y el tiempo entre 0 y Tc e integrar esto sobre el rango de 0 a Tc.

15 La Figura 4C ilustra lo que ocurre en el caso de que la señal Si de entrada contenga una celda C1 HL como se

ilustra en la Figura 2C; en la siguiente explicación, el nivel L bajo se considerará igual a cero. Para cada momento de tiempo entre t=0 y t=0.5 Tc, la señal de entrada tiene un valor H y la forma FS del filtro tiene un valor + 1, de tal forma que el producto FS(t)- Si(t) = H para estos tiempos. Para cada momento en el tiempo entre t=0.5·Tc y t=Tc, la señal de entrada tiene el valor cero y la forma FS del filtro tiene valor -1, de tal manera que el producto FS(t) Si(t)=0

para estos tiempos. Integrar este producto sobre el rango de 0 a Tc produce S0 = 0.5·Tc·H

La Figura 4D ilustra lo que ocurre en el caso de que la señal Si de entrada contenga una celda C3 LH como se ilustra en la Figura 2C. Para cada momento en el tiempo entre t=0 y t=0.5 Tc, la señal de entrada tiene el valor cero y la forma FS del filtro tiene valor +1, de tal manera que el producto FS(t)·Si(t)=0 para estos tiempos. Para cada momento en el tiempo entre t=0.5 Tc y t=Tc, la señal de entrada tiene el valor H y la forma FS del filtro tiene el valor -1 de tal manera que el producto FS(t)-Si(t) =-H para esos tiempos. Integrar este producto sobre el rango de 0 a Tc produce So=-0.5·Tc·H.

25

30

20

La Figura 4A muestra además que la señal de salida del filtro So se puede suministrar a un comparador 53, que compara la señal So de salida del filtro con un nivel de umbral predefinido TH. Un valor adecuado para el nivel TH umbral en el ejemplo anterior sería cero. Si el comparador 53 encuentra que la señal So está por encima de cero, este decide sacar un digital "1"; si el comparador 53 encuentra que la señal So está por debajo de cero, este decide sacar un digital "0".

35

40

En referencia al ejemplo de la Figura 4C, en el caso de que la señal Si de entrada se afecte por el ruido o la atenuación, de tal manera que, en algún momento en la primera mitad del periodo de la señal, el valor de la señal sea menor que H, la contribución a la señal de salida integrada se vuelve menor, es decir, el valor de la señal So de salida disminuye. De manera similar, en el caso en que en algún momento en la segunda mitad del periodo de señal, el valor de la señal esté por encima de cero, resulta en una contribución negativa a la señal de salida integrada, de tal manera que el valor de señal de salida So disminuye también. Sin embargo, en tanto que la señal So de salida este por encima de cero, la señal Si de entrada se reconocerá como una señal HL decodificada como "1", con base en la presunción de que es más probable que la señal de entrada Si sea una señal LH que codifica para "0". Se debe notar que esta "decodificación" se basa en información de que la señal de entrada pude tener solo una salida o dos posibles formas, y en la información que defina estas dos posibles formas.

45

De lo anterior se sigue que la forma FS del filtro ilustrada en la Figura 4B es la forma más adecuada para decodificar la señal codificada bifase en la Figura 2C (NB: lo mismo aplicaría al filtro que tiene la forma de filtro invertida). Se espera que la señal solo tome una de dos posibles formas de onda, y la salida del filtro So tenga valores absolutos máximos en el caso de que la señal de entrada sea exactamente igual a una de dos formas de onda esperadas. En general, en el caso de que una señal a ser analizada solo pueda tomar una de dos posibles formas de onda, esta puede mostrar que se obtenga la forma de filtro optima al sustraer estas dos formas de ondas posibles una de la otra, se puede ver fácilmente que sustraer una señal LH de una señal HL produce una forma FS de filtro ilustrada en la Figura 4B.

55

50

Con referencia a las Figuras 3A y 3B, un problema ahora es el hecho de que la señal a ser analizada pueda tomar más de solamente dos posibles formas de onda, ya que el ciclo de trabajo puede tomar cualquier valor desde casi cero a casi 100%. Solamente si se conoce el ciclo de trabajo, la señal a ser analizada puede tomar solamente una de dos posibles formas de onda de nuevo (ver celdas C(1) y C(2) en la Figura 3A), y sería posible adaptar adecuadamente la forma FS del filtro (es decir, ajustar el filtro).

60

Se debe notar que lo anterior no implica que sea posible detectar confiablemente los códigos HL o LH de señal. Utilizando la forma FS del filtro de la Figura 4B, debe ser claro que la celda C(1) de la Figura 3A resultaría de las salidas So del filtro que tiene el valor So=t₁·H mientras que la celda C(2) de la Figura 3A resultaría en la salida So del filtro que tiene valor So=-t<sub>T</sub> H. Lo mismo aplicaría a la celda C(1) y C(2) de la Figura 3B. Sin embargo, es

65 deseable poder detectar el ciclo de trabajo. Desafortunadamente, no es posible medir de manera directa el ciclo de trabajó sobre la base del nivel de señal promedio de la señal Si de entrada, en vista del hecho de que el valor H no es fijo sino que depende, entre otros, de la distancia entre el LED y el sensor.

5 La presente invención suministra un método para solucionar este problema.

10

20

25

30

35

40

45

50

65

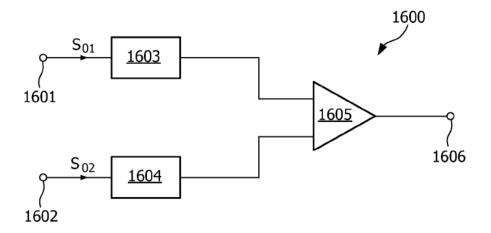

La Figura 5A es un diagrama de bloque que ilustra esquemáticamente un circuito 60 de decodificación de señal, que comprende dos filtros 61 y 62 de case dispuestos en paralelo. El circuito 60 tiene una entrada 63 de circuito para recibir la señal Si a ser analizada; los dos filtros 61 y 62 de case tienen sus entradas respectivas acopladas a la entrada 63 del circuito, de tal manera que ellos reciben ambos la misma señal. Se debe notar que el circuito 60 puede comprender un amplificador de entrada, no mostrados por motivos de simplicidad. Los dos filtros 61 y 62 de case tienen formas FS1 y FS2 de filtro, respectivamente, que son mutuamente diferentes.

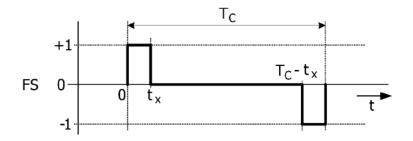

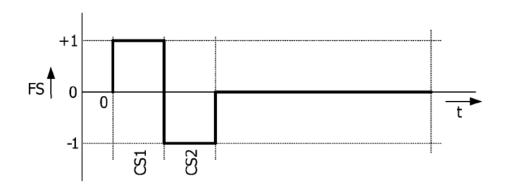

La Figura 5B ilustra el perfil general de una forma de filtro. Para el tiempo t=0 a tx, la forma FS del filtro tiene el valor +1. Para el tiempo t=(Tc-tx) a Tc, la forma FS de filtro tiene valor -1. Entre los tiempos tx y (Tc-tx), la forma FS del filtro tiene valor 0.

Como se explicó anteriormente, tales formas de filtro son óptimas para decodificar una señal que tiene un ciclo de trabajo  $\Delta$ =tx/Tc. Por lo tanto, en lo que sigue, esta forma de filtro se denominará mediante el valor del ciclo de trabajo  $\Delta$ . Así, la forma del filtro de la Figura 4B se indicara como el 50% de la forma del filtro, y el filtro de case que tiene esta forma de filtro se indicará como un 50% del filtro. Además, se dice que el filtro tiene un valor  $\Delta$  de ciclo de trabajo.

Los dos filtros 61 y 62 de case del circuito 60 de decodificación de señal tienen valores  $\Delta 1$  y  $\Delta 2$  de ciclo de trabajo mutuamente diferentes, respectivamente. Aunque no es esencial, se prefiere que uno de los filtros tenga un valor del 50% del ciclo de trabajo; por lo tanto, en la realización de ejemplo de la Figura 5A, el primer filtro 61 de case es un 50% del filtro (ver Figura 4B). El segundo filtro 62 de case tiene un valor  $\Delta 2$  de ciclo de trabajo más pequeño que  $\Delta 1$ ; por vía de ejemplo, el segundo valor  $\Delta 2$  de ciclo de trabajo puede ser tan bajo como 0.1% (por motivos de claridad,  $\Delta 2$  se exagera en las Figuras 5B-5D).

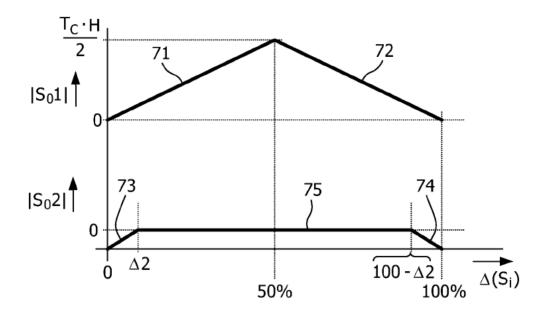

La Figura 5C es una gráfica que muestra el valor absoluto de las señales So1 y So2 de salida del primer y segundo filtro 61, 62 de case, respectivamente (eje vertical) como una función del ciclo de trabajo  $\Delta(Si)$  de las señales Si de entrada a ser analizada. En referencia a la explicación anterior, el valor absoluto |So1| de la señal So1 de salida del primer filtro 61 de case tiene un valor |So1| máximo =  $0.5 \cdot Tc \cdot H$  si el ciclo de trabajo  $\Delta(Si)$  de la señal Si de entrada es igual al 50%. Si el ciclo de trabajo  $\Delta(Si)$  de la señal Si de entrada es menos del 50%, el valor absoluto |So1| de la señal So1 de salida del primer filtro 61 de case también es menor. Más específicamente, si el ciclo de trabajo  $\Delta(Si)$  de la señal Si de entrada esta entre 0 y 50%, el valor absoluto entre |So1| de la señal So1 de salida del primer filtro 61 de case es proporcional al ciclo de trabajo  $\Delta(Si)$  de acuerdo a  $|So1| = \Delta(Si) \cdot Tc \cdot H$  (porción 71 de línea). De manera similar, si el ciclo de trabajo  $\Delta(Si)$  de la señal Si de entrada está entre 50% y 100%, el valor absoluto |So1| de la señal So1 de salida del primer 61 de case es inversamente proporcional al ciclo de trabajo  $\Delta(Si)$  de acuerdo a  $|So1| = (1-\Delta(Si)) \cdot Tc \cdot H$  (porción de línea 72).

Con respecto al segundo filtro 62 de case, que tiene un ciclo de trabajo  $\Delta 2$  menor del 50%, se puede ver fácilmente que existe una relación similar. Si el ciclo de trabajo  $\Delta (Si)$  de la señal Si de entrada está entre 0 y  $\Delta 2$ , el valor absoluto |So2| de la señal So2 de salida del segundo filtro 62 de case es proporcional al ciclo de trabajo  $\Delta (Si)$  de acuerdo al  $|So2|=\Delta (Si)\cdot Tc\cdot H$  (porción de línea 73), mientras que, si el ciclo de trabajo  $\Delta (Si)$  de la señal Si de salida está entre 100% - $\Delta 2$  y 100%, el valor absoluto |So2| de la señal So2 de salida del segundo filtro 62 de case es inversamente proporcional al ciclo de trabajo  $\Delta (Si)$  de acuerdo a  $|So2|=(1-\Delta (Si))$ ,  $Tc\cdot H$  (porción de línea 74). Ya que la señal Si de entrada del tiempo  $\Delta 2\cdot Tc$  al tiempo (100%- $\Delta 2$ ). To no contribuye la señal So2 de salida, el valor absoluto |So2| de la señal So2 de salida del segundo filtro 62 de case no cambia si el ciclo de trabajo  $\Delta (Si)$  de la señal Si de entrada se cambia entre  $\Delta 2$  y (100%- $\Delta 2$ ) es decir, el valor absoluto |So2| de la señal So2 de salida del segundo filtro 62 de case es constante si el ciclo de trabajo  $\Delta (Si)$  de la señal Si de entrada esta entre  $\Delta 2$  y (100% - $\Delta 2$ ) (porción de línea 75).

Esto le permite a un procesador 64 que tiene una primera entrada 65 recibir las señales So1 de salida del primer filtro 61 de case y que tiene una segunda entrada 66 que recibe la señal So2 de salida del segundo filtro 62 de case para calcular una señal indicativa del ciclo de trabajo Δ(Si) de la señal Si de entrada al calcular la proporción R de sus dos señales de entrada de acuerdo a R=|So1|/|So2|. Si el ciclo de trabajo Δ(Si) de la señal Si de entrada esta entre Δ2 y 50%, dicha proporción R es igual a Δ(Si)/Δ2, así Δ(Si) se puede calcular de acuerdo a Δ(Si) = R·Δ2. Si el ciclo de trabajo Δ(Si) de la señal Si de entrada esta entre el 50% y (100%-Δ2), dicha proporción R es igual a (1-Δ(Si))/Δ2, así Δ(Si) se puede calcular de acuerdo a Δ(Si) = 1-R·Δ2.

El ciclo de trabajo  $\Delta(Si)$  es ya un parámetro importante para un controlador 30 central o cualquier otro receptor. Además, es posible que el ciclo de trabajo  $\Delta(Si)$  calculado de la señal recibida se utilice para adaptar el ciclo de trabajo  $\Delta 2$  del segundo filtro 62 de case para ser sustancialmente igual al ciclo de trabajo  $\Delta(Si)$  calculado de la señal recibida, de tal manera que el proceso de decodificar la corriente de datos contenida en la señal Si de entrada se

optimice. Esta afinación del segundo filtro 62 de case se indica mediante la línea 69 punteada en la Figura 5A. El procesador 64 (o un procesador diferente) tomara la señal So2 de salida del segundo filtro 62 de case afinado como la entrada para detectar "0" y "1" bits codificados en las celdas HL y LH, respectivamente.

5 Se debe notar aquí que el receptor requiere saber si el ciclo de trabajo está por debajo o por encima del 50%; esta información puede estar contenida en los datos decodificados de la señal.

10

15

65

Se debe notar además que el procesador 64 también tiene suficiente información para permitírsele calcular el nivel Smax de salida de luz máxima posible a ser esperado en el sitio del dispositivo 40 de recepción de acuerdo a Smax= $|So2|/\Delta2$ , si el ciclo de trabajo  $\Delta(Si)$  de la señal Si de entrada esta entre  $\Delta2$  y (100%- $\Delta2$ ).

Se debe notar adicionalmente que, en lugar de basarse en el ciclo de trabajo que está siendo medido, es posible que la transmisión de datos comprenda información del sistema. Por ejemplo, se pueden transmitir datos en cuadros, cada cuadro contiene un número de campos de dato, y uno de estos campos de datos puede contener información que revela el ciclo de trabajo. En tal caso, el procesador 64 puede derivar el ciclo de trabajo  $\Delta(Si)$  de los datos de la señal Si de entrada, y posiblemente afinar el segundo filtro 62 sobre la base de esta información.

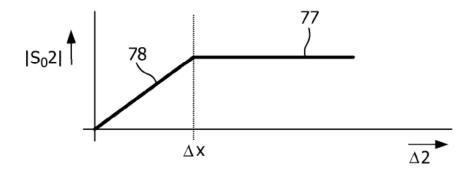

El método anterior se basa en el uso de dos filtros 61 y 62 de case. En un método alternativo, solo se requiere un filtro 62 de case afinable. Una señal Si de salida es recibida, la cual tiene un ciclo de trabajo  $\Delta(Si)$  especifico; asumiendo que este ciclo de trabajo  $\Delta(Si)$  sea menor que el 50%. La Figura 5D es una gráfica, que ilustra el valor absoluto |So2| del filtro 62 de case afinable (eje vertical) como una función del ciclo de trabajo  $\Delta 2$  del filtro 62 de case afinable es mayor que el ciclo de trabajo  $\Delta(Si)$  especifico de la señal Si de entrada, el valor absoluto |So2| de la señal So2 de salida del filtro 62 de case afinable es constante (porción 77 de línea). Si el ciclo  $\Delta 2$  de trabajo del filtro 62 de case afinable es inferior que el ciclo de trabajo  $\Delta(Si)$  especifico de la señal Si de entrada, el valor absoluto |So2| de la señal So2 de salida del filtro 62 de case afinable es proporcional al ciclo de trabajo  $\Delta 2$  del filtro 62 de case afinable de acuerdo a |So2| =  $\Delta 2$ .Tc.H (porción de línea 78).

Así, la presente invención propone un método para determinar el ciclo de trabajo Δ(Si) de una señal Si de entrada, un método que comprende las etapas de variar el ciclo de trabajo Δ2 del filtro 62 de case afinable con el fin de encontrar un valor Δx especifico donde la porción 78 de línea inclinada se encuentra con la porción 77 de línea horizontal: el ciclo de trabajo Δ(Si) de la señal Si de entrada será igual a Δx. En una realización específica, el método puede comprender la etapa de incrementar el ciclo de trabajo Δ2 del filtro 62 de case afinable que inicia en cero, o disminuye el ciclo de trabajo Δ2 al filtro 62 de case afinable que inicia en 50%.

En lo anterior, la celda de tiempo solo contiene un bit de información. La presente invención además está destinada a suministrar una mejora, en donde el número de bits por celda puede ser mayor de uno, y donde el ciclo de trabajo de la señal puede aún variar.

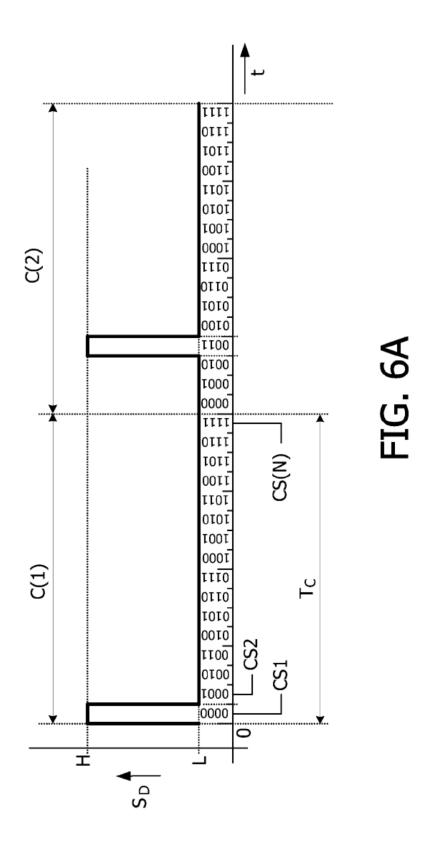

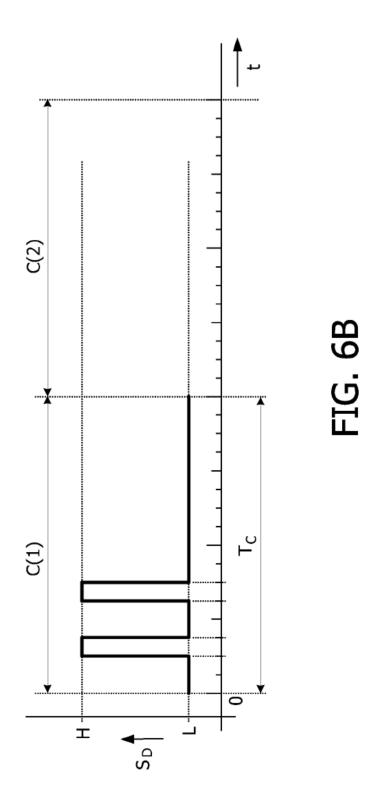

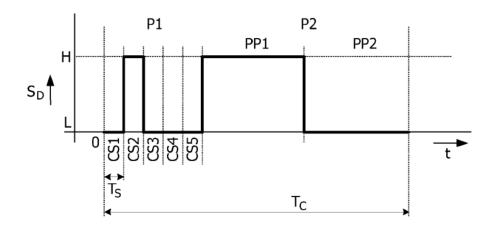

La Figura 6A es una gráfica, comparable con las Figuras 2C, de una señal S<sub>D</sub> de manejo propuesta por la presente invención. De nuevo, la señal es dividida en celdas de tiempo, indicadas como C(1), C(2), etc. Las celdas tienen duración T<sub>C</sub> mutuamente igual que se puede determinar por una señal de reloj (no mostrada) por motivos de simplicidad. Cada celda C(i) de tiempo esta subdivida en una pluralidad N de segmentos CS1, CS2, CS3,...CS(N) segmentos consecutivos de celda de duración mutuamente igual. Como tal, se puede considerar como una generalización de la señal codificada bifase, donde N = 2. De nuevo, la señal S<sub>D</sub> puede tener dos valores H y L de señal solamente. Más particularmente, en cada segmento de celda la señal S<sub>D</sub> es H o L, en donde los valores de la señal de diferentes segmentos CS de celda puede establecerse independientemente el uno del otro

Los segmentos de celda que tienen valor H se indicaran como segmentos H mientras que los otros segmentos se indicarán como segmentos L. En cada celda C(i), se define un ciclo de trabajo  $\Delta$ (i) como la proporción a la duración combinada de los segmentos H de la de la duración  $T_C$  de celda. Así, el ciclo de trabajo  $\Delta$ (i) se puede describir como N(H)/N, en donde N(H) indica el número de segmentos H. Así, es posible variar el ciclo de trabajo  $\Delta$ (i) en las celdas entre 0 y 1 en las etapas de 1/N.

55 Se debe notar que, normalmente, el ciclo de trabajo puede ser sustancialmente constante durante un periodo de tiempo mayor que la duración de la celda. Por lo tanto, en la siguiente discusión, se asumirá que el ciclo de trabajo es constante.

La Figura 6A muestra un ejemplo de una señal que tiene un ciclo de trabajo Δ=1/n. En este ejemplo, el primer segmento CS1 de celda de la celda C(1) es H mientras que los otros segmentos de celda son L. En la celda C(2) el cuarto segmento CS4 de celda es H mientras que los otros segmentos son L.

Debe ser claro que, en tanto se relacione con el ciclo de trabajo, no importa cuál de los segmentos de celda es H. De otra parte, la selección de cual celda es H contiene información: existen N posibilidades de tal manera que la celda pude tener un "valor" de 1 a N. Por motivos de simplicidad, asumir que N = 2<sup>n</sup>. En ese caso, una celda puede codificar para n bits. Esto se ilustra en la Figura 6A, donde n se selecciona para ser igual a 4 de tal manera que

N=16. En los segmentos de celda, se describen los códigos binarios para los valores 0 a 15 (es decir 0000 a 1111). Si el primer segmento CS1 de celda es H este se interpreta como siendo equivalente a la contraseña 000. Si el cuarto segmento CS4 de celda es H, este se interpreta como siendo equivalente a la contraseña 0011. Y así sucesivamente (se debe notar que las diferentes traducciones entre el número del segmento H y las contraseñas son posibles). Así, mientras que se mantiene constante el ciclo de trabajo, el número de bits llevados por celda de tiempo se ha incrementado por un factor 4 comparado con la técnica anterior, donde la celda de tiempo lleva solamente un bit de información.

Lo anterior aplica no solamente a 2<sup>n</sup> los segundos segmentos de celda por celda. Más generalmente, si la celda contiene N segmentos de celda, son posibles N posiciones para el segmento H único, el cual puede codificar para <sup>2</sup>log(N) bits por celda.

Lo anterior aplica a un ciclo de trabajo  $\Delta$ =1/N. La Figura 6B muestra un ejemplo de una señal que tiene un ciclo de trabajo  $\Delta$ =2/N. En este ejemplo, el tercer y sextos segmentos de celda CS3 y CS6 son H mientras que los otros segmentos de celda son L. En el caso de que N=16, debe ser claro para una persona experta en la técnica que existen 120 diferentes posibles combinaciones para las ubicaciones de los dos segmentos H en una celda, lo cual puede codificar para  $^2$ log(120)=6.9 bits por celda. Más generalmente, si una celda contiene N segmentos de celda, existen  $\binom{N}{2}$  posibles combinaciones para los dos elementos H, que pueden codificar para  $^2$ log  $\binom{N}{2}$  bits por celda. Aún más generalmente, si el ciclo de trabajo  $\Delta$ =m/N, en donde m es un entero entre 1 y N-1, existen  $\binom{N}{m}$  posibles

combinaciones para los dos segmentos H, que pueden codificar para  ${}^2\log{N\choose m}$  bits por celda

15

20

35

40

45

50

55

De la anterior explicación, debe ser claro que la señal contiene datos así como también información del ciclo de trabajo.

De la explicación anterior, debe ser claro adicionalmente, que, para una velocidad de datos dada determinada por el ciclo de trabajo, el contenido de datos se puede seleccionar libremente sin afectar el ciclo del trabajo. Además, debe ser claro que el ciclo de trabajo puede variar (en las etapas de 1/N) y que, para cada valor del ciclo de trabajo, el número de bits de información por celda se ha incrementado con respecto a la codificación bifase de la técnica anterior, anotándose que la extensión del incremento depende del ciclo de trabajo.

En general, con el ciclo de trabajo permaneciendo constante, el número de bits por celda incrementa el número de segmentos de celda por celda. Sin embargo, manteniéndose constante la longitud de la celda, existe un límite inferior como la duración de los segmentos de celda. Si se desea aun incrementar adicionalmente el número de segmentos de celda por celda, la longitud de la celda se debe incrementar. Sin embargo, no es necesario incrementar el número de segmentos de celda por celda, al infinitum, ya que el efecto de tal incremento disminuye.

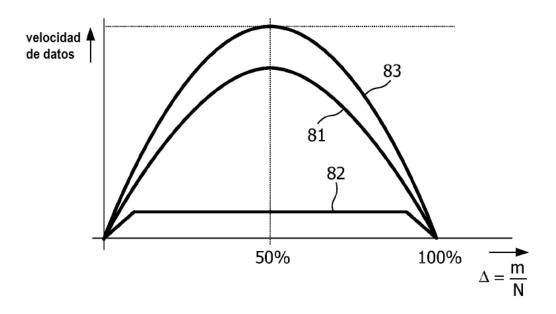

La Figura 7 es una gráfica que muestra la velocidad de datos expresada como el número de bits por segmento de celda eje vertical, como una función del ciclo de trabajo  $\Delta$ =m/N (eje horizontal). Una primera curva 81 relaciona el

ejemplo anterior de una celda que tiene 16 segmentos de celda y muestra  $\frac{^{2}Log\binom{16}{m}}{^{16}}$  como una función del ciclo de trabajo  $\Delta$ =m/16. Una línea horizontal 82, por vía de comparación, indica la cantidad de 1/16 que corresponde a un bit por celda para una celda que tiene 16 segmentos, que indica la velocidad de datos de la técnica anterior. Se puede ver que la mejora de la velocidad de datos comparada con la técnica anterior involucra un factor 10 si el ciclo de trabajo es del orden de 0.5. Una tercera curva 83 muestra la velocidad de datos máxima que se puede lograr, es

decir  $\frac{^2Log\binom{N}{m}}{N}$  para límite de N aproximándose a infinito. Aquí, se hace referencia a la "función de entropía" h de Shannon. Se puede ver que al establecer el número de N de los segmentos de celda en 16, se logra el 85% de velocidad de datos máxima posible. Si el numero N de segmentos de celda se incrementará a 100, la velocidad de datos solo se incrementaría a 96% de la velocidad de datos máxima posible. Así, N=16 es la selección adecuada, suficiente y preferida, si la velocidad de datos es solo el tema de preocupación. Sin embargo, ya que el ciclo de trabajo solo puede variar en las etapas de 1/N, como se mencionó, sería preferible tener N mucho mayor, por ejemplo tan alto como 1024 o aún mayor.

La Figura 7 ilustra que la velocidad más alta de datos se obtiene si el ciclo de trabajo es cercano al 50%. Sin embargo normalmente el ciclo de trabajo no se puede seleccionar libremente con miras a una velocidad optima de datos, ya que el ciclo de trabajo se determina con miras a obtener un cierto efecto de iluminación (atenuación de un LED) y se puede considerar como una restricción dada cuando se determina la capacidad de velocidad de datos de un LED. Por ejemplo, se puede ver en la Figura 7 que si un LED es operado en un ciclo de trabajo de 12.5% la capacidad de la velocidad de datos es de solo 43% de la velocidad de datos máxima posible, que es la mitad de la capacidad comparada con la situación con un 50% del ciclo de trabajo

60 Sin embargo, en caso de que el sistema comprenda una pluralidad LED, es posible incrementar la velocidad de datos. Por vía de ejemplo, considere una realización donde una fuente de luz comprende 4 LED para incrementar la salida de luz. En caso de que los LED sean operados en paralelo en un ciclo de trabajo de 12.5%, la capacidad de

velocidad de datos es de solo el 43%, como se mencionó. Sin embargo, también es posible solo utilizar un LED en un ciclo de trabajo del 50% aunque manteniendo los otros LED apagados: en ese caso, la salida de luz del sistema como un todo corresponderá a un al 12.5% del máximo, mientras que la capacidad de la velocidad de datos se ha incrementado a un 100%.

5

De manera similar, en el caso de fuentes de luz que van a ser operadas a una salida de luz del 87.5%, la capacidad de la velocidad de datos se incrementa si un LED es conmutado a un ciclo de trabajo del 50% aunque manteniendo los otros LED continuamente prendidos.

10

Así, en general, en caso de que una fuente de luz que comprende X LED va a ser operada a una salida de luz de Y%, la presente invención propone operar solo parte de aquellos LED aunque manteniendo los otros LED prendidos o apagados (dependiendo de Y siendo mayor o menor del 50%). El número de LED operado se selecciona de tal manera que el ciclo de trabajo es tan cercano al 50% como sea posible.

15

Se debe notar que no es necesario que los otros LED estén todos prendidos o apagados: es posible que algunos de los otros LED estén continuamente prendidos mientras que el resto de los otros LED estén continuamente apagados. Por ejemplo, si un LED es conmutado a un ciclo de trabajo del 50%, un LED está continuamente prendido, y el resto de los dos LED están continuamente apagados, la salida de luz promedio es igual al 37,5%

Se debe notar que se puede lograr más flexibilidad si el número de los LED operados difiere de una celda de tiempo

25

20

a la siguiente, en tanto que no sea visible el parpadeo en que se incurre. Por ejemplo, si en una celda de tiempo solamente se opera un LED en un ciclo de trabajo del 50% y los otros tres LED están apagados, el promedio de salida de luz total considerado sobre aquellos cuatro LED es igual al 12.5% de la salida de luz máxima (cuyo máximo se lograría si todos los cuatro LED estuvieran continuamente prendidos). Si en la siguiente celda de tiempo dos LED están operados a un ciclo de trabajo del 50% y los otros tres LED están apagados, el promedio de salida de luz total considerado sobre aquellos cuatro LED es igual al 25%. Considerados sobre aquellas dos celdas de tiempo, la salida de luz total promedio será igual a 18.75%. Si este segundo LED se usa solamente una vez cada tres celdas de tiempo, la salida de luz total promedio considerada sobre aquellas tres celdas de tiempo y considerada sobre aquellos cuatro LED es igual al 16.6%. Así, es posible combinar un ciclo de trabajo del 50% con 30 el fin de lograr una velocidad de datos máxima con una salida de luz total promedio que difiere del 50%. Es además posible que el ciclo de trabajo de los LED activos se establezca para estar cercano a 50 pero no igual a 50, para ser posible aproximar el nivel de salida de luz pretendida más cercanamente. Notoriamente, sin embargo, esta aproximación introduce contenido de baja frecuencia y de esta manera incrementa las posibilidades de parpadeo

35

Un incremento adicional en la velocidad de datos es posible sino es necesario que los LED sean operados en paralelo: como se puede ver fácilmente en la Figura 7, la velocidad de datos combinados de los cuatro LED operados independientemente el uno del otro en un ciclo de trabajo del 12.5% cada uno es mayor que la velocidad de datos de un LED operado en un ciclo de trabajo del 50%.

40

45

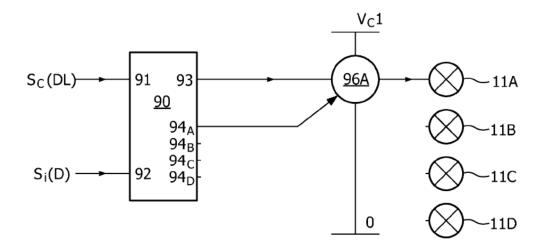

La Figura 8 es un diagrama de bloque que ilustra un manejador 90 de fuente de acuerdo con la presente invención, que permite el método de operación anterior, para manejar una fuente que comprende 4 LED 11A, 11B, 11C, 11D. El manejador 90 tiene una primera entrada 91 para recibir una señal de comando de nivel de atenuación Sc(DL) y una segunda entrada 92 para recibir una señal Si(D) de entrada de datos. Aquellas dos entradas pueden ser físicamente distintas, pero ellas también se pueden ejecutar como una entrada combinada. En un modo de operación, el manejador 90 determina un número m de segmentos de celda activos sobre la base de la señal Sc(DL) del comando de nivel de atenuación de m=DL·N, donde DL indica el nivel de atenuación. Si se requiere, m puede ser redondeado. Con este número m de segmentos activos, es decir, segmentos que tienen el valor H, el manejador 90 entonces puede manejar todos los LED en paralelo, efectuando m de N codificaciones; esto requiere solo una salida.

50

55

60

65

Para una velocidad de datos más eficiente, el manejador comprende cuatro interruptores 96A, 96B, 96C, 96D, de tres vías controlables, cada una asociada con un LED 11A, 11B, 11C, 11D, respectivo. Por motivos de claridad, solamente un interruptor 96A se muestra, asociado con el primer LED 11A. El manejador 90 tiene una salida 93 de datos, y cuatro salidas de control de interruptor, 94A, 94B, 94C, 94D de control de interruptor, cada una acoplada a un terminal de control de uno de los interruptores 96A, 96B, 96C, 96D, correspondientes. Cada interruptor tiene una primera entrada acoplada a una fuente Vcl de voltaje constante, una segunda entrada acoplada a un voltaje cero, y una tercera entrada acoplada a la salida 93 de datos. Además, cada interruptor tiene una salida acoplada al LED 11A, 11B, 11C, 11D correspondiente. Controlado por una señal de control de interruptor desde la respectiva salida 94A, 94B, 94C, 94D de control de interruptor, un interruptor 96A, 96B, 96C, 96D de tres vías es una primera condición operativa donde su salida es continuamente acoplada a su primera entrada de tal manera que el correspondiente LED 11A, 11B, 11C, 11D está continuamente PRENDIDO, o en una segunda condición operativa donde su salida está continuamente acoplada a su segunda entrada de tal manera que el correspondiente LED 11A, 11B, 11C, 11D está continuamente APAGADO, o en una tercera condición operativa donde su salida está continuamente acoplada a su tercera entrada de tal manera que el correspondiente LED 11A, 11B, 11C, 11D esta operado en un modo de conmutación de ciclo de trabajo. Con base en la señal de comando del nivel de atenuación. el manejador calcula los valores adecuados para m, para un número de m1 de LED que estarán continuamente PRENDIDOS, y para un número m2 de LED que estarán continuamente APAGADOS. Él manejador genera entonces sus señales de control de interruptor para los interruptores 96A, 96B, 96C, 96D, de tal manera que m3 interruptores están en su tercera condición operativa, m1 interruptores están en su primera condición operativa, y m2 interruptores están en su segunda condición operativa, donde m3=N<sub>LS-</sub>m1-m2, N<sub>LS</sub> indicando el número total de fuentes de luz.

Se debe notar que los interruptores 96A, 96B, 96C, 96D pueden ser internos o externos al manejador 90

Se debe notar que la explicación anterior se relaciona con el número de LED que están PRENDIDOS, APAGADOS, o conmutados, no necesariamente a la identidad de los LED. Por ejemplo, es posible que un LED específico este continuamente PRENDIDO durante la primera celda de tiempo y continuamente APAGADO durante la segunda celda de tiempo mientras que otro LED específico está continuamente APAGADO durante la primera celda de tiempo y continuamente PRENDIDO durante la segunda celda de tiempo: aunque esto cambia la identidad de los LED PRENDIDOS y los LED APAGADOS, este no cambia el número de LED PRENDIDOS o el número de LED APAGADOS.

La explicación anterior se relaciona con el uso de N segmentos en una celda de tiempo, y controlar el ciclo de trabajo al establecer m de N segmentos para ser iguales a H mientras que los otros son L; esto se indicará como m de N operaciones. En una mejora adicional, la presente invención propone combinar las m de N operaciones con el concepto bifase. De nuevo, una celda de tiempo se subdivide en N segmentos de celda, siendo N un número par. Cada segmento es pareado con otro segmento, de tal manera que existen N/2 pares, aquí, la frase "par" se utiliza para significar dos segmentos asociados el uno con el otro. Cada segmento puede ser H o L. En el concepto bifase original como se describió anteriormente, donde N=2, los segmentos pareados siempre tienen valor opuesto, de tal manera que el par solo puede ser HL o LH. Esta característica se puede utilizar en una implementación donde el ciclo de trabajo se fija a 50%. Con el fin de permitir que se varíe el ciclo de trabajo, la presente invención propone además que cada segmento de un par pueda ser individualmente establecido en H o L, independientemente del valor del otro segmento, de tal manera que el par puede ser LL, LH, HL, o HH. El valor del par se puede medir utilizando un filtro de case que es +1 para el primer segmento y -1 para el segundo segmento del par, y el cual es 0 para todos los otros segmentos. Por vía de ejemplo, la Figura 9 ilustra una forma de filtro para un filtro pareado que es +1 durante el primer segmento y -1 durante el último segmento, y 0 durante los segmentos 2-15, en una celda de tiempo dividida en 16 segmentos; este filtro de case sería adecuado para decodificar el par de segmentos 1 y 16, como será claro para una persona experta en la técnica.

La codificación de tales pares de segmento puede ser como sigue:

LL y HH codifican "0" (la salida del filtro será 0);

5

20

25

30

35

50

60

LH y HL codifican "1" (el valor absoluto de la salida del filtro estará por encima de un umbral)

Por vía de ejemplo, N se toma como igual 16, de tal manera que el número de pares es igual 8. Asumiendo que el ciclo de trabajo es igual a 1/N (1/16 en este caso). Esto significa que solamente uno de los pares debe codificar como "1" mientras que todos los otros pares deben ser LL que codifican para "0" de tal manera que exactamente un segmento es H. Existen 8 posibilidades de hacerlo si (es decir existen 8 pares de los cuales escoger), que pueden ser representados por una contraseña de 3 bits de información. La selección del par que es LH o HL ofrece el cuarto bit de información.

Si el ciclo de trabajo es igual a 2/N (2/16 en este caso), existen dos maneras de lograr esto: una manera es tener dos pares que codifican para un "1" mientras que los otros pares son LL que codifican para "0", la otra manera es tener un par que es HH que codifica para "0" mientras que los otros pares son LL que codifican para "0". Los dos pares que codifican para "1" se pueden seleccionar en  $\binom{N/2}{2}$ = 28 maneras posibles; cada par puede ser LH o HL, multiplicando así el número de posibilidades por 4. El un par que es HH se puede seleccionar de 8 posibles maneras. Así, el número total de posibilidades es igual 4\*28+8=120, que se puede representar mediante una contraseña de 6.9 bits de información.

De manera más general, si el ciclo de trabajo es igual a m/N (m/16 en este caso), m de N/2 de los pares debe codificar un "1", y existen  $\binom{N/2}{m}$  posibilidades de hacerlo así, más existe m bits de información en los pares mismos.

Similares cálculos se deben efectuar para los otros valores de m. Debe ser claro que el cálculo para m es igual al cálculo para N-m

Expresando la capacidad de velocidad de datos como el número de bits de información que se puede cubrir por segmento de celda, los métodos bifase convencionales producen 0.5 bits por segmento (bps) El método propuesto por la invención para m=1 o m=15 produce 4/16=0.25 bps; para m=2 o m=14: 6.9/16=0.43 bps. Se puede mostrar que para todos los valores de m de 3 a 13 la capacidad de la velocidad de datos es igual o mayor de 0.5 bps.

Se debe notar que existen varios métodos posibles para parear segmentos de celda. La Figura 10 ilustra una celda de tiempo con 16 segmentos de celda, donde 8 flechas en forma de U indican pares de segmento. En el ejemplo de la Figura 10A, un segmento de celda es siempre pareado con su vecino, en una configuración que se puede denominar "pares vecino". La Figura 10A también muestra la forma del filtro de un filtro pareado adecuado para analizar el primer par de segmento: esta forma de filtro es +1 durante el primer segmento de celda, -1 durante el segundo segmento, y 0 para todos los otros segmentos.

5

20

50

55

60

- La Figura 10B ilustra una manera diferente de pareado: aquí, un segmento de celda i es siempre pareado con el segmento i+8 de celda, para i=1 a 8, en una configuración que se puede denominar "pares intercalados". La Figura 10B también muestra la forma de filtro de un filtro pareado adecuado para analizar el primer par de segmento: esta forma de filtro es +1 durante el primer segmento de celda, -1 durante el noveno segmento, y 0 para todos los otros segmentos.

- La Figura 10C ilustra aun una manera diferente de parear: aquí, un segmento de celda es siempre pareado con el segmento de celda 17-i, para i=1 a 8, en una configuración que se puede denominar "pares anidados". La Figura 10B también muestra la forma del filtro de un filtro de case adecuado para analizar el primer par de segmento. Esta forma de filtro es +1 durante el primer segmento de celda. -1 durante el décimo sexto segmento, y 0 para todos los otros segmentos.

- Se debe notar que, en tanto que se refieran a la codificación y al ciclo de trabajo, no hay diferencia de cual método de pareado se ejecuta, en tanto que los filtros de case del receptor/decodificador correspondan al método de codificación utilizado por quien lo envía. Sin embargo, el método de los "pares intercalados" de la Figura 10B del método "pares anidados" de la Figura 10C ofrece la ventaja de que el receptor está bien adecuado para recibir y procesar señales que son codificadas bifase con 50% del ciclo de trabajo de acuerdo a la técnica anterior (compatible hacia atrás). El método de "pares vecinos" de la Figura 10A tiene un contenido de frecuencia bajo más bajo comparado con el método de "pares intercalados" de la Figura 10B y el método de los "pares anidados" de la Figura 10C. El método de los "pares intercalados" de la Figura 10B es más fácil de ejecutar.

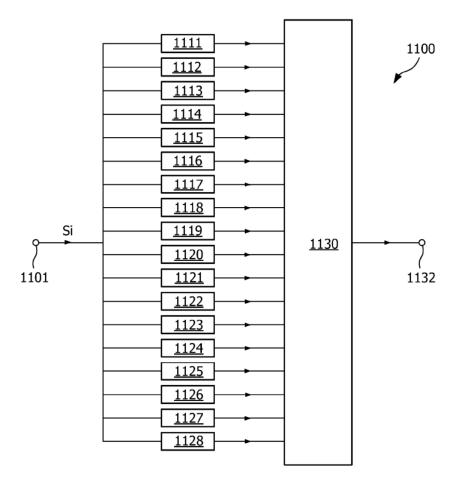

- La Figura 11A es un diagrama de bloque que ilustra esquemáticamente una posible realización de un dispositivo 1100 para recibir y codificar la luz emitida por un LED de acuerdo con los métodos anteriormente explicados de la invención. En una salida 1101 de señal, se recibe la señal Si a ser analizada, es decir, una señal de salida de un sensor de luz. El dispositivo 1100 comprende una primera serie de ocho filtros 1111-1118 de case que tiene sus respectivas terminales de entrada acopladas a la entrada 1101 de la señal. Cada filtro de case de la primera serie tiene una forma de filtro adaptada a un par correspondiente de segmentos de case para determinar si este par correspondiente de segmentos de case es HL o LH. La Figura 10C ilustra un ejemplo de una forma de filtro para el caso de los pares anidados: el primer valor del primer segmento de celda es igual a +1, el valor del filtro para el segmento de celda enésimo es igual a -1, el valor de filtro es 0 para todos los otros segmentos.

- El dispositivo 1100 comprende además una segunda serie de ocho filtros 1121-1128 de case que tienen sus respectivas terminales de entrada acopladas a la entrada 1101 de señal. Cada filtro de case de la segunda serie tiene una forma de filtro adaptada a un par correspondiente de segmentos de case para determinar si este par correspondiente de segmentos de case es LL o HH. La Figura 11B ilustra un ejemplo de una forma de filtro para el caso de los pares anidados: el primer valor para el primer segmento de celda es igual a +1, el primer valor del enésimo segmento de celda es igual a +1, el primer valor es 0 para todos los otros segmentos.

- El dispositivo 1100 comprende además un procesador 1130, que tiene entradas acopladas a las respectivas salidas de los filtros 1111-1118 y 1121-1128. El procesador 1130 es capaz de determinar, mediante cálculo o al considerar una tabla de consulta, el contenido de datos de las celdas de tiempo, sobre la base de la información combinada de los segmentos de tiempo individuales. El contenido de datos decodificado se puede suministrar en una salida 1132, para procesamiento adicional.

- Se debe notar que, si se requiere, el procesador 1130 es capaz de calcular el ciclo de trabajo de la señal Si de entrada.

- En las realizaciones anteriores, cada segmento de celda contribuye al ciclo de trabajo así como también contribuye al código de datos. En lo sucesivo, una realización de la presente invención se describirá, en la cual la información de datos y la información de ciclo de trabajo está separada (multiplexada) dentro de las celdas. Esto tiene la ventaja de que se reduce el contenido espectral para frecuencias inferiores.

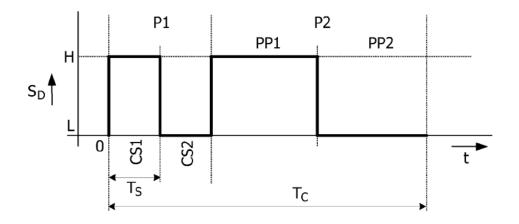

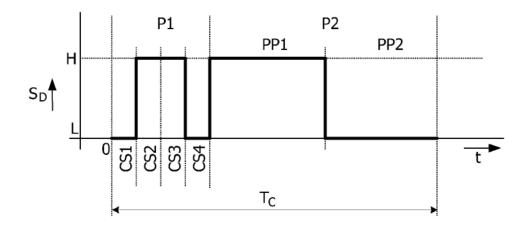

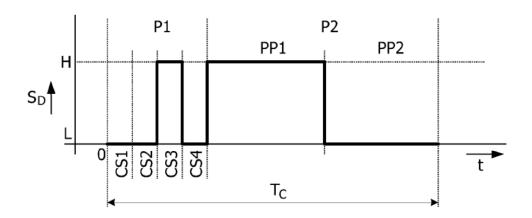

- La Figura 12A es un diagrama de tiempo, que muestra la señal de la lámpara (es decir la señal S<sub>D</sub> de manejo, o la intensidad de luz, o la señal de salida del sensor de luz) como una función del tiempo. La señal se divide en celdas de tiempo que tienen una duración T<sub>C</sub>. Cada celda de tiempo se subdivide en dos porciones P1 y P2 de celda, indicadas como porción de datos y porción del ciclo de trabajo, respectivamente. La porción de datos se subdivide en un número predefinido de segmentos CS de celda que tienen una duración T<sub>S</sub>. En la Figura 12A, este número predeterminado es igual a 2, los segmentos de celda se indican como CS1, CS2. La porción P2 de ciclo de trabajo

se puede subdividir en segmentos de celda también, en cuyo caso la duración de los segmentos de celda de la porción de ciclo de trabajo es preferiblemente igual a la duración de los segmentos de celda de la porción P1 de datos.

- Los dos segmentos CS1, CS2 de celda de la porción P1 de datos puede ser L o H, los dos segmentos CS1, CS2 de celda siempre tienen valores mutuamente opuestos, de tal manera que la porción P1 de datos se pueda representar como siendo LH o HL. Así, la porción P1 de datos se puede considerar como siendo un bi de código bifase, que tiene un valor "1" (LH) o "0" (HL).

- La porción P2 del ciclo de trabajo se utiliza para controlar la intensidad promedio del nivel de iluminación del LED que nos ocupa. Para este fin, la porción P2 del ciclo de trabajo se subdivide en dos partes PP1 y PP2, la primera parte PP1 es continuamente H y la segunda parte PP2 es continuamente L. Las longitudes de la primera y segunda partes PP1 y PP2 pueden variar, continua o discretamente. En el caso de que la porción P2 del ciclo de trabajo se subdivida en segmentos de celda también, todos los segmentos teniendo la misma duración, aplica la siguiente relación:

$N = T_C/T_S$

20

35

40

60

Siendo N el número de segmentos en una celda;

$N_{PP2} = N - 2 - N_{PP1}$

N<sub>PP1</sub> y N<sub>PP2</sub> siendo el número de H y L segmentos en la porción P2 del ciclo de trabajo, respectivamente;

25  $\Delta = (N_{PP1} + 1)/N$ ,

Siendo A el ciclo de trabajo.

De la explicación anterior, debe ser claro que la señal contiene datos así como también información del ciclo de trabajo. Preferiblemente, N es igual a una energía grande de 2, por ejemplo 1024, permitiendo una resolución de 10 bits del nivel de luz promedio.

De la explicación anterior debe ser además claro que el contenido de datos se puede seleccionar libremente sin afectar el ciclo de trabajo. El número de segmentos H siempre igual a 1 en la porción P1 de datos. Además, debe ser claro que el ciclo de trabajo puede variar (en las etapas de 1/N) de un mínimo de 1/N a un máximo de (N-1)/N sin afectar los datos.

La Figura 12B es un diagrama que ilustra la forma del filtro de un filtro de case adecuado para detectar el contenido de datos de la señal. Esta forma de filtro tiene un valor +1 durante el primer segmento CS1 de la porción P1 de datos, tiene un valor -1 durante el segundo segmento CS2 de la porción P1 de datos, y tiene un valor 0 durante la porción P2 del ciclo de trabajo. El valor de salida ≥0 de este filtro representa la decodificación de un "0" el valor de salida <0 de este filtro representa la decodificación de un "1".

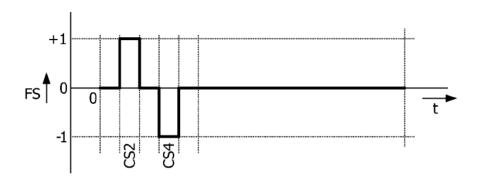

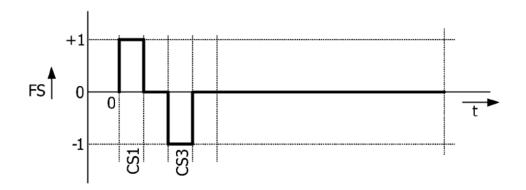

Con el esquema de codificación de la Figura 12A, los dos segmentos de celda CS1, CS2 del bit codificado y fase en la porción P1 de datos son directamente adyacentes el uno al otro, a la primera parte PP1 de la misma celda de tiempo, y a la segunda parte PP2 de la celda previa. Existe la posibilidad de que ocurra una interferencia de símbolo, es decir, interferencia entre celdas de tiempo adyacentes. Con el fin de mitigar este efecto, la presente invención propone una elaboración adicional ilustrada en la Figura 13A, que es un diagrama de tiempo comparable con la Figura 12A. En este caso, el número predeterminado de segmentos CS de celda en la porción de datos es igual a 5.

El primero, tercero, y quinto segmentos de celda CS1, CS3, CS5 son siempre L. El segundo y cuarto segmentos CS2, CS4 de celda pueden ser L o H, los dos segmentos CS2, CS4 de celda siempre tienen valores mutuamente opuestos, de tal manera que la porción P1 de datos se pueda representar como siendo LH o HL. Así, la porción P1 de datos puede de nuevo ser considerada como siendo un bit codificado bifase, que tiene valor "1" (LH) o "0" (HL). Así, el número de bits H en la porción P1 de datos es siempre igual a 1, y el bit de datos puede tener cualquier valor (0, 1) sin interferir con el ciclo de trabajo establecido.

La Figura 13B es un diagrama comparable con la Figura 12B, que ilustra la forma del filtro de un filtro de case adecuada para detectar el contenido de datos de la señal. Esta forma de filtro tiene un valor +1 durante el segundo segmento CS2 de la porción P1 de datos, tiene valor -1 durante el cuarto segmento CS4 de la porción P1 de datos, y tiene valor 0 durante el primer, tercero y quintos segmentos de la porción P1 de datos y durante la porción P2 del ciclo de trabajo. El valor ≥0 de salida de este filtro representa la decodificación de un "0", valor de salida menor que cero de este filtro representa la decodificación de un "1".

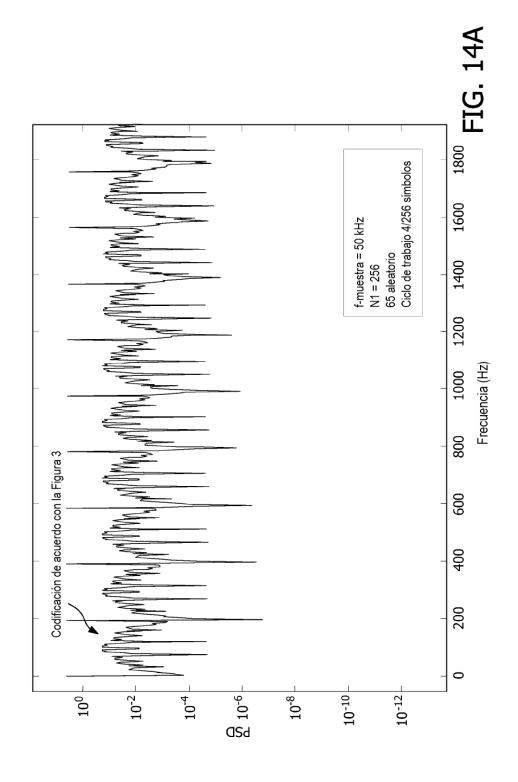

Las Figuras 14A-C son graficas que ilustran el contenido espectral de la señal S<sub>D</sub> para el esquema de codificación de acuerdo a la Figura 3A-B (Figura 14A), el esquema de codificación de acuerdo a la Figura 12A (Figura 14B) y el esquema de codificación de acuerdo a la Figura 13A (Figura 14C) puede ser claramente visto. Se puede ver de

manera clara que en el caso del esquema de codificación de acuerdo a las Figuras 12A y 13A, el contenido espectral es inferior, especialmente a frecuencias inferiores, comparado con el caso del esquema de codificación de acuerdo a la Figura 3A-B.