# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 625 275

61 Int. Cl.:

**H04L 25/03** (2006.01) **H03H 21/00** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 27.09.2012 PCT/CN2012/082224

(87) Fecha y número de publicación internacional: 03.04.2014 WO14047854

96 Fecha de presentación y número de la solicitud europea: 27.09.2012 E 12885440 (3)

(97) Fecha y número de publicación de la concesión europea: 29.03.2017 EP 2897334

(54) Título: Método y sistema de filtrado adaptativo basado en una sub-banda de error

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 19.07.2017

(73) Titular/es:

HUAWEI TECHNOLOGIES CO., LTD. (100.0%) Huawei Administration Building, Bantian Longgang District, Shenzhen, Guangdong 518129, CN

(72) Inventor/es:

SHI, DONGYUAN; HE, DONGMEI y CAI, MENG

(74) Agente/Representante:

**LEHMANN NOVO, María Isabel**

## **DESCRIPCIÓN**

Método y sistema de filtrado adaptativo basado en una sub-banda de error

#### 5 CAMPO TÉCNICO

15

30

40

45

50

55

60

La presente invención se refiere al campo de tecnologías de procesamiento de señales y en particular, a un método de filtrado adaptativo y un sistema basado en una sub-banda de error.

#### 10 ANTECEDENTES DE LA INVENCIÓN

Un filtrado adaptativo se aplica ampliamente en campos tales como identificación de sistemas, cancelación de interferencias de ecos y ecualización de canales y un método más frecuentemente utilizado es un método de filtrado transversal ajustado por el algoritmo LMS (Least Mean Square, algoritmo de mínimos cuadrados). Más concretamente, un algoritmo adaptativo se utiliza para corregir automáticamente un vector de ponderación en función de una señal de error de estimación, de modo que la señal de error consiga una media de mínimos cuadrados; sin embargo, la convergencia del método disminuye a medida que aumenta el valor del factor de ponderación de un filtro.

Con el fin de mejorar la convergencia de un algoritmo del método de filtrado transversal ajustado por LMS, un banco de filtros de análisis se añade en una ruta de una señal de entrada, de modo que se reduzca la autocorrelación de la señal de entrada, con lo que se mejora la convergencia del algoritmo. Sin embargo, puesto que la señal de entrada pasa a través de un grupo de filtros de análisis, se necesita, además, un grupo de filtros integrados para restablecer la señal cuando funciona el grupo de filtros; de esta manera, aumenta, en gran medida, la complejidad de una estructura del dispositivo de filtrado adaptativo, con lo que se aumenta la cantidad de cálculo de un algoritmo de filtrado adaptativo completo, por lo que es difícil aplicar el algoritmo de filtrado adaptativo a un sistema digital de procesamiento de alta velocidad.

El documento GB 2439988 A da a conocer un filtro adaptativo que tiene un conjunto de filtros de sub-banda para descomponer la señal entrante y la señal de error en varias señales de sub-banda y que genera ponderaciones de coeficientes de sub-banda a partir de las señales de sub-banda.

#### SUMARIO DE LA INVENCIÓN

La presente invención da a conocer un método de filtrado adaptativo de conformidad con la reivindicación 1 y un sistema en conformidad con la reivindicación 4 sobre la base de una sub-banda de error, con el fin de reducir la cantidad de cálculo de un algoritmo de filtrado adaptativo.

En conformidad con el método de filtrado adaptativo y el sistema basado en una sub-banda de error que se dan a conocer en las formas de realización de la presente invención, un procesamiento de filtrado de análisis se realiza sobre una señal de error y una señal de entrada con el fin de obtener una señal de sub-banda de error y una señal de sub-banda de entrada respectivamente; se realiza un cálculo en función de la señal de sub-banda de entrada y la señal de sub-banda de error para obtener una nueva ponderación de filtrado adaptativo, y se actualiza un factor de ponderación en un filtro adaptativo, de modo que cuando funciona el filtro adaptativo, el filtro adaptativo puede utilizar directamente una ponderación actualizada para realizar un procesamiento de filtro adaptativo sobre la señal de entrada, con el fin de obtener una señal de filtrado adaptativo. En comparación con una solución técnica en la técnica anterior, en donde el procesamiento de filtrado de análisis necesita realizarse primero sobre una señal de entrada, y un resultado del procesamiento se aplica a la entrada de un filtro adaptativo para realizar un procesamiento adaptativo con el fin de obtener una señal de sub-banda de filtrado adaptativo, y luego, se puede obtener una señal de filtrado adaptativo realizando un procesamiento de filtrado integrado sobre la señal de subbanda de filtrado adaptativo, en la presente invención, sin que exista necesidad de restablecer un resultado del procesamiento de un filtro adaptativo; en comparación con la solución técnica dada a conocer en la técnica anterior, se omite un filtro integrado para la reconstrucción de la señal, con lo que se reduce la cantidad de cálculo de un algoritmo de filtrado adaptativo.

## BREVE DESCRIPCIÓN DE LOS DIBUJOS

Para describir las soluciones técnicas en las formas de realización de la presente invención o en la técnica anterior con mayor claridad, a continuación se introducen, de forma concisa, los dibujos adjuntos requeridos para describir las formas de realización de la técnica anterior. Evidentemente, los dibujos adjuntos en la descripción siguiente muestran solamente algunas formas de realización de la presente invención y un experto en esta técnica puede derivar todavía otros dibujos a partir de estos dibujos adjuntos sin necesidad de esfuerzos creativos.

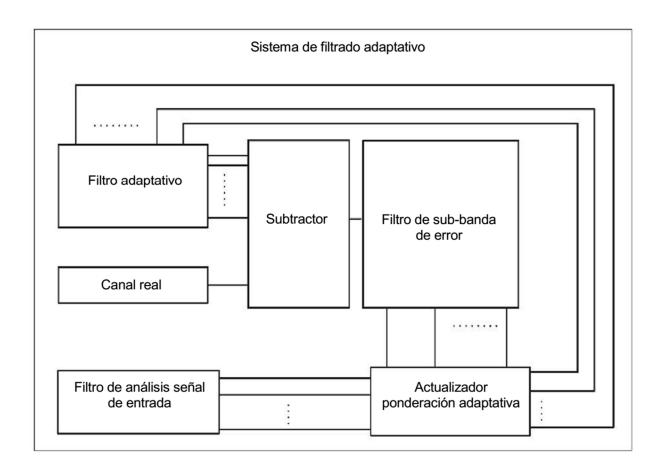

La Figura 1 es un diagrama de bloques de composición de un sistema de filtrado adaptativo sobre la base de una sub-banda de error en conformidad con la presente invención,

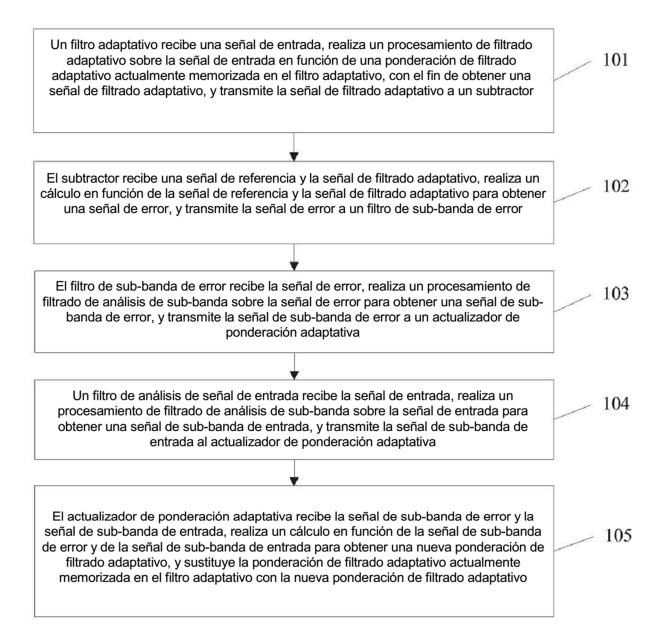

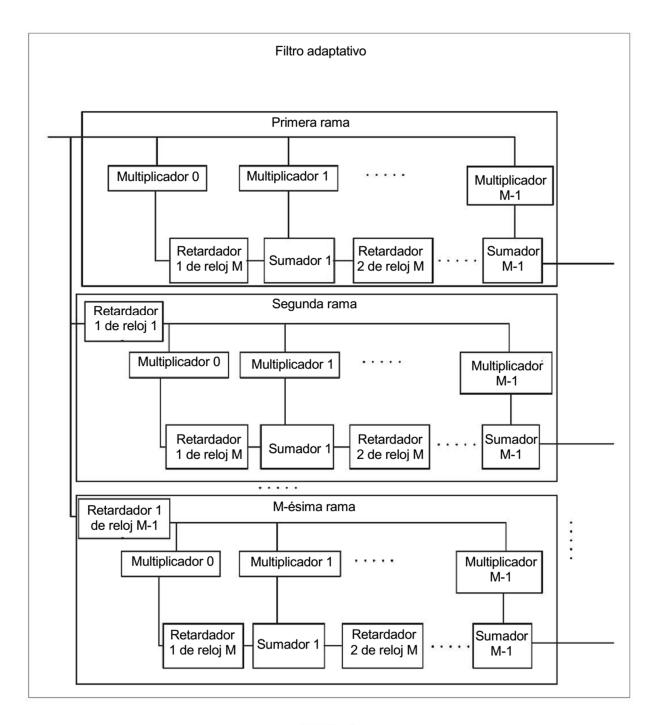

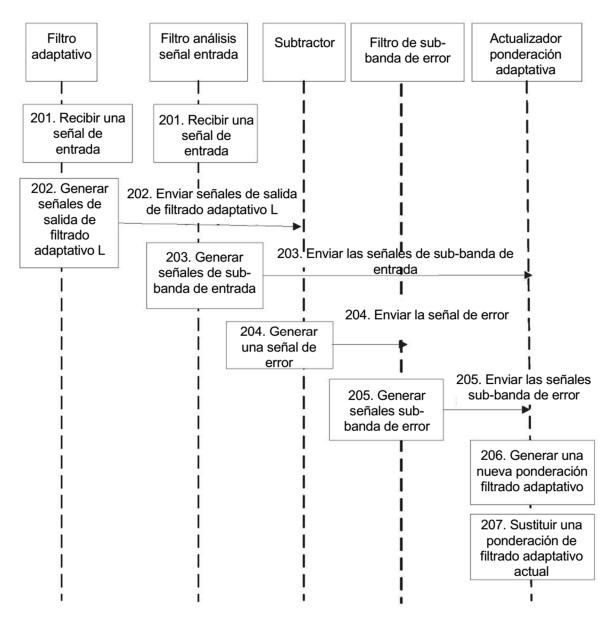

La Figura 2 es un diagrama de flujo de un método de filtrado adaptativo sobre la base de una sub-banda de error en conformidad con la forma de realización 1 de la presente invención;

La Figura 3 es un diagrama de flujo de otro método de filtrado adaptativo sobre la base de una sub-banda de error en conformidad con la forma de realización 1 de la presente invención;

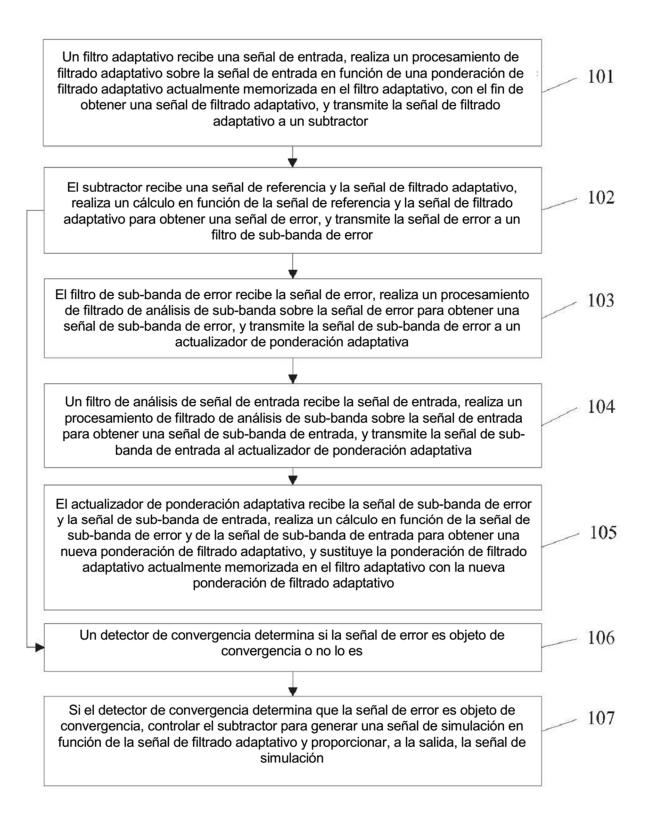

La Figura 4 es un diagrama de bloques de composición de un filtro adaptativo en conformidad con la presente invención.

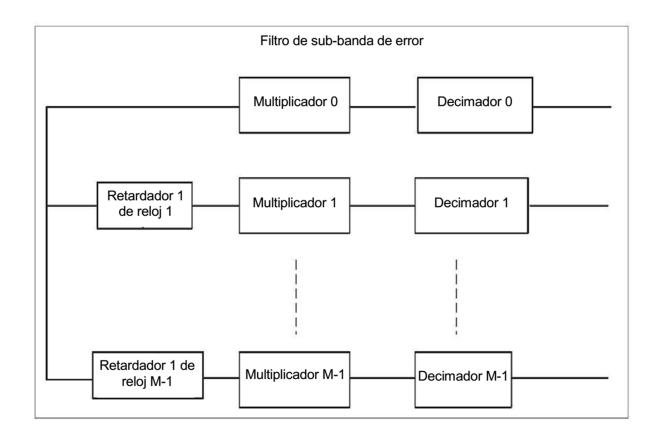

La Figura 5 es un diagrama de bloques de composición de un filtro de sub-banda de error en conformidad con la presente invención;

La Figura 6 es un diagrama de flujo de un método de filtrado adaptativo sobre la base de una sub-banda de error en conformidad con la forma de realización 2 de la presente invención;

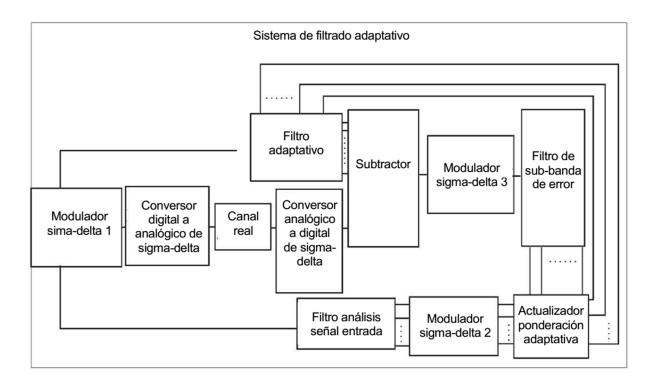

La Figura 7 es un diagrama de bloques de composición de un sistema de filtrado adaptativo sobre la base de una sub-banda de error en conformidad con la forma de realización 2 de la presente invención; y

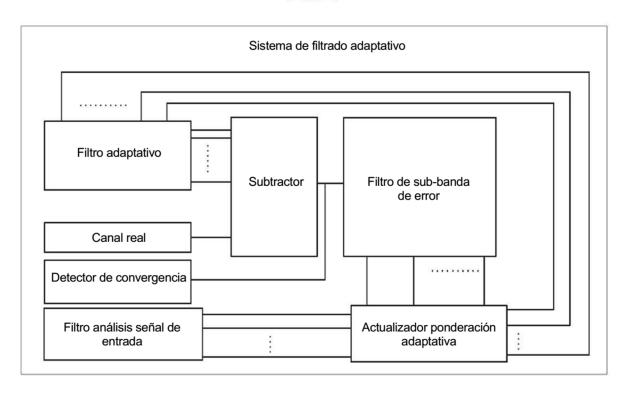

La Figura 8 es un diagrama de bloques d composición de un sistema de filtrado adaptativo sobre la base de una sub-banda de error en conformidad con la forma de realización 3 de la presente invención.

#### DESCRIPCIÓN DETALLADA DE LAS FORMAS DE REALIZACIÓN

A continuación se describe, de forma clara y completa, las soluciones técnicas de las formas de realización de la presente invención haciendo referencia a los dibujos adjuntos en dichas formas de realización de la presente invención. Evidentemente, las formas de realización descritas son simplemente una parte y no la totalidad de las formas de realización de la presente invención. Todas las demás formas de realización obtenidas por un experto en esta técnica, basadas en las formas de realización de la presente invención, sin necesidad de esfuerzos creativos, deberán caer dentro del alcance de protección de la presente invención.

#### Forma de realización 1

5

15

20

30

35

40

45

50

55

60

Esta forma de realización de la presente invención da a conocer un método de filtrado adaptativo sobre la base de una sub-banda de error, en donde el método puede aplicarse a un sistema de filtrado adaptativo ilustrado en la Figura 1, y el sistema incluye: un filtro adaptativo, un subtractor, un filtro de sub-banda de error, un filtro de análisis de señal de entrada y un actualizador de ponderación adaptativa.

Un puerto de entrada del filtro adaptativo está configurado para recibir una señal de entrada, y un puerto de salida del filtro adaptativo está conectado a un puerto de entrada del subtractor; el otro puerto de entrada del subtractor está configurado para recibir una señal de referencia, y un puerto de salida del subtractor está conectado al filtro de sub-banda de error; un puerto de entrada del filtro de análisis de la señal de entrada está configurado para recibir la señal de entrada, y un puerto de salida del filtro de análisis de señal de entrada está conectado a un puerto de entrada del actualizador de ponderación adaptativa; y un puerto de salida del filtro de sub-banda de error está conectado al otro puerto de entrada del actualizador de ponderación adaptativa.

La señal de entrada es una señal digital, que es una señal a procesarse por el filtro adaptativo; y la señal de referencia es una señal generada después de que la señal de entrada pase a través de un canal real, en donde el canal real puede ser un dispositivo de procesamiento de señal físico o puede ser una ruta de propagación de señal en el espacio libre, lo que no está limitado en esta forma de realización de la presente invención.

Según se ilustra en la Figura 2, sobre la base del sistema de filtrado adaptativo anterior, el método incluye:

101. Un filtro adaptativo recibe una señal de entrada, realiza un procesamiento de filtrado adaptativo sobre la señal de entrada en función del factor de ponderación del filtrado adaptativo actualmente memorizado en el filtro adaptativo, con el fin de obtener una señal de filtrado adaptativo y transmitir la señal de filtrado adaptativo a un subtractor.

Cuando el factor de ponderación de filtrado adaptativo actualmente memorizado en el filtro adaptativo no se actualiza por un actualizador de ponderación adaptativa, el factor de ponderación del filtrado adaptativo es un valor por defecto pre-memorizado, y un valor del valor por defecto puede ser un valor empírico en el campo técnico; después de que el actualizador de ponderación adaptativa actualice el coeficiente de ponderación del filtrado adaptativo actualmente memorizado en el filtro adaptativo, el factor de ponderación del filtrado adaptativo actualmente memorizado en el filtro adaptativo es un factor de ponderación de filtrado adaptativo actualizado.

Conviene señalar que la señal de filtro adaptativo no es simplemente una sola señal, y el número de señales de filtrado adaptativo depende del número derivaciones del filtro adaptativo. En el filtro adaptativo, una rama de

derivación del filtro adaptativo genera una señal de filtro adaptativo.

5

10

20

40

45

102. El subtractor recibe una señal de referencia y la señal de filtrado adaptativo, realiza un cálculo en función de la señal de referencia y de la señal de filtrado adaptativo con el fin de obtener una señal de error, y transmite la señal de error a un filtro de sub-banda de error.

103. El filtro de sub-banda de error recibe la señal de error, realiza un procesamiento de filtrado de análisis de sub-banda sobre la señal de error con el fin de obtener una señal de sub-banda de error, y transmite la señal de sub-banda de error a un actualizador de ponderación adaptativa.

Conviene señalar que la señal de sub-banda de error no es simplemente una sola señal, y el número de señales de sub-banda de error depende del número de divisiones de bandas de frecuencias del filtro de sub-banda de error. En el filtro de sub-banda de error, una rama del filtro de sub-banda de error genera una señal de sub-banda de error.

15 104. Un filtro de análisis de señal de entrada recibe la señal de entrada, realiza un procesamiento de filtrado de análisis de sub-banda sobre la señal de entrada para obtener una señal de sub-banda de entrada, y transmite la señal de sub-banda de entrada al actualizador de ponderación adaptativa.

Conviene señalar que la señal de sub-banda de entrada no es simplemente una sola señal, y el número de señales de sub-banda de entrada depende del número de divisiones de banda de frecuencia del filtro de análisis de señal de entrada. En el filtro de análisis de la señal de entrada, una rama del filtro de entrada genera M señales de sub-banda de entrada, en donde M es el número de divisiones de banda de frecuencia del filtro de análisis de señal de entrada.

105. El actualizador de ponderación adaptativa recibe la señal de sub-banda de error y la señal de sub-banda de entrada, realiza un cálculo en función de la señal de sub-banda de error y de la señal de sub-banda de entrada con el fin de obtener una nueva ponderación de filtrado adaptativo y sustituye a la ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo con la nueva ponderación de filtrado adaptativo.

Para un método de cálculo de la nueva ponderación de filtrado adaptativo, puede hacerse referencia a la fórmula a siguiente y dicha fórmula es concretamente:

$$\hat{s}_{ik}(n+1) = \hat{s}_{ik}(n) + 2\mu \sum_{l=0}^{M-1} \alpha_l e_l(n) x_{ll}(n-k)$$

$$i = 0, 1, ..., (M-1)$$

$$k = 0, 1, ..., (\frac{L}{M} - 1)$$

(Fórmula a)

en donde  $\hat{s}_{ik}$  (n+1) es una ponderación de filtrado adaptativo actualizada,  $\hat{s}_{ik}(n)$  es una ponderación de filtrado adaptativo actual,  $\mu$  y  $\alpha_i$  son ambas constantes prestablecidas, L es el número de derivaciones de un filtro adaptativo, M es el número de sub-bandas obtenido por medio de un procesamiento de filtrado de análisis,  $e_i$  (n), es un valor de señal de error de una primera rama y  $x_{ij}$  (n - k) es un valor de señal de entrada de una i-ésima componente de la primera rama.

Conviene señalar que cuando una diferencia entre una señal de salida real y una señal de salida de filtrado adaptativo, que se obtiene realizando un filtrado adaptativo sobre la señal de entrada utilizando la ponderación del filtrado adaptativo actual, fluctúa constantemente en un margen relativamente pequeño, es decir, cuando la señal de error es objeto de convergencia, con lo que puede considerarse que el filtro adaptativo puede simular un canal real. En este caso, necesita proporcionarse, a la salida, una señal del filtro adaptativo. Por lo tanto, las siguientes etapas están dispuestas después de la etapa 102 y según se ilustra en la Figura 3, el método incluye, además:

106. Un detector de convergencia determina si la señal de error es objeto de convergencia.

50 107. Si el detector de convergencia determina que la señal de error es objeto de convergencia, controlar el subtractor para generar una señal de simulación en conformidad con la señal de filtrado adaptativo y proporcionar, a la salida, la señal de simulación.

Más concretamente, un método de puesta en práctica en el que el detector de convergencia controla el subtractor para generar una señal de simulación en función de la señal de filtrado adaptativo puede ser: cuando existe solamente una señal de filtrado adaptativo única, controlar el subtractor para proporcionar directamente, a la salida, la señal adaptativa única como una señal de simulación; y cuando existen múltiples señales de filtrado adaptativo, realizar un cálculo de adición sobre las múltiples señales de filtrado adaptativo con el fin de obtener una señal de simulación.

Además, conviene señalar que esta forma de realización de la presente invención da a conocer un filtro adaptativo, y una estructura del filtro adaptativo se ilustra en la Figura 4. El filtro tiene L ramas que incluyen una primera rama a una L-ésima rama, y cada rama tiene un puerto de entrada y un puerto de salida, en donde L es un número entero positivo.

5

10

15

20

25

30

35

40

45

50

Cuando L es igual a 1, M multiplicadores, M-1 sumadores y M-1 retardadores de reloj M están dispuestos en la Lésima rama, en donde los M multiplicadores son un multiplicador 0 a un multiplicador M-1, los M-1 sumadores son un sumador 1 a un sumador M-1 y los M-1 retardadores de reloj M son un retardador 1 de reloj M a un retardador M-1 de reloj M; cada retardador tiene un puerto de entrada y un puerto de salida, cada multiplicador tiene un puerto de entrada y un puerto de salida, M es un número entero positivo, y un puerto de entrada de la L-ésima rama está conectado a puertos de entrada del multiplicador 0 al multiplicador M-1, un puerto de salida del multiplicador 0 está conectado a un puerto de entrada del retardador 1 de reloj M, un puerto de salida de cada uno de un multiplicador 1 al multiplicador M-1 está conectado a un puerto de entrada del retardador 1 de reloj M al retardador M-1 de reloj M está conectado al otro puerto de entrada del sumador 1 al sumador M-1.

A continuación, la recepción, por un filtro adaptativo, de una señal de entrada, la realización de un procesamiento de filtrado adaptativo sobre la señal de entrada en función de un factor de ponderación de filtrado adaptativo actualmente memorizado en el filtro adaptativo de manera que se obtenga una señal de filtrado adaptativo comprende:

En la L-ésima rama, recibir, por cada uno del multiplicador 0 al multiplicador M-1, la señal de entrada por intermedio del puerto de entrada de la L-ésima rama, y efectuar una multiplicación sobre la señal de entrada en función de un factor de ponderación de filtrado adaptativo memorizado en cada uno de los multiplicadores, con el fin de obtener una señal de salida de multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; proporcionar, a la salida, por cada uno del multiplicador 0 al multiplicador M-1, por intermedio de un puerto de salida de cada uno del multiplicador 0 al multiplicador M-1, la señal de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; efectuar, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, un procesamiento de retardo de reloj M sobre una señal recibida en un puerto de entrada de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, con el fin de obtener una señal de retardo de reloj M generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; proporcionar, a la salida, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, por intermedio del puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, la señal de retardo de reloj M generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; realizar, por el sumador 1 al sumador M-1, un procesamiento de adición sobre las señales recibidas por intermedio de dos puertos de entrada que corresponden a cada uno del sumador 1 al sumador M-1, con el fin de obtener una señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1, y proporcionar, a la salida, por cada uno del sumador 1 al sumador M-1, por intermedio de un puerto de salida correspondiente a cada uno del sumador 1 al sumador M-1, la señal de salida del sumador generada por cada uno del sumador 1 al sumador M-1.

Cuando L es mayor que 1, un retardador de reloj (L-1), M multiplicadores, M-1 sumadores y M-1 retardadores de reloj M están dispuestos en la L-ésima rama, en donde los M multiplicadores son un multiplicador 0 a un multiplicador M-1, los M-1 sumadores son un sumador 1 a un sumador M-1 y los M-1 retardadores de reloj M son un retardador 1 de reloj M a un retardador M-1 de reloj M; cada retardador tiene un puerto de entrada y puerto de salida, cada multiplicador tiene un puerto de entrada y un puerto de salida; y en la L-ésima rama, un puerto de entrada de la L-ésima rama está conectado a un puerto de entrada del retardador de reloj (L-1), un puerto de salida del retardador de reloj (L-1) está conectado a puertos de entrada de todos los multiplicadores, un puerto de salida del multiplicador 0 está conectado a un puerto de entrada del retardador 1 de reloj M, un puerto de salida de cada uno del multiplicador 1 al multiplicador M-1 está conectado a un puerto de entrada de cada uno del sumador 1 al sumador M-1, y un puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M está conectado al otro puerto de salida de cada uno del sumador 1 al sumador M-1.

- A continuación, la recepción, por un filtro adaptativo, de una señal de entrada, la realización de un procesamiento de filtrado adaptativo sobre la señal de entrada en función de un factor de ponderación de filtrado adaptativo actualmente memorizado en el filtro adaptativo, con el fin de obtener una señal de filtrado adaptativo que comprende:

- en la L-ésima rama, la recepción, por el retardador de reloj (L-1), de la señal de entrada por intermedio del puerto de entrada del retardador de reloj (L-1), y realizar un procesamiento de retardo de reloj (L-1) sobre la señal de entrada para generar una señal de retardo de reloj (L-1); proporcionar, a la salida, por el retardador de reloj (L-1), la señal de retardo de reloj (L-1) por intermedio del puerto de salida del retardador de reloj (L-1); la recepción, por cada uno del multiplicador 0 al multiplicador M-1, de la señal de retardo de reloj (L-1) por intermedio del puerto de entrada de la L-ésima rama, y realizar una multiplicación sobre la señal de retardo de reloj (L-1) en función de un factor de ponderación de filtrado adaptativo memorizado en cada uno de los multiplicadores, con el fin de obtener una señal

de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; proporcionar, a la salida, por cada uno del multiplicador 0 al multiplicador M-1 por intermedio de un puerto de salida de cada uno del multiplicador 0 al multiplicador M-1, la señal de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; realizar, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, un procesamiento de retardo de reloj M sobre una señal recibida en un puerto de entrada de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, con el fin de obtener una señal de retardo generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; proporcionar, a la salida, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M por intermedio del puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, la señal de retardo generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; realizar, por cada uno del sumador 1 al sumador M-1, un procesamiento de adición sobre las señales recibidas por intermedio de dos puertos de entrada correspondientes a cada uno del sumador 1 al sumador M-1, con el fin de obtener una señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1, y proporcionar, a la salida, por cada uno del sumador 1 al sumador M-1, por intermedio de un puerto de salida correspondiente a cada uno del sumador 1 al sumador M-1, la señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1.

15

10

Por supuesto, esta forma de realización de la presente invención no está limitada a que solamente pueda utilizarse una estructura del filtro adaptativo anterior para realizar un método de filtrado adaptativo sobre la base de una subbanda de error, y un filtro FIR (Respuesta Finita al Impulso) normalmente utilizado en el campo técnico puede utilizarse también para poner en práctica el método de filtrado adaptativo basado en una sub-banda de error.

20

Esta forma de realización de la presente invención da a conocer, además, un filtro de sub-banda de error y una estructura del filtro de sub-banda de error según se ilustra en la Figura 5. El filtro tiene N ramas que incluyen una primera rama a una N-ésima rama y cada rama tiene un puerto de entrada y un puerto de salida, en donde N es un número entero positivo.

25

Cuando X es igual a 1, un filtro de paso bajo, un multiplicador X-1 y un decimador X-1 están dispuestos en una Xésima rama; un puerto de entrada del filtro de paso bajo está conectado a un puerto de entrada de la X-ésima rama. un puerto de salida del filtro de paso bajo está conectado a un puerto de entrada del multiplicador X-1, un puerto de salida del multiplicador X-1 está conectado al decimador X-1 y un puerto de salida del decimador X-1 está conectado a un puerto de salida de la X-ésima rama.

30

A continuación, la recepción, por el filtro de sub-banda de error, de la señal de error, la realización de un procesamiento de filtrado de análisis de sub-banda sobre la señal de error para obtener una señal de sub-banda de error, que comprende:

35

40

recibir, por el filtro de paso bajo, la señal de error por intermedio del puerto de entrada del filtro de paso bajo, y realizar un procesamiento de filtrado sobre la señal de error en función del ajuste de paso de banda del filtro de paso bajo para obtener una señal de filtro de paso bajo; proporcionar, a la salida, por el filtro de paso bajo, la señal de filtro de paso bajo por intermedio del puerto de salida del filtro de paso bajo; realizar, por el multiplicador X-1, en función de un factor de ponderación memorizado en el multiplicador X-1, un procesamiento de multiplicación sobre una señal recibida por intermedio del puerto de entrada del multiplicador X-1, con el fin de obtener una señal de salida del multiplicador; proporcionar, a la salida, por el multiplicador X-1, la señal de salida del multiplicador por intermedio del puerto de salida del multiplicador X-1; realizar, por el decimador X-1, X veces un procesamiento de muestreo descendente sobre una señal recibida por intermedio de un puerto de entrada del decimador X-1, con el fin de obtener una señal de sub-banda de error de la X-ésima rama; y proporcionar, a la salida, por el decimador X-1, la señal de sub-banda de error de la X-ésima rama por intermedio del puerto de salida del decimador X-1.

45

50

Cuando X es mayor que 1 y menor que N-1, un filtro de paso de banda, un retardador de reloj (X-1), un multiplicador X-1 y un decimador X-1 están dispuestos en una X-ésima rama; un puerto de entrada del filtro de paso de banda está conectado a un puerto de entrada de la X-ésima rama, un puerto de salida del filtro de paso de banda está conectado a un puerto de entrada del retardador de reloj (X-1), un puerto de salida del retardador de reloj (X-1) está conectado a un puerto de entrada del multiplicador X-1, un puerto de salida del multiplicador X-1 está conectado al decimador X-1, y un puerto de salida del decimador X-1 está conectado a un puerto de salida de la X-ésima rama.

55

A continuación, la recepción, por el filtro de sub-banda de error, de la señal de error, la realización de un procesamiento de filtrado de análisis de sub-banda sobre la señal de error para obtener una señal de sub-banda de error, que comprende:

recibir, por el filtro de paso de banda, la señal de error por intermedio del puerto de entrada del filtro de paso de

60 banda, y realizar un procesamiento de filtrado sobre la señal de error en función del ajuste del paso de banda del

65

filtro de paso de banda con el fin de obtener una señal de filtro de paso de banda; proporcionar, a la salida, por el filtro de paso de banda, la señal de filtro de paso de banda por intermedio del puerto de salida del filtro de paso de banda; realizar, por el retardador de reloj (X-1), un procesamiento de retardo de reloj (X-1) sobre una señal recibida por intermedio del puerto de entrada del retardador de reloj (X-1), con el fin de obtener una señal de retardo; proporcionar, a la salida, por el retardador de reloj (X-1), la señal de retardo por intermedio del puerto de salida del retardador de reloj (X-1); realizar, por el multiplicador X-1 en función de un factor de ponderación memorizado en el multiplicador X-1, un procesamiento de multiplicación sobre una señal recibida por intermedio del puerto de entrada del multiplicador X-1, con el fin de obtener una señal de salida del multiplicador; proporcionar, a la salida, por el multiplicador X-1, la señal de salida del multiplicador por intermedio del puerto de salida del multiplicador X-1; realizar, por el decimador X-1, X veces un procesamiento de muestreo descendente sobre una señal recibida por intermedio de un puerto de entrada del decimador X-1, con el fin de obtener una señal de sub-banda de error de la X-ésima rama; y proporcionar, a la salida, por el decimador X-1, la señal de sub-banda de error de la X-ésima rama por intermedio del puerto de salida del decimador X-1.

Cuando X es igual a N, un filtro de paso alto, un retardador de reloj (X-1), un multiplicador X-1 y un decimador X-1 están dispuestos en una X-ésima rama; un puerto de entrada del filtro de paso alto está conectado a un puerto de entrada de la X-ésima rama, un puerto de salida del filtro de paso alto está conectado a un puerto de entrada del retardador de reloj (X-1), un puerto de salida del retardador de reloj (X-1) está conectado a un puerto de entrada del multiplicador X-1, un puerto de salida del multiplicador X-1 está conectado al decimador X-1 y un puerto de salida del decimador X-1 está conectado a un puerto de salida del a X-ésima rama.

A continuación, la recepción, por el filtro de sub-banda de error, de la señal de error, realizar un procesamiento de filtrado de análisis de sub-banda sobre la señal de error para obtener al menos una señal de sub-banda de error, comprende:

20 recibir, por el filtro de paso alto, la señal de error por intermedio del puerto de entrada del filtro de paso alto, y realizar un procesamiento de filtrado sobre la señal de error en función del ajuste de paso alto del filtro de paso alto con el fin de obtener una señal de filtro de paso alto; proporcionar, a la salida, por el filtro de paso alto, la señal de filtro de paso alto por intermedio del puerto de salida del filtro de paso alto; realizar, por el retardador de reloj (X-1), un procesamiento de retardo de reloj (X-1) sobre una señal recibida por intermedio del puerto de entrada del 25 retardador de reloj (X-1), con el fin de obtener una señal de retardo; proporcionar, a la salida, por el retardador de reloj (X-1), la señal de retardo por intermedio del puerto de salida del retardador de reloj (X-1); realizar, por el multiplicador X-1 en función de un factor de ponderación memorizado en el multiplicador X-1, un procesamiento de multiplicación sobre una señal recibida por intermedio del puerto de entrada del multiplicador X-1, con el fin de obtener una señal de salida del multiplicador; proporcionar, a la salida, por el multiplicador X-1, la señal de salida del 30 multiplicador por intermedio del puerto de salida del multiplicador X-1; realizar, por el decimador X-1, X veces un procesamiento de muestreo descendente sobre una señal recibida por intermedio de un puerto de entrada del decimador X-1, con el fin de obtener una señal de sub-banda de error de la X-ésima rama; y proporcionar, a la salida, por el decimador X-1, una señal de sub-banda de error de la X-ésima rama por intermedio del puerto de salida del decimador X-1.

Por supuesto, esta forma de realización de la presente invención no está limitada a que solamente una estructura del filtro de sub-banda de error anterior pueda utilizarse para poner en práctica un método de filtrado adaptativo sobre una sub-banda de error y un filtro de análisis de sub-banda normalmente utilizado en el campo técnico puede emplearse también para poner en práctica el método de filtrado adaptativo en una sub-banda de error.

Además, una estructura del filtro de análisis de señal de entrada es similar a la estructura del filtro de sub-banda de error, y un método para el procesamiento de filtrado de análisis sobre una señal de entrada es también similar a un método de procesamiento de una señal de error por el filtro de sub-banda de error, que no se describe en detalle en esta forma de realización de la presente invención.

En conformidad con el método de filtrado adaptativo que está basado en una sub-banda de error y dado a conocer en esta forma de realización de la presente invención, se realiza un procesamiento de filtrado de análisis sobre una señal de error y una señal de entrada con el fin de obtener una señal de sub-banda de error y una señal de subbanda de entrada, respectivamente, se realiza un cálculo en función de la señal de sub-banda de entrada y de la señal de sub-banda de error con el fin de obtener un nuevo factor de ponderación de filtrado adaptativo, y un factor de ponderación en un filtro adaptativo es objeto de actualización, de modo que cuando funciona el filtro adaptativo, el filtro adaptativo puede utilizar directamente una ponderación actualizada para realizar un procesamiento de filtro adaptativo sobre la señal de entrada, con el fin de obtener una señal de filtrado adaptativo. En comparación con una solución técnica en la técnica anterior, en donde necesita realizarse primero un procesamiento de filtrado de análisis sobre una señal de entrada, y un resultado de procesamiento se aplica a la entrada de un filtro adaptativo para realizar un procesamiento adaptativo con el fin de obtener una señal de sub-banda de filtrado adaptativo, y luego, una señal de filtrado adaptativo puede obtenerse utilizando un procesamiento de filtrado integrado sobre la señal de sub-banda de filtrado adaptativo, en la presente invención, un resultado del procesamiento de un filtro adaptativo no necesita restablecerse; en comparación con la solución técnica dada a conocer en la técnica anterior, se omite un filtro integrado para reconstrucción de la señal, con lo que se reduce la cantidad de cálculo de un algoritmo de filtrado adaptativo.

# Forma de realización 2

5

10

15

35

40

45

50

55

60

Sobre la base de una descripción de una arquitectura del sistema que se ilustra en la Figura 1, en la que el número de sub-bandas es 2, se utiliza a modo de ejemplo en esta forma de realización de la presente invención para

describir específicamente un método de filtrado adaptativo que está basado en una sub-banda de error y se da a conocer en esta forma de realización de la presente invención. Según se ilustra en la Figura 6, el método incluye:

201. Un filtro adaptativo y un filtro de análisis de la señal de entrada reciben una señal de entrada x(n).

202. El filtro adaptativo realiza un procesamiento de filtrado adaptativo sobre x(n) en función de un factor de ponderación de filtrado adaptativo actual para generar L señales de salida de filtrado adaptativo  $y_0(n)$ ,  $y_1(n)$ , ..., e  $y_L(n)$ , y transmite las señales  $y_0(n)$ ,  $y_1(n)$ , ..., y  $y_L(n)$  a un subtractor.

10 L es el número de derivaciones del filtro adaptativo.

5

15

20

25

30

40

203. El filtro de análisis de señal de entrada realiza un procesamiento de filtrado de análisis de sub-banda sobre x(n) para obtener cuatro señales de sub-banda de entrada  $x_{00}(n)$ ,  $x_{01}(n)$ ,  $x_{10}(n)$ ,  $x_{11}(n)$ , y transmite las señales  $x_{00}(n)$ ,  $x_{01}(n)$ ,  $x_{10}(n)$ ,  $x_{11}(n)$ , y  $x_{11}(n)$  a un actualizador de ponderación adaptativa.

204. El subtractor recibe las señales  $y_0(n)$ ,  $y_1(n)$ , ...,  $y_{L}(n)$  y una señal de referencia d(n), obtiene una diferencia entre

$$\sum_{i=0}^{L} y_i(n)$$

y d(n) como una señal de error e(n) y transmite e(n) a un filtro de sub-banda de error.

205. El filtro de sub-banda de error realiza un procesamiento de filtrado de análisis sobre e(n) para obtener dos señales de sub-banda de error  $e_0(n)$  y  $e_1(n)$ , y transmite las señales  $e_0(n)$  y  $e_1(n)$  al actualizador de ponderación adaptativa.

206. El actualizador de ponderación adaptativa obtiene una nueva ponderación de filtrado adaptativo en función de  $x_{00}(n)$ ,  $x_{01}(n)$ ,  $x_{10}(n)$ ,  $x_{11}(n)$ ,  $e_0(n)$ , y  $e_1(n)$  con referencia a la fórmula 2 siguiente:

$$\hat{s}_{0k}(n+1) = \hat{s}_{0k}(n) + 2\mu[\alpha_0 e_0(n) x_{00}(n-k) + \alpha_1 e_1(n) x_{10}(n-k)]$$

$$\hat{s}_{1k}(n+1) = \hat{s}_{1k}(n) + 2\mu[\alpha_0 e_0(n) x_{01}(n-k) + \alpha_1 e_1(n) x_{11}(n-k)]$$

(Fórmula b)

en donde k es igual a 0, 1, ..., o  $\frac{L}{2}$  -1 .

35 207. El actualizador de ponderación adaptativa sustituye la ponderación de filtrado adaptativo actual en el filtro adaptativo con la nueva ponderación de filtrado adaptativo.

En esta forma de realización, un proceso de derivación de una fórmula de actualización del coeficiente de ponderación, es decir, la fórmula b, es específicamente como sigue:

Una función de coste un algoritmo de filtrado adaptativo se supone que es:

$$J = E\{\alpha_0 e_0^2(n) + \alpha_1 e_1^2(n)\}$$

(1)

45 entonces, la fórmula de actualización del coeficiente de ponderación puede expresarse como:

$$\hat{\mathbf{S}}_{m}(n+1) = \hat{\mathbf{S}}_{m}(n) - \mu \frac{\partial J}{\partial \hat{\mathbf{S}}_{m}(n)} \quad m = 0, 1 \quad (2)$$

en donde  $\hat{S}_m(n) = [\hat{s}_{m,1}, \hat{s}_{m2}, \dots, \hat{s}_{m,k}]^T$ ,  $k = 1, 2, \dots, L/2-1$ , y en la fórmula, L es un coeficiente de derivación de un filtro; y

$$\frac{\partial J}{\partial \hat{\mathbf{S}}_{m}(n)} = E\{2\alpha_{0}e_{0}(n)\frac{\partial e_{0}(n)}{\partial \hat{\mathbf{S}}_{m}(n)} + 2\alpha_{1}e_{1}(n)\frac{\partial e_{1}(n)}{\partial \hat{\mathbf{S}}_{m}(n)}\}, m = 1, 2$$

(3)

Una función de transferencia del filtro adaptativo es:

$$\hat{S}(z) = \hat{S}_0(z^2) + z^{-1} \hat{S}_1(z^2)$$

(4

5 una salida de señal mediante un filtro es:

$$Y(z) = X(z)\hat{S}(z) = X(z)\hat{S}_0(z^2) + X(z)z^{-1}\hat{S}_1(z^2)$$

(5)

una señal de error es:

10

15

20

25

$E(z) = D(z) - Y(z) \quad (6)$

en función de una relación entre la entrada y salida del filtro de sub-banda de error, pudiéndose obtener las expresiones siguientes:

$E_0(z) = \frac{1}{2} [E(z^{1/2}) H_0(z^{1/2}) + E(-z^{1/2}) H_0(-z^{1/2})]$   $E_1(z) = \frac{1}{2} [E(z^{1/2}) H_1(z^{1/2}) + E(-z^{1/2}) H_1(-z^{1/2})]$ (7)

$$E_{0}(z) = \frac{1}{2} \{ [D(z^{1/2}) + D(-z^{1/2})] H_{0}(z^{1/2})$$

$$-\hat{S}_{0}(z) [X(z^{1/2}) H_{0}(z^{1/2}) + X(-z^{1/2}) H_{0}(-z^{1/2})]$$

$$-\hat{S}_{1}(z) [X(z^{1/2}) z^{-1/2} H_{0}(z^{1/2}) + X(-z^{1/2}) (-z^{-1/2}) H_{0}(-z^{1/2})] \}$$

(8)

$$E_{1}(z) = \frac{1}{2} \{ [D(z^{1/2}) + D(-z^{1/2})] H_{1}(z^{1/2})$$

$$-\hat{S}_{0}(z) [X(z^{1/2}) H_{1}(z^{1/2}) + X(-z^{1/2}) H_{1}(-z^{1/2})]$$

$$-\hat{S}_{1}(z) [X(z^{1/2}) z^{-1/2} H_{1}(z^{1/2}) + X(-z^{1/2}) (-z^{-1/2}) H_{1}(-z^{1/2})] \}$$

(9)

puesto que

$$\frac{\partial E(z^{1/2})}{\partial \hat{S}_0(z)} = -X(z^{1/2}) \tag{10}$$

$$\frac{\partial E(-z^{1/2})}{\partial \hat{S}_0(z)} = -X(-z^{1/2}) \quad (11),$$

$$\frac{\partial E_{0}(z)}{\partial \hat{S}_{0}(z)} = -\frac{1}{2} [X(z^{1/2}) H_{0}(z^{1/2}) + X(-z^{1/2}) H_{0}(-z^{1/2})]

\frac{\partial E_{1}(z)}{\partial \hat{S}_{0}(z)} = -\frac{1}{2} [X(z^{1/2}) H_{1}(z^{1/2}) + X(-z^{1/2}) H_{1}(-z^{1/2})]

\frac{\partial E_{0}(z)}{\partial \hat{S}_{1}(z)} = -\frac{1}{2} [X(z^{-1/2}) z^{1/2} H_{0}(z^{1/2}) + X(-z^{1/2}) (-z^{-1/2}) H_{0}(-z^{1/2})]

\frac{\partial E_{1}(z)}{\partial \hat{S}_{1}(z)} = -\frac{1}{2} [X(z^{-1/2}) z^{1/2} H_{1}(z^{1/2}) + X(-z^{1/2}) (-z^{-1/2}) H_{1}(-z^{1/2})]$$

(12)

30 suponiendo

$$X'_{00} = -\frac{\partial E_0(z)}{\partial \, \hat{S}_0(z)} \quad , \quad X'_{10} = -\frac{\partial E_1(z)}{\partial \, \hat{S}_0(z)} \quad , \quad X'_{01} = -\frac{\partial E_0(z)}{\partial \, \hat{S}_1(z)} \quad , \quad X'_{11} = -\frac{\partial E_1(z)}{\partial \, \hat{S}_1(z)} \, , \label{eq:X'_00}$$

$$X'_{11} = -\frac{\partial E_1(z)}{\partial \hat{S}_1(z)},$$

5

$$\frac{\partial E_{0}(z)}{\partial \hat{S}_{0k}(z)} = -X'_{00} z^{-K}$$

$$\frac{\partial E_{1}(z)}{\partial \hat{S}_{0k}(z)} = -X'_{10} z^{-K}$$

$$\frac{\partial E_{0}(z)}{\partial \hat{S}_{1k}(z)} = -X'_{01} z^{-K}$$

$$\frac{\partial E_{0}(z)}{\partial \hat{S}_{1k}(z)} = -X'_{11} z^{-K}$$

$$\frac{\partial E_{1}(z)}{\partial \hat{S}_{1k}(z)} = -X'_{11} z^{-K}$$

y las formulas (8) y (9) pueden expresarse como:

(14)

10

$$E_{0}(z) = \frac{1}{2} [D(z^{1/2}) + D(-z^{1/2})] H_{0}(z^{1/2}) - \hat{S}_{0}(z) X'_{00}(z) - \hat{S}_{1}(z) X'_{01}(z)$$

$$E_{1}(z) = \frac{1}{2} [D(z^{1/2}) + D(-z^{1/2})] H_{0}(z^{1/2}) - \hat{S}_{0}(z) X'_{10}(z) - \hat{S}_{1}(z) X'_{11}(z)$$

15

con referencia a (14), (13), y (12), la fórmula (2) puede expresarse de nuevo como:

$$\hat{s}_{0k}(n+1) = \hat{s}_{0k}(n) + 2\mu[\alpha_0 E\{e_0(n)x_{00}(n-k)\} + \alpha_1 E\{e_1(n)x_{10}(n-k)\}]$$

20

$$\hat{s}_{1k}(n+1) = \hat{s}_{1k}(n) + 2\mu [\alpha_0 E\{e_0(n)x_{01}(n-k)\} + \alpha_1 E\{e_1(n)x_{11}(n-k)\}]$$

(15)

$$k = 1, 2, ..., \frac{L}{2} - 1$$

25

una fórmula de actualización de ponderación de un algoritmo LMS puede obtenerse sustituyendo un valor de referencia por un valor instantáneo:

$$\hat{s}_{0k}(n+1) = \hat{s}_{0k}(n) + 2\mu[\alpha_0 e_0(n) x_{00}(n-k) + \alpha_1 e_1(n) x_{10}(n-k)]$$

$$\hat{s}_{1k}(n+1) = \hat{s}_{1k}(n) + 2\mu[\alpha_0 e_0(n) x_{01}(n-k) + \alpha_1 e_1(n) x_{11}(n-k)]$$

(16)

de conformidad con las formulas (13) y (12), puede obtenerse lo siguiente:

$$X'_{00}(z) = \frac{1}{2} [X(z^{1/2})H_0(z^{1/2}) + X(-z^{1/2})H_0(-z^{1/2})]$$

$$X'_{10}(z) = \frac{1}{2} [X(z^{1/2})H_1(z^{1/2}) + X(-z^{1/2})H_1(-z^{1/2})]$$

$$X'_{01}(z) = \frac{1}{2} [X(z^{-1/2})z^{1/2}H_0(z^{1/2}) + X(-z^{1/2})(-z^{-1/2})H_0(-z^{1/2})]$$

$$X'_{11}(z) = \frac{1}{2} [X(z^{-1/2})z^{1/2}H_1(z^{1/2}) + X(-z^{1/2})(-z^{-1/2})H_1(-z^{1/2})]$$

$$(17)$$

En esta forma de realización, un proceso de derivación para convergencia del algoritmo de filtrado adaptativo incluye lo siguiente:

una descomposición de multifase se realiza sobre una función de transferencia S(z) de un canal real; entonces, se puede expresarse una señal de referencia como:

$$D(z) = X(z)S_0(z) + X(z)z^{-1}S_1(z)$$

(18)

la formula (6) puede expresarse como:

$$E(z) = X(z)[S_0(z^2) - \hat{S}_0(z^2)] + X(z)[z^{-1}S_1(z^2) - z^{-1}\hat{S}_1(z^2)]$$

(19)

suponiendo que  $V_0(z) = S_0(z) - \hat{S}_0(z)$  y  $V_1(z) = S_1(z) - \hat{S}(z)$ , la fórmula anterior puede expresarse ahora como:

$$E(z) = X(z)V_0(z^2) + X(z)z^{-1}V_1(z^2)$$

(20)

que se sustituye en (7), con lo que se obtiene lo siguiente:

$$E_0(z) = X_{00}(z)V_0(z) + X_{01}(z)V_0(z)$$

$$E_1(z) = X_{10}(z)V_0(z) + X_{11}(z)V_1(z)$$

(21)

una expresión en el dominio del tiempo en (21) es:

$$e_0(n) = \mathbf{x}_{00}^T(n)\mathbf{v}_0(n) + \mathbf{x}_{01}^T(n)\mathbf{v}_1(n)$$

$$e_1(n) = \mathbf{x}_{10}^T(n)\mathbf{v}_0(n) + \mathbf{x}_{11}^T(n)\mathbf{v}_1(n)$$

(22)

en donde

5

10

20

25

30

$$\mathbf{x}_{lk}^{T} = [x_{lk}(n), x_{lk}(n-1), ..., x_{lk}(n-L/2+1)], l, k = 1, 2;$$

puede obtenerse lo que sigue sustituyendo la fórmula anterior en la fórmula de actualización de ponderación (16):

$$\mathbf{v}_{0}(n+1) = \mathbf{v}_{0}(n) - 2\mu\alpha_{0}\mathbf{x}_{00}(n)\mathbf{x}_{00}^{T}(n)\mathbf{v}_{0}(n)$$

$$-2\mu\alpha_{0}\mathbf{x}_{00}(n)\mathbf{x}_{01}^{T}(n)\mathbf{v}_{1}(n)$$

$$-2\mu\alpha_{1}\mathbf{x}_{10}(n)\mathbf{x}_{10}^{T}(n)\mathbf{v}_{0}(n)$$

$$-2\mu\alpha_{1}\mathbf{x}_{10}(n)\mathbf{x}_{11}^{T}(n)\mathbf{v}_{1}(n)$$

(23)

$$\mathbf{v}_{1}(n+1) = \mathbf{v}_{1}(n) - 2\mu\alpha_{0}\mathbf{x}_{01}(n)\mathbf{x}_{00}^{T}(n)\mathbf{v}_{0}(n)$$

$$-2\mu\alpha_{0}\mathbf{x}_{01}(n)\mathbf{x}_{01}^{T}(n)\mathbf{v}_{1}(n)$$

$$-2\mu\alpha_{1}\mathbf{x}_{11}(n)\mathbf{x}_{10}^{T}(n)\mathbf{v}_{0}(n)$$

$$-2\mu\alpha_{1}\mathbf{x}_{11}(n)\mathbf{x}_{11}^{T}(n)\mathbf{v}_{1}(n)$$

(24)

Las formulas (23) y (24) se expresan en una forma de un vector como sigue:

$$\begin{bmatrix} \mathbf{v}_0(n+1) \\ \mathbf{v}_1(n+1) \end{bmatrix} = \begin{bmatrix} \mathbf{v}_0(n) \\ \mathbf{v}_1(n) \end{bmatrix} - 2\mu[\alpha_0 \mathbf{A}_0 + \alpha_1 \mathbf{A}_1] \begin{bmatrix} \mathbf{v}_0(n) \\ \mathbf{v}_1(n) \end{bmatrix}$$

(25)

en donde

5

10

25

30

35

40

45

$\mathbf{A}_{0} = \begin{bmatrix} \mathbf{x}_{00}(n)\mathbf{x}_{00}^{T}(n) & \mathbf{x}_{00}(n)\mathbf{x}_{01}^{T}(n) \\ \mathbf{x}_{01}(n)\mathbf{x}_{00}^{T}(n) & \mathbf{x}_{01}(n)\mathbf{x}_{01}^{T}(n) \end{bmatrix}$ (26)

$$\mathbf{A}_{1} = \begin{bmatrix} \mathbf{x}_{10}(n)\mathbf{x}_{10}^{T}(n) & \mathbf{x}_{10}(n)\mathbf{x}_{11}^{T}(n) \\ \mathbf{x}_{11}(n)\mathbf{x}_{10}^{T}(n) & \mathbf{x}_{11}(n)\mathbf{x}_{11}^{T}(n) \end{bmatrix}$$

(27)

para (25), un valor medio se toma como sigue:

$E\begin{bmatrix} \mathbf{v}_0(n+1) \\ \mathbf{v}_1(n+1) \end{bmatrix} = E\begin{bmatrix} \mathbf{v}_0(n) \\ \mathbf{v}_1(n) \end{bmatrix} - 2\mu E[\alpha_0 \mathbf{A}_0 + \alpha_1 \mathbf{A}_1] E\begin{bmatrix} \mathbf{v}_0(n) \\ \mathbf{v}_1(n) \end{bmatrix}$ (28)

suponiendo  $\Phi = E[\alpha_0 A_0 + \alpha_1 A_1],$

15 la fórmula anterior puede expresarse como la expresión clásica siguiente:

$$\varepsilon(n+1) = [1 - 2\mu\Phi]\varepsilon(n) \quad (29)$$

en este caso,  $x_{00}$  (n),  $x_{01}$  (n),  $x_{10}$  (n), y  $x_{11}$  (n) son componentes analíticas de x y tienen diferentes componentes espectrales y un producto interior de  $x_{00}$  (n),  $x_{01}$ (n),  $x_{10}$  (n), y  $x_{11}$  (n) es cero; por lo tanto,  $x_{00}$  (n),  $x_{01}$  (n),  $x_{10}$ (n), y  $x_{11}$ (n) no están en correlación. A continuación, puede conocerse que  $A_0$ ,  $A_1$ , y  $\Phi$  son matrices diagonales definidas positivas.

Un valor de croquis de Φ se supone como:

$\lambda_1 \le \lambda_2 \le \dots \le \lambda_L \tag{30}$

entonces, una condición para la convergencia del algoritmo de filtrado adaptativo es:

$$0 < \mu < \frac{1}{\lambda_{\tau}}$$

(31)

En esta forma de realización, se realiza una descripción solamente suponiendo que el número de sub-bandas es 2; sin embargo, un algoritmo de filtrado adaptativo que está basado en una sub-banda de error y se da a conocer en esta forma de realización de la presente invención no está limitado a un procesamiento basado en solamente dos sub-bandas. Si el número de sub-bandas se amplía a M, una condición de convergencia del algoritmo de filtrado adaptativo es como sigue:

En primer lugar, se realiza una descomposición de multifase del grupo M sobre un filtro de estimación  $\hat{S}(z)$ :

$$\hat{S}(z) = \hat{S}_0(z^M) + z^{-1} \hat{S}_2(z^M) + \dots + z^{-M-1} \hat{S}_{M-1}(z^M)$$

(32)

en este caso, una función de coste es:

$$J(n) = E\{\alpha_0 e_0^2(n) + \alpha_1 e_1^2(n) + \dots + \alpha_{M-1} e_{M-1}^2(n)\}$$

(33)

y una fórmula de actualización de ponderación de  $\hat{S}(z)$  es:

$$\hat{s}_{ki}(n+1) = \hat{s}_{ki}(n) + 2\mu \sum_{l=0}^{M-1} \alpha_l e_l(n) x_{lk}(n-l)$$

$$k = 0, 1, \dots, (M-1)$$

$$i = 0, 1, \dots, (\frac{L}{M} - 1)$$

(34)

L es el número de derivaciones de  $\hat{S}(z)$ . La fórmula (28) puede ampliarse como:

$$E\begin{bmatrix} \mathbf{v}_{0}(n+1) \\ \mathbf{v}_{1}(n+1) \\ \vdots \\ \mathbf{v}_{M-1}(n+1) \end{bmatrix} = [\mathbf{I}_{L} - 2\mu\mathbf{\Phi}]E\begin{bmatrix} \mathbf{v}_{0}(n) \\ \mathbf{v}_{1}(n) \\ \vdots \\ \mathbf{v}_{M-1}(n) \end{bmatrix}$$

(35)

$$\mathbf{\Phi} = \alpha_0 \mathbf{\Phi}_0 + \alpha_1 \mathbf{\Phi}_1 + \dots + \alpha_{M-1} \mathbf{\Phi}_{M-1}$$

(36)

en donde

5

10

15

20

30

$$\Phi_{k} = E \begin{bmatrix} x_{k0}(n) \\ x_{k1}(n) \\ \vdots \\ x_{k,M-1}(n) \end{bmatrix} \begin{bmatrix} x_{k0}^{T}(n) & x_{k1}^{T}(n) & \cdots & x_{k,M-1}^{T}(n) \end{bmatrix}$$

$$K = 0.1.\dots(M-1)$$

(37)

en este caso, una condición de convergencia es:

$$1 < \mu < \frac{1}{\lambda_{\max}} \tag{38}$$

para facilidad de descripción, se supone, en este caso, que una longitud de  $\hat{S}(n)$  es 8, y el número de sub-bandas es 4.

$$\mathbf{\Phi} = \sum_{k=0}^{s} \alpha_k \mathbf{\Phi}_k \qquad (39)$$

$$\mathbf{\Phi} = \begin{pmatrix} \mathbf{x}_{k0} \\ \mathbf{x}_{k1} \\ \mathbf{x}_{k2} \\ \mathbf{x}_{k3} \end{pmatrix} \begin{bmatrix} \mathbf{x}_{k0}^T & \mathbf{x}_{k1}^T & \mathbf{x}_{k2}^T & \mathbf{x}_{k3}^T \end{bmatrix}$$

(40)

25 en donde

$$\mathbf{x}_{i,l}(n) = [b_i(l+4n) \quad b_i(l+4n+4)]^T$$

(41)

suponiendo

$$r_{k}(m) = E[b_{k}(n)b_{k}(n+m)]$$

(42),

$$\Phi_{k} = \begin{bmatrix}

r_{k}(0) & r_{k}(4) & r_{k}(1) & r_{k}(5) & r_{k}(2) & r_{k}(6) & r_{k}(3) & r_{k}(7) \\

r_{k}(4) & r_{k}(0) & r_{k}(3) & r_{k}(1) & r_{k}(2) & r_{k}(2) & r_{k}(1) & r_{k}(3) \\

r_{k}(1) & r_{k}(3) & r_{k}(0) & r_{k}(4) & r_{k}(1) & r_{k}(5) & r_{k}(2) & r_{k}(6) \\

\vdots & \vdots \\

\vdots & \vdots \\

r_{k}(7) & r_{k}(3) & r_{k}(6) & r_{k}(2) & r_{k}(5) & r_{k}(1) & r_{k}(4) & r_{k}(0)

\end{bmatrix} (43)$$

En este caso, se supone que las funciones de transferencia de cuatro ramas del filtro de sub-banda de error son  $H_0$

$(e^{j\omega})$ ,  $H_1$   $(e^{j\omega})$ ,  $H_2$   $(e^{j\omega})$ , y  $H_3$   $(e^{j\omega})$ , cuyos anchos de banda son  $\pi/4$ . Suponiendo que una banda de paso de  $H(e^{j\omega})$  es  $[-\pi/8, \pi/8]$  y una ganancia de banda de paso es 1, se puede obtener un grupo de filtros mediante traslación del filtro.

$$H_k(e^{j\omega}) = H(e^{(j(\omega - \omega_k))}) + H(e^{(j(\omega + \omega_k))})$$

(44)

en donde

5

10

20

30

40

$$\omega_k = (2k+1)(\pi/8), k = 0,1,2,3$$

(45)

Una función de densidad de espectro de potencia de x(n) se supone como:

$$P_{x}(e^{j\omega}) = \sum_{k=0}^{3} r_{k} \left( P(e^{j(\omega - \omega_{k})}) + P(e^{j(\omega + \omega_{k})}) \right)$$

(46)

15 en donde una ganancia de  $P(e^{i\omega})$  en el ancho de banda es 1, y el ancho de banda es  $[-\pi/8, \pi/8]$ .

Entonces, una función del espectro de potencia de b(n) es:

$$P_{k}(e^{j\omega}) = P_{k}(e^{j\omega})\{|H(e^{j(\omega-\omega_{k})})|^{2} + |H(e^{j(\omega-\omega_{k})})|^{2}\}$$

(47)

$P(e^{j\omega})$  y  $H(e^{j\omega})$  tienen una misma propiedad, y por lo tanto, (47) puede expresarse también como:

$$P_{k}(e^{j\omega}) = P_{k}(e^{j\omega})r_{k}(P(e^{j(\omega-\omega_{k})}) + P(e^{j(\omega-\omega_{k})}))$$

(48)

25 Una transformada de Fourier inversa se realiza en la fórmula anterior:

$$r_k(n) = 2r_k p(n) \cos(\omega_k n)$$

(49)

p(n) es la transformada de Fourier inversa de  $P(e^{j\omega})$ .

Suponiendo

$$q(n) = \sum_{k=0}^{3} \alpha_k r_k(n) \qquad (50)$$

35 entonces

$$\Phi = \begin{bmatrix}

q(0) & q(4) & q(1) & q(5) & q(2) & q(6) & q(3) & q(7) \\

q(4) & q(0) & q(3) & q(1) & q(2) & q(2) & q(1) & q(3) \\

q(1) & q(3) & q(0) & q(4) & q(1) & q(5) & q(2) & q(6) \\

\vdots & \vdots \\

\vdots & \vdots \\

q(7) & q(3) & q(6) & q(2) & q(5) & q(1) & q(4) & q(0)

\end{bmatrix} (51)$$

suponiendo que  $\alpha_k$  es igual a c /  $r_k$ , entonces

$$q(n) = 2cp(n) \sum_{k=0}^{3} \cos(\omega_k n)$$

(52)

Puesto que  $\omega_k = (2k+1)/(\pi/8)$ , k = 0, 1, 2, 3, cuando n = 8m, m = ... -2, -1,0,1,2,...

$$\sum_{k=0}^{3}\cos(\omega_{k}n)$$

no es igual a 0; además, puesto que una función senoidal p(n) es igual a 0 cuando n = 8m, m = ... - 2, -1,1,2,... q(n) no es igual a 0 solamente cuando n=0; entonces,  $\Phi = q$  (0)I. Por lo tanto, el algoritmo tiene una convergencia adecuada. Puede deducirse de la fórmula anterior que el número de condiciones de una matriz de autocorrelación de señal es 1 (un valor de croquis máximo de la matriz dividido por un valor de croquis mínimo de la matriz); sin embargo, el número de condiciones de una matriz de autocorrelación de entrada de un algoritmo de filtrado adaptativo es mayor que 1. De conformidad con una teoría de un algoritmo adaptativo, puede deducirse que una velocidad de convergencia de filtrado adaptativo disminuye cuando aumenta el número de condiciones de una matriz de autocorrelación. Por lo tanto, una velocidad de convergencia de filtrado adaptativo sobre la base de una sub-banda de error es más elevada.

Además, conviene señalar que el método del filtrado adaptativo que está basado en una sub-banda de error y dado a conocer en esta forma de realización de la presente invención, podrá no solamente utilizarse para simular un canal digital, sino que también podrá usarse para simular un canal analógico. Si ha de simularse un canal digital, el método de filtrado adaptativo que está basado en una sub-banda de error y dado a conocer en esta forma de realización de la presente invención podrá utilizarse directamente. Si ha de simularse un canal analógico, un sistema de Sigma-Delta necesita introducirse además en esta forma de realización de la presente invención, y el sistema incluye: un modulador de Sigma-Delta, configurado para realizar un sobremuestreo sobre una señal de entrada analógica a una velocidad más elevada que una tasa de muestreo de Nyquist; un conversor de digital a analógico de Sigma-Delta, configurado para realizar una conversión de digital a analógico sobre los datos; y un conversor de analógico a digital de Sigma-Delta, configurado para realizar una conversión de analógico a digital sobre los datos. Un sistema de filtrado adaptativo, en el que se introduce el sistema Sigma-Delta, se ilustra en la Figura 7.

En conformidad con el método de filtrado adaptativo que está basado en una sub-banda de error y dado a conocer en esta forma de realización de la presente invención, se realiza un procesamiento de filtrado de análisis sobre una señal de error y una señal de entrada con el fin de obtener una señal de sub-banda de error y una señal de sub-banda de entrada, respectivamente; se realiza un cálculo en función de la señal de sub-banda de entrada y la señal de sub-banda de error con el fin de obtener una nueva ponderación de filtrado adaptativo, y se actualiza un factor de ponderación en un filtro adaptativo, de modo que cuando funciona el filtro adaptativo, el filtro adaptativo puede utilizar directamente una ponderación actualizada para realizar un procesamiento de filtro adaptativo sobre la señal de entrada, con el fin de obtener una señal de filtrado adaptativo. En comparación con una solución técnica en la técnica anterior, en la que necesita realizarse primero un procesamiento de filtrado de análisis sobre una señal de entrada, y un resultado de procesamiento se aplica como entrada a un filtro adaptativo para realizar un procesamiento adaptativo para obtener una señal de sub-banda de filtrado adaptativo y entonces, puede obtenerse una señal de filtrado adaptativo, en la presente invención, no necesita restablecerse un resultado del procesamiento de un filtro adaptativo; en comparación con la solución técnica proporcionada en la técnica anterior, se omite un filtro integrado para reconstrucción de la señal, con lo que se reduce la cantidad de cálculo de un algoritmo de filtrado adaptativo.

## Forma de realización 3

10

15

20

25

30

35

40

45

50

55

60

Esta forma de realización de la presente invención da a conocer un sistema de filtrado adaptativo basado en una sub-banda de error. Haciendo referencia a la Figura 1, el sistema incluye: un filtro adaptativo, un subtractor, un filtro de sub-banda de error, un filtro de análisis de señal de entrada y un actualizador de ponderación adaptativa.

El filtro adaptativo está configurado para recibir una señal de entrada, realizar un procesamiento de filtrado adaptativo sobre la señal de entrada en función de una ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo, con el fin de obtener una señal de filtrado adaptativo, y para transmitir la señal de filtrado adaptativo al subtractor.

El subtractor está configurado para recibir una señal de referencia y la señal de filtrado adaptativo, para realizar un cálculo en función de la señal de referencia y de la señal de filtrado adaptativo con el fin de obtener una señal de error y para transmitir la señal de error al filtro de sub-banda de error, en donde la señal de referencia es una señal generada después de que la señal de entrada pase a través de un canal real.

El filtro de sub-banda de error está configurado para recibir la señal de error, para realizar un procesamiento de filtrado de análisis de sub-banda sobre la señal de error con el fin de obtener una señal de sub-banda de error y para transmitir la señal de sub-banda de error al actualizador de ponderación adaptativa.

El filtro de análisis de señal de entrada está configurado para recibir la señal de entrada, para realizar un procesamiento de filtrado de análisis de sub-banda sobre la señal de entrada con el fin de obtener una señal de sub-banda de entrada y transmitir la señal de sub-banda de entrada al actualizador de ponderación adaptativa.

El actualizador de ponderación adaptativa está configurado para recibir la señal de sub-banda de error y la señal de sub-banda de entrada, para realizar un cálculo en función de la señal de sub-banda de error y la señal de sub-banda de entrada con el fin de obtener un nueva ponderación de filtrado adaptativo y para sustituir la ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo con la nueva ponderación de filtrado adaptativo.

5

10

De modo opcional, haciendo referencia a la Figura 4, el filtro adaptativo anterior tiene L ramas que incluyen una primera rama a una L-ésima rama, y cada rama tiene un puerto de entrada y un puerto de salida, en donde L es un número entero positivo;

cuando L es igual a 1, M multiplicadores, M-1 sumadores y M-1 retardadores de reloj M están dispuestos en la L-

15

ésima rama, en donde los M multiplicadores son un multiplicador 0 a un multiplicador M-1, los M-1 sumadores son un sumador 1 a un sumador M-1 y los M-1 retardadores de reloj M son un retardador 1 de reloj M a un retardador M-1 de reloj M; cada retardador tiene un puerto de entrada y un puerto de salida, cada multiplicador tiene un puerto de entrada y un puerto de salida, M es un número entero positivo, y un puerto de entrada de la L-ésima rama está conectado a puertos de entrada del multiplicador 0 al multiplicador M-1, un puerto de salida del multiplicador 0 está conectado a un puerto de entrada del retardador 1 de reloj M, un puerto de salida de cada uno de un multiplicador 1 al multiplicador M-1 está conectado a un puerto de entrada de retardador 1 de reloj M al retardador M-1 de reloj M está conectado al otro puerto de salida de cada uno del sumador 1 al sumador M-1; γ

20

25

cuando L es mayor que 1, un retardador de reloj (L-1), M multiplicadores, M-1 sumadores y M-1 retardadores de reloj M están dispuestos en la L-ésima rama, en donde los M multiplicadores son un multiplicador 0 a un multiplicador M-1, los M-1 sumadores son un sumador 1 a un sumador M-1 y los M-1 retardadores de reloj M son un retardador 1 de reloj M a un retardador M-1 de reloj M; cada retardador tiene un puerto de entrada y puerto de salida, cada multiplicador tiene un puerto de entrada y un puerto de salida; y en la L-ésima rama, un puerto de entrada de la L-ésima rama está conectado a un puerto de entrada del retardador de reloj (L-1), un puerto de salida del retardador de reloj (L-1) está conectado a puertos de entrada de todos los multiplicadores, un puerto de salida del multiplicador 0 está conectado a un puerto de entrada del retardador 1 de reloj M, un puerto de salida de cada uno de un multiplicador 1 al multiplicador M-1 está conectado a un puerto de entrada de cada uno del sumador M-1, y un puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M está conectado al otro puerto de entrada de cada uno del sumador 1 al sumador M-1.

30

De modo opcional, haciendo referencia a la Figura 5, el filtro de sub-banda de error anterior tiene N ramas que incluyen una primera rama a una N-ésima rama, y cada rama tiene un puerto de entrada y un puerto de salida, en donde N es un número entero positivo;

35

40

cuando X es igual a 1, un filtro de paso bajo, un multiplicador X-1 y un decimador X-1 están dispuestos en una X-ésima rama; un puerto de entrada del filtro de paso bajo está conectado a un puerto de entrada del a X-ésima rama, un puerto de salida del filtro de paso bajo está conectado a un puerto de entrada del multiplicador X-1, un puerto de salida del multiplicador X-1 está conectado a un puerto de salida del decimador X-1 está conectado a un puerto de salida del decimador X-1 está conectado a un puerto de salida de la X-ésima rama;

45

cuando X es mayor que 1 y menor que N-1, un filtro de paso de banda, un retardador de reloj (X-1), un multiplicador X-1 y un decimador X-1 están dispuestos en una X-ésima rama; un puerto de entrada del filtro de paso de banda está conectado a un puerto de entrada de la X-ésima rama, un puerto de salida del filtro de paso de banda está conectado a un puerto de entrada del retardador de reloj (X-1), un puerto de salida del retardador de reloj (X-1) está conectado a un puerto de entrada del multiplicador X-1, un puerto de salida del multiplicador X-1 está conectado al decimador X-1, y un puerto de salida del decimador X-1 está conectado a un puerto de salida de la X-ésima rama; y

50

cuando X es igual a N, un filtro de paso alto, un retardador de reloj (X-1), un multiplicador X-1 y un decimador X-1 están dispuestos en una X-ésima rama; un puerto de entrada del filtro de paso alto está conectado a un puerto de entrada del retardador de reloj (X-1), un puerto de salida del filtro de paso alto está conectado a un puerto de entrada del retardador de reloj (X-1), un puerto de salida del retardador de reloj (X-1) está conectado a un puerto de entrada del multiplicador X-1, un puerto de salida del multiplicador X-1 está conectado a un puerto de salida del decimador X-1 está conectado a un puerto de salida del A X-ésima rama.

55

De modo opcional, según se ilustra en la Figura 8, el sistema incluye, además, un detector de convergencia.

60

El detector de convergencia está configurado para determinar si la señal de error es objeto de convergencia; y si se determina que la señal de error es objeto de convergencia, controlar el subtractor para generar una señal de simulación en función de la señal de filtrado adaptativo y proporcionar, a la salida, la señal de simulación.

65

En conformidad con el aparato de filtrado adaptativo que está basado en una sub-banda de error y dado a conocer en esta forma de realización de la presente invención, se realiza un procesamiento de filtrado de análisis sobre una señal de error y una señal de entrada con el fin de obtener una señal de sub-banda de error y una señal de sub-

banda de entrada, respectivamente; se realiza un cálculo en función de la señal de sub-banda de entrada y de la señal de sub-banda de error con el fin de obtener una nueva ponderación de filtrado adaptativo, de modo que cuando una señal se proporcione a la salida, no necesite restablecerse la señal de entrada. En comparación con una solución técnica dada a conocer en la técnica anterior, se omite un filtro integrado para reconstrucción de la señal, con lo que se reduce la cantidad de cálculo de un algoritmo de filtrado adaptativo.

Sobre la base de las descripciones anteriores de las formas de realización, un experto en esta técnica puede entender claramente que la presente invención puede ponerse en práctica mediante software en adición al hardware universal necesario o mediante hardware. En la mayoría de las circunstancias operativas, lo anterior es una forma de realización preferida. Sobre la base de dicho conocimiento, las soluciones técnicas de la presente invención esencialmente, o la parte que contribuye a la técnica anterior, pueden ponerse en práctica en una forma de un producto informático. El producto informático se memoriza en un soporte de memorización legible, tal como un disco flexible, un disco duro o un disco óptico de un ordenador, e incluye varias instrucciones para ordenar a un dispositivo informático (que puede ser un ordenador personal, un servidor o un dispositivo de red) para realizar los métodos descritos en las formas de realización de la presente invención.

Las descripciones anteriores son simplemente formas de realización específicas de la presente invención, pero no están previstas para limitar el alcance de protección de la presente invención. Cualquier variación o sustitución fácilmente creadas por un experto en esta técnica dentro del alcance técnico dado a conocer en la presente invención deberán caer dentro del alcance de protección de la presente invención. Por lo tanto, el alcance de protección de las reivindicaciones.

25

20

5

10

15

#### **REIVINDICACIONES**

1. Un método de filtrado adaptativo ajustado por al menos un algoritmo de mínimos cuadrados LMS sobre la base de una sub-banda de error, que comprende:

5

10

15

35

40

45

50

55

60

recibir, por un filtro adaptativo, una señal de entrada, realizar un procesamiento de filtrado adaptativo sobre la señal de entrada en función de un factor de ponderación de filtrado adaptativo actualmente memorizado en el filtro adaptativo, con el fin de obtener L señales de filtrado adaptativo, y transmitir las L señales de filtrado adaptativo a un subtractor;

recibir, por el subtractor, una señal de referencia y las L señales de filtrado adaptativo, realizar un cálculo en función de la señal de referencia y de las L señales de filtrado adaptativo para obtener una señal de error, y transmitir la señal de error a un filtro de sub-banda de error, en donde la señal de referencia es una señal generada después de que la señal de entrada pase a través de un canal real;

recibir, por el filtro de sub-banda de error, la señal de error, realizar un procesamiento de filtrado de análisis de subbanda sobre la señal de error para obtener N señales de sub-banda de error, y transmitir las N señales de subbanda de error a un actualizador de ponderación adaptativa,

recibir, por un filtro de análisis de señal de entrada, la señal de entrada, realizar un procesamiento de filtrado de análisis de sub-banda sobre la señal de entrada para obtener N señales de sub-banda de entrada, y transmitir las N señales de sub-banda de entrada al actualizador de ponderación adaptativa; y

recibir, por el actualizador de ponderación adaptativa, las N señales de sub-banda de error y las M señales de sub-banda de error y de las M señales de sub-banda de error y de las M señales de sub-banda de error y de las M señales de sub-banda de error y de las M señales de sub-banda de entrada para obtener una nueva ponderación del filtrado adaptativo, y sustituir la ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo por la nueva ponderación de filtrado adaptativo;

en donde el filtro adaptativo tiene L ramas que comprenden una primera rama a una L-ésima rama, y cada rama 30 tiene un puerto de entrada y un puerto de salida, en donde L es un número entero positivo;

cuando L es igual a 1, M multiplicadores, M-1 sumadores y M-1 retardadores de reloj M están dispuestos en la L-ésima rama, en donde los M multiplicadores son un multiplicador 0 a un multiplicador M-1, los M-1 sumadores son un sumador 1 a un sumador M-1 y los M-1 retardadores de reloj M son un retardador 1 de reloj M a un retardador M-1 de reloj M; cada retardador tiene un puerto de entrada y un puerto de salida, cada multiplicador tiene un puerto de entrada y un puerto de salida, M es un número entero positivo, y un puerto de entrada de la L-ésima rama está conectado a puertos de entrada del multiplicador 0 al multiplicador M-1, un puerto de salida del multiplicador 0 está conectado a un puerto de entrada del retardador 1 de reloj M, un puerto de salida de cada uno de un multiplicador 1 al multiplicador M-1 está conectado a un puerto de entrada del retardador 1 de reloj M al retardador M-1 de reloj M está conectado al otro puerto de entrada del sumador 1 al sumador M-1;

a continuación, la recepción, por un filtro adaptativo, de una señal de entrada, realizando un procesamiento de filtrado adaptativo sobre la señal de entrada en función de una ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo de manera que se obtenga una señal de filtrado adaptativo comprende:

en la 1ª rama, recibir, por cada uno del multiplicador 0 al multiplicador M-1, la señal de entrada por intermedio del puerto de entrada de la L-ésima rama, y efectuar una multiplicación sobre la señal de entrada en función de una ponderación de filtro adaptativo memorizada en cada uno de los multiplicadores, para obtener una señal de salida de multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; proporcionar, a la salida, por cada uno del multiplicador 0 al multiplicador M-1, por intermedio de un puerto de salida de cada uno del multiplicador 0 al multiplicador M-1, la señal de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; efectuar, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, un procesamiento de retardo de reloj M sobre una señal recibida en un puerto de entrada de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, para obtener una señal de retardo de reloj M generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; proporcionar, a la salida, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, por intermedio del puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, la señal de retardo de reloj M generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; efectuar, por el sumador 1 al sumador M-1, un procesamiento de adición sobre las señales recibidas por intermedio de dos puertos de entrada que corresponden a cada uno del sumador 1 al sumador M-1, para obtener una señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1, y proporcionar, a la salida, por cada uno del sumador 1 al sumador M-1, por intermedio de un puerto de salida correspondiente a cada uno del sumador 1 al sumador M-1, la señal de salida del sumador generada por cada uno del sumador 1 al sumador M-1; y

65 cuando L es mayor que 1, un retardador de reloj (L-1), M multiplicadores, M-1 sumadores y M-1 retardadores de reloj M están dispuestos en la L-ésima rama, en donde los M multiplicadores son un multiplicador 0 a un multiplicador M-

1, los M-1 sumadores son un sumador 1 a un sumador M-1 y los M-1 retardadores de reloj M son un retardador 1 de reloj M a un retardador M-1 de reloj M; cada retardador tiene un puerto de entrada y puerto de salida, cada multiplicador tiene un puerto de entrada y un puerto de salida; y en la L-ésima rama, un puerto de entrada de la L-ésima rama está conectado a un puerto de entrada del retardador de reloj (L-1), un puerto de salida del retardador de reloj (L-1) está conectado a puertos de entrada de todos los multiplicadores, un puerto de salida del multiplicador 0 está conectado a un puerto de entrada del retardador 1 de reloj M, un puerto de salida de cada uno del multiplicador 1 al multiplicador M-1 está conectado a un puerto de entrada de cada uno del sumador 1 al sumador M-1, y un puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M está conectado al otro puerto de entrada de cada uno del sumador 1 al sumador M-1;

a continuación, la recepción, por un filtro adaptativo, de una señal de entrada, la realización de un procesamiento de filtrado adaptativo sobre la señal de entrada en función de una ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo, con el fin de obtener una señal de filtrado adaptativo comprende:

10

15

20

25

30

35

40

45

50

55

60

en la L-ésima rama, la recepción, por el retardador de reloj (L-1), de la señal de entrada por intermedio del puerto de entrada del retardador de reloj (L-1), y realizar un procesamiento de retardo de reloj (L-1) sobre la señal de entrada para generar una señal de retardo de reloj (L-1); proporcionar, a la salida, por el retardador de reloj (L-1), la señal de retardo de reloj (L-1) por intermedio del puerto de salida del retardador de reloj (L-1); la recepción, por cada uno del multiplicador 0 al multiplicador M-1, de la señal de retardo de reloj (L-1) por intermedio del puerto de entrada de la Lésima rama, y realizar una multiplicación sobre la señal de retardo de reloj (L-1) en función de una ponderación de filtrado adaptativo memorizada en cada uno de los multiplicadores, para obtener una señal de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; proporcionar, a la salida, por cada uno del multiplicador 0 al multiplicador M-1 por intermedio de un puerto de salida de cada uno del multiplicador 0 al multiplicador M-1, la señal de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; realizar, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, un procesamiento de retardo de reloj M sobre una señal recibida en un puerto de entrada de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, con el fin de obtener una señal de retardo generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; proporcionar, a la salida, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M por intermedio del puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, la señal de retardo generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; realizar, por cada uno del sumador 1 al sumador M-1, un procesamiento de adición sobre las señales recibidas por intermedio de dos puertos de entrada correspondientes a cada uno del sumador 1 al sumador M-1, con el fin de obtener una señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1, y proporcionar, a la salida, por cada uno del sumador 1 al sumador M-1, por intermedio de un puerto de salida correspondiente a cada uno del sumador 1 al sumador M-1, la señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1.

**2.** El método según la reivindicación 1, en donde el filtro de sub-banda de error tiene N ramas que comprenden una primera rama a una N-ésima rama y cada rama tiene un puerto de entrada y un puerto de salida, en donde N es un número entero positivo;

cuando X es igual a 1, un filtro de paso bajo, un multiplicador X-1 y un decimador X-1 están dispuestos en una X-ésima rama; un puerto de entrada del filtro de paso bajo está conectado a un puerto de entrada de la X-ésima rama, un puerto de salida del filtro de paso bajo está conectado a un puerto de entrada del multiplicador X-1, un puerto de salida del multiplicador X-1 está conectado a un puerto de salida del decimador X-1 está conectado a un puerto de salida del a X-ésima rama;

a continuación, la recepción, por el filtro de sub-banda de error, de la señal de error, la realización de un procesamiento de filtrado de análisis de sub-banda sobre la señal de error para obtener al menos una señal de sub-banda de error, comprende:

recibir, por el filtro de paso bajo, la señal de error por intermedio del puerto de entrada del filtro de paso bajo, y realizar un procesamiento de filtrado sobre la señal de error en función del ajuste de paso de banda del filtro de paso bajo para obtener una señal de filtro de paso bajo; proporcionar, a la salida, por el filtro de paso bajo, la señal de filtro de paso bajo por intermedio del puerto de salida del filtro de paso bajo; realizar, por el multiplicador X-1, en función de un factor de ponderación memorizado en el multiplicador X-1, un procesamiento de multiplicación sobre una señal recibida por intermedio del puerto de entrada del multiplicador X-1, para obtener una señal de salida del multiplicador; proporcionar, a la salida, por el multiplicador X-1, la señal de salida del multiplicador por intermedio del puerto de salida del multiplicador X-1; realizar, por el decimador X-1, X veces un procesamiento de muestreo descendente sobre una señal recibida por intermedio de un puerto de entrada del decimador X-1, con el fin de obtener una señal de sub-banda de error de la X-ésima rama; y proporcionar, a la salida, por el decimador X-1, la señal de sub-banda de error de la X-ésima rama por intermedio del puerto de salida del decimador X-1;

cuando X es mayor que 1 y menor que N-1, un filtro de paso de banda, un retardador de reloj (X-1), un multiplicador X-1 y un decimador X-1 están dispuestos en una X-ésima rama; un puerto de entrada del filtro de paso de banda está conectado a un puerto de entrada de la X-ésima rama, un puerto de salida del filtro de paso de banda está

conectado a un puerto de entrada del retardador de reloj (X-1), un puerto de salida del retardador de reloj (X-1) está conectado a un puerto de entrada del multiplicador X-1, un puerto de salida del multiplicador X-1 está conectado al decimador X-1, y un puerto de salida del decimador X-1 está conectado a un puerto de salida de la X-ésima rama;

5 a continuación, la recepción, por el filtro de sub-banda de error, de la señal de error, la realización de un procesamiento de filtrado de análisis de sub-banda sobre la señal de error para obtener al menos una señal de sub-banda de error, comprende: