# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 626 438

51 Int. CI.:

**G06K 7/10** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 26.10.2012 PCT/US2012/062292

(87) Fecha y número de publicación internacional: 02.05.2013 WO13063517

(96) Fecha de presentación y número de la solicitud europea: 26.10.2012 E 12784842 (2)

(97) Fecha y número de publicación de la concesión europea: 29.03.2017 EP 2771840

(54) Título: Transceptor NFC

(30) Prioridad:

26.10.2011 US 201113282336

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **25.07.2017**

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121, US

(72) Inventor/es:

SAVOJ, JAFAR

74) Agente/Representante:

FORTEA LAGUNA, Juan José

### **DESCRIPCIÓN**

Transceptor NFC

#### 5 **ANTECEDENTES**

#### Campo

La presente invención se refiere en general a la comunicación de campo cercano (NFC). Más específicamente, la presente invención se refiere a transceptores NFC, que incluyen un convertidor digital-analógico (DAC) programable para accionar una antena en un modo activo y realizar la modulación de carga en un modo pasivo o accionado por campo.

#### **Antecedentes**

15

10

La Comunicación de Campo Cercano (NFC) es una tecnología inalámbrica que puede permitir el intercambio de corto alcance de información entre dos o más dispositivos. Los dispositivos capaces de la NFC pueden simplificar las transacciones de presencia orientada para permitir un intercambio rápido y más seguro de información, por ejemplo, como en las compras de bienes y servicios o en el intercambio de información en las mismas.

20

Como un experto en la materia apreciará y entenderá, las tecnologías NFC comunican a través de la inducción de campo magnético, donde se encuentran al menos dos antenas de bucle una dentro del "campo cercano" de la otra, formando efectivamente un transformador de núcleo de aire que funciona dentro de una frecuencia de radio globalmente disponible y sin licencia que, como se indica, es una banda industrial, científica y médica (ISM) de 13,56 MHz, con un ancho de banda de casi dos (2) MHz.

25

Los transceptores NFC convencionales pueden incluir componentes analógicos, lo cual puede dar como resultado requisitos de una superficie grande y puede complicar el soporte de los estándares NFC deseados. Además, los transceptores NFC convencionales pueden requerir circuitos adicionales para soportar la modulación de carga.

30

Existe una necesidad de procedimientos, sistemas y dispositivos para un transceptor NFC mejorado. Más específicamente, existe una necesidad de un transceptor NFC, que requiera menos superficie que los transceptores convencionales y que soporte el funcionamiento en modo activo y pasivo. Existe también una necesidad de sistemas que incluyan el transceptor NFC y procedimientos de funcionamiento asociados.

35

Se llama la atención sobre el documento WO 2008/013418 contra el cual se delimitan las reivindicaciones independientes y que divulga un aparato RFID integrado de lector-etiqueta y un procedimiento para controlar el mismo. El aparato incluye una unidad de etiqueta para comunicarse con un lector externo y transmitir una señal de respuesta y datos correspondientes a una señal transmitida desde el lector externo hasta el lector externo, una unidad de lector para seleccionar un canal entre otro lector y el aparato RFID integrado de lector-etiqueta con un tiempo de retardo diferente y comunicarse con una etiqueta externa usando un valor aleatorio para minimizar la colisión; y un controlador para activar de forma selectiva una de la unidad de etiqueta y de la unidad de lector si es necesario.

40

Se llama la atención además sobre un documento titulado "NEAR FIELD COMMUNICATION PN531-MUC BASED 45 TRANSMISSION MODULE", de PHILIPS SEMICONDUCTORS. FORMA CORTA DE LA MEMORIA DESCRIPTIVA, vol. Revisión 2.0, 1 de febrero de 2004, páginas 1-19, XP007900763. El PN531 es un módulo de transmisión altamente integrado para la comunicación sin contacto a 13,56 MHz que incluye la funcionalidad de controlador µ basándose en un núcleo 80C51 con 32 kbyte de ROM y 1 kbyte de RAM. Este módulo de transmisión basado en µc 50 combina un concepto de modulación y demodulación destacado completamente integrado para diferentes tipos de procedimientos y de protocolos de comunicación sin contacto a 13,56 MHz con un firmware fácil de usar para los diferentes modos soportados y las interfaces de servidor requeridas.

55

60

Se llama también la atención sobre un artículo de SRIDHARAN S ET AL: "An 8-bit 1.8 V 500 MSPS CMOS Segmented Current Steering DAC", VLSI, 2009. ISVLSI '09. IEEE COMPUTER SOCIETY ANNUAL SYMPOSIUM ON, IEEE, PISCATAWAY, NJ, EEUU, 13 de mayo de 2009, páginas 268-273, XP031476283, ISBN: 978-1-4244-4408-3. Este artículo presenta el diseño de un convertidor digital-analógico, DAC, de guiado de corriente segmentada (CS) de 8 bit 1,8 V, utilizando la tecnología de cinco polimetales dobles CMOS de 0.18. El DAC se ha segmentado en un 6 + 2 para lograr un rendimiento óptimo para la superficie mínima. El resultado de la simulación muestra un DNL máximo de 0,30 LSB y un INL de 0,33 LSB. El fallo técnico del código medio es de 0,27 pV s: Los SNDR y SFDR simulados del DAC segmentado son de 52,13 dB y 44,83 dB respectivamente. La instalación del DAC segmentado es de 6,02 ns. El consumo de energía se simula en 7,88 mW. El prototipo se usará en aplicaciones de telecomunicaciones.

65

La invención se define por las reivindicaciones independientes. Los modos de realización preferidos se exponen en las reivindicaciones dependientes.

#### **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

5

15

30

35

40

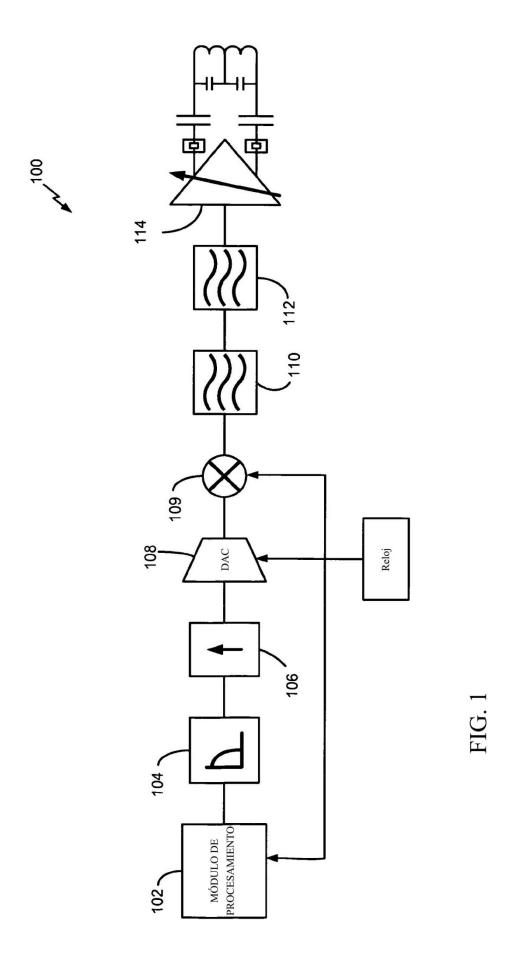

- La FIG. 1 es un diagrama de bloques de un transmisor NFC convencional.

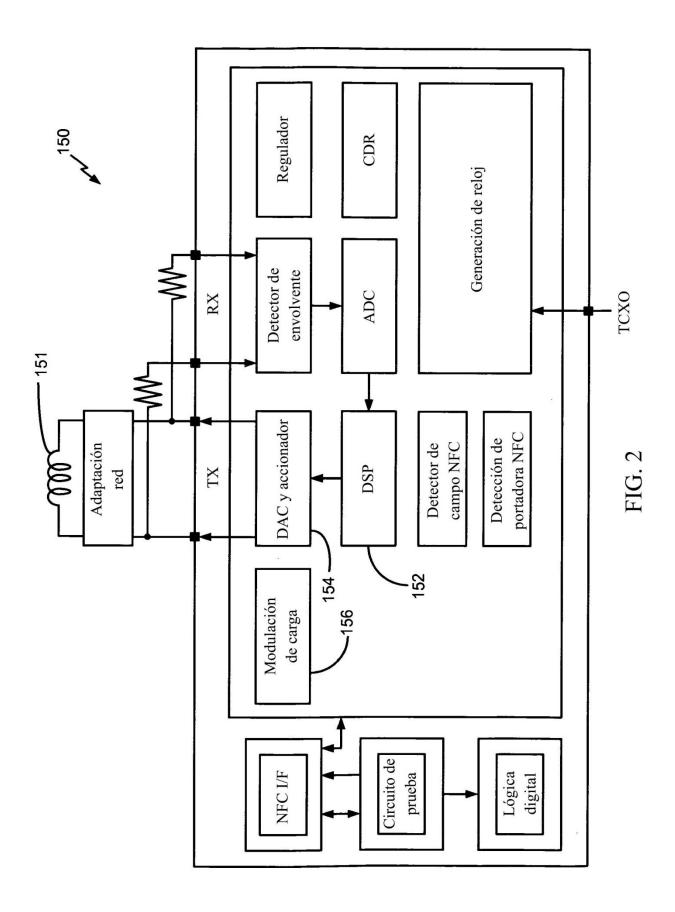

- La FIG. 2 es un diagrama de bloques de un sistema NFC que incluye un transmisor, de acuerdo con un modo de realización a modo de ejemplo de la presente invención.

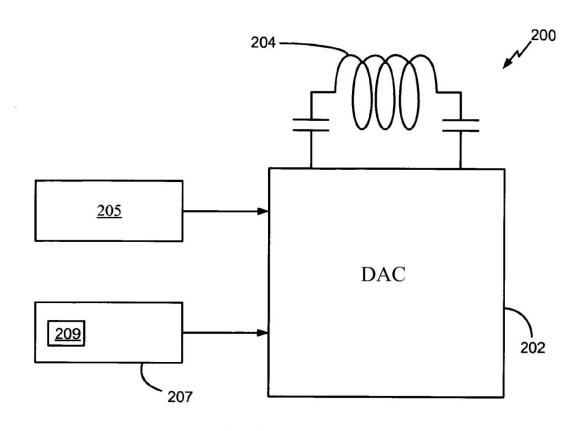

- La FIG. 3 ilustra un sistema que incluye un dispositivo que comprende un convertidor digital-analógico (DAC) de corriente acoplado a una antena, de acuerdo con un modo de realización a modo de ejemplo de la presente invención.

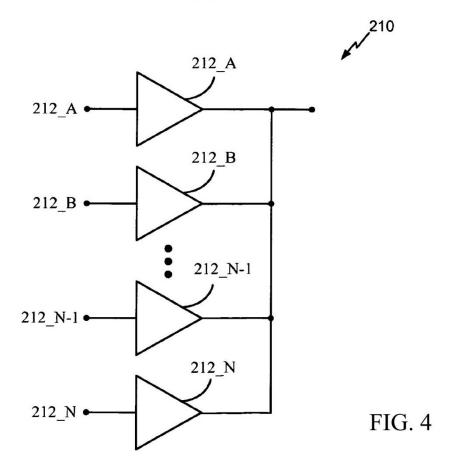

- La FIG. 4 ilustra una serie de accionadores dentro de un convertidor digital-analógico (DAC), de acuerdo con un modo de realización a modo de ejemplo de la presente invención.

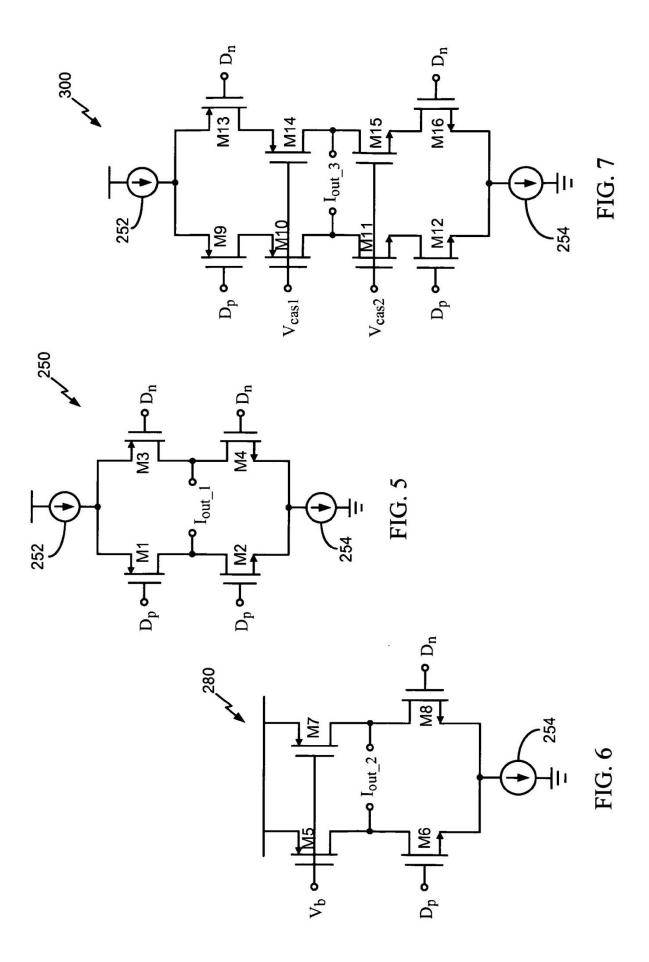

- La FIG. 5 ilustra una célula DAC que incluye un accionador de señalización diferencial de baja tensión (LVDS), de acuerdo con un modo de realización a modo de ejemplo de la presente invención.

- La FIG. 6 ilustra otra célula DAC que incluye un accionador LVDS, de acuerdo con un modo de realización a modo de ejemplo de la presente invención.

- La FIG. 7 ilustra otra célula DAC que incluye un accionador LVDS, de acuerdo con un modo de realización a modo de ejemplo de la presente invención.

- La FIG. 8 representa otra célula DAC más que incluye un accionador LVDS, de acuerdo con un modo de realización a modo de ejemplo de la presente invención.

- La FIG. 9 es un diagrama de flujo que ilustra un procedimiento de acuerdo con un modo de realización a modo de ejemplo de la invención.

#### **DESCRIPCIÓN DETALLADA**

La descripción detallada expuesta a continuación en conexión con los dibujos adjuntos está prevista como una descripción de modos de realización a modo de ejemplo de la presente invención y no está prevista para representar los únicos modos de realización en los cuales la presente invención pueda practicarse. La expresión "a modo de ejemplo" usada a lo largo de esta descripción significa "que sirve de ejemplo, caso o ilustración" y no debería interpretarse necesariamente como preferida o ventajosa a través de otros modos de realización a modo de ejemplo. La descripción detallada incluye detalles específicos para el propósito de proporcionar un entendimiento profundo de los modos de realización a modo de ejemplo de la invención. Resultará evidente para los expertos en la materia que los modos de realización a modo de ejemplo de la invención pueden practicarse sin estos detalles específicos. En algunos casos, se muestran estructuras y dispositivos bien conocidos en forma de diagrama de bloques con el fin de evitar complicar la novedad de los modos de realización a modo de ejemplo presentados en el presente documento.

- La NFC es un estándar de comunicación que permite que los dispositivos de comunicación inalámbrica, tales como los teléfonos móviles, los teléfonos inteligentes y los asistentes digitales personales (PDA), establezcan redes entre pares (P2P). La NFC puede permitir que los dispositivos electrónicos intercambien datos e inicien aplicaciones de forma automática cuando se traigan muy cerca, por ejemplo, desde menos de un centímetro hasta una distancia de aproximadamente 10 cm. A modo de ejemplos no limitativos, la NFC puede permitir la descarga de las imágenes almacenadas en una cámara digital a un ordenador personal, la descarga de entretenimiento de audio y vídeo a dispositivos portátiles o la descarga de datos almacenados en un teléfono inteligente a un ordenador personal u otro dispositivo inalámbrico. La NFC puede ser compatible con las tecnologías de las tarjetas inteligentes y puede usarse también para permitir la compra de bienes y servicios. En un modo de realización a modo de ejemplo, la frecuencia usada para la NFC está centrada a aproximadamente 13,56 MHz.

- Un transceptor NFC puede incluir circuitos para la adaptación de la impedancia a una antena u otros circuitos dentro de un elemento de acoplamiento. El transceptor NFC puede incluir también lógica, circuitos, procesadores, código, o combinaciones de los mismos adecuados para permitir la recepción y la transmisión de señales NFC, para las cuales la frecuencia portadora de la señal recibida está en la banda de frecuencia NFC. Los datos pueden modularse en la frecuencia de portadora.

La NFC convencional puede basarse en la tecnología de Identificación de Radiofrecuencia (RFID) que usa la inducción de campo para permitir la comunicación entre dispositivos electrónicos muy cerca. Esto puede permitir que los usuarios realicen transacciones seguras, intuitivas y sin contacto. La NFC del estado de la técnica convencional puede funcionar a 13,56 MHz y transferir datos a hasta 424 Kbits/segundo. Por supuesto, las mejoras en la tecnología NFC pueden dar como resultado frecuencia(s) diferentes(s), valores de rendimiento diferentes o ambos. La comunicación entre dos o más dispositivos compatibles con la NFC puede producirse cuando los dispositivos se

traigan dentro de una distancia corta entre sí y pueden ser compatibles con otras tecnologías inalámbricas conocidas como Bluetooth o Wi-Fi, por ejemplo.

Actualmente, existen dos modos principales de funcionamiento disponibles bajo los estándares de NFC presentes: activo y pasivo (es decir, accionado por campo). En el modo activo, un dispositivo puede generar su propio campo de radio para transmitir datos. En el modo pasivo, un dispositivo puede generar un campo de radio, mientras que el otro usa la modulación de carga para transferir datos. El modo pasivo de comunicación es a menudo útil para los dispositivos de potencia limitada, tales como teléfonos móviles y PDA, que tienen para minimizar el uso de energía. Puede impedir también la interrupción de la comunicación NFC cuando se agote la batería del dispositivo.

10

15

En los diversos modos de realización a modo de ejemplo descritos en el presente documento, se entiende que el término NFC abarca cualquier protocolo de comunicación inalámbrica o de proximidad cercana conocidos ahora o en el futuro o sistemas que faciliten la transferencia inalámbrica de corto alcance de información y se entiende que no se limita a los estándares o protocolos actuales promulgados por un cuerpo u organización estándar NFC. En consecuencia, se entiende que la NFC se aplica en el presente documento como un sentido genérico del término.

Como entenderá un experto en la materia medio, puede ser ventajoso para un transceptor NFC proporcionar una oscilación adecuada en un modo activo, que puede denominarse también en el presente documento "modo iniciador" y realizar la modulación de carga en un modo pasivo, que puede denominarse también en el presente documento "modo de etiqueta" o "modo accionado por campo" Como entenderá un experto en la materia medio, la implementación de dicho transceptor NFC de forma analógica verdadera puede dar como resultado requisitos de una superficie grande y puede complicar el soporte de múltiples estándares, que pueden requerirse en las aplicaciones NFC. Además, los transceptores NFC convencionales pueden estar configurados solamente para realizar una única función (es decir, funcionan en un modo único, ya sea pasivo o activo).

25

30

20

Los modos de realización a modo de ejemplo de la presente invención, como se describe en el presente documento, están relacionados con un transceptor NFC, que incluye un convertidor digital-analógico (DAC) programable para soportar la modulación de carga en un modo pasivo (es decir, el modo de etiqueta) y el accionamiento de corriente en un modo activo (es decir, el modo inicio). El transceptor NFC puede permitir que otros componentes asociados (por ejemplo, los filtros UPC) se implementen con componentes digitales, lo cual puede dar como resultado la facilidad de diseño y una cantidad reducida de superficie requerida.

35

De acuerdo con un modo de realización a modo de ejemplo de la presente invención, un transceptor NFC puede incluir un convertidor digital-analógico (DAC) de corriente, que está acoplado a una antena. El DAC de corriente puede estar acoplado también a y configurado para recibir una señal desde un componente digital, tal como un filtro digital (por ejemplo, un filtro UPC). Además, el DAC de corriente puede incluir una pluralidad de accionadores, en donde cada accionador de la pluralidad de accionadores esté configurado para transmitir una corriente a la antena. Como se describe con más detalle a continuación, el DAC de corriente puede estar configurado para accionar una corriente en un primer modo de comunicación de campo cercano (NFC) (es decir, un modo activo) y soportar la modulación de carga en un segundo modo NFC (por ejemplo, un modo pasivo) .

45

50

40

La FIG. 1 es un diagrama de bloques de un transmisor NFC 100 que utiliza una trayectoria RF. El transmisor 100 incluye un módulo de procesamiento 102, un conformador de impulsos 104, un interpolador 106, cada uno de los cuales son componentes digitales. El transmisor 100 incluye además un convertidor digital-analógico (DAC) 108, que es un componente analógico, y un mezclador 109 de un convertidor ascendente (UPC), que es un componente RF. Además, el transmisor 100 incluye filtros de reconstrucción 110 y 112 y un amplificador de potencia 114, que son también componentes RF. Como apreciará un experto en la materia medio, el transmisor NFC 100 puede utilizar una superficie grande debido a los estrictos requisitos de ancho de banda en los filtros analógicos y puede sufrir grandes variaciones debido a los desajustes en los componentes analógicos. Además, se observa que el transmisor NFC 100 puede requerir adicionalmente un filtro de compatibilidad electromagnética (EMC) para suprimir los armónicos de salida del amplificador de potencia 114. Además, el transmisor NFC 100 requiere circuitos adicionales para soportar la modulación de carga en un modo pasivo (es decir, el modo de etiqueta).

55

60

La FIG. 2 es un diagrama de bloques de un sistema NFC 150, que está configurado para soportar los modos activos y pasivos, como se mencionó anteriormente. El sistema NFC 150 incluye, entre otros componentes, una antena 151, un procesador de señales digitales (DSP) 152, que se denomina también comúnmente módem de banda base, un convertidor digital-analógico (DAC) y un módulo accionador 154 y un módulo de modulación de carga 156. Como apreciará un experto en la materia medio, el DAC y el módulo accionador 154 pueden utilizarse en un modo activo y el módulo de modulación de carga 156 puede utilizarse en un modo pasivo. Sin embargo, se observa que el convertidor digital-analógico y el módulo accionador 154 son componentes independientes y distintos dentro del sistema NFC 150.

65

La FIG. 3 ilustra un sistema 200 que incluye un convertidor de digital a analógico (DAC) de corriente 202, de acuerdo con un modo de realización a modo de ejemplo de la presente invención. Se observa que el DAC de corriente 202 puede denominarse también en el presente documento "DAC segmentado". El DAC de corriente 202 está acoplado a una antena 204 y puede estar configurado para recibir una o más señales digitales desde un componente digital,

## ES 2 626 438 T3

tales como, por ejemplo solamente, un filtro, tal como un filtro digital de conversión ascendente (UPC). El DAC de corriente 202 puede estar configurado también para recibir una o más señales de control desde un módulo de control 207, que puede comprender, por ejemplo solamente, un procesador, un controlador o similar. El módulo de control 207 puede comprender un selector de modo 209 configurado para determinar si el sistema 200 debería estar en un modo activo o en un modo pasivo. El módulo de control 207 puede determinar un modo (es decir, activo o pasivo) del sistema 200 a través de uno o más sensores, de la entrada de usuario o de otros medios adecuados conocidos. Tras la determinación de un modo, el módulo de control 207 puede transmitir una o más señales de control al DAC de corriente 202 para controlar una configuración del mismo.

Además, como se describe con más detalle a continuación, el DAC de corriente 202 puede estar configurado para accionar una corriente dentro de la antena 204. Más específicamente, en un modo de funcionamiento (por ejemplo, un modo activo), el DAC de corriente 202 puede estar configurado para transmitir una corriente directamente a la antena 204 y, por lo tanto, en comparación con los transmisores NFC convencionales, tal vez no sea necesario un controlador independiente.

15

55

60

65

- Se observa que un conductor de antena, que se implementa por el DAC de corriente 202, puede producir una variedad de modulaciones de señales. Además, en nodos de proceso más finos (por ejemplo, nodos de proceso CMOS), pueden implementarse filtros UPC mediante los componentes digitales sin una penalización importante, dando como resultado la facilidad del diseño y la reducción de la superficie. Más específicamente, por ejemplo, pueden implementarse un convertidor ascendente (UPC) y filtros dentro del sistema 200 con componentes digitales. Se observa que el DAC de corriente 202 puede hacerse funcionar en un múltiplo de 13,56 MHz para una conformación de impulsos mejorada y, por lo tanto, tal vez no sea necesario un filtro de compatibilidad electromagnética (EMC).

- La FIG. 4 ilustra una serie de accionadores 210, que es un ejemplo de una serie de accionadores dentro del DAC de corriente 202. Cada accionador 216 (es decir, 216\_A-216\_N) incluye una entrada asociada 212 (es decir, 212\_A-212\_N) y, además, la serie de accionadores 210 incluye una salida 214. Como entenderá un experto en la materia medio, un DAC de corriente, tal como el DAC de corriente 202, puede incluir una serie de accionadores en donde cada accionador 216 incluye una o más células. Por ejemplo, el accionador 216\_A puede incluir 2^0 células (es decir, una célula), el accionador 216\_B puede incluir 2^1 células (es decir, dos células), el accionador 216\_N-1 puede incluir 2^(n-1) células (por ejemplo, dieciséis células si N es igual a cinco) y el accionador 216\_N puede incluir 2^N células (por ejemplo, treinta y dos células si N es igual a cinco). Se observa que cualquier número de accionadores dentro de una serie de accionadores está dentro del alcance de la invención.

- La FIG. 5 ilustra una célula DAC 250 de acuerdo con un modo de realización a modo de ejemplo de la presente 35 invención. La célula DAC 250 comprende un accionador de señalización diferencial de baja tensión (LVDS) que incluye una pluralidad de transistores M1, M2, M3 y M4 y las fuentes de corriente 252 y 254. Como apreciará un experto en la materia medio, la célula DAC 250 puede estar configurada para recibir las señales de entrada Dp y Dn desde, por ejemplo, el módulo de control 207 y dar salida a una corriente I<sub>out 1</sub>. En un funcionamiento contemplado, 40 la corriente de desviación se conmuta en la antena de acuerdo con la entrada de datos. Usa cuatro conmutadores MOS (M1-M4) en una configuración en puente. Si los conmutadores M1 y M4 están encendidos (Dp = 0 & Dn = 1), la polaridad de la corriente de salida es positiva. Por el contrario, si los conmutadores M2 y M3 están encendidos (Dp = 1 & Dn = 0), la polaridad de la corriente de salida es negativa. Se observa que la presente invención no se limita a la célula DAC 250 y otros diseños de células pueden estar dentro del alcance de la invención. Por ejemplo, con referencia a la FIG. 6, se ilustra una célula DAC 280. La célula DAC 280 comprende un accionador LVDS que 45 incluye una pluralidad de transistores M5, M6, M7 y M8 y una fuente de corriente 254. Como apreciará un experto en la materia medio, la célula DAC 280 puede estar configurada para recibir las señales de entrada V<sub>D</sub>, D<sub>D</sub> y D<sub>D</sub> desde, por ejemplo, el módulo de control 207 y dar salida a una corriente Iout\_2. Esta configuración de célula DAC 280 permite que el circuito se ejecute desde un suministro inferior, en comparación con un enfoque LVDS típico. 50

- Otra célula DAC 300, de acuerdo con un modo de realización a modo de ejemplo de la presente invención, se ilustra en la FIG. 7. La célula DAC 300 comprende un accionador LVDS que incluye una pluralidad de transistores M9, M12, M13 y M16 y las fuentes de corriente 252 y 254. Además, las células DAC 300 incluye los dispositivos cascodo M10, M11, M14 y M15. Como apreciará un experto en la materia medio, un dispositivo cascodo puede mejorar los problemas relacionados con la tensión de la célula DAC 300, especialmente a tensiones más altas (por ejemplo, 1,8 voltios). Más específicamente, los dispositivos cascodo pueden proporcionar una protección añadida para los dispositivos reduciendo la caída de tensión a través de dichos dispositivos. Como apreciará un experto en la materia medio, la célula DAC 300 puede estar configurada para recibir las señales de entrada V<sub>cas1</sub>, V<sub>cas2</sub>, D<sub>p</sub> y D<sub>n</sub> desde, por ejemplo, el módulo de control 207 y dar salida a una corriente l<sub>out\_3</sub>.

- Como apreciará un experto en la materia medio, una técnica NFC típica es el uso de la modulación de carga, en la cual un dispositivo varía una impedancia de carga de su bobina para cambiar su frecuencia de resonancia y su factor de calidad Q. Esta acción causa una variación de la tensión en otro dispositivo (es decir, un dispositivo en un modo iniciador).

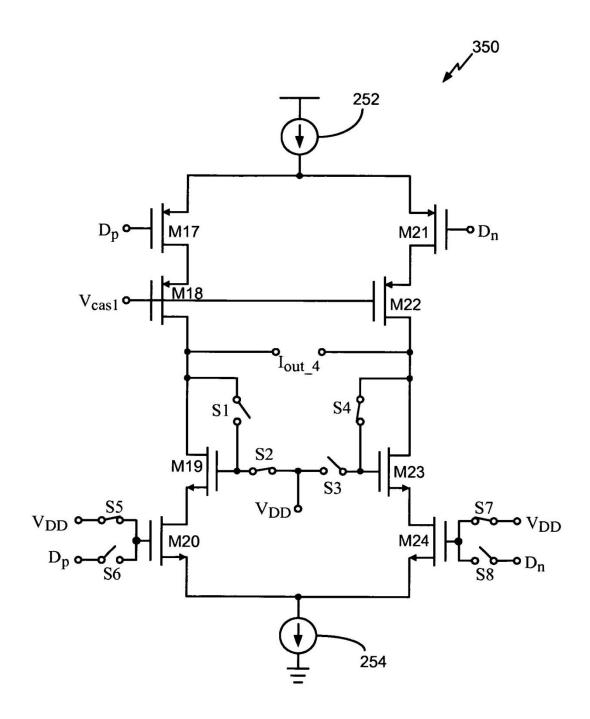

De acuerdo con un modo de realización a modo de ejemplo de la presente invención, una etapa de accionador de

señalización diferencial de baja tensión (LVDS) puede reconfigurarse con una pluralidad de conmutadores para realizar la modulación de carga. Además, una serie de células LVDS, en donde al menos una célula incluya uno o más conmutadores, puede permitir el ajuste de la fuerza de la modulación de carga. Además, una o más células LVDS pueden estar configuradas para proporcionar simetría en la modulación de carga. Con referencia a la FIG. 8, se ilustra una célula DAC 350. La célula DAC 350 comprende un controlador LVDS que incluye una pluralidad de transistores M17, M19, M20, M21, M23 y M24 y las fuentes de corriente 252 y 254. Adicionalmente, la célula DAC 350 incluye los dispositivos cascodo M18 y M22, que, como se ha indicado anteriormente, pueden proporcionar una protección adicional para la célula DAC 350. La célula DAC 350 incluye además una pluralidad de conmutadores S1-S8, de acuerdo con un modo de realización a modo de ejemplo de la presente invención. Como apreciará un experto en la materia medio, la célula DAC 280 puede estar configurada para recibir las señales de entrada V<sub>cas1</sub>, V<sub>DD</sub>, D<sub>P</sub> y D<sub>n</sub> desde, por ejemplo, el módulo de control 207 y dar salida a una corriente l<sub>out 4</sub>.

Se observa que en la configuración ilustrada en la FIG. 8 (es decir, los conmutadores S2, S4, S5 y S7 están cerrados y los conmutadores S1, S3, S6, y S8 están abiertos), la célula DAC 350 está en un modo activo y, por lo tanto, está adaptada para accionar una corriente en una antena asociada. En otras configuraciones contempladas, la célula DAC puede proporcionar la modulación de carga. Durante la modulación de carga, las fuentes de corriente 252 y 254 están apagadas. Además, cuando S2, S4, S5 y S7 están cerrados, el circuito parece efectivamente un diodo (formado por M23) y pequeñas resistencias (formadas por M19, M20, y M24). Efectivamente, si la oscilación de la tensión a través de los nodos de salida (lout 4) es mayor que un umbral (Vth), la trayectoria se enciende y modula la carga. Se observa que la razón para colocar un dispositivo conectado a un diodo, M23, es introducir alguna histéresis en el funcionamiento del circuito. De manera similar, la célula 350 puede estar configurada de tal manera que los conmutadores S1, S3, S5 y S7 estén encendidos y el resto de los conmutadores están apagados. En consecuencia, la célula 350 puede funcionar todavía en el modo de modulación de carga, pero se alterna la polaridad de la histéresis. Además, si los conmutadores S2, S3, S6 y S8 están encendidos y el resto de los conmutadores están apagados mientras que 252 y 254 están conduciendo corriente, entonces la célula de accionador funciona en el modo activo y acciona la corriente en la antena.

15

20

25

30

45

55

Por lo tanto, de acuerdo con diversos modos de realización a modo de ejemplo de la presente invención, una célula DAC (por ejemplo, la célula DAC 350) puede ser configurable, a través de uno o más conmutadores, para accionar (es decir, transmitir) una corriente en un modo activo y soportar la modulación de carga en un modo pasivo. En consecuencia, el DAC de corriente 200 que incluye la célula DAC 350 puede ser programable para su funcionamiento en los modos activo y pasivo. Se observa que una configuración de célula puede ser constante a través de un DAC de corriente.

35 Se describirá ahora un funcionamiento contemplado de la célula DAC 350. Durante un modo activo (es decir, un modo en el cual el DAC de corriente 200 esté transmitiendo una corriente a la antena 204), los conmutadores S2, S4, S5 y S7 pueden estar cerrados y los conmutadores S1, S3, S6 y S8 pueden estar abiertos. Por lo tanto, como entenderá un experto en la materia medio, la corriente Iout 4 puede transmitirse a una antena asociada, junto con la corriente desde otras células dentro del DAC. Además, durante un modo pasivo, uno o más de los conmutadores 40 S1-S8 pueden reconfigurarse para proporcionar la modulación de carga, como apreciará un experto en la materia medio.

Se observa que los modos de realización a modo de ejemplo, como se describe en el presente documento, pueden requerir una superficie más pequeña en comparación con los dispositivos de la técnica anterior. Por ejemplo solamente, un DAC de 8 bits (por ejemplo, el DAC 202), que esté configurado para manejar 50-80 mA de corriente, puede ocupar 0,05 mm2 de superficie en un CMOS submicrónico profundo tal como un proceso de 90 nm.

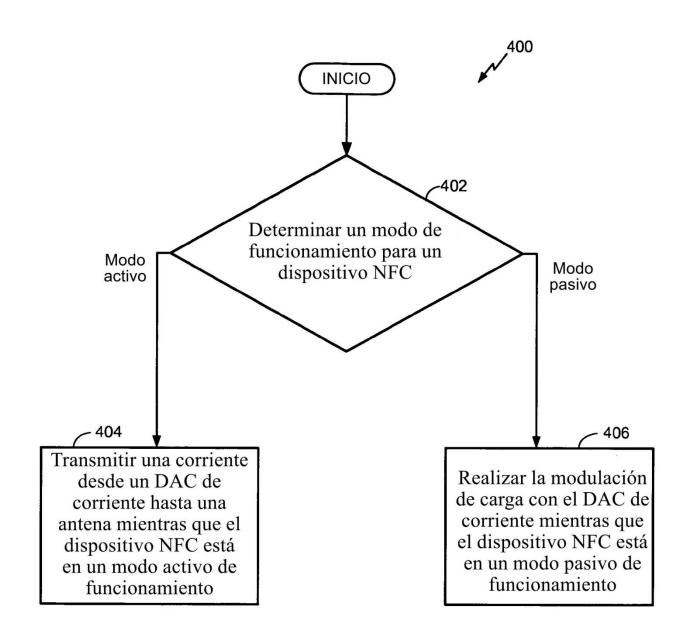

La FIG. 9 es un diagrama de flujo que ilustra un procedimiento 400 de acuerdo con un modo de realización a modo de ejemplo. El procedimiento 400 puede incluir determinar un modo de funcionamiento de un dispositivo NFC 50 (representado con el número 402). Como se observó anteriormente, un módulo de control, tal como el módulo de control 207, puede estar configurado para determinar si un NFC debería estar en un modo activo o en un modo pasivo. El procedimiento 400 puede incluir también transmitir un DAC de corriente a una antena mientras que el dispositivo NFC está en un modo activo de funcionamiento (representado con el número 404). Además, el procedimiento 400 puede incluir realizar la modulación de carga con el DAC de corriente mientras que el dispositivo NFC está en un modo pasivo de funcionamiento (representado con el número 406).

#### REIVINDICACIONES

1. Un dispositivo, que comprende:

5 un convertidor digital-analógico, DAC, (202) configurado para transmitir una corriente a una antena (204) en un primer modo de comunicación de campo cercano, NFC, y permitir la modulación de carga en un segundo modo NFC.

caracterizado por que el DAC (202) proporciona la carga de modulación.

- 10 2. El dispositivo de la reivindicación 1, comprendiendo el DAC de corriente una pluralidad de accionadores, cada accionador de la pluralidad configurado para transmitir una corriente a la antena.

- 3. El dispositivo de la reivindicación 1, que comprende además un filtro digital acoplado al DAC de corriente; y/o que comprende además un convertidor ascendente digital acoplado al DAC de corriente.

- 4. El dispositivo de la reivindicación 2, incluyendo cada accionador una o más células configuradas para transmitir una corriente a la antena; e incluyendo preferentemente cada célula de las una o más células un circuito de señalización diferencial de baja tensión, LVDS; y comprendiendo además preferentemente el circuito LVDS una pluralidad de conmutadores para ajustar una resistencia a la modulación de carga y/o comprendiendo el circuito LVDS al menos un dispositivo cascodo.

- **5.** El dispositivo de la reivindicación 2, incluyendo cada conductor una o más células reconfigurables para transportar una corriente a la antena o realizar la modulación de carga.

- 25 **6.** El dispositivo de la reivindicación 1, estando el DAC de corriente (202) configurado para accionar la corriente a la antena en un modo de iniciar y modular una carga en un modo de modulación de carga.

- 7. Un procedimiento (400), que comprende:

- transmitir (404) una corriente desde un convertidor digital-analógico, DAC, de corriente (202) a una antena (204) durante un primer modo de comunicación de campo cercano, NFC; y

- realizar (406) la modulación de carga con el DAC de corriente (202), durante un segundo modo NFC, **caracterizado por que** el DAC (202) proporciona la carga de modulación.

- 8. El procedimiento según la reivindicación 7, comprendiendo la transmisión transmitir la corriente desde el DAC de corriente a la antena en un modo NFC activo; y/o comprendiendo el modo de realización realizar la modulación de carga con el DAC de corriente en un modo de NFC pasivo.

- 40 9. El procedimiento según la reivindicación 7, que comprende además transmitir una señal digital al DAC de corriente antes de transmitir una corriente desde el DAC de corriente hasta la antena; y que comprende preferentemente además filtrar la señal digital con un filtro digital antes de transmitir la señal digital al DAC de corriente.

- 45 **10.** El procedimiento según la reivindicación 7, comprendiendo la modulación modular la carga con una o más células, comprendiendo cada una de las una o más células un circuito de señalización diferencial de baja tensión, LVDS; y/o comprendiendo la modulación recibir una o más señales de control en el DAC de corriente.

- 50 **11.** El procedimiento según la reivindicación 7, que comprende además determinar (402) si el DAC de corriente debería funcionar en un modo pasivo o en un modo activo.

- **12.** El procedimiento según la reivindicación 7, comprendiendo la modulación modular la carga ajustando uno o más conmutadores dentro de las una o más células.

55

35

15

FIG. 3

FIG. 8

FIG. 9