# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 640 970

61 Int. Cl.:

H04J 14/02 (2006.01) H04Q 11/00 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 25.10.2011 PCT/SE2011/051262

(87) Fecha y número de publicación internacional: 02.05.2013 WO13062452

(96) Fecha de presentación y número de la solicitud europea: 25.10.2011 E 11874798 (9)

(97) Fecha y número de publicación de la concesión europea: 19.07.2017 EP 2772066

(54) Título: Interfaz y procedimiento para habilitar una interconexión de un dispositivo anfitrión y un módulo conectable con factor de forma pequeño

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **07.11.2017**

(73) Titular/es:

TELEFONAKTIEBOLAGET LM ERICSSON (PUBL) (100.0%)

164 83 Stockholm, SE

(72) Inventor/es:

TROJER, ELMAR; CHEN, LING y SUN, YUE

(74) Agente/Representante:

ELZABURU, S.L.P

#### **DESCRIPCIÓN**

Interfaz y procedimiento para habilitar una interconexión de un dispositivo anfitrión y un módulo conectable con factor de forma pequeño

#### Campo técnico

La presente invención se refiere a una interfaz y a un procedimiento para permitir una interconexión de un dispositivo anfitrión ("host") y un módulo conectable con factor de forma pequeño.

#### **Antecedentes**

10

15

20

25

30

35

40

45

50

En una red de telecomunicaciones móviles jerárquica, la parte de red de retorno ("backhaul") de la red comprende los enlaces intermedios entre la red central de la red de telecomunicaciones móviles y las pequeñas sub-redes en la periferia de toda la red jerárquica. Por ejemplo, aunque el equipo de usuario que se comunica con una estación base constituye una subred local, la conexión entre la estación base y el resto del mundo comienza con un enlace de red de retorno al núcleo de la red del proveedor de telecomunicaciones. Pueden usarse una diversidad de redes ópticas pasivas (Passive Optical Network, PON) diferentes como redes de retorno móviles. Por ejemplo, las redes ópticas tales como las redes ópticas gigabit-pasivas (GPONs), que proporcionan múltiples procedimientos de acceso, son soluciones de redes de retorno móviles adecuadas a las que se hace referencia como redes de acceso de radio GPON (GRPON Radio Access Networks, GPON RAN). Sin embargo, son posibles otras soluciones de PON, tales como, por ejemplo, Ethernet PON (EPON) o multiplexación por división de longitud de onda PON (Wavelength Division Multiplexing PON, WDMPON). A continuación, se usará GPON para ejemplificar las redes xPON.

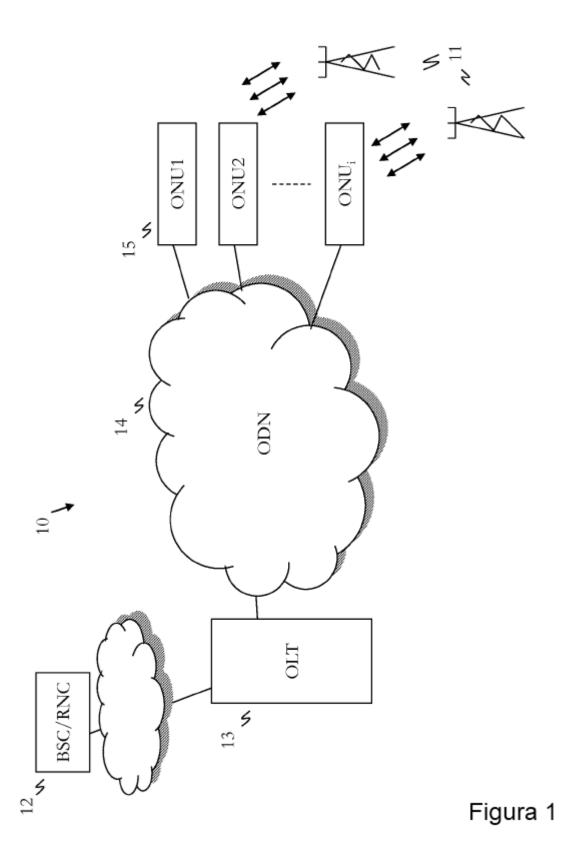

Una GPON es una tecnología de acceso basada en fibra ilustrada en la Figura 1, en la que una red 10 óptica transporta esencialmente tráfico entre las estaciones 11 base y un controlador 12 de estación base. Una pluralidad de nodos de usuario 15 en forma de unidades de red óptica (Optical Network Unit, ONU) proporciona servicios de telecomunicaciones a usuarios finales a través de equipos locales de cliente (Customer-Premises Equipment, CPE), que se refiere en general a dispositivos tales como teléfonos, enrutadores, conmutadores, decodificadores, etc. Las ONUs están conectadas a un nodo 13 de oficina central en forma de un terminal de línea óptica (Optical Line Terminal, OLT), a través de una red de distribución óptica 14 (Optical Distribution Network, ODN), donde la pluralidad (hasta 64) de ONUs comparten un divisor común y una fibra troncal conectada al OLT. El OLT sirve como multiplexor de acceso que agrega tráfico desde las ONUs y distribuye tráfico hacia las ONUs. De esta manera, en el extremo de la red, el OLT proporciona la interfaz entre la GPON y los servicios de red del proveedor de servicios, que incluyen, por ejemplo, tráfico IP tal como Ethernet e interfaces por multiplexación por división de tiempo (Time Division Multiplexed, TDM) tales como SONET. En el otro extremo de la red, las ONUs proporcionan la interfaz entre la GPON y los usuarios finales, donde los servicios incluyen, por ejemplo, voz en forma de servicio de telefonía tradicional (Plain Old Telephone Service, POTS) o voz sobre IP (Voice Over IP, VoIP), datos tales como Ethernet, vídeo, etc.

Una ONU contiene además de la óptica, un dispositivo de ajuste de trama de GPON para gestionar datos de paquetes, así como una CPU anfitriona para controlar el dispositivo de ajuste de trama de GPON, así como una lógica relacionada con Ethernet (conmutador, gestión de tráfico, funciones L3, etc.) y lógica relacionada con voz. La ONU contiene también memoria flash para almacenar software que puede ser actualizado de manera remota por el OLT.

En la actualidad, hay disponibles chipsets de ONU altamente integrados que contienen muchas más funciones, además del dispositivo de ajuste de trama. Esto permite fabricar ONUs muy pequeñas que pueden ser alojadas en un módulo conectable con pequeño factor de forma (Small-Formfactor Pluggable, SFP). De manera ventajosa, en la ONU, a medida que aumentan los requisitos de ancho de banda, pueden conectarse uno o más módulos SFP haciendo que la ONU sea altamente escalable. Además, pueden conectarse diferentes SFPs dependiendo de los requerimientos de alcance, ya que diferentes tipos de SFP tienen diferentes alcances (1 km, 5 km, 80 km, etc.)

El SFP es en la actualidad el factor de forma de transceptor más popular, usado para Ethernet (1G), SDH/SONET, Fibre Channel y PONs (EPON, GPON, WDM). Los módulos SFP se conectan en conectores SFP que están montados en una placa principal de una ONU. Los conectores están alojados dentro de una jaula EMI donde está conectado el módulo SFP. El SFP ha sido estandarizado por el grupo SFA MSA, y en la actualidad se usa una versión mejorada SFP+ para 10G Ethernet con el mismo diseño de conector.

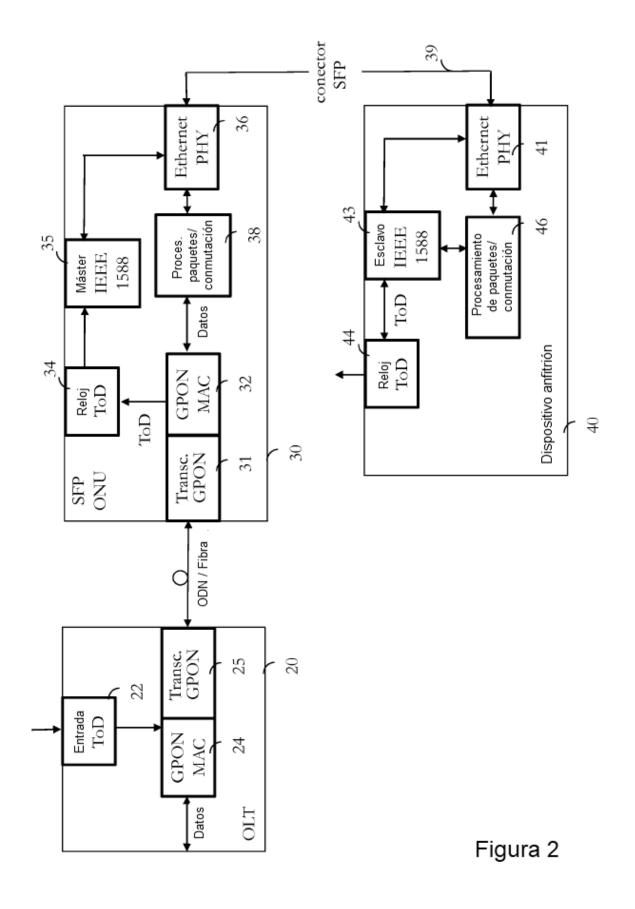

Para hacer que los PON síncronos puedan usarse como redes de retorno móviles, el transporte de señales de sincronización es un requisito estricto. En la técnica, esto se ha resuelto integrando una infraestructura 1588 basada en paquetes en el módulo SFP, que se describe detalladamente con referencia a la Figura 2. Es decir, el módulo SFP ha sido modificado para cumplir con un protocolo de tiempo de precisión descrito en una norma denominada IEEE 1588. Con este protocolo, es posible sincronizar relojes distribuidos con una precisión de menos de 1 microsegundo a través de redes Ethernet. Sin embargo, este enfoque requiere una gran modificación de los módulos SFP comerciales ordinarios,

convirtiéndolos en complejos y costosos.

El documento US 2007/153823 describe una ONU conectable con factor de forma pequeño que incluye un transceptor óptico bidireccional configurado para transmitir señales ópticas a y recibir señales ópticas desde un OLT. La ONU incluye además un chip de ONU acoplado al transceptor óptico y configurado para comunicarse con el OLT. Hay incluida también una interfaz conectable configurada para una interconexión eléctrica entre el chip de ONU y una pieza del equipo local de abonado (Subscriber Premise Equipment, SPE). La ONU incluye un módulo gestor de energía para proporcionar energía al chip de ONU y al transceptor óptico, usando la energía suministrada desde el SPE a través de la interfaz conectable.

#### Sumario

5

15

20

25

30

35

40

45

50

Un objeto de la presente invención es resolver estos problemas en la técnica.

Este objetivo se consigue en un primer aspecto de la presente invención mediante una interfaz para permitir la interconexión de un dispositivo anfitrión y un módulo conectable con factor de forma pequeño según la reivindicación 1.

Este objeto se consigue en un segundo aspecto de la presente invención mediante un procedimiento para permitir la interconexión de un dispositivo anfitrión y un módulo conectable con factor de forma pequeño según la reivindicación 9

De manera ventajosa, haciendo que la interfaz conmute de manera selectiva una o más señales transportadas sobre el conector del dispositivo anfitrión para separar rutas de señal, es decir, en la práctica para separar las patillas en una placa de circuito impreso del dispositivo anfitrión, es posible conectar diferentes tipos de módulos SFP al dispositivo anfitrión. Por ejemplo, la presente invención facilita la conexión de una SFP de Gigabit-Ethernet (GE) o de una GPON ONU SFP en el mismo conector SFP del dispositivo anfitrión que es, por ejemplo, una micro/macro/pico estación base de radio (RBS).

En una realización de la presente invención, el dispositivo de conmutación de la interfaz está dispuesto para conmutar de manera selectiva un conjunto de señales transportadas sobre el conector del dispositivo anfitrión a una primera ruta de señal respectiva cuando está en un primer modo de conmutación y a una segunda ruta de señal respectiva separada de la primera ruta de señal cuando está en un segundo modo. En una realización ejemplar, el conjunto de señales transportadas sobre el conector del dispositivo anfitrión comprende una señal TxFault, una señal TxDisable, una señal RateSelect y una señal LOS en el primer modo y al menos una señal 1PPS en el segundo modo. De esta manera, en el caso de, por ejemplo, GE SFP, las señales conmutadas a las patillas PCB del dispositivo anfitrión tendrán su función habitual, mientras que, en el caso, por ejemplo, de una GPON ONU SFP, al menos una de las señales conmutadas a las patillas PCB del dispositivo anfitrión será una sincronización en forma de la 1PPS. La señal 1PPS es un impulso cuyo flanco ascendente indica el comienzo de un segundo. La señal 1PPS debe ser proporcionada a una de las patillas de contacto del conector SFP TxFault, TxDisable, RateSelect y LOS en el lado del módulo SFP del dispositivo anfitrión. Tal como se describirá más detalladamente, el SFP ha sido estandarizado por el grupo SFA MSA, en el que TxFault es una salida de indicación de fallo del transmisor que indica que el controlador láser del módulo SFP ha detectado un fallo láser, TxDisable es una entrada de deshabilitación del transmisor que ordena al controlador láser deshabilitar el láser, RS es una entrada de selección de velocidad con la cual se puede realizar la selección de ancho de banda para soportar estándares de múltiples velocidades, tal como en Fibre Channel, y LOS es una pérdida de señal-salida que indica que no se recibe

En una realización de la presente invención, una señal de hora de día (Time-of-Day, ToD) está dispuesta además para ser recibida sobre el conector de dispositivo anfitrión a través de señales de comunicación entre circuitos integrados (Inter-Integrated Circuit, I2C) cuando dicho conjunto de señales transportadas sobre el conector de dispositivo anfitrión comprende una señal 1PPS. Como alternativa, la señal ToD está dispuesta para estar comprendida en el conjunto de señales transportadas sobre el conector del dispositivo anfitrión cuando el dispositivo de conmutación está en el segundo modo.

En realizaciones adicionales de la presente invención, el modo de conmutación del dispositivo de conmutación está dispuesto para ser controlado por señales I2C transportadas sobre el conector del dispositivo anfitrión. Además, las señales I2C pueden estar dispuestas para definir el tipo de dispositivo conectable con factor de forma pequeño con el que el conector del dispositivo anfitrión está dispuesto para interconectarse. Además, puede conectarse una circuitería lógica I2C a las señales I2C transportadas sobre el conector del dispositivo anfitrión y al dispositivo de conmutación, cuya circuitería lógica I2C determina, a partir de las señales I2C, qué modo de conmutación debería ser seleccionado y causa que el dispositivo de conmutación conmute al modo seleccionado. En todavía otra realización de la presente invención, el tipo de dispositivo conectable con factor de forma pequeño con el que el conector del dispositivo anfitrión está dispuesto para interconectarse está definido por los datos de identificación almacenados en una EPROM del módulo SFP y enviados a través de las señales I2C. Cabe señalar que el bus I2C mencionado anteriormente está incluido en el conector SFP estándar. Sin embargo, podría usarse cualquier otro bus estándar para este propósito, si se incluyera en el conector SFP.

En comparación con el sistema de la técnica anterior, en el que una infraestructura 1588 basada en paquetes debe estar integrada en el módulo SFP, las diversas realizaciones de la presente invención tienen numerosas ventajas. En primer lugar, se requieren pocos componentes de hardware adicionales o ninguno. Una infraestructura 1588 requiere chips Ethernet PHY, lógica de temporización, tal como osciladores de cristal y un bucle o lazo de seguimiento de fase, interfaces, etc. El uso de un bucle de seguimiento de fase implica además una sincronización lenta e inestable. En segundo lugar, el consumo de energía es más alto y las dimensiones son mayores con una infraestructura 1588. En tercer lugar, se requiere software en el módulo SFP para gestionar una pila de protocolo 1588. Con la interfaz de la invención para interconectar un módulo SFP con un dispositivo anfitrión, dicho software no es necesario.

La interfaz para habilitar la interconexión de un dispositivo anfitrión y un dispositivo conectable con factor de forma pequeño según las realizaciones de la presente invención permite, de manera ventajosa, que múltiples tipos de SFP compartan el mismo conector SFP en productos CPE de telecomunicaciones.

Características y ventajas adicionales de la presente invención resultarán evidentes tras un estudio de las reivindicaciones adjuntas y la descripción siguiente. Las personas con conocimientos en la materia comprenderán que pueden combinarse diferentes características de la presente invención para crear realizaciones distintas a las descritas a continuación.

#### Breve descripción de los dibujos

5

10

15

20

25

45

A continuación, la invención se describe, a modo de ejemplo, con referencia a los dibujos adjuntos, en los que:

La Figura 1 ilustra una GPON de la técnica anterior como red de retorno móvil, en la que puede aplicarse la presente invención;

La Figura 2 ilustra una solución de la técnica anterior para transportar señales de sincronización desde un OLT a un dispositivo anfitrión a través de un módulo SFP conectado al dispositivo anfitrión;

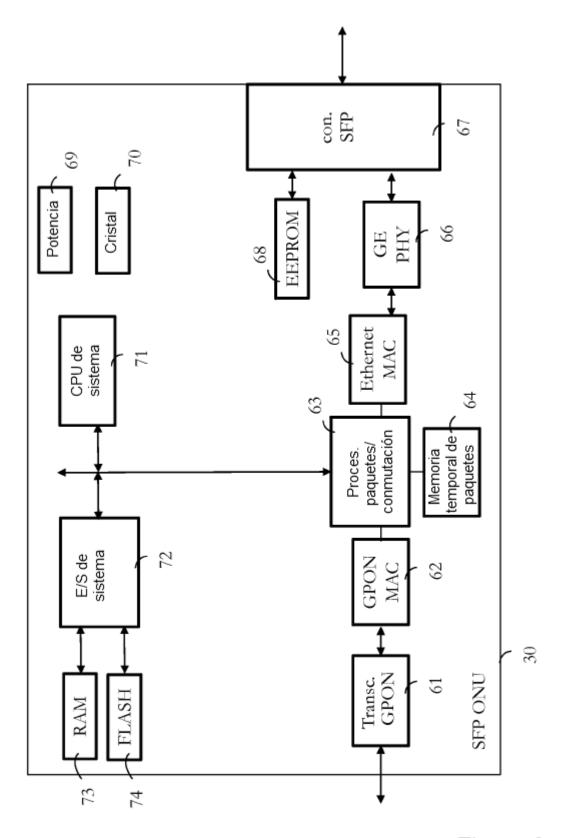

La Figura 3 muestra un ejemplo de SFP ONU de la técnica anterior;

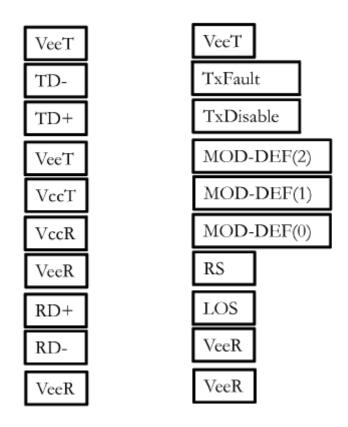

La Figura 4 muestra un conector de módulo SFP estándar;

La Figura 5 ilustra una interfaz según una realización de la presente invención;

La Figura 6 ilustra la interconexión de un OLT, una SFP ONU y un dispositivo anfitrión

La Figura 7 ilustra cómo se sincronizan un pulso 1PPS y datos ToD serie

La Figura 8 ilustra un diagrama de flujo que muestra una realización de un procedimiento según la presente invención; y

La Figura 9 ilustra un diagrama de flujo que muestra una realización adicional de un procedimiento según la presente invención.

### Descripción detallada

- A continuación, la invención se describirá más detalladamente con referencia a los dibujos adjuntos, en los que se muestran ciertas realizaciones de la invención. Sin embargo, la presente invención puede llevarse a la práctica en muchas formas diferentes y no debería ser interpretada como limitada a las realizaciones expuestas en la presente memoria; por el contrario, estas realizaciones se proporcionan a modo de ejemplo con el propósito de que la presente descripción sea completa, y transmita completamente el alcance de la invención a las personas con conocimientos en la materia.

- La presente invención se describe a continuación con referencia a ejemplos particulares. En particular, las realizaciones de la invención se describen en un contexto general no limitativo con relación a una red óptica pasiva con capacidad Gigabit (GPON). Sin embargo, cabe señalar que la invención y sus realizaciones ejemplares pueden aplicarse también en todos los sistemas PON síncronos.

- La Figura 1 ilustra una GPON como una red de retorno móvil. La red 10 óptica transporta tráfico entre las estaciones 11 base y el controlador 12 de estación base. La red 10 óptica comprende un terminal 13 de línea óptica (OLT), una red 14 de distribución óptica (ODN) y varias unidades 15 de red óptica (ONU1, ONU2 ...ONU), en los que puede implementarse la presente invención.

- GPON es sólo una opción de entre muchas en lo que se refiere a una red de retorno móvil. VDSL2, basados en microondas o Gigabit-Ethernet (GE) son otros tipos de red de retorno bien conocidos. Cuál de ellos usar debe decidirse para la estación base de radio (RBS) a desplegar, dependiendo de la infraestructura de red de retorno disponible. De esta manera, un requisito es hacer que las diferentes interfaces de red de retorno sean conectables en el RBS. Esto mantiene la utilización de PCB RBS pequeña y CAPEX bajo. Incluso es necesario permitir que diferentes tipos de SFP (GE SFP,

GPON ONU SFP) se conecten al mismo conector SFP en el RBS. En otras palabras, debe ser posible conectar un módulo GE SFP o un módulo GPON ONU SFP al mismo conector SFP en micro/macro/pico RBS.

En Ethernet, así como en OTN/Fibre Channel, el módulo SFP contiene típicamente las funciones de capa física y dependientes del medio, manteniendo la función del controlador de acceso al medio real (MAC) fuera (típicamente como parte de un conmutador Ethernet en la placa principal). Por lo tanto, el SFP MSA ha especificado las funciones de los veinte pines de contacto de E/S en el conector SFP.

5

10

15

20

25

30

35

40

45

50

55

Un módulo SFP típico contiene estrictamente la capa física y las funciones dependientes del medio, tales como el conector al medio de transmisión (RJ45 para cobre, SC único o LC único/dual para fibra), los componentes del controlador de línea (interfaz ("front-end") analógica para cobre, láser/fotodiodo para fibra (normalmente un BOSA así como un controlador láser y un amplificador limitador), y una CPU con memoria ROM/RAM para controlar las funciones del controlador de línea, el módulo de soporte/identificación de características y supervisión óptica.

La Figura 2 ilustra una solución actual para transportar señales de sincronización desde un OLT a un dispositivo anfitrión a través de un módulo SFP conectado al dispositivo anfitrión. La interfaz SFP estandarizada sólo define enlaces Ethernet serie y señales de gestión I2C, así como señales típicas de transceptor (mostradas en la Figura 4). De esta manera, el OLT 20 recibe una señal de hora de día (ToD) a través de la interfaz 22 y tráfico de datos, siendo suministrados ambos al GPON MAC 24 y además al transceptor 25 de GPON, desde por ejemplo un controlador de estación base (no mostrado) de un proveedor de servicios para su envío a través de ODN/Fibra que cumple con la norma G.984.3. Una SFP ONU 30 recibe las señales en el transceptor 31 GPON y GPON MAC 32. Sin embargo, debido a que no hay soporte para señales de sincronización en el módulo SFP, debe integrarse una infraestructura 1588 basada en paquetes en el módulo SFP (siendo IEEE 1588 un estándar para un protocolo de sincronización de reloj de precisión). Por lo tanto, la señal ToD es extraída y suministrada a la circuitería 34 ToD y al maestro 35 IEEE 1588 al transceptor 36 de Ethernet, mientras que el tráfico de datos es suministrado a la circuitería 38 de conmutación y de procesamiento de paquetes. El transceptor 36 de Ethernet es interconectado a un transceptor 41 correspondiente en el dispositivo 40 anfitrión a través del conector 39 SFP. La señal ToD es extraída por un esclavo 43 IEEE 1588 y es suministrada a una interfaz 44 para una transmisión adicional. El tráfico de datos es suministrado por el transceptor a la circuitería 46 de conmutación y de procesamiento de paquetes.

La Figura 3 muestra un ejemplo del SFP ONU 30 de la técnica anterior. El SFP ONU 30 comprende un transceptor GPON 61 y GPON MAC 62 para comunicarse con un OLT. El transceptor GPON comprende básicamente un diodo láser para la transmisión de datos y un sensor de detección de luz para la recepción de datos. Hay incluida circuitería 63 de conmutación/procesamiento de paquetes para gestionar paquetes de datos y una memoria 64 intermedia de paquetes para poner en cola los datos de paquetes. Además, hay incluida una unidad 65 Ethernet MAC para gestionar el direccionamiento Ethernet MAC en una capa de enlace, así como circuitería 66 GE PHY para conectar la capa de enlace a una capa física Gigabit-Ethernet y comunicarse de esta manera con un dispositivo anfitrión a través del conector SFP 67. Además, el módulo 30 SFP comprende una EEPROM 68 que almacena, por ejemplo, datos de identificación SPF. La EEPROM y los datos de identificación se discutirán más detalladamente a continuación. El SFP ONU 30 comprende también circuitería 69 de potencia para alimentar los diversos componentes incluidos en el módulo SFP y un cristal 70 para generar una señal de reloj con una frecuencia muy precisa. Un componente principal del módulo SFP es una CPU 71 de sistema y periféricos tales como E/S 72 de sistema, RAM 73 para la ejecución de software y Flash 74 para almacenamiento de software. Las funciones de la CPU 71 de sistema incluyen la gestión de una interfaz de control de gestión, el control de otros componentes, tales como el procesamiento de paquetes, la realización de supervisión y el envío de información al OLT, etc.

La Figura 4 muestra un conector SFP estándar. Dicho conector SFP tiene 20 patillas de contacto para transportar señales sobre una interfaz de SFP/dispositivo anfitrión. La funcionalidad de la patilla respectiva se indica en la Figura 4. A continuación, se detallará la funcionalidad de cada patilla y se indicará la disposición o configuración de patillas del conector. Los datos hacia y desde el módulo SFP son normalmente serie diferencial con dos patillas de contacto por dirección (TD+(patilla 19)/TD- (patilla 18) para la transmisión; RD+(patilla 12)/RD- (patilla 13) para la recepción).

VccT (patilla 16) y VeeT (patillas 10, 17 y 20) proporcionan energía de CC a la circuitería del transmisor, mientras que VccR (patilla 15) y VeeR (patillas 1, 2, 11 y 14) proporcionan energía de CC a la circuitería del receptor. Deben usarse todas las patillas de contacto para permitir suficiente corriente al SFP (los GPON ONU SFPs necesitan más energía en comparación con los Ethernet SFPs).

TxFault (patilla 9, indicación de fallo del transmisor, salida) indica que el controlador láser SFP ha detectado un fallo láser y TxDisable (patilla 8, transmisor deshabilitado, entrada) ordena al controlador láser que deshabilite el láser.

MOD-DEF son tres patillas de contacto que definen la interfaz de comunicación I2C del módulo SFP. MOD-DEF 0 (patilla 5) se pone a tierra para indicar que hay presente un módulo SFP, MOD-DEF 1 (patilla 6) es una línea de reloj para la EEPROM I2C y MOD-DEF 2 (patilla 7) es una línea de datos para la EEPROM I2C.

## ES 2 640 970 T3

RS (patilla 4, selección de velocidad, entrada), selección de ancho de banda para soportar estándares de múltiples velocidades, tal como en Fibre Channel. En PONs, esta patilla se usa para la detección de señal TX (indica transmisión de datos TX). En las ONUs y los OLTs, se usa para el disparo de RSSI.

LOS (patilla 3, pérdida de señal, salida), indicación de no recepción de señal.

25

30

40

45

50

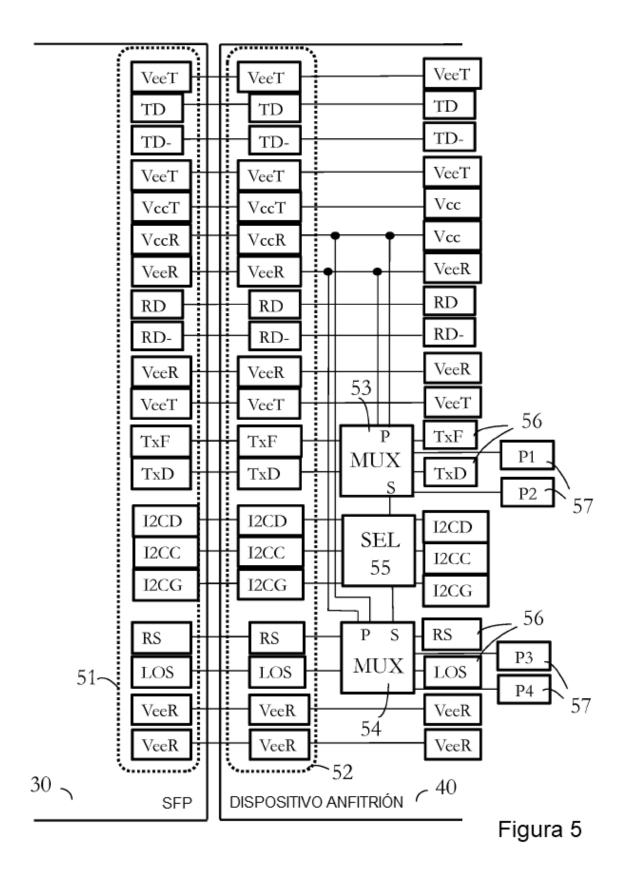

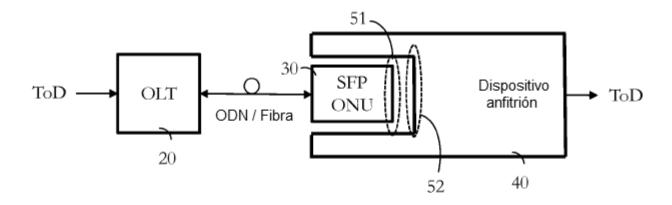

- La Figura 5 ilustra una realización de la presente invención, en la que se proporciona una interfaz que facilita la conexión de un módulo GE SFP o un módulo GPON ONU SFP en el mismo conector SFP de un dispositivo anfitrión. De esta manera, un dispositivo 40 anfitrión es interconectado a un módulo 30 SFP a través de un conector 52 de dispositivo anfitrión dispuesto para recibir un conector 51 SFP coincidente.

- Esto se ilustra adicionalmente en la Figura 6 que muestra el OLT 20, el canal ODN/Fibre, la SFP ONU 30 y el dispositivo 40 anfitrión, todos los cuales se han descrito con referencia a la Figura 2. Tal como puede verse en la Figura 6, la interfaz según las realizaciones de la presente invención está dispuesta en el dispositivo anfitrión e incluye el conector 52 del dispositivo anfitrión dispuesto para recibir el conector 51 del módulo SFP. La interconexión física creada mediante la unión del conector 52 del dispositivo anfitrión al conector 51 del módulo SFP corresponde a la conexión 39 SFP en la Figura 2 (y a la conexión 67 SFP de la Figura 3).

- Con referencia una vez más a la Figura 5, uno o más dispositivos de conmutación materializados en forma de multiplexores 53, 54, están conectados al conector del dispositivo anfitrión y están dispuestos para conmutar de manera selectiva un conjunto de señales TxFault (TxF), TxDisable (TxD), RS y LOS transportadas sobre el conector del dispositivo anfitrión a una primera ruta 56 de señal respectiva indicada por medio de las patillas TxF, TxD, RS, LOS en la placa de circuito impreso (Printed Circuit Board, PCB) del dispositivo anfitrión cuando está en un primer modo de conmutación y a una segunda ruta 57 de señal respectiva, indicada por medio de las patillas P1, P2, P3 y P4, separada de la ruta de la primera señal cuando está en un segundo modo. Las patillas más a la derecha en la Figura 5 están conectadas a diversos componentes en el dispositivo anfitrión, tal como por ejemplo una CPU principal.

- Tal como puede verse, TxFault, TxDisable, LOS y RS son líneas específicas de transceptor típicas empleadas para GE SFPs y normalmente controladas/usadas desde fuera del módulo SFP. En una GPON ONU SFP, esas líneas son controladas por la GPON MAC (o su CPU anfitriona integrada) y son funcionalmente superfluas. Por consiguiente, cualquiera de estas cuatro patillas de contacto puede ser usada para transferir señales de sincronización en la forma de una señal 1PPS y una señal ToD requerida para GPON ONU SFPs.

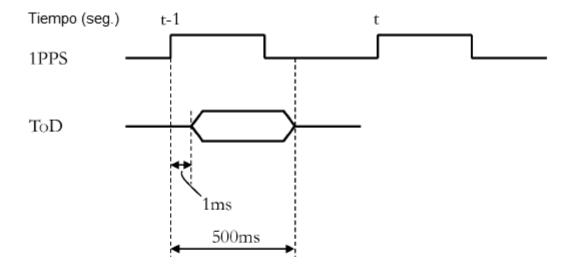

- El transporte de la señal 1PPS y ToD sobre la interfaz SFP desde el módulo ONU SFP al dispositivo anfitrión incluye dos rutas de señal: el impulso 1PPS cuyo flanco ascendente indica el comienzo de un segundo, y los datos ToD serie que comprenden una descripción detallada relacionada con el impulso 1PPS (tal como el tiempo absoluto del 1PPS, el estado y la indicación de calidad del impulso 1PPS, etc.).

- Los datos ToD serie deben ser transmitidos periódicamente. Su periodo será sincronizado con el impulso 1PPS y la transmisión de datos serie deberá completarse antes del comienzo del siguiente impulso 1PPS. La Figura 7 ilustra cómo se sincronizan el impulso 1PPS y los datos ToD serie.

- Diferentes operadores pueden requerir un formato diferente de los datos ToD serie. Se establece un posible formato en la especificación NMEA 0183. Sin embargo, podría usarse cualquier formato.

- Ahora, con referencia una vez más a la Figura 5, con el fin de determinar qué modo de conmutación debería seleccionarse, es decir, si un módulo GE SFP está conectado y las patillas de contacto del conector SFP deben tener su funcionalidad estándar y las señales transportadas a través de las mismas deberían ser transferidas, de esta manera, a las patillas TxF, TxD, RS y LOS correspondientes, o si un módulo GPON ONU SFP está conectado o no y deberían transferirse señales ToD y 1PPS a una cualquiera de las patillas P1-P4, deberían evaluarse las señales transferidas a través de las patillas I2C. El tipo de SFP que requiere señales de sincronización en este contexto se ejemplifica por medio de un GPON ONU SFP. Cabe señalar que otros tipos de módulos SFP que requieren señales de sincronización que deberían poder ser conectados a la interfaz de la presente invención comprenden SFPs de canal de fibra, SFPs de red de transporte óptico (Optical Transport Network, OTN), SFPS para multiplexación por división de onda gruesa (Coarse Wave Division Multiplexing, CWDM) o multiplexación por división de onda densa (Multiplexing (Dense Wave Division Multiplexing, DWDM) y WDM-PON SFPs.

- En el módulo 30 SFP que está conectado al conector 52 del dispositivo anfitrión, hay una EPROM que aloja datos relativos al módulo SFP particular. Estos datos son leídos por la circuitería 55 lógica I2C y controlan los multiplexores 53, 54 a través de la entrada S de selección de manera que se seleccione el modo de conmutación apropiado. Es decir, o bien el módulo SFP es un módulo Ethernet SFP y las señales TxD, TxF, RS y LOS tienen su función ordinaria y se conmutan en un primer modo a las patillas TxD, TxF, RS y LOS correspondientes, respectivamente, o bien el módulo SFP es del tipo indicado anteriormente que requiere sincronización que tiene el efecto de que la señal 1PPS y la señal ToD

sean transportadas en dos cualesquiera de estas cuatro patillas de conector SFP y son conmutadas en un segundo modo a dos patillas P1-P4 cualesquiera en el dispositivo anfitrión. Podrían transportarse además otras señales sobre la interfaz y podrían ser conmutadas en el segundo modo a una patilla P1-P4 cualquiera, por ejemplo, un canal de datos más rápido o señales de uso general. La lógica I2C puede ser un circuito de propósito especial en la forma, por ejemplo, de un ASIC o una FPGA, pero de manera alternativa podría ser implementada por una CPU de dispositivo anfitrión. Los multiplexores podrían ser implementados también por circuitería de propósito especial o por la CPU del dispositivo anfitrión. Aunque en la Figura 5 se muestran dos multiplexores 53, 54 separados, su funcionalidad podría ser implementada perfectamente en un único multiplexor. En caso de que los multiplexores se implementen mediante circuitería de propósito especial, su suministro de energía puede tomarse desde la interfaz de SFP. Una ventaja de tener un hardware de propósito especial para controlar los multiplexores, en lugar de que las señales de selección sean proporcionadas por la CPU del dispositivo anfitrión, es que el propio módulo de SFP puede seleccionar el modo de conmutación. Por otra parte, la implementación del multiplexor o los multiplexores y la circuitería lógica I2C en la CPU del dispositivo anfitrión, no requiere hardware adicional, ya que esta funcionalidad es implementada en software.

5

10

15

20

25

45

50

55

En cualquier caso, la interfaz es configurada (es decir, se selecciona el modo de conmutación de los multiplexores), haciendo que la lógica I2C lea la EPROM SFP a través de las señales I2C. Esto puede hacerse, por ejemplo, leyendo códigos de transceptor (almacenados en direcciones estandarizadas en EPROM SFP), o leyendo el número de pieza, el número de serie, la cadena de copyright, la contraseña (almacenada en la sección definida por el usuario de la EPROM SFP). La lógica I2C puede proporcionar posteriormente a los multiplexores las señales de selección apropiadas para adaptar el modo de conmutación al tipo de módulo SFP acoplado al dispositivo anfitrión. Además, al leer el número de serie, la cadena de copyright y/o la contraseña, la interfaz puede bloquear los tipos de módulos SFP ilegales (tipo no admitido, cadena de copyright/contraseña inválida). En tal caso, el multiplexor pasa algunas o todas las patillas de contacto a un estado de alta resistencia (colector/drenaje abierto), levantándolo efectivamente del bus, si es necesario.

Con referencia adicional a la Figura 5, en todavía otra realización de la interfaz de la presente invención, la señal 1PPS es transferida a través de una cualquiera de las patillas de contacto TxF, TxD, RS o LOS sobre el conector del dispositivo anfitrión y es conmutada por el multiplexor o los multiplexores 53, 54, mientras que la señal ToD es transportada a través de las patillas de contacto I2C. Por lo tanto, la señal ToD es transportada a través de las patillas de contacto I2C desde la EPROM SFP (la sección RAM de la EPROM) y la CPU en los dispositivos anfitriones copia la marca de tiempo proporcionada por la señal ToD a una ubicación de memoria una vez por segundo (estipulada por el impulso 1PPS) enviada sobre otras patillas de contacto del conector.

Los transceptores SFP ópticos modernos soportan funciones de supervisión de diagnóstico digital (Digital Diagnostics Monitoring, DDM) según la norma industrial SFF-8472 vía I2C. Esta característica es conocida también como supervisión digital óptica (Digital Optical Monitoring, DOM). Esta característica proporciona al usuario final la capacidad de supervisar los parámetros en tiempo real del módulo SFP, tales como la energía de salida óptica, la energía de entrada óptica, la temperatura, la corriente de polarización láser y la tensión de alimentación del transceptor. La supervisión de diagnóstico está disponible a través de las señales I2C de la SFP EPROM que comienza en la dirección A2h, y un espacio de direcciones de escritura de usuario (en la dirección 127~247) de 120 bytes es usado normalmente como un área de extensión para las comunicaciones entre el anfitrión y el módulo SFP. En el espacio de direcciones de escritura de usuario, puede incluirse un mensaje ToD de 38 bytes en la dirección 127~165 y puede transferirse sobre las patillas de contacto I2C.

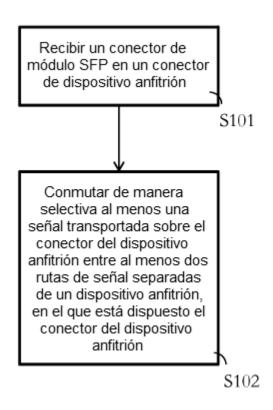

La Figura 8 ilustra un diagrama de flujo que muestra una realización de un procedimiento según la presente invención. En una primera etapa S101, un dispositivo anfitrión recibe un conector de módulo SFP en su conector de dispositivo anfitrión. A continuación, en una segunda etapa S102, al menos una señal transportada sobre el conector del dispositivo anfitrión es conmutada de manera selectiva entre al menos dos rutas de señal separadas del dispositivo anfitrión.

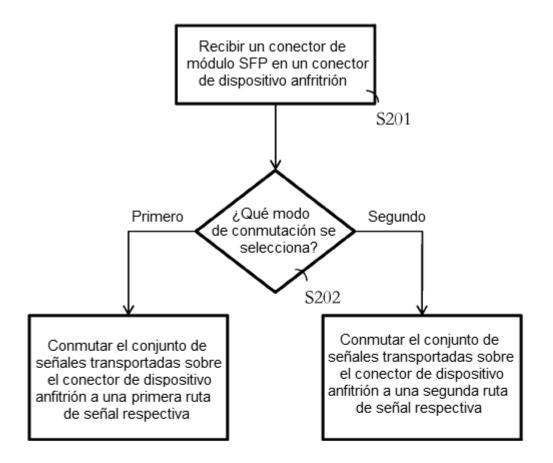

La Figura 9 ilustra un diagrama de flujo que muestra una realización adicional del procedimiento según la presente invención. En una primera etapa S201, un dispositivo anfitrión recibe un conector de módulo SFP en su conector de dispositivo anfitrión. A continuación, en una segunda etapa S202, se determina un modo de conmutación, en el que un conjunto de señales transportadas sobre el conector del dispositivo anfitrión son conmutadas a una primera ruta de señal respectiva en caso de que se determine la ocurrencia de un primer modo de conmutación y son conmutadas a una segunda ruta de señal respectiva, separada de la primera ruta, en caso de que se determine la ocurrencia de un segundo modo de conmutación.

Con referencia adicional a la Figura 9, en todavía otra realización adicional del procedimiento según la presente invención, los modos de conmutación de las etapas S202 se determinan mediante señales transportadas sobre el conector del dispositivo anfitrión; cuando el conjunto de señales transportadas sobre el conector del dispositivo anfitrión comprende una señal TxFault, una señal TxDisable, una señal RateSelect y una señal LOS, se selecciona el primer modo, mientras que, si el conjunto de señales comprende al menos una señal 1PPS, se selecciona el segundo modo.

Para propósitos de sincronización, debería transportarse además una señal ToD sobre el conector del dispositivo anfitrión,

## ES 2 640 970 T3

tal como se ha indicado anteriormente. De esta manera, en todavía una realización adicional del procedimiento según la presente invención, la señal ToD está dispuesta para ser transferida por el conector del dispositivo anfitrión a través de señales I2C cuando el conjunto de señales transportadas sobre el conector del dispositivo anfitrión comprende una señal 1PPS, mientras que, en una realización alternativa del procedimiento, la señal ToD está comprendida en el conjunto de señales que determinan el modo de conmutación.

Aunque la invención ha sido descrita con referencia a realizaciones ejemplares específicas de la misma, muchas alteraciones, modificaciones, etc., diferentes serán evidentes para las personas con conocimientos en la materia. Por lo tanto, las realizaciones descritas no pretenden limitar el alcance de la invención, tal como se define en las reivindicaciones adjuntas.

10

5

#### REIVINDICACIONES

- 1. Interfaz para habilitar la interconexión de un dispositivo (40) anfitrión y un módulo (30) conectable con factor de forma pequeño, en el que dicha interfaz está caracterizada por que comprende:

- un conector (52) de dispositivo anfitrión dispuesto para recibir un conector (51) de módulo conectable de factor de forma pequeño; y

- un dispositivo (53, 54) de conmutación conectado al conector del dispositivo anfitrión y dispuesto para conmutar de manera selectiva un conjunto de señales transportadas sobre el conector del dispositivo anfitrión a una primera ruta (56) de señal respectiva del dispositivo anfitrión cuando está en un primer modo de conmutación y a una segunda ruta (57) de señal respectiva del dispositivo anfitrión separada de la primera ruta de señal cuando está en un segundo modo de conmutación;

- en el que el dispositivo (53, 54) de conmutación está dispuesto para ser configurado en el primer modo de conmutación cuando el conjunto de señales transportadas sobre el conector (52) del dispositivo anfitrión comprende una señal TxFault, una señal TxDisable, una señal RateSelect y una señal LOS, y en el segundo modo de conmutación cuando el conjunto de señales transportadas sobre el conector del dispositivo anfitrión comprende al menos una señal 1PPS, en la que hay dispuesta además una señal de hora de día, ToD, para ser recibida sobre el conector (52) de dispositivo anfitrión a través de señales de circuitería lógica I2C, cuando dicho conjunto de señales transportadas sobre el conector del dispositivo anfitrión comprende la al menos una señal 1PPS.

- 2. Interfaz según la reivindicación 1, en la que:

5

10

15

25

35

- 20 el dispositivo (53, 54) de conmutación está dispuesto para cambiar el modo de conmutación dependiendo de las señales I2C transportadas sobre el conector (52) del dispositivo anfitrión.

- 3. Interfaz según la reivindicación 2, en la que:

- las señales I2C transportadas sobre el conector (52) del dispositivo anfitrión están dispuestas para identificar el tipo del módulo (30) conectable, con factor de forma pequeño, con el que el conector (52) del dispositivo anfitrión está dispuesto para interconectarse.

- 4. Interfaz según una cualquiera de las reivindicaciones 2 o 3, que comprende, además:

- circuitería (55) lógica I2C dispuesta para recibir las señales I2C transportadas sobre el conector (52) del dispositivo anfitrión y dispuesta además para determinar a partir de las señales I2C qué modo de conmutación debería seleccionarse y causar que el dispositivo de conmutación conmute al modo seleccionado.

- 5. Interfaz según una cualquiera de las reivindicaciones 2-4, en la que el tipo del dispositivo conectable, con factor de forma pequeño, con el que el conector (52) de dispositivo anfitrión está dispuesto para interconectarse se define mediante datos de identificación almacenados en una EPROM del módulo (30) conectable, con factor de forma pequeño, y enviados a través de las señales I2C.

- 6. Interfaz según una cualquiera de las reivindicaciones anteriores, en la que el dispositivo (53, 54) de conmutación está dispuesto para ser alimentado por señales VccR y VeeR transportadas sobre el conector (52) del dispositivo anfitrión.

- 7. Interfaz según una cualquiera de las reivindicaciones anteriores, en el que dicho dispositivo de conmutación es un multiplexor (53, 54) dispuesto con una entrada de selección, S, a través de la cual es controlado el modo de conmutación del multiplexor.

- 40 8. Un dispositivo (40) anfitrión que comprende la interfaz según una cualquiera de las reivindicaciones 1-7.

- 9. Un procedimiento para habilitar la interconexión de un dispositivo anfitrión y un módulo conectable, con un factor forma pequeño, en el que dicho procedimiento está caracterizado por que comprende las etapas de:

- recibir (S201) un conector (51) de módulo conectable, con factor de forma pequeño, en un conector (52) de dispositivo anfitrión;

- 45 determinar (S202) un modo de conmutación; y

- conmutar de manera selectiva un conjunto de señales transportadas sobre el conector del dispositivo anfitrión a una primera ruta (56) de señal respectiva de un dispositivo anfitrión en el caso de que se determine la

## ES 2 640 970 T3

ocurrencia de un primer modo de conmutación, y a una segunda ruta (57) de señal respectiva del dispositivo anfitrión en el caso de que se determine la ocurrencia de un segundo modo de conmutación, en el que

la ocurrencia del primer modo de conmutación se determina cuando el conjunto de señales transportadas sobre el conector (52) del dispositivo anfitrión comprende una señal TxFault, una señal TxDisable, una señal RateSelect y una señal LOS; y

5

10

la ocurrencia del segundo modo de conmutación se determina cuando el conjunto de señales transportadas sobre el conector del dispositivo anfitrión comprende al menos una señal 1PPS, una señal hora del día, ToD, dispuesta además para ser recibida sobre el conector (52) de dispositivo anfitrión a través de señales de comunicación entre circuitos integrados, I2C, cuando dicho conjunto de señales transportadas sobre el conector del dispositivo anfitrión comprende la al menos una señal 1PPS.

11

Figura 3

Figura 4

Figura 6

Figura 7

Figura 8

Figura 9