### OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11 Número de publicación: 2 647 817

51 Int. CI.:

**G09G 3/32** (2006.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: 05.11.2014 E 14191844 (1)

(97) Fecha y número de publicación de la concesión europea: 16.08.2017 EP 2884484

(54) Título: Dispositivo de pantalla orgánica emisora de luz que tiene una estructura de píxel de compensación

(30) Prioridad:

13.12.2013 KR 20130155542

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 26.12.2017

(73) Titular/es:

LG DISPLAY CO., LTD. (100.0%) 128, Yeoui-daero Yeongdeungpo-gu Seoul 150-721, KR

72 Inventor/es:

HAN, INHYO y YUN, SANGUK

(74) Agente/Representante:

LLAGOSTERA SOTO, María Del Carmen

#### Descripción

Dispositivo de pantalla orgánica emisora de luz que tiene una estructura de píxel de compensación.

#### REFERENCIA CRUZADA A LA SOLICITUD RELACIONADA

5 Esta solicitud reivindica prioridad de la Solicitud de Patente Coreana Número 10-2013-0155542 presentada el 13 de diciembre de 2013.

#### **ANTECEDENTES DE LA INVENCIÓN**

10 Campo de la Invención

20

55

La presente invención se refiere a un dispositivo de pantalla orgánica emisora de luz.

Descripción de la Técnica Relacionada

15

Los dispositivos de pantalla orgánica emisora de luz que están recientemente en el centro de atención como dispositivos de pantalla de próxima generación tienen ventajas, tales como unas velocidades de respuesta relativamente rápidas, una alta eficiencia y luminancia de emisión de luz y unos amplios ángulos de visión, ya que utilizan diodos emisores de luz orgánicos (OLED) que emiten luz por sí mismos.

Los dispositivos de pantalla orgánica emisora de luz tienen una estructura de matriz en la que están dispuestos píxeles que incluyen diodos emisores de luz orgánica, en los que el brillo de cada píxel seleccionado mediante una señal de escaneado se controla de acuerdo con la escala de grises de datos.

Cada píxel en un dispositivo de pantalla orgánica emisora de luz de este tipo incluye un diodo orgánico emisor de luz (OLED) así como un transistor de accionamiento para controlar el OLED. El transistor de accionamiento tiene unas características exclusivas, como por ejemplo un umbral de voltaje y movilidad. Una diferencia en el valor característico entre los transistores de control de píxeles adyacentes puede reducir la calidad de luminancia de los píxeles correspondientes.

Por lo tanto, el desarrollo de estructuras de píxeles para compensar el voltaje de umbral y la movilidad del transistor de accionamiento está en curso.

Sin embargo, a pesar de dicha tecnología de compensación, la información sobre el voltaje de umbral se pierde por un componente de condensador parásito en el nodo de puerta del transistor de accionamiento, lo cual resulta problemático. La pérdida en la información sobre el voltaje de umbral puede conducir a una calidad de imagen no uniforme severa.

US 2010/289830 describe un dispositivo de pantalla que incluye un circuito de píxeles para generar un valor de señal para visualización sintetizando valores de señal introducidos en un período horizontal, y creando una visualización en una gradación que corresponde al valor de señal para visualización, una línea de señal dispuesta en forma de columna en una matriz de píxeles en que el circuito de píxeles está dispuesto en forma de matriz, una línea de escaneado dispuesta en forma de una fila en la matriz de píxeles, una sección de accionamiento de línea de señal configurada para enviar valores de señal como un valor de señal que se suministra a cada circuito de píxeles para la línea de señal en cada período horizontal, y una sección de activación de línea de escaneado configurada para introducir secuencialmente los valores de señal en un período horizontal, en que los valores de señal se generan en la línea de señal, en el circuito de píxeles en cada fila activando la línea de escaneado. US 2010/289830 describe asimismo que el circuito de píxeles incluye un elemento emisor de luz, un transistor de accionamiento para aplicar una corriente correspondiente a dicho valor de señal para visualización, en que dicho valor de señal para visualización

se introduce en el transistor de accionamiento, en dicho elemento emisor de luz, una capacitancia que tiene un extremo como punto de introducción de dicho valora de señal para visualización en un nodo de puerta de dicho transistor de accionamiento, un primer elemento de conmutación conectado entre dicho extremo de dicha capacitancia y dicha línea de señal, y cuya conducción es controlada por un potencial de una primera línea de escaneado, y un segundo elemento de conmutación conectado entre otro extremo de dicha capacitancia y dicha línea de señal, y cuya conducción es controlada por un potencial de una segunda línea de escaneado, y cuando dicho primer valor de señal se encía a dicha línea de señal, dicha sección de accionamiento de línea de escaneado hace que dicho primer elemento de conmutación introduzcan dicho primer alor de señal a dichos ambos extremos de dicha escania de linea de conmutación introduzcan dicho primer valor de señal a dichos ambos extremos de dicha escania de linea de conmutación introduzcan dicho primer valor de señal a dichos ambos extremos de dicha escania de linea de conmutación introduzcan dicho primer valor de señal a dichos ambos extremos de dicha escania de linea de conmutación introduzcan dicho primer valor de señal a dichos ambos extremos de dicha escania de linea de conmutación introduzcan dicho primer valor de señal a dichos ambos extremos de dicha escana de linea de conmutación introduzcan dicho primer valor de señal de linea de conmutación introduzcan dicho primer valor de señal de linea de señal de linea de conmutación introduzcan dicho primer valor de señal a dichos ambos extremos de dicha escana de linea de conmutación introduzcan dicho primer valor de señal de linea de li

capacitancia, y cuando dicho segundo valor de señal se envía a dicha línea de señal, dicha sección de activación de línea de señal hace que solamente dicho segundo elemento de conmutación introduzca dicho segundo valor de señal en dicho otro extremo de dicha capacitancia, por lo que dicho valor de señal para visualización que es el resultado de la síntesis de dicho primer valor de señal y dicho segundo valor de señal se obtiene en dicho punto de introducción.

US 2013/249857 describe un dispositivo semiconductor (por ejemplo, un dispositivo emisor de luz, un dispositivo de pantalla) que incluye un primer cableado, un primer condensador, un segundo condensador, un primer conmutador que tiene una función de controlar la conexión eléctrica entre el primer cableado y uno de un par de electrodos del segundo condensador, un segundo cableado, un transistor de una fuente y un drenaje los cuales están conectados al segundo cableado y una puerta que está conectada eléctricamente al otro de los dos electrodos del primer condensador, un segundo condensador que tiene una función de controlar la conexión eléctrica entre la puerta del transistor y la de la fuente y el drenaje del transistor, y un tercer conmutador que tiene una función de controlar la conexión eléctrica entre el otro de la fuente y el drenaje del transistor y uno de los dos electrodos del primer condensador y entre el otro de la fuente y el drenaje del transistor y uno de los dos electrodos del segundo condensador.

WO 2013/021623 y US 2014/022288 describen un método de accionamiento de un aparato de pantalla que 15 incluye una pluralidad de circuitos de píxeles en matriz. Cada uno de los circuitos de píxeles incluye un dispositivo emisor de luz de corriente, un transistor de accionamiento que suministra corriente al dispositivo emisor de luz de corriente, un primer condensador que tiene un primer terminal conectado a una puerta del transistor de accionamiento, un segundo condensador conectado entre un segundo terminal del primer condensador y una fuente del transistor de accionamiento, un primer conmutador que aplica un voltaje de 20 referencia a la puerta del transistor de accionamiento, un segundo conmutador que suministra un voltaje de señal de imagen a un nodo en el cual están conectados el primer y el segundo condensador, un tercer conmutador que suministra un voltaje de inicialización a la fuente del transistor de accionamiento, y un cuarto conmutador configurado para cortocircuitar el primer condensador. El método de accionamiento incluye: (a) dividir un período de fotograma en un período de inicialización, un período de detección de 25 umbral, un período de escritura y un período de luminiscencia, (b) aplicar, en el período de inicialización, un voltaje diferencial entre el voltaje de referencia y el voltaje de inicialización al segundo condensador estableciendo el segundo conmutador en APAGADO y estableciendo el primer, el tercer y el cuarto condensadores en ENCENDIDO; (c) reduciendo, en el período de detección de umbral, el voltaje del segundo condensador cerrando una trayectoria de corriente formada por el segundo condensador y el 30 transistor de accionamiento, en que la trayectoria de la corriente se cierra estableciendo el segundo y el tercer conmutador en APAGADO y el primer y el cuarto conmutador en ENCENDIDO, (d) aplicando, en el período de escritura, un voltaje diferencial entre el voltaje de referencia y el voltaje de señal de imagen en el primer condensador estableciendo el tercer y el cuarto conmutador en APAGADO y el primer y el tercer conmutador en ENCENDIDO, y (e) aplicando, en el período de luminiscencia, una corriente al transistor de 35 accionamiento y al dispositivo emisor de luz corriente correspondiente al voltaje de señal de imagen, estableciendo el primer, el segundo, el tercer y el cuarto conmutadores en APAGADO.

US 2005/057182 describe un aparato de pantalla de tipo matriz activa que incluye un elemento autoluminiscente que está conectado a una primera fuente de alimentación de voltaje y que emite luz de acuerdo

con una corriente eléctrica suministrada, un transistor de accionamiento que está conectado entre una

segunda línea de fuente de alimentación de voltaje y el elemento auto-luminiscente y que controla una

cantidad de corriente eléctrica suministrada al elemento auto-luminiscente de acuerdo con un voltaje de

control de puerta, un primer conmutador formado por un transistor y conectado entre una puerta y un drenaje

del transistor de accionamiento, una primera capacitancia conectada a la puerta, un segundo conmutador

formado por un transistor y conectado entre el drenaje del transistor de accionamiento y el elemento autoluminiscente, y una segunda capacitancia conectada entre el segundo conmutador y la puerta del transistor

de accionamiento.

#### **BREVE RESUMEN DE LA INVENCIÓN**

50

55

60

Varios aspectos de la presente invención proporcionan un dispositivo de pantalla orgánica emisora de luz que tiene una estructura de píxel capaz de mejorar significativamente la capacidad y el intervalo de compensación de voltaje de umbral compensando una pérdida en un voltaje de umbral que se produciría durante el funcionamiento.

También se proporciona un dispositivo de pantalla orgánica emisora de luz que tiene una estructura de píxel capaz de compensar la movilidad y controlar un tiempo de compensación de movilidad basándose en un diseño de condensador dentro de la estructura de píxel, logrando así un tiempo de escritura de datos suficiente.

También se proporciona un dispositivo de pantalla orgánica emisora de luz que tiene una estructura de píxel que tiene unas características de uniformidad global superiores.

En un aspecto de la presente invención, se proporciona un dispositivo de pantalla orgánica emisora de luz de acuerdo con la reivindicación 1.

En una o más formas de realización, cada uno de los píxeles comprende, además: un tercer transistor controlado por una tercera señal de escaneado, en que el tercer transistor está conectado entre el primer nodo del transistor de accionamiento y el nodo de retención.

- 5 En una o más formas de realización, una capacitancia del segundo condensador de almacenamiento es menor que una capacitancia del primer condensador de almacenamiento o una capacitancia del condensador de refuerzo.

- En una o más formas de realización, un voltaje de accionamiento suministrado a través de la línea de voltaje de accionamiento es un voltaje de corriente alterna, y cada uno de los píxeles realiza una operación de inicialización, una operación de detección de voltaje de umbral, una operación de escritura y compensación de movilidad y una operación de emisión.

- En una o más formas de realización, en la operación de inicialización, se aplica un voltaje de accionamiento de bajo nivel al tercer nodo del transistor de accionamiento, se encienden el primer y el tercer transistores, y se desconecta el segundo transistor, de modo que el nodo de retención y el primer nodo del transistor de accionamiento se inicializan mediante un voltaje de fuente, y el segundo nodo del transistor de accionamiento se inicializa mediante el voltaje de accionamiento de bajo nivel.

- En una o más formas de realización, en la operación de detección de voltaje de umbral, se aplica un voltaje de accionamiento de alto nivel al tercer nodo del transistor de accionamiento, el primer transistor se mantiene en un estado encendido, el segundo transistor se apaga, y el tercer transistor se mantiene en un estado apagado, de modo que el primer nodo del transistor de accionamiento se mantiene en el voltaje de la fuente, aumenta el voltaje en el segundo nodo del transistor de accionamiento y aumenta el voltaje en el nodo de retención de acuerdo con un cambio de voltaje en el segundo nodo del voltaje de accionamiento y una primera relación de capacitancia.

- En una o más formas de realización, el voltaje en el nodo de retención aumenta a un voltaje obtenido multiplicando el cambio de voltaje en el segundo nodo del voltaje de accionamiento con la primera relación de capacitancia, y la primera relación de capacitancia es un valor obtenido dividiendo la capacitancia del segundo condensador de almacenamiento por un total de la capacitancia del condensador de refuerzo y la capacitancia del segundo condensador de almacenamiento.

- En una o más formas de realización, en la operación de escritura de datos y detección de movilidad, se aplica un voltaje de datos al segundo transistor a través de la línea de datos correspondiente, se aplica un voltaje de accionamiento de alto nivel al tercer nodo del transistor de accionamiento, se apaga el primer transistor, y se enciende el segundo transistor, de modo que aumenta el voltaje en el nodo de retención, un voltaje en el segundo nodo del transistor de accionamiento aumenta de acuerdo con la operación de detección de movilidad y un voltaje en el primer nodo del transistor de accionamiento aumenta de acuerdo con un cambio de voltaje en el nodo de retención, un cambio de voltaje en el segundo nodo del transistor de accionamiento, una segunda relación de capacitancia y una tercera relación de capacitancia.

- En una o más formas de realización, el voltaje en el primer nodo del transistor de accionamiento aumenta en un total de un voltaje obtenido multiplicando el cambio de voltaje en el nodo de retención con la segunda relación de capacitancia y un voltaje obtenido multiplicando el cambio de voltaje en el segundo nodo del transistor de accionamiento por la tercera relación de capacitancia.

- En una o más formas de realización, la segunda relación de capacitancia es un valor obtenido dividiendo la capacitancia del condensador de refuerzo por un total de la capacitancia del primer condensador de almacenamiento y la capacitancia del condensador de refuerzo, y la tercera relación de capacitancia es un valor obtenido dividiendo la capacitancia del primer condensador de almacenamiento por el total de la capacitancia del primer condensador de almacenamiento y la capacitancia del condensador de refuerzo.

- En una o más formas de realización, la tercera relación de capacitancia determina una velocidad a la cual disminuye una diferencia de voltaje entre el primer nodo y el segundo nodo del transistor de accionamiento.

- En una o más formas de realización, en la operación de emisión, el transistor de accionamiento, el primer transistor, el segundo transistor y el tercer transistor se apagan, y el diodo emisor de luz orgánica emite luz mientras que el voltaje en el segundo nodo del transistor de accionamiento aumenta.

- En una o más formas de realización, la capacitancia del segundo condensador de almacenamiento determina una cantidad a controlar en la compensación de una pérdida en la información de voltaje de umbral causada por un condensador parásito del primer nodo del transistor de accionamiento.

- En una o más formas de realización, un voltaje de accionamiento suministrado a través de la línea de voltaje de accionamiento es un voltaje de corriente continua, y cada uno de los píxeles realiza una operación de inicialización, una operación de detección de voltaje de umbral, una operación de escritura de datos y

compensación de movilidad y una operación de emisión, comprendiendo cada uno de los otros píxeles un cuarto transistor conectado entre el segundo nodo del transistor de accionamiento y una línea de voltaje de inicialización, estando el cuarto transistor controlado por la tercera señal de escaneado mediante la cual se controla el tercer transistor.

5

10

En una o más formas de realización, en la operación de inicialización, el voltaje de accionamiento se aplica al tercer nodo del transistor de accionamiento, y el primer transistor, el tercer transistor y el cuarto transistor se encienden, y el segundo transistor se apaga, de manera que el nodo de retención y el primer nodo del transistor de accionamiento son inicializados por un voltaje de fuente, y el segundo nodo del transistor de accionamiento se inicializa mediante un voltaje de inicialización.

En una o más formas de realización, un voltaje de accionamiento suministrado a través de la línea de voltaje de accionamiento es un voltaje de corriente alterna.

15

En una o más formas de realización, el nodo de retención es inicializado por un voltaje aplicado a través de la línea de datos correspondiente, en que el voltaje aplicado a través de la línea de datos comprende un voltaje de datos de inicialización de nivel bajo y un voltaje de datos de nivel alto que se alterna con el voltaje de datos de inicialización de nivel bajo, y el segundo transistor repite en encendido y apagado por medio de una línea horizontal.

20

25

En una o más formas de realización, cada uno de los píxeles comprende además un tercer transistor conectado entre el segundo nodo del transistor de accionamiento y una línea de voltaje de inicialización, en que el tercer transistor está controlado por la segunda señal de escaneado por medio de la cual se controla el segundo transistor, en que se suministra un voltaje de accionamiento a través de la línea de voltaje de accionamiento, que es un voltaje de corriente continua.

En otro aspecto de la presente invención, se proporciona un dispositivo de pantalla orgánica emisora de luz de acuerdo con la reivindicación 10.

En otro aspecto de la presente invención, se proporciona un dispositivo de pantalla orgánica emisora de luz de acuerdo con la reivindicación 12.

En otro aspecto de la presente invención, se proporciona un dispositivo de pantalla orgánica emisora de luz de acuerdo con la reivindicación 13.

35

Las formas de realización preferentes se describen en las reivindicaciones dependientes.

De acuerdo con la presente invención tal como se establece anteriormente, el dispositivo de pantalla orgánica emisora de luz tiene la estructura de píxel capaz de mejorar significativamente la capacidad y el intervalo de compensación de voltaje de umbral compensando una pérdida en un voltaje de umbral que se produciría durante el funcionamiento.

Además, el dispositivo de pantalla orgánica emisora de luz tiene la estructura de píxel capaz de compensar la movilidad y controlar un tiempo de compensación de movilidad basándose en un diseño de condensador dentro de la estructura de píxel, logrando así un tiempo de escritura de datos suficiente.

Además, dispositivo de pantalla orgánica emisora de luz tiene la estructura de píxel que tiene unas características superiores de uniformidad global.

#### 50 BREVE DESCRIPCIÓN DE LOS DIBUJOS

El anterior y otros objetos, características y ventajas de la presente invención se entenderán más claramente a partir de la siguiente descripción detallada cuando se toma junto con los dibujos adjuntos, en los cuales:

55

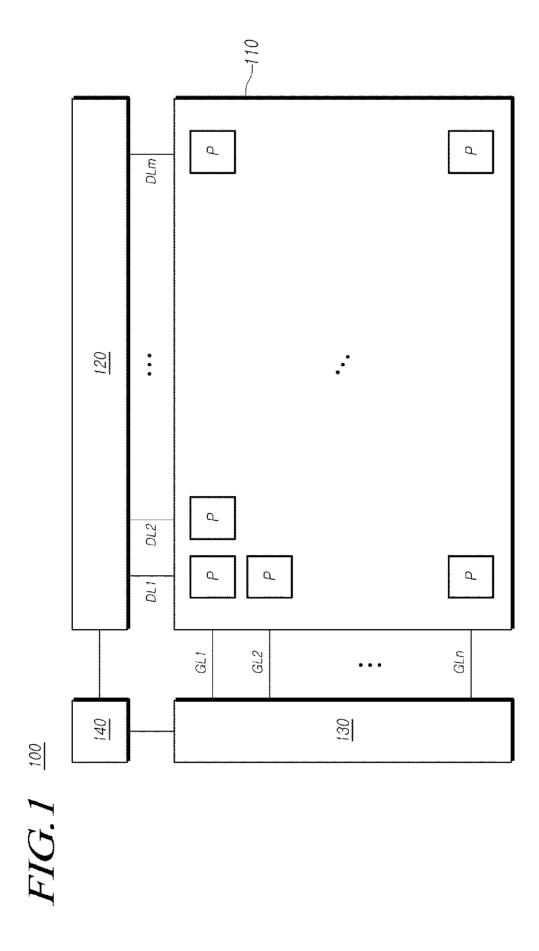

la FIG. 1 es una vista esquemática de la configuración del sistema que ilustra un dispositivo de pantalla orgánica emisora de luz de acuerdo con las formas de realización ejemplares de la presente invención;

60

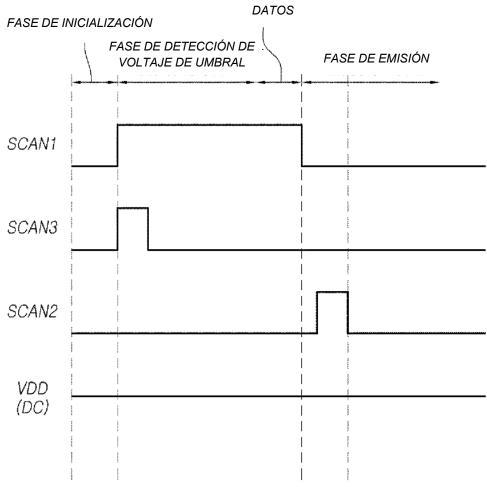

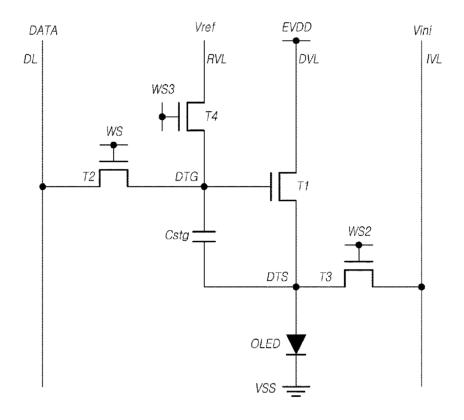

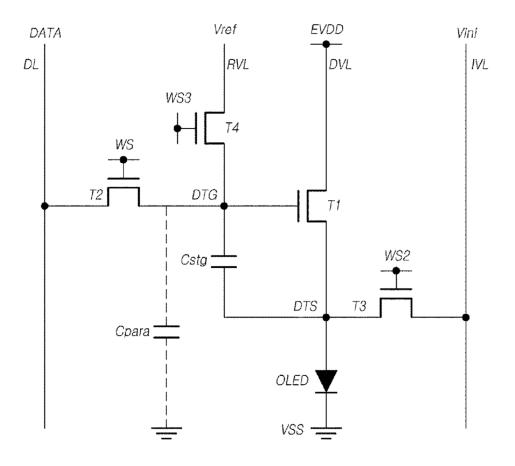

la FIG. 2 es un diagrama de circuito equivalente que ilustra una estructura de píxel de un dispositivo de pantalla orgánica emisora de luz de acuerdo con un ejemplo comparativo; la FIG. 3 es un diagrama de temporización de funcionamiento de un píxel que tiene la estructura de píxel del dispositivo de pantalla orgánica emisora de luz de acuerdo con un ejemplo comparativo;

65

la FIG. 4 es un diagrama de circuito que ilustra un componente de condensador parásito de la estructura de píxel del dispositivo de pantalla orgánica emisora de luz de acuerdo con un ejemplo comparativo;

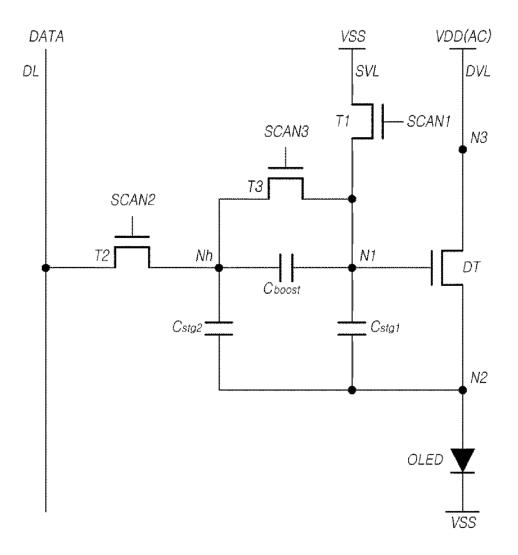

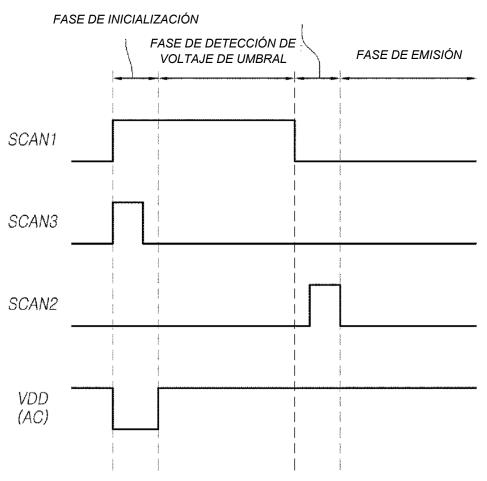

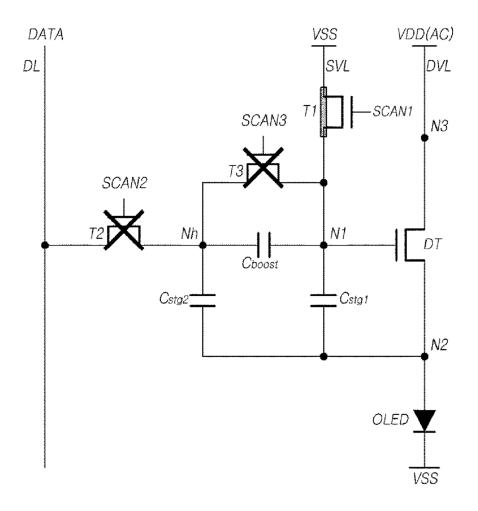

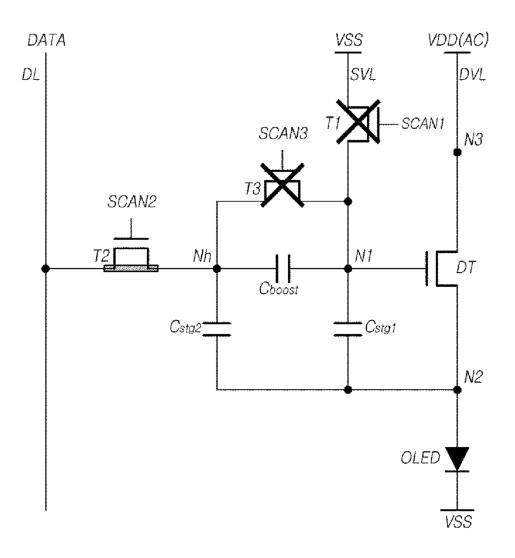

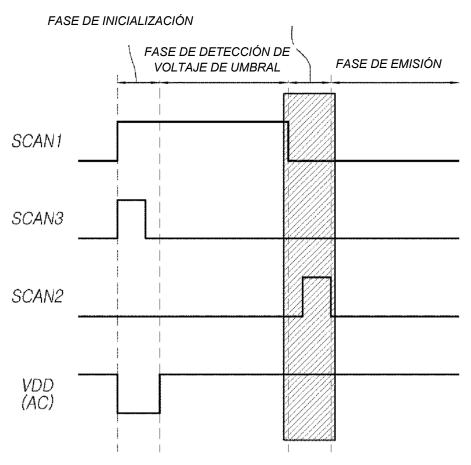

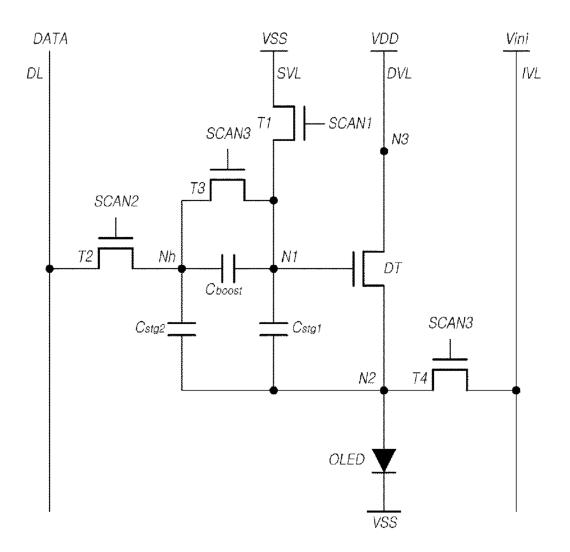

la FIG. 5 es un diagrama de circuito equivalente que ilustra una estructura de píxel de un

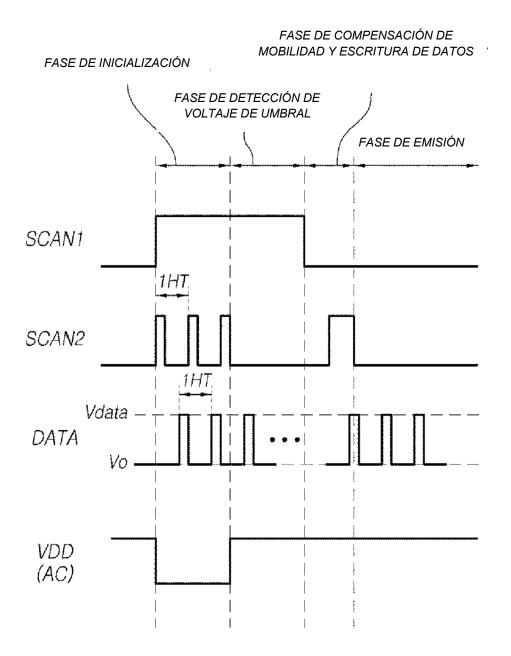

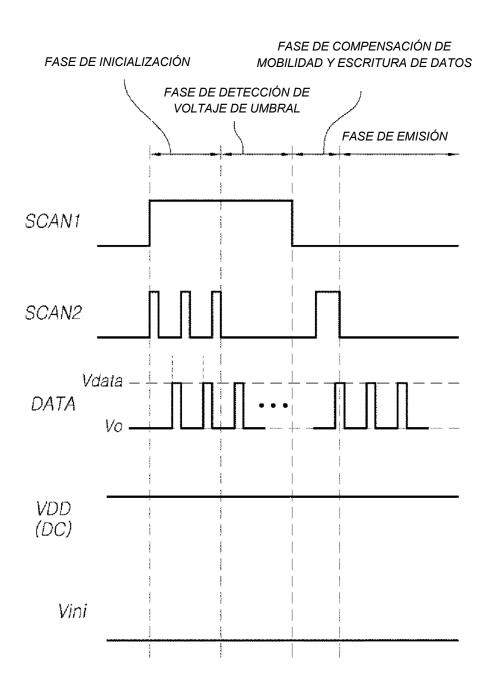

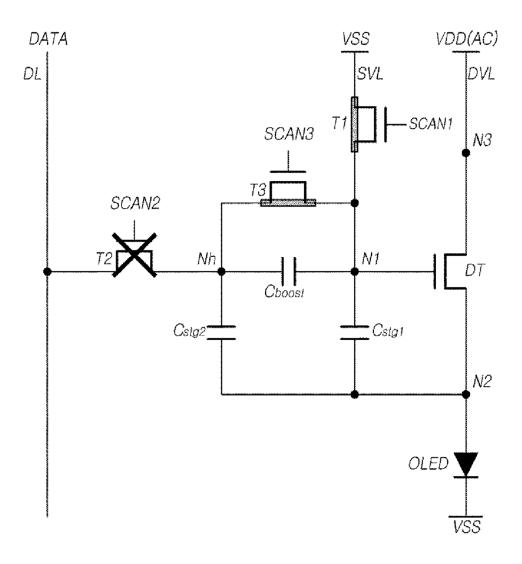

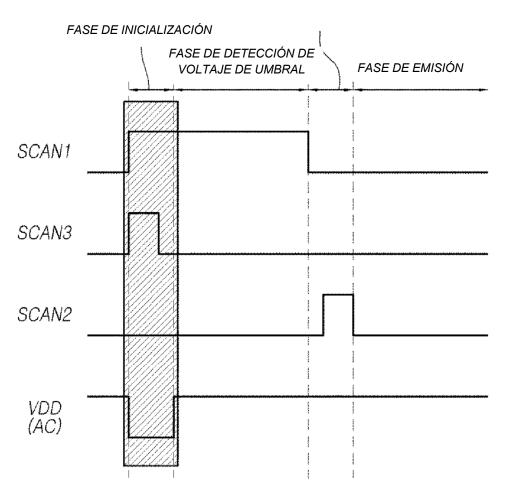

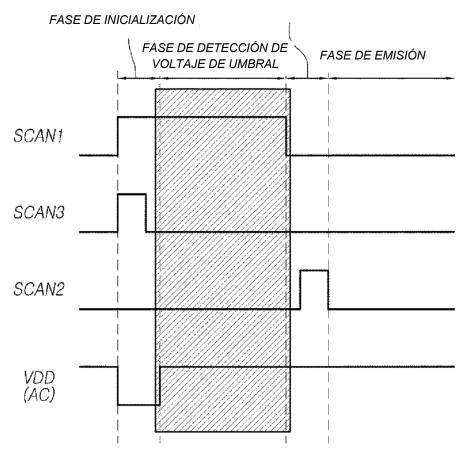

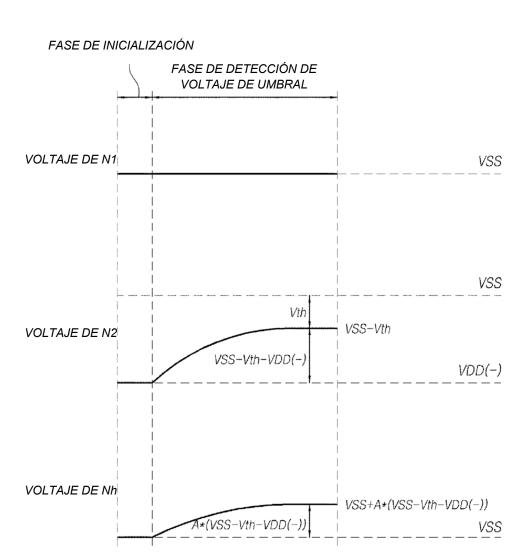

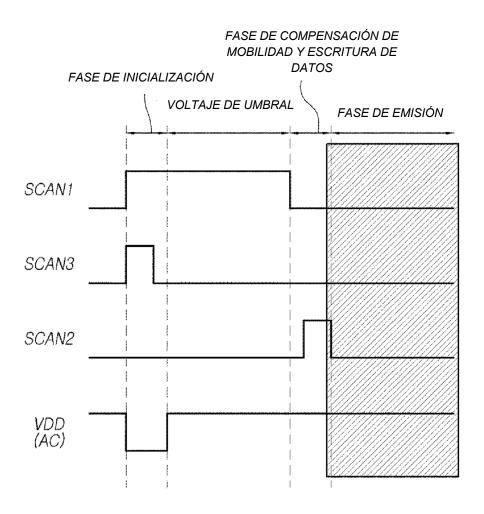

dispositivo de pantalla orgánica emisora de luz de acuerdo con una segunda forma de realización ejemplar de la presente invención; la FIG. 6 es un diagrama de temporización de funcionamiento de un píxel que tiene la 5 estructura de píxel del dispositivo de pantalla orgánica emisora de luz de acuerdo con la primera forma de realización ejemplar: las FIG. 7A, FIG. 7B, FIG. 8A, FIG. 8B, FIG. 9, FIG. 10A, FIG. 10B, FIG. 11, FIG. 12A y FIG. 12B son diagramas de circuito que ilustran el funcionamiento de acuerdo con los pasos y gráficos del proceso que ilustran los cambios de voltaje en los principales nodos en la 10 estructura de píxel del dispositivo de pantalla emisora de luz orgánica de acuerdo con la primera forma de realización ejemplar; las FIG. 13A, FIG. 13B, FIG. 14A, FIG. 14B, FIG. 15A, FIG. 15B y FIG. 16 son gráficos que ilustran una variedad de simulaciones en la estructura de píxel del dispositivo de pantalla orgánica emisora de luz de acuerdo con la primera forma de realización ejemplar; 15 la FIG. 17 es un diagrama de circuito equivalente que ilustra una estructura de píxel de un dispositivo de pantalla orgánica emisora de luz de acuerdo con una segunda forma de realización ejemplar de la presente invención; la FIG. 18 es un diagrama de temporización de funcionamiento de un píxel que tiene la estructura de píxel del dispositivo de pantalla orgánica emisora de luz de acuerdo con la 20 segunda forma de realización eiemplar: la FIG. 19 es un diagrama de circuito equivalente que ilustra una estructura de píxel de un dispositivo de pantalla orgánica emisora de luz de acuerdo con una tercera forma de realización ejemplar de la presente invención; las FIG. 20 y FIG. 21 son un diagrama de temporización de funcionamiento y un gráfico de 25 cambio de voltaje en nodos principales en la estructura de píxel del dispositivo de pantalla orgánica emisora de luz de acuerdo con la tercera forma de realización ejemplar; la FIG. 22 es un diagrama de circuito equivalente que ilustra una estructura de píxel de un dispositivo de pantalla orgánica emisora de luz de acuerdo con una cuarta forma de realización ejemplar de la presente invención; y 30 la FIG. 23 es un diagrama de funcionamiento de un píxel que tiene la estructura de píxel del dispositivo de pantalla orgánica emisora de luz de acuerdo con la cuarta forma de realización

#### **DESCRIPCION DETALLADA DE LA INVENCIÓN**

ejemplar.

35

40

45

50

60

A continuación, se hará referencia en detalle a la presente invención, cuyas formas de realización se ilustran en los dibujos adjuntos. A lo largo de este documento, se debe hacer referencia a los dibujos, en los que se pueden utilizar los mismos números de referencia y signos a lo largo de los diferentes dibujos para designar los mismos componentes o similares. En la siguiente descripción de la presente invención, se omitirán las descripciones detalladas de las funciones y componentes conocidos incorporados en el presente documento en el caso de que el tema de la presente invención pueda quedar poco claro por ello.

También se entenderá que, aunque términos tales como "primero", "segundo", "A", "B", "(a)" y "(b)" se pueden utilizar en este documento para describir varios elementos, tales términos se utilizan solamente para distinguir un elemento de otro elemento. La sustancia, secuencia, orden o número de estos elementos no está limitado por estos términos. Se entenderá que cuando se hace referencia a un elemento como "conectado a" o "acoplado a" otro elemento, no solo puede estar "directamente conectado" o "acoplado" al otro elemento, sino que también puede estar "indirectamente" conectado o acoplado a "el otro elemento a través de un elemento" interviniente". En el mismo contexto, se entenderá que cuando se hace referencia a un elemento como formado "sobre" o "debajo" de otro elemento, no solo puede estar formado directamente sobre o debajo de otro elemento, sino que también puede estar formado indirectamente en o bajo otro elemento a través de un elemento intermedio.

La FIG. 1 es una vista esquemática de la configuración del sistema que ilustra un dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con las formas de realización ejemplares de la presente invención.

Con referencia a la FIG. 1, el dispositivo de pantalla orgánica emisora de luz incluye un panel de pantalla 110 en el que están dispuestas una pluralidad de líneas de datos DL1 a DLm y una pluralidad de líneas de puerta GL1 a GLn de manera que se define un número de píxeles P, un controlador de datos 120 para conducir las líneas de datos LD1 a DLm, un controlador de puerta 130 para accionar las líneas de puerta GL1 a GLn, y un controlador de temporización 140 para controlar el controlador de datos 120 y el controlador de puerta 130.

El controlador de datos 120 puede incluir una pluralidad de circuitos integrados del controlador de datos (también denominados circuitos integrados del controlador de fuente) que pueden estar conectados a las almohadillas de unión del panel de pantalla 110 mediante un método de unión automática por cinta (TAB)

o un método de chip en el cristal (COG), puede estar formado directamente en el panel de pantalla 110 mediante un método de puerta en panel (GIP), o puede estar integrado en el panel de pantalla 110.

El controlador de puerta 130 puede estar posicionado solo en un lado del panel de pantalla 110 tal como se ilustra en la FIG. 1 o puede estar dividido en dos secciones, cada una de las cuales está posicionada a cada lado del panel de pantalla 110.

10

15

40

45

50

- El controlador de puerta 130 puede proporcionar a cada uno de los píxeles una o más señales de escaneado de acuerdo con varias estructuras de píxeles, que se describirán más adelante.

- Además, el controlador de puerta 130 puede incluir una pluralidad de circuitos integrados de controlador de puerta que se pueden conectar a las almohadillas de unión del panel de pantalla mediante un método de unión automática por cinta (TAB) o un método de chip en vidrio (COG), pueden estar formados directamente en el panel de pantalla 110 mediante un método de puerta en panel (GIP), o pueden estar integrados en el panel de pantalla 110.

- El controlador de temporización 140 controla la temporización de funcionamiento del controlador de datos 120 y el controlador de puerta 130, y emite una variedad de señales de control con esta finalidad.

- Cada uno de los píxeles del dispositivo de pantalla orgánica emisora de luz 100 incluye un diodo emisor de luz orgánica (OLED) y un circuito para accionar el OLED.

- El circuito para accionar el OLED incluye un transistor de accionamiento para suministrar una corriente al OLED, un transistor de conmutación para aplicar un voltaje de datos a un nodo de puerta del transistor de accionamiento y un condensador de almacenamiento para mantener un voltaje de datos durante el período de un fotograma. El circuito puede incluir además al menos un transistor para compensar el voltaje de umbral Vth y la movilidad del transistor de accionamiento.

- Las estructuras de píxeles pueden variar de acuerdo con los números y las estructuras de conexión de los transistores y los condensadores incluidos en el circuito.

- Se hará referencia a cinco estructuras de píxeles de acuerdo con un ejemplo comparativo y cuatro formas de realización ejemplares de la presente invención.

- En primer lugar, se describirá una estructura de píxel que incluye cuatro transistores y un condensador de acuerdo con un ejemplo comparativo con referencia a la FIG. 2 a la FIG. 4.

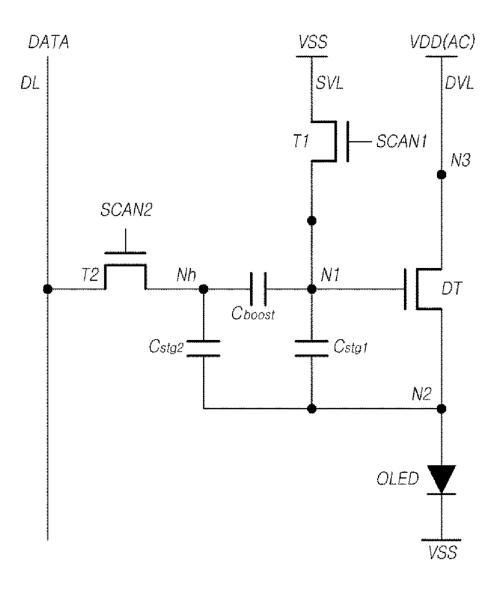

- La FIG. 2 es un diagrama de circuito equivalente que ilustra la estructura de píxel de un dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con el ejemplo comparativo.

- Con referencia a la FIG. 2, cada píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización tiene una estructura de píxel que incluye un diodo emisor de luz orgánica (OLED), un primer transistor T1 conectado entre una línea de voltaje de accionamiento DVL a través de la cual se suministra un voltaje de accionamiento EVDD y el OLED, un segundo transistor T2 conectado entre una línea de datos DL y un nodo de puerta DTG del primer transistor T1, un tercer transistor T3 conectado entre un nodo fuente DTS del primer transistor T1 y una línea de voltaje de inicialización IVL a través de la cual se suministra un voltaje de inicialización Vini, un cuarto transistor T4 conectado entre una línea de voltaje de referencia a través de la cual se suministra un voltaje de referencia Vref y el nodo de puerta DTG del primer transistor T1 y un condensador de almacenamiento Cstg conectado entre el nodo de puerta DTG

- El primer transistor T1 es un transistor de accionamiento para operar el OLED.

y el nodo fuente DTS del primer transistor T1.

- Aunque los cuatro transistores T1 a T4 se ilustran como un tipo N, esto es meramente un ejemplo ilustrativo, y los cuatro transistores pueden diseñarse para ser de un tipo P.

- Se dará una descripción de un método de funcionamiento de cada píxel que tiene esta estructura de píxel con referencia a un diagrama de temporización de funcionamiento ilustrado en la FIG. 3.

- 60 La FIG. 3 es el diagrama de temporización de funcionamiento de un píxel que tiene la estructura de píxel del dispositivo de pantalla orgánica emisora de luz de acuerdo con el ejemplo comparativo.

- Con referencia a la FIG. 3, el píxel que tiene la estructura de pixeles del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización lleva a cabo una operación que incluye una etapa de inicialización, una etapa de detección de voltaje de umbral, una etapa de escritura de datos y compensación de movilidad y una etapa de emisión.

Con referencia a la FIG. 3, en la etapa de inicialización, el segundo transistor T2 está apagado, y el cuarto transistor T4 y el tercer transistor T3 están encendidos, de modo que el nodo de puerta DTG y el nodo fuente DTS del primer transistor T1 se inicializan respectivamente con un voltaie de referencia Vref y un voltaie de inicialización Vini.

5

Con referencia a la FIG. 3, en la etapa de detección de voltaje de umbral, el tercer transistor T3 se desconecta, y el nodo fuente DTS del primer transistor T1 detecta un voltaje de umbral del primer transistor T1. Es decir, el voltaje Vs en el nodo de fuente DTS del primer transistor T1 puede expresarse incluyendo el voltaje de umbral (Vs = Vref-Vth).

10

En este momento, la información sobre el voltaje de umbral Vth del primer transistor T1 se almacena en el condensador de almacenamiento Cstg. Es decir, la diferencia en el voltaje entre ambos extremos del condensador de almacenamiento Cstg es idéntica al voltaje de umbral Vth del primer transistor T1.

15

Con referencia a la FIG. 3, en la etapa de escritura de datos y compensación de movilidad, el tercer transistor T3 y el cuarto transistor T4 se apagan, y el segundo transistor T2 se enciende, de modo que se aplica un voltaje de datos Vdata (o se escribe en él) al nodo de puerta DTG del primer transistor T1.

20

En este momento, el primer transistor T1 se enciende y el voltaje en el nodo fuente DTS del primer transistor T1 aumenta.

El aumento del voltaje en el nodo de fuente DTS del primer transistor T1 es proporcional a la movilidad del primer transistor T1.

25 Por ejemplo, suponiendo que la movilidad del primer transistor T1 es  $\mu$ 1 o  $\mu$ 2, donde  $\mu$ 1 >  $\mu$ 2, un cambio de voltaje ΔDTS1 en el nodo de fuente DTS cuando la movilidad del primer transistor T1 es μ1 es mayor que un cambio de voltaje ΔDTS2 en el nodo fuente DTS cuando la movilidad del primer transistor T1 es μ2. Por consiguiente, la diferencia de voltaje Vgs1 entre el nodo de puerta DTG y el nodo fuente DTS cuando la movilidad del primer transistor T1 es µ1 es menor que la diferencia de voltaje Vgs2 entre el nodo de puerta

30 DTG y el nodo fuente DTS en la movilidad del primer transistor T1 es µ2.

Basándose en el grado en un aumento de voltaje (o cambio de voltaje) en el nodo de fuente DTS del primer transistor T1, se puede detectar la movilidad del primer transistor T1, y las variaciones en la movilidad se pueden compensar mediante retroalimentación negativa.

35

Con referencia a la FIG. 3, en la etapa de emisión, todos los transistores T2 a T4 excepto el primer transistor T1 que sirve como transistor de accionamiento se apagan. El OLED comienza a emitir luz mientras que el voltaje en el nodo de fuente DTS del primer transistor T1 aumenta de manera tal que la corriente del primer transistor T1 es idéntica a la del OLED.

40

En este momento, la información sobre el voltaje de umbral que ha estado presente en el nodo de fuente DTS del primer transistor T1 se transfiere al nodo de puerta DTG del primer transistor T1, compensando así el voltaje de umbral del primer transistor T1.

45 Específicamente, el voltaje en el nodo de fuente DTS del primer transistor T1 se expresa sin el voltaje de umbral, y el voltaje del nodo de puerta DTG del primer transistor T1 se expresa incluyendo el voltaje de umbral. El primer transistor T1 puede operar al OLED libre de la influencia del voltaje de umbral.

50

La estructura de píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización hace posible la detección del voltaje de umbral, la compensación de la movilidad y similares que han sido problemáticos en la técnica relacionada.

55

Tal como se ha descrito anteriormente, en la estructura de píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con el ejemplo comparativo, en la etapa de detección de voltaje de umbral, el voltaje de umbral Vth del primer transistor T1 que sirve como transistor de accionamiento se almacena en el nodo fuente DTS del primer transistor T1. El voltaje de umbral Vth almacenado en el nodo fuente DTS del primer transistor T1 de esta manera se transfiere al nodo de puerta DTG del primer transistor T1 que sirve como el transistor de accionamiento en la etapa de emisión.

60

Aquí, almacenar el voltaje de umbral en el nodo fuente DTS del primer transistor T1 indica que el voltaje en el nodo fuente DTS del primer transistor T1 puede expresarse mediante el voltaje de umbral. Además, la transferencia del voltaje de umbral Vth almacenado en el nodo fuente DTS del primer transistor T1 al nodo de puerta DTG del primer transistor T1 indica que el voltaje de umbral incluido en una fórmula de voltaje del nodo de fuente DTS del primer transistor T1 está incluido en una fórmula de voltaje del nodo de puerta DTG

65 del primer transistor T1.

En el proceso de almacenar y transferir el voltaje de umbral, tal como se ilustra en la FIG. 4, un condensador parásito Cpara formado en el nodo de puerta DTG del primer transistor T1 que sirve como transistor de accionamiento puede provocar una pérdida en el voltaje de umbral.

- 5 En particular, la pérdida en el voltaje de umbral causada por el condensador parásito Cpara formado en el nodo de puerta DTG del primer transistor T1 puede crear un voltaje de fuente de compuerta relativamente grande a una escala de grises baja que se controla en base a un voltaje de fuente de puerta pequeña del transistor de accionamiento T1, lo que conduce a una calidad de imagen gravemente no uniforme en el voltaje de umbral.

- Además, el intervalo de compensación para el voltaje de umbral puede reducirse significativamente, disminuyendo de este modo el rendimiento de los transistores.

- Además, es difícil obtener un tiempo de escritura de datos suficiente debido a un corto tiempo de compensación de movilidad.

- Por lo tanto, a continuación se hará referencia a formas de realización ejemplares (formas de realización primera a cuarta) de la estructura de píxel que pueden mejorar significativamente la capacidad de compensación de voltaje de umbral y el intervalo compensando una pérdida en un voltaje de umbral que se produciría durante el funcionamiento, puede compensar la movilidad y controlar un tiempo de compensación de movilidad basado en un diseño de condensador dentro de la estructura de píxel, logrando así un tiempo de escritura de datos suficiente, y tiene características superiores de uniformidad global.

- En primer lugar, se dará una descripción de una estructura de píxel 4T3C que incluye cuatro transistores (T) y tres condensadores (C) de acuerdo con una primera forma de realización ejemplar con referencia a la FIG. 5 a la FIG. 16.

20

45

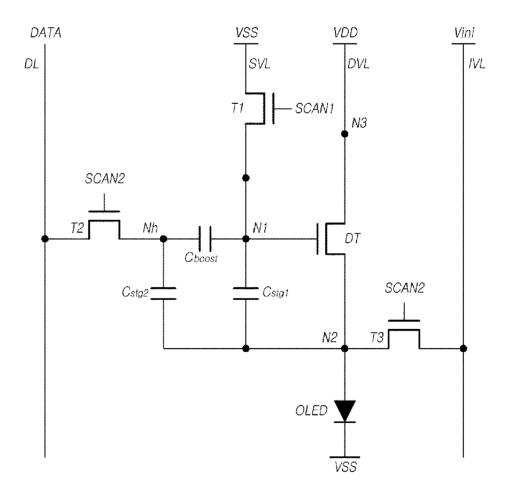

- La FIG. 5 es un diagrama de circuito equivalente que ilustra la estructura de píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización ejemplar de la presente invención.

- Con referencia a la FIG. 5, cada uno de los píxeles definidos en el plano de visualización 110 del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización incluye: un diodo emisor de luz orgánica (OLED); cuatro transistores que incluyen un transistor de accionamiento DT, un primer transistor T1, un segundo transistor T2 y un tercer transistor T3; y tres condensadores que incluyen un primer condensador de almacenamiento Cstg1, un segundo condensador de almacenamiento Cstg2 y un condensador de refuerzo Cboost.

- El transistor de accionamiento DT acciona el OLED e incluye un primer nodo N1 que forma un nodo de puerta, un segundo nodo N2 conectado al OLED y un tercer nodo N3 conectado a una línea de voltaje de accionamiento DVL a través de la cual se suministra un voltaje de accionamiento EVDD.

- El primer transistor T1 está controlado por una primera señal de escaneado SCAN1 y está conectado entre una línea de voltaje de fuente SVL y el primer nodo N1 del transistor de accionamiento DT.

- El primer condensador de almacenamiento Cstg1 está conectado entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT.

- El segundo condensador de almacenamiento Cstg2 y el condensador de refuerzo Cboost están conectados entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT.

- El segundo transistor T2 está controlado por una segunda señal de escaneado SCAN2, y está conectado entre un nodo de retención Nh al que están conectados el segundo condensador de almacenamiento Cstg2 y el condensador de refuerzo Cboost y una línea de datos DL.

- El tercer transistor T3 está controlado por una tercera señal de escaneado SCAN3, y está conectado entre el primer nodo N1 del transistor de accionamiento DT y el nodo de retención Nh.

- En la estructura de píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización, un voltaje de accionamiento VDD aplicado al tercer nodo N3 del transistor de conducción DT a través de la línea de voltaje de accionamiento DVL es un voltaje de CA, que se desplaza 1 H

- Aquí, el voltaje de accionamiento VDD en un nivel bajo se puede indicar mediante VDD(-), y el voltaje de accionamiento VDD en un nivel alto se puede indicar mediante VDD(+).

En la estructura de píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización, los tres condensadores tienen sus propias capacitancias. Comparando las capacitancias del primer condensador de almacenamiento Cstg1, el condensador de refuerzo Cboost y el segundo condensador de almacenamiento Cstg2, la capacitancia del segundo condensador de almacenamiento Cstg2 es la más pequeña. Las capatancias del primer condensador de almacenamiento Cstg1 y el condensador de refuerzo Cboost se diseñan de forma similar.

A continuación, se proporcionará una descripción del funcionamiento del píxel que tiene la estructura de píxel 4T3C descrita anteriormente.

10

- La FIG. 6 es un diagrama de temporización de funcionamiento de un píxel que tiene la estructura de píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización ejemplar.

- 15 Con referencia a la FIG. 6, el pixel que tiene la estructura de pixeles del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización lleva a cabo una operación que incluye una etapa de inicialización, una etapa de detección de voltaje de umbral, una etapa de escritura de datos y compensación de movilidad y una etapa de emisión.

- 20 A continuación, se proporcionará una descripción de las fases respectivas del funcionamiento con referencia a las FIG. 7A, FIG. 7B, FIG. 8A, FIG. 8B, FIG. 9, FIG. 10A, FIG. 10B, FIG. 11, FIG. 12A y FIG. 12B.

- Primero, refiriéndose a la FIG. 7A y FIG. 7B, en la fase de inicialización, se aplica un voltaje de accionamiento de bajo nivel VDD(-) al tercer nodo N3 del transistor de accionamiento DT, el primer transistor 25 T1 y el tercer transistor T3 se encienden mediante una primera señal de escaneado SCAN1 y una tercera señal de escaneado SCAN3 que son señales de escaneado de alto nivel, y el segundo transistor T2 se enciende mediante una segunda señal de escaneado SCAN2 que es una señal de escaneado de bajo nivel.

- Por consiguiente, el nodo de retención Nh y el primer nodo N1 del transistor de accionamiento DT se 30 inicializan utilizando un voltaje de fuente Vss, y el segundo nodo N2 del transistor de accionamiento DT se inicializa utilizando el voltaje de accionamiento de bajo nivel VDD(-).

- En esta etapa de inicialización, los voltajes en el primer nodo N1 del transistor de accionamiento DT, el segundo nodo N2 del transistor de accionamiento DT y el nodo de retención Nh pueden expresarse como 35 en la siguiente Fórmula 1:

Voltaje de N1 = VSS Voltaje de N2 = VDD(-) Voltaje de Nh = VSS

..... Fórmula 1

40

60

En la Fórmula 1, VSS indica un voltaje de fuente, y VDD(-) indica un voltaje de accionamiento de bajo nivel.

A continuación, haciendo referencia a la FIG. 8A y la FIG. 8B, en la fase de detección del voltaje de umbral, se aplica un voltaje de accionamiento de alto nivel VDD(+) al tercer nodo N3 del transistor de conducción 45 DT, el primer transistor T1 se mantiene en el estado encendido por medio de una primera señal de escaneado de alto nivel SCAN1, el segundo transistor T2 se apaga mediante una segunda señal de bajo nivel de voltaje SCAN2, y el tercer transistor T3 se apaga mediante una tercera señal de escaneo de nivel bajo SCAN3.

- 50 En esta etapa de detección de voltaje de umbral, los cambios en los voltajes en el primer nodo N1 del transistor de accionamiento DT, el segundo nodo N2 del transistor de accionamiento DT y el nodo de retención Nh se describirán con referencia a la FIG. 9.

- Con referencia a la FIG. 9, en la etapa de detección de voltaje de umbral, el primer nodo N1 del transistor 55 de accionamiento DT se mantiene en el voltaje de fuente VSS.

Además, en la etapa de detección de voltaje de umbral, el voltaje en el segundo nodo N2 del transistor de accionamiento DT aumenta a partir del voltaje inicializado VDD(-). El voltaje aumenta de VDD(-) a VSS-Vth, que es menor que el voltaje de fuente Vss, es decir, el voltaje en el primer nodo N1 del transistor de accionamiento DT, restado del voltaje de umbral Vth.

Por lo tanto, en el paso de detección de voltaje de umbral, un cambio de voltaje en el segundo nodo N2 del transistor de accionamiento DT es VSS-Vth-VDD(-).

65 Además, en el paso de detección de voltaje de umbral, el voltaje en el nodo de retención Nh aumenta de acuerdo con el cambio de voltaje VSS-Vth-VDD(-) en el segundo nodo N2 del transistor de accionamiento DT y una primera relación de capacitancia A.

Más específicamente, el voltaje en el nodo de retención Nh aumenta en un valor obtenido al multiplicar el cambio de voltaje VSS-Vth-VDD(-) en el segundo nodo N2 del transistor de accionamiento DT por la primera relación de capacitancia A. Aquí, la primera relación de capacitancia A es un valor que se obtiene dividiendo la capacitancia del segundo condensador de almacenamiento Cstg2 por un total de la capacitancia del condensador de refuerzo Cboost y de la capacitancia del segundo condensador de almacenamiento Cstg2.

En la etapa de detección de voltaje de umbral, los voltajes en el primer nodo N1 del transistor de accionamiento DT, el segundo nodo N2 del transistor de accionamiento DT y el nodo de retención Nh pueden expresarse siguiendo la Fórmula 2 y la Fórmula 3:

Voltaje de N1 = VSS Voltaje de N2 = VSS-Vth Voltaje de Nh = VSS+A \*(VSS-Vth-VDD(-)), donde A = Cstg2/(Cboost+Cstg2) ...... Fórmula 2 Si VSS = 0, Voltaje de N1 = 0 Voltaje de N2 = -Vth Voltaje de Nh = -A \*(VDD(-)+Vth) ..... Fórmula 3

En la Fórmula 2 y en la Fórmula 3, VSS indica un voltaje de fuente, Vth indica un voltaje umbral del transistor de accionamiento DT, VDD(-) indica un voltaje de accionamiento de bajo nivel, A indica una primera relación de capacitancia, Cstg2 indica una capacitancia del segundo condensador de almacenamiento Cstg2 y Cboost indica una capacitancia del condensador de refuerzo Cboost.

A continuación, haciendo referencia a la FIG. 10A y a la FIG. 10B, en la etapa de escritura de datos y detección de movilidad, el segundo transistor T2 se enciende mediante una segunda señal de escaneado de alto nivel SCAN2, se aplica un voltaje de datos Vdata a través de la línea de datos DL al segundo transistor T2, se aplica un voltaje de accionamiento de alto nivel VDD(+) al tercer nodo N3 del transistor conductor DT, y el primer transistor T1 se enciende mediante una primera señal de escaneado de bajo nivel SCAN1.

En la etapa de escritura de datos y detección de movilidad, se enciende el segundo transistor T2, mediante el cual el voltaje de datos Vdata suministrado a través de la línea de datos DL se aplica al nodo de retención Nh.

En consecuencia, el voltaje en el nodo de retención Nh aumenta hasta el voltaje de datos Vdata.

40 Un cambio de voltaje en el nodo de retención Nh es expresado por Vdata-[VSS+A\*(VSS-Vth-VDD(-))].

En respuesta a la detección de movilidad, el voltaje en el segundo nodo N2 del transistor de accionamiento DT aumenta adicionalmente desde el voltaje VSS-Vth que se ha incrementado en la fase de detección de voltaje de umbral.

Un cambio de voltaje  $\Delta Vu$  en el segundo nodo N2 del transistor de accionamiento DT debido a este aumento de voltaje puede variar de acuerdo con un cambio de voltaje  $\Delta Vp$  en el nodo de retención Nh.

- En respuesta a los datos acoplados que se aplican al primer nodo N1 del transistor de accionamiento DT y, simultáneamente, a la detección de movilidad, el voltaje en el primer nodo N1 del transistor de accionamiento DT aumenta a partir del voltaje de fuente VSS que se ha mantenido a través de la fase de detección de voltaje de umbral.

- El voltaje en el primer nodo N1 del transistor de accionamiento DT puede aumentar de acuerdo con el cambio de voltaje ΔVp en el nodo de retención Nh, el cambio de voltaje ΔVu en el segundo nodo N2 del transistor de accionamiento DT en respuesta al funcionamiento de detección de movilidad, una segunda relación de capacitancia B y una tercera relación de capacitancia C.

- Más específicamente, el voltaje en el primer nodo N1 del transistor de accionamiento DT aumenta adicionalmente mediante un valor de voltaje B\*ΔVp+C\*ΔVu, es decir, un total de un voltaje obtenido multiplicando el cambio de voltaje ΔVp en el nodo de retención Nh por la segunda relación de capacitancia B y un voltaje obtenido multiplicando el cambio de voltaje ΔVu en el segundo nodo N2 del transistor conductor DT en respuesta a la operación de detección de movilidad con la tercera relación de capacitancia C.

65

5

10

25

30

Aquí, la segunda relación de capacitancia B es un valor obtenido dividiendo la capacitancia del condensador de refuerzo Cboost por un total de la capacitancia del primer condensador de almacenamiento Cstg1 y la capacitancia del condensador de refuerzo Cboost.

- La tercera relación de capacitancia C es un valor obtenido dividiendo la capacitancia del primer condensador de almacenamiento Cstg1 por un total de la capacitancia del condensador de refuerzo Cboost y la capacitancia del primer condensador de almacenamiento Cstg1.

- Esta tercera relación de capacitancia C puede determinar la velocidad a la que disminuye la diferencia en el voltaje entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT.

En la etapa de escritura de datos y detección de movilidad, los voltajes en el primer nodo N1 del transistor de accionamiento DT, el segundo nodo N2 del transistor de accionamiento DT y el nodo de retención Nh pueden expresarse siguiendo la Fórmula 4 y la Fórmula 5 (VSS = 0) :

15

```

Voltaje de N1 = VSS+B*\DeltaVp+C*\DeltaVu

Voltaje de N2 = VSS-Vth+\DeltaVu

Voltaje de Nh = Vdata-VSS+A*(VSS-Vth-VDD(-))+\DeltaVp

donde B = Cboost/(Cstg1+Cboost)

C = Cstg1/(Cboost+Cstg1) ....... Fórmula 4

Si VSS = 0,

Voltaje de N1 = B*\DeltaVp+C*\DeltaVu

Voltaje de N2 = -Vth+\DeltaVu

Voltaje de Nh = Vdata = -A*(VDD(-)+Vth)+\DeltaVp ...... Fórmula 5

```

25

20

En la Fórmula 4 y la Fórmula 5, VSS indica un voltaje de fuente, Vth indica un voltaje de umbral del transistor de accionamiento DT, VDD(-) indica un voltaje de accionamiento de bajo nivel, Vdata indica un voltaje de datos, ΔVp indica un cambio de voltaje en el nodo de retención Nh, ΔVu indica un cambio de voltaje en el segundo nodo N2 del transistor de accionamiento DT, B indica una segunda capacitancia, C indica una tercera capacitancia, Cstg1 indica una capacitancia del primer condensador de almacenamiento Cstg1, y Cboost indica una capacitancia del condensador de refuerzo .

En secuencia, con referencia a la FIG. 12A y FIG. 12B, en la etapa de emisión, se apagan el primer transistor T1, el segundo transistor T2 y el tercer transistor T3.

35

30

En consecuencia, el voltaje en el segundo nodo N2 del transistor de accionamiento DT aumenta, y el OLED emite luz.

En este momento, se transfiere un voltaje de umbral del voltaje de accionamiento DT.

40

Un lds de corriente que fluye entre el nodo de drenaje N3 y el nodo fuente N2 del transistor conductor DT puede expresarse siguiendo la Fórmula 6:

$Ids = k(Vgs-Vth)^2$ , donde  $k = 1/2 \mu Cox W/L$  ..... Fórmula 6

45

50

En la Fórmula 6, Ids indica una corriente que fluye entre el nodo de drenaje N3 y el nodo de fuente N1 del transistor de accionamiento DT, Vgs indica una diferencia en el voltaje entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT, y Vth es un voltaje de umbral del transistor de accionamiento DT. k es un componente sobre la movilidad del transistor conductor DT, y está definido por la movilidad  $\mu$ , una capacitancia de óxido Cox, un ancho de canal W y una longitud de canal L.

Cuando el OLED emite luz, la corriente que fluye entre el nodo de drenaje N3 y el nodo de fuente N2 del transistor de accionamiento DT es idéntica a una corriente que fluye a través del OLED.

- Por lo tanto, es posible determinar si el voltaje de umbral Vth del transistor conductor DT tiene o no tiene un efecto sobre un píxel correspondiente, es decir, si el voltaje de umbral Vth del transistor conductor DT tiene o no un efecto sobre la corriente loled que fluye a través del OLED, al evaluar "Vgs-Vth."

- En base a los voltajes en el primer nodo N1 del transistor de accionamiento DT, el segundo nodo N2 del transistor de accionamiento DT y el nodo de retención Nh de acuerdo con los pasos descritos anteriormente, Vgs-Vth puede expresarse siguiendo la Fórmula 7:

$Vgs-Vth = B*\Delta Vp+C*\Delta Vu-(-Vth+\Delta Vu)-Vth \\ = B(Data+A(VDD(-)+Vth))+C*\Delta Vu+Vth-\Delta Vu-Vth \\ = B*Data+B*A*VDD(-)+B*A*Vth-\Delta Vu*(1-C), \\ donde A = Cstg2/(Cboost+Cstg2) \\ B = (Cboost/Cstg1+Cboost) \\ C = Cstg1/(Cboost+Cstg1) ......Fórmula 7$

5

10

15

En la Fórmula 7, VSS indica un voltaje de fuente, Vth indica un voltaje de umbral del transistor de accionamiento DT, VDD(-) indica un voltaje de accionamiento de bajo nivel, Vdata indica un voltaje de datos, ΔVp indica un cambio de voltaje en el nodo de retención Nh, ΔVu indica un cambio de voltaje en el segundo nodo N2 del transistor de accionamiento DT, A indica una primera relación de capacitancia, B indica una segunda relación de capacitancia, C indica una tercera relación de capacitancia, Cstg1 indica una capacitancia del primer condensador de almacenamiento Cstg1, Cboost indica una capacitancia del condensador de refuerzo Cboost, y Cstg2 indica una capacitancia del segundo condensador de almacenamiento Cstg2.

En la Fórmula 7, "B\*A\*Vth" es una parte que cancela una pérdida en el voltaje de umbral. Si las capacitancias de los tres condensadores Cstg1, Cstg2 y Cboost se determinan de manera que B\*A sea muy pequeño, B\*A\*Vth en Vgs-Vth se convierte en un valor despreciable pequeño. Es posible hacer un flujo de corriente a través del OLED sin un efecto significativo sobre el voltaje de umbral Vth del transistor de accionamiento DT.

Teniendo en cuenta esto, es posible controlar la parte que cancela la pérdida a través del segundo condensador de almacenamiento Cstg2.

25

- Específicamente, la capacitancia del condensador Cstg2 permite determinar la cantidad a controlar en la compensación de la pérdida en la información sobre el voltaje de umbral causada por el condensador parásito Cpara del primer nodo N1 del transistor de accionamiento DT.

- 30 Además, en la Fórmula 7, ΔVu\*(1-C) indica una disminución en la diferencia de voltaje Vgs entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT en la etapa de detección de movilidad.

- Aquí, la tercera relación de capacitancia C puede reducir la velocidad a la que disminuye la diferencia de voltaje Vgs. Específicamente, la tercera relación de capacitancia C determina la tasa de reducción de la diferencia de voltaje Vgs entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT.

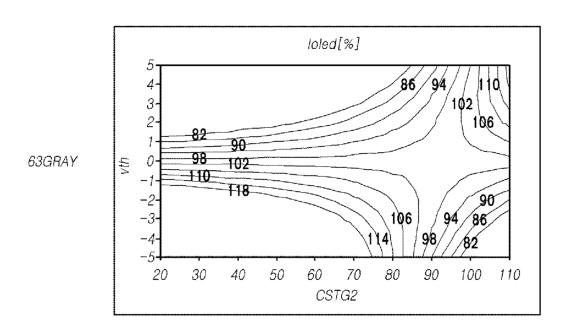

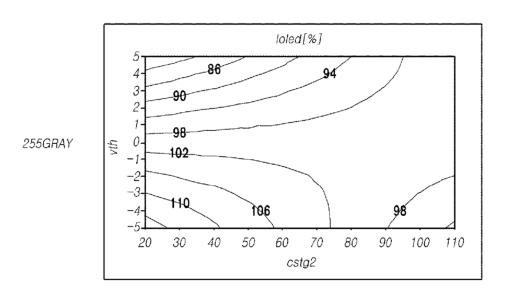

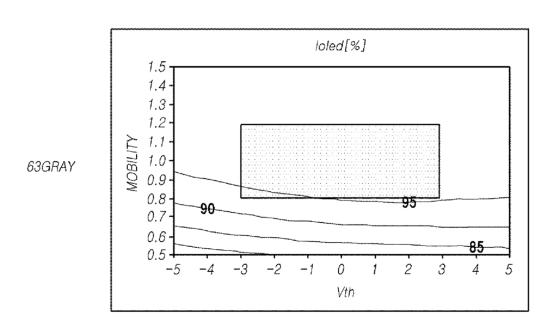

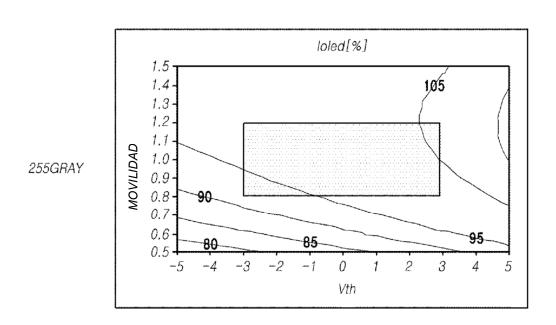

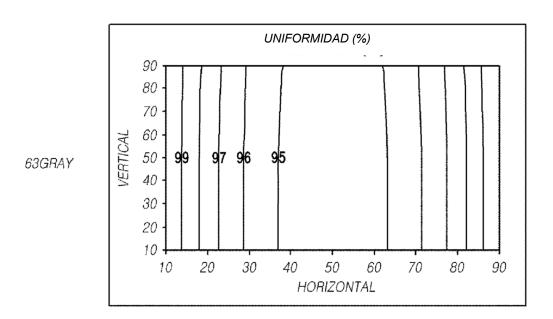

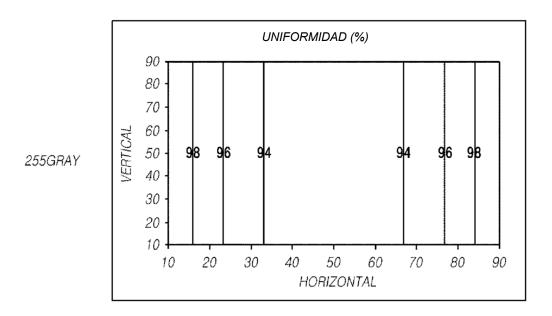

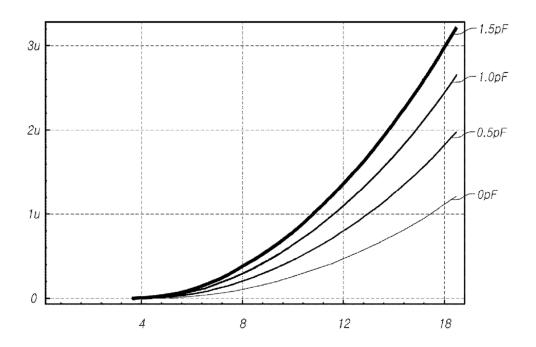

- Las FIG. 13A, FIG. 13B, FIG. 14A, FIG. 14B, FIG. 15A, FIG. 15B y FIG. 16 son gráficos que ilustran una variedad de simulaciones en la estructura de píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la primera forma de realización ejemplar.

40

Las FIG. 13A y FIG. 13B ilustran los resultados de las simulaciones sobre la capacidad de compensación de voltaje de umbral de la estructura de píxel de acuerdo con la primera forma de realización, realizada cambiando el segundo condensador Cstg2 para compensar una pérdida en el voltaje de umbral causada por el condensador parásito Cpara.

45

- Con referencia a las FIG. 13A y FIG. 13B, la estructura de píxel tiene el valor de capacitancia del segundo condensador Cstg2 que tiene un rendimiento óptimo tanto en un nivel de gris bajo (63 Gray) como en un nivel de gris alto (255 Gray).

- Las FIG. 14A y FIG. 14B ilustran los resultados de simulaciones en la capacidad de compensación compleja de la estructura de píxel de acuerdo con la primera forma de realización cuando tanto el voltaje de umbral Vth como la movilidad del transistor de accionamiento DT se desvían de una referencia.

- Con referencia a la FIG. 14A y FIG. 14B, se aprecia que hay amplios intervalos de compensación para el voltaje de umbral Vth y la movilidad en un nivel de gris bajo (63 Gray) o un nivel de gris alto (255 Gray) cuando Δloled está dentro del 5%.

- Las FIG. 15A y FIG. 15B ilustran la uniformidad global de la estructura de píxel de acuerdo con la primera forma de realización a un bajo nivel de gris (63 Gray) y un alto nivel de gris (255 Gray).

- Con referencia a la FIG. 15A y FIG. 15B, se aprecia que la estructura de píxel de acuerdo con la primera forma de realización tiene una uniformidad global superior en el nivel de gris bajo (63 Gray) o en el nivel de gris alto (255 Gray).

- La FIG. 16 ilustra variaciones en una corriente (eje Y) que fluye a través del OLED según los voltajes de datos (eje X) en la estructura de píxel de acuerdo con la primera forma de realización.

Con referencia a la FIG. 16, los pasos 1.5, 1.0, 0.5 y 0 pF indican las capacitancias entre un primer electrodo (por ejemplo, un ánodo) del OLED y el voltaje de fuente VSS.

- Con referencia a la FIG. 16, es posible diseñar un condensador para controlar la capacidad de la corriente cuando la capacidad de corriente es insuficiente, aunque el OLED funciona como un condensador. Específicamente, incluso en el caso de que el voltaje de datos sea el mismo, es posible aumentar la cantidad de corriente que fluye a través del OLED aumentando la capacitancia diseñada del componente del condensador del OLED.

- La estructura de píxel 4T3C de acuerdo con la primera forma de realización y el funcionamiento del píxel que tiene la estructura de píxel 4T3C se han descrito anteriormente.

- A continuación, se hará referencia a una forma de realización modificada (segunda forma de realización) de la estructura de píxel 4T3C de acuerdo con la primera forma de realización y al funcionamiento de la misma en relación con la FIG. 17 y FIG. 18.

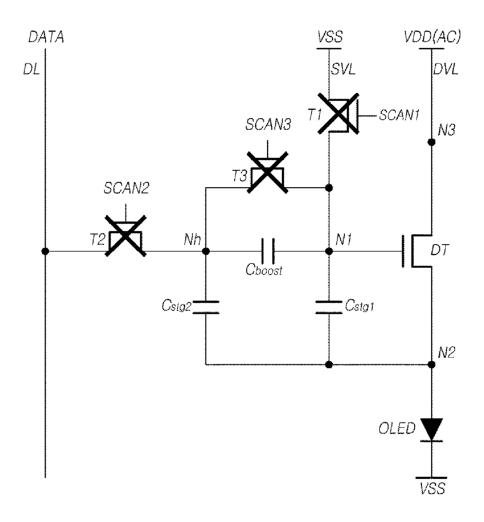

- La FIG. 17 es un diagrama de circuito equivalente que ilustra una estructura de píxel de un dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con una segunda forma de realización ejemplar de la presente invención.

- Con referencia a la FIG. 17, cada uno de los píxeles del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la segunda forma de realización tiene una estructura de píxel que incluye: un diodo orgánico emisor de luz (OLED); cinco transistores que incluyen un transistor de accionamiento DT, un primer transistor T1, un segundo transistor T2, un tercer transistor T3 y un cuarto transistor T4; y tres condensadores que incluyen un primer condensador de almacenamiento Cstg1, un segundo condensador de almacenamiento Cstg2 y un condensador de refuerzo Cboost.

20

- El transistor de accionamiento DT incluye un primer nodo N1 que forma un nodo de puerta, un segundo nodo N2 conectado al OLED y un tercer nodo N3 conectado a una línea de voltaje de accionamiento DVL a través de la cual se suministra un voltaje de accionamiento VDD.

- El primer transistor T1 está controlado por una primera señal de escaneado SCAN1 y está conectado entre una línea de voltaje de fuente SVL y el primer nodo N1 del transistor de accionamiento DT.

- 35 El primer condensador de almacenamiento Cstg1 está conectado entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT.

- El segundo condensador de almacenamiento Cstg2 y el condensador de refuerzo Cboost están conectados entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT.

- El segundo transistor T2 está controlado por una segunda señal de escaneado SCAN2, y está conectado entre un nodo de retención Nh y una línea de datos DL.

- El tercer transistor T3 está controlado por una tercera señal de escaneado SCAN3, y está conectado entre el primer nodo N1 del transistor de accionamiento DT y el nodo de retención Nh.

- El cuarto transistor T4 está conectado entre el segundo nodo N2 del transistor de accionamiento DT y una línea de voltaje de inicialización IVL a través de la cual se suministra un voltaje de inicialización Vini.

- El cuarto transistor T4 es controlado habitualmente por la tercera señal de escaneado SCAN3 mediante la cual se controla el tercer transistor T3.

- La estructura de píxel 5T3C de acuerdo con la segunda forma de realización ilustrada en la FIG. 17 es sustancialmente idéntica a la estructura de píxel 4T3C de acuerdo con la primera forma de realización ilustrada en la FIG. 5, excepto que el voltaje de accionamiento VDD suministrado a través de una línea de voltaje de accionamiento DVL es un voltaje de CC, y que se añade el cuarto transistor T4.

- Por consiguiente, el segundo nodo N2 del transistor de accionamiento DT se inicializa mediante un voltaje de inicialización IVL suministrado a través de la línea de voltaje de inicialización IVL en la estructura de píxel de acuerdo con la segunda forma de realización ilustrada en la FIG. 17, mientras que el segundo nodo N2 del transistor de accionamiento DT se inicializa mediante VDD(-) en la estructura de píxel 4T3C de acuerdo con la primera forma de realización ilustrada en la FIG. 5.

- Tal como se ha descrito anteriormente, el sistema de funcionamiento y las características operativas de la estructura de píxel 5T3C de acuerdo con la segunda forma de realización ilustrada en la FIG. 17 son sustancialmente idénticos a los de la estructura de píxel 4T3C de acuerdo con la primera forma de

realización ilustrada en la FIG. 5, excepto la inicialización del segundo nodo N2 del transistor de accionamiento DT.

- Por lo tanto, el tiempo de funcionamiento de un píxel que tiene la estructura de píxel 5T3C de acuerdo con la segunda forma de realización ilustrada en la FIG. 17 es idéntica a la temporización de funcionamiento de un píxel que tiene la estructura de píxel 4T3C de acuerdo con la primera forma de realización ilustrada en la FIG. 5.

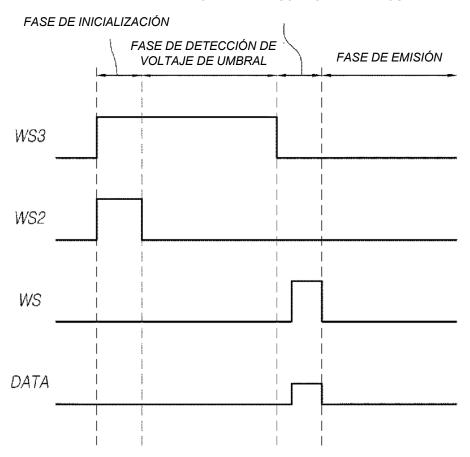

- La temporización de funcionamiento del píxel que tiene la estructura de píxel 5T3C de acuerdo con la segunda forma de realización ilustrada en la FIG. 17 se describirá brevemente con referencia a la FIG. 18.

- Con referencia a la FIG. 18, el píxel que tiene la estructura de píxel 5T3C de acuerdo con la segunda forma de realización también lleva a cabo una operación, que incluye una etapa de inicialización, una etapa de detección de voltaje de umbral, una etapa de escritura de datos y compensación de movilidad y una etapa de emisión, igual que en la primera forma de realización.

- Comparando el tiempo de funcionamiento de un píxel que tiene la estructura de píxel 5T3C de acuerdo con la segunda forma de realización ilustrada en la FIG. 17 con la temporización de funcionamiento de un píxel que tiene la estructura de píxel 4T3C de acuerdo con la primera forma de realización ilustrada en la FIG. 5, el sistema de funcionamiento y las características operativas del mismo son idénticos, excepto que el voltaje de accionamiento VDD es un voltaje de CC en la estructura de píxel 5T3C.

- Dado que se suministra el voltaje de accionamiento de CC VDD, se añade el cuarto transistor T4 para inicializar el segundo nodo N2 del transistor de accionamiento DT.

- Por lo tanto, en la etapa de inicialización, el voltaje de accionamiento de CC VDD se aplica al tercer nodo N3 del transistor de accionamiento DT, el primer transistor T1 se enciende mediante una primera señal de escaneo de alto nivel SCAN1, el tercer transistor T3 y el cuarto transistor T4 son encendidos por una tercera señal de escaneado de alto nivel, y el segundo transistor T2 es encendido por una segunda señal de escaneado de bajo nivel SCAN2.

- En consecuencia, el nodo de retención Nh y el primer nodo N1 del transistor de accionamiento DT se inicializan mediante una fuente de voltaje VSS suministrada a través del primer transistor T1, y el segundo nodo N2 del transistor de accionamiento DT se inicializa mediante el voltaje de inicialización Vini suministrado a través el cuarto transistor T4.

- Las descripciones de la etapa de detección de voltaje de umbral, la etapa de escritura de datos y compensación de movilidad y la etapa de emisión se omitirán ya que son idénticas a las del funcionamiento de la estructura de píxel 4T3C de acuerdo con la primera forma de realización.

- La estructura de píxel 4T3C de acuerdo con la primera forma de realización y la estructura de píxel 5T3C que incluye un transistor más (el cuarto transistor T4) de acuerdo con la segunda forma de realización se han descrito anteriormente.

- A continuación, se hará referencia a una estructura de píxel 3T3C de acuerdo con una tercera forma de realización correspondiente a una forma de realización modificada de la estructura de píxel 4T3C de acuerdo con la primera forma de realización junto con la FIG. 19 a la FIG. 21.

- La FIG. 19 es un diagrama de circuito equivalente que ilustra la estructura de píxel de un dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la tercera forma de realización a modo de ejemplo de la presente invención.

- El dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la tercera forma de realización incluye un panel de pantalla 110 en el que están dispuestas una pluralidad de líneas de datos DL1 a DLm y una pluralidad de líneas de puerta GL1 a GLn de modo que se define un número de píxeles P, el controlador de datos 120 para conducir las líneas de datos LD1 a DLm, un controlador de puerta 130 para controlar las líneas de puerta GL1 a GLn, y un controlador de temporización 140 para controlar el controlador de datos 120 y el controlador de puerta 130.

- Con referencia a la FIG. 19, cada uno de una pluralidad de píxeles del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la tercera forma de realización tiene una estructura de píxel 3T3C que incluye un diodo orgánico emisor de luz (OLED), un transistor de accionamiento DT, un primer transistor T1, un segundo transistor T2, un primer condensador de almacenamiento Cstg1, un segundo condensador de almacenamiento Cstg2 y un condensador de refuerzo Cboost.

65

15

25

35

Aquí, el transistor de accionamiento DT sirve para accionar el OLED, e incluye un primer nodo N1 que forma un nodo de puerta, un segundo nodo N2 conectado al OLED y un tercer nodo N3 conectado a una línea de voltaje de accionamiento DVL.

- 5 El primer transistor T1 está controlado por una primera señal de escaneado SCAN1 y está conectado entre una línea de fuente de voltaje SVL y el primer nodo N1 del transistor de accionamiento DT.

- El primer condensador de almacenamiento Cstg1 está conectado entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT.

- El segundo condensador de almacenamiento Cstg2 y el condensador de refuerzo Cboost están conectados entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT. El nodo de conexión entre el segundo condensador de almacenamiento y el condensador de refuerzo forma un nodo de retención Nh.

- El segundo transistor T2 está controlado por una segunda señal de escaneado SCAN2, y está conectado entre el nodo de retención Nh al que están conectados el segundo condensador de almacenamiento Cstg2 y el condensador de refuerzo Cboost y una línea de datos DL.

- 20 Con referencia a la FIG. 19, en cada uno de la pluralidad de píxeles del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la tercera forma de realización, se suministra un voltaje de accionamiento CA VDD al tercer nodo N3 del transistor de accionamiento DT a través de la línea de voltaje de accionamiento DVL.

- 25 El funcionamiento de un píxel que tiene la estructura de píxel 3T3C de acuerdo con la tercera forma de realización ilustrada en la FIG. 19 se describirá con referencia a la FIG. 20 y FIG. 21.

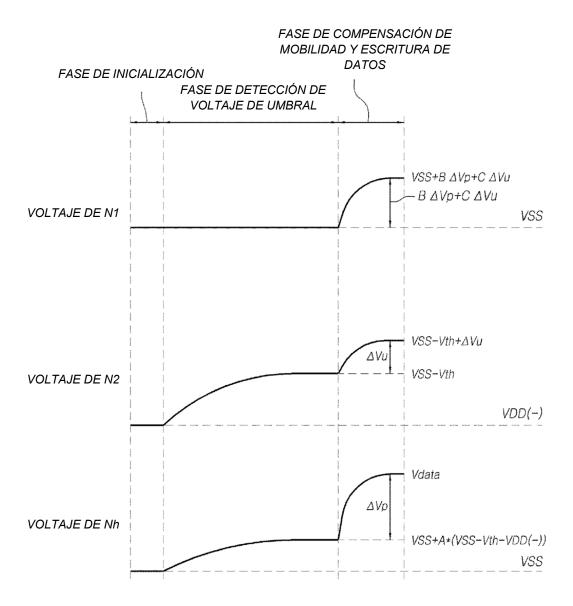

- Las FIG. 20 y FIG. 21 son un diagrama de temporización de funcionamiento y un gráfico de cambio de voltaje en nodos principales en la estructura de píxel del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la tercera forma de realización ejemplar.

- Con referencia a la FIG. 20, el funcionamiento de un píxel que tiene la estructura de píxel 3T3C de acuerdo con la tercera forma de realización es idéntico al funcionamiento de un píxel que tiene la estructura de píxel 4T3C de acuerdo con la primera forma de realización.

- Además, con referencia a la FIG. 20, el funcionamiento del píxel que tiene la estructura de píxel 3T3C de acuerdo con la tercera forma de realización incluye una etapa de inicialización, una etapa de detección de voltaje de umbral, una etapa de escritura de datos y compensación de movilidad y una etapa de emisión, como el funcionamiento del píxel que tiene la estructura de píxel 4T3C de acuerdo con la primera forma de realización.

- El funcionamiento del píxel que tiene la estructura de píxel 3T3C de acuerdo con la tercera forma de realización difiere del funcionamiento del píxel que tiene la estructura de píxel 4T3C de acuerdo con la primera forma de realización en que el nodo de retención Nh se inicializa mediante un voltaje de datos suministrado a través de la línea de datos DL, ya que no se proporciona el transistor (T3 en la FIG. 5) para inicializar el nodo de retención Nh.

- Por lo tanto, los voltajes de datos de entrada se dividen en un voltaje de datos de inicialización de bajo nivel Vo y un voltaje de datos de alto nivel Vdata, y el nodo de retención Nh se inicializa mediante el voltaje de datos de inicialización Vo.

- En el píxel que tiene la estructura de píxel 3T3C de acuerdo con la tercera forma de realización, el nodo de retención Nh se inicializa mediante un voltaje aplicado a través de la línea de datos DL. El voltaje aplicado a través de la línea de datos DL es un voltaje en el que el voltaje de datos de inicialización de bajo nivel Vo y el voltaje de datos de alto nivel Vdata se alternan entre sí.

- Por consiguiente, puede evitarse el transistor (T3 en la FIG. 5) conectado entre el nodo de retención Nh y el primer nodo N1 del transistor de accionamiento DT, así como una señal de escaneado para controlar el transistor (T3 en la FIG. 5).

- Además, en referencia a la temporización de funcionamiento de la etapa de inicialización en la FIG. 20, dado que el nodo de retención Nh se inicializa mediante el voltaje de datos de inicialización de bajo nivel Vo, un tiempo de inicialización puede ser insuficiente cuando se realiza la inicialización a través de la línea de datos DL.

65

60

10

15

Por lo tanto, es posible complementar el tiempo insuficiente activando la segunda señal de escaneado SCAN2 de forma múltiple en un tiempo horizontal (HT). En consecuencia, el segundo transistor T2 repite encendido y apagado por el tiempo horizontal (HT).

- De esta manera, en la etapa de inicialización, el nodo de retención Nh se inicializa para que tenga la forma de dientes de sierra mediante el voltaje de datos de inicialización de bajo nivel Vo, tal como se ilustra en la FIG. 21, de acuerdo con el tipo de voltaje de datos Vdata + Vo y el tipo de la segunda señal de escaneado SCAN2.

- 10 A excepción de esta etapa de inicialización, el otro funcionamiento (en la etapa de detección de voltaje de umbral, la etapa de escritura y compensación de movilidad y la etapa de emisión) y la sincronización de la misma son idénticos a las del píxel que tiene la estructura de píxel 4T3C de acuerdo con la primera forma de realización.

- En consecuencia, el voltaje cambia en el primer nodo N1, el segundo nodo N2 y el nodo de retención Nh en el píxel que tiene la estructura de píxel 3T3C de acuerdo con la tercera forma de realización ilustrada en la FIG. 21 son idénticos a los cambios de voltaje en el primer nodo N1, el segundo nodo N2 y el nodo de retención Nh en el píxel que tiene la estructura de píxel 4T3C de acuerdo con la primera forma de realización ilustrada en la FIG. 11, excepto por un cambio de voltaje en el nodo de retención en la fase de inicialización.

- Las descripciones de las otras operaciones del píxel que tiene la estructura de píxel 3T3C de acuerdo con la tercera forma de realización en la fase de detección de voltaje de umbral, la fase de escritura de datos y compensación de movilidad y la fase de emisión y cambios de voltaje en los nodos N1, N2 y Nh en estos pasos se omitirán ya que son idénticos a los del píxel que tiene la estructura de píxel 4T3C de acuerdo con la primera forma de realización.

- A continuación, se hará referencia a una estructura de píxel 4T3C de acuerdo con una cuarta forma de realización correspondiente a una forma de realización modificada de la tercera forma de realización y al funcionamiento de un píxel que tiene la estructura de píxel 3T3C junto con la FIG. 22 y 23.

- La FIG. 22 es un diagrama de circuito equivalente que ilustra la estructura de píxel de un dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la cuarta forma de realización ejemplar de la presente invención.

- Con referencia a la FIG. 22, la estructura de píxel de cada uno de una pluralidad de píxeles del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la cuarta forma de realización es sustancialmente idéntica a la estructura de píxel 3T3C de acuerdo con la tercera forma de realización ilustrada en la FIG. 19, excepto que se aplica un voltaje de accionamiento CC VDD a un tercer nodo N3 de un transistor de accionamiento DT y, para ello, se añade un tercer transistor T3 conectado entre un segundo nodo N2 de un transistor de accionamiento DT y una línea de voltaje de inicialización IVL.

- Específicamente, el transistor de accionamiento DT acciona un diodo emisor de luz orgánica (OLED) e incluye un primer nodo N1 que forma un nodo de puerta, un segundo nodo N2 conectado al OLED y el tercer nodo N3 conectado a la línea de voltaje de accionamiento DVL. El primer transistor T1 está controlado por una primera señal de escaneado SCAN1 y está conectado entre una línea de voltaje de fuente SVL y el primer nodo N1 del transistor de accionamiento DT. El primer condensador de almacenamiento Cstg1 está conectado entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT. El segundo condensador de almacenamiento Cstg2 y el condensador de refuerzo Cboost están conectados entre el primer nodo N1 y el segundo nodo N2 del transistor de accionamiento DT. El nodo de conexión entre el segundo condensador de almacenamiento y el condensador de refuerzo forma un nodo de retención Nh. El segundo transistor T2 está controlado por una segunda señal de escaneado SCAN2, y está conectado entre el nodo de retención Nh al que están conectados el segundo condensador de almacenamiento Cstg2 y el condensador de refuerzo Cboost y una línea de datos DL.

- La estructura de píxel de cada uno de la pluralidad de píxeles del dispositivo de pantalla orgánica emisora de luz 100 de acuerdo con la cuarta forma de realización ilustrada en la FIG. 22 forma una estructura de píxel de 4T3C, ya que esta estructura de píxel tiene un transistor más (es decir, el tercer transistor T3) que la estructura de píxel de 3T3C de acuerdo con la tercera forma de realización ilustrada en la FIG. 19.

- El tercer transistor T3 añadido a la estructura de píxel de 4T3C de acuerdo con la cuarta forma de realización se controla habitualmente por medio de la segunda señal de escaneado SCAN2 mediante la cual se controla el segundo transistor T2.

- Con referencia a la FIG. 23, a continuación, se proporcionará una descripción del funcionamiento de un píxel que tiene la estructura de píxel 4T3C de acuerdo con la cuarta forma de realización ilustrada en la FIG. 22.

Con referencia a la FIG. 23, la temporización del funcionamiento del píxel que tiene la estructura de píxel 4T3C de acuerdo con la cuarta forma de realización es sustancialmente idéntica a la temporización de funcionamiento del píxel que tiene la estructura de píxel 3T3C de acuerdo con la tercera forma de realización ilustrada en la FIG. 20, excepto en que se suministra un voltaje de accionamiento CC VDD y, en consecuencia, se aplica un voltaje de inicialización Vini al segundo nodo N2 del transistor de accionamiento DT a través del tercer transistor T3 conectado al segundo nodo N2 del transistor de accionamiento DT.

De acuerdo con la presente invención tal como se ha establecido anteriormente, el dispositivo de pantalla orgánica emisora de luz tiene la estructura de píxel capaz de mejorar significativamente la capacidad y el intervalo de compensación de voltaje de umbral compensando una pérdida en un voltaje de umbral que se produciría durante el funcionamiento.

Es decir, la utilización de la estructura de píxel de acuerdo con ciertas formas de realización de la presente invención hace posible almacenar un voltaje de umbral relativo además de un voltaje de umbral absoluto, compensando así una pérdida en el voltaje de umbral.

El dispositivo de pantalla orgánica emisora de luz tiene la estructura de píxel capaz de compensar la movilidad y controlar un tiempo de compensación de movilidad basándose en un diseño de condensador dentro de la estructura de píxel, logrando así un tiempo de escritura de datos suficiente.

Es decir, la utilización de la estructura de píxel de acuerdo con ciertas formas de realización de la invención hace posible controlar un tiempo de detección de movilidad hasta un tiempo deseable utilizando un condensador interno, logrando así un tiempo de escritura de datos suficiente.

25 El dispositivo de pantalla orgánica emisora de luz tiene la estructura de píxel que tiene características superiores de uniformidad global.