OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 662 127

51 Int. Cl.:

G06F 12/10 (2006.01) G06F 11/07 (2006.01) G06F 11/10 (2006.01) G06F 12/1009 (2006.01) G06F 12/1027 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

- 86 Fecha de presentación y número de la solicitud internacional: 15.06.2011 PCT/JP2011/063695

- (87) Fecha y número de publicación internacional: 29.03.2012 WO12039169

- (96) Fecha de presentación y número de la solicitud europea: 15.06.2011 E 11826615 (4)

- (97) Fecha y número de publicación de la concesión europea: 17.01.2018 EP 2620875

- (54) Título: Dispositivo de inspección de traducción de dirección, dispositivo de procesamiento central y procedimiento de inspección de traducción de dirección

- (30) Prioridad:

22.09.2010 JP 2010212435

Fecha de publicación y mención en BOPI de la traducción de la patente: 05.04.2018 (73) Titular/es:

MITSUBISHI HEAVY INDUSTRIES, LTD. (100.0%) 16-5, Konan 2-chome Minato-ku Tokyo 108-8215, JP

(72) Inventor/es:

NAKAIDE, MINORU y TODA, SHINICHI

(74) Agente/Representante:

**CARPINTERO LÓPEZ, Mario**

### **DESCRIPCIÓN**

Dispositivo de inspección de traducción de dirección, dispositivo de procesamiento central y procedimiento de inspección de traducción de dirección

#### Campo técnico

10

20

25

35

40

45

50

5 La presente invención se refiere a un dispositivo de comprobación de traducción de dirección, una unidad de procesamiento central y un procedimiento de comprobación de traducción de dirección.

### Antecedentes de la técnica

Una CPU (Unidad de Procesamiento Central) puede usar direcciones virtuales para acceder una memoria física, tal como RAM (Memoria de Acceso Aleatorio), divididas en páginas (teniendo cada una un tamaño de varios kilobytes, por ejemplo). Direcciones virtuales son direcciones en memoria virtual que virtualiza áreas no contiguas en memoria física como áreas contiguas y son por lo tanto diferentes de direcciones físicas. Cuando la CPU usa direcciones virtuales, una unidad de gestión de memoria (en lo sucesivo denominada como una MMU) traduce las direcciones virtuales en direcciones físicas para permitir que la CPU acceda a la memoria física.

La MMU lee (carga) una tabla de paginación, que es una tabla de traducción de traducción de direcciones físicas en direcciones virtuales, de RAM en una memoria intermedia de traducción anticipada (en lo sucesivo denominada como una TLB). La MMU usa la tabla de paginación para traducir una dirección virtual solicitada para accederse mediante la CPU en una dirección física.

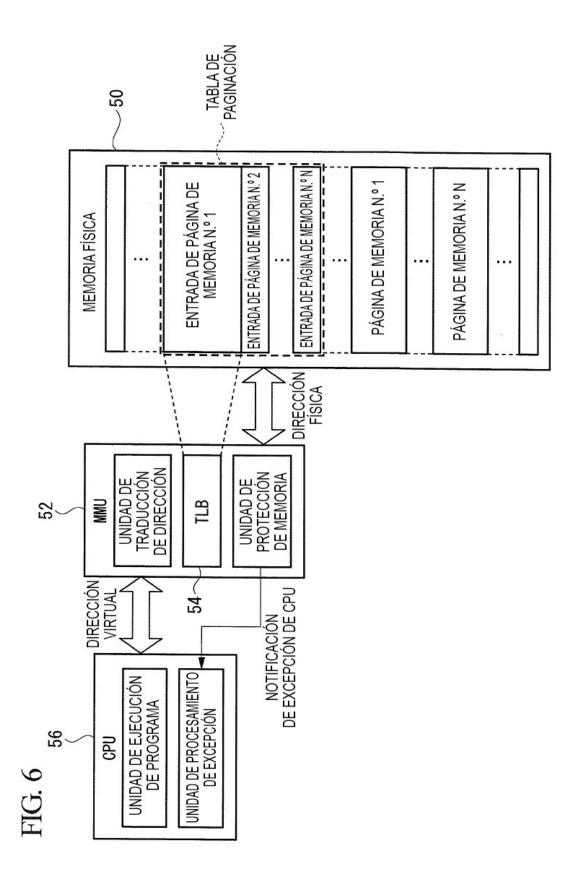

Como se muestra en un diagrama de bloques de la Figura 6, una tabla de paginación incluye entradas de página de memoria de acceso a respectivas páginas de una memoria 50 física. En cada entrada de página de memoria, se escriben una dirección virtual y una dirección física de una página de memoria correspondiente. Entradas de página de memoria necesarias se leen de información de tabla de paginación almacenada en la memoria 50 física en una TLB 54 proporcionada en una MMU 52 y almacenada en la TLB 54.

También escrito en cada entrada de página de memoria existe un atributo de protección de memoria que indica "leer," "escribir," "ejecutar," etc. Una técnica descrita en la Bibliografía de Patente 1 implica establecer un valor para un bit de protección del atributo de protección de memoria de una entrada de página de memoria de una tabla de paginación a leer en una MMU. Esto habilita evitar que una variable global usada únicamente por una tarea se reescriba por otra tarea para provocar una pérdida de control de la tarea.

### Lista de citas

### Bibliografía de patente

30 {PTL 1} Solicitud de Patente no Examinada de Japón, Publicación N.º Hei10-289158

El documento US 2004/015753 A1 se ocupa de detección de errores de bits en memorias de contenido direccionable (CAM). Bit(s) de paridad se almacena en una Memoria de Acceso Aleatorio(RAM) que se acopla a una CAM. Esta CAM puede ser parte de una TLB. El bit(s) de paridad se almacena en conjunción con la entrada de CAM escribir. Tras una concordancia de consulta de CAM, el bit(s) de paridad de referencia almacenado en la dirección emitida por la CAM se emiten desde la RAM. Este bit(s) de paridad de referencia se comparan con bit(s) de paridad generado a partir del valor de datos de consulta. En la ausencia de un error de bit de CAM o RAM, el bit(s) de paridad de referencia de la RAM y el bit(s) de paridad generado a partir de los datos de solicitud coincidirán. Si se produce un error de bit de CAM o RAM, estos dos conjuntos de bit(s) de paridad no coincidirán y por lo tanto se detectará un error. Este error puede usarse como una indicación de que se ha producido una coincidencia de CAM falsa.

El documento US 6 901 540 B1 desvela un microprocesador, sistema de procesamiento de datos y procedimiento para tratar errores de paridad en instalación de traducción de dirección tales como una TLB. El microprocesador incluye una unidad de carga/almacenamiento configurada para generar una dirección efectiva asociada con la instrucción de carga/almacenamiento. Una unidad de traducción de dirección adaptada para traducir la dirección efectiva a una dirección real que usa una memoria intermedia de traducción anticipada (TLB). La unidad de traducción de dirección incluye un comprobador de paridad configurado para verificar la paridad de la dirección real generada por la TLB y para señalizar la unidad de almacenamiento de carga cuando la dirección real contiene un error de paridad. La unidad de almacenamiento de carga se configura para iniciar una rutina de interrupción de error de paridad de TLB en respuesta a la señal desde la unidad de traducción. La rutina de interrupción de TLB invalida selectivamente la entrada de TLB que contiene el error de paridad.

### Sumario de la invención

## Problema técnico

Una CPU 56 puede fallar en la realización de un acceso normal a la memoria 50 física a través de la MMU 52 por

una razón tal como corrupción de la tabla de paginación leída en la TLB 54 de la MMU 52 mostrada en el diagrama de bloques de la Figura 6, o un fallo en la MMU 52. La CPU 56 puede entonces provocar un mal funcionamiento, tales como un cuelgue o pérdida de control de la CPU 56 o cambios repentinos en valores emitidos a otros dispositivos conectados.

La presente invención se ha realizado en vista de tales circunstancias. Un objeto de la presente invención es proporcionar un dispositivo de comprobación de traducción de dirección, una unidad de procesamiento central y un procedimiento de comprobación de traducción de dirección que son capaces de comprobar, mientras otro programa sigue ejecutándose, si la unidad de procesamiento central puede realizar o no un acceso normal a memoria física que usa una tabla de traducción leída en una memoria intermedia proporcionada en una unidad de gestión de memoria.

### Solución al problema

15

20

25

30

35

40

Para resolver el problema anterior, se proporciona un dispositivo de comprobación de traducción de dirección como se describe en la reivindicación independiente 1, una unidad de procesamiento central como se describe en la reivindicación independiente 4 y un procedimiento de comprobación de traducción de dirección como se describe en la reivindicación independiente 5. Desarrollos ventajosos se definen en las reivindicaciones dependientes.

Un dispositivo de comprobación de traducción de dirección de acuerdo con un primer aspecto de la presente invención incluye: una unidad de gestión de memoria de traducción entre una dirección virtual y una dirección física sobre la base de una tabla de traducción de traducción entre direcciones físicas que son direcciones en memoria física y direcciones virtuales que son direcciones en memoria virtual, estando la unidad de gestión de memoria provista de una memoria intermedia de almacenamiento de información de tabla de traducción que indica la tabla de traducción; medio de almacenamiento proporcionado fuera de la unidad de gestión de memoria y de almacenamiento de la información de tabla de traducción e información de detección de error adjuntada a la información de tabla de traducción, siendo la información de detección de error de detección de la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la unidad de gestión de memoria; y medio de detección de error de detección de la presencia o ausencia del error sobre la base de la información de detección de error.

De acuerdo con esta configuración, la unidad de gestión de memoria traduce entre una dirección virtual y una dirección física sobre la base de la tabla de traducción de traducción entre direcciones físicas que son direcciones en la memoria física y direcciones virtuales que son direcciones en la memoria virtual. La memoria intermedia proporcionada en la unidad de gestión de memoria almacena la información de tabla de traducción que indica la tabla de traducción para su uso en la traducción.

La memoria física puede ser RAM, por ejemplo, y la memoria virtual es memoria que virtualiza áreas no contiguas en la memoria física como áreas contiguas. Cuando la unidad de procesamiento central usa direcciones virtuales, la unidad de gestión de memoria traduce entre direcciones virtuales y direcciones físicas sobre la base de la tabla de traducción porque no puede accederse directamente a la memoria física con direcciones virtuales. Esta traducción permite que la unidad de procesamiento central acceda a la memoria física.

Antes de ser leída en la memoria intermedia proporcionada en la unidad de gestión de memoria, la información de tabla de traducción se almacena en el medio de almacenamiento proporcionado fuera de la unidad de gestión de memoria. La información de detección de error de detección de la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la unidad de gestión de memoria se adjunta a la información de tabla de traducción y almacena en el medio de almacenamiento.

Sobre la base de la información de detección de error, el medio de detección de error detecta la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la unidad de gestión de memoria.

- Por lo tanto, la información de detección de error adjuntada a la información de tabla de paginación se usa para detectar la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la unidad de gestión de memoria. Por lo tanto, puede comprobarse, mientras otro programa sigue ejecutándose, si la unidad de procesamiento central puede realizar o no un acceso normal a la memoria física que usa la tabla de traducción leída en la memoria intermedia proporcionada en la unidad de gestión de memoria.

- En el primer aspecto anterior, preferentemente, la información de detección de error es un valor de CRC para su uso en comprobación de redundancia cíclica generada sobre la base de la tabla de traducción indicada por la información de tabla de traducción y el medio de detección de error genera, antes de que la información de detección de error se lea en la memoria intermedia junto con la información de tabla de traducción, un nuevo valor de CRC sobre la base de la tabla de traducción indicada por la información de tabla de traducción a leer y detecta si el valor de CRC como la información de detección de error es o no el mismo que el nuevo valor de CRC.

De acuerdo con esta configuración, la información de detección de error es un valor de CRC para su uso en comprobación de redundancia cíclica generada sobre la base de la tabla de traducción indicada por la información

# ES 2 662 127 T3

de tabla de traducción. El medio de detección de error genera, antes de que la información de detección de error se lea en la memoria intermedia junto con la información de tabla de traducción, un nuevo valor de CRC sobre la base de la tabla de traducción indicada por la información de tabla de traducción a leer y detecta si el valor de CRC como la información de detección de error es o no el mismo que el nuevo valor de CRC.

Por lo tanto, puede detectarse si la tabla de traducción leída en la memoria intermedia está corrupta o no. Por lo tanto, si la unidad de procesamiento central puede realizar o no un acceso normal a la memoria física puede comprobarse mientras otro programa sigue ejecutándose.

En el primer aspecto anterior, la información de detección de error se adjunta preferentemente para cada página de la tabla de traducción.

De acuerdo con esta configuración, ya que generalmente la memoria física se divide en páginas y la tabla de traducción se configura para permitir que la unidad de procesamiento central acceda a la memoria física por página, la información de detección de error se adjunta para cada página de la tabla de traducción.

Por lo tanto, si la tabla de traducción está o no corrupta puede comprobarse por página.

25

35

55

En el primer aspecto anterior, preferentemente, un valor predeterminado se almacena en una dirección física predeterminada en la memoria física, la información de detección de error es información de traducción entre la dirección física predeterminada y una dirección virtual, y el medio de detección de error usa la información de detección de error leída en la memoria intermedia para leer un valor almacenado en la memoria física de acuerdo con la dirección virtual que corresponde a la dirección física predeterminada y detectar si el valor leído es o no el mismo que el valor predeterminado.

De acuerdo con esta configuración, un valor predeterminado se almacena en una dirección física predeterminada en la memoria física y la información de detección de error es información de traducción entre la dirección física predeterminada y una dirección virtual.

El medio de detección de error usa la información de detección de error leída en la memoria intermedia para leer un valor almacenado en la memoria física de acuerdo con la dirección virtual que corresponde a la dirección física predeterminada y detectar si el valor leído es o no el mismo que el valor predeterminado. Es decir, si la unidad de gestión de memoria puede traducir apropiadamente la dirección virtual de entrada en la dirección física, el valor leído debería ser el mismo que el valor predeterminado. En contraste, si la unidad de gestión de memoria no puede traducir apropiadamente la dirección virtual de entrada en la dirección física, el valor leído debería ser diferente del valor predeterminado.

Por lo tanto, puede detectarse la presencia o ausencia de un error en traducción entre la memoria virtual y la memoria física realizada por la unidad de gestión de memoria. Por lo tanto, si la unidad de procesamiento central puede realizar o no un acceso normal a la memoria física puede comprobarse mientras otro programa sigue ejecutándose.

Una unidad de procesamiento central de acuerdo con un segundo aspecto de la presente invención incluye el dispositivo de comprobación de traducción de dirección anteriormente descrito, en el que, cuando el medio de detección de error del dispositivo de comprobación de traducción de dirección detecta un error en traducción entre una dirección virtual y una dirección física realizada por la unidad de gestión de memoria, la unidad de procesamiento central detiene un programa en ejecución.

De acuerdo con esta configuración, la unidad de procesamiento central detiene un programa en ejecución cuando el medio de detección de error del dispositivo de comprobación de traducción de dirección detecta un error en traducción entre una dirección virtual y una dirección física realizada por la unidad de gestión de memoria.

Esto puede evitar un mal funcionamiento de la unidad de procesamiento central provocado por la traducción errónea entre una dirección virtual y una dirección física realizada por la unidad de gestión de memoria.

Un procedimiento de comprobación de traducción de dirección de acuerdo con un tercer aspecto de la presente invención es un procedimiento de comprobación de traducción de dirección para una unidad de procesamiento central que accede a una unidad de gestión de memoria, almacenando la unidad de gestión de memoria información de tabla de traducción del medio de almacenamiento externo en una memoria intermedia y traduciendo entre una dirección virtual y una dirección física sobre la base de la información de tabla de traducción almacenada en la memoria intermedia, indicando la información de tabla de traducción una tabla de traducción de traducción entre direcciones físicas que son direcciones en memoria virtual, incluyendo el procedimiento, sobre la base de información de detección de error adjuntada a la información de tabla de traducción de detección de la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la unidad de gestión de memoria, detectar la presencia o ausencia del error.

De acuerdo con esta configuración, la información de detección de error adjuntada a la información de tabla de traducción se usa para detectar la presencia o ausencia de un error en traducción entre una dirección virtual y una

dirección física realizada por la unidad de gestión de memoria. Por lo tanto, puede comprobarse, mientras otro programa sigue ejecutándose, si la unidad de procesamiento central puede realizar o no un acceso normal a la memoria física que usa la tabla de traducción leída en la memoria intermedia proporcionada en la unidad de gestión de memoria.

5 La presente invención es altamente ventajosa en que, mientras otro programa sigue ejecutándose, puede comprobarse si la unidad de procesamiento central puede realizar o no un acceso normal a la memoria física que usa la tabla de traducción leída en la memoria intermedia proporcionada en la unidad de gestión de memoria.

### Breve descripción de los dibujos

10

15

20

25

35

40

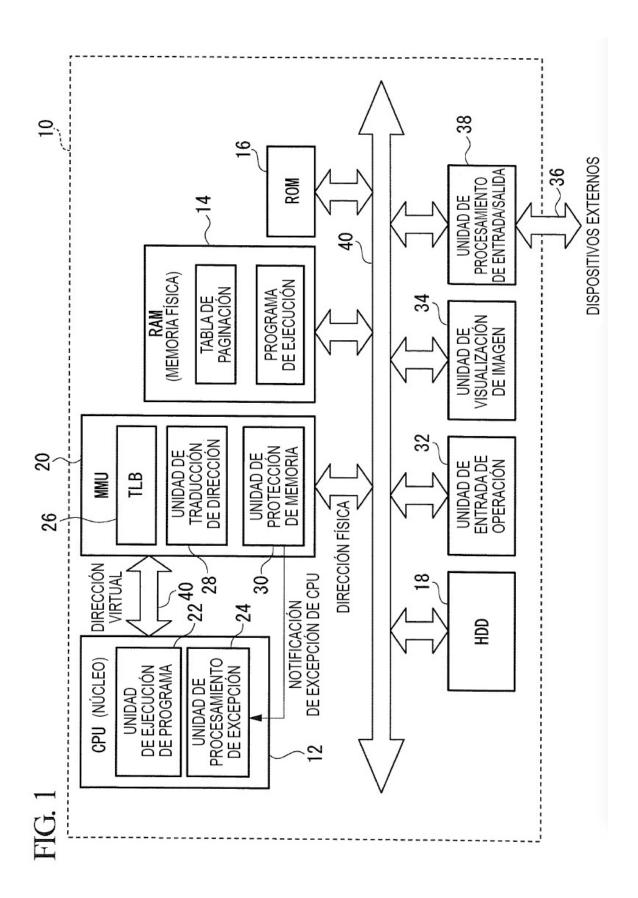

- {Fig. 1} La Figura 1 es un diagrama que muestra componentes principales de un sistema eléctrico de un aparato de procesamiento de información de acuerdo con una primera realización de la presente invención.

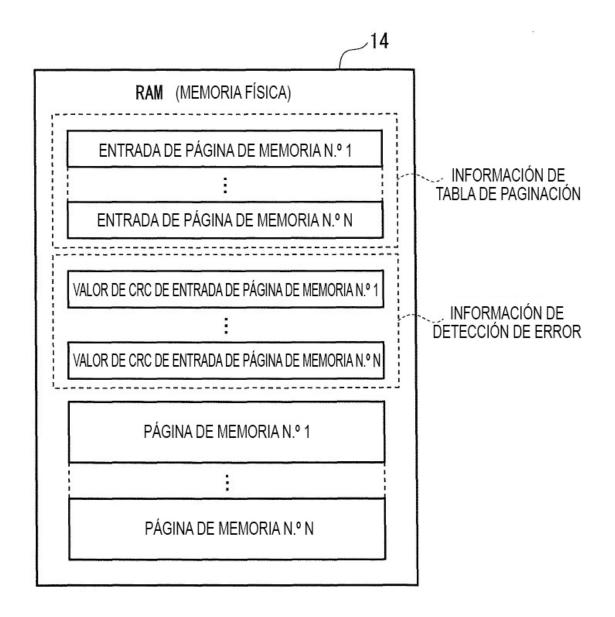

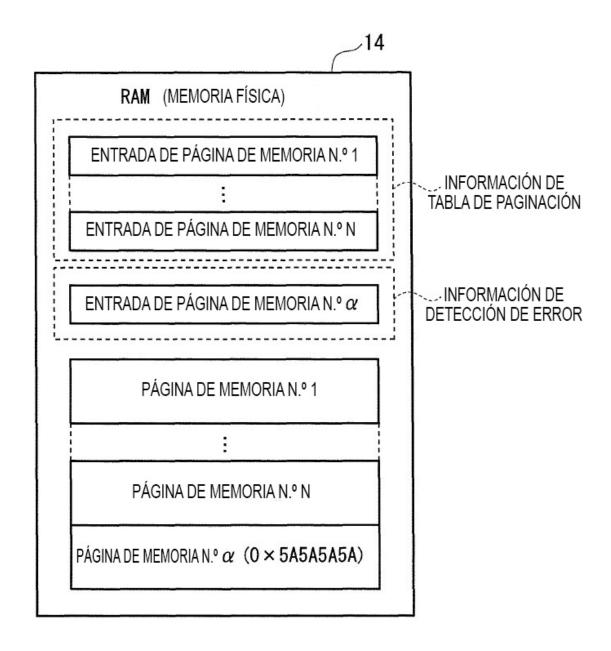

- {Fig. 2} la Figura 2 es un diagrama de bloques que muestra una estructura de información de tabla de paginación e información de detección de error almacenada en RAM de acuerdo con la primera realización de la presente invención.

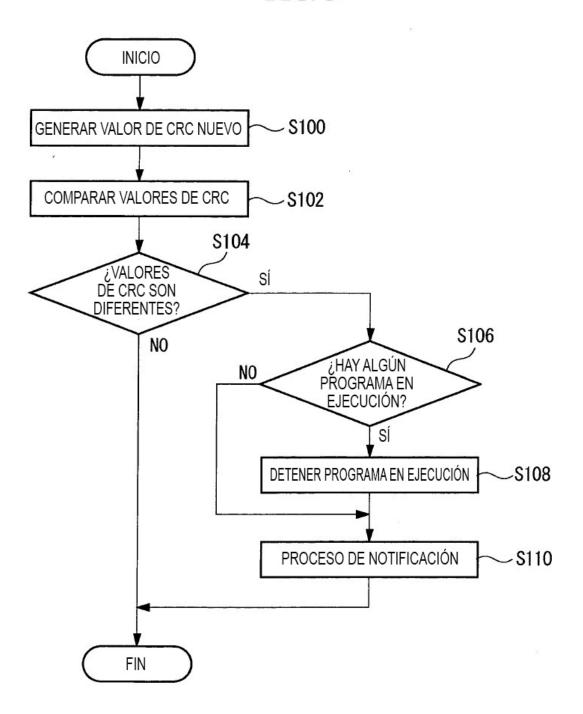

- {Fig. 3} la Figura 3 es un diagrama de flujo que muestra un flujo de procedimiento de un programa de comprobación de traducción de dirección de acuerdo con la primera realización de la presente invención.

- {Fig. 4} la Figura 4 es un diagrama de bloques que muestra una estructura de información de tabla de paginación e información de detección de error almacenada en RAM de acuerdo con una segunda realización de la presente invención.

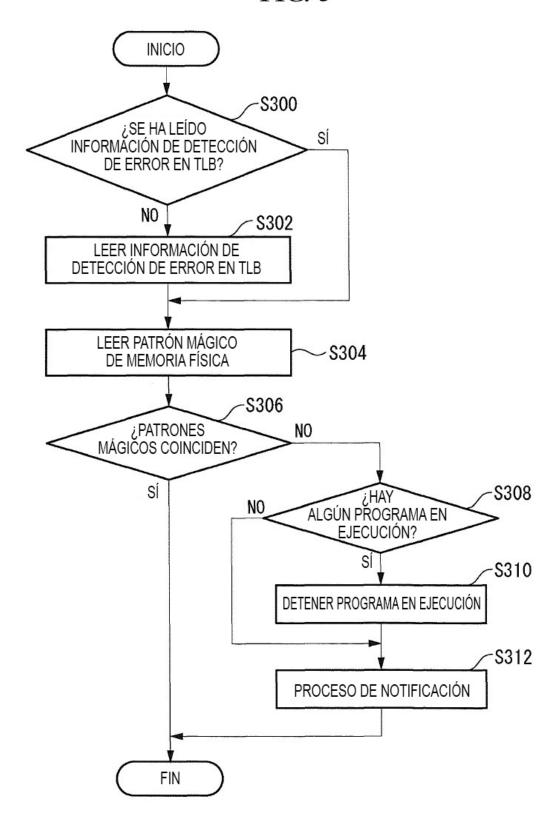

- {Fig. 5} la Figura 5 es un diagrama de flujo que muestra un flujo de procedimiento de un programa de comprobación de traducción de dirección de acuerdo con la segunda realización de la presente invención.

- {Fig. 6} la Figura 6 es un diagrama de bloques de descripción de procesamiento mediante una MMU convencional.

#### Descripción de las realizaciones

Una realización de un dispositivo de comprobación de traducción de dirección, una unidad de procesamiento central y un procedimiento de comprobación de traducción de dirección de acuerdo con la presente invención se describirán a continuación con referencia a los dibujos.

[Primera Realización]

Una primera realización no reivindicada de la presente invención se describirá a continuación.

La Figura 1 es un diagrama de bloques que muestra una configuración eléctrica de un aparato 10 de procesamiento de información de acuerdo con la realización.

El aparato 10 de procesamiento de información incluye: una CPU 12 que controla la operación de todo el aparato 10 de procesamiento de información; una RAM 14 que sirve como memoria física usada como, por ejemplo, un área de trabajo cuando la CPU 12 ejecuta diversos programas; una ROM 16 (Memoria de Solo Lectura) que tienen almacenados en la misma diversos programas y diversos tipos de información (datos); y una HDD 18 (Unidad de Disco Duro) que sirve como medio de almacenamiento de almacenamiento de diversos programas y diversos tipos de información. El medio de almacenamiento no se limita a la HDD 18 sino que puede ser cualquier medio de almacenamiento capaz de almacenar datos, tales como ROM flash.

La CPU 12 incluye una unidad 22 de ejecución de programa de ejecución de programas y una unidad 24 de procesamiento de excepción que realiza el procedimiento de detención de un programa en ejecución en respuesta a una entrada de una notificación de excepción de CPU (fallo de página) que se describirá a continuación.

La CPU 12 se conecta a una MMU 20 a través de un bus 40 interno. La MMU 20 traduce una dirección virtual emitida desde la CPU 12 en una dirección física sobre la base de una tabla de traducción de traducción entre direcciones virtuales y direcciones físicas (en lo sucesivo denominada como una "tabla de paginación").

Como se muestra en la Figura 2, la tabla de paginación incluye entradas de página de memoria (una entrada de página de memoria n.º 1 a una entrada de página de memoria n.º N) proporcionadas para respectivas páginas (una página de memoria n.º 1 a una página de memoria n.º N (N es un número entero)) de la RAM 14 (memoria física). Escrito en cada entrada de página de memoria hay una dirección virtual y una dirección física de una página de memoria correspondiente, así como un atributo de protección de memoria que indica "leer," "escribir," "ejecutar," "modo de súper usuario" en el que únicamente se aceptan accesos de un usuario con total autoridad, etc.

50 La MMU 20 incluye una TLB 26, una unidad 28 de traducción de dirección y una unidad 30 de protección de memoria.

# ES 2 662 127 T3

La TLB 26 almacena información de tabla de paginación que indica la tabla de paginación. Más específicamente, la TLB 26 lee entradas de página de memoria requeridas para un programa ejecutado por la CPU 12 de información de tabla de paginación almacenada en la RAM 14 y almacena las entradas de página de memoria leídas.

La unidad 28 de traducción de dirección realiza el procedimiento de traducción entre direcciones virtuales y direcciones físicas usando la información de tabla de paginación leída en la TLB 26.

5

25

30

45

50

55

La unidad 30 de protección de memoria detecta cualquier acceso no válido de tal forma que la memoria física no puede accederse con una dirección física que resulta de la traducción de una dirección virtual por la unidad 28 de traducción de dirección. Para cualquier acceso no válido detectado, la unidad 30 de protección de memoria emite una notificación de excepción de CPU, que es una señal que indica el acceso no válido, a la CPU 12.

La información de tabla de paginación se almacena en la HDD 18 previamente. Tras el inicio de la operación del aparato 10 de procesamiento de información, la información de tabla de paginación se envía desde la HDD 18 a la RAM 14 y se almacena en la misma. La información de tabla de paginación almacenada en la RAM 14 se lee en la TLB 26 de acuerdo con un programa ejecutado por la CPU 12.

El aparato 10 de procesamiento de información también incluye: una unidad 32 de entrada de operación implementada mediante un teclado, un ratón, etc., y recibir diversas entradas operacionales; y una unidad 34 de visualización de imagen, por ejemplo, un dispositivo de pantalla de cristal líquido. La unidad 32 de entrada de operación no se limita a un teclado o un ratón, sino que puede ser cualquier dispositivo de entrada capaz de recibir entradas operacionales al aparato 10 de procesamiento de información, tales como pulsadores. La unidad 34 de visualización de imagen no se limita a una pantalla de cristal líquido, sino que puede ser cualquier dispositivo de visualización capaz de proporcionar una notificación de diversos tipos de información a un usuario del aparato 10 de procesamiento de información, tales como un dispositivo de LED (Diodo Emisor de Luz).

El aparato 10 de procesamiento de información adicionalmente incluye una unidad 38 de procesamiento de entrada/salida conectada a través de una línea 36 de comunicación a dispositivos externos, tales como otros aparatos de procesamiento de información y otros dispositivos controlados por el aparato 10 de procesamiento de información, para intercambiar diversos tipos de información con los dispositivos externos.

La línea 36 de comunicación puede ser una línea de comunicación de área extensa proporcionada por una instalación de electricidad, una red privada tal como una LAN (Red de Área Local) o una trayectoria externa. La línea 36 de comunicación puede ser o bien una línea por cable o bien una línea inalámbrica.

La MMU 20, la RAM 14, la ROM 16, la HDD 18, la unidad 32 de entrada de operación, la unidad 34 de visualización de imagen y la unidad 38 de procesamiento de entrada/salida están eléctricamente conectadas entre sí a través del bus 40 interno. Por consiguiente, a través de la MMU 20, la CPU 12 puede acceder a la RAM 14, la ROM 16 y la HDD 18, reconocer el estado de operaciones realizadas en la unidad 32 de entrada de operación, visualizar una imagen en la unidad 34 de visualización de imagen y transmitir y recibir diversos tipos de información a y desde los dispositivos externos a través de la unidad 38 de procesamiento de entrada/salida.

La CPU 12 puede fallar en realizar un acceso normal a la RAM 14 a través de la MMU 20 por una razón tal como corrupción de la tabla de paginación leída en la TLB 26 de la MMU 20 o un fallo en la MMU 20. La CPU 12 puede entonces provocar mal funcionamiento, tales como un cuelgue o pérdida de control de la CPU 12 o cambios repentinos en valores emitidos a otros dispositivos conectados. Por lo tanto, la información de tabla de paginación, así como información de detección de error de detección de la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la MMU 20, se leen de la RAM 14 en la TLB 26 de la MMU 20 de acuerdo con la primera realización.

La información de detección de error de acuerdo con la primera realización es un valor de CRC para su uso en comprobación de redundancia cíclica generada sobre la base de la tabla de paginación indicada por la información de tabla de paginación. El valor de CRC puede generarse con cualquier técnica convencionalmente conocida, que no se describirá en la primera realización.

Como se muestra en la Figura 2, el valor de CRC se proporciona para cada una de las entradas de página de memoria n.º 1 a n.º N que corresponden a las páginas memoria n.º 1 a n.º N de la RAM 14 (memoria física). Es decir, el valor de CRC se genera para cada página de la RAM 14.

Antes de que la información de tabla de paginación se lea en la TLB 26, la CPU 12 de acuerdo con la primera realización realiza un procedimiento de comprobación de traducción de dirección. En el procedimiento de comprobación de traducción de dirección, se detecta la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la MMU 20 sobre la base de la información de detección de error adjuntada a la información de tabla de paginación.

Ahora, se describirá operación del aparato 10 de procesamiento de información de acuerdo con la primera realización.

# ES 2 662 127 T3

La Figura 3 es un diagrama de flujo que muestra un flujo de procedimiento de un programa de comprobación de traducción de dirección ejecutado por la CPU 12 antes de que la información de tabla de paginación almacenada en la RAM 14 se lea en la TLB 26 junto con la información de detección de error. El programa se almacena previamente en un área predeterminada de la HDD 18.

5 En la etapa 100, para cada entrada de página de memoria de la información de tabla de paginación a leer en la TLB 26, se genera un nuevo valor de CRC sobre la base de la entrada de página de memoria.

A continuación, en la etapa 102, para cada entrada de página de memoria, se compara un valor de CRC como información de detección de error acerca de la información de tabla de paginación a leer en la TLB 26 con el nuevo valor de CRC generado en la etapa 100.

- A continuación, en la etapa 104, se determina si el valor de CRC como la información de detección de error es o no diferente del nuevo valor de CRC. Si la determinación resulta en SÍ, la información de tabla de paginación a leer no se lee en la TLB 26 y el procedimiento continúa a la etapa 106. Si la determinación resulta en NO, la información de tabla de paginación a leer se lee en la TLB 26 y el programa finaliza.

- Es decir, la determinación en la etapa 104 que resulta en SÍ significa la detección de corrupción de tabla de paginación indicada por la información de tabla de paginación leída por la TLB 26 por alguna razón. La razón de la corrupción de la tabla de paginación puede ser la reescritura de la tabla de paginación por un programa errante o bits ilegibles de la tabla de paginación provocados por un error temporal que se produjo en la RAM 14 debido a, por ejemplo, radiación.

- En la etapa 106, se determina si algún programa se está o no ejecutando. Si la determinación resulta en SÍ, el procedimiento continúa a la etapa 108. Si la determinación resulta en NO, el procedimiento continúa a la etapa 110.

En la etapa 108, se detiene el programa que se ejecuta mediante la unidad 22 de ejecución de programa y el procedimiento continúa a la etapa 110.

En la etapa 110, se realiza un procedimiento de notificación. Es decir, se proporciona una notificación visualizando, en una pantalla de la unidad 34 de visualización de imagen, el hecho de que los datos de página están corrompidos y el nombre, etc. de cualquier programa detenido que ha estado en funcionamiento. El programa de comprobación de traducción de dirección finaliza a continuación. En el procedimiento de notificación, puede proporcionarse una notificación de una entrada de página de memoria detectada como que implica la corrupción.

25

30

40

50

El valor de CRC como la información de detección de error puede generarse y almacenarse en la HDD 18 cuando se genera la información de tabla de paginación. Como alternativa, el valor de CRC puede generarse y actualizarse cada vez que la CPU 12 se inicializa, cada vez que un atributo de la tabla de paginación se actualiza o cada vez que la información de tabla de paginación se lee en la TLB 26.

En particular, si el valor de CRC se genera y almacena en la HDD 18 cuando se genera la información de tabla de paginación, detección de la diferencia entre los valores de CRC sugiere que la tabla de paginación se ha corrompido durante el procedimiento de ser leída de la HDD 18 en la TLB 26 a través de la RAM 14.

35 Si el contenido de la tabla de paginación se cambia con el paso del tiempo, tal como que se cambian atributos, el valor de CRC debe generarse cada vez que la información de tabla de paginación se lee de la RAM 14 en la TLB 26.

Como se ha descrito anteriormente, en el aparato 10 de procesamiento de información de acuerdo con la primera realización, la MMU 20 traduce entre una dirección virtual y una dirección física sobre la base de la tabla de traducción de traducción entre direcciones virtuales y direcciones físicas. La información de tabla de traducción que indica la tabla de traducción se almacena en la TLB 26 proporcionada en la MMU 20.

Antes de ser leída en la TLB 26, la información de tabla de traducción se almacena en la RAM 14 proporcionada fuera de la MMU 20. La información de detección de error de detección de la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la MMU 20 se adjunta a la información de tabla de traducción.

La CPU 12 detecta, sobre la base de la información de detección de error, la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la MMU 20.

Por lo tanto, la CPU 12 de acuerdo con la primera realización usa la información de detección de error adjuntada a la información de tabla de paginación para detectar la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la MMU 20. Por lo tanto, puede comprobarse, mientras otro programa sigue ejecutándose, si la CPU 12 puede o no realizar un acceso normal a la memoria física que usa la tabla de paginación leída en la TLB 26 proporcionada en la MMU 20.

La información de detección de error de acuerdo con la primera realización es un valor de CRC para su uso en comprobación de redundancia cíclica generada sobre la base de la tabla de paginación indicada por la información de tabla de paginación. Antes de que la información de tabla de paginación se lea en la TLB 26, un nuevo valor de

CRC se genera sobre la base de la tabla de paginación indicada por la información de tabla de paginación a leer. A continuación, se detecta si el valor de CRC como la información de error es el mismo que el nuevo valor de CRC.

Por lo tanto, la CPU 12 de acuerdo con la primera realización puede detectar si la tabla de paginación leída en la TLB 26 está o no corrompida. Por lo tanto, si la CPU 12 puede o no realizar un acceso normal a la memoria física puede comprobarse mientras otro programa sigue ejecutándose.

La información de detección de error de acuerdo con la primera realización se adjunta a cada página de la tabla de paginación. Por lo tanto, si la tabla de paginación está o no corrompida puede comprobarse por página.

Además, la CPU 12 de acuerdo con la primera realización detiene un programa en ejecución si se detecta un error en traducción entre una dirección virtual y una dirección física realizada por la MMU 20. Esto puede evitar un mal funcionamiento de la CPU 12 provocado por la traducción errónea entre una dirección virtual y una dirección física realizada por la MMU 20.

[Segunda Realización]

5

10

30

45

50

Una segunda realización reivindicada de la presente invención se describirá a continuación.

La configuración del aparato 10 de procesamiento de información de acuerdo con la segunda realización es la misma que la del aparato 10 de procesamiento de información de acuerdo con la primera realización mostrada en la Figura 1 y, por lo tanto, no se describirá.

En la segunda realización, un valor predeterminado (en lo sucesivo denominado como un "patrón mágico") se almacena en una dirección física predeterminada de la RAM 14 (memoria física). La información de detección de error es información de traducción entre la dirección física predeterminada y una dirección virtual.

Específicamente, como se muestra en la Figura 4, la información de detección de error de acuerdo con la segunda realización es una entrada de página de memoria de acceso a una página de memoria n.º α (α es un número entero diferente de los números 1 a N) en la que se almacena el patrón mágico. Esta entrada de página de memoria se adjunta a la información de tabla de paginación. La página de memoria n.º α de acuerdo con la segunda realización almacena 035A5A5A5A como un patrón mágico ilustrativo. La misma información que el patrón mágico almacenado en la RAM 14 se escribe previamente en un programa de comprobación de traducción de dirección que se describirá a continuación.

Si el aparato 10 de procesamiento de información se configura para permitir que la CPU 12 escriba a la RAM 14 sin la intervención de la MMU 20, el patrón mágico se escribe convenientemente a la RAM 14 antes de que se active la MMU 20. Sin embargo, esto no es limitación, pero el patrón mágico puede escribirse a la RAM 14 después de que se active la MMU 20.

El patrón mágico puede cambiarse en cada intervalo de tiempo predeterminado. También, la dirección física en la que se escribe el patrón mágico puede cambiarse en cada intervalo de tiempo predeterminado.

Ahora, se describirá operación del aparato 10 de procesamiento de información de acuerdo con la segunda realización.

La Figura 5 es un diagrama de flujo que muestra un flujo de procedimiento de un programa de comprobación de traducción de dirección ejecutado por la unidad 22 de ejecución de programa de la CPU 12 en la realización de un procedimiento de detección de error de acuerdo con la segunda realización. El programa se almacena previamente en un área predeterminada de la HDD 18. El programa de comprobación de traducción de dirección se envía desde la HDD 18 a la RAM 14 en intervalos de tiempo predeterminados (por ejemplo, cada diez minutos) para almacenarse en la misma y ejecutarse.

En la etapa 300, se intenta un acceso a una dirección virtual de una entrada de página de memoria como la información de detección de error para determinar si la información de detección de error ha sido o no leída en la TLB 26. Si la determinación resulta en SÍ, el procedimiento continúa a la etapa 304. Si la determinación resulta en NO, el procedimiento continúa a la etapa 302. Es decir, si no puede accederse a la dirección virtual, la información de detección de error no se ha leído en la TLB 26. Si puede accederse a la dirección virtual, la información de detección de error se ha leído en la TLB 26.

En la etapa 302, ya que la entrada de página de memoria como la información de detección de error no se ha leído en la TLB 26, la información de detección de error se lee de la RAM 14 en la TLB 26.

En la etapa 304, la dirección virtual de lectura de un patrón mágico almacenado en la RAM 14 se emite a la MMU 20 y traduce en una dirección física sobre la base de la entrada de página de memoria como la información de detección de error leída en la TLB 26. El número mágico se lee a continuación de la RAM 14.

A continuación, en la etapa 306, se detecta si un patrón mágico escrito previamente en el programa de comprobación de traducción de dirección es diferente del patrón mágico leído de la RAM 14. Es decir, en esta etapa,

se determina si el patrón mágico escrito previamente en el programa de comprobación de traducción de dirección coindice o no con el patrón mágico leído de la RAM 14. Si la determinación resulta en SÍ, el programa finaliza. Si la determinación resulta en NO, el procedimiento continúa a la etapa 308.

Si la MMU 20 ha tenido éxito en traducir apropiadamente la dirección virtual de entrada en la dirección física, el patrón mágico leído de la RAM 14 debería ser el mismo que el patrón mágico escrito previamente en el programa de comprobación de traducción de dirección. En contraste, si la MMU 20 ha fallado en traducir apropiadamente la dirección virtual de entrada en la dirección física, el patrón mágico leído de la RAM 14 debería ser diferente del patrón mágico escrito previamente en el programa de comprobación de traducción de dirección. Si el patrón mágico leído de la RAM 14 es diferente del patrón mágico escrito previamente en el programa de comprobación de traducción de dirección, sugiere un error que se produce en la traducción entre la dirección virtual y la dirección física realizada por la MMU 20, es decir, un fallo que se produce en la MMU 20.

En la etapa 308, se determina si algún programa se está o no ejecutando. Si la determinación resulta en SÍ, el procedimiento continúa a la etapa 310. Si la determinación resulta en NO, el procedimiento continúa a la etapa 312.

En la etapa 310, se detiene el programa que se ejecuta mediante la unidad 22 de ejecución de programa.

En la etapa 312, se realiza un procedimiento de notificación. Es decir, se proporciona una notificación visualizando, en la pantalla de la unidad 34 de visualización de imagen, el hecho de que los patrones mágicos no coinciden entre sí y el nombre, etc. de cualquier programa detenido que ha estado en funcionamiento. El programa de comprobación de traducción de dirección finaliza a continuación.

Se ha de observar que, si el patrón mágico no puede leerse de la RAM 14 en la etapa 304 anterior, se continua el procedimiento con la suposición de que los patrones mágicos no coinciden entre sí en la etapa 306. Es decir, si el patrón mágico no puede leerse de la RAM 14, de nuevo, sugiere un error que se produce en la traducción entre la memoria virtual y la memoria física realizada por la MMU 20, es decir, un fallo que se produce en la MMU 20.

Como se ha descrito anteriormente, el aparato 10 de procesamiento de información de acuerdo con la segunda realización almacena el patrón mágico en una dirección física predeterminada en la memoria física. La información de detección de error es información de traducción entre la dirección física predeterminada y una dirección virtual. La CPU 12 de acuerdo con la segunda realización usa la información de detección de error leída en la TLB 26 para leer un valor almacenado en la memoria física sobre la base de la dirección virtual que corresponde a la dirección física y detectar si el valor leído es el mismo que el patrón mágico.

Por lo tanto, la CPU 12 de acuerdo con la segunda realización puede detectar la presencia o ausencia de un error en traducción entre la memoria virtual y la memoria física realizada por la MMU 20. Por lo tanto, si la CPU 12 puede o no realizar un acceso normal a la memoria física puede comprobarse mientras otro programa sigue ejecutándose.

Mientras la presente invención se ha descrito de acuerdo con las anteriores realizaciones, el ámbito técnico de la presente invención no se limita a lo que se ha descrito en las realizaciones anteriores.

Por ejemplo, mientras la RAM 14 sirve como la memoria física en las realizaciones anteriormente descritas, la presente invención no se limita a esto. En su lugar, la RAM 14 y la HDD 18 pueden servir como la memoria física.

También, mientras la notificación se proporciona a través de la imagen dispositivo de visualización en el procedimiento de notificación en las realizaciones anteriormente descritas, la presente invención no se limita a esto. Por ejemplo, si se conecta una impresora a la unidad 28 de procesamiento de entrada/salida, puede proporcionarse la notificación provocando que la impresora forme una notificación escrita como una imagen en un medio tal como papel. Como alternativa, la notificación puede proporcionarse como sonido a través de un altavoz (no mostrado).

### {Lista de signos de referencia}

10 aparato de procesamiento de información

12 CPU

14 RAM

20 MMU

5

10

25

30

35

40

45

26 TLB

30 unidad de protección de memoria

### **REIVINDICACIONES**

1. Un dispositivo de comprobación de traducción de dirección que comprende:

una unidad (20) de gestión de memoria de traducción entre una dirección virtual y una dirección física sobre la base de una tabla de traducción de traducción entre direcciones físicas que son direcciones en memoria (14) física y direcciones virtuales que son direcciones en memoria virtual, estando la unidad de gestión de memoria provista de una memoria (26) intermedia de almacenamiento de información de tabla de traducción que indica la tabla de traducción:

medio (18) de almacenamiento proporcionado fuera de la unidad (20) de gestión de memoria y que tiene almacenado en el mismo la información de tabla de traducción e información de detección de error adjuntada a la información de tabla de traducción, siendo la información de detección de error de detección de la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la unidad (20) de gestión de memoria; y

medio (12) de detección de error de detección de la presencia o ausencia del error sobre la base de la información de detección de error,

### caracterizado porque

un valor predeterminado se almacena en una dirección física predeterminada en la memoria (14) física, la información de detección de error es información de traducción entre la dirección física predeterminada y una dirección virtual, y

el medio (12) de detección de error se configura para usar la información de detección de error leída en la memoria (26) intermedia para leer un valor almacenado en la memoria (14) física de acuerdo con la dirección virtual que corresponde a la dirección física predeterminada y detectar si el valor leído es o no el mismo que el valor predeterminado.

- 2. Una unidad (12) de procesamiento central que comprende el dispositivo de comprobación de traducción de dirección de acuerdo con la reivindicación 1, en la que

- cuando el medio (12) de detección de error del dispositivo de comprobación de traducción de dirección detecta un error en traducción entre una dirección virtual y una dirección física realizada por la unidad (20) de gestión de memoria, la unidad (12) de procesamiento central se configura para detener un programa en ejecución.

- 3. Un procedimiento de comprobación de traducción de dirección para una unidad (12) de procesamiento central que accede a una unidad (20) de gestión de memoria, almacenando la unidad (20) de gestión de memoria información de tabla de traducción de medio (18) de almacenamiento externo en una memoria (26) intermedia y traduciendo entre una dirección virtual y una dirección física sobre la base de la información de tabla de traducción almacenada en la memoria (26) intermedia, indicando la información de tabla de traducción una tabla de traducción de traducción entre direcciones físicas que son direcciones en memoria (14) física y direcciones virtuales que son direcciones en memoria virtual, comprendiendo el procedimiento

- detectar la presencia o ausencia del error sobre la base de información de detección de error adjuntada a la información de tabla de traducción de detección de la presencia o ausencia de un error en traducción entre una dirección virtual y una dirección física realizada por la unidad (20) de gestión de memoria, en el que un valor predeterminado se almacena en una dirección física predeterminada en la memoria (14) física y la información de detección de error es información de traducción entre la dirección física predeterminada y una dirección virtual,

leer un valor almacenado en la memoria (14) física de acuerdo con la dirección virtual que corresponde a la dirección física predeterminada que usa la información de detección de error leída en la memoria (26) intermedia, v

detectar si el valor leído es o no el mismo que el valor predeterminado.

45

5

10

15

20

30

FIG. 2

FIG. 3

FIG. 4

FIG. 5