# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 664 851

61 Int. Cl.:

H04N 19/91 (2014.01) H04N 19/12 (2014.01) H04N 19/46 (2014.01)

12 TRADUCCIÓN DE PATENTE EUROPEA

T3

96) Fecha de presentación y número de la solicitud europea: 06.11.2012 E 16195297 (3)

97) Fecha y número de publicación de la concesión europea: 17.01.2018 EP 3139617

(54) Título: Codificación aritmética de la posición del último coeficiente distino de cero

(30) Prioridad:

07.11.2011 US 201161556398 P

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 23.04.2018

73) Titular/es:

TAGIVAN II LLC (100.0%) 5425 Wisconsin Avenue, Suite 801 Chevy Chase MD 20815, US

72 Inventor/es:

SASAI, HISAO; NISHI, TAKAHIRO; SHIBAHARA, YOUJI; SUGIO, TOSHIYASU; TANIKAWA, KYOKO; MATSUNOBU, TORU y TERADA, KENGO

(74) Agente/Representante:

MILTENYI, Peter

### **DESCRIPCIÓN**

Codificación aritmética de la posición del último coeficiente distinto de cero

#### Campo de la técnica

La presente invención se refiere a una técnica de codificación de imágenes para codificación aritmética.

5 La descripción describe tanto la técnica de codificación de imágenes como una técnica de decodificación de imágenes correspondiente para proporcionar una mejor comprensión de la invención. Sin embargo, la invención se limita a la técnica de codificación de imágenes

#### Estado de la técnica

10

15

20

25

35

40

Cada vez hay más aplicaciones para proporcionar servicios a través de Internet (por ejemplo, videoconferencia, difusión de vídeo digital y servicios de vídeo bajo demanda, incluyendo transmisión continua de contenido de vídeo). Estas aplicaciones se basan en la transmisión de datos de vídeo. Cuando las aplicaciones transmiten datos de vídeo, la mayor parte de los datos de vídeo se transmiten a través de un trayecto de transmisión convencional que tiene un ancho de banda limitado. Además, cuando las aplicaciones graban datos de vídeo, la mayor parte de los datos de vídeo se graban en un medio de grabación convencional que tiene una capacidad limitada. Para transmitir datos de vídeo a través del trayecto de transmisión convencional o grabar datos de vídeo en el medio de grabación convencional, resulta indispensable comprimir o reducir la cantidad de datos de los datos de vídeo.

En vista de esto, se han desarrollado muchas normas de codificación de vídeo para comprimir datos de vídeo. Estas normas de codificación de vídeo son, por ejemplo, las normas ITU-T denominadas H.26x y las normas ISO/IEC denominadas MPEG-x. En la actualidad, la norma de codificación de vídeo más reciente y más avanzada es la norma denominada H.264/MPEG-4 AVC (véase la bibliografía no de patentes (NPL) 1 y la bibliografía no de patentes (NPL) 2).

El enfoque de codificación subyacente a la mayor parte de estas normas de codificación de vídeo se basa en codificación predictiva que incluye las siguientes etapas principales de (a) a (d): (a) Dividir cada trama de vídeo en bloques que tienen cada uno píxeles para comprimir datos de la trama de vídeo para un bloque cada vez. (b) Predecir cada bloque basándose en datos de vídeo anteriormente codificados para identificar redundancia temporal y espacial. (c) Restar los datos predichos de los datos de vídeo para eliminar la redundancia identificada. (d) Comprimir los datos restantes (bloques residuales) mediante transformada de Fourier, cuantificación y codificación por entropía.

En cuanto a la etapa (a), la norma de codificación de vídeo actual proporciona diferentes modos de predicción dependiendo de un macrobloque que va a predecirse. Según la mayor parte de las normas de codificación de vídeo, se usan estimación del movimiento y compensación del movimiento para predecir datos de vídeo basándose en una trama anteriormente codificada y decodificada (predicción inter-tramas). Alternativamente, pueden extrapolarse datos de bloque a partir de un bloque adyacente de la misma trama (predicción intra-tramas).

En la etapa (d), coeficientes cuantificados incluidos en un bloque actual que va a codificarse se exploran en un orden predeterminado (orden de exploración). Después se codifica información (indicador significativo) que indica si los coeficientes explorados son coeficientes cero o coeficientes distintos de cero (por ejemplo, información binaria (símbolo) que indica un coeficiente distinto de cero como 1 y un coeficiente cero como 0).

Además, se binariza información que indica la posición del último coeficiente distinto de cero en el orden de exploración (información de última posición), se codifica mediante codificación aritmética binaria adaptativa de contexto, y se decodifica mediante decodificación aritmética binaria adaptativa de contexto (véase la bibliografía no de patentes (NPL) 3).

#### Lista de menciones

#### Bibliografía no de patentes

[NPL 1] Recomendación de ITU-T H.264 "Advanced video coding for generic audiovisual services", marzo de 2010.

45 [NPL 2] JCT-VC "WD4: Working Draft 4 of High-Efficiency Video Coding", JCTVC-F803, julio de 2011.

[NPL 3] Seregin V et al: "Binarisation modification for last position coding", 97. MPEG Meeting, 18-22 de julio de 2011, Turín.

## Sumario de la invención

## Problema técnico

50 Sin embargo, con la técnica convencional, una conmutación apropiada entre contextos resulta difícil en la

codificación aritmética binaria adaptativa de contexto y la decodificación aritmética binaria adaptativa de contexto de la información de última posición. Por ejemplo, cuando se usa el mismo contexto para símbolos binarios que son significativamente diferentes en cuanto a la probabilidad de aparición de símbolo, la precisión de la probabilidad de aparición de símbolo disminuye, y por tanto la eficiencia de codificación también disminuye.

En vista de esto, una realización a modo de ejemplo y no limitativa proporciona un método/aparato de codificación de imágenes y un método/aparato de decodificación de imágenes para codificar de manera aritmética y decodificar de manera aritmética la información de última posición usando un contexto que se conmuta de manera apropiada entre una pluralidad de contextos.

### Solución al problema

10 La solución al problema se expone mediante las reivindicaciones independientes

Debe observarse que este aspecto general puede implementarse usando un sistema, un aparato, un circuito integrado, un programa informático, o un medio de grabación legible por ordenador tal como un CD-ROM, o cualquier combinación de sistemas, aparatos, circuitos integrados, programas informáticos o medios de grabación legibles por ordenador.

## 15 Efectos ventajosos de la invención

Con el método de codificación de imágenes según un aspecto de la presente invención, es posible codificar de manera aritmética la información de última posición usando un contexto que se conmuta de manera apropiada entre una pluralidad de contextos.

#### Breve descripción de los dibujos

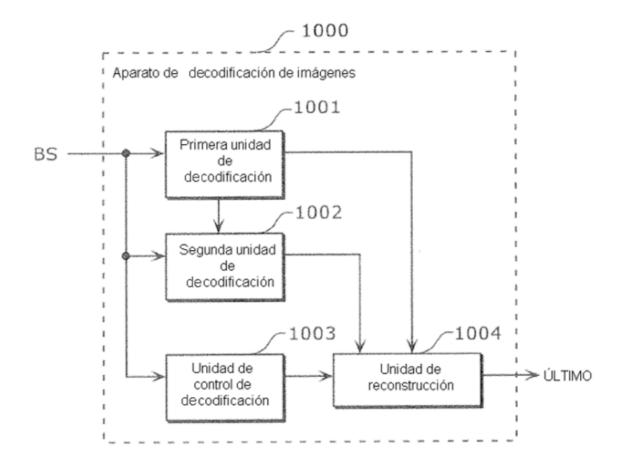

- [Fig. 1] La figura 1 es un diagrama de bloques que muestra un ejemplo de una configuración de un aparato de decodificación de imágenes según el conocimiento subyacente.

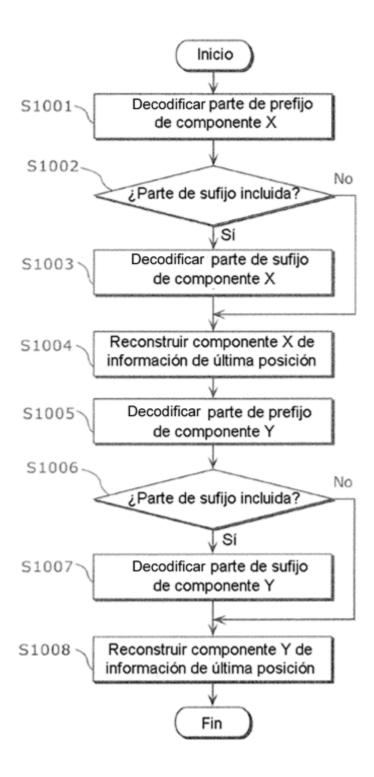

- [Fig. 2] La figura 2 es un diagrama de flujo que muestra un ejemplo de un método de decodificación de imágenes según el conocimiento subyacente.

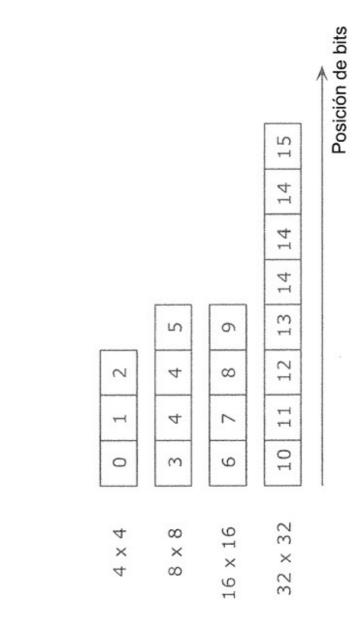

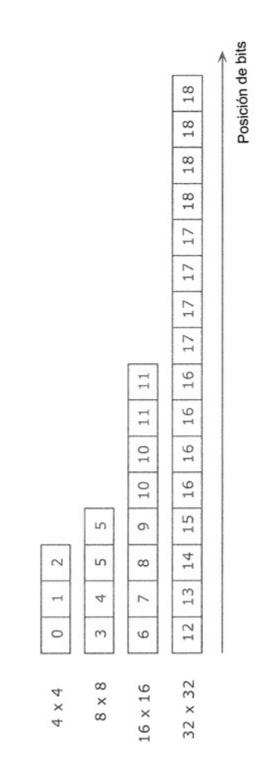

- [Fig. 3A] La figura 3A es un diagrama que muestra un ejemplo de señales binarias de información de última posición cuando el tamaño de bloque es de 4x4.

- [Fig. 3B] La figura 3B es un diagrama que muestra un ejemplo de señales binarias de información de última posición cuando el tamaño de bloque es de 8x8.

- [Fig. 3C] La figura 3C es un diagrama que muestra un ejemplo de señales binarias de información de última posición cuando el tamaño de bloque es de 16x16.

- [Fig. 3D] La figura 3D es un diagrama que muestra un ejemplo de señales binarias de información de última posición cuando el tamaño de bloque es de 32x32.

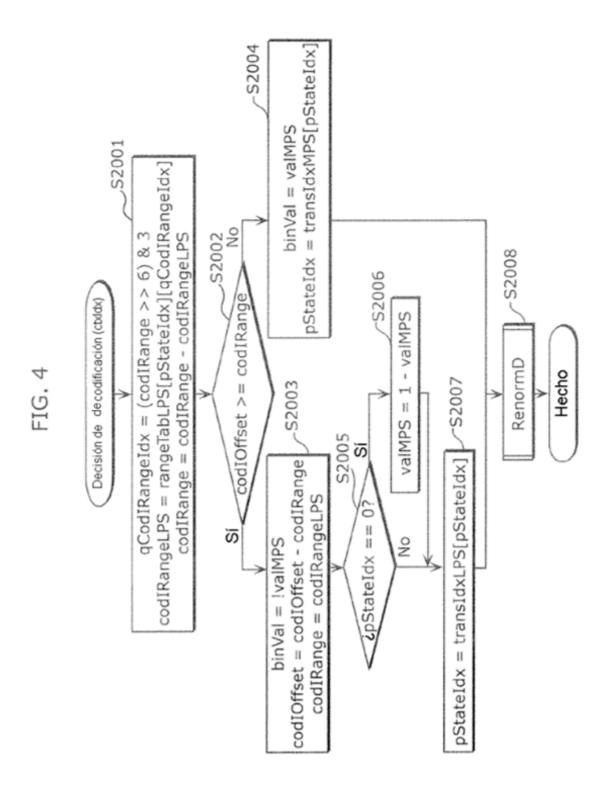

- [Fig. 4] La figura 4 es un diagrama de flujo que muestra decodificación aritmética binaria adaptativa de contexto.

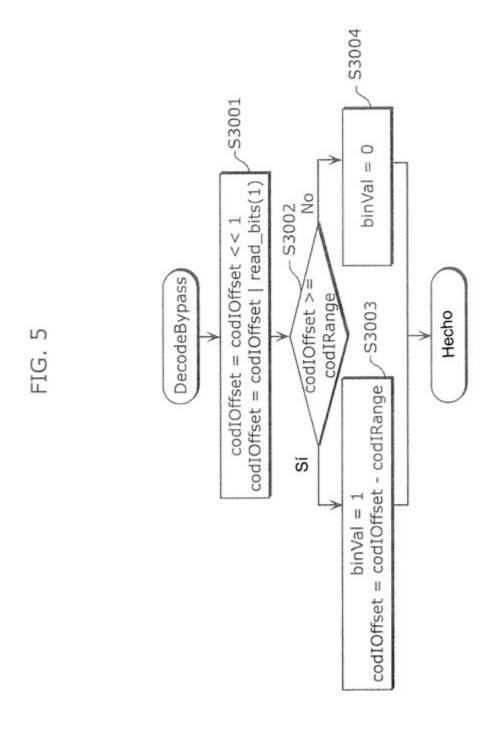

- [Fig. 5] La figura 5 es un diagrama de flujo que muestra decodificación de derivación.

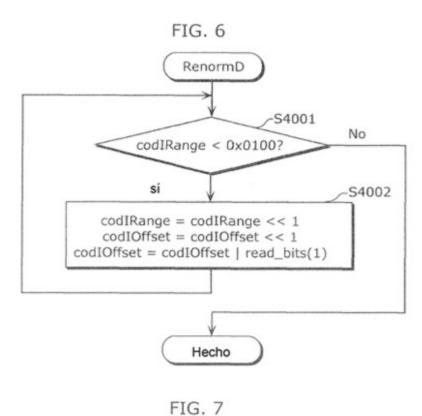

- [Fig. 6] La figura 6 es un diagrama de flujo que muestra normalización.

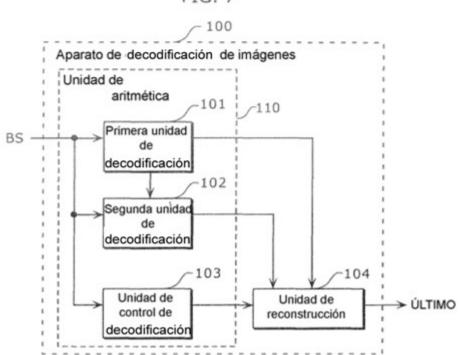

- [Fig. 7] La figura 7 es un diagrama de bloques que muestra una configuración funcional de un aparato de decodificación de imágenes según la realización 1.

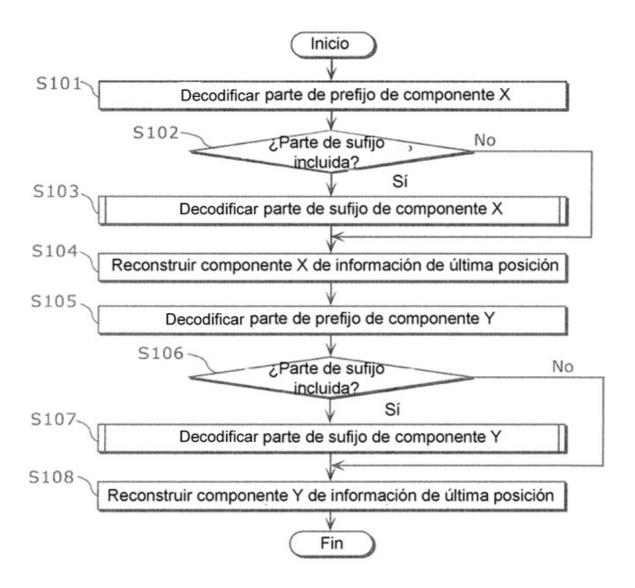

- [Fig. 8A] La figura 8A es un diagrama de flujo que muestra un ejemplo de operaciones de procesamiento de un aparato de decodificación de imágenes según la realización 1.

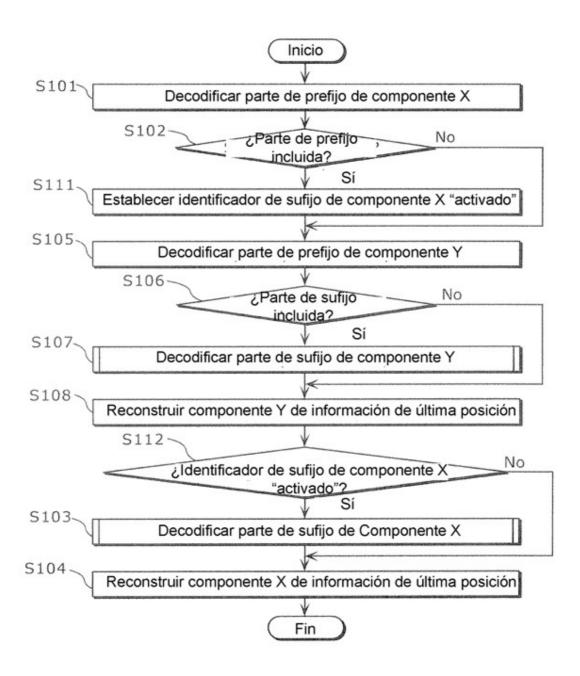

- [Fig. 8B] La figura 8B es un diagrama de flujo que muestra otro ejemplo de operaciones de procesamiento de un aparato de decodificación de imágenes según la realización 1.

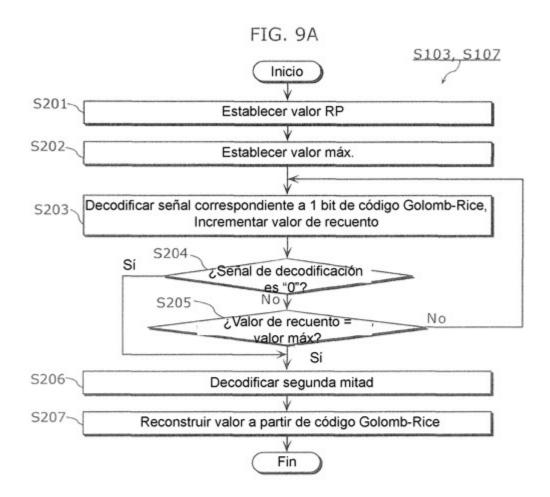

- [Fig. 9A] La figura 9A es un diagrama de flujo que muestra un ejemplo de operaciones de procesamiento de una segunda unidad de decodificación según la realización 1.

- [Fig. 9B] La figura 9B es un diagrama que muestra un ejemplo de una relación entre el tamaño de bloque y la longitud máxima de una parte de prefijo según la realización 1.

- [Fig. 9C] La figura 9C es un diagrama que muestra otro ejemplo de una relación entre el tamaño de bloque y la longitud máxima de una parte de prefijo según la realización 1.

- [Fig. 9D] La figura 9D es un diagrama que muestra un ejemplo de una relación entre el tamaño de bloque y el

- parámetro de Rice según la realización 1.

- [Fig. 9E] La figura 9E es un diagrama que muestra otro ejemplo de una relación entre el tamaño de bloque y el parámetro de Rice según la realización 1.

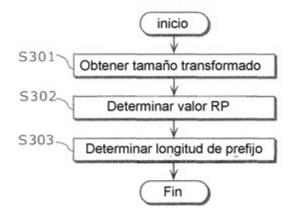

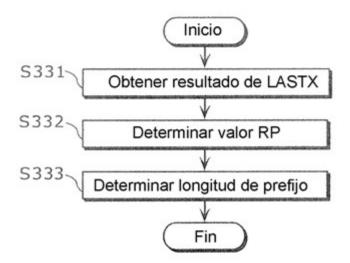

- [Fig. 10A] La figura 10A es un diagrama de flujo que muestra un ejemplo de un método de determinación de un valor de RP y una longitud máxima de una parte de prefijo.

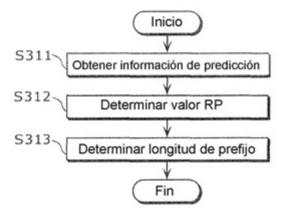

- [Fig. 10B] La figura 10B es un diagrama de flujo que muestra otro ejemplo de un método de determinación de un valor de RP y una longitud máxima de una parte de prefijo.

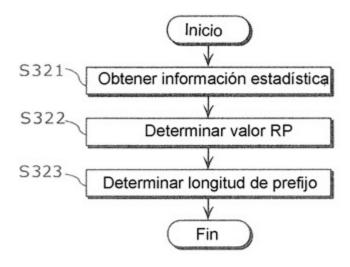

- [Fig. 10C] La figura 10C es un diagrama de flujo que muestra otro ejemplo de un método de determinación de un valor de RP y una longitud máxima de una parte de prefijo.

- 10 [Fig. 10D] La figura 10D es un diagrama de flujo que muestra otro ejemplo de un método de determinación de un valor de RP y una longitud máxima de una parte de prefijo.

- [Fig. 11A] La figura 11A es un diagrama para describir una relación entre posiciones de bits y contextos según la realización 1.

- [Fig. 11B] La figura 11B es un diagrama para describir una relación entre posiciones de bits y contextos según un ejemplo comparable.

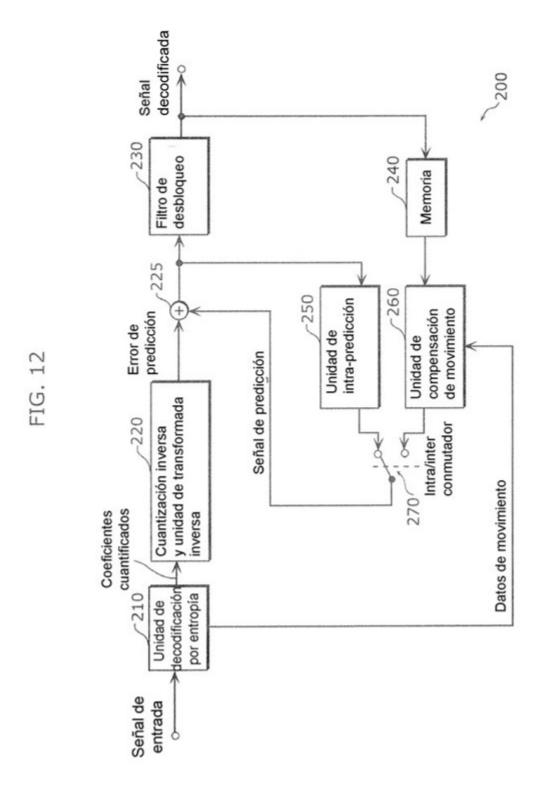

- [Fig. 12] La figura 12 es un diagrama de bloques que muestra un ejemplo de una configuración de un aparato de decodificación de imágenes según una variación de la realización 1.

- [Fig. 13] La figura 13 es un diagrama de bloques que muestra una configuración funcional de un aparato de codificación de imágenes según la realización 2.

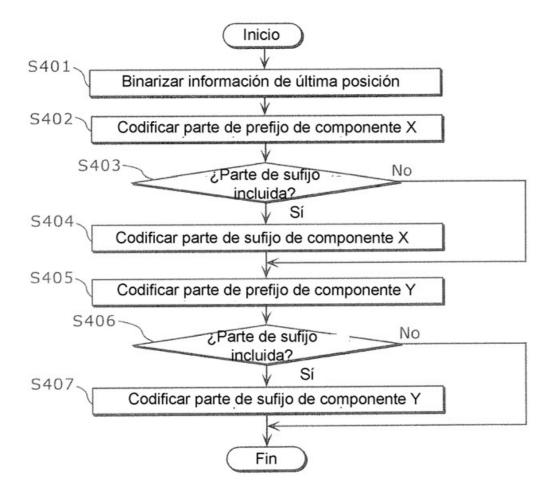

- [Fig. 14A] La figura 14A es un diagrama de flujo que muestra un ejemplo de operaciones de procesamiento de un aparato de codificación de imágenes según la realización 2.

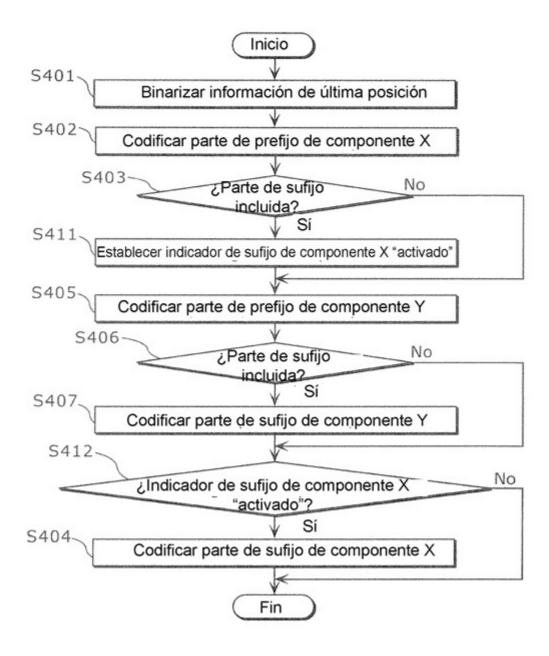

- [Fig. 14B] La figura 14B es un diagrama de flujo que muestra otro ejemplo de operaciones de procesamiento de un aparato de codificación de imágenes según la realización 2.

- [Fig. 15] La figura 15 es un diagrama que muestra un ejemplo de señales binarias de información de última posición cuando el tamaño de bloque es de 16x16.

- [Fig. 16] La figura 16 es un diagrama de bloques que muestra un ejemplo de una configuración de un aparato de codificación de imágenes según la realización 2.

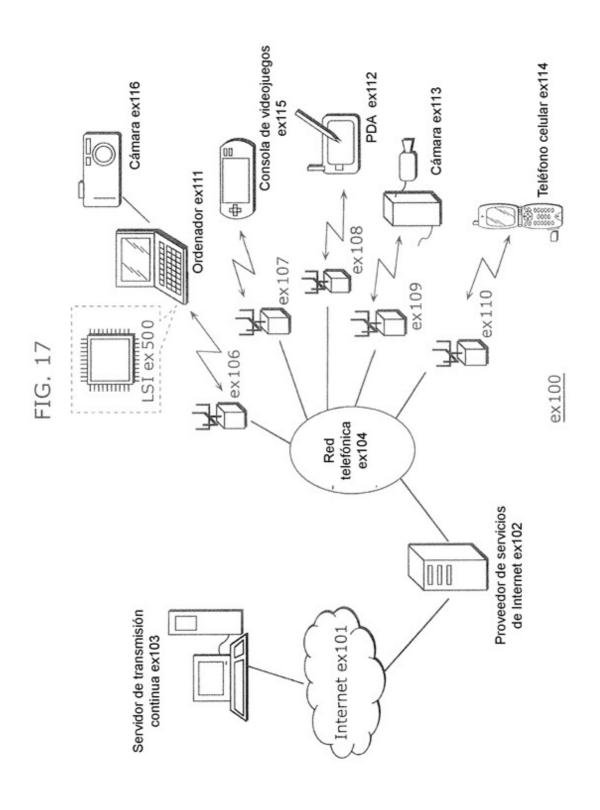

- [Fig. 17] La figura 17 muestra una configuración global de un sistema para proporcionar contenido para implementar servicios de distribución de contenido.

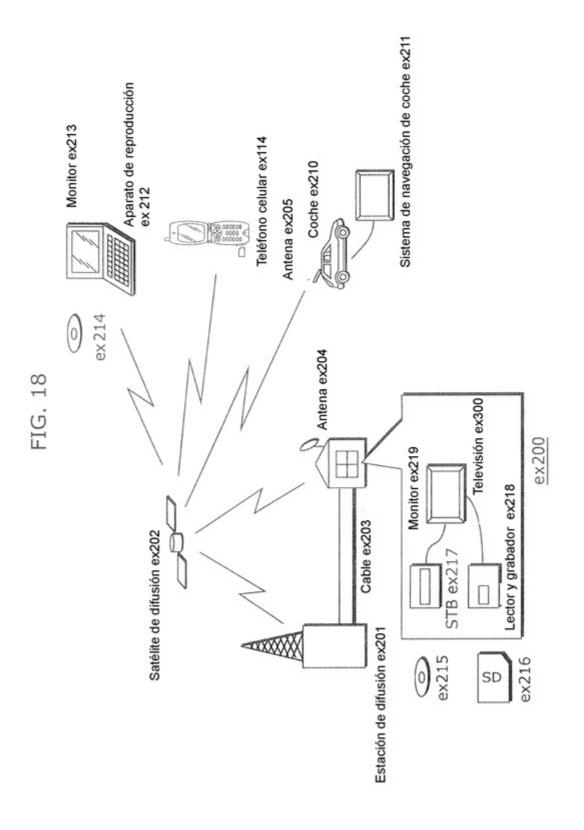

- 30 [Fig. 18] La figura 18 muestra una configuración global de un sistema de difusión digital.

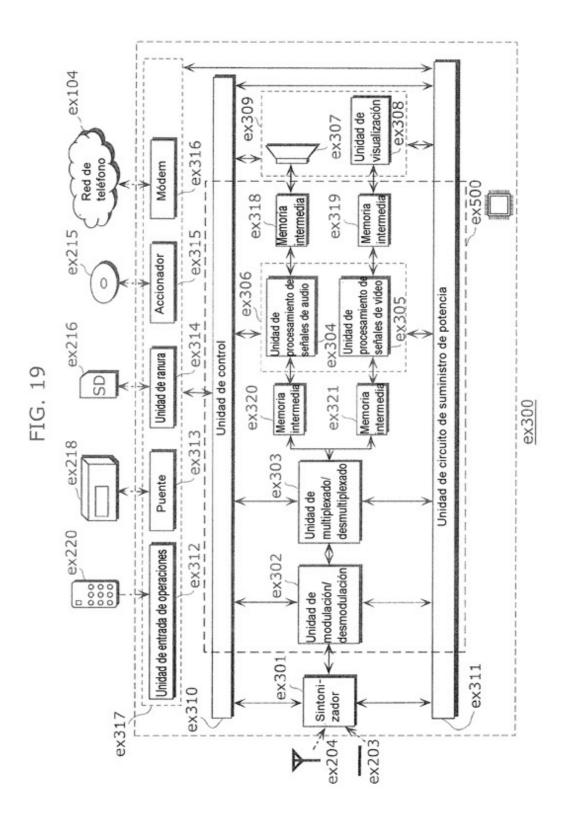

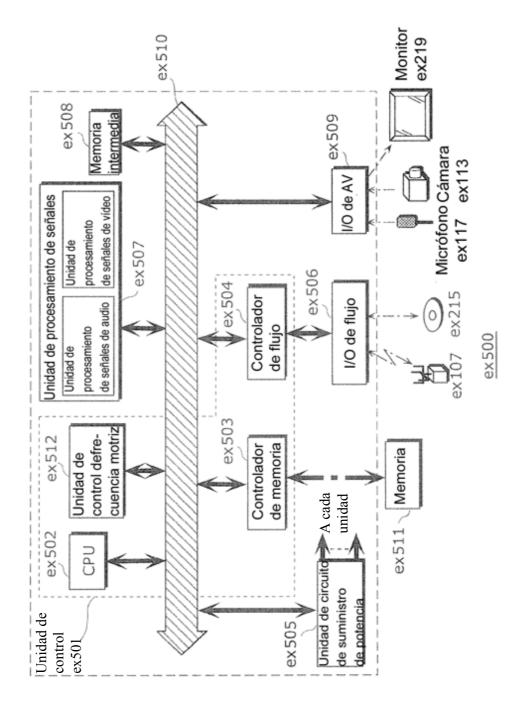

- [Fig. 19] La figura 19 muestra un diagrama de bloques que ilustra un ejemplo de una configuración de una televisión.

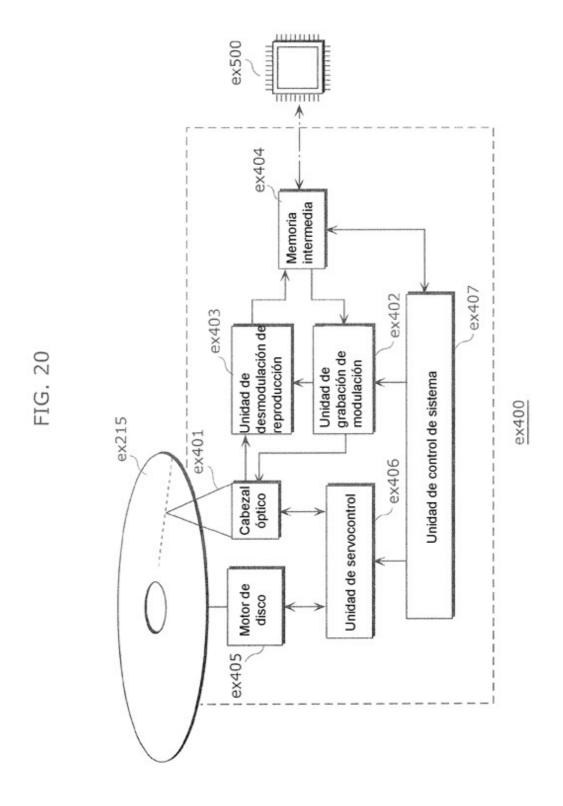

- [Fig. 20] La figura 20 muestra un diagrama de bloques que ilustra un ejemplo de una configuración de una unidad de reproducción/grabación de información que lee y escribe información de y en un medio de grabación que es un disco óptico.

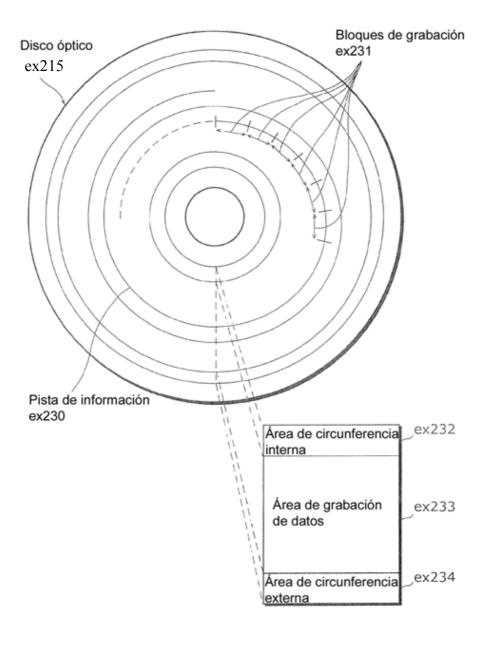

- 35 [Fig. 21] La figura 21 muestra un ejemplo de una configuración de un medio de grabación que es un disco óptico.

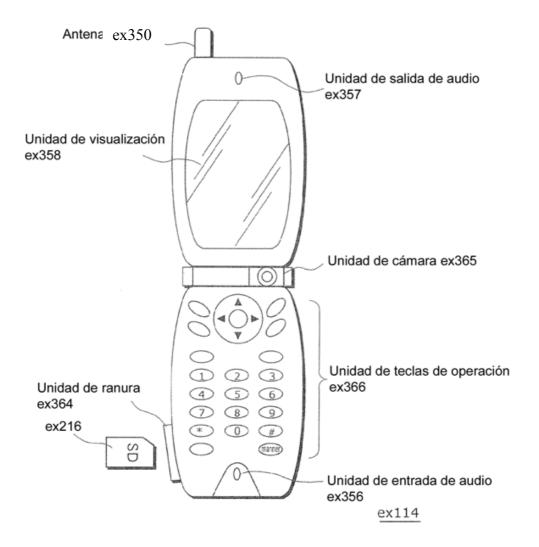

- [Fig. 22A] La figura 22A muestra un ejemplo de un teléfono celular.

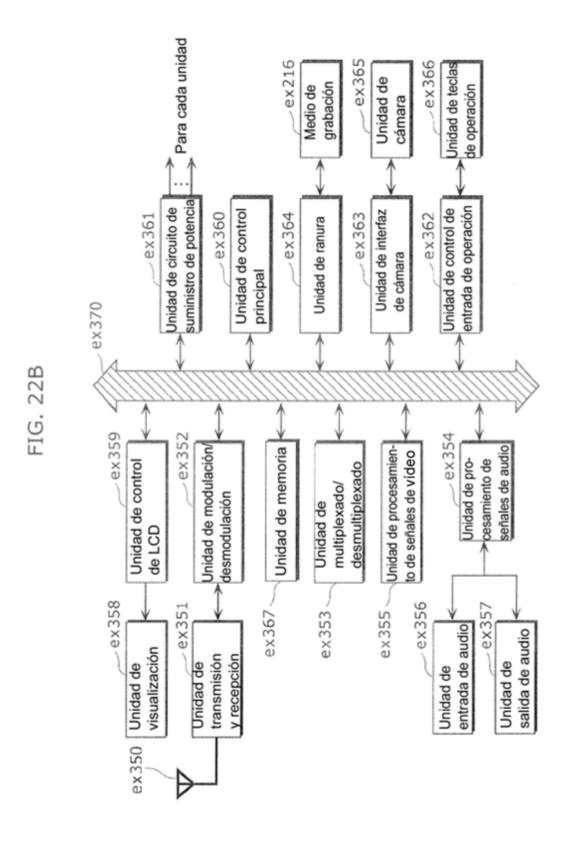

- [Fig. 22B] La figura 22B es un diagrama de bloques que muestra un ejemplo de una configuración de un teléfono celular.

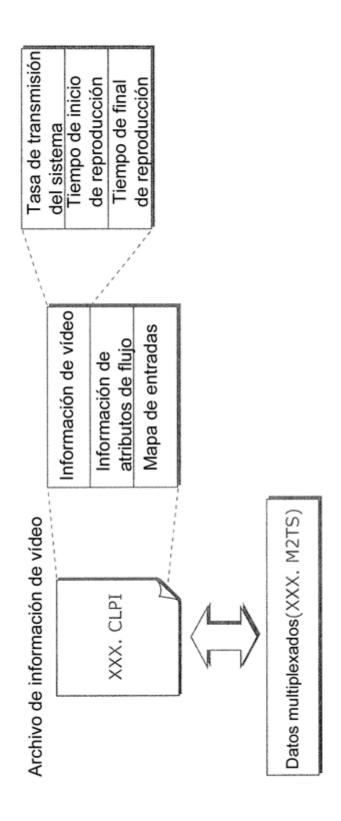

- [Fig. 23] La figura 23 ilustra una estructura de datos multiplexados.

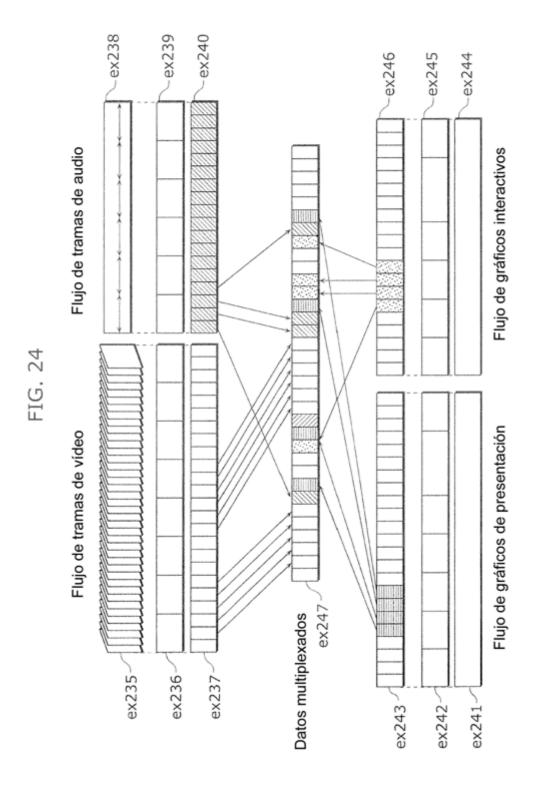

- 40 [Fig. 24] La figura 24 muestra esquemáticamente cómo se multiplexa cada flujo para dar datos multiplexados.

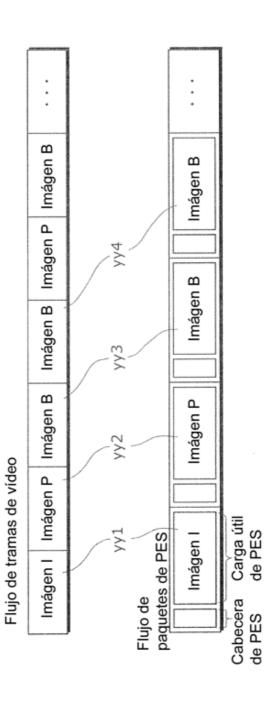

- [Fig. 25] La figura 25 muestra cómo se almacena un flujo de vídeo en un flujo de paquetes de PES en más detalle.

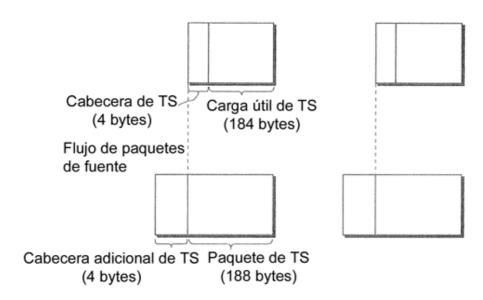

- [Fig. 26] La figura 26 muestra una estructura de paquetes de TS y paquetes de fuente en los datos multiplexados.

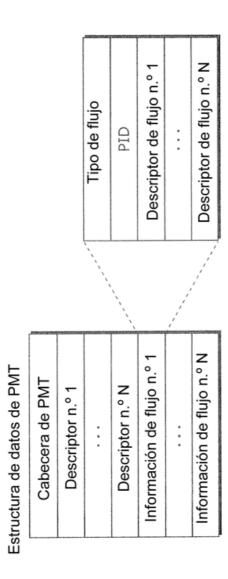

- [Fig. 27] La figura 27 muestra una estructura de datos de un PMT.

- [Fig. 28] La figura 28 muestra una estructura interna de información de datos multiplexados.

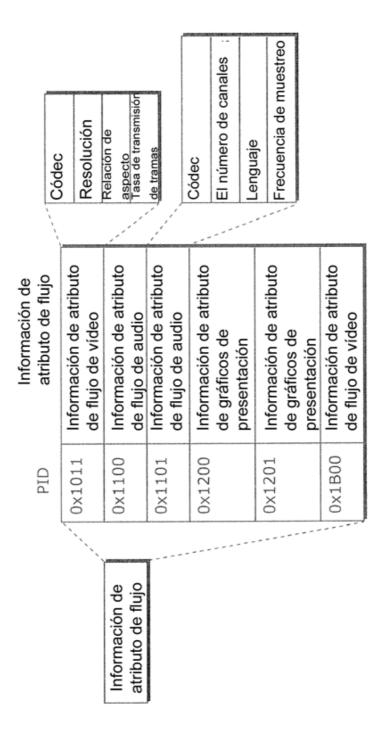

- [Fig. 29] La figura 29 muestra una estructura interna de información de atributos de flujo.

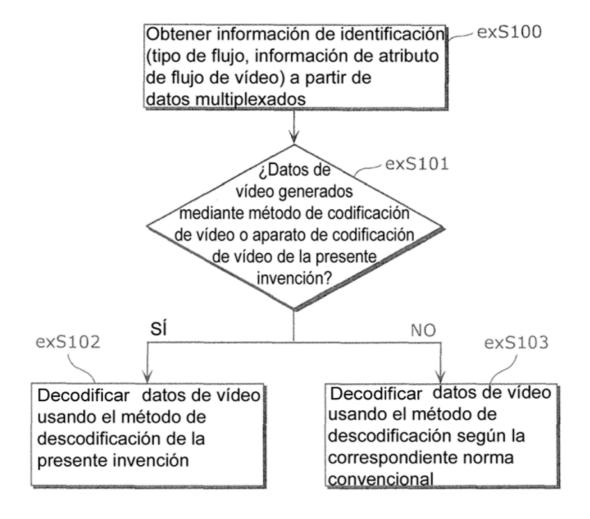

- [Fig. 30] La figura 30 muestra etapas para identificar datos de vídeo.

- [Fig. 31] La figura 31 muestra un ejemplo de una configuración de un circuito integrado para implementar el método de codificación de imágenes en movimiento y el método de decodificación de imágenes en movimiento según cada una de las realizaciones.

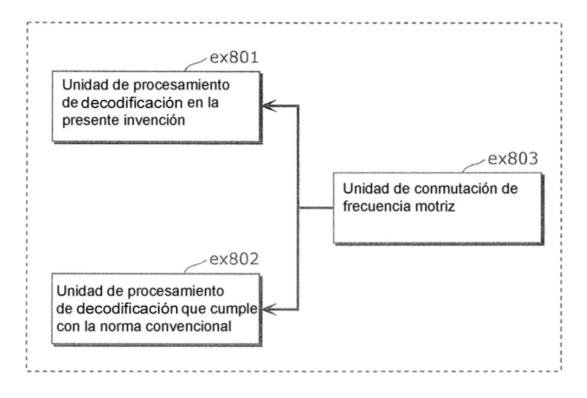

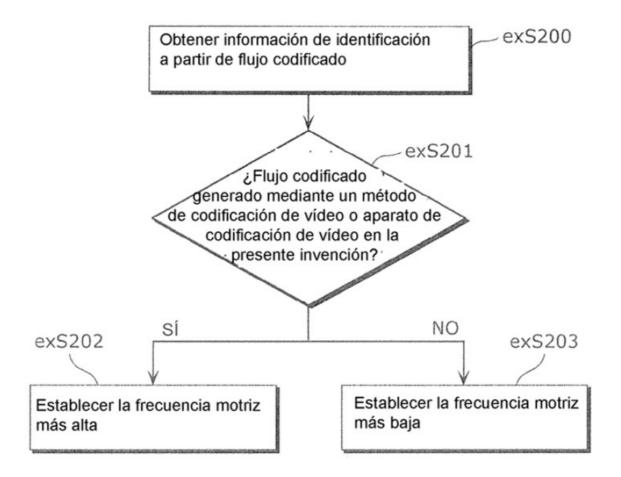

- [Fig. 32] La figura 32 muestra una configuración para conmutar entre frecuencias motrices.

- [Fig. 33] La figura 33 muestra etapas para identificar datos de vídeo y conmutar entre frecuencias motrices.

- [Fig. 34] La figura 34 muestra un ejemplo de una tabla de consulta en la que normas de datos de vídeo están asociadas con frecuencias motrices.

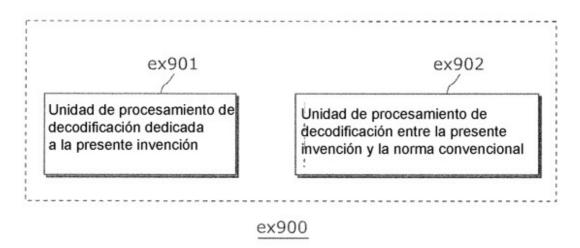

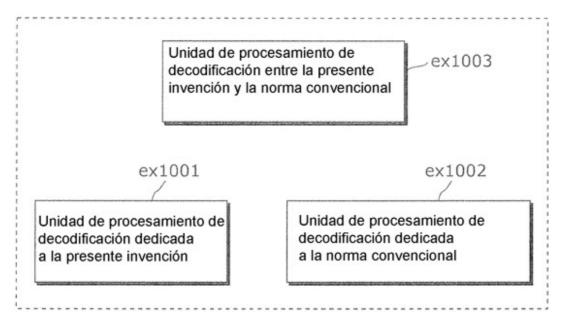

- 10 [Fig. 35A] La figura 35A es un diagrama que muestra un ejemplo de una configuración para compartir un módulo de una unidad de procesamiento de señales.

- [Fig. 35B] La figura 35B es un diagrama que muestra otro ejemplo de una configuración para compartir un módulo de la unidad de procesamiento de señales.

## Descripción de realizaciones

20

50

15 (Conocimiento subyacente que forma la base de la presente invención)

Los inventores han encontrado el siguiente contenido referente a la codificación aritmética y la decodificación aritmética de la información de última posición descrita en la sección de "antecedentes".

Debe observarse que en la siguiente descripción, la información de última posición indica una posición horizontal y una posición vertical del último coeficiente distinto de cero en un orden predeterminado en un bloque actual. En este caso, la información de última posición incluye una componente horizontal (denominada a continuación en el presente documento "componente X") y una componente vertical (denominada a continuación en el presente documento "componente Y"). La componente X indica una posición horizontal en el bloque actual. La componente Y indica una posición vertical en el bloque actual.

- La figura 1 es un diagrama de bloques que muestra un ejemplo de una configuración de un aparato de decodificación de imágenes 1000 según el conocimiento subyacente. La figura 2 es un diagrama de flujo que muestra un ejemplo de un método de decodificación de imágenes según el conocimiento subyacente. Tal como se muestra en la figura 1, el aparato de decodificación de imágenes 1000 incluye una primera unidad de decodificación 1001, una segunda unidad de decodificación 1002, una unidad de control de decodificación 1003, y una unidad de reconstrucción 1004.

- 30 El aparato de decodificación de imágenes 1000 obtiene un flujo de bits BS que incluye la información de última posición. Entonces, el aparato de decodificación de imágenes 1000 introduce el flujo de bits BS en la primera unidad de decodificación 1001, la segunda unidad de decodificación 1002 y la unidad de control de decodificación 1003.

- La unidad de control de decodificación 1003 gestiona si cada señal en el flujo de bits obtenido BS es la componente X o la componente Y de la información de última posición.

- La primera unidad de decodificación 1001 decodifica de manera aritmética una parte de prefijo de la componente X de la información de última posición incluida en el flujo de bits BS (S1001). Más específicamente, la primera unidad de decodificación 1001 decodifica de manera aritmética la parte de prefijo de la componente X mediante decodificación aritmética binaria adaptativa de contexto. En este caso, la parte de prefijo es una parte de la señal binaria de la componente X o la componente Y, que se codifica mediante codificación aritmética binaria adaptativa de contexto.

A continuación, la primera unidad de decodificación 1001 determina si la señal binaria de la componente X incluye una parte de sufijo o no (S1002). La parte de sufijo es una parte de la señal binaria de la componente X o la componente Y, que se codifica mediante codificación de derivación.

La parte de prefijo y la parte de sufijo se determinan según cada valor (también denominado a continuación en el presente documento "último valor") de la componente X y la componente Y tal como se muestra en la figura 3A a la figura 3D, por ejemplo. Por tanto, con un método predeterminado, la primera unidad de decodificación 1001 puede determinar si la señal binaria de la componente X incluye la parte de sufijo o no.

Más específicamente, cuando el tamaño de un bloque transformado (denominado a continuación en el presente documento "tamaño transformado") es de 4x4, por ejemplo, la señal binaria de la componente X incluye únicamente la parte de prefijo y no incluye la parte de sufijo independientemente del último valor tal como se muestra en la figura 3A. Por tanto, la primera unidad de decodificación 1001 determina que la señal binaria de la componente X no

incluye la parte de sufijo cuando el tamaño de un bloque que va a decodificarse es de 4x4.

5

20

25

45

50

55

En el caso en el que el tamaño transformado es de 8x8, por ejemplo, la primera unidad de decodificación 1001 determina que la señal binaria decodificada de la componente X no incluye la parte de sufijo cuando cualquiera de los valores de símbolo binario hasta el valor de símbolo binario del 4º bit de la señal binaria de la componente X es "1" tal como se muestra en la figura 3B. Por otro lado, la primera unidad de decodificación 1001 determina que la señal binaria decodificada de la componente X incluye una parte de sufijo que tiene una longitud fija de 2 bits cuando los valores de símbolo binario hasta el valor de símbolo binario del 4º bit de la señal binaria de la componente X son todos "0".

En el caso en el que el tamaño transformado es de 16x16, por ejemplo, la primera unidad de decodificación 1001 determina que la señal binaria decodificada de la componente X no incluye la parte de sufijo cuando cualquiera de los valores de símbolo binario hasta el valor de símbolo binario del 8º bit de la señal binaria de la componente X es "1" tal como se muestra en la figura 3C. Por otro lado, la primera unidad de decodificación 1001 determina que la señal binaria decodificada de la componente X incluye una parte de sufijo que tiene una longitud fija de 3 bits cuando los valores de símbolo binario hasta el valor de símbolo binario del 8º bit de la señal binaria de la componente X son todos "0".

En el caso en el que el tamaño transformado es de 32x32, por ejemplo, la primera unidad de decodificación 1001 determina que la señal binaria decodificada de la componente X no incluye la parte de sufijo cuando cualquiera de los valores de símbolo binario hasta el valor de símbolo binario del 16º bit de la señal binaria de la componente X es "1" tal como se muestra en la figura 3D. Por otro lado, la primera unidad de decodificación 1001 determina que la señal binaria decodificada de la componente X incluye una parte de sufijo que tiene una longitud fija de 4 bits cuando los valores de símbolo binario hasta el valor de símbolo binario del 16º bit de la señal binaria de la componente X son todos "0".

En este caso, cuando la señal binaria de la componente X incluye la parte de sufijo (Sí en S1002), la segunda unidad de decodificación 1002 decodifica de manera aritmética la parte de sufijo que tiene una longitud de bits fija, predeterminada (S1003). Más específicamente, la segunda unidad de decodificación 1002 decodifica la parte de sufijo de la componente X mediante decodificación de derivación. Por otro lado, cuando la señal binaria de la componente X no incluye la parte de sufijo (No en S1002), se omite el procedimiento de decodificación para la parte de sufijo.

La unidad de reconstrucción 1004 reconstruye la componente X de la información de última posición usando la parte de prefijo y la parte de sufijo que se han decodificado (S1004). Más específicamente, cuando la señal binaria de la componente X incluye la parte de sufijo, la unidad de reconstrucción 1004 reconstruye la componente X desbinarizando la señal binaria que incluye la parte de prefijo y parte de sufijo decodificadas. Por otro lado, cuando la señal binaria de la componente X no incluye la parte de sufijo, la unidad de reconstrucción 1004 reconstruye la componente X desbinarizando la señal binaria que incluye la parte de prefijo decodificada.

A continuación, la primera unidad de decodificación 1001 decodifica de manera aritmética la parte de prefijo de la componente Y de la información de última posición como en la etapa S1001 (S1005). Después de eso, la primera unidad de decodificación 1001 determina si la señal binaria de la componente Y incluye la parte de sufijo o no como en la etapa S1002 (S1006).

En este caso, cuando la señal binaria de la componente Y incluye la parte de sufijo (Sí en S1006), la segunda unidad de decodificación 1002 decodifica de manera aritmética la parte de sufijo que tiene una longitud fija predeterminada como en la etapa S1003 (S1007). Por otro lado, cuando la señal binaria de la componente Y no incluye la parte de sufijo (No en S1006), se omite el procedimiento de decodificación para la parte de sufijo.

Por último, la unidad de reconstrucción 1004 reconstruye la componente Y de la información de última posición como en la etapa S1004 (S1008). Más específicamente, cuando la señal binaria de la componente Y incluye la parte de sufijo, la unidad de reconstrucción 1004 reconstruye la componente Y desbinarizando la señal binaria que incluye la parte de prefijo y parte de sufijo decodificadas. Por otro lado, cuando la señal binaria de la componente Y no incluye la parte de sufijo, la unidad de reconstrucción 1004 reconstruye la componente Y desbinarizando la señal binaria que incluye la parte de prefijo decodificada.

Esta es la manera en la que se reconstruyen la componente X y la componente Y incluidas en la información de última posición.

A continuación, se describirá la codificación de longitud variable y la decodificación de longitud variable. H.264 emplea codificación aritmética binaria adaptativa de contexto (CABAC) como uno de los métodos de codificación de longitud variable. La parte de prefijo se codifica mediante CABAC. En cambio, la parte de sufijo se codifica mediante codificación de derivación, que es codificación aritmética en la que se usa una probabilidad fijada (por ejemplo, "0,5"). A continuación en el presente documento, se describirán la decodificación aritmética binaria adaptativa de contexto y la decodificación de derivación usando la figura 4 a la figura 6.

La figura 4 es un diagrama de flujo que muestra decodificación aritmética binaria adaptativa de contexto. Debe

observarse que la figura 4 se ha extraído del documento NPL 1. A menos que se especifique lo contrario, la descripción de la figura 4 es tal como se facilita en el documento NPL 1.

Con la decodificación aritmética, en primer lugar, se introduce contexto (ctxldx) que se determina basándose en el tipo de señal de una señal actual que va a decodificarse.

5 A continuación, se realiza el siguiente procedimiento en la etapa S2001.

En primer lugar, se calcula qCodIRangeldx a partir de un primer parámetro codIRange que indica un estado actual de decodificación aritmética. Además, se obtiene pStateldx que es un valor de estado correspondiente a ctxldx. Entonces, se obtiene codIRangeLPS correspondiente a los dos valores (qCodIRangeldx y pStateldx) mediante consulta de una tabla (rangeTableLPS).

Debe observarse que codlRangeLPS indica un estado de decodificación aritmética cuando se ha producido LPS en un estado de decodificación aritmética indicado por el primer parámetro codlRange. LPS especifica uno de los símbolos "0" y "1" que tiene una menor probabilidad de aparición.

Además, se establece un valor obtenido restando el codlRangeLPS anteriormente mencionado del codlRange actual para codlRange.

A continuación, en la etapa S2002, se realiza una comparación entre codlRange y un segundo parámetro codlOffset que indica un estado de decodificación aritmética.

En este caso, cuando codlOffset es mayor que o igual a codlRange (Sí en S2002), se realiza el siguiente procedimiento en la etapa S2003.

En primer lugar, se determina que se ha producido LPS, y se establece un valor diferente de valMPS ("0" cuando valMPS = 1, y "1" cuando valMPS = 0) para binVal que es un valor de salida de decodificación. valMPS indica un valor específico de MPS ("0" o "1"). MPS especifica uno de los valores de símbolo binario "0" y "1" que tiene una mayor probabilidad de aparición.

Además, se establece un valor obtenido restando codlRange del codlOffset actual para el segundo parámetro codlOffset que indica un estado de decodificación aritmética. Además, el valor de codlRangeLPS que se ha establecido en la etapa S2001 se establece para el primer parámetro codlRange que indica un estado de decodificación aritmética.

A continuación, en la etapa S2005, se determina si el valor de pStateldx es "0" o no.

25

30

35

40

50

En este caso, cuando el valor de pStateldx es "0" (Sí en S2005), significa que la probabilidad de LPS es mayor que la probabilidad de MPS. Por tanto, se conmuta el valor de valMPS (es decir, se establece "0" cuando valMPS = 1, y se establece "1" cuando valMPS = 0) (etapa S2006). Por otro lado, cuando el valor de pStateldx no es "0" (No en S2005), se actualiza el valor de pStateldx basándose en una tabla de transformada transldxLPS que se consulta cuando se produce cuando LPS (etapa S2007).

Además, cuando codlOffset es menor que codlRange (No en S2002), se determina que se ha producido MPS. Por tanto, se establece valMPS para binVal que es un valor de salida de decodificación, y se actualiza el valor de pStateldx basándose en una tabla de transformada transldxMPS que se consulta cuando se produce MPS (etapa S2004).

Por último, se realiza la normalización (RenormD) (etapa S2008) y la decodificación aritmética termina.

Tal como se mostró anteriormente, con la decodificación aritmética binaria adaptativa de contexto, múltiples probabilidades de aparición de símbolo, que son probabilidades de aparición de símbolos binarios, se mantienen en asociación con índices de contexto. Los contextos se conmutan según una condición (por ejemplo, valor de un bloque adyacente), y por tanto, es necesario mantener el orden de procesamiento.

La figura 5 es un diagrama de flujo que muestra la decodificación de derivación. Debe observarse que la figura 5 se ha extraído del documento NPL 1. A menos que se especifique lo contrario, la descripción de la figura 5 es tal como se facilita en el documento NPL 1.

En primer lugar, el segundo parámetro codlOffset que indica un estado actual de decodificación aritmética se desplaza a la izquierda (se duplica). Además, se lee un bit del flujo de bits, y cuando el bit leído es "1", se añade 1 a codlOffset (etapa S3001).

A continuación, cuando codlOffset es mayor que o igual al primer parámetro codlRange que indica un estado de decodificación aritmética (Sí en S3002), se establece "1" para binVal que es un valor de salida de decodificación, y se establece un valor obtenido restando codlRange del codlOffset actual para codlOffset (etapa S3003). Por otro lado, cuando codlOffset es menor que el primer parámetro codlRange que indica un estado de decodificación aritmética (No en S3002), se establece "0" para binVal que es un valor de salida de decodificación (etapa S3004).

La figura 6 es un diagrama de flujo para describir en detalle la normalización (RenormD) mostrada en la etapa S2008 en la figura 4. La figura 6 se ha extraído del documento NPL 1. A menos que se especifique lo contrario, la descripción de la figura 6 es tal como se facilita en el documento NPL 1.

Cuando el primer parámetro codlRange que indica un estado de decodificación aritmética se ha vuelto menor que 0x100 (en base 16: 256 (en base 10)) (Sí en S4001), codlRange se desplaza a la izquierda (se duplica). Además, el segundo parámetro codlOffset que indica un estado de decodificación aritmética se desplaza a la izquierda (se duplica). Además, se lee un bit del flujo de bits, y cuando el bit leído es "1", se añade 1 a codlOffset (etapa S4002).

Cuando codIRange alcanza finalmente 256 o más mediante este procedimiento en la etapa S4002 (No en S4001), la normalización termina.

10 Esta es la manera en la que se realiza la decodificación aritmética.

5

15

35

45

50

55

Sin embargo, una conmutación apropiada entre contextos (modelos de contexto) resulta difícil cuando se codifica o decodifica la parte de prefijo mediante codificación aritmética binaria adaptativa de contexto o decodificación aritmética binaria adaptativa de contexto. Por ejemplo, en codificación aritmética y decodificación aritmética de la parte de prefijo, los contextos se conmutan según la posición de bit en la señal binaria. En este momento, si un contexto es común para una pluralidad de posiciones de bits para reducir la capacidad requerida de la memoria y reducir el acceso una memoria, en algunos casos se usa un contexto idéntico para posiciones de bits que son significativamente diferentes en cuanto a la probabilidad de aparición de símbolo. En un caso de este tipo, la precisión de predicción de la probabilidad de aparición de símbolo disminuye, y por tanto la eficiencia de codificación también disminuye.

En vista de lo anterior, un método de codificación de imágenes según un aspecto de la presente invención es un 20 método de codificación de imágenes para codificar información de última posición que indica una posición de un último coeficiente distinto de cero en un orden predeterminado en un bloque actual que va a codificarse, incluyendo el método de codificación de imágenes: binarizar la información de última posición para generar (i) una señal binaria que incluye una primera señal que tiene una longitud menor que o igual a una longitud máxima predeterminada y no incluye una segunda señal o (ii) una señal binaria que incluye la primera señal que tiene la longitud máxima 25 predeterminada y la segunda señal; primera codificación para codificar de manera aritmética cada uno de los símbolos binarios incluidos en la primera señal usando un contexto conmutado entre una pluralidad de contextos según una posición de bit del símbolo binario; y segunda codificación para codificar de manera aritmética la segunda señal usando una probabilidad fijada cuando la señal binaria incluye la segunda señal, en el que en la primera 30 codificación, un símbolo binario en una última posición de bit de la primera señal se codifica de manera aritmética usando un contexto exclusivo para la última posición de bit, cuando la primera señal tiene la longitud máxima predeterminada.

El símbolo binario en la última posición de bit de la primera señal indica si la señal binaria incluye la segunda señal o no. Esto significa que el símbolo binario en la última posición de bit de la primera señal tiene una gran influencia sobre la eficiencia de codificación. Por tanto, el símbolo binario en la última posición de bit de la primera señal tiene una característica en la aparición de símbolo diferente de la de los símbolos binarios en las otras posiciones de bits. En vista de esto, es posible aumentar la eficiencia de codificación codificando de manera aritmética el símbolo binario en la última posición de bit de la primera señal usando el contexto exclusivo para la última posición de bit.

Por ejemplo, en la primera codificación, cada uno de los símbolos binarios en dos o más posiciones de bits distintas de la última posición de bit de la primera señal pueden codificarse de manera aritmética usando un contexto común a las dos o más posiciones de bits.

Con esto, cada uno de los símbolos binarios en dos o más posiciones de bits distintas de la última posición de bit de la primera señal pueden codificarse de manera aritmética usando un contexto común para las dos o más posiciones de bits. Esto reduce el número de contextos en comparación con el caso de usar un contexto diferente para cada posición de bit, y por tanto puede reducirse la capacidad requerida de la memoria.

Por ejemplo, la binarización puede incluir hacer variar la longitud máxima predeterminada según un tamaño del bloque actual.

Con esto, la longitud máxima de la primera señal puede hacerse variar según el tamaño del bloque actual que va a codificarse. Esto hace posible establecer de manera apropiada la longitud máxima de la primera señal, aumentando así la eficiencia de codificación.

Por ejemplo, el método de codificación de imágenes puede incluir además: conmutar un procedimiento de codificación a o bien un primer procedimiento de codificación que cumple con una primera norma o bien un segundo procedimiento de codificación que cumple con una segunda norma; y añadir, a un flujo de bits, información de identificación que indica o bien la primera norma o bien la segunda norma que cumple el procedimiento de codificación al que se conmuta, en el que cuando se conmuta el procedimiento de codificación, la binarización, la primera codificación y la segunda codificación pueden realizarse como el primer procedimiento de codificación.

Esto hace posible conmutar entre el primer procedimiento de codificación que cumple con la primera norma y el segundo procedimiento de codificación que cumple con la segunda norma.

Además, un método de decodificación de imágenes según un aspecto de la presente invención es un método de decodificación de imágenes para decodificar información de última posición que indica una posición de un último coeficiente distinto de cero en un orden predeterminado en un bloque actual que va a decodificarse, incluyendo el método de decodificación de imágenes: primera decodificación para decodificar de manera aritmética cada uno de los símbolos binarios incluidos en una primera señal usando un contexto conmutado entre una pluralidad de contextos según una posición de bit del símbolo binario, incluyéndose la primera señal en una señal binaria de la información de última posición y teniendo una longitud menor que o igual a una longitud máxima predeterminada; y segunda decodificación para, cuando la señal binaria de la información de última posición incluye una segunda señal, decodificar de manera aritmética la segunda señal usando una probabilidad fijada, en el que en la primera decodificación, un símbolo binario en una última posición de bit de la primera señal se decodifica de manera aritmética usando un contexto exclusivo para la última posición de bit, cuando la primera señal tiene la longitud máxima predeterminada.

El símbolo binario en la última posición de bit de la primera señal indica si la señal binaria incluye la segunda señal o no. Esto significa que el símbolo binario en la última posición de bit de la primera señal tiene una gran influencia sobre la eficiencia de codificación. Por tanto, el símbolo binario en la última posición de bit de la primera señal tiene una característica en la aparición de valor diferente de la de los símbolos binarios en las otras posiciones de bits. En vista de esto, es posible aumentar la eficiencia de codificación decodificando de manera aritmética el símbolo binario en la última posición de bit de la primera señal usando el contexto exclusivo para la última posición de bit.

Por ejemplo, en la primera decodificación, cada uno de los símbolos binarios en dos o más posiciones de bits distintas de la última posición de bit de la primera señal pueden decodificarse de manera aritmética usando un contexto común para las dos o más posiciones de bits.

Con esto, cada uno de los símbolos binarios en dos o más posiciones de bits distintas de la última posición de bit de la primera señal pueden decodificarse de manera aritmética usando un contexto común para las dos o más posiciones de bits. Esto reduce el número de contextos en comparación con el caso de usar un contexto diferente para cada posición de bit, y por tanto puede reducirse la capacidad requerida de la memoria.

Por ejemplo, la longitud máxima predeterminada puede variar según el tamaño del bloque actual.

Con esto, la longitud máxima de la primera señal puede hacerse variar según el tamaño del bloque actual que va a decodificarse. Esto hace posible establecer de manera apropiada la longitud máxima de la primera señal, aumentando así la eficiencia de codificación.

Por ejemplo, el método de decodificación de imágenes puede incluir además conmutar un procedimiento de decodificación a o bien un primer procedimiento de decodificación que cumple con una primera norma o bien un segundo procedimiento de decodificación que cumple con una segunda norma, según información de identificación que se añade a un flujo de bits e indica o bien la primera norma o bien la segunda norma, en el que cuando el procedimiento de decodificación se conmuta al primer procedimiento de decodificación, la primera decodificación y la segunda decodificación pueden realizarse como el primer procedimiento de decodificación.

Esto hace posible conmutar entre el primer procedimiento de decodificación que cumple con la primera norma y el segundo procedimiento de decodificación que cumple con la segunda norma.

Debe observarse que estos aspectos generales y específicos pueden implementarse usando un sistema, un aparato, un circuito integrado, un programa informático o un medio de grabación legible por ordenador tal como un CD-ROM, o cualquier combinación de sistemas, aparatos, circuitos integrados, programas informáticos o medios de grabación legibles por ordenador.

A continuación en el presente documento, se describirán realizaciones en detalle usando los dibujos.

Debe observarse que cada una de las realizaciones descritas a continuación muestra un ejemplo general o específico. Los valores numéricos, formas, materiales, elementos estructurales, la disposición y conexión de los elementos estructurales, etapas, el orden de procesamiento de las etapas, etc., mostrados en las siguientes realizaciones son simplemente ejemplos, y por tanto no se pretende que limiten el alcance de las reivindicaciones. Además, entre los elementos estructurales en las siguientes realizaciones, los elementos estructurales no mencionados en ninguna de las reivindicaciones independientes que representan los conceptos más genéricos se describen como elementos estructurales arbitrarios.

(Realización 1)

5

10

35

55

La figura 7 es un diagrama de bloques que muestra una configuración funcional de un aparato de decodificación de imágenes 100 según la realización 1. El aparato de decodificación de imágenes 100 decodifica la información de última posición.

Tal como se muestra en la figura 7, el aparato de decodificación de imágenes 100 incluye una unidad de decodificación aritmética 110 y una unidad de reconstrucción 104. La unidad de decodificación aritmética 110 incluye una primera unidad de decodificación 101, una segunda unidad de decodificación 102, y una unidad de control de decodificación 103.

5 El aparato de decodificación de imágenes 100 obtiene un flujo de bits BS que incluye la información de última posición codificada.

10

15

20

25

30

35

45

50

55

La primera unidad de decodificación 101 decodifica de manera aritmética cada símbolo binario incluido en una primera señal que se incluye en una señal binaria de la información de última posición, usando un contexto conmutado entre una pluralidad de contextos según la posición de bit del símbolo binario. En otras palabras, la primera unidad de decodificación 101 decodifica la primera señal mediante decodificación aritmética binaria adaptativa de contexto.

La primera señal es una parte de la señal binaria de la información de última posición, que se ha codificado de manera aritmética usando un contexto conmutado entre una pluralidad de contextos. La primera señal tiene una longitud menor que o igual a una longitud máxima predeterminada. La primera señal corresponde a la parte de prefijo, por ejemplo.

En este caso, cuando la primera señal tiene la longitud máxima predeterminada, la primera unidad de decodificación 101 decodifica de manera aritmética el símbolo binario en la última posición de bit de la primera señal usando un contexto exclusivo para la última posición de bit. En otras palabras, la primera unidad de decodificación 101 decodifica de manera aritmética el símbolo binario en la última posición de bit de la primera señal usando un contexto diferente de contextos usados para la decodificación aritmética de símbolos binarios en las otras posiciones de bits.

Por ejemplo, cuando va a decodificarse la parte de prefijo correspondiente al último valor "7" mostrado en la figura 3C, la primera unidad de decodificación 101 decodifica de manera aritmética el símbolo binario del 8° bit usando un contexto exclusivo para el símbolo binario del 8° bit. En otras palabras, la primera unidad de decodificación 101 decodifica de manera aritmética el símbolo binario del 8° bit usando, como contexto para la posición de bit del 8° bit, un contexto diferente de contextos para las posiciones de bits de los bits 1° a 7°.

Cuando la señal binaria de la información de última posición incluye una segunda señal, la segunda unidad de decodificación 102 decodifica de manera aritmética la segunda señal usando una probabilidad fijada. En otras palabras, la segunda unidad de decodificación 102 decodifica la segunda señal mediante decodificación de derivación.

La segunda señal es una parte de la señal binaria de la información de última posición, que se ha codificado de manera aritmética usando una probabilidad fijada. La segunda señal corresponde a la parte de sufijo, por ejemplo.

La unidad de control de decodificación 103 gestiona, para cada parte del flujo de bits BS, si la parte es la componente X o la componente Y de la información de última posición. Debe observarse que no se necesita incluir la unidad de control de decodificación 103 en la unidad de decodificación aritmética 110. Es decir, no se necesita que el aparato de decodificación de imágenes 100 incluya la unidad de control de decodificación 103.

La unidad de reconstrucción 104 reconstruye la componente horizontal o la componente vertical incluida en la información de última posición desbinarizando (i) la señal binaria que incluye la primera señal y no incluye la segunda señal o (ii) la señal binaria que incluye la primera señal y la segunda señal.

40 A continuación, usando la figura 8A y la figura 8B, lo siguiente describe en detalle operaciones del aparato de decodificación de imágenes 100 que tiene la configuración anterior. A continuación en el presente documento se describe el caso en el que la primera señal es la parte de prefijo y la segunda señal es la parte de sufijo.

La figura 8A es un diagrama de flujo que muestra un ejemplo de operaciones de procesamiento del aparato de decodificación de imágenes 100 según la realización 1. En cuanto a la figura 8A, la parte de prefijo de la componente X, la parte de sufijo de la componente Y, y la parte de sufijo de la componente Y se codifican y colocan en el flujo de bits BS en este orden. Debe observarse que en algunos casos la parte de sufijo de cada componente no se incluye en el flujo de bits BS dependiendo del valor de la componente.

En primer lugar, la primera unidad de decodificación 101 decodifica, a partir del flujo de bits BS, la parte de prefijo codificada de la componente X mediante decodificación aritmética binaria adaptativa de contexto (S101). Por ejemplo, la primera unidad de decodificación 101 decodifica de manera aritmética la parte de prefijo codificada para un bit cada vez hasta que se alcanza una longitud máxima predeterminada o hasta que se decodifica "1". Debe observarse que la conmutación de contexto se describirá más adelante.

A continuación, la primera unidad de decodificación 101 determina si la señal binaria de la componente X incluye la parte de sufijo o no (S102). Por ejemplo, la primera unidad de decodificación 101 determina que la señal binaria de la componente X incluye la parte de sufijo cuando la parte de prefijo tiene la longitud máxima predeterminada y los

valores de símbolo binario incluidos en la parte de prefijo son todos "0".

15

Debe observarse que la longitud máxima de la parte de prefijo se predetermina según el tamaño transformado, por ejemplo. Por ejemplo, la longitud máxima de la parte de prefijo se determina de la manera mostrada en la figura 9B o la figura 9C.

- En este caso, cuando la señal binaria de la componente X incluye la parte de sufijo (Sí en S102), la segunda unidad de decodificación 102 decodifica la parte de sufijo codificada de la componente X mediante decodificación de derivación (S103). Por otro lado, cuando la señal binaria de la componente X no incluye la parte de sufijo (No en S102), se omite la etapa S103.

- A continuación, la unidad de reconstrucción 104 reconstruye la componente X de la información de última posición desbinarizando la señal binaria de la componente X que incluye tanto la parte de prefijo como la parte de sufijo o que incluye únicamente la parte de prefijo (S104).

- Después de eso, la primera unidad de decodificación 101 decodifica, a partir del flujo de bits BS, la parte de prefijo codificada de la componente Y mediante la decodificación aritmética binaria adaptativa de contexto (S105). Más específicamente, la primera unidad de decodificación 101 decodifica la parte de prefijo de la componente Y de la misma manera que la decodificación de la parte de prefijo de la componente X.

- Entonces, la primera unidad de decodificación 101 determina si la señal binaria de la componente Y incluye la parte de sufijo o no (S106). Más específicamente, la primera unidad de decodificación 101 determina si la señal binaria de la componente Y incluye la parte de sufijo o no de la misma manera que la determinación en cuanto a si la señal binaria de la componente X incluye la parte de sufijo o no.

- 20 En este caso, cuando la señal binaria de la componente Y incluye la parte de sufijo (Sí en S106), la segunda unidad de decodificación 102 decodifica la parte de sufijo codificada de la componente Y mediante decodificación de derivación (S107). Por otro lado, cuando la señal binaria de la componente Y no incluye la parte de sufijo (No en S106), se omite la etapa S107.

- Por último, la unidad de reconstrucción 104 reconstruye la componente Y de la información de última posición desbinarizando la señal binaria de la componente Y que incluye tanto la parte de prefijo como la parte de sufijo o que incluye únicamente la parte de prefijo (S108).

- A continuación, lo siguiente describe el caso en el que la parte de prefijo y la parte de sufijo de cada componente se colocan en el flujo de bits en un orden diferente del de la figura 8A.

- La figura 8B es un diagrama de flujo que muestra otro ejemplo de operaciones de procesamiento del aparato de decodificación de imágenes 100 según la realización 1. Debe observarse que en la figura 8B, los procedimientos realizados en las etapas indicadas mediante los mismos signos de referencia que los de la figura 8A son básicamente los mismos que los procedimientos descritos en la figura 8A. Además, en este caso, se supone que un indicador de sufijo se establece a "OFF" (desactivado) como valor por defecto. Debe observarse que el indicador de sufijo es un indicador interno que indica si la señal binaria de la componente X de la información de última posición incluye la parte de sufijo o no.

- En cuanto a la figura 8B, la parte de prefijo de la componente X, la parte de prefijo de la componente Y, la parte de sufijo de la componente Y, y la parte de sufijo de la componente X se codifican y colocan en el flujo de bits BS en este orden. Debe observarse que en algunos casos la parte de sufijo de cada componente no se incluye en el flujo de bits BS dependiendo del valor de la componente, como en el caso de la figura 8A.

- 40 En primer lugar, la primera unidad de decodificación 101 decodifica la parte de prefijo codificada de la componente X mediante decodificación aritmética binaria adaptativa de contexto (S101). Entonces, la primera unidad de decodificación 101 determina si la señal binaria de la componente X incluye la parte de sufijo o no (S102). En este caso, cuando la señal binaria de la componente X incluye la parte de sufijo (Sí en S102), la primera unidad de decodificación 101 establece el indicador de sufijo a "ON" (activado) (S111).

- Por otro lado, cuando la señal binaria de la componente X no incluye la parte de sufijo (No en S102), la primera unidad de decodificación 101 no establece el indicador de sufijo a "ON". En otras palabras, el indicador de sufijo permanece en "OFF", que es el valor por defecto. Debe observarse que la primera unidad de decodificación 101 puede establecer el indicador de sufijo a "OFF" en este caso.

- A continuación, desde la etapa S105 hasta la etapa S108, se realiza un procedimiento relacionado con la componente Y de la misma manera que en la figura 8A.

- Después de eso, la segunda unidad de decodificación 102 determina si el indicador de sufijo se establece a "ON" o no (S112). En este caso, cuando el indicador de sufijo se establece a "ON" (Sí en S112), la segunda unidad de decodificación 102 decodifica la parte de sufijo de la componente X mediante decodificación de derivación (S103). Por otro lado, cuando el indicador de sufijo no se establece "ON" (No en S112), se omite la etapa S103.

Por último, la unidad de reconstrucción 104 reconstruye la componente X de la información de última posición desbinarizando la señal binaria de la componente X que incluye tanto la parte de prefijo como la parte de sufijo o que incluye únicamente la parte de prefijo (S104).

Decodificando consecutivamente las partes de prefijo de la componente X y la componente Y, y decodificando consecutivamente las partes de sufijo de la componente X y la componente Y de esta manera, se hace posible reducir el número de veces que se conmutan los métodos de decodificación aritmética (decodificación aritmética binaria adaptativa de contexto y decodificación de derivación). Esto permite que la unidad de decodificación aritmética 110 decodifique de manera aritmética la información de última posición codificada de manera eficiente.

5

10

15

20

25

30

40

50

Además, decodificando consecutivamente las partes de sufijo de la componente X y la componente Y se hace más fácil realizar la decodificación de derivación en paralelo, aumentando así la velocidad de procesamiento.

Además, decodificando consecutivamente la parte de prefijo y la parte de sufijo de y la componente Y se elimina la necesidad de establecer el indicador de sufijo para la componente Y. En otras palabras, puede reducirse la capacidad requerida de la memoria en comparación con el caso de decodificar la parte de prefijo de la componente X, la parte de prefijo de la componente Y, la parte de sufijo de la componente Y en este orden.

A continuación, lo siguiente describe un ejemplo del procedimiento de decodificación en las partes de sufijo codificadas de la componente X y la componente Y (S108 y S111). En el presente documento se describe el caso en el que las partes de sufijo se binarizan mediante codificación de Golomb-Rice.

Con la codificación de Golomb-Rice, no se fija la longitud de cada parte de sufijo. La parte de sufijo puede dividirse en dos partes, la primera mitad y la segunda mitad.

La segunda mitad es una parte de longitud fija que tiene una longitud indicada por un parámetro de Rice (denominado a continuación en el presente documento "RP").

Debe observarse que en este caso se conoce la cantidad de información que va a representarse mediante la parte de sufijo, y por tanto es posible omitir el último "0" de la primera mitad cuando la primera mitad tiene la longitud máxima. Por ejemplo, cuando RP es "2" y la cantidad máxima de información es "12", la primera mitad puede representarse mediante uno cualquiera de 0, 0, 0, 0, 10, 10, 10, 10, 11, 11, 11 y 11. Al omitir el último "0" de la primera mitad de esta manera, la cantidad de codificación de la señal binaria puede reducirse en 1 bit.

La cantidad máxima de información puede representarse mediante la diferencia entre la longitud en el tamaño transformado y la longitud de la parte de prefijo. Esto reduce el/los bit(s) redundante(s).

Es suficiente siempre que RP se predetermine según el tamaño transformado tal como se muestra en la figura 9D o la figura 9E, por ejemplo. Esto hace posible representar la parte de sufijo con una señal binaria que tiene una longitud adaptada al tamaño transformado, y por tanto, puede aumentarse la eficiencia de codificación.

Lo siguiente describe, usando la figura 9A, operaciones de la segunda unidad de decodificación 102 para decodificar la parte de sufijo binarizada mediante codificación de Golomb-Rice tal como se describió anteriormente. La figura 9A es un diagrama de flujo que muestra un ejemplo de operaciones de procesamiento de la segunda unidad de decodificación 102 según la realización 1.

En primer lugar, la segunda unidad de decodificación 102 establece un valor de RP (S201). Más específicamente, la segunda unidad de decodificación 102 consulta una tabla predeterminada, por ejemplo, para establecer el valor de RP. La tabla predeterminada en este caso es una tabla mostrada en la figura 9D o la figura 9E, por ejemplo.

Debe observarse que la segunda unidad de decodificación 102 puede establecer el valor de RP sin consultar la tabla. El establecimiento del valor de RP se describirá más adelante en detalle usando la figura 10A a la figura 10D.

A continuación, la segunda unidad de decodificación 102 establece un valor máx. (S202). En este caso, el valor máx indica el valor máximo de la longitud de la primera mitad del código de Golomb-Rice. Más específicamente, el valor máx. indica la longitud más corta de la señal binaria que puede representar un valor obtenido restando la longitud máxima de la parte de prefijo del valor máximo del último valor. Por tanto, la segunda unidad de decodificación 102 deriva el valor máx. (i) restando la longitud de la parte de prefijo del valor máximo del último valor y (ii) dividiendo el valor resultante entre 2 a la potencia RP o realizando una operación de desplazamiento a la derecha con el valor resultante en RP bit(s).

Debe observarse que la longitud máxima de la parte de prefijo puede hacerse variar según el tamaño transformado

tal como se muestra en la figura 9B o la figura 9C.

10

15

40

45

50

A continuación, la segunda unidad de decodificación 102 decodifica, a partir del flujo de bits BS, una señal correspondiente a 1 bit del código de Golomb-Rice mediante decodificación de derivación, e incrementa el valor de recuento (por defecto es "0") en 1 (S203).

5 En este caso, cuando la señal decodificada correspondiente a 1 bit es "0" (Sí en S204), la decodificación de la primera mitad del código de Golomb-Rice termina, y el procedimiento avanza a la etapa S206.

Por otro lado, cuando la señal decodificada no es "0" (cuando la señal decodificada es "1") (No en S204), se determina si el valor de recuento es igual al valor máx. o no (S205). En este caso, cuando el valor de recuento no es igual al valor máx. (No en S205), el procedimiento vuelve a la etapa S203. Más específicamente, la segunda unidad de decodificación 102 decodifica una señal correspondiente al siguiente 1 bit del código de Golomb-Rice mediante decodificación de derivación.

Por otro lado, cuando el valor de recuento es igual al valor máx. (Sí en S205), la decodificación de la primera mitad de la parte de sufijo termina, y el procedimiento avanza a la etapa S206.

A continuación, la segunda unidad de decodificación 102 decodifica la segunda mitad del código de Golomb-Rice (una señal binaria que tiene una longitud fija de RP bit(s)) mediante decodificación de derivación (S206).

Por último, la segunda unidad de decodificación 102 reconstruye el valor representado mediante codificación de Golomb-Rice (S207). En este caso, el valor se reconstruye sumando la segunda mitad del código de Golomb-Rice y un valor obtenido mediante desplazamiento, a la izquierda en los RP bit(s), de un valor obtenido restando 1 del valor representado por la primera mitad del código de Golomb-Rice.

Debe observarse que en algunos casos el valor de la señal binaria de la segunda mitad se binariza en forma de un valor invertido. En tales casos, la segunda unidad de decodificación 102 realiza la reconstrucción teniendo en cuenta esta inversa. Debe observarse que es suficiente siempre que el aparato de decodificación y el aparato de codificación determinen por adelantado si el valor de la señal binaria debe invertirse o no. Ni la eficiencia de codificación ni la carga de procesamiento se ven afectados independientemente de si el valor de la señal binaria se invierte o no.

A continuación, lo siguiente describe, usando la figura 10A a la figura 10D, un método de determinación del valor de RP y la longitud máxima de la parte de prefijo.

La figura 10A muestra un método de determinación del valor de RP y la longitud máxima de la parte de prefijo según el tamaño transformado.

En primer lugar, la segunda unidad de decodificación 102 obtiene el tamaño transformado (S301). Entonces, la segunda unidad de decodificación 102 consulta una tabla tal como se muestra en la figura 9D o la figura 9E que indica una relación entre el tamaño transformado y el valor de RP, para determinar el valor de RP asociado con el tamaño transformado obtenido (S302). Además, la segunda unidad de decodificación 102 consulta una tabla tal como se muestra en la figura 9B o la figura 9C que indica una relación entre el tamaño transformado y la longitud máxima de la parte de prefijo, para determinar la longitud máxima de la parte de prefijo (S303).

La figura 10B muestra un método de determinación del valor de RP y la longitud máxima de la parte de prefijo según información de predicción.

En primer lugar, la segunda unidad de decodificación 102 obtiene información de predicción (S311). La información de predicción es información relacionada con la predicción de un bloque transformado que es un bloque actual que va a decodificarse. Por ejemplo, la información de predicción indica si el bloque transformado tiene que decodificarse mediante intra-predicción o inter-predicción. Además, por ejemplo, la información de predicción puede ser información que indica una dirección de predicción en intra-predicción.

A continuación, la segunda unidad de decodificación 102 determina el valor de RP basándose en la información de predicción (S312). Por ejemplo, se sabe que en el caso de inter-predicción, generalmente hay menos componentes de alta frecuencia que en la intra-predicción. Por tanto, cuando la información de predicción indica inter-predicción, es suficiente siempre que la segunda unidad de decodificación 102 determine un valor de RP de este tipo que permite que la componente X y la componente Y que tienen valores pequeños se representen mediante señales binarias cortas. Más específicamente, cuando la información de predicción indica inter-predicción, es suficiente siempre que la segunda unidad de decodificación 102 determine un valor de RP menor que un valor de RP determinado cuando la información de predicción indica intra-predicción.

Además, cuando la dirección de intra-predicción es la dirección horizontal, generalmente se espera que la componente Y de la información de última posición sea menor que la componente X. En vista de esto, cuando la dirección de predicción de intra-predicción es la dirección horizontal, es suficiente siempre que la segunda unidad de decodificación 102 determine, como valor de RP de la componente Y, un valor de RP menor que el valor de RP de la

componente X. Debe observarse que cuando la dirección de predicción de intra-predicción es la dirección vertical, es suficiente siempre que la segunda unidad de decodificación 102 determine, como valor de RP de la componente X, un valor de RP menor que el valor de RP de la componente Y.

Por último, la segunda unidad de decodificación 102 determina la longitud máxima de la parte de prefijo basándose en la información de predicción (S313).

5

15

25

30

40

45

Tal como se describió anteriormente, la segunda unidad de decodificación 102 puede variar la longitud de código de la señal binaria según la información de predicción, y por tanto, puede aumentarse la eficiencia de codificación.

La figura 10C muestra un método de determinación del valor de RP y la longitud máxima de la parte de prefijo según información estadística.

En primer lugar, la segunda unidad de decodificación 102 obtiene información estadística (S321). La información estadística es, por ejemplo, información sobre datos estadísticos de la longitud de la señal binaria de la componente X o la componente Y incluidos en la información de última posición de un bloque anteriormente decodificado.

A continuación, la segunda unidad de decodificación 102 determina el valor de RP basándose en la información estadística (S322). Por último, la segunda unidad de decodificación 102 determina la longitud máxima de la parte de prefijo basándose en la información estadística (S323).

Tal como se describió anteriormente, la segunda unidad de decodificación 102 puede hacer variar la longitud de código de la señal binaria según la información estadística, y por tanto, la eficiencia de codificación puede aumentarse adicionalmente.

La figura 10D muestra un método de determinación del valor de RP y la longitud máxima de la parte de prefijo según una componente anteriormente decodificada de la componente X y la componente Y.

En primer lugar, la segunda unidad de decodificación 102 obtiene una componente anteriormente decodificada de la componente X y la componente Y (S331). Por ejemplo, la segunda unidad de decodificación 102 obtiene una componente X anteriormente decodificada cuando se decodifica una componente Y codificada. Además, por ejemplo, la segunda unidad de decodificación 102 puede obtener una componente Y anteriormente decodificada cuando se decodifica una componente X codificada.

Entonces, la segunda unidad de decodificación 102 determina, usando la anteriormente decodificada componente de la componente X y la componente Y, el valor de RP de la otra, aún por decodificar, de la componente X y la componente Y (S332). Generalmente, es probable que la componente X y la componente Y tengan valores iguales o similares. Por tanto, cuando el valor de una componente X anteriormente decodificada es menor que un determinado valor (por ejemplo, la mitad del tamaño transformado), por ejemplo, la segunda unidad de decodificación 102 determina, como valor de RP de la componente Y, un valor menor que el valor de RP de la componente X.

Por último, la segunda unidad de decodificación 102 determina, usando la componente anteriormente decodificada de la componente X y la componente Y, la longitud máxima de la parte de prefijo de la otra, aún por decodificar, de la componente X y la componente Y (S333).

Tal como se describió anteriormente, la segunda unidad de decodificación 102 puede hacer variar la longitud de código de la señal binaria según una componente anteriormente decodificada de la componente X y la componente Y, y por tanto, puede aumentarse adicionalmente la eficiencia de codificación.

Debe observarse que los métodos de determinación del valor de RP y la longitud máxima de la parte de prefijo mostrados en la figura 10A a la figura 10D pueden usarse en combinación. Por ejemplo, cuando no hay ninguna información que consultar, la segunda unidad de decodificación 102 puede determinar el valor de RP basándose en una tabla predeterminada, mientras que cuando hay información que consultar, la segunda unidad de decodificación 102 puede determinar el valor de RP según la información que puede consultarse.

Además, la segunda unidad de decodificación 102 puede determinar la longitud máxima de la parte de prefijo de la misma manera que el valor de RP. Debe observarse que cuando se predice que los valores de la componente X y la componente Y son grandes, es suficiente siempre que la segunda unidad de decodificación 102 determine que la longitud máxima de la parte de prefijo es más corta que cuando se predice que la componente X y la componente Y son pequeñas. Reducir la longitud de prefijo de esta manera reduce el número de contextos necesarios.

A continuación, lo siguiente describe los contextos usados para decodificar la información de última posición mediante decodificación aritmética binaria adaptativa de contexto.

La figura 11A es un diagrama que muestra un ejemplo de una relación entre posiciones de bits y contextos según la realización 1. La figura 11B es un diagrama que muestra un ejemplo de una relación entre posiciones de bits y contextos según un ejemplo comparable.

La figura 11A y la figura 11B muestran una relación entre posiciones de bits y contextos para cuatro tipos de tamaño

transformado (4x4, 8x8, 16x16 y 32x32). En la figura 11A y la figura 11B, los bloques rectangulares dispuestos en la dirección horizontal corresponden a las posiciones de bits del 1<sup>er</sup> bit, el 2º bit, el 3<sup>er</sup> bit, etc., en secuencia desde la izquierda. Además, el valor numérico en cada bloque es un valor de índice del contexto usado para derivar una probabilidad que va a usarse en la decodificación del símbolo binario en esa posición de bit.

En la figura 11A hay 16 tipos (de 0 a 15) de contextos usados en la decodificación de la parte de prefijo. Además, en la figura 11A, la longitud máxima de la parte de prefijo es "3", "4", "4" y "8" para el tamaño transformado de 4x4, 8x8, 16x16 y 32x32, respectivamente.

10

20

25

30

35

40

45

50

55

En cuanto a la figura 11A, cuando el tamaño transformado es de 8x8, por ejemplo, se usa un valor de probabilidad derivado del contexto identificado mediante un valor de índice de "3" como valor de probabilidad para decodificar el símbolo binario del 1<sup>er</sup> bit de la parte de prefijo. De manera similar, se usa un valor de probabilidad derivado del contexto identificado mediante un valor de índice de "4" como valor de probabilidad para decodificar los símbolos binarios del 2º bit y el 3<sup>er</sup> bit. De manera similar, se usa un valor de probabilidad derivado del contexto identificado mediante un valor de índice de "5" como valor de probabilidad para decodificar el símbolo binario del 4º bit.

De tal manera, en cuanto a la figura 11A, el símbolo binario en la última posición de bit de la parte de prefijo se decodifica de manera aritmética usando un contexto exclusivo para la última posición de bit. En otras palabras, el contexto para la última posición de bit es un contexto diferente de los contextos para las otras posiciones de bits.

El símbolo binario en la última posición de bit de la parte de prefijo indica si la señal binaria de la componente X o la componente Y incluye la parte de sufijo o no. Esto significa que el símbolo binario en la última posición de bit de la parte de prefijo tiene una gran influencia sobre la eficiencia de codificación. Por tanto, el símbolo binario en la última posición de bit de la parte de prefijo tiene una característica en la aparición de símbolo diferente de la de los símbolos binarios en las otras posiciones de bits. En vista de esto, la eficiencia de codificación puede aumentarse decodificando el símbolo binario en la última posición de bit de la parte de prefijo usando el contexto exclusivo para la última posición de bit.

Además, un contexto puede ser común para una pluralidad de posiciones de bits, tales como las posiciones de bits del 2º bit y el 3<sup>er</sup> bit para el tamaño transformado de 8x8 o las posiciones de bits del 5º bit al 7º bit para el tamaño transformado de 32x32 en la figura 11A. En otras palabras, cada uno de los símbolos binarios en dos o más posiciones de bits distintas de la última posición de bit de la parte de prefijo pueden decodificarse de manera aritmética usando un contexto común para las dos o más posiciones de bits.

Esto reduce el número de contextos en comparación con el caso de usar un contexto diferente para cada posición de bit, y por tanto puede reducirse la capacidad requerida de la memoria.

Debe observarse que, aunque en la figura 11A el símbolo binario en la última posición de bit de la parte de prefijo se decodifica usando el contexto exclusivo para la última posición de bit para todos los tamaños transformados predeterminados, no se necesita que el símbolo binario en la última posición de bit se decodifique necesariamente de esta manera para todos los tamaños transformados. En otras palabras, un contexto puede ser común para la última posición de bit y otra posición de bit de la parte de prefijo para algunos de los tamaños transformados.

Por ejemplo, cuando la parte de sufijo tiene una longitud fija de 1 bit, un contexto puede ser común para la última posición de bit de la parte de prefijo y una posición de bit que precede inmediatamente a la última posición de bit.

Esto permite la estimación estable de la probabilidad incluso cuando el flujo de bits incluye pocas partes de prefijo que tienen la longitud máxima predeterminada, por ejemplo. Por ejemplo, la eficiencia de codificación puede aumentarse en el caso en el que la última posición se cambie de manera dinámica con la longitud de código tenida en cuenta en el momento de la codificación.

Tal como se ha descrito hasta ahora, el aparato de decodificación de imágenes 100 según la presente realización puede decodificar de manera aritmética el símbolo binario en la última posición de bit de la primera señal usando el contexto exclusivo para la última posición de bit. Es decir, el aparato de decodificación de imágenes 100 puede decodificar de manera aritmética la información de última posición usando un contexto conmutado de manera apropiada entre una pluralidad de contextos, y por tanto, puede aumentarse la eficiencia de codificación.

Debe observarse que los valores de RP y las longitudes máximas de la parte de prefijo mostrados en la figura 9B a la figura 9E son simples ejemplos, y puede haber diferentes valores de RP y diferentes longitudes máximas de la parte de prefijo. Por ejemplo, la longitud máxima de la parte de prefijo puede ser más corta y la parte de sufijo puede ser más larga. Esto permite adicionalmente la decodificación aritmética en paralelo y aumenta adicionalmente la velocidad de decodificación aritmética.

Debe observarse que cada uno de los elementos estructurales en la presente realización puede configurarse en forma de un producto de hardware exclusivo, o puede implementarse ejecutando un programa de software adecuado para el elemento estructural. Cada elemento estructural puede implementarse por medio de una unidad de ejecución de programa, tal como una CPU o un procesador, que lee y ejecuta el programa de software grabado en un medio de grabación tal como un disco duro o una memoria de semiconductor. En este caso, el programa de

software para implementar el aparato de decodificación de imágenes según la presente realización es un programa descrito a continuación.

Este programa hace que un ordenador ejecute un método de decodificación de imágenes para decodificar información de última posición que indica una posición de un último coeficiente distinto de cero en un orden predeterminado en un bloque actual que va a decodificarse, incluyendo el método de decodificación de imágenes: una primera decodificación para decodificar de manera aritmética cada uno de los símbolos binarios incluidos en una primera señal usando un contexto conmutado entre una pluralidad de contextos según una posición de bit del símbolo binario, incluyéndose la primera señal en una señal binaria de la información de última posición y teniendo una longitud menor que o igual a una longitud máxima predeterminada; y una segunda decodificación para, cuando la señal binaria de la información de última posición incluye una segunda señal, decodificar de manera aritmética la segunda señal usando una probabilidad fijada, en el que, en la primera decodificación, un símbolo binario en una última posición de bit de la primera señal se decodifica de manera aritmética usando un contexto exclusivo para la última posición de bit, cuando la primera señal tiene la longitud máxima predeterminada.

(Variación de la realización 1)

5

10

20

25

30

35

45

El aparato de decodificación de imágenes 100 según la realización 1 puede incluirse en un aparato de decodificación de imágenes a continuación. La figura 12 es un diagrama de bloques que muestra un ejemplo de una configuración de un aparato de decodificación de imágenes 200 según una variación de la realización 1.

El aparato de decodificación de imágenes 200 decodifica datos de imagen codificados generados mediante codificación por compresión. Por ejemplo, el aparato de decodificación de imágenes 200 recibe datos de imagen codificados para un bloque cada vez como señal actual que va a decodificarse. El aparato de decodificación de imágenes 200 realiza decodificación de longitud variable, cuantificación inversa y transformada inversa con la señal actual recibida para reconstruir datos de imagen.

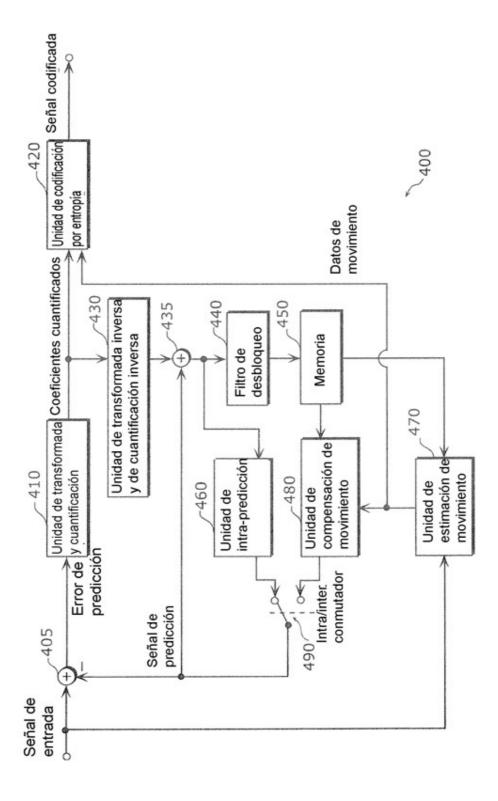

Tal como se muestra en la figura 12, el aparato de decodificación de imágenes 200 incluye una unidad de decodificación por entropía 210, una unidad de cuantificación inversa y transformada inversa 220, un sumador 225, un filtro de desbloqueo 230, una memoria 240, una unidad de intra-predicción 250, una unidad de compensación de movimiento 260 y un conmutador de intra/inter-predicción 270.

La unidad de decodificación por entropía 210 realiza la decodificación de longitud variable con una señal de entrada (flujo de bits) para reconstruir coeficientes cuantificados. En este caso, la señal de entrada es una señal actual que va a decodificarse y corresponde a datos para un bloque cada vez de los datos de imagen codificados. Los datos de imagen codificados incluyen la información de última posición codificada. Además, la unidad de decodificación por entropía 210 obtiene datos de movimiento a partir de la señal de entrada y emite los datos de movimiento a la unidad de compensación de movimiento 260.

Debe observarse que el aparato de decodificación de imágenes 100 según la realización 1 corresponde a parte de la unidad de decodificación por entropía 210. Es decir, la unidad de decodificación por entropía 210 decodifica la información de última posición codificada.

La unidad de cuantificación inversa y transformada inversa 220 realiza la cuantificación inversa con los coeficientes cuantificados reconstruidos por la unidad de decodificación por entropía 210, para reconstruir coeficientes transformados. Entonces, la unidad de cuantificación inversa y transformada inversa 220 realiza la transformada inversa sobre los coeficientes transformados para reconstruir un error de predicción.

40 El sumador 225 suma el error de predicción y una señal de predicción para generar una imagen decodificada.

El filtro de desbloqueo 230 aplica un filtro de desbloqueo a la imagen decodificada. La imagen decodificada resultante se emite como señal decodificada.

La memoria 240 es una memoria para almacenar una imagen de referencia usada en la compensación de movimiento. Más específicamente, la memoria 240 almacena la imagen decodificada a la que se le ha aplicado el filtro de desbloqueo.

La unidad de intra-predicción 250 realiza la intra-predicción para generar una señal de predicción (señal de intra-predicción). Más específicamente, la unidad de intra-predicción 250 genera una señal de intra-predicción realizando la intra-predicción mediante referencia a una imagen circundante al bloque actual que va a decodificarse (señal de entrada) en la imagen decodificada generada mediante el sumador 225.

La unidad de compensación de movimiento 260 realiza la compensación de movimiento basándose en los datos de movimiento emitidos por la unidad de decodificación por entropía 210, para generar una señal de predicción (señal de inter-predicción).

El conmutador de intra/inter-predicción 270 selecciona o bien la señal de intra-predicción o bien la señal de inter-predicción, y emite la señal seleccionada al sumador 225 como señal de predicción.

Con la configuración anterior, el aparato de decodificación de imágenes 200 decodifica los datos de imagen codificados generados mediante codificación por compresión.

(Realización 2)

20

25

30

Lo siguiente describe un aparato de codificación de imágenes según la realización 2 usando los dibujos.

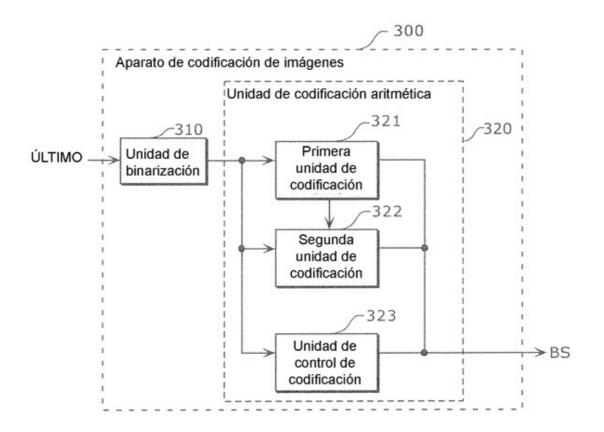

- La figura 13 es un diagrama de bloques que muestra una configuración funcional de un aparato de codificación de imágenes 300 según la realización 2. El aparato de codificación de imágenes 300 codifica la información de última posición. El aparato de codificación de imágenes 300 incluye una unidad de binarización 310 y una unidad de codificación aritmética 320. La unidad de codificación aritmética 320 incluye una primera unidad de codificación 321, una segunda unidad de codificación 322, y una unidad de control de codificación 323.