# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 665 040

51 Int. Cl.:

**H03M 1/06** (2006.01) **H03M 1/66** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 03.12.2008 PCT/EP2008/066677

(87) Fecha y número de publicación internacional: 11.06.2009 WO09071568

96 Fecha de presentación y número de la solicitud europea: 03.12.2008 E 08857306 (8)

(97) Fecha y número de publicación de la concesión europea: 28.02.2018 EP 2241010

(54) Título: Dispositivo de resincronización de señales analógicas obtenidas por conversión, con unos convertidores digital-analógico DDR, de señales digitales sincronizadas

(30) Prioridad:

07.12.2007 FR 0708550

Fecha de publicación y mención en BOPI de la traducción de la patente: 24.04.2018

(73) Titular/es:

THALES (100.0%)

Tour Carpe Diem, Place des Corolles, Esplanade

Nord

92400 Courbevoie, FR

(72) Inventor/es:

AUTRUSSON, BERTRAND; PASSELAIGUE, DANIEL y VERYERAS, ALEXANDRE

(74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

#### **DESCRIPCIÓN**

Dispositivo de resincronización de señales analógicas obtenidas por conversión, con unos convertidores digitalanalógico DDR, de señales digitales sincronizadas

La presente invención se refiere a un dispositivo de resincronización de una pluralidad de señales analógicas obtenidas por conversión, con unos convertidores digital-analógico de doble tasa de datos, de una pluralidad de señales digitales sincronizadas en la salida de un componente digital. Se aplica por ejemplo en el campo de la electrónica.

10

15

20

25

30

35

40

45

La conversión en analógico de señales digitales de alta frecuencia de muestreo siempre ha planteado problemas, a causa principalmente de fenómenos físicos remanentes sobre unos componentes internos en los convertidores digital-analógico (CDA). Una solución actual es la utilización de CDA funcionando de acuerdo con el protocolo de doble tasa de datos, siendo más conocido este protocolo por el acrónimo anglosajón "DDR" que significa "Double Data Rate". El principio del protocolo DDR es utilizar los flancos ascendentes y los flancos descendentes de una señal de reloj en lugar de utilizar únicamente sus flancos ascendentes. Concretamente, para hacer funcionar un CDA sobre unas señales digitales de frecuencia de muestreo 2F, el CDA recibe una señal de reloj de frecuencia 2F en la entrada, que divide por dos mediante unos mecanismos internos con el fin de obtener una señal de reloj de frecuencia F. La señal de frecuencia F se utiliza por el CDA para marcar el ritmo de sus etapas de registros, principalmente sus registros de entrada que reciben la señal digital a convertir. Por un lado, trabajando sobre los flancos ascendentes y sobre los flancos descendentes de la señal de frecuencia F, de acuerdo con el protocolo DDR, estas etapas de registros pueden procesar una señal digital de entrada muestreada a la frecuencia 2F. Por otro lado, al trabajar a la frecuencia F en lugar de trabajar a la frecuencia 2F, estas etapas de registros limitan el impacto de los fenómenos físicos remanentes. En lo que sigue, un CDA funcionando de acuerdo con el protocolo DDR se denominará simplemente CDA DDR.

En ciertas situaciones, pueden tener que convertirse en señales analógicas varias señales digitales sincronizadas y de la misma frecuencia elevada, de tal manera que dichas señales analógicas deben permanecer sincronizadas. Puede ser entonces interesante hacer trabajar en paralelo varios CDA DDR que reciben una misma señal de reloj. Por ejemplo, considerando dos señales digitales sincronizadas de frecuencia elevada 2F, estas dos señales pueden suministrarse en la entrada de dos CDA DDR respectivamente, recibiendo los dos CDA DDR una misma señal de reloj de frecuencia 2F. Pero desgraciadamente, a pesar del hecho de recibir una misma señal de reloj de frecuencia 2F, no hay ninguna razón para que las señales de frecuencia F obtenidas por división interna en cada uno de los dos CDA DDR estén en fase. Las señales de frecuencia F obtenidas por división por dos interna en cada uno de los dos CDA DDR pueden estar en oposición de fase una con relación a la otra. En efecto, al realizarse independientemente entre sí estas divisiones de la señal mediante unos componentes electrónicos ciertamente idénticos pero distintos, no hay ninguna razón para que den unas señales idénticas en fase. En el caso actual, esto puede explicarse por unos tiempos de latencia específicos de cada componente electrónico que, a pesar de una misma señal de reloj, se desplazan en el tiempo en los CDA DDR a partir de sus arranques. De ese modo, las divisiones por dos pueden hacerse en unas fases diferentes de la señal de reloj de frecuencia 2F y las señales de frecuencia F encontrarse en oposición de fase. Las señales analógicas convertidas a la salida de los dos CDA DDR se encuentran ellas también en oposición de fase. Por otro lado, es necesario observar que este fenómeno no es determinista y que de una puesta en tensión a otra estos dos CDA DDR a pesar de las condiciones de puesta en tensión que puede parecer idénticas, puede estar en fase o en oposición de fase sin que sea posible preverlo.

El problema parece haber sido identificado por unos fabricantes de CDA DDR, habiendo publicado incluso algunos de ellos unas notas técnicas que se dirigen a dar unas pistas y consejos a los usuarios enfrentados al problema. Se trata esencialmente de tener cuidado en hacer funcionar los CDA DDR en unos entornos similares en tanto que se pueda hacer, por ejemplo poniendo cuidado principalmente en someter a las líneas que transportan la señal de reloj a las mismas restricciones. Pero las tentativas en este sentido llevadas a cabo por el presente solicitante con la ayuda de los fabricantes no han tenido éxito. Un fabricante concibe producir próximamente un dispositivo que incluye dos CDA DDR sobre un mismo chip lo que, según el fabricante en cuestión, debería resolver el problema puesto que los dos CDA DDR compartirán los componentes de arranque sospechosos de estar en el origen del problema. Pero esta solución no está aún disponible en la actualidad.

50 En una nota técnica titulada "Synchronizing Multiple High-Speed Multiplexed DACs for Transmit Applications" disponible en el sitio internet de la compañía MAXIM, se divulga una solución para detectar y posteriormente corregir la oposición de fase entre dos CDA DDR utilizados para convertir en analógico dos salidas sincronizadas de un componente digital. Pero esta solución necesita la adición de un componente dedicado que distribuye la compañía MAXIM.

La invención tiene principalmente por objeto resolver el problema antes mencionado, aprovechando juiciosamente la arquitectura material de los CDA DDR. Con este fin, la invención tiene por objeto un dispositivo de resincronización tal como se define por las reivindicaciones.

La invención tiene también por principales ventajas que no necesita un mecanismo para detectar en un primer tiempo una oposición de fase y un mecanismo para corregir en un segundo tiempo una eventual oposición de fase.

## ES 2 665 040 T3

La invención proporciona una solución simple, unitaria y autónoma que funciona de manera idéntica tanto si hay oposición de fase como si no.

Surgirán otras características y ventajas de la invención con la ayuda de la descripción que sigue realizada con relación a los dibujos adjuntos que representan:

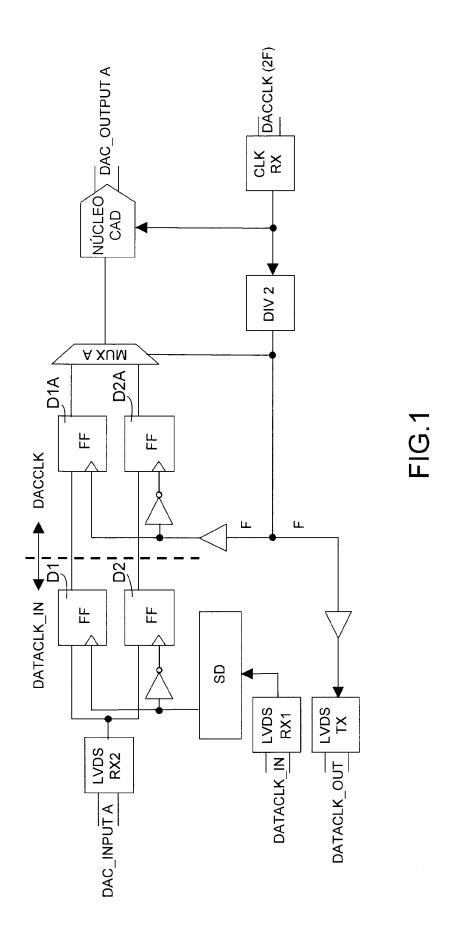

- 5 la figura 1, una ilustración mediante un sinóptico de un ejemplo de arquitectura material de un CDA DDR;

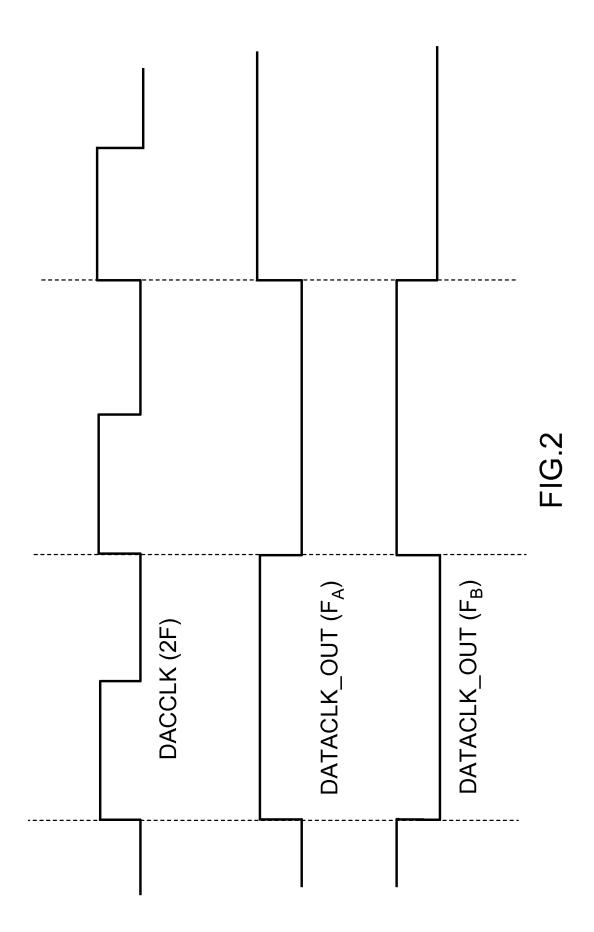

- la figura 2, una ilustración de ejemplos de señales que pueden ser el resultado de la división por dos de una señal de reloj;

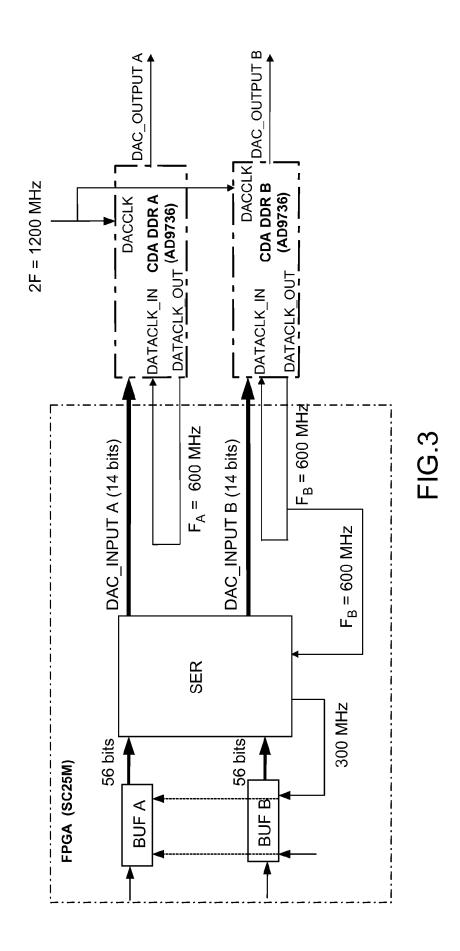

- la figura 3, una ilustración mediante un sinóptico de un ejemplo de dispositivo según la invención.

La figura 1 ilustra mediante un sinóptico un ejemplo de arquitectura material de un CDA DDR A. El CDA DDR A de la 10 figura 1 es un CDA DDR de la marca Analog Device de tipo AD9736. Incluye un elemento CLKRX que puede recibir desde el exterior una señal de reloj DACCLK a la frecuencia 2F. Un elemento DIV2 divide por dos la frecuencia de DACCLK para obtener una señal de reloj DATACLK\_OUT de frecuencia F, siendo suministrada la señal de reloj DATACLK\_OUT por una parte a la salida por medio de un componente LVDSTX y siendo suministrada por otra parte la señal de reloj DATACLK\_OUT a unos registros de salida D1A y D2A internos del CDA DDR A. Por tanto se marca el ritmo de los registros D1A y D2A a la frecuencia F. El CDA DDR A del ejemplo de la figura 1 incluye 15 igualmente un elemento LVDSRX1 que puede recibir del exterior una señal de reloj DATACLK\_IN. La señal de reloj DATACLK IN se suministra a unos registros de entrada D1 y D2 por medio de un elemento SD de muestreo. Los registros D1 y D2 pueden recibir por medio de un elemento LVDSRX2 una señal digital DAC INPUTA a convertir. Para convertir correctamente la señal digital DAC\_INPUTA, los registros D1 y D2 deben estar sincronizados con los 20 registros de salida del componente exterior que suministra la señal DAC INPUTA. En otros términos, la señal de reloj DATACLK IN debe ser idéntica a la señal que marca el ritmo de los registros de salida del componente que suministra la señal digital DAC\_INPUTA a convertir. El CDA DDR A incluye igualmente un multiplexor MUXA que permite procesar alternativamente los registros D1A y D2A y suministrar los datos que contienen a un elemento DACCORE. El elemento DACCORE suministra a la salida del CDA DDR A una señal analógica DAC OUTPUTA que 25 es la conversión de la señal DAC INPUTA. La arquitectura del CDA DDR A aparece como claramente separada en dos dominios: un dominio en el que se marca el ritmo de las etapas de registros a la frecuencia DATACLK\_IN y un dominio en el que se marca el ritmo de las etapas de registros a la frecuencia DACCLK. La invención se propone aprovechar juiciosamente esta propiedad que se encuentra en la mayoría de los CDA DDR.

La figura 2 ilustra las dos señales DATACLK\_OUT que pueden ser el resultado de la división por dos de la señal DACCLK por el componente DIV2. Como se ha explicado anteriormente, la división realizada por DIV2 puede hacerse sobre unas fases diferentes de la señal DACCLK de frecuencia 2F, y esto de manera determinista. De ese modo, pueden resultar dos señales DATACLK\_OUT de la división de la señal DACCLK: o bien una señal DATACLK\_OUT de frecuencia F<sub>B</sub>, estando las frecuencias F<sub>A</sub> y F<sub>B</sub> en oposición de fase.

La figura 3 ilustra mediante un sinóptico un ejemplo de dispositivo según la invención. El dispositivo incluye dos CDA DDR idénticos de tipo AD9736, el CDA DDR A de la figura 1 y un CDA DDR B, para procesar en paralelo dos señales digitales DAC\_INPUTA y DAC\_INPUTB sincronizadas de 14 bits cada una. Estas dos señales digitales DAC\_INPUTA y DAC\_INPUTB sincronizadas pueden ser suministradas por una red de puertas programables, o "FPGA" según la terminología anglosajona ("field-programmable gate array"). Por ejemplo, la FPGA puede ser de la marca Lattice de la familia SC25M. Puede incluir dos memorias intermedias BUF A y BUF B de tipo FIFO ("First In First Out") que pueden recibir por ejemplo dos series de datos de 56 bits cada una, y esto de manera discontinua. La FPGA puede incluir un módulo SER de serialización de los datos hacia el que se transfieren las series de datos de 56 bits. Por ejemplo, el módulo SER puede permitir pasar de dos bus de 56 bits a 300 megahercios en la entrada a dos bus de 14 bits con un reloj cuatro veces más rápido en la salida, es decir un reloj a 1200 megahercios.

45 El CDA DDR A y el CDA DDR B deben por tanto convertir las dos señales digitales sincronizadas de 14 bits a 1200 megahercios, de tal manera que las dos señales analógicas DAC OUTPUTA y DAC OUTPUTB en la salida de CDA DDR A y de CDA DDR B respectivamente, estén siempre sincronizadas. Para ello, el CDA DDR A y el CDA DDR B reciben en la entrada de sus elementos CLKRX respectivos la misma señal de reloj DACCLK a la frecuencia 2F de la figura 2 siendo 2F=1200 megahercios. En el ejemplo de la figura 3, la señal a F=600 megahercios en la 50 salida DATACLK\_OUT del CDA DDR B puede suministrarse ventajosamente como señal de reloj de los registros de salida del módulo SER. En efecto, al ser tratadas la salida del módulo SER por los componentes DDR, a saber el CDA DDR A y el CDA DDR B, es suficiente un reloj a 600 megahercios en lugar de 1200 megahercios. Porque como se ha explicado anteriormente, un reloj a 600 megahercios utilizado en DDR es equivalente a un reloj a 1200 megahercios utilizado como tasa de datos simple. De ese modo, según la invención, los datos se envían hacia 55 la salida del módulo SER con un reloj síncrono del CDA DDR B, que se denominará en lo que sigue "convertidor de referencia". Por otro lado, cada una de las señales de reloj en las salidas DATACLK OUT puede enviarse a su propio convertidor: la señal a la frecuencia F=600 megahercios en la salida DATACLK OUT del CDA DDR B se suministra como señal de reloj a la entrada DATACLK\_IN del CDA DDR B y la señal a la frecuencia F=600 megahercios en la salida DATACLK OUT del CDA DDR A se suministra como señal de reloj a la entrada 60 DATACLK IN del CDA DDR A. Pero como se ha explicado anteriormente, a pesar del hecho de que reciben la misma señal de reloj DACCLK a la frecuencia 2F=1200 megahercios y al hecho de que las líneas que transmiten la

## ES 2 665 040 T3

señal se sometan a las mismas restricciones, no hay ninguna razón para que las dos señales de frecuencia F=600 megahercios disponibles en las salidas DATACLK\_OUT respectivas del CDA DDR A y del CDA DDR B estén en fase.

En un primer caso, que es el ilustrado por la figura 3, pueden estar en oposición de fase, pudiendo estar la señal en 5 la salida DATACLK OUT del CDA DDR A a la frecuencia FA de la figura 2 y pudiendo estar la señal en la salida DATACLK\_OUT del CDA DDR B a la frecuencia FB de la figura 2. Como se ilustra por la figura 1, el multiplexor MUXA procesa alternativamente los datos a la salida del registro D1A y posteriormente los datos a la salida del registro D2A, marcándose a su vez el ritmo asimismo de los registros D1A y D2A así como del multiplexor MUXA internamente en el CDA DDR A a la frecuencia F<sub>A</sub>. De manera similar, el CDA DDR B incluye un multiplexor MUXB que procesa alternativamente los datos a la salida de un registro D1B y posteriormente los datos a la salida de un 10 registro D2B, marcándose a su vez el ritmo asimismo de los registros D1B v D2B así como del multiplexor MUXB internamente en el CDA DDR B a la frecuencia F<sub>B</sub>. Pero puesto que por hipótesis F<sub>A</sub> y F<sub>B</sub> están en oposición de fase, entonces MUXA y MUXB trabajan de manera simétrica o inversa: MUXA procesa D1A cuando MUXB procesa D2B y MUXA procesa D2A cuando MUXB procesa D1 B. Ahora bien, las salidas del módulo SER tienen marcado su ritmo 15 por su parte a la frecuencia F<sub>B</sub>, siendo el CDA DDR B el convertidor de referencia que suministra la señal de reloj al módulo SER. Por tanto los registros de entrada D1 y D2 del CDA DDR A con su ritmo marcado a FA trabajan igualmente de manera invertida o simétrica con relación a los registros de salida del módulo SER: se encuentra que el registro D1A contiene lo que hubiera debido contener al registro D2A y se encuentra que el registro D2A contiene lo que hubiera debido contener el registro D1A. Esta inversión del contenido de los registros D1A y D2A combinada 20 con la inversión en el secuenciamiento de los procesamientos por MUXA de los registros D1A y D2A permite restablecer la sincronización. De alguna manera, una inversión anula la otra.

En un segundo caso, las señales de frecuencia F=600 megahercios disponibles en las salidas DATACLK\_OUT respectivas del CDA DDR A y del CDA DDR B pueden estar en fase, pudiendo estar la señal a la salida DATACLK\_OUT del CDA DDR A y la señal a la salida DATACLK\_OUT del CDA DDR B a la misma frecuencia F<sub>A</sub> de la figura 2. En este caso, no hay ninguna inversión y la sincronización no se rompe nunca.

25

35

En un segundo caso, las señales de frecuencia F=600 megahercios disponibles en las salidas DATACLK\_OUT respectivas del CDA DDR A y del CDA DDR B pueden estar en fase, pudiendo estar la señal a la salida DATACLK\_OUT del CDA DDR A y la señal a la salida DATACLK\_OUT del CDA DDR B a la misma frecuencia F<sub>B</sub> de la figura 2. En este caso igualmente, no hay ninguna inversión y la sincronización no se rompe nunca.

30 Así, gracias a la invención, las señales analógicas convertidas a la salida de los dos CDA DDR A y CDA DDR B están siempre fase, no se desincronizan nunca.

Además de la ventaja de ofrecer una solución simple, unitaria, autónoma y poco costosa, la invención descrita anteriormente tiene también como principales ventajas que es aplicable cualquiera que sea el número de CDA DDR utilizados, constituyendo uno solo de entre ellos el convertidor de referencia para todos los demás. Independientemente de la frecuencia, es por otro lado aplicable a frecuencias elevadas.

#### **REIVINDICACIONES**

- 1. Dispositivo de resincronización de una pluralidad de señales analógicas (DAC\_OUTPUTA, DAC\_OUTPUTB) obtenidas por conversión, con unos convertidores digital-analógico de doble tasa de datos, de una pluralidad de señales digitales (DAC\_INPUTA, DAC\_INPUTB) de frecuencia 2F, sincronizadas a la salida de un módulo de serialización (SER):

- incluyendo el dispositivo al menos dos convertidores digital-analógico A y B de doble tasa de datos, estando conectado cada convertidor respectivamente a una vía de salida de dicho módulo de serialización:

- recibiendo los convertidores A y B una misma señal de reloj de frecuencia 2F, dividiendo los convertidores A y B por dos de manera independiente esta señal de reloj, para obtener una señal de reloj de frecuencia F lo que permite marcar el ritmo a la frecuencia F de sus registros de salida (D1A, D2A) y sus registros de entrada (D1, D2);

estando dicho dispositivo **caracterizado porque** el convertidor B suministra la señal de reloj a la frecuencia F a dicho módulo de serialización (SER) para marcar el ritmo de los registros de salida de dicho módulo de serialización (SER), suministrando a la salida de reloj del convertidor B la señal de reloj de los registros de salida de dicho módulo de serialización (SER), de manera que las señales analógicas (DAC\_OUTPUTA, DAC\_OUTPUTB) a la salida de los dos convertidores A y B permanezcan sincronizadas incluso si la señal de reloj a la frecuencia F<sub>A</sub> obtenida por división en el convertidor A está en oposición de fase con relación a la señal de reloj a la frecuencia F<sub>B</sub> obtenida por división en el convertidor B.

2. Dispositivo según la reivindicación 1, caracterizado porque:

5

10

15

25

- los convertidores A y B incluyen cada uno una salida de reloj (DATACLK\_OUT) que suministra la señal de reloj a la frecuencia F;

- los convertidores A y B incluyen cada uno una entrada de reloj (DATACLK\_IN) que permite marcar el ritmo de sus registros de entrada (D1, D2);

- la salida de reloj del convertidor A está conectada a la entrada de reloj del convertidor A y la salida de reloj del convertidor B está conectada a la entrada de reloj del convertidor B.

- 3. Dispositivo según la reivindicación 1, **caracterizado porque** el módulo de serialización (SER) se implementa en una red de puertas programables (FPGA).

- 4. Dispositivo según la reivindicación 1, **caracterizado porque** el módulo de serialización (SER) permite pasar señales digitales sobre 56 bits a señales sobre 14 bits multiplicando la frecuencia de las señales por cuatro.

- 30 5. Dispositivo según la reivindicación 1, caracterizado porque la frecuencia 2F es superior a 1000 megahercios.

5