# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 672 225

51 Int. Cl.:

H01Q 3/26 (2006.01) H04B 7/06 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 30.06.2011 PCT/US2011/042527

(87) Fecha y número de publicación internacional: 05.01.2012 WO12003276

96 Fecha de presentación y número de la solicitud europea: 30.06.2011 E 11729873 (7)

(97) Fecha y número de publicación de la concesión europea: 18.04.2018 EP 2589108

(54) Título: Matrices de antena activa de bajo coste

(30) Prioridad:

01.07.2010 US 360737 P

Fecha de publicación y mención en BOPI de la traducción de la patente: 13.06.2018

(73) Titular/es:

BLUE DANUBE SYSTEMS, INC. (100.0%) 200 Warren Corporate Center Drive, 2nd Floor Warren, NJ 07059, US

(72) Inventor/es:

BANU, MIHAI; FENG, YIPING y PRODANOV, VLADIMIR, IVANOV

(74) Agente/Representante:

SÁEZ MAESO, Ana

#### **DESCRIPCIÓN**

Matrices de antena activa de bajo coste

5 Esta solicitud reivindica el beneficio de la Solicitud Provisional de Estados Unidos No. 61/360,737, presentada el 1 de julio de 2010, que se incorpora aquí como referencia.

Campo técnico

25

30

35

50

55

60

65

10 Las realizaciones de la presente invención generalmente se refieren a matrices activas tales como matrices en fase para antenas inteligentes.

Antecedentes de la invención

Las matrices de antenas se utilizan en aplicaciones tales como radares y sistemas de comunicación basados en haces. Por ejemplo, véase R. Mailloux, "Phased Array Antenna Handbook", 2ª edición, Artech House, 2005; D. Parker y D. Zimmermann, "Phased Arrays-Part I: Theory and Architectures," IEEE Trans. Microwave Theory and Techniques, vol. 50, March 2002; D. Parker and D. Zimmermann, "Phased Arrays-Part II: Implementations, Applications, and Future Trends," IEEE Trans. Microwave Theory and Techniques vol. 50, Marzo de 2002. La razón principal para usar las matrices de antenas es su capacidad de generar patrones de radiación dinámicos especiales, tales como haces dirigibles sin ningún movimiento mecánico.

En general, cada elemento de matriz de una matriz de antena consiste en una antena pasiva llamada elemento de antena o simplemente una antena y un bloque de circuito. Por lo general, los elementos de antena se colocan en una cuadrícula regular. La separación de esta cuadrícula es aproximadamente o igual a la mitad de la longitud de onda en la que opera la matriz de antenas. El bloque de circuitos del elemento de matriz puede ser tan simple como un desplazador por fases pasivo o tan compleja como una radio completa que incluye amplificadores, mezcladores, filtros, convertidores de datos y circuitos digitales. Si la matriz de antena contiene solo componentes pasivos, se llama matriz de antena contiene componentes activos, se llama matriz de antena activa.

Las matrices de antena pueden generar muchos patrones de radiación. Por ejemplo, pueden aceptar señales entrantes desde ciertas direcciones y bloquear las señales entrantes desde otras direcciones o pueden transmitir solo haces estrechos, aunque cada elemento de antena se irradie ampliamente. Dichos patrones de radiación son extremadamente útiles en muchas aplicaciones. En el radar que usa matrices de antena, las señales transmitidas se enfocan en una dirección espacial particular y las únicas reflexiones de señal aceptadas son de la misma dirección sin ningún movimiento físico de antenas como en los sistemas convencionales. En los sistemas de comunicación inalámbricos, que utilizan canales espaciales para señales transmitidas y recibidas, una técnica generalmente llamada dirección del haz, aumenta sustancialmente la capacidad del sistema de comunicación.

La forma en que una matriz de antena genera patrones de radiación dinámicos especiales es combinar adecuadamente las señales recibidas de los elementos de antena en el modo de recepción y excitando adecuadamente los elementos de antena en modo de transmisión. Dependiendo de cómo se realicen estas operaciones, las matrices de antena se llaman analógicas o digitales. En las matrices analógicas, los patrones de radiación de recepción y transmisión están formados por circuitos analógicos, mientras que en la matriz digital están formados por procesamiento digital bajo control de software.

Hasta la fecha, las matrices de antena analógicas más exitosas son las matrices por fases tradicionales. Históricamente, la matriz pasiva electrónicamente dirigida (PESA) se ha desarrollado primero. Este diseño utiliza una red de distribución/combinación de señal llamada alimentación corporativa y desplazador por fases pasivo ajustables en cada elemento de antena. Estos componentes tienen una gran pérdida que limita el rendimiento del sistema. Agregar módulos amplificadores de recepción/transmisión (Rx/Tx) por elemento de antena individual ayuda a que este problema resulte en una matriz activa electrónicamente dirigida o AESA, actualmente la arquitectura de radar militar predominante. Tanto para PESA como para EISA, la alimentación corporativa y las desfasadoras de fase programables son componentes caros de alto rendimiento.

La alimentación corporativa es una red de árbol pasivo hechas por múltiples secciones de líneas de transmisión interconectadas con múltiples divisores/combinadores. La alimentación corporativa tiene un puerto de entrada/salida (E/S) conectado al comienzo de la troncal del árbol y muchos puertos de E/S conectados al final de las derivaciones superiores del árbol. La red es eléctricamente simétrica de modo que una señal aplicada en el puerto troncal llega simultáneamente a todos los puertos de derivación. La red es recíproca de forma tal que las señales aplicadas en los puertos de derivación viajan la misma cantidad de tiempo para llegar al puerto troncal. En otras palabras, el tiempo de vuelo de la señal desde el puerto troncal a cualquier puerto de derivación y viceversa es una constante. Además, la alimentación corporativa es una red de combinación de señales. Cuando se aplican diferentes señales de entrada a los puertos de derivación simultáneamente, la señal en el puerto troncal es la suma de estas señales de entrada. La realización práctica de la alimentación corporativa es costosa porque esta red contiene muchas operaciones de división/combinación de señales y

porque las secciones de línea de transmisión deben coincidir con precisión en longitud y terminarse eléctricamente con impedancias precisas. Todas estas condiciones de diseño son propensas a errores.

Si bien en un extremo del espectro de la tecnología de matriz de antena se encuentran las matrices por fase tradicionales PESA/EISA, que generan patrones de radiación exclusivamente con métodos analógicos, en el otro extremo de este espectro se encuentran los sistemas digitales configurados por software. Típicamente, estos sistemas usan 4-12 radios independientes conectados a 4-12 antenas independientes, respectivamente. No hay conexiones físicas entre estos radios o estas antenas. Cada radio contiene conversores de datos que convierten las señales recibidas de formato analógico a formato digital y convierte las señales transmitidas de formato digital a formato analógico. Las respectivas 4-12 señales de transmisión digital y 4-12 de recepción digital son generadas y/o procesadas por un procesador de señal digital bajo el control de un software especial, usualmente llamado software de "formación/dirección del haz".

Las matrices digitales configuradas por software se pueden construir fácilmente con hardware estándar y son extremadamente flexibles en términos de programabilidad, pero adolecen de deficiencias fundamentales. Primero, el hardware de estos sistemas es naturalmente costoso ya que hay muchos (4-12) sistemas de radio presentes. Además, estas radios deben tener un rendimiento muy alto para garantizar que las representaciones digitales de las señales de antena (que son siempre analógicas) sean correctas. En segundo lugar, el software que genera las señales es extenso y se ejecuta en tiempo real, lo que requiere una potencia de procesamiento sustancial. En tercer lugar, tener solo 12 o menos antenas por sistema limita el rendimiento de la matriz. Un compromiso común es formar patrones dinámicos (por ejemplo, haces, etc.) solo en acimut (direcciones horizontales) con patrones de elevación fija (dirección vertical). En el caso de la formación de haces, típicamente, estos son conos alargados que abarcan regiones estrechas pero largas. En contraste con esto, una matriz por fase analógica PESA/EISA con cientos o miles de antenas genera haces redondos estrechos dirigibles tanto en azimut como en elevación.

En principio, la cantidad de antenas en las matrices digitales configuradas por software se pueden escalar con un aumento correspondiente en el coste y el tamaño del sistema. Un enfoque común para limitar el tamaño físico del sistema es colocar la mayor cantidad posible de hardware de radio en los paneles de matriz por faces. Estas matrices digitales altamente compactadas con muchas decenas o incluso cientos de elementos están destinados a aplicaciones, donde el coste no es un factor de tecnología primario, como algunos radares militares.

Entre los dos extremos tecnológicos definidos por todo el procesamiento analógico o todo el procesamiento digital, existen otras posibilidades conocidas para implementar matrices de antenas activas, parcialmente con técnicas analógicas y parcialmente con técnicas digitales. Por ejemplo, una gran matriz puede ser segmentada en muchas submatrices, cada submatriz está diseñada como un sistema analógico. Sin embargo, las señales hacia/desde cada submatriz se generarían en el dominio digital.

#### Resumen de la invención

5

10

15

20

30

35

40

45

50

55

60

65

Las realizaciones de la presente invención incluyen métodos y sistemas para la distribución y agregación de señales de recepción y transmisión en una matriz de antena activa o submatriz con control de amplitud y fase en cada elemento de antena. Los métodos y sistemas incluidos en las realizaciones de la presente invención contienen al menos una de las redes de señalización bidireccionales (red BDS) descrita anteriormente. Por ejemplo, ver V. Prodanov y M. Banu "GHz Serial Passive Clock Distribution in VLSI Using Bidirectional Signaling,", Actas, 2006 IEEE Custom Integrated Circuits Conference; y la solicitud de patente de Estados Unidos Nº US 2009/086867 presentada el 21 de julio de 2008.

En general, una red BDS comprende un conjunto de redes de árbol de distribución de señal denominado "bus BDS" y un conjunto de circuitos de procesamiento locales. Estos circuitos de procesamiento local se denominan circuitos de cliente con tiempo promediado de llegada (ATAC) y se definen en la especificación de la solicitud de patente de Estados Unidos Nº US 2009/086867. Un circuito ATAC importante es un multiplicador analógico llamado multiplicador BDS. En la presente invención, usamos circuitos ATAC o combinaciones de circuitos ATAC con amplitud de salida sintonizable y fase de salida sintonizable bajo el control de señales electrónicas. Llamamos a estos circuitos ATAC o combinaciones de tales circuitos ATAC Circuitos de amplitud y fase sintonizables ATAC o circuitos TAPA. Los circuitos TAPA comprenden subcircuitos, que pueden cambiar la amplitud y la fase de las señales bajo control electrónico denominadas circuitos "de ajuste A/P". En general, un circuito de ajuste de ajuste A/P podría proporcionar control de amplitud completo, control de amplitud parcial o control de amplitud cero y control de fase completo, control de fase parcial o control de fase cero. Si un circuito de ajuste de A/P proporciona solo control de amplitud, se denomina "Ajuste A" y si un circuito de ajuste de A/P proporciona solo control de fase, se denomina "Ajuste P".

De acuerdo con una realización de la presente invención, se proporciona un circuito transmisor de matriz activa que comprende un bus BDS con dos árboles BDS, una pluralidad de circuitos TAPA, una pluralidad de circuitos mezcladores, una pluralidad de circuitos de Ajuste A y una pluralidad de antenas. El bus BDS se excita con una señal de oscilador local proporcionada por un sintetizador de frecuencia u otra fuente externa. Cada circuito TAPA tiene terminales de señal de entrada primero y segundo conectados al primer y segundo árboles BDS del bus BDS, respectivamente. Cada circuito TAPA tiene un terminal de señal de salida conectado a un primer terminal de señal de entrada de un circuito mezclador. Cada circuito mezclador tiene terminales de señal de entrada primero y segundo y un terminal de señal de salida acoplado a una antena. La segunda entrada de señal de cada circuito mezclador está conectada a la salida de un circuito de Ajuste-

A. Cada circuito de Ajuste-A tiene un terminal de señal de entrada y un terminal de señal de salida. Los terminales de señal de entrada de todos los circuitos de ajuste-A están conectados entre sí y reciben una señal modulada de frecuencia intermedia (IF) desde una fuente externa. Cada circuito TAPA comprende un multiplicador analógico con una primera y una segunda entradas y una salida y un primero, un segundo y un tercer circuitos de Ajuste P, cada circuito de Ajuste P con una entrada y una salida. La entrada del primer circuito de Ajuste P está conectada a la primera entrada del multiplicador analógico. La entrada del segundo circuito de Ajuste P está conectada a la segunda entrada del circuito TAPA. La salida del segundo circuito de Ajuste P está conectada a la segunda entrada del circuito TAPA. La salida del segundo circuito de Ajuste P está conectada a la segunda entrada del multiplicador analógico. La entrada del tercer circuito de Ajuste P se conecta a la salida del multiplicador analógico. La salida del tercer circuito de Ajuste P está conectada a la salida del circuito TAPA. El circuito transmisor de la matriz activa comprende además medios para controlar independientemente el ajuste de todos los circuitos de Ajuste P y Ajuste A que éste incluye.

10

15

20

25

50

55

60

65

De acuerdo con otra realización de la presente invención, se proporciona un circuito transmisor de matriz activa que comprende un bus BDS con dos árboles BDS, una pluralidad de circuitos TAPA y una pluralidad de antenas. El primer árbol BDS del bus BDS se excita con una señal de oscilador local proporcionada por un sintetizador de frecuencia u otra fuente externa. El segundo árbol BDS del bus BDS está excitado con una portadora modulada. La portadora en el segundo árbol BDS tiene la misma frecuencia que la señal del oscilador local en el primer árbol BDS. Cada circuito TAPA tiene terminales de señal de entrada primero y segundo conectados al primer y segundo árboles BDS del bus BDS, respectivamente. Cada circuito TAPA tiene un terminal de señal de salida acoplado a una antena. Cada circuito TAPA comprende un multiplicador analógico con primera y segunda entradas y una salida, un circuito de ajuste A/P con una entrada y una salida y un primer y segundo circuitos de Ajuste P, cada circuito de Ajuste P con una entrada y una salida. La entrada del circuito de ajuste de A/P está conectada a la primera entrada del circuito TAPA. La salida del circuito de ajuste A/P está conectada a la primera entrada del multiplicador analógico. La entrada del primer circuito de Ajuste P está conectada a la segunda entrada del circuito TAPA. La salida del primer circuito de Ajuste P se conecta a la segunda entrada del multiplicador analógico. La entrada del segundo circuito de Ajuste P se conecta a la salida del multiplicador analógico. La salida del tercer circuito de Ajuste P está conectada a la salida del circuito TAPA. El circuito transmisor de matriz activa comprende además medios para controlar de forma independiente el ajuste de todos los circuitos de Ajuste A/P y Ajuste A que éste incluye.

30 De acuerdo con otra realización de la presente invención, se proporciona un circuito receptor de matriz activa que comprende un bus BDS con dos árboles BDS, una pluralidad de circuitos TAPA, una pluralidad de circuitos mezcladores, una pluralidad de circuitos de ajuste A y una pluralidad de antenas. El bus BDS se excita con una señal de oscilador local proporcionada por un sintetizador de frecuencia u otra fuente externa. Cada circuito TAPA tiene terminales de señal de entrada primero y segundo conectados al primer y segundo árboles BDS del bus BDS, respectivamente. Cada circuito 35 TAPA tiene un terminal de señal de salida conectado a una primera terminal de señal de entrada de un circuito mezclador. Cada circuito mezclador tiene terminales de señal de entrada primero y segundo y un terminal de señal de salida. El segundo terminal de señal de entrada de cada circuito mezclador está acoplado a una antena a través de un amplificador de bajo ruido o directamente. El terminal de señal de salida de cada circuito mezclador está conectado a la entrada de un circuito de ajuste A. Cada circuito de ajuste A tiene un terminal de señal de entrada y un terminal de señal de salida. Los 40 terminales de señal de salida de todos los circuitos de ajuste A están conectados entre sí y transportan una señal de frecuencia intermedia (IF) modulada a un circuito externo, como la etapa del receptor de radio IF. Cada circuito TAPA comprende un multiplicador analógico con una primera y una segunda entradas y una salida y un primero, un segundo y un tercer circuito de ajuste P, cada circuito de ajuste P con una entrada y una salida. La entrada del primer circuito de ajuste P está conectada a la primera entrada del circuito TAPA. La salida del primer circuito de ajuste P está conectada a la primera entrada del multiplicador analógico. La entrada del segundo circuito de ajuste P está conectada a la segunda 45 entrada del circuito TAPA. La salida del segundo circuito de ajuste P está conectada a la segunda entrada del multiplicador analógico. La entrada del tercer circuito de ajuste P se conecta a la salida del multiplicador analógico. La salida del tercer circuito de ajuste P está conectada a la salida del circuito TAPA. El circuito receptor de matriz activa comprende además medios para controlar independientemente el ajuste de todos los circuitos de ajuste P y ajuste A que éste incluye.

De acuerdo con otra realización de la presente invención, se proporciona un circuito para uso en receptores y transmisores de matriz activa que comprende un bus BDS con dos árboles BDS, una red de distribución extra y una pluralidad de circuitos TAPA conectados a los dos árboles BDS y a la red de distribución extra. La red de distribución extra lleva una señal idéntica a la señal del segundo árbol BDS pero se desplaza noventa grados en fase en comparación con la señal del segundo árbol BDS en todos los lugares donde los circuitos TAPA se conectan a los árboles BDS y a la red de distribución extra respectivamente. Cada circuito TAPA tiene terminales de señal de entrada primero, segundo y tercero conectados al primer árbol BDS del bus BDS, a la red de distribución adicional y al segundo árbol BDS del bus BDS, respectivamente. Cada circuito TAPA tiene un terminal de señal de salida, que proporciona la salida para el circuito de esta realización. Cada circuito TAPA comprende un multiplicador analógico con una primera y una segunda entradas y una salida y un primer y segundo circuitos de ajuste de A/P. La salida del multiplicador analógico está conectada a la salida del circuito TAPA. El primer circuito de ajuste de A/P tiene una primera y una segunda entradas conectadas a la primera y segunda entradas TAPA, respectivamente, y una salida conectada a la primera entrada del multiplicador analógico. El segundo circuito de ajuste de A/P tiene una entrada conectada al tercer terminal de señal del circuito TAPA y una salida conectada a la segunda entrada del multiplicador analógico. El primer circuito de ajuste de A/P comprende medios para escalar en magnitud sus señales de entrada y agregarlas. El circuito de esta realización comprende, además. medios para controlar independientemente el ajuste de todos los circuitos de ajuste de A/P que éste incluye.

De acuerdo con otra realización de la presente invención, se proporciona un circuito para uso en receptores y transmisores de matriz activa que comprende un bus BDS con dos árboles BDS y una pluralidad de circuitos de conversión de frecuencia ascendente/descendente conectados a los dos árboles BDS. Cada circuito de conversión de frecuencia ascendente/descendente tiene terminales de señal de entrada primero, segundo y tercero y un terminal de señal de salida que proporciona una salida del circuito de esta realización. El primer terminal de señal de entrada del circuito de conversión de frecuencia ascendente/descendente está conectado al primer árbol BDS y el segundo terminal de señal de entrada del circuito de conversión de frecuencia ascendente/descendente está conectado al segundo árbol BDS. Cada circuito de conversión de frecuencia ascendente/descendente comprende un primer, segundo y tercer circuito de ajuste de A/P, mezcladores primero y segundo, y un bloque de procesamiento analógico. El primer circuito de ajuste de A/P tiene una entrada conectada al primer terminal de señal de entrada del circuito de conversión de frecuencia ascendente/descendente y una salida conectada a la primera entrada del primer mezclador. El segundo circuito de ajuste de A/P tiene una entrada conectada al segundo terminal de señal de entrada del circuito de conversión de frecuencia ascendente/descendente y una salida conectada a la primera entrada del segundo mezclador. El primer mezclador tiene una primera y una segunda entrada y una salida. La segunda entrada del primer mezclador es una entrada del circuito de esta realización. La salida del primer mezclador está conectada a la entrada del bloque de procesamiento analógico. El bloque de procesamiento analógico tiene una entrada y una salida y proporciona una función de filtrado lineal. La salida del bloque de procesamiento analógico está conectada a la segunda entrada del segundo mezclador. El segundo mezclador tiene una primera y una segunda entrada y una salida conectada a la entrada del tercer circuito de ajuste A/P. El tercer circuito de ajuste de A/P tiene una entrada y una salida conectadas a la salida del circuito de conversión de frecuencia ascendente/descendente. El circuito de esta realización comprende además medios para controlar independientemente el ajuste de todos los circuitos de ajuste de A/P que éste incluye.

5

10

15

20

En general, en un aspecto, la invención caracteriza un sistema transmisor para una matriz de elementos de antena, 25 incluyendo el sistema transmisor: una red de señalización bidireccional (BDS) que incluye una primera red para transportar una primera señal de portadora y una segunda red para transportar una segunda señal de portadora, y que tiene un conjunto de n pares de ubicación sincrónica de fase (ai, bi), cada uno correspondiente a una ubicación ai, en la primera red y una ubicación bi en la segunda red; y una pluralidad de circuitos transmisores sintonizables, cada uno para manejar un elemento de antena diferente correspondiente de la matriz de elementos de antena, donde cada circuito transmisor 30 sintonizable de la pluralidad de circuitos transmisores sintonizables tiene una línea de salida para transportar una señal de salida y una primera y segunda líneas de entrada conectadas eléctricamente a la primera y segunda redes del BDS en ubicaciones de una correspondiente del conjunto de pares de ubicación sincrónica de fase. Cada circuito transmisor sintonizable incluye: un multiplicador que tiene una primera entrada conectada eléctricamente a la primera línea de entrada de ese circuito transmisor sintonizable; un circuito de ajuste de fase que tiene una entrada de control para recibir una señal de control de fase, el circuito de ajuste de fase conectado eléctricamente al multiplicador para controlar la fase de 35 la señal de salida de ese circuito transmisor sintonizable; y un circuito de ajuste de amplitud después del multiplicador y que tiene una entrada de control para recibir una señal de control de amplitud, el circuito de ajuste de amplitud para controlar la amplitud de la señal de salida de ese circuito transmisor sintonizable.

Otras realizaciones pueden incluir una o más de las siguientes características. Dentro de cada circuito transmisor sintonizable, el circuito de ajuste de fase está conectado eléctricamente al multiplicador dentro de ese circuito sintonizable para implementar una ajuste seleccionada del grupo que consiste en una primera ajuste y una segunda ajuste, teniendo la primera ajuste el circuito de ajuste de fase entre el primer línea de entrada del circuito transmisor sintonizable y la primera entrada del multiplicador, y la segunda ajuste que tiene el circuito de ajuste de fase entre la salida del multiplicador y la línea de salida del circuito transmisor sintonizable. Cada circuito transmisor sintonizable incluye además un amplificador de potencia que tiene una entrada conectada eléctricamente al circuito de ajuste de amplitud dentro de ese circuito de transmisor sintonizable y para proporcionar una señal de accionamiento al elemento de antena correspondiente de la matriz de elementos de antena.

Todavía otras realizaciones pueden incluir una o más de las siguientes características adicionales. Cada circuito transmisor sintonizable de la pluralidad de circuitos de transmisión sintonizables incluye además un mezclador de conversión ascendente que tiene una primera entrada para recibir una señal de una señal de transmisión IF, una segunda entrada para recibir una señal de la salida del multiplicador en ese circuito transmisor sintonizable, y una salida para proporcionar una señal a la línea de salida de ese circuito transmisor sintonizable. Dentro de cada circuito transmisor sintonizable de la pluralidad de circuitos del transmisor, el multiplicador dentro de ese circuito transmisor sintonizable tiene una segunda entrada conectada eléctricamente a la segunda entrada de ese circuito de transmisión sintonizable. El sistema de transmisor también incluye un mezclador de conversión ascendente para mezclar la primera señal de portadora y una señal de transmisión IF para generar la segunda señal de portadora en la segunda red de la red de BDS.

Aún otras realizaciones pueden incluir una o más de las siguientes características adicionales. Dentro de cada circuito transmisor sintonizable de la pluralidad de circuitos del transmisor, el multiplicador dentro de ese circuito del transmisor sintonizable tiene una segunda entrada conectada eléctricamente a la segunda entrada de ese circuito de transmisión sintonizable. Cada circuito transmisor sintonizable de la pluralidad de circuitos transmisores sintonizables incluye además un mezclador de conversión ascendente con una primera entrada acoplada eléctricamente a la salida del multiplicador en ese circuito de transmisión sintonizable, una segunda entrada para recibir la señal de transmisión IF, y una salida eléctrica acoplada al circuito de ajuste de amplitud en ese circuito de transmisión sintonizable. Cada circuito de transmisión

sintonizable de la pluralidad de circuitos de transmisión sintonizables (1) incluye, además, un segundo multiplicador que tiene una salida, una primera entrada y una segunda entrada conectadas eléctricamente a la segunda línea de entrada de ese circuito de transmisión sintonizable, (2) donde el primer multiplicador mencionado en ese circuito de transmisión sintonizable tiene una salida y una segunda entrada para recibir la señal de transmisión IF, y (3) en donde la primera entrada del segundo multiplicador está conectada eléctricamente a la salida del primer multiplicador mencionado en ese circuito de transmisión sintonizable.

5

10

15

20

25

30

35

40

45

50

55

60

65

En general, en otro aspecto, la invención caracteriza un sistema receptor para una matriz de elementos de antena, incluyendo el sistema receptor: una red de señalización bidireccional (BDS) que incluye una primera red para transportar una primera señal de portadora y una segunda red para transportar una segunda portadora señal, y que tiene un conjunto de n pares de ubicación sincrónica de fase (a, b,), cada uno correspondiente a una ubicación a, en la primera red y una ubicación bi en la segunda red; y una pluralidad de circuitos receptores sintonizables, cada uno para recibir entrada desde un elemento de antena correspondiente de la matriz de elementos de antena, en el que cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables tiene una línea de salida y líneas de entrada primera y segunda conectadas eléctricamente al primera y segunda redes de BDS en ubicaciones de uno de los pares de ubicación síncrónica de fase correspondientes. Cada circuito receptor sintonizable incluye: un multiplicador que tiene una primera entrada conectada eléctricamente a la primera línea de entrada de ese circuito receptor sintonizable y que tiene una salida; un circuito de ajuste de fase que tiene una entrada de control para recibir una señal de control de fase para controlar la fase de una señal que pasa a través del circuito de ajuste de fase, el circuito de ajuste de fase conectado eléctricamente al multiplicador; un mezclador que tiene una primera entrada para recibir una señal del elemento de antena correspondiente de la matriz de elementos de antena, una segunda entrada para recibir una señal de portadora local obtenida de la red BDS, y una salida; y un circuito de ajuste de amplitud que tiene una entrada, una salida y una entrada de control para recibir una señal de control de amplitud para controlar la amplitud de una señal que pasa a través del circuito de ajuste de amplitud; el circuito de ajuste de amplitud conectado a uno del mezclador para ese circuito receptor sintonizable y el multiplicador para ese circuito receptor sintonizable.

Otras realizaciones pueden incluir una o más de las siguientes características. Dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, el circuito de ajuste de fase está conectado eléctricamente al multiplicador dentro de ese circuito receptor sintonizable para implementar una ajuste seleccionada del grupo que consiste en una primera ajuste y una segunda ajuste, teniendo la primera ajuste dicho circuito de ajuste de fase entre la primera línea de entrada del circuito receptor sintonizable y la primera entrada de dicho multiplicador, y la segunda ajuste que tiene dicho circuito de ajuste de fase conectado eléctricamente a la salida de dicho multiplicador. Cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables incluye además un amplificador de bajo ruido que tiene una entrada para recibir una señal del elemento de antena correspondiente de la pluralidad de elementos de antena y una salida conectada eléctricamente a la primera entrada del mezclador en ese circuito receptor sintonizable. Dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores, el multiplicador dentro de ese circuito receptor sintonizable tiene una segunda entrada conectada eléctricamente a la segunda entrada de ese circuito receptor sintonizable. Dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, la segunda entrada del mezclador para ese circuito receptor sintonizable está conectada eléctricamente a la salida del multiplicador para ese circuito receptor sintonizable.

Todavía otras realizaciones pueden incluir una o más de las siguientes características adicionales. Dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, la entrada del circuito de ajuste de amplitud en ese circuito receptor sintonizable está conectada eléctricamente a la salida del mezclador en ese circuito receptor sintonizable. El sistema receptor incluye además una línea de señal de recepción y dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, la salida del circuito de ajuste de amplitud en ese circuito receptor sintonizable está conectada eléctricamente a la línea de señal de recepción. Dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, la salida del circuito de ajuste de amplitud para ese circuito receptor sintonizable está conectada eléctricamente a una de las redes primera y segunda de la red BDS.

Todavía otras realizaciones pueden incluir una o más de las siguientes características. Dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, la segunda entrada del mezclador para ese circuito receptor sintonizable está conectada eléctricamente a la segunda línea de entrada de dicho circuito receptor sintonizable. Dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, la segunda entrada del multiplicador en ese circuito receptor sintonizable está conectada eléctricamente a la salida del mezclador en ese circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, la salida del multiplicador para ese circuito receptor sintonizable está eléctricamente acoplada a la entrada del circuito de ajuste de amplitud para ese circuito receptor sintonizable. Dentro de cada circuito receptor sintonizable de la pluralidad de circuitos receptores sintonizables, la salida del circuito de ajuste de amplitud para ese circuito receptor sintonizable está conectada eléctricamente a una de las redes primera y segunda de la red BDS.

En general, en otro aspecto más, la invención presenta un sistema transceptor para una matriz de elementos de antena, incluyendo el sistema transceptor: una red de señalización bidireccional (BDS) que incluye una primera red para transportar una primera señal de portadora y una segunda red para transportar una segunda señal de portadora, y que tiene un conjunto de n pares de ubicación sincrónicos de fase (ai, bi), cada uno correspondiente a una ubicación ai; en la primera red y una ubicación bi en la segunda red; y una pluralidad de circuitos transceptores, cada uno para conectarse

a un elemento de antena diferente correspondiente de la matriz de elementos de antena. Cada circuito transceptor incluye: (1) un circuito transmisor para manejar el elemento de antena correspondiente de la matriz de elementos de antena, teniendo el circuito transceptor una línea de salida para transportar una señal de salida y líneas de entrada primera y segunda conectadas eléctricamente a la primera y segunda redes de los BDS en ubicaciones de uno correspondiente del conjunto de pares de ubicación sincrónicos de fase, e incluyendo un multiplicador que tiene una primera entrada conectada eléctricamente a la primera línea de entrada de ese circuito transmisor; y (2) un circuito receptor para recibir la entrada del elemento de antena correspondiente de la matriz de elementos de antena, teniendo el circuito receptor una línea de salida y líneas de entrada primera y segunda conectadas eléctricamente a la primera y segunda redes del BDS en ubicaciones de uno correspondiente de los pares de ubicación sincrónicos de fase, e incluyendo: (a) un multiplicador que tiene una primera entrada conectada eléctricamente a la primera línea de entrada de ese circuito receptor y que tiene una salida; y (b) un mezclador que tiene una primera entrada para recibir una señal del elemento de antena correspondiente de la matriz de elementos de antena, una segunda entrada para recibir una señal de portadora local obtenida de la red BDS, y una salida.

Otras realizaciones pueden incluir una o más de las siguientes características. Dentro de cada circuito transceptor de la 15 pluralidad de circuitos transceptores, la línea de salida del circuito receptor en ese circuito transceptor está conectada eléctricamente a una de las redes primera y segunda de la red BDS. Dentro de cada circuito transceptor de la pluralidad de circuitos transceptores, el circuito transmisor incluye además: un circuito de ajuste de fase que tiene una entrada de control para recibir una señal de control de fase, el circuito de ajuste de fase conectado eléctricamente al multiplicador en 20 ese circuito transmisor para controlar la fase de la señal de salida de ese circuito transmisor; y un circuito de ajuste de amplitud después del multiplicador en ese circuito transmisor y que tiene una entrada de control para recibir una señal de control de amplitud, el circuito de ajuste de amplitud para controlar la amplitud de la señal de salida de ese circuito transmisor. Dentro de cada circuito transceptor de la pluralidad de circuitos transceptores, el circuito receptor incluye además: un circuito de ajuste de fase que tiene una entrada de control para recibir una señal de control de fase, el circuito 25 de ajuste de fase conectado eléctricamente al multiplicador en ese circuito receptor para controlar la fase del señal de salida del circuito receptor; un circuito de ajuste de amplitud conectado eléctricamente a la salida del mezclador en ese circuito receptor y que tiene una entrada de control para recibir una señal de control de amplitud. Dentro de cada circuito transceptor de la pluralidad de circuitos transceptores, la salida del circuito de ajuste de amplitud dentro del circuito receptor para ese circuito transceptor está conectada eléctricamente a una de las redes primera y segunda de la red BDS. 30

Los detalles de una o más realizaciones de la invención se exponen en los dibujos adjuntos y la descripción a continuación. Otras características, objetos y ventajas de la invención serán evidentes a partir de la descripción y los dibujos, y de las reivindicaciones.

35 Breve descripción de los dibujos

10

45

65

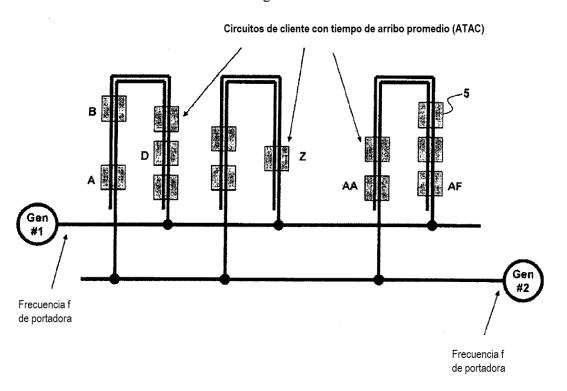

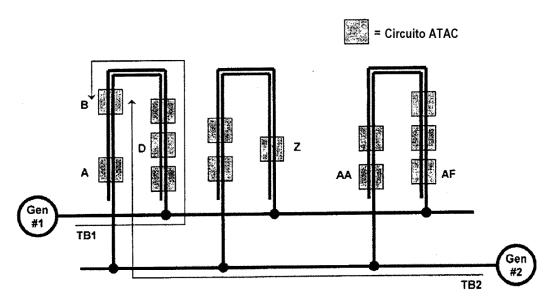

Las Figs. 1(a)-(c) representan diagramas esquemáticos de un sistema de sincronización que tiene dos redes de árbol independientes con derivaciones emparejadas, excitadas por dos generadores independientes.

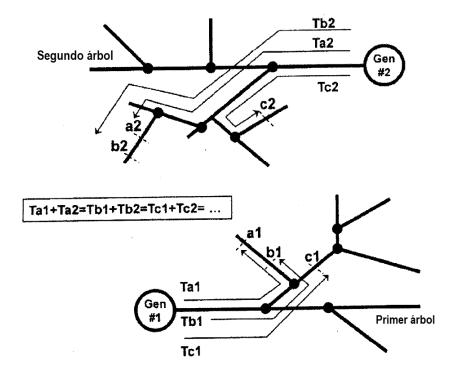

40 La Fig. 2 representa un diagrama esquemático de un sistema de sincronización que tiene dos redes de árbol generales con puntos de detección elegidos para crear pares de sincronización de fase (a1, a2), (b1, b2), (c1, c2) ... (n1, n2).

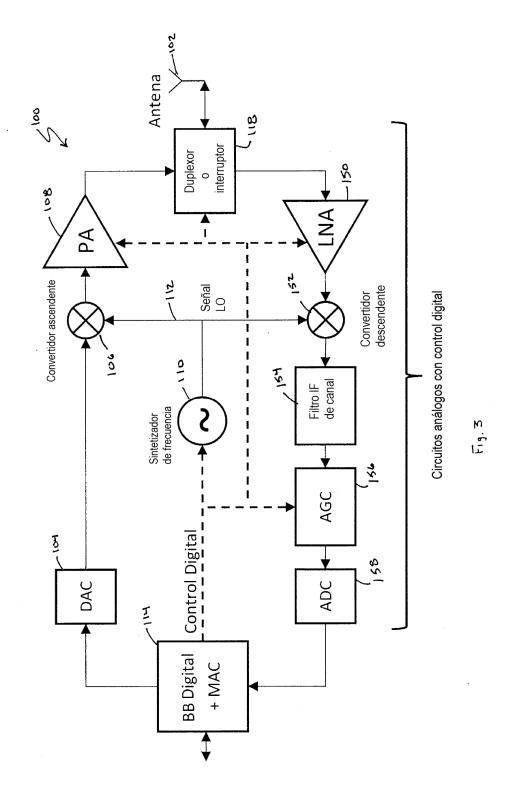

La Fig. 3 representa un diagrama esquemático de un radio transceptor inalámbrico típico que incluye mezcladores de conversión ascendentes (convertidor ascendente), mezcladores de conversión descendentes (convertidor descendente), amplificador de potencia (PA), amplificador de bajo ruido (LNA), sintetizador de frecuencia (Sintetizador de frecuencia) generando señales de oscilador local (LO), filtros de canal receptor (filtro IF de canal), amplificadores de control de ganancia automática de receptor (AGC), convertidores digitales de datos digital a analógico (DAC) de transmisor, convertidores de datos analógico a digital (ADC) de receptor y hardware de procesamiento digital (Digital BB + MAC).

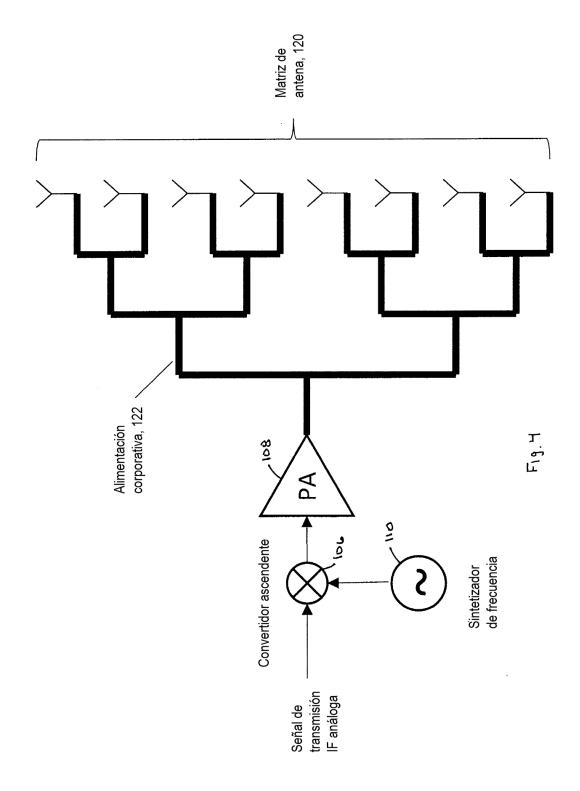

La Fig. 4 representa un diagrama esquemático de un transmisor inalámbrico para un sistema de antenas de matriz por fase con señal de salida PA distribuida a través de una alimentación corporativa, y sin control de amplitud o fase para señales transmitidas por antena.

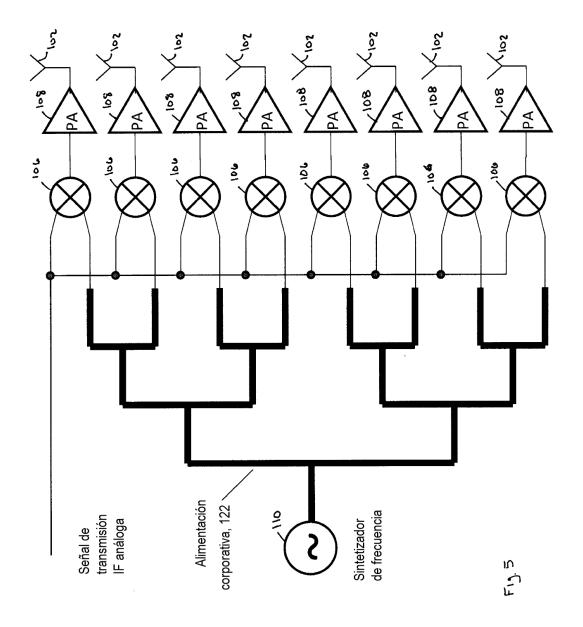

La Fig. 5 representa un diagrama esquemático de un transmisor inalámbrico para un sistema de antenas de matriz en fase con señal LO distribuida a través de una alimentación corporativa, con conversión ascendente de señal de frecuencia intermedia (IF) en cada antena individual, con PA en cada antena individual, y sin amplitud o control de fase para señales transmitidas por antena.

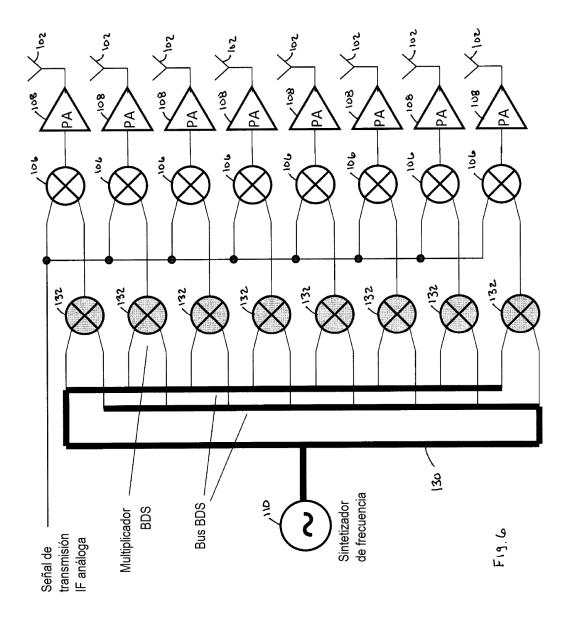

La Fig. 6 representa un diagrama esquemático de un transmisor inalámbrico para un sistema de antenas de matriz en fase con señal LO distribuida a través de un sistema BDS, con conversión ascendente de señales IF en cada antena individual, con PA en cada antena individual, y sin amplitud o control de fase para las señales transmitidas por antena.

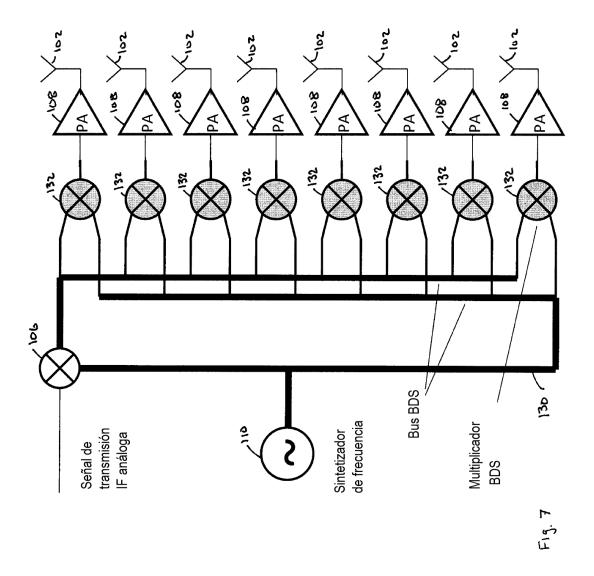

La Fig. 7 representa un diagrama esquemático de un transmisor inalámbrico para un sistema de antenas de matriz en fase con señal LO y señal IF distribuida a través de un sistema BDS, con PA en cada antena individual, y sin amplitud o control de fase para señales transmitidas por antena.

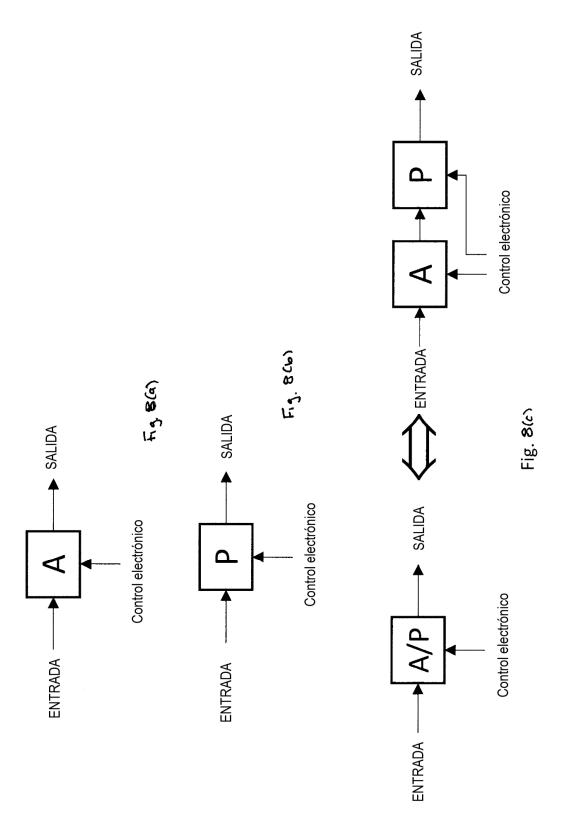

La Fig. 8(a)-(c) ilustran los circuitos de Ajuste de A, de Ajuste de P y de Ajuste A/P.

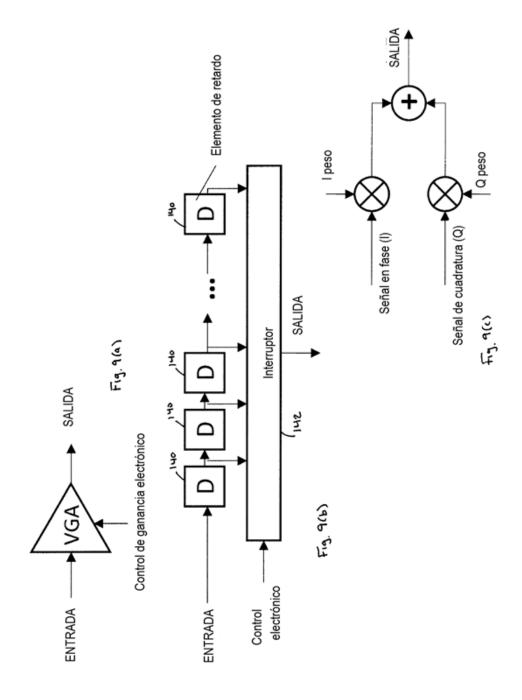

Las Figs. 9(a)-(c) representan diagramas esquemáticos para posibles implementaciones de los circuitos de Ajuste A y Ajuste de P.

5

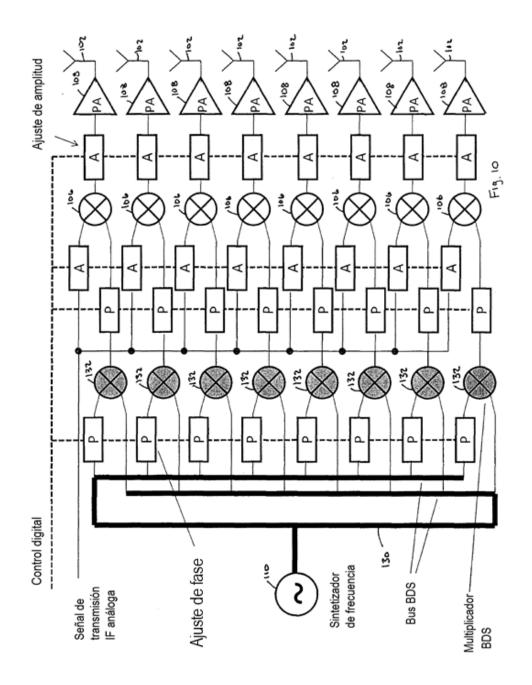

La Fig. 10 representa un diagrama esquemático de un transmisor inalámbrico para un sistema de antenas de matriz de fases con señal LO distribuida a través de un sistema BDS, con conversión ascendente de señales IF en cada antena individual, con PA en cada antena individual, y con amplitud o control de fase para las señales transmitidas por antena.

10

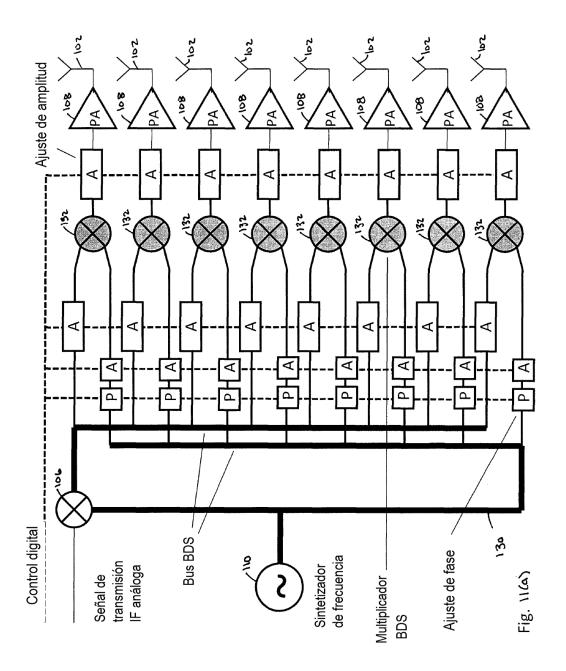

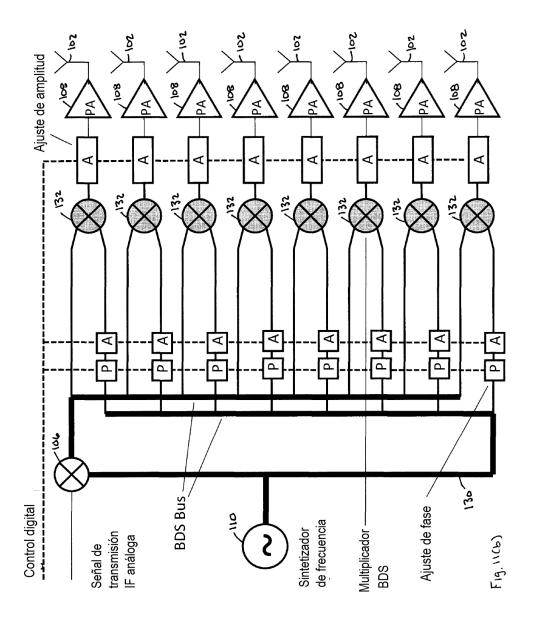

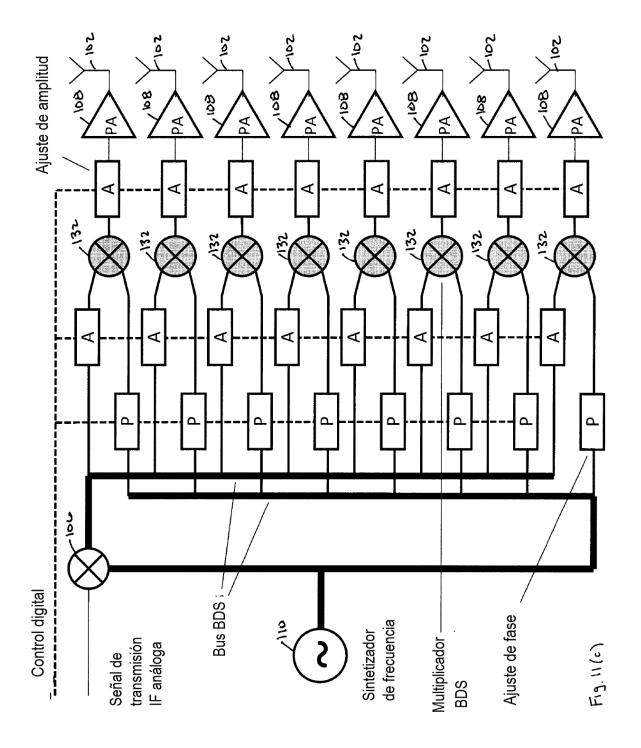

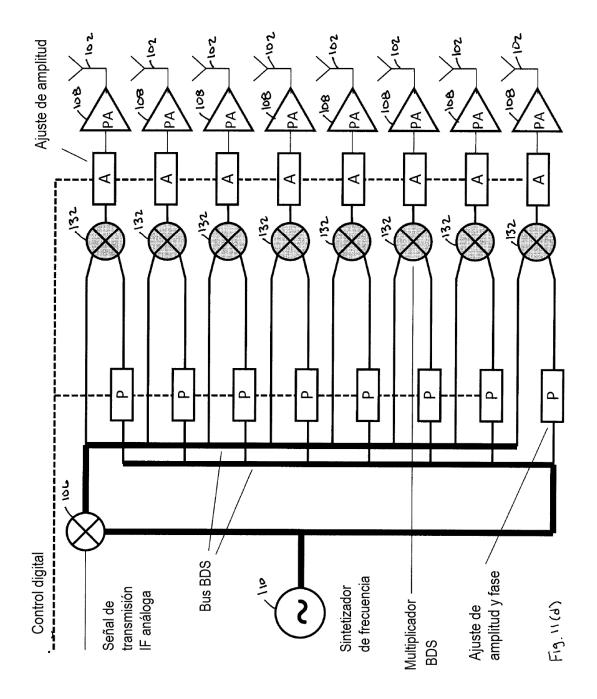

La Figs. 11(a)-(d) representan diagramas esquemáticos de diversos transmisores inalámbricos para un sistema de antena de matriz por fase con señal LO y señal IF distribuida a través de un sistema BDS, con PA en cada antena individual, y con control de amplitud o fase para las señales transmitidas por antena.

15

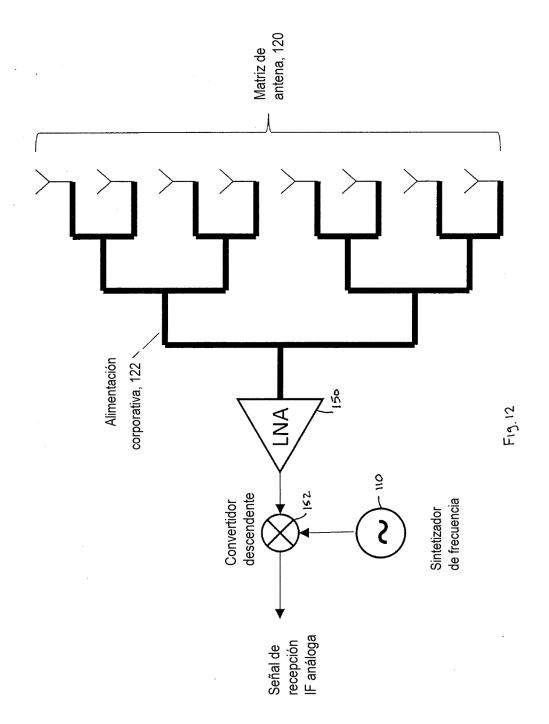

La Fig. 12 representa un diagrama esquemático de un receptor inalámbrico para un sistema de antenas con matriz por fase con señal de entrada LNA acumulada a través de una alimentación corporativa, y sin control de amplitud o fase para señales recibidas por antena.

20

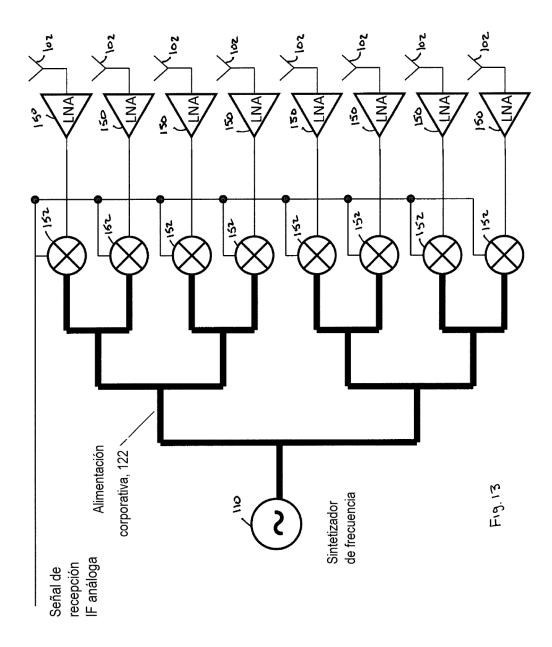

La Fig. 13 representa un diagrama esquemático de un receptor inalámbrico para un sistema de antenas de matriz en fase con señal LO distribuida a través de una alimentación corporativa, con conversión de señal IF en cada antena individual, con LNA en cada antena individual, y sin control de amplitud o fase para las señales recibidas por antena.

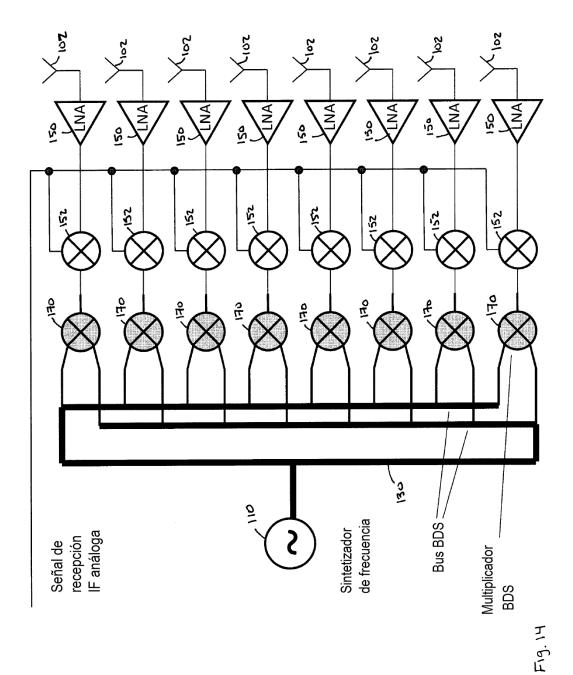

La Fig. 14 representa un diagrama esquemático de un receptor inalámbrico para un sistema de antenas de matriz por fase con señal LO distribuida a través de un sistema BDS, con conversión descendente de señal IF en cada antena individual, con LNA en cada antena individual, y sin control de amplitud o fase para las señales recibidas por antena.

25

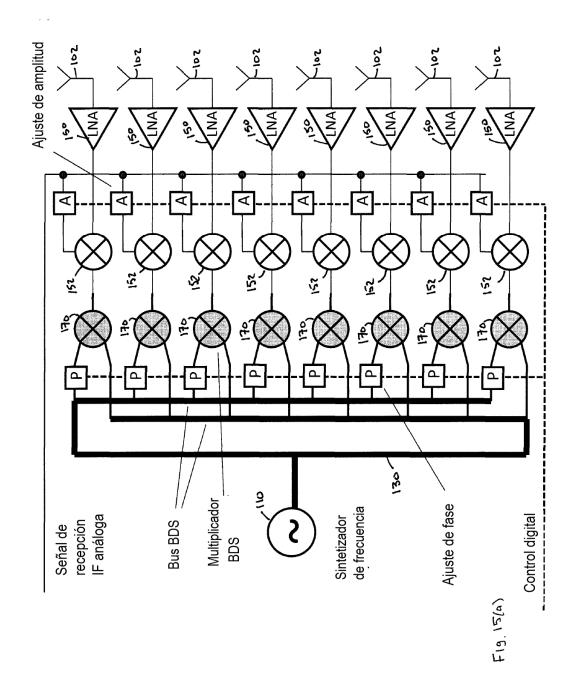

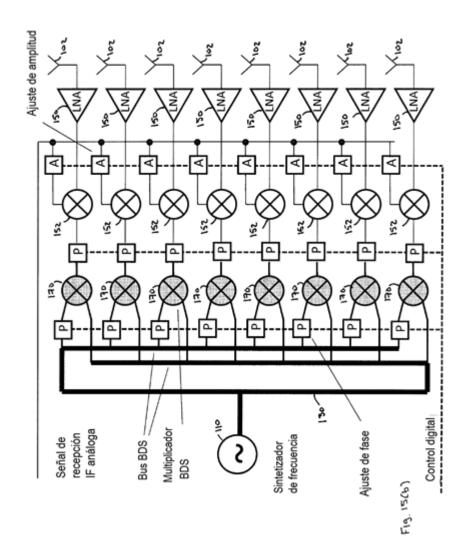

Las Figs. 15(a)-(b) representan diagramas esquemáticos de receptores inalámbricos para un sistema de antenas de matriz de fases con señal LO distribuida a través de un sistema BDS, con conversión de señal IF en cada antena individual, con LNA en cada antena individual, y con control de amplitud o fase para las señales recibidas por antena.

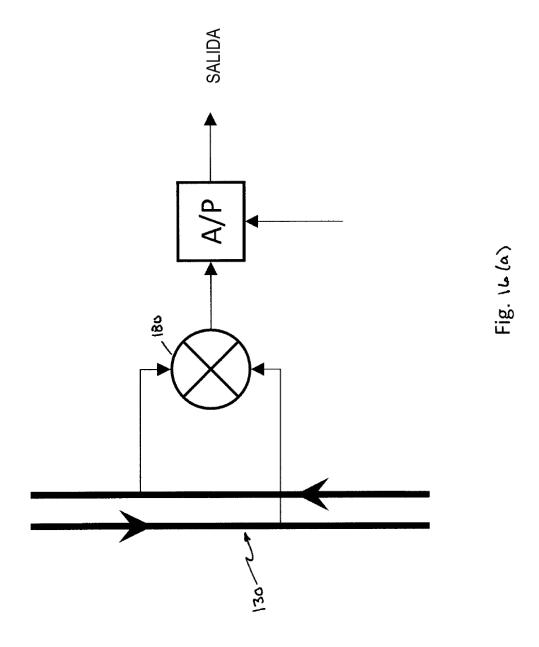

30 La Fig. 16(a) representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz por fase, con una sola multiplicación de BDS y con un circuito de ajuste de A/P después de la multiplicación de BDS.

35

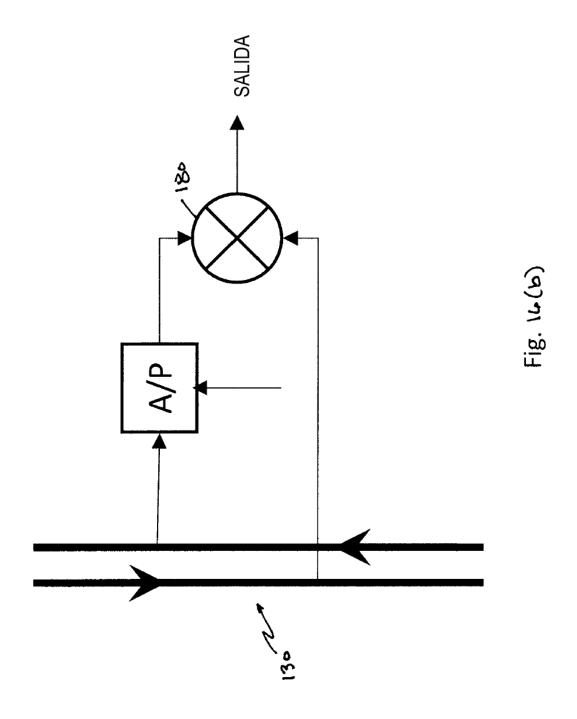

La Fig. 16(b) representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz por fase, con una única multiplicación de BDS y con un circuito de ajuste de A/P antes de la multiplicación de BDS.

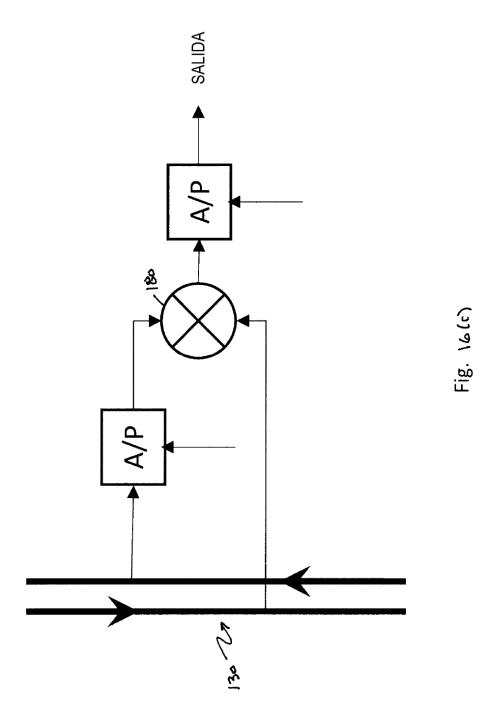

La Fig. 16(c) representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz por fases, con una sola multiplicación BDS, con un circuito de ajuste de A/P colocado antes de la multiplicación BDS y con otro circuito de Ajuste A/P colocado después de la multiplicación BDS.

40

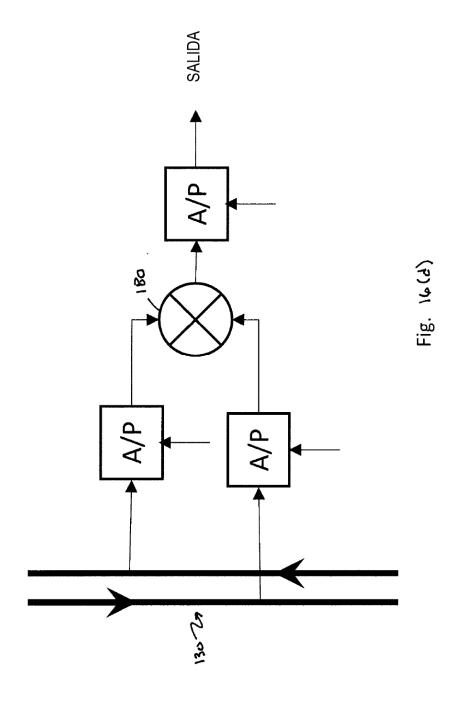

La Fig. 16(d) muestra un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz de fases, con una sola multiplicación de BDS, con dos circuitos de ajuste de A/P colocados antes de la multiplicación de BDS y con un circuito de ajuste A/P colocado después de la multiplicación BDS

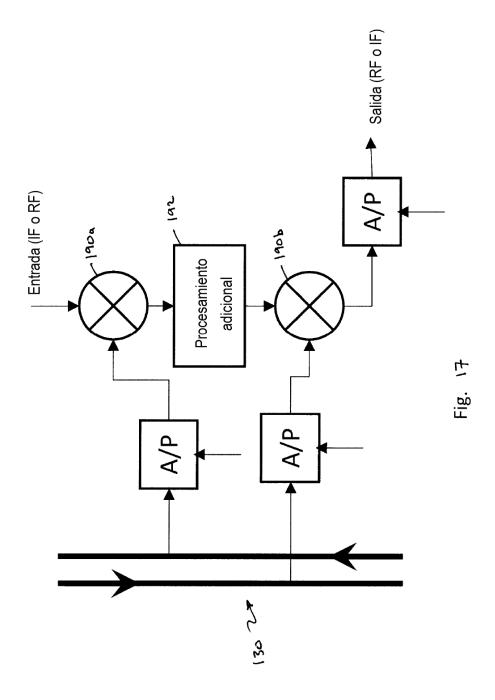

45 La Fig. 17 representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz de fases, con dos multiplicaciones, con dos circuitos de ajuste de A/P colocados antes de la multiplicación y con un circuito de ajuste de A/P colocado después de multiplicaciones.

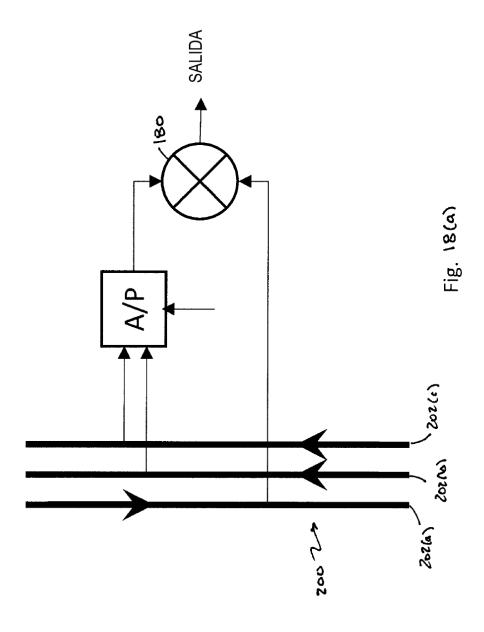

La Fig. 18(a) representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de 50 matriz de fases, con una multiplicación de BDS y con un circuito de ajuste de A/P colocado antes de la multiplicación de BDS, el circuito de ajuste de A/P recibe dos señales de entrada iguales pero desfasadas.

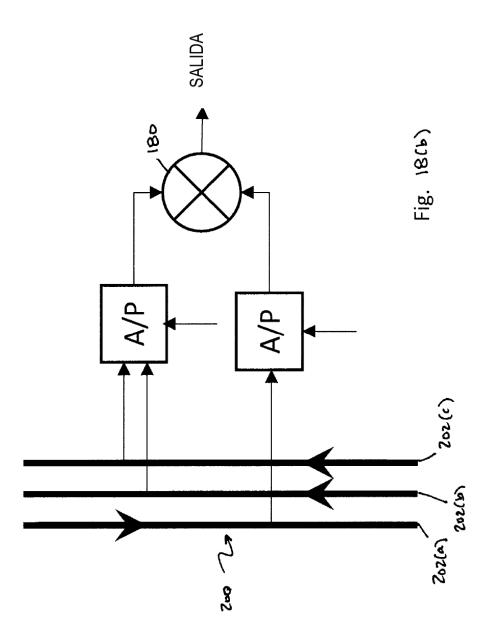

La Fig. 18(b) representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz de fases, con una multiplicación de BDS y con dos circuitos de ajuste de A/P colocados antes de la multiplicación de BDS, un circuito de ajuste de A/P recibe dos señales de entrada iguales pero desfasadas.

55

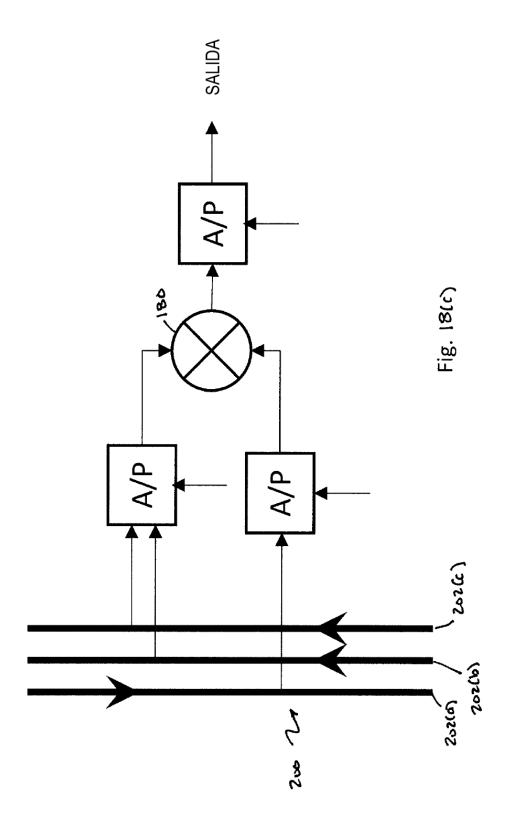

La Fig. 18(c) representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz por fases, con una multiplicación BDS, con dos circuitos de ajuste de A/P colocados antes de la multiplicación BDS, un circuito de juste de A/P recibe dos señales de entrada iguales pero desfasadas, y con un circuito de ajuste de A/P colocado después de la multiplicación de BDS.

60

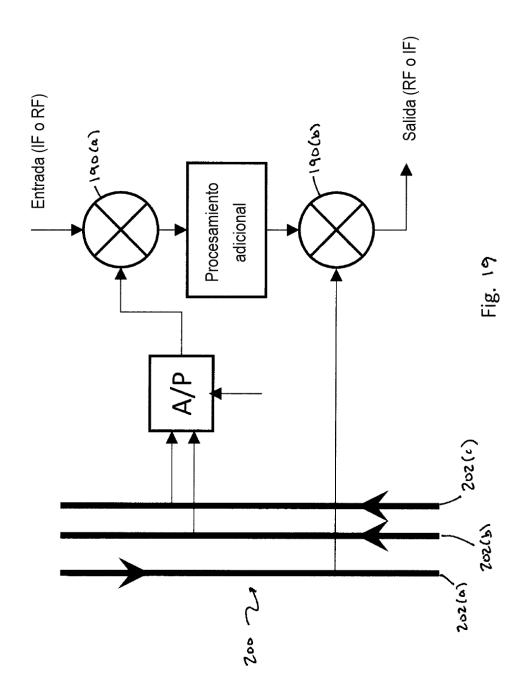

La Fig. 19 representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz por fases, con dos multiplicaciones y con un circuito de ajuste de A/P colocado antes de la multiplicación, recibiendo el circuito de ajuste de A/P dos señales de entrada iguales pero desfasadas.

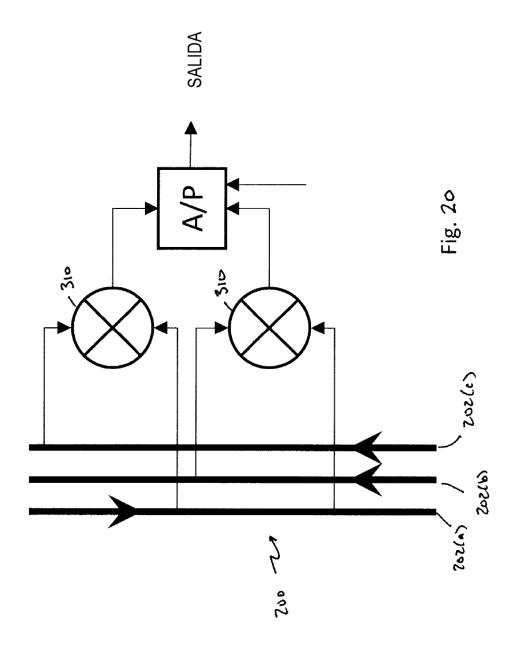

- La Fig. 20 representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz por fases, con dos multiplicaciones BDS, cada multiplicación BDS recibe pares de señales BDS independientes y con un circuito de ajuste de A/P colocado después de multiplicaciones BDS.

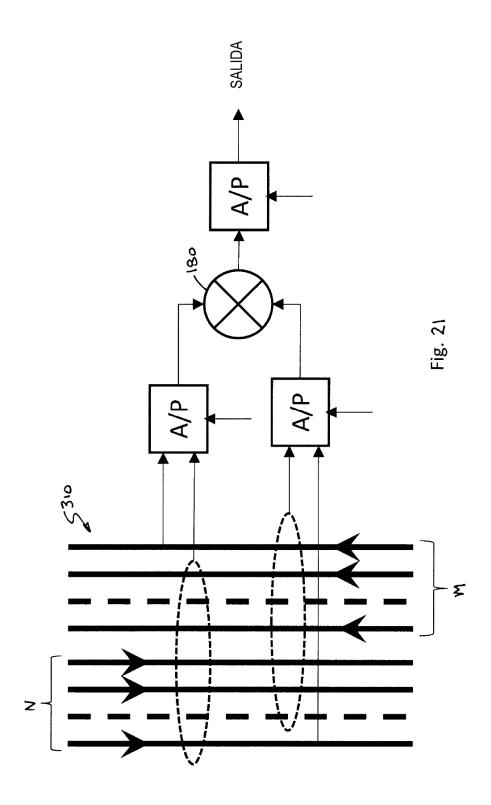

- La Fig. 21 representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz por fases, con una multiplicación BDS, con dos circuitos de ajuste de A/P colocados antes de la multiplicación BDS, recibiendo los circuitos de ajuste de A/P múltiples pares de señales BDS y múltiples señales iguales pero desfasadas, y con un circuito de ajuste A/P colocado después de la multiplicación BDS.

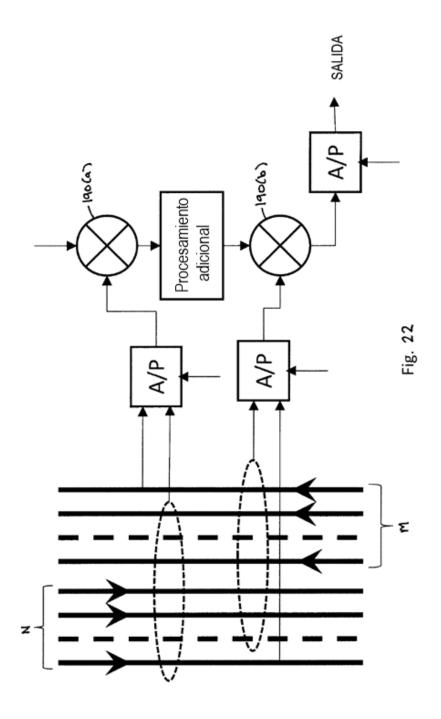

- La Fig. 22 representa un diagrama esquemático de un circuito TAPA, que puede usarse en un sistema de antenas de matriz de fases, con dos multiplicaciones BDS, con dos circuitos de ajuste de A/P colocados antes de la multiplicación BDS, recibiendo los circuitos de ajuste de A/P múltiples pares de señales BDS y múltiples señales iguales pero desfasadas, y con un circuito de ajuste de A/P colocado después de la multiplicación BDS.

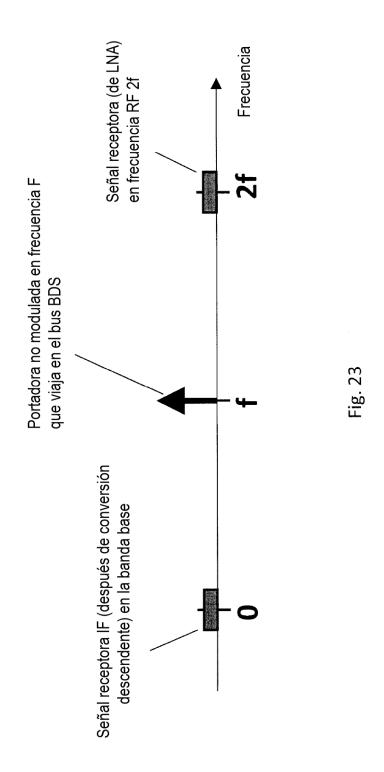

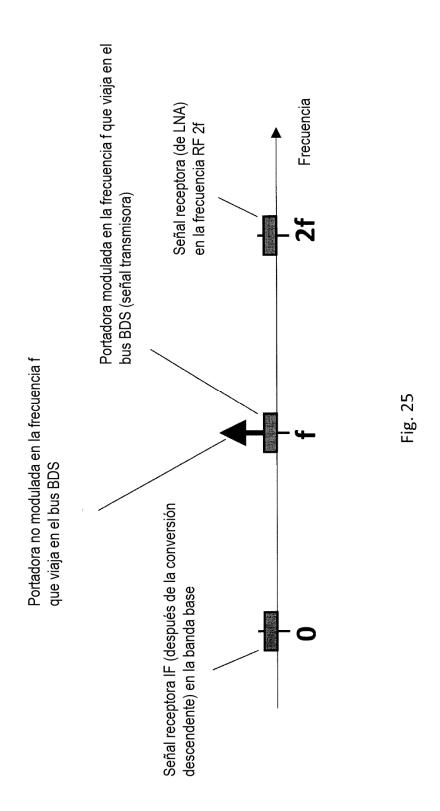

- 15 La Fig. 23 representa el plan de frecuencias para los receptores en las Figs. 14, 15(a)-(b) suponiendo una conversión directa.

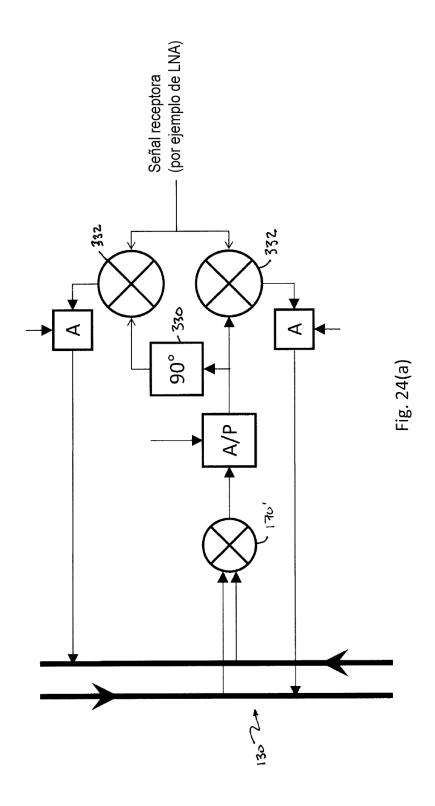

- La Fig. 24(a) representa un receptor en el que el bus BDS se usa para transportar señales BDS y agregar y transportar señales IF.

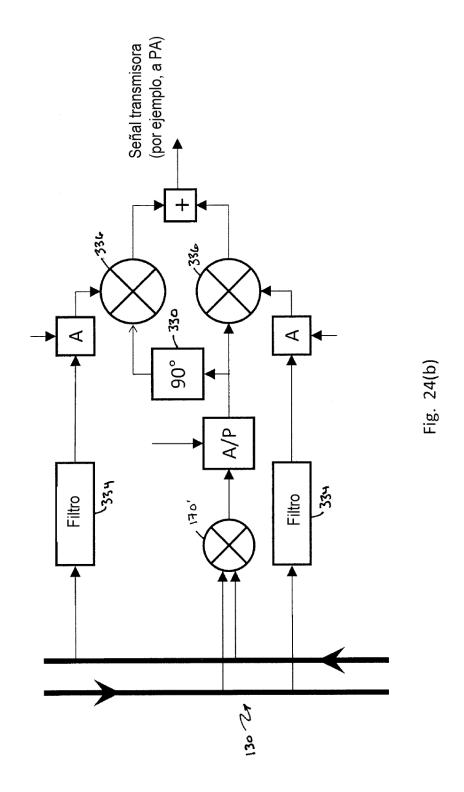

- La Fig. 24(b) representa un transmisor en el que el bus BDS se usa para transportar señales BDS y transportar las señales IF del transmisor.

- La Fig. 25 representa el plan de frecuencia en la figura 23 con señalización BDS modulada.

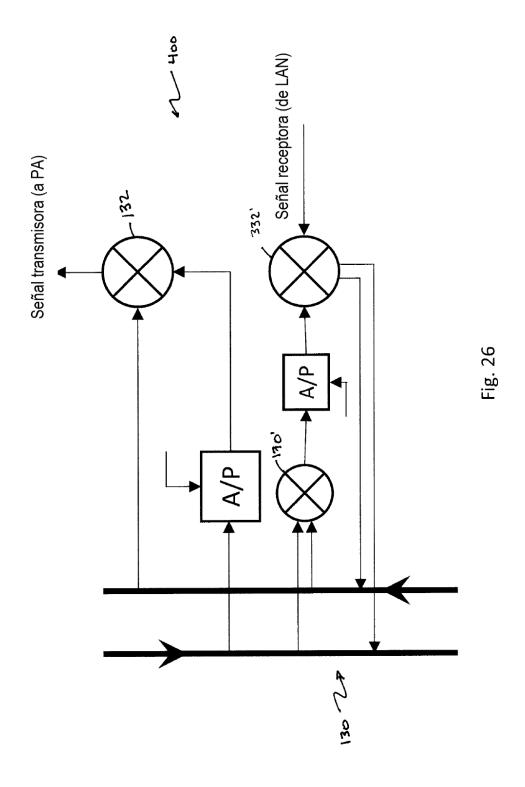

- La Fig. 26 representa un transceptor TDD en el que el bus BDS se usa para transportar señales BDS moduladas y agregar y transportar señales IF.

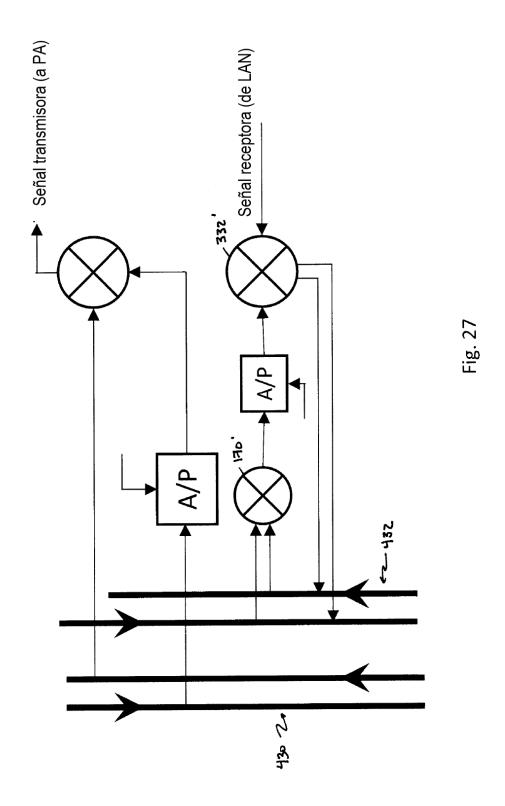

- La Fig. 27 representa un transceptor FDD en el que se usa un primer bus BDS para transportar señales BDS moduladas y un segundo bus BDS se usa para agregar y transportar las señales IF del receptor.

- Los títulos utilizados en este documento son solo para fines de organización y no están destinados a ser utilizados para limitar el alcance de la descripción o las reivindicaciones. Tal como se usa a lo largo de esta solicitud, la palabra "puede" se usa en un sentido permisivo (es decir, que significa que tiene el potencial para), en lugar del sentido obligatorio (es decir, significando debe). De manera similar, las palabras "incluir", "que incluye" e "incluyen" significan, pero no se limitan a incluir. Para facilitar la comprensión, se han utilizado los mismos números de referencia, siempre que sea posible, para designar elementos similares comunes a las Figuras.

#### Descripción detallada

20

25

35

40

55

- Antes de presentar descripciones detalladas de varias realizaciones de la invención, es útil entender primero el funcionamiento del concepto de distribución de señal bidireccional que se usará en esas diversas realizaciones.

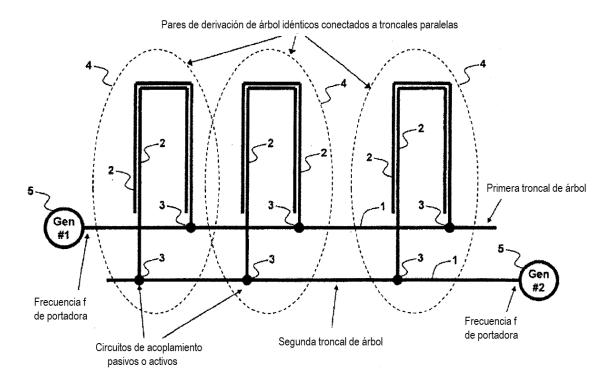

- La Fig. 1(a) muestra un diagrama esquemático de dos redes de árboles independientes, cada una de las cuales consiste en una troncal de árbol 1 y derivaciones de árbol 2. Nos referiremos a esto más abajo generalmente como un bus BDS (señalización bidireccional). La troncal de árbol y las derivaciones de árbol de cada una de las redes de árbol son líneas de transmisión de señal terminadas adecuadamente (los circuitos de terminación no se muestran en la fig. 1(a) por simplicidad), tales como líneas eléctricas de microbanda, guías de ondas ópticas, guías de propagación de sonido o sencillos rastreos eléctricos. La diferencia entre la troncal 1 y las derivaciones 2 no es sustancial, sino más bien de nombre, en función de la posición relativa de las líneas de transmisión de señal (TL) con respecto al puerto de entrada de la red del árbol. Troncal 1 se define como la línea de transmisión de señal conectada directamente al puerto de entrada. Las derivaciones 2 están acopladas a la troncal 1 a través de circuitos 3 pasivos o activos. Se supone que los retardos de señal a través de estos circuitos de acoplamiento son idénticos para todos los circuitos de acoplamiento o en relaciones conocidas entre sí.

- Las redes de árbol descritas con respecto a la fig. 1(a) son casos particulares de una clase más grande de redes de árbol a las que se hace referencia en este documento como redes de árbol TL. En general, una red de árbol TL tiene una troncal, que es un TL acoplado a la entrada del árbol TL, y muchas derivaciones, que son TL acopladas a la troncal o a otras derivaciones. El nivel de la red de árbol TL es el mayor número de derivaciones a través del cual una señal aplicada en la entrada del árbol TL viaja más uno (contando la troncal como una derivación). Por ejemplo, los árboles TL en la Fig. 1 son árboles de dos niveles (las señales de entrada viajan a través de una troncal y una derivación).

- Las dos redes de árboles en la fig. 1(a) tienen troncales paralelas que se extienden cerca unas de otras y sus derivaciones están emparejadas de manera que todos los pares 4 tienen una estructura física sustancialmente idéntica. La posición donde cada par de derivaciones se conecta a las troncales paralelas no es crítica. Las dos derivaciones en cada par están muy cerca la una de la otra (por ejemplo, paralelas o que se conforman la una a la otra).

Dos generadores 5 aplican señales de entrada a las redes de árbol en la fig. 1(a). Las señales del generador pueden ser portadoras moduladas o no moduladas de frecuencia f. Entonces, por ejemplo, en la señal generada podría ser una portadora no modulada de frecuencia f y la otra señal generada podría ser una portadora modulada de frecuencia f. Una portadora es cualquier señal periódica cuando la modulación no está presente (modulación cero) y la frecuencia de la portadora es la frecuencia de la portadora cuando la modulación no está presente. Cuando la modulación está presente, tal como la modulación de fase o frecuencia, la portadora generalmente no es una señal periódica.

También nótese que, si solo se transportan señales de portadora no moduladas a ambos lados del bus BDS, se puede usar un generador en lugar de dos. En ese caso, el generador está conectado a la entrada de un árbol y un extremo de ese árbol está conectado a la entrada del segundo árbol.

El sistema de distribución de señal que se muestra en la figura 1(b) incluye un número de bloques de circuitos sustancialmente idénticos llamados "cliente promediando tiempo de llegada" o circuitos ATAC conectados a la red. El bloque 6 representa uno de los circuitos ATAC en la fig. 1a. Otros circuitos ATAC en la fig. 1a están etiquetados como A, B, D, Z, AA y AF.

Cada circuito ATAC tiene dos entradas y una salida. Las entradas del circuito ATAC están conectadas en la misma ubicación a una derivación diferente del par de derivaciones. Algunos de los circuitos ATAC se pueden conectar en orden inverso a los demás. Por ejemplo, si el orden de conexión "normal" se define como la primera entrada del circuito ATAC conectado a la primera red de árbol y la segunda entrada del circuito ATAC conectado a la segunda red de árbol, entonces algunos de los circuitos ATAC pueden estar conectados con su primera entrada conectada a la segunda red de árbol y sus segundas entradas conectadas a la primera red de árbol.

Se supone que los circuitos ATAC no cargan las líneas de transmisión que forman las derivaciones de los árboles de manera significativa. En otras palabras, se supone que las señales que viajan en cada árbol no son perturbadas por la presencia de los circuitos ATAC. Como una aclaración adicional, si el sistema en la fig. 1(b) es puramente eléctrico, la impedancia de entrada de los circuitos ATAC se asume grande con respecto a la impedancia característica de las líneas de transmisión de modo que los circuitos ATAC solo detectan los voltajes o corrientes en las derivaciones sin efectos significativos en las señales del árbol. Esta suposición es razonable en la práctica si la cantidad de circuitos ATAC no es excesiva.

Cuando las señales del generador son pulsos periódicos (modulación cero), los pulsos llegan a las dos entradas del circuito ATAC en diferentes momentos. El circuito ATAC genera pulsos de salida en el medio del período entre los dos pulsos de entrada, de ahí el nombre del circuito. En otras palabras, los pulsos de salida del circuito ATAC se colocan en el tiempo promedio entre los tiempos de llegada de los pulsos de entrada. La funcionalidad del circuito ATAC para el caso de pulsos periódicos se describe como en los circuitos de extracción de reloj en más detalle en Wayne D. Grover "Method and Apparatus for Clock Distribution and for Distributed Clock Synchronization" U.S. Pat. No. 5,361,277, Nov. 1, 1994; Michael Farmwald and Mark Horowitz, "Apparatus for Synchronously Generating Clock Signals in a Data Processing System" U.S. Pat. No. 5,243,703, Sep. 7, 1993; and Charles D. Miller "Signals Distribution System" Pat. U.S. No.

5,243,703, 7 de septiembre de 1993; y Charles D. Miller "Signals Distribution System", U.S Pat.No. 5,712,882, del 27 de enero de 1998. Las implementaciones practicas incluyen los circuitos, PLL y DLL.

Las salidas de los circuitos ATAC en el sistema de la fig. 1(b) tienen portadores sincrónicos de fase. Que esto es cierto se puede apreciar más plenamente a partir del siguiente análisis. Para simplificar, considere el caso de las señales del generador, que son periódicas y no tienen modulación. La Fig. 1(b) también muestra las diferentes rutas y tiempos de propagación de señal específicamente indicados. Los circuitos ATAC etiquetados como A, B, C, Z, AA, AF se denominarán Cliente A, B, C, etc.

Con referencia a la Fig. 1(b), los tiempos de propagación de señal desde las entradas de árbol al Cliente B son TB1 y TB2. Definimos un parámetro llamado "Tiempo de Vuelo de Sincronización" o SFT como la suma de TB1 y TB2:

SFT = TB1 + TB2

15

35

40

50

55

60

65

La Fig. 1(c) muestra las rutas de señal al Cliente D y los tiempos de recorrido de señal asociado TD1 y TD2. Estas dos cantidades pueden expresarse en términos de TB1 y TB2 de la siguiente manera:

TD1 = TB1 - ΔT1

$TD2 = TB2 + \Delta T1$

La cantidad ΔT1 es el tiempo de viaje de la señal en las derivaciones del árbol entre las posiciones de los Clientes B y D. Agregando las dos relaciones anteriores, tenemos:

TD1 + TD2 = SFT

Nótese que esta relación se derivó sin suposiciones específicas con respecto a la posición del Cliente D en su par de derivación. Por lo tanto, para el par de derivación considerado, SFT es una constante. Mediante argumentos similares, se puede demostrar que todos los pares de derivaciones tienen un SFT constante. Además, se puede mostrar que el SFT de todos los pares de derivación tienen el mismo valor y, por lo tanto, SFT es una constante del sistema.

Por lo tanto, se puede concluir que para el sistema de distribución en la fig. 1(a) (por ejemplo, líneas paralelas muy próximas entre sí), todos los clientes (circuitos ATAC) colocados en una posición arbitraria en los pares de derivaciones detectan señales cuyo tiempo de viaje total combinado desde sus respectivos generadores es una constante (SFT). El tiempo medio de llegada del impulso es una instancia de tiempo absoluta igual a la mitad del valor de SFT (suponiendo que el tiempo cero se define en la instancia en que el generador genera pulsos). Por lo tanto, todas las salidas de Cliente están en sincronización de fase precisa. Esta propiedad es independiente de los tiempos de generación de impulsos.

Aunque los Clientes en el sistema de la Fig. 1(a) están posicionados en diferentes coordenadas en el espacio, sus salidas están en alineación de fase precisa si las entradas son señales periódicas, es decir, portadoras no moduladas. La adición de una modulación de ángulo cuyo ancho de banda es pequeño con respecto a la portadora, no cambia el comportamiento práctico del sistema de ninguna manera significativa.

Como SFT es un sistema invariante, cualquier función de SFT también es invariante. Por esta razón, en general, se puede usar cualquier circuito de cliente que produzca una salida, que es una función de SFT, para obtener la sincronización de fase global. Para mayor claridad, el término "función" aquí no se refiere a ninguna fórmula específica sino al concepto matemático general que asocia un único valor para cada elemento (por ejemplo, número) de un conjunto fijo.

Un circuito que implementa una función de SFT se denomina Cliente de sincronización o "Cliente S". Los circuitos ATAC son casos particulares de todos los posibles Clientes S. Un simple cliente S, que no es un circuito ATAC, sería un bloqueo DLL (Bucle Bloqueado de retraso) en un desfase de tiempo constante de los tiempos de llegada de pulso promedio. El retardo de tiempo constante ΔT puede derivarse del período de los trenes de pulsos que viajan a través de las dos redes. Otros ejemplos de Clientes S para el caso en que se usan señales de portadoras sinusoidales son multiplicadores analógicos, ejemplos de los cuales se pueden encontrar en NRAO, A Proposal for Very Large Array Radio Telescope, vol. II, Observatorio Nacional de Radioastronomía, Green Bank, W. Va., Ch. 14, 1967; y Richard R Goulette "Technique for Distributing Common Phase Clock Signals", U.S. Pat. N° 6,531,358 B1, 13 de mayo de 2003, Otros ejemplos incluyen multiplicadores analógicos con desfases de fase.

Para apreciar por qué un multiplicador es útil para generar un tiempo sincrónico a partir de las dos señales de portadora en el bus BDS, considere lo siguiente. El multiplicador toma como dos entradas una primera señal portadora en la primera línea en el punto X y una segunda señal portadora en la segunda línea también en el punto X. En relación con un punto de referencia dentro del bus dual, la primera señal portadora se desplaza en fase en una cantidad  $-\Delta \phi$  y la segunda señal de portadora se desplaza en fase en una cantidad  $+\Delta \phi$ . Es decir, las dos señales de portadora pueden representarse con  $a_1$ sen( $\omega_0$ t +  $\phi_0$  -  $\Delta \phi$ ) y  $a_2$ sen( $\omega_0$ t +  $\phi_0$  +  $\Delta \phi$ ). Por lo tanto, el multiplicador produce como salida el producto de estas dos señales, que se representa de la siguiente manera:

$A_1 \operatorname{sen}(\omega_0 t + \varphi_0 - \Delta \varphi) \times a_2 \operatorname{sen}(\omega_0 t + \varphi_0 + \Delta \varphi) = a_1 a_2 [\cos(2\Delta \varphi) - \cos(2\omega_0 t + 2\varphi_0)]$

En otras palabras, la simple multiplicación de dos señales portadoras no moduladas en los dos puntos a igual distancia eléctrica (longitud) desde el punto medio produce un término DC  $a_1a_2\cos(2\Delta\phi)$  y un término invariante de fase  $a_1a_2\cos(2\omega_0t + 2\phi_0)$  al doble de la frecuencia de señal transmitida. El término DC se puede eliminar fácilmente a través del acoplamiento de CA y el término  $a_1a_2\cos(2\omega_0t + 2\phi_0)$  restante proporciona una señal sincronizada con una relación de fase precisa con la fase de referencia.

Con referencia de nuevo a la figura 1(a), una primera generalización del sistema ilustrado es una en la que las troncales tienen una forma distorsionada. Comenzando con el sistema original en la Fig. 1(a), uno puede distorsionar las troncales sin consecuencias para la sincronización del portador de las salidas del cliente, siempre que las troncales tengan las mismas longitudes de sección. Un efecto de cambiar la longitud de la troncal o incluso distorsionar sus formas físicas (siempre que ambas troncales tengan las mismas longitudes de sección) es un cambio de referencia de temporización global. Del mismo modo, lo mismo es cierto si todas las derivaciones están distorsionadas en longitud y forma, mientras se mantienen las mismas secciones de longitud entre dos ubicaciones.

Una generalización aún mayor es aquella en la que hay dos árboles, no iguales en forma o dimensiones, cada árbol tiene una troncal y cualquier número de derivaciones conectadas en cualquier número de niveles y con un generador que excita cada troncal de árbol, como se muestra en la Fig. 2. Uno puede elegir pares de puntos de árbol, de modo que cada par contenga un punto del primer árbol y un punto del segundo árbol. Estos pares se llaman pares de sincronización de fase. Cada par de sincronización de fase tiene un SFT único. En general, uno puede identificar muchos puntos de sincronización de fase con el mismo SFT. Por ejemplo, uno puede elegir dos puntos arbitrariamente, uno en cada árbol y formar un primer par.

65

60

5

Para este primer par particular, hay una SFT calculado como la suma del tiempo de propagación de la señal desde el generador n° 1 al primer punto del árbol en el par con el tiempo de propagación de la señal desde el generador n° 2 al segundo punto del árbol en el par. A continuación, uno puede alejarse del generador n° 1 en el primer árbol y hacia el generador n° 2 en el segundo árbol y encontrar otros pares de puntos con el mismo SFT. Además, uno puede buscar otras derivaciones y encontrar pares adicionales con el mismo SFT. Claramente, para cualquier red de árbol dual, hay muchos posibles SFT y conjuntos asociados de pares de puntos de árbol. Un conjunto de pares de sincronización con el mismo SFT se llama una colección de pares de sincronización. La Fig. 2 ilustra una colección de pares de sincronización de tres fases (a1, a2), (b1, b2) y (c1, c2).

El sistema más general en la fig. 2 se puede usar para generar señales con portador síncrono de fase basado únicamente en un subconjunto de puntos. De hecho, en general, la misma configuración de red es capaz de generar muchos conjuntos de salidas sincronizadas de portadora, cada conjunto usando una colección específica de pares de sincronización de fase. La red de la figura 1(a) es un caso especial donde todos los puntos adyacentes en las derivaciones de árbol colocadas una al lado de la otra forman una colección de pares de sincronización de fase.

Ahora describiremos cómo se emplea el concepto de señalización bidireccional para implementar transceptores para su uso con una matriz de antenas para producir patrones de haz direccionales y direccionables.

Transmisor de matriz activa basado en la distribución de señal de alimentación corporativa

15

20

25

30

35

40

La fig. 3 representa un diagrama esquemático de una típica radio 100 transceptora inalámbrica que usa una sola antena 102. La parte del transmisor incluye un convertidor 104 digital a analógico (DAC), un mezclador convertidor ascendente (convertidor ascendente) 106 y un amplificador de potencia (PA) 108. Un sintetizador de frecuencia (sintetizador de frecuencia) 110 genera la señal 112 de oscilador local (LO), utilizada por el mezclador 106 de convertidor ascendente. La señal transmitida se crea en el dominio digital por el procesador 114 de banda base (BB) y control de acceso a medios (MAC) y convertidos a formato analógico por DAC 104. La señal analógica en la salida del DAC 104 es una señal de frecuencia intermedia (IF), que es una señal modulada de una portadora IF. En general, la frecuencia portadora de IF es mucho menor que la frecuencia portadora transmitida por la antena 102. Esta restricción es impuesta por la operación del DAC. Los DAC habituales, que no son excesivamente caros, no pueden generar frecuencias de portadora muy elevadas. La frecuencia portadora se traslada hacia arriba mediante el mezclador convertidor ascendente 106 desde IF a la frecuencia de la portadora de antena, que se denominará radiofrecuencia o RF.

En los casos de IF cero o muy bajo, el transmisor incluiría dos DAC y dos mezcladores de conversores ascendentes (no mostrados en la Fig. 3). Los dos DAC recibirían dos señales independientes de los procesadores digitales, generalmente llamadas señales en fase (I) y fase en cuadratura (Q). Después de la conversión ascendente independiente de IF a RF, las señales I y Q en RF se agregarán y se aplicarán al amplificador de potencia como una sola señal combinada. La razón para usar las señales I y Q en los casos de IF cero o bajo es generar señales transmitidas por una banda lateral única, como lo requieren la mayoría de los sistemas de comunicación inalámbricos modernos. Cuando el IF es lo suficientemente alto (por ejemplo, más grande que el ancho de banda de la señal transmitida), no hay necesidad de procesar I/Q y una sola señal de IF es suficiente. El sistema representado en la fig. 3 representa el caso en el que el DAC 104 genera una señal IF que está a una frecuencia suficientemente alta para evitar la necesidad de procesamiento I/Q. En la práctica, dicho IF puede elegirse lo suficientemente bajo como para no requerir un DAC muy caro.

Se enfatiza que todas las consideraciones en esta especificación son válidas, en general, independientemente del valor IF (IF cero, IF bajo, IF medio o incluso IF muy alto). Solo por razones de simplicidad, en el caso del transmisor y en el caso del receptor (ver secciones a continuación) mostramos sistemas sin procesamiento I/Q (frecuencia IF mayor que el ancho de banda de la señal), pero las mismas soluciones y arquitecturas son válidas para los casos con procesamiento I/Q. Los casos I/Q son extensiones simples que son obvias para una persona de habilidad normal en el campo.

- La fig. 3 muestra que la señal transmitida se acopla desde la salida del amplificador de potencia 108 a la antena 102 a través de un duplexor o conmutador de antena 118. Estos dispositivos se utilizan cuando un transmisor y un receptor están conectados eléctricamente a la antena. Típicamente, un duplexor se usa en sistemas de multiplexación por división de frecuencia (FDD), cuando los RF de transmisión y recepción son diferentes. El duplexor es un filtro pasivo que aísla mutuamente las rutas de transmisión y de recepción, mientras que la antena está conectada eléctricamente a los circuitos de transmisión y recepción en todo momento. Típicamente, un interruptor de antena se usa en sistemas de multiplexación por división de tiempo (TDM) con los mismos RF de recepción y transmisión. En el modo de transmisión, la antena está conectada eléctricamente solo al receptor.

- (Nótese que a lo largo de la descripción contenida en este documento cuando se dice que un elemento está conectado o conectado eléctricamente a otro elemento, a menos que se indique específicamente lo contrario, podría ser a través de un elemento intermedio. En otras palabras, a menos que se indique explícitamente lo contrario, no debe implicar solo una conexión directa).

- Si en lugar de aplicar la señal transmitida a una sola antena, aplicamos la señal transmitida a múltiples antenas (por ejemplo, matriz de antena), podríamos usar el sistema transmisor ilustrado en la fig. 4, que es típico para las matrices en

fase clásicas. Como este caso ilustra solo un transmisor, no es necesario incluir un duplexor o un interruptor de antena. Estos dispositivos estarían presentes si se agregara un receptor al diagrama.

La señal de salida del amplificador de potencia se distribuye a cada elemento de antena de una matriz 120 de antena mediante una alimentación corporativa 122. Una alimentación corporativa se describió anteriormente en términos generales. La alimentación corporativa particular ilustrada en la fig. 4 tiene una arquitectura de árbol binario. Como se ilustra, la alimentación corporativa 122 primero divide la señal de salida del amplificador 108 de potencia en dos señales teóricamente idénticas, luego divide de nuevo cada señal resultante en dos señales teóricamente idénticas, y así sucesivamente hasta que todas las antenas reciban señales idénticas. El principal desafío práctico en la fabricación de alimentaciones corporativas es la precisión en la división de señal y la transmisión de señal a través de todas las derivaciones, de modo que las señales aplicadas a las antenas son prácticamente iguales con errores de fase y magnitud muy bajos. Las alimentaciones corporativas tienen restricciones geométricas estrictas porque un contribuidor principal para la precisión de la señal de salida es la simetría geométrica de niveles múltiples.

La alimentación corporativa con arquitectura de árbol binario como en la Fig. 4 es el componente más simple y es útil en matrices lineales. Si la matriz es bidimensional (por ejemplo, plana), se necesita una alimentación corporativa más complicada, tal como la basada en árboles H. En este caso, la señal se divide en cuatro componentes idénticos en cada nodo, lo que en la práctica presenta serios desafíos.

Otra forma de describir la distribución de las señales de RF a través de una alimentación corporativa es llamarlo una "distribución sincrónica paralela". El frente de una onda de señal que comienza desde la raíz de la alimentación corporativa (conectada a la salida del amplificador 108 de potencia en la fig. 4) viaja hacia las antenas, dividiéndose sucesivamente en muchos frentes de onda, que viajan juntos en "paralelo ", alcanzando las antenas al mismo tiempo o sincrónicamente, a pesar de que las antenas están ubicadas en diferentes posiciones en el espacio. Una distribución en serie, como enviar la señal de RF desde la primera antena a la segunda antena a la tercera antena, etc., no daría como resultado una operación de matriz de antenas sincrónicas porque se agregarían retrasos significativos a cada señal de antena individual. Estos retrasos son significativos cuando son grandes en comparación con la duración de los símbolos contenidos en las señales del transmisor modulado (estos símbolos llevan la información que se transmitirá). Una vez que la señal del transmisor se convierte en RF, la duración del símbolo se vuelve comparable con los retrasos debido a la distribución de la señal de RF.

En la fig. 5 se muestra un enfoque diferente del de la fig. 4 para lograr la misma función de transmisor. En este diagrama, la señal de LO, en lugar de la señal de RF modulada, se distribuye utilizando la alimentación corporativa 122. La señal IF de transmisión analógica se convierte por incremento a RF por separado mediante un mezclador ascendente correspondiente 106 para cada elemento de antena 102. La razón por la cual no es necesario utilizar una alimentación corporativa para distribuir la señal IF en este caso es que los retardos de señal debido a la propagación de ondas electromagnéticas en todo el sistema son pequeños en comparación con la duración del símbolo en IF.

Transmisor de matriz activa basado en la distribución de señales BDS

La alimentación corporativa puede eliminarse mediante la distribución de BDS descrita anteriormente. En ese caso, los grandes retrasos resultantes de la conectividad en serie se compensan automáticamente con la metodología BDS. La fig. 6 muestra un esquema correspondiente al mostrado en la fig. 5 pero con un bus BDS 130 y multiplicadores BDS 132 usados para distribuir las señales LO. En este caso, las señales LO sincronizadas son generadas por los multiplicadores BDS 132 y la señal de transmisión IF analógica se convierte en RF para cada elemento de antena 102 mediante un mezclador 106 de convertidor ascendente asociado con cada elemento 122 de antena. Entonces, en este ejemplo, hay un número igual de multiplicadores BDS 132 y mezcladores 106 convertidores ascendentes.

Como debería ser evidente, el sistema de la figura 6 es redundante en términos del uso del circuito mezclador/multiplicador ya que la funcionalidad de los mezcladores ascendentes está incluida en los multiplicadores BDS. Un ajuste más simple que elimina la redundancia se muestra en la Fig. 7, donde la señal IF se convierte a la mitad de RF una sola vez, antes de distribuirse a través de uno de los dos árboles BDS. Más específicamente, hay un mezclador 106 convertidor ascendente que recibe la señal LO y genera una señal de RF que se suministra al otro árbol del bus BDS 130. Entonces, un árbol del bus BDS lleva la señal LO y la derivación de árbol del bus BDS lleva la señal de RF. Los multiplicadores BDS 132 multiplican estas dos señales distribuidas para generar una distribución RF efectivamente sincronizada. (Nótese que los árboles BDS pueden ser simplemente líneas BDS o troncales BDS sin derivaciones. En otras palabras, el uso de la palabra "árbol" en la descripción actual no implica que la red BDS deba ser tan complicada como se muestra en la fig. 3 y que continuará siendo cierta para el resto de la descripción.

60 Ajuste de amplitud y fase bajo control electrónico

5

10

35

40

45

50

55

65

Los transmisores de matriz activa considerados hasta ahora tienen señales de antena sincronizadas, pero no tienen mecanismos para cambiar la fase relativa o la amplitud de las señales de antena individuales. Esta capacidad es necesaria para crear diversos patrones de radiación y se realiza mediante el uso de circuitos adicionales denominados circuitos de Ajuste de A, de Ajuste de P, o de Ajuste de A/P, ilustrados en las Figs. 8(a)-(c).

Un circuito de ajuste de A es equivalente a un amplificador de ganancia variable, como se ilustra en la fig. 9(a). La relación entre la amplitud de la señal de salida y la amplitud de la señal de entrada es programable y se configura mediante control electrónico. Típicamente, este control es analógico o digital (preferido), cambiando los parámetros del circuito tales como condiciones de polarización, relaciones de resistencia de retroalimentación, etc.

5

Un circuito de Ajuste de P tiene la capacidad fundamental de cambiar la señal de entrada en fase (o tiempo) bajo control electrónico. Las figs. 9(b) y 9(c) muestran posibles realizaciones prácticas de los circuitos de Ajuste de P. En la fig. 9(b), se usan múltiples elementos 140 de demora para demorar la señal de entrada en cantidades fijas y se usa un interruptor de múltiples entradas/salida única (o multiplexor) 142 bajo control electrónico para conectar a la salida la versión deseada demorada de la entrada.

10

En la figura 9(c) se muestra un tipo diferente de circuito de ajuste P. Este circuito usa el principio de suma vectorial. Las señales en cuadratura (I y Q) primero se ponderan en amplitud al multiplicarse con constantes (alternativamente, uno podría usar los circuitos de Ajuste de A para hacer esto) y luego se agregan las señales multiplicadas. Dependiendo del valor de los pesos (es decir, cambios de amplitud), la señal de salida cambia en fase por valores bien controlados.

15

20

Los circuitos de ajuste de A/P pueden configurar tanto la amplitud de salida como la fase de salida bajo controles electrónicos. En principio, el circuito de ajuste de A/P es una combinación en serie de circuitos de ajuste de A y de Ajuste de P, como se ilustra en la Fig. 8(c). El circuito de suma de vectores I/Q de la fig. 9(c) se puede utilizar como un circuito de ajuste de A/P además de ser un circuito de ajuste de P. (Nótese que, en los circuitos descritos en este documento, el uso de un circuito de ajuste de A/P implica que puede funcionar para controlar tanto la amplitud como la fase, solo la fase o solo la amplitud)

Transmisor de matriz activa con distribución de BDS y control de amplitud/fase

25

El transmisor de la matriz de antena en la fig. 10 se deriva del circuito en la fig. 6 agregando los circuitos de Ajuste de A y de Ajuste de P en varios puntos de la red. Esta topología es solo una de las muchas posibilidades para dar al transmisor básico de la fig. 6 la capacidad de controlar independientemente de los valores de amplitud y fase de las señales de antena individuales. Se prefieren los controles digitales, pero también son posibles los controles analógicos.

30

Es útil tener al menos un circuito de Ajuste de P asociado con cada multiplicador BDS, ya sea en una de las entradas del multiplicador BDS o en la salida del multiplicador BDS. El circuito ilustrado incluye un circuito de Ajuste P en ambas ubicaciones con relación al multiplicador BDS.

De forma similar, es útil tener al menos un circuito de ajuste A asociado con cada mezclador de convertidor ascendente 106, ya sea en una de las entradas del mezclador de convertidor ascendente o en la salida del mezclador de convertidor ascendente. El circuito ilustrado incluye un circuito de ajuste A en ambas ubicaciones con respecto al mezclador de convertidor ascendente.

35

40

La fig. 11(a) muestra un transmisor de conjunto de antena derivado del circuito de la fig. 7 en el que la conversión ascendente se realiza en una señal entregada a uno de los árboles del BDS. Más específicamente, el mezclador 106 de convertidor ascendente convierte ascendentemente la señal de transmisión IF y la entrega a uno de los árboles BDS, de modo que un árbol BDS transporta la señal LO y el otro árbol BDS transporta la señal LO modulada.

45