# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 677 709

51 Int. Cl.:

G06F 9/30 (2008.01) G06F 9/50 (2006.01) G06F 9/38 (2008.01)

12 TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 19.03.2015 PCT/EP2015/055746

(87) Fecha y número de publicación internacional: 01.10.2015 WO15144544

(96) Fecha de presentación y número de la solicitud europea: 19.03.2015 E 15711725 (0)

(97) Fecha y número de publicación de la concesión europea: 06.06.2018 EP 3123328

(54) Título: Habilitación dinámica del multihilo

(30) Prioridad:

27.03.2014 US 201414226881

Fecha de publicación y mención en BOPI de la traducción de la patente: **06.08.2018**

(73) Titular/es:

INTERNATIONAL BUSINESS MACHINES CORPORATION (100.0%) New Orchard Road Armonk, New York 10504, US

(72) Inventor/es:

GREINER, DAN;

FARRELL, MARK;

OSISEK, DAMIAN, LEO;

SCHMIDT, DONALD, WILLIAM;

BUSABA, FADI, YUSUF;

KUBALA, JEFFREY, PAUL;

BRADBURY, JONATHAN, DAVID;

HELLER, LISA, CRANTON;

SLEGEL, TIMOTHY y

JACOBI, CHRISTIAN

74 Agente/Representante:

ELZABURU, S.L.P

## **DESCRIPCIÓN**

Habilitación dinámica del multihilo

#### **Antecedentes**

5

10

15

20

25

30

45

50

55

La presente invención se relaciona de manera general con un sistema informático que soporta múltiples hilos, y más específicamente, a la habilitación dinámica del multihilo en un sistema informático.

Según ha aumentado la velocidad de los sistemas informáticos en las pasadas décadas, no ha existido un aumento proporcional de la velocidad a la que la memoria se puede acceder en dichos sistemas informáticos. Por tanto, cuanto más rápido es el tiempo de ciclo del procesador, más pronunciado es el retardo de espera para que los datos sean recogidos de la memoria. Los efectos de dicho retardo han sido mitigados mediantes diversos niveles de almacenamiento en caché, y en los recientes procesadores, mediante el multihilo (MT).

El MT permite que diversos recursos de núcleo de un procesador sean compartidos por una pluralidad de flujos de instrucciones conocidos como hilos. Los recursos de núcleo pueden incluir las unidades de ejecución, la cachés, las memorias intermedias de traducción anticipada (TLB) y similares, que generalmente se pueden referir de manera colectiva como un núcleo. Durante la latencia causada por un fallo de caché u otro retardo en un hilo, uno o más hilos pueden utilizar los recursos del núcleo, aumentando así la utilización de los recursos del núcleo. En una implementación multihilo simultánea (SMT) de procesador súper escalar, los múltiples hilos pueden ser servidos de manera simultánea por los recursos del núcleo de uno o más núcleos.

En las plataformas de hardware contemporáneas, el MT normalmente se implementa de una manera que es transparente a un sistema operativo (OS) que se ejecuta en el hardware de MT. Un aspecto de esta característica es que el OS no requiere modificación para utilizar el hardware MT. Sin embargo, una operación MT transparente con respecto al OS puede resultar en una alta variabilidad de los tiempos de respuesta, del aprovisionamiento de la capacidad, de la planificación de la capacidad, y del orden de importancia. Esta variabilidad puede ocurrir ya que el OS no es consciente de si sus tareas tienen el control exclusivo de un núcleo, o si sus tareas se están ejecutando como hilos que comparten un núcleo. Mediante el diseño, se logra la mayor capacidad de carga de trabajo intensiva de memoria en un hardware con capacidad MT cuando existe una densidad de hilos media cuando los núcleos están en uso. Una capacidad adicional se puede deber a la explotación aumentada de la memoria caché proporcionada por el MT. Si un OS no mantiene de manera consistente una alta densidad media de hilos para utilizar los núcleos, entonces no estará disponible la capacidad de rendimiento total adicional proporcionada por el MT. Por ejemplo, si el hardware ejecuta un hilo MT único por núcleo cuando hay una baja utilización de computación y ejecuta una alta densidad de hilos cuando hay una alta utilización computacional, entonces puede ser muy difícil determinar cuanta capacidad total de computación MT hay disponible para la carga de trabajo. Esta variabilidad de hardware en la explotación de los hilos MT puede llevar a una variabilidad en tanto los tiempos de respuesta de transacción como en el orden de importancia de una manera similar a como se ha descrito anteriormente con respecto a la capacidad.

La solicitud de patente US2004215939A1 se relaciona con un conmutador dinámico de un procesador multihilo entre los modos de hilo único y de multihilo simultáneos. Un procesador multihilo tiene al menos un hilo hardware entre una pluralidad de hilos hardware que es capaz de ser activado y desactivado de manera selectiva en respuesta a un circuito de control. El circuito de control proporciona de manera adicional la capacidad de controlar cómo se puede activar un hilo inactivo después de que el hilo se haya desactivado, por ejemplo, habilitando o deshabilitando la reactivación en respuesta a una interrupción.

La solicitud de patente US2008114973A1 se relaciona con un hardware multihilo dinámico y un hardware multihilo particionado. Se usa una función de detención de hardware o una función de rendimiento de hardware en un núcleo del procesador para habilitar o deshabilitar un hilo de hardware que comparte el núcleo, en donde el hilo de hardware está deshabilitado colocando el hilo de hardware en un estado de detención o un estado de rendimiento, y habilitando otro hilo de hardware para utilizar el núcleo.

# Compendio

Las realizaciones incluyen un sistema, un método y un producto de programa informático para la habilitación dinámica del multihilo. Según un aspecto, un sistema informático incluye una configuración con un núcleo configurable entre un modo de hilo único (ST) y un modo de multihilo (MT). El modo ST aborda un hilo principal, y el modo MT aborda el hilo principal y uno o más hilos secundarios en los recursos compartidos del núcleo. El sistema informático incluye también una facilidad de multihilo configurada para controlar la configuración para realizar un método. El método incluye la ejecución en el hilo principal en el modo ST, de una instrucción de configuración del modo MT. El número de hilos solicitados se obtiene de una ubicación especificada por la instrucción de configuración del modo MT. En base a la determinación de que el número de hilos solicitados indica múltiples hilos, el modo MT está habilitado para ejecutar los múltiples hilos incluyendo el hilo principal y el uno o más hilos secundarios.

Según otro aspecto, se proporciona un método implementado por ordenador para el establecimiento dinámico del multihilo en una configuración. La configuración incluye un núcleo configurable entre un modo ST y un modo Mt, donde el modo ST aborda un hilo principal y el modo MT aborda el hilo principal y uno o más hilos secundarios en los recursos compartidos del núcleo. El método incluye ejecutar en el hilo principal en el modo ST, una instrucción de configuración del modo MT. El número de hilos solicitados es obtenido a partir de una ubicación especificada por la instrucción de configuración del modo MT. En base a la determinación de que el número de hilos solicitados indique múltiples hilos, el modo MT se habilita para ejecutar los múltiples hilos incluyendo el hilo principal y el uno o más hilos secundarios.

Un aspecto adicional incluye un producto de programa informático para implementar la habilitación dinámica del multihilo en una configuración. La configuración incluye un núcleo configurable entre un modo ST y un modo MT, donde el modo ST aborda un hilo principal y el modo MT aborda el hilo principal y uno o más hilos secundarios en los recursos compartidos del núcleo. El producto de programa informático incluye un medio de almacenamiento legible por ordenador que tiene instrucciones de programa incrustadas en este, donde el medio de almacenamiento legible por ordenador no es una señal. Las instrucciones de programa son legibles con un circuito de procesamiento para provocar que el circuito de procesamiento realice un método. El método incluye la ejecución en el hilo principal en el modo ST en el núcleo de la configuración, de una instrucción de configuración del modo MT. El número de hilos solicitados se obtiene de una ubicación especificada por la instrucción de configuración del modo MT. En base a la determinación de que el número de hilos solicitados indica múltiples hilos, se habilita el modo MT para ejecutar los múltiples hilos incluyendo el hilo principal y uno o más hilos secundarios.

#### 20 Breve descripción de las distintas vistas de los dibujos

5

La materia que es considerada como las realizaciones se señala y reivindica de manera distintiva en las reivindicaciones en la conclusión de la especificación. Las características y ventajas anteriores y otras, de las realizaciones serán evidentes de la siguiente descripción detallada tomada en conjunción con los dibujos adjuntos en los que:

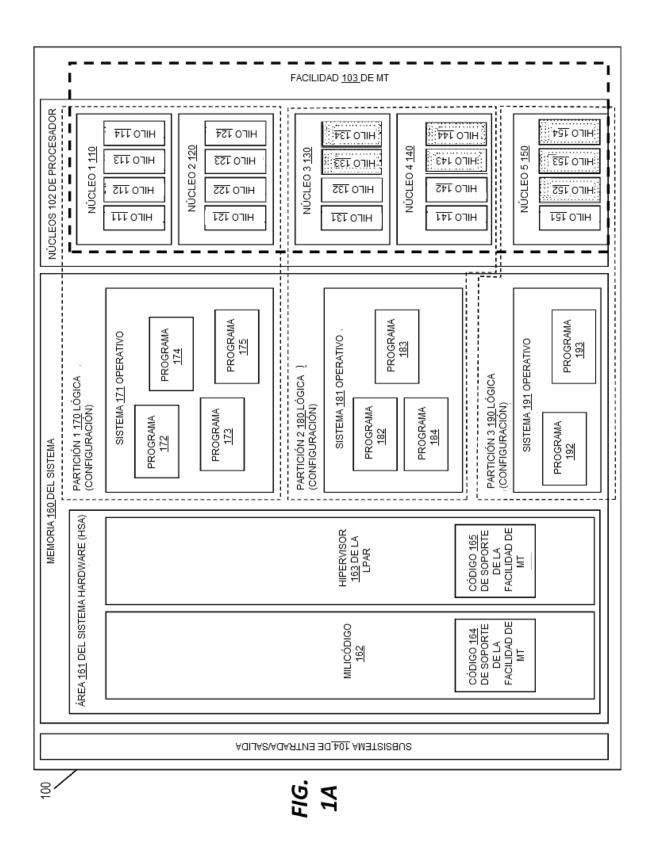

- 25 La FIG. 1A representa un entorno informático que se puede implementar de acuerdo con una realización;

- La FIG. 1B representa un entorno informático que se puede implementar de acuerdo con una realización;

- La FIG. 2 representa una circuitería de procesamiento de un núcleo que se puede implementar de acuerdo con una realización;

- La FIG. 3 representa un entorno informático que se puede implementar de acuerdo con una realización;

- La FIG. 4 representa un ejemplo de retención de contexto de hipervisor en un entorno informático que se puede implementar de acuerdo con una realización;

- La FIG. 5 representa un flujo de proceso para la habilitación dinámica del multihilo de acuerdo con una realización;

- La FIG. 6A representa un ejemplo de un proceso de expansión de la dirección de la CPU de acuerdo con una realización:

- La FIG. 6B representa un ejemplo de un proceso de contracción de la dirección de la CPU de acuerdo con una realización:

- La FIG. 7 representa un flujo de procesos para una orden de configuración de multihilo de acuerdo con una realización:

- La FIG. 8 representa un ejemplo de almacenamiento de la información de la capacidad de multihilo de acuerdo con una realización;

- La FIG. 9 representa un flujo de procesos para determinar la capacidad de multihilo de acuerdo con una realización;

- La FIG. 10 representa un ejemplo de diversas ubicaciones de contexto de hilos de acuerdo con una realización;

- La FIG. 11 representa un ejemplo de preservación del registro de multihilo de acuerdo con una realización;

- La FIG. 12 representa un flujo de procesos para la preservación del registro de multihilo de acuerdo con una realización;

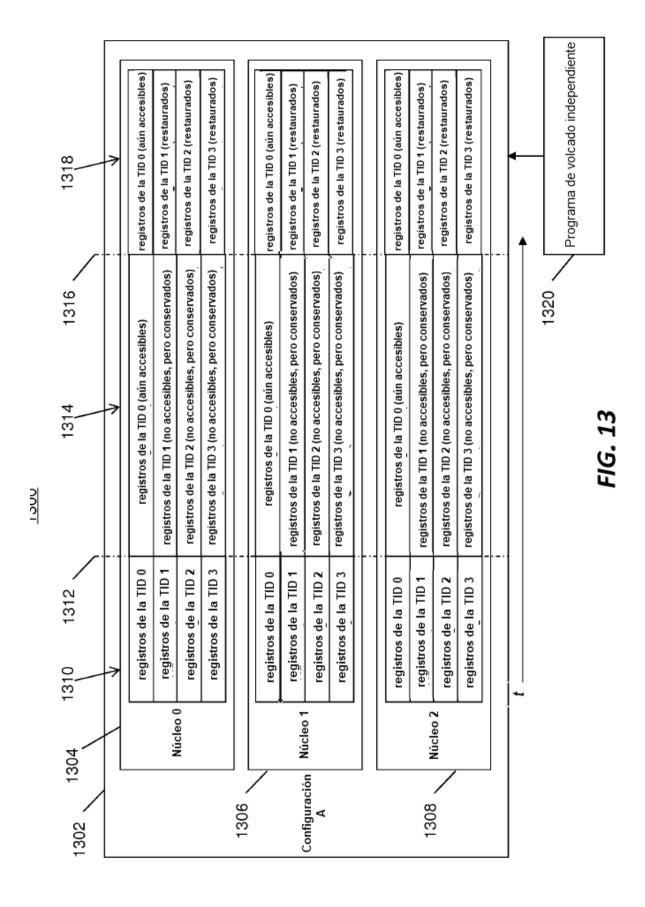

- La FIG. 13 representa un ejemplo de restauración del registro de multihilo de acuerdo con una realización;

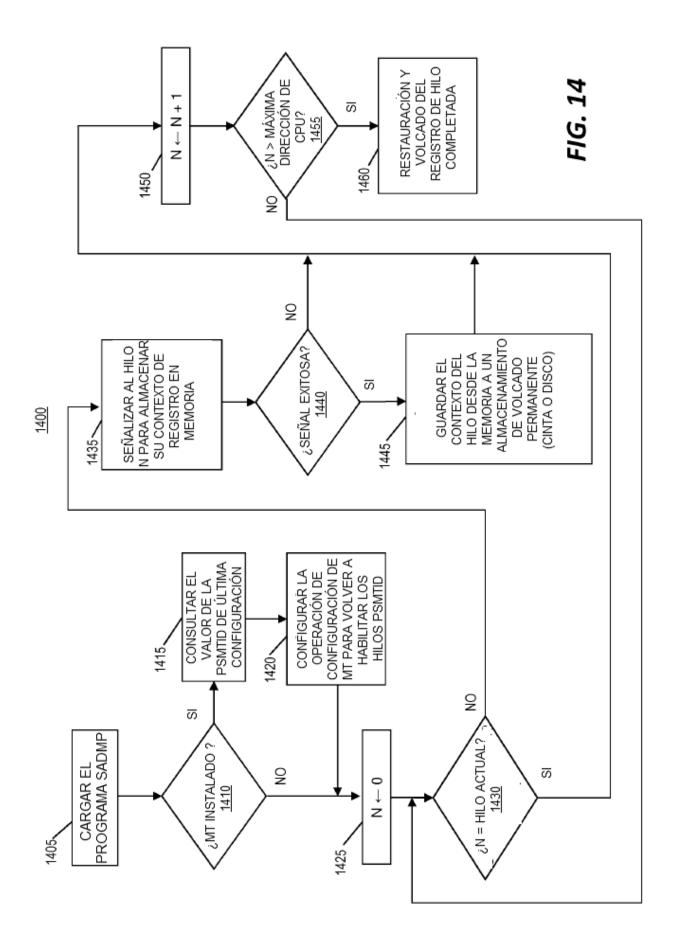

- La FIG. 14 representa un flujo de procesos para la restauración del registro de multihilo de acuerdo con una realización; y

- La FIG. 15 representa un medio legible por ordenador según una realización.

### Descripción detallada

5

20

25

30

35

40

45

Las realizaciones ejemplares proporcionan la operación de multihilo en un sistema informático que soporte un hilo único y un modo de operación de multihilo. Como se usa en la presente memoria, un hilo lógico se refiere a un flujo de instrucciones único y su estado asociado. Esto es, en un nivel de arquitectura, cada hilo lógico representa una unidad o procesador de procesamiento central (CPU) independiente En un nivel de hardware, un hilo es la ejecución de un flujo de instrucciones asociado con un hilo lógico, combinado con el mantenimiento de ese estado de invitado, cuando el hilo se despacha. Por lo tanto, los términos "hilo" y "CPU" se pueden usar de manera intercambiable en la presente memoria.

En una realización ejemplar, una CPU contiene las facilidades de secuencia y procesamiento para la ejecución de la instrucción, la acción de interrupción, las funciones de temporización, la carga inicial del programa, y otras funciones relacionadas con la máquina. Una CPU define las funciones lógicas, que pueden hacerse corresponder con una variedad de implementaciones físicas subyacentes. La CPU, en las instrucciones en ejecución, puede procesar los números enteros binarios y los números en punto flotante (por ejemplo, binarios, decimales, y hexadecimales) de longitud fija, los números enteros decimales de longitud variable, y la información lógica de ya sea la longitud fija o variable. El procesamiento puede ser en paralelo o en serie. La anchura de los elementos de procesamiento, la multiplicidad de las rutas cambiantes, y el grado de simultaneidad en la realización de los diferentes tipos de aritmética puede diferir de un modelo de CPU a otro sin afectar a los resultados lógicos.

Las instrucciones que ejecuta la CPU pueden incluir un número de clases de instrucciones, tales como, generales, decimales, de soporte en punto flotante (FPS), de punto flotante binario (BFP), de punto flotante decimal (DFP), de punto flotante hexadecimal (HFP), de control, y/o instrucciones de I/O. Las instrucciones generales se pueden usar en la realización de las operaciones y la lógica de aritmética de números enteros binarios, derivación, y otras operaciones no aritméticas. Las instrucciones decimales operan sobre los datos en formato decimal, Las instrucciones BFP, DFP, y HFP operan sobre datos de formatos BFP, DFP, y HFP respectivamente, mientras que las instrucciones FPS operan sobre datos de punto flotante independientes del formato o convierte de un formato a otro. Se pueden ejecutar instrucciones de control privilegiadas y de I/O cuando la CPU está en un estado supervisor, y se pueden ejecutar instrucciones de control semi privilegiadas en un estado problemático, sujetas a los mecanismos de autorización apropiados.

La CPU proporciona registros que están disponibles para los programas pero no tienen representaciones direccionables en el almacenamiento principal. Los registros pueden incluir, por ejemplo, una palabra de estado actual del programa (PSW), registros generales, registros de punto flotante y registros de control del punto flotante, registros de vector, registros de control, registros de acceso, un registro de prefijo, un registro programable de la hora del día (TOD), y registros para un comparador de reloj y un temporizador de CPU. Este conjunto de registros puede ser referido para el contexto de registros de la arquitectura de la CPU. Cada CPU en una configuración puede proporcionar acceso a un reloj TOD, que puede ser compartido por todas las CPU en la configuración. Un código de operación de instrucción puede determinar qué tipo de registro se ha de usar en una operación.

Cada CPU puede tener un atributo de tipo que indique si proporciona un complemento total de las funciones y facilidades (por ejemplo, una CPU general), o si está destinada a procesar tipos específicos de cargas de trabajo (por ejemplo, una CPU especial). Una CPU principal es bien una CPU general o una CPU que tiene el mismo tipo que la CPU que ha empezado a seguir una última operación de la carga de programa inicial (IPL) (la CPU IPL). Una CPU secundaria es cualquier CPU distinta de la CPU general que tiene un tipo de CPU que difiere de la CPU IPL.

Una facilidad de multihilo puede estar disponible en un sistema informático que implementa una arquitectura de soporte. La facilidad de multihilo proporciona soporte para el multihilo para habilitar un grupo de hilos, que puede ser referido también como CPU, que comparten un núcleo. Cuando se habilita la facilidad de multihilo, las CPU dentro de un núcleo pueden compartir ciertos recursos de hardware tales como las unidades de ejecución o las memorias cachés. Cuando una CPU en un núcleo está esperando por los recursos de hardware (normalmente, mientras espera por un acceso de memoria), otras CPU en el núcleo pueden utilizar los recursos compartidos en el núcleo en lugar de mantenerlos inactivos. Cuando la facilidad de multihilo se instala y se habilita, un hilo es síncrono con una CPU que es un miembro de un núcleo. Cuando la facilidad de multihilo no está instalada, o la facilidad está instalada pero no habilitada, un núcleo comprende una CPU o hilo único.

Cuando la facilidad de multihilo está instalada, puede ser habilitada mediante la ejecución de una orden de configuración de un procesador de señal de multihilo (SIGP). En una realización ejemplar, cuando la facilidad multihilo está habilitada, el número de CPU en una configuración es aumentado por un múltiplo, el valor del cual está determinado por una identificación de los hilos máximos especificados por el programa (PSMTID). El número de CPU en un núcleo puede ser uno más que el PSMTID. Un número de CPU correspondiente a este múltiplo se agrupa en un núcleo. Cada núcleo del mismo tipo de CPU en una configuración puede tener el mismo número de CPU. Cada CPU dentro de un núcleo es del mismo tipo de CPU. Sin embargo, en base al modelo y el tipo de CPU, algunas CPU dentro de un núcleo pueden no estar operativas.

En una realización ejemplar, un programa de control, tal como un sistema operativo (OS) habilita de manera explícita el multihilo para .que éste se pueda usar por la configuración que gestiona el OS. De manera alternativa, un

hipervisor puede habilitar el multihilo y los invitados del hipervisor y sus aplicaciones pueden beneficiarse de manera transparente. Un programa de aplicación generalmente no es consciente de si se ha habilitado el multihilo. Cuando se habilita el multihilo, las direcciones de CPU de todas las CPU en la configuración se ajustan para incluir una identificación de núcleo (o ID de núcleo) en los bits más a la izquierda de la dirección y una identificación de hilo (ID de hilo, o TID) en los bits más a la derecha de la dirección. La ID de núcleo puede ser también referida como un valor de dirección de hilo. Las CPU dentro de un núcleo pueden compartir ciertas facilidades de hardware tales como las unidades de ejecución o las memorias cachés de nivel inferior, así la ejecución dentro de una CPU de un núcleo puede afectar el rendimiento de otras CPU en el núcleo.

Para gestionar los cambios asociados con el cambio dinámico de uno o más núcleos de una configuración entre los modos de hilo único y de multihilo, se incluyen un número de características de soporte. Para mantener la compatibilidad con los programas que no soportan el multihilo, el modo de hilo único puede ser el modo por defecto después de un reinicio o una desactivación. Las realizaciones ejemplares incluyen características para preservar, comunicar, y restaurar el contexto de los hilos desde el modo de multihilo para soportar el análisis y/o la restauración del contexto de hilo después de la transición desde el modo de multihilo al modo de hilo único.

Un entorno informático que puede ser implementado por una realización ejemplar puede estar basado, por ejemplo, en la z/Architecture ofrecida por la International Business Machines Corporation, Armonk, Nueva York. La z/ Architecture se describe en una publicación de IBM® titulada. "Principios de Operación de la z/Architecture," Publicación de IBM Nº SA22-7832-09, Agosto del 2012. En un ejemplo, un entorno informático basado en la z/Architecture incluye un eServer zSeries, ofrecido por la International Business Machines Corporation, Armonk, Nueva York. Un entorno informático puede incluir, por ejemplo, un complejo procesador con una o más particiones (por ejemplo particiones lógicas) con uno o más núcleos (por ejemplo núcleos de procesador), y uno o más niveles de hipervisores como se describe de manera adicional en la presente memoria.

25

30

35

40

45

50

55

60

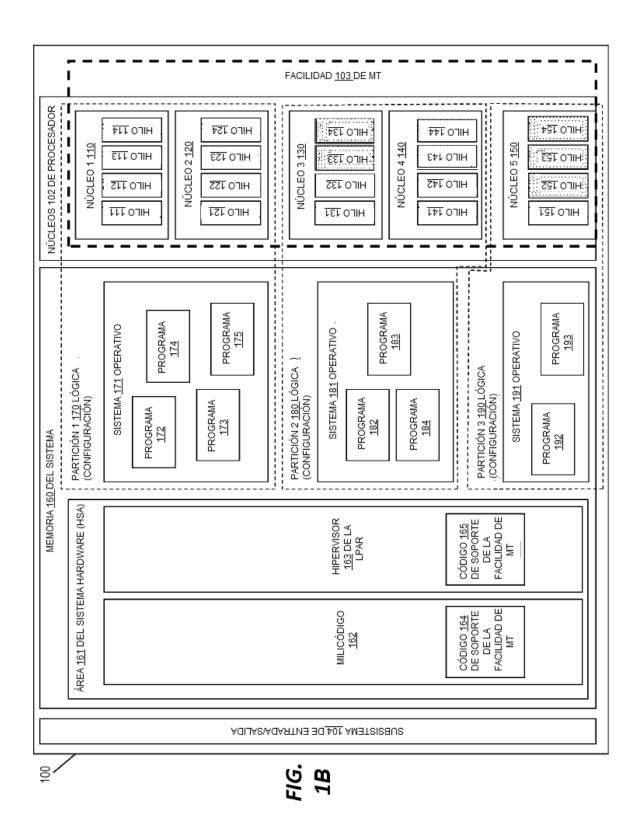

La FIG. 1A muestra un sistema 100 informático como un ejemplo de un entorno informático que soporta multihilo (MT). En el ejemplo de la FIG. 1A, el sistema 100 informático incluye una pluralidad de núcleos 102 de procesador, un subsistema 104 de entrada/salida (I/O), y una memoria 160 de sistema. El subsistema 104 de I/O puede proporcionar acceso a los dispositivos de I/O conocidos en la técnica. Los núcleos 102 de procesador, también referidos simplemente como "núcleos" en la presente memoria, pueden incluir circuitería de procesamiento con elementos de soporte. En el ejemplo de la FIG. 1A, se representan cinco núcleos 102 como el núcleo1 110, el núcleo2 120, el núcleo3 130, el núcleo4 140, y el núcleo5 150; sin embargo, se contempla también un mayor y un menor número de núcleos 102. Una facilidad 103 MT puede ser un componente de hardware de cada uno de los núcleos 102. En este ejemplo, cada uno de los núcleos 102 es capaz de soportar hasta cuatro hilos. Por ejemplo, el núcleo1 110 puede soportar los hilos 111, 112, 113, y 114. El núcleo2 120 puede soportar los hilos 121, 122, 123, y 124. El núcleo3 130 puede soportar los hilos 131, 132, 133, y 134. El núcleo4 140 puede soportar los hilos 141, 142, 143, y 144. El núcleo5 150 puede soportar los hilos 151, 152, 153, y 154. Observe que no todos los cuatro hilos de cada núcleo 102 pueden estar operativos en cualquier instante. Por ejemplo, en el núcleo 3 130, los hilos 131 y 132 pueden estar operativos mientras que los hilos 133 y 134 se habilitan para estar operativos (representado con el sombreado).

La FIG.1A también representa la memoria 160 de sistema del sistema 100 informático, donde las partes de la memoria 160 del sistema se distribuyen en la partición1 170 lógica (LPAR1), la LPAR2 180, y la LPAR3 190. Las LPAR 170, 180, 190 representan los sistemas informáticos virtualizados (también conocidos como configuraciones) en las que un sistema operativo tal como Linux<sup>™</sup> o el sistema operativo z/OS<sup>™</sup>, z/VM, o zTPF de IBM® se pueden ejecutar. La FIG. 1A también muestra la distribución de los núcleos 102 a las LPAR 170, 180, 190. En esta ilustración, el núcleo1 110 y el núcleo2 120 están dedicados para su uso por la LPAR1 170. El núcleo 3 130 está dedicado para su uso por la LPAR2 180, y el núcleo 5 150 está dedicado para su uso por la LPAR3 190. El núcleo4 140 puede ser compartido entre la LPAR2 180 y la LPAR3 190, pero se muestra como que se asigna a la LPAR2 180 en la FIG. 1A. La LPAR3 190 muestra un ejemplo de dos diferentes tipos de núcleos 102 que se emplean por la partición, donde el núcleo4 140 habilita múltiples hilos para ser operativos, pero el núcleo5 150 no habilita múltiples hilos para ser operativos en este ejemplo. En el ejemplo de la FIG. 1A, la LPAR1 170 proporciona recursos de procesamiento para el OS 171 y los programas 172, 173, 174, y 175. La LPAR2 180 proporciona recursos de procesamiento para el OS 181 y los programas 182, 183, y 184. La LPAR4 190 proporciona recursos de procesamiento para el OS 191 y los programas 192 y 193.

Bajo el control de un sistema operativo que se ejecuta en una LPAR, los programas se ejecutan en los hilos de un núcleo. En una realización ejemplar, un hilo individual ejecuta sólo un programa a la vez, sin embargo, un programa que se diseña para ser reentrante se puede ejecutar en múltiples hilos o núcleos de manera simultánea. Por ejemplo, el programa 172 del OS 171 de la LPAR1 170 se puede estar ejecutando en los hilos 111 y 113 en el núcleo1 110 y en los hilos 121 y 124 del núcleo2 120. Sujeto al control de un OS, los diferentes programas se pueden despachar en el mismo o diferentes hilos, sujeto a las reglas de despacho y a los acuerdos de calidad de servicio.

También residiendo en la memoria 160 del sistema existen diversos niveles de firmware, que incluyen por ejemplo, el Milicódigo 162 y el hipervisor 163 de la LPAR. El Milicódigo 162 se puede incrustar como firmware para soportar

funciones de sistema de nivel inferior. El hipervisor 163 de la LPAR puede ser, por ejemplo, código interno de licencia tal como el IBM Processor-Resource / System Manager <sup>TM</sup> (PR/SM<sup>TM</sup>). El hipervisor 163 de la LPAR puede establecer las LPAR 170, 180, 190 y puede gestionar el despacho en los núcleos 102. Cuando la facilidad 103 MT se instala en el sistema 100 informático, el Milicódigo 162 y el hipervisor 163 de la LPAR contienen también el código 164 y 165 de soporte de la facilidad MT respectivamente. El código 164 y 165 de soporte de la facilidad MT se puede considerar parte de la facilidad 103 MT, ya que la lógica para soportar el MT se puede distribuir entre el Milicódigo 162, el hipervisor 163 de la LPAR, y los núcleos 102. Aunque no se representa, cada uno de los OS 171, 181, 191 pueden incluir también el código de soporte de la facilidad MT para habilitar y explotar el MT en sus respectivas LPAR 170, 180, 190.

- La FIG. 1B muestra el mismo sistema 100 informático que la FIG. 1A, excepto que en el entorno informático de la FIG. 1B, el núcleo4 140 se asigna ahora a la LPAR3 190 en lugar de la LPAR2 180. Observe también que a diferencia de la FIG. 1A, donde los hilos 143 y 144 no estaban operativos, en la FIG. 1B, todos los cuatro hilos 141-144 están operativos actualmente cuando la LPAR3 190 se despacha en el núcleo4 140. El despacho y el no despacho de una LPAR en un núcleo 102 es dinámico, y en otros momentos distintos las LPAR (no mostradas) pueden estar operativas en los mismos núcleos 102.

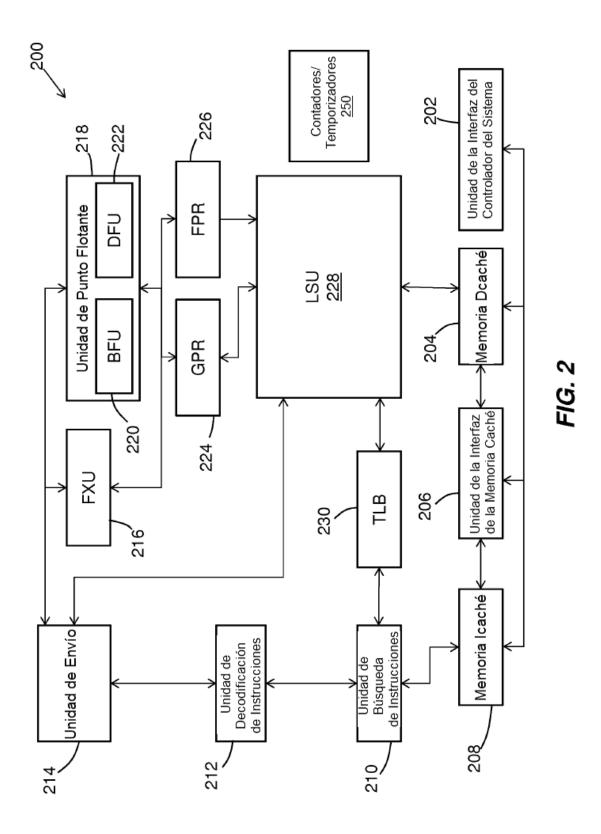

- Volviendo ahora a la FIG.2, se muestra de manera general un diagrama de bloques de la circuitería 200 de procesamiento para implementar un núcleo de procesamiento, tal como uno de los núcleos 102 de las FIG. 1A y 1B, de acuerdo con una realización. La circuitería 200 de procesamiento es un ejemplo de un circuito de procesamiento que puede soportar uno o más hilos de manera simultánea en un entorno de MT. La circuitería 200 de procesamiento mostrada en la FIG. 2 incluye una unidad 202 de la interfaz del controlador del sistema que puede acoplar la circuitería 200 de procesamiento a otros procesadores y dispositivos periféricos. La unidad 202 de la interfaz del controlador del sistema se puede conectar también a una memoria Dcaché 204, que lee y almacena los valores de los datos, una memoria lcaché 208, que lee las instrucciones de programa, y una unidad 206 de la interfaz de la memoria caché para la memoria externa, los procesadores, y otros dispositivos periféricos.

20

50

55

60

- La memoria Icaché 208 puede proporcionar la carga de flujos de instrucciones en conjunción con una unidad 210 de búsqueda de instrucciones (IFU), que realiza una búsqueda previa de las instrucciones y puede incluir capacidades de carga especulativa y predicción de bifurcación. Las instrucciones buscadas se pueden proporcionar a una unidad 212 de decodificación de instrucciones (IDU) para decodificarlas en datos de procesamiento de las instrucciones.

- La IDU 212 puede proporcionar las instrucciones a una unidad 214 de salida que puede controlar la salida de las instrucciones a las diversas unidades de ejecución, tal como una o más unidades 216 de punto fijo (FXU) para ejecutar las operaciones generales y una o más unidades 218 de punto flotante (FPU) para ejecutar las operaciones en punto flotante. Las FPU 218 pueden incluir una unidad 220 de punto flotante binaria (BFU), una unidad 222 de punto flotante decimal (DFU), o cualquier otra unidad de punto flotante. La unidad 214 de salida se puede acoplar también a una o más unidades 228 de carga/almacenamiento (LSU) a través de uno o más tubos LSU. Los múltiples tubos LSU son tratados como unidades de ejecución para realizar las cargas y los almacenamientos y la generación de direcciones para las bifurcaciones. Tanto la LSU 228 como la IFU 210 pueden utilizar una memoria 230 intermedia de traducción anticipada (TLB) para proporcionar las traducciones almacenadas en la memoria intermedia para el operando y las direcciones de instrucción.

- La FXU 216 y la FPU 218 se acoplan a los diversos recursos tales como los registros 224 de propósito general (GPR) y los registros 226 en punto flotante (FPR). El GPR 224 y el FPR 226 proporcionan el almacenamiento de los valores de los datos para los valores de los datos cargados y almacenados desde la memoria Dcaché 204 mediante una LSU 228.

- La circuitería 200 de procesamiento puede incluir también contadores y/o temporizadores 250 para ayudar en las acciones de generación y diagnóstico de base de tiempo del sistema. Por ejemplo, los contadores y/o los temporizadores 250 se pueden usar para soportar la opción hora del día, así como diversas facilidades de diagnóstico y medición.

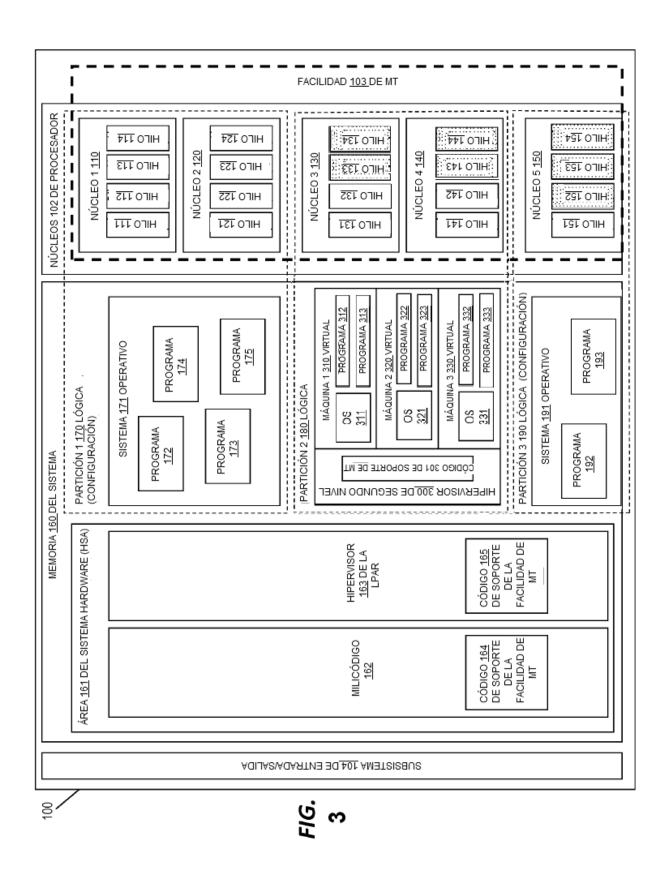

- Volviendo ahora a la FIG. 3, se representa un entorno informático similar a la FIG. 1A excepto en que en la FIG. 3, se ejecuta un hipervisor 300 de segundo nivel en la LPAR2 180 del sistema 100 informático. El hipervisor 300 de segundo nivel, por ejemplo, el sistema operativo z/VM de IBM, incluye código 301 de soporte MT, similar al código 165 de soporte MT proporcionado por el hipervisor 163 (de primer nivel) de la LPAR. El hipervisor 300 de segundo nivel proporciona soporte para una pluralidad de máquinas virtuales 310, 320, y 330 (también referido como configuraciones) en las que operan respectivamente los sistemas 311, 321, y 331 operativos de invitado. Los sistemas 311, 321, y 331 operativos de invitado pueden incluir, por ejemplo, Linux™ o el z/OS™, el z/VM, o el z/TPF de IBM®, o pueden incluir un entorno de desarrollo de invitado tal como el sistema de monitoreo conversacional de IBM (CMS). Cada OS 311, 321, y 331 de invitado puede o no habilitar el multihilo, en cuyo caso el hipervisor 300 de segundo nivel puede ser responsable de despachar los OS 311, 321, 331 de invitado y los programas 312, 313, 322, 323, 333 asociados usando los recursos de procesamiento físicos (núcleos 130, 140, y los hilos 131-134, 141-144) que están disponibles para la LPAR2 180 en la que opera el hipervisor 300 de segundo nivel. Los programas 312, 313, 322, 323, 332, 333 de las diversas máquinas 310, 320, 330 virtuales pueden ejecutarse en los hilos 131-134, 141-144 disponibles para los respectivos OS 311, 321, y 331 de invitado. Los OS 311, 321, y 331 de invitado no

necesitan incluir código de soporte de MT, ya que pueden beneficiarse del MT de manera transparente si el hipervisor 300 de segundo nivel explota el multihilo.

5

10

15

20

25

55

60

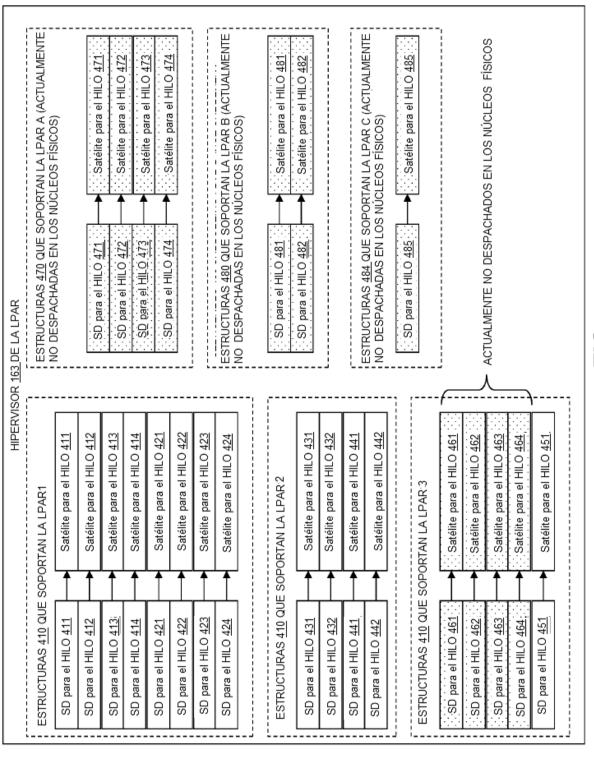

Volviendo ahora a la FIG. 4, se representa un ejemplo de retención de contexto de hipervisor en un entorno informático que se puede implementar de acuerdo con una realización. En el ejemplo de la FIG. 4, se representa un número de estructuras de soporte dentro del hipervisor 163 de la LPAR de las FIG. 1A y 1B. Por ejemplo, las estructuras 410 pueden soportar la LPAR1 170 de la FIG. 1A, que incluye las descripciones de estado y los bloques satélite que almacenan contextos de registro de arquitectura (esto es, contexto de hilos) para los hilos 411, 412, 413, 414, 421, 422, 423, 424 lógicos que están ejecutándose actualmente en los hilos 111, 112, 113, 114, 121, 122, 123, 124 físicos como se muestra en la FIG. 1A. Mientras se despachan estos hilos lógicos, los hilos físicos mantienen el contexto de registro de la arquitectura actual de los hilos. El contexto de registro de la arquitectura se mantendrá en las descripciones de estado y los bloques satélite cuando ya no se despachen, Las estructuras 430 pueden soportar la LPAR2 180 de la FIG. 1A, incluyendo las descripciones de estado y los bloques satélite que almacenan el contexto de registro de la arquitectura para los hilos 431, 432, 441, 442 lógicos que se están ejecutando actualmente en los hilos 131, 132, 141, 142 físicos como se muestra en la FIG. 1A. Las estructuras 450 pueden soportar la LPAR3 190 de la FIG. 1A, incluyendo las descripciones de estado y los bloques satélite que almacenan el contexto de registro de la arquitectura para los hilos 451 lógicos que se están ejecutando actualmente en el hilo 151 físico como se muestra en la FIG. 1A. Las estructuras 450 también incluyen descripciones de estado y bloques satélite que almacenan el contexto de registro de la arquitectura para los hilos 461, 462, 463 y 464 lógicos que no se despachan actualmente en el procesador físico (como se muestra con el sombreado). Otras estructuras que soportan las LPAR que no se despachan en los núcleos físicos pueden ser conservadas también por el hipervisor 163 de la LPAR, tales como las estructuras 470 para una LPAR A (no representada en la FIG. 1A) que incluye las descripciones de estado y las estructuras satélite para los hilos 471, 472, 473, y 474 lógicos. Ejemplos adicionales de estructuras incluyen las estructuras 480 que soportan la LPAR B no despachada (no representada en la FIG. 1A) que incluye las descripciones de estado y las estructuras satélite para los hilos 481 y 482 lógicos, así como las estructuras 484 para la LPAR C no despachada (no representada en la FIG. 1A) para el hilo 485 lógico.

Aunque se representan un número de estructuras en el ejemplo de la FIG. 4, se entenderá que estructuras adicionales pueden ser soportadas por el hipervisor 163 de la LPAR y también en el sistema 100 informático para gestionar el multihilo. Por ejemplo, las estructuras para soportar multihilo de las máquinas 310, 320, 330 virtuales de la FIG. 3 pueden ser conservadas por el hipervisor 300 de segundo nivel de la FIG. 3.

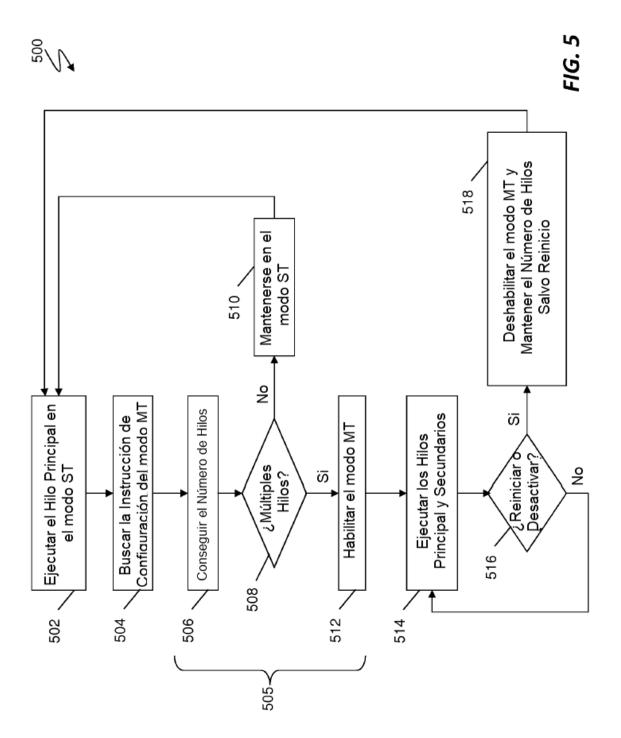

- Volviendo ahora a la FIG. 5, se representa un flujo 500 de proceso para la habilitación dinámica del multihilo de acuerdo con una realización. En el bloque 502, un hilo principal se ejecuta en un modo de hilo único (ST). En el bloque 504, se busca una instrucción de configuración del modo multihilo (MT) en el modo ST. Al ejecutar esta instrucción como se representa de manera colectiva en 505, se obtiene un número de hilos solicitado desde una ubicación especificada por la instrucción de configuración del modo MT en el bloque 506. La ubicación puede ser especificada por un registro de parámetro al emitir la instrucción de configuración del modo MT. La instrucción de configuración del modo MT puede ser una instrucción del procesador de señal (SIGP) que incluye una orden de configuración de MT y una id de hilo máximo especificado por el programa (PSMTID) asociado con el número de hilos solicitados. Un ejemplo de un proceso asociado con una orden de configuración de MT de una instrucción SIGP se describe de manera adicional en la presente memoria en referencia a la FIG. 7.

- Continuando con el proceso 500, en el bloque 508, se realiza la determinación de si el número de hilos solicitados indica múltiples hilos. Por ejemplo, los múltiples hilos pueden ser indicados por un valor mayor que uno. En realizaciones donde un valor de cero indica un hilo único, un valor de uno o más de uno puede indicar múltiples hilos. En base a la determinación de que el número de hilos solicitados no indica múltiples hilos, el núcleo se mantiene en el modo ST en el bloque 510, se completa la ejecución de la instrucción de configuración del modo MT, y el control vuelve al bloque 502. En base a la determinación de que el número de hilos solicitados indica múltiples hilos, el modo MT se habilita en el bloque 512, y la ejecución de la instrucción de configuración del modo MT se completa. En el bloque 514, se ejecutan los múltiples hilos incluyendo los hilos principal y uno o más secundarios. En el bloque 516, si no hay reinicio o desactivación, el proceso 500 vuelve al bloque 514, en otro caso, en el bloque 518, se deshabilita el modo MT en base a un reinicio o una desactivación de la configuración que vuelve al modo ST. Como parte del hecho de deshabilitar el modo MT, el número de hilos (PSMTID) se conserva en un reinicio sin borrado o se pone a cero en un reinicio con borrado. El proceso 500 vuelve al bloque 502.

Una CPU puede entrar en un estado de carga cuando se activa una clave de carga normal, carga con volcado, carga con borrado, o carga con borrado de lista dirigida. Si se completa una operación de carga de programa inicial del tipo palabra de comando de canal (CCW) de manera exitosa, la CPU cambia desde el estado de carga al estado de operación.

Un reinicio de la CPU se puede usar para borrar las indicaciones de comprobación de equipo y cualquier resultado impredecible en el estado de la CPU con la menor cantidad de información destruida. En concreto, se puede usar para borrar las condiciones de comprobación cuando el estado de la CPU se ha de preservar para su análisis o reanudación de la operación. Si un reinicio de la CPU está provocado por la activación de la clave de carga normal o de carga con volcado, (a) se puede configurar el modo de arquitectura a un modo por defecto, y (b) si la facilidad de

multihilo está instalada y habilitada, se deshabilita el multihilo. Cuando el reinicio de la CPU configura el modo por defecto, puede salvar la actual PSW para que la PSW se pueda restaurar.

Un reinicio inicial de la CPU proporciona las funciones de un reinicio de CPU junto con la inicialización de la actual PSW, el temporizador de la CPU, el comparador de reloj, y otros registros, tales como: la dirección del evento ruptura, la PSW capturada, el control, el control del punto flotante, el prefijo, y los registros programables TOD. El reinicio inicial de la CPU puede configurar el modo de arquitectura al modo por defecto si está provocado por la activación de la clave de carga normal o carga con volcado. Las funciones del reinicio inicial de la CPU se pueden realizar para la CPU con el número más bajo de un núcleo, y el reinicio de la CPU es realizado por todos las otras CPU en el núcleo. Un reinicio con borrado provoca el reinicio inicial de la CPU y el reinicio del subsistema para ser realizado y, de manera adicional, borra o inicializa todas las ubicaciones de almacenamiento y los registros en todas las CPU en la configuración, con la excepción del reloj TOD. El borrado no afecta al almacenamiento externo, tal como los dispositivos de almacenamiento por acceso directo usados por el programa de control para mantener los contenidos de las páginas no direccionables.

5

10

25

30

35

Un reinicio del encendido de la CPU provoca que se realice el reinicio inicial de la CPU y se borren los contenidos o los registros generales, los registros de acceso, los registros de control, y los registros de punto flotante a los valores de cero/por defecto con un código de bloqueo de comprobación válido. Se entenderá que el borrado o la inicialización de los estados no necesita que sean valores igual a cero sino que por defecto pueden ser valores distintos de cero en el estado borrado. Si un reinicio del encendido de la CPU establece la configuración, éste puede configurar el modo de arquitectura al modo por defecto, en otro caso, puede configurar el modo de arquitectura al de las CPU ya en configuración. El reinicio de la CPU, el reinicio de la CPU inicial, el reinicio del subsistema, y el reinicio con borrado se pueden iniciar de manera manual.

En realizaciones ejemplares, cada CPU tiene un número asignado, llamado su dirección de CPU. Una dirección de CPU identifica de manera única una CPU dentro de una configuración. Una CPU está designada especificando esta dirección en un campo de dirección de CPU de la instrucción SIGP. Una CPU que señaliza una alerta por malfuncionamiento, una señal de emergencia, o una llamada externa puede ser identificada mediante el almacenamiento de esta dirección en el campo de dirección de la CPU con la interrupción. La dirección de la CPU está asignada mediante un proceso de definición de la configuración y normalmente no se cambia como resultado de los cambios de reconfiguración. Un programa puede determinar la dirección de una CPU usando una instrucción de dirección de la CPU almacenada se puede usar también para identificar una dirección de CPU mediante la cual se identifica a una CPU en una configuración de multiprocesamiento.

Cuando se habilita el multihilo, la dirección de la CPU puede incluir una identificación del núcleo (una ID de núcleo), concatenada con una identificación de una CPU dentro del núcleo. La identificación de la CPU dentro de un núcleo es una identificación de hilo (ID de hilo, o TID). Dentro de una configuración, todos los núcleos proporcionan el mismo número de CPU; sin embargo, dependiendo del modelo y el tipo de CPU, algunas CPU en un núcleo pueden no ser operacionales.

Basado en la PSMTID del registro de parámetros usado por la orden de configuración de multihilo del procesador de señal, un número fijo de bits representa la identificación de hilo. Este número de bits es referido como la anchura de la TID.

La ID del núcleo puede estar formada a partir de los bits más a la derecha de la dirección de la CPU antes de que se habilite el multihilo. La ID de núcleo es desplazada a la izquierda por los bits de ancho de la TID, resultando en los bits más a la izquierda de la dirección de la CPU después de que el multihilo esté disponible. La ID de hilo tiene el mismo número de bits de la anchura de la TID, y ocupa los bits más a la derecha de la dirección de la CPU después de que se habilite el multihilo. Las ID de hilo se pueden asignar en un intervalo contiguo de números. La tabla 1 ilustra un ejemplo de relación de la PSMTID, la anchura de la TID y los bits de la dirección de la CPU que comprenden la identificación del núcleo y la identificación del hilo.

| PSMTID | Anchura de<br>la TID | Bits de la Dirección de la CPU |                |

|--------|----------------------|--------------------------------|----------------|

|        | W 1.12               | ID del núcleo                  | ID del<br>hilo |

| 0      | 0                    | 0-15                           | -              |

| 1      | 1                    | 0-14                           | 15             |

| 2-3    | 2                    | 0-13                           | 14-15          |

| 4-7    | 3                    | 0-12                           | 13-15          |

| 8-15   | 4                    | 0-11                           | 12-15          |

| 16-31  | 5                    | 0-10                           | 11-15          |

Tabla 1 – Ejemplo de mapeo de los bits de dirección

5

10

15

20

25

30

35

40

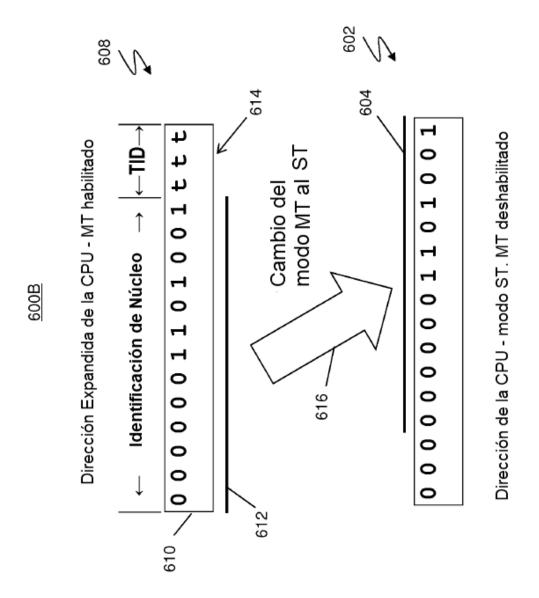

En la FIG. 6A se representa la expansión de la dirección como un ejemplo de un proceso 600A de expansión de la dirección de la PCU de acuerdo con una realización. En el bloque 602, un hilo principal se puede acceder en el modo ST usando un valor 604 de dirección de núcleo como un número de bits de la dirección de la CPU. La flecha 606 indica el cambio desde el modo ST al modo MT. En el bloque 608, el hilo principal o uno o más hilos secundarios se pueden acceder en el modo MT usando un valor 610 de dirección expandido. El valor 610 de dirección expandido incluye el valor 604 de la dirección de núcleo desplazado según un valor 612 de la dirección del núcleo desplazado y concatenado con un valor 614 de la dirección del hilo. El valor 612 de la dirección del núcleo desplazado es una identificación del núcleo (una ID del núcleo), y el valor 614 de la dirección del hilo es una identificación del hilo (TID). El valor 612 de la dirección del núcleo desplazado puede ser desplazado mediante una cantidad en base a la máxima identificación de hilo solicitado, por ejemplo, la PSMTID. Se puede determinar un número de bits de la TID en el valor 614 de dirección en base a la PSMTID mostrada en la tabla 1 anterior. El valor 614 de la dirección del hilo se puede concatenar a los bits de orden inferior del valor 612 de la dirección del núcleo desplazado para formar el valor 610 de la dirección expandida. Un valor 614 de la dirección del hilo de todo ceros designaría el hilo principal, y los valores mayores que cero identifican y direccionan los hilos secundarios.

Al cambiar entre el modo MT y el modo ST, se selecciona bien el valor 604 de la dirección del núcleo (modo ST) o el valor 610 de la dirección expandida (modo MT) para usar como una dirección de la CPU en un respectivo modo ST o MT. El valor 604 de la dirección del núcleo es un ejemplo de una dirección de formato estándar usada en el modo ST, y el núcleo vuelve desde el modo MT al modo ST en base al hecho de deshabilitar el modo MT. En una realización ejemplar, sólo el hilo principal (esto es, no los hilos secundarios) son accesibles en base al hecho de deshabilitar el modo MT. La FIG. 6B representa un ejemplo de un proceso 600B de contracción de la dirección de la CPU de acuerdo con una realización. La flecha 616 de la FIG. 6B ilustra el cambio desde el modo MT del bloque 608 de vuelta al modo ST del bloque 602, La reversión desde el modo MT al modo ST puede incluir el desplazamiento del valor 610 de la dirección expandida a la derecha y la eliminación del valor 614 de la dirección del hilo para formar una dirección con formato estándar que incluye el valor 604 de la dirección del núcleo (ID del núcleo) como la dirección de la CPU a partir del valor 612 de la dirección del núcleo desplazado.

Cuando una función de reinicio deshabilita el multihilo, (a) la dirección o las direcciones de la CPU o de las CPU que tienen la ID de hilo a cero se desplazan a la derecha el mismo número de bits de la anchura de la TID usada durante la habilitación, (b) se insertan los ceros en el número de bits de la anchura de la TID a la izquierda de la dirección, y (c) la dirección de la CPU se revierte a su formato original no multihilo (esto es, la dirección de formato estándar). Todas las CPU en un núcleo que tienen ID de hilo distinta de cero cuando se habilita el multihilo no son más operacionales cuando se deshabilita el multihilo.

Cuando el multihilo no está habilitado, la dirección de la CPU se mantiene sin cambios del valor asignado por el proceso de definición de la configuración. En este caso, no existe la identificación de hilo.

Un número de órdenes de los procesadores de señal pueden proporcionar las órdenes a las CPU incluyendo, por ejemplo, el inicio, la detenida, la reanudación, el estado de detención y almacenamiento, el reinicio inicial de la CPU, el estado del almacenamiento en la dirección, la configuración de la arquitectura, la detección del estado de ejecución, la configuración del multihilo, el estado adicional de almacenamiento en la dirección, y similares. Un reinicio inicial de la CPU o un reinicio de la CPU pueden ser iniciado por una instrucción del procesador de señal y no afecta al modo de arquitectura o a las otras CPU. No deshabilita el multihilo, y no provoca el reinicio de la I/O.

Una orden de configuración de la arquitectura especifica el modo de arquitectura al que se ha de configurar todas las CPU en la configuración. Las diferencias de arquitectura pueden incluir los diferentes modos de direccionamiento, las definiciones de registros, y las instrucciones soportadas por las CPU. Tras un cambio en el modo de arquitectura,

la selección de los campos de bits de los registros se puede configurar a un estado por defecto (por ejemplo, a cero), las memorias intermedias de traducción de acceso al registro anticipada (ALB) y las memorias intermedias de traducción anticipada (TLB) de todas las CPU en la configuración se borran, y la función de serialización y sincronización del punto de control se puede realizar en todas las CPU en la configuración.

- Una orden de detección del estado de ejecución puede indicar si una CPU direccionada está ejecutándose. En el modo ST, se puede devolver un indicador como estado de ejecución/no ejecución. En el modo MT, se puede usar un indicador para identificar si cualquier CPU del núcleo en el que la CPU direccionada es un miembro está ejecutándose, o todas las CPU del núcleo del que la CPU direccionada es un miembro no están ejecutándose.

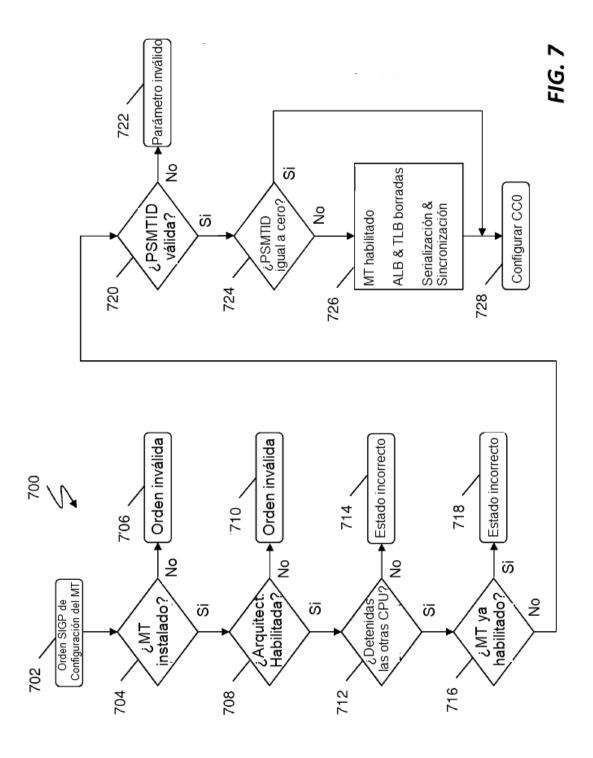

- Una orden de configuración MT habilita la facilidad de multihilo. Las posiciones de los bits de un registro de parámetros pueden contener la PSMTID a proporcionar en la configuración. La PSMTID se puede definir como uno menos que el número de CPU a hacer direccionables en cada núcleo. Por ejemplo, un valor de 3 en las posiciones de bit designadas indica que un máximo de cuatro hilos se han de proporcionar. Los contenidos de un registro de direcciones de CPU de la instrucción SIGP se pueden ignorar según se consideren direccionadas todas las CPU en la configuración. Si se acepta, la orden de configuración MT es completada por todas las CPU durante la ejecución de la instrucción .SIGP. Con referencia a la FIG. 7, se representa un proceso 700 para una orden 702 SIGP de configuración MT Se puede proporcionar una indicación de error y evitar la habilitación del modo MT en base a la determinación de que la orden 702 SIGP de configuración MT fue emitida con uno o más de: una orden inválida, un estado incorrecto, y un parámetro inválido, como se describe de manera adicional en la presente memoria en referencia al proceso 700 de la FIG. 7.

- Si la facilidad de multihilo no está instalada en el bloque 704 o la CPU no está habilitada en un modo 708 de arquitectura válido, entonces la orden de configuración MT no se acepta y se puede devolver una indicación de orden inválida en los bloques 706 o 710 respectivamente. Si las otras CPU en la configuración no están en el estado detenido o de comprobación detenida en el bloque 712, o si la configuración está ya habilitada para el multihilo en el bloque 716, la orden de configuración MT no se acepta y se puede devolver una indicación de estado incorrecto en el bloque 714 o 718 respectivamente.

- Si la PSMTID es inválida en el bloque 720, entonces la orden de configuración MT no se acepta y se puede devolver una indicación de parámetro inválido en el bloque 722. Cuando la PSMTID es cero en el bloque 724, la configuración no está habilitada para el multihilo, manteniéndose en el modo ST, y proporcionando cualquier estado como un código de condición en el bloque 728. En una realización ejemplar, cuando la PSMTID es válida y distinta de cero, en el bloque 726, se habilita la configuración para el multihilo, lo que resulta en una expansión de la dirección de la CPU. Las ALB y las TLB de todas las CPU en la configuración se borran de sus contenidos, y se realiza una función de serialización y sincronización del punto de control en todas las CPU en la configuración. Se puede proporcionar el estado en el bloque 728 en un código de condición. Tras la finalización con éxito, todas las CPU distintas a la CPU que ejecuta la orden de configuración de MT se mantienen en el estado detenido o de comprobación detenida. Sin embargo, si una CPU estaba en el estado de comprobación detenida antes de que se habilitase el multihilo, puede ser impredecible si las CPU que tienen ID de hilo distintos de cero en el mismo núcleo se colocan en el estado de detención o de comprobación detenida.

30

35

50

55

- Un contexto de hilo se puede referir también a un contexto del registro de arquitectura. Que el contexto del registro de arquitectura (esto es, los contenidos de la PSW, el temporizador de la CPU, el comparador de reloj, los registros generales, los registros de punto flotante y el registro de control de punto flotante, los registros de vector, los registros de control, los registros de acceso, el registro de prefijo, y el registro programable TOD, etc.) de cada CPU antes del multihilo esté habilitado resulta en que el contexto del registro de arquitectura de la CPU que tiene la TID a cero de cada respectivo núcleo después del multihilo esté habilitado. De manera similar, el contexto del registro de arquitectura de la CPU que tiene la TID a cero de cada núcleo de una configuración habilitada de MT resulta en que el contexto del registro de arquitectura de cada respectiva CPU cuando el multihilo está deshabilitado como resultado de la activación de la tecla de carga normal o carga con volcado.

- El contexto del registro de arquitectura de todas las CPU que tienen una identificación de hilo distinta de cero se puede conservar cuando la facilidad de multihilo se deshabilita como resultado de la activación de una operación de clave de carga normal o de carga con volcado. Si posteriormente la facilidad de multihilo se vuelve a habilitar sin la intervención de un reinicio de borrado, el contexto del registro de arquitectura de todas las CPU que tienen una identificación de hilo distinta de cero se restaura.

- Cuando el multihilo se vuelve a habilitar después haber sido deshabilitado por la activación de la clave de carga normal o de carga con volcado. Si el valor de la PSMTID en bits del registro de parámetros difiere del usado en la habilitación anterior, entonces el contexto de registro de la arquitectura de todas las CPU que tiene una ID de hilo distintas de cero puede ser impredecible.

Se puede usar una instrucción de información del sistema almacenada para almacenar la información sobre un componente o componentes de una configuración en un bloque de información del sistema (SYSIB). El SYSIB puede incluir un campo MT instalado, un campo MT general, un contador total de CPU/núcleos, un contador de CPU/núcleos configurados, un contador de CPU/núcleos de modo de espera, un contador de CPU/núcleos

reservados, y otros campos. El campo de MT instalada puede indicar si la facilidad de multihilo está instalada y puede también indicar la mayor TID soportada para un primer tipo de núcleo, por ejemplo, un tipo de núcleo especial. El campo general de MT puede indicar la mayor TID soportada para un segundo tipo de núcleo, por ejemplo, un tipo de núcleo general. La mayor TID soportada en el campo de MT general se puede limitar a ser menor o igual que la mayor TID soportada en el campo de MT instalada, El contador de CPU/núcleos totales puede indicar un número total de CPU generales o núcleos que comprenden CPU generales en la configuración, ya sea en el estado configurado, de espera, o reservado. El contador de CPU/núcleos configurados puede indicar el número de CPU generales o núcleos que comprenden CPU generales en el estado configurado, esto es, en la configuración y listos para ejecutar programas. El contador de CPU/núcleos en espera puede indicar el número de CPU generales o núcleos que comprenden CPU generales en el estado de espera. El contador de CPU/núcleos reservados puede indicar el número de CPU generales o núcleos que comprenden CPU generales en el estado reservado, esto es no disponibles para ser usados para ejecutar programas e incapaces de ser llevados al estado configurado.

10

15

20

55

60

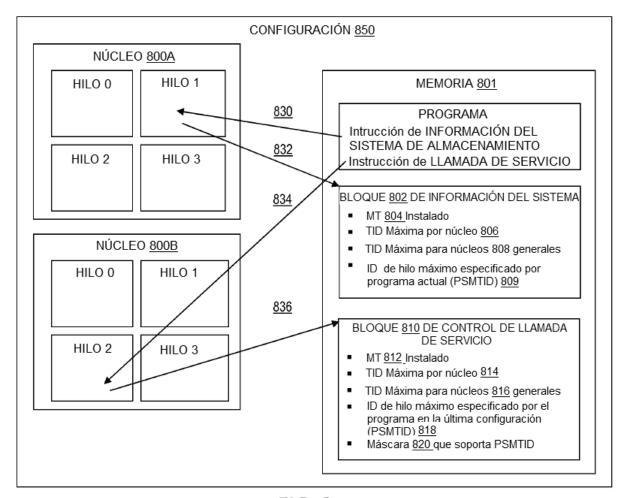

La FIG. 8 representa un ejemplo de almacenamiento de la información de la capacidad multihilo de acuerdo con una realización. Un programa que se ejecuta en un hilo, tal como un hilo1 del núcleo 800A, puede traer la instrucción 830 de INFORMACIÓN DEL SISTEMA DE ALMACENAMIENTO (STSI) de la memoria 801 de una configuración 850 tal como la LPAR. La ejecución de la instrucción de STSI puede resultar en el almacenamiento 832 de un bloque de información del sistema (SYSIB) 802. En el ejemplo de la FIG. 8, el SYSIB 802 incluye una identificación 804 de MT instalado que indica si la configuración 850 soporta el multihilo. El SYSIB 802 incluye también una identificación de hilo máximo del mayor hilo soportado por un núcleo 800A/800B que se puede proporcionar como una TID máxima por núcleo 806 para los núcleos especiales y una TID máxima para los núcleos 808 generales. El SYSIB 802 puede incluir también una identificación 809 de hilo máximo especificado por el programa actual (PSMTID). La PSMTID 809 actual refleja el modo multihilo como habilitado en la configuración 850 por el programa. La PSMTID 809 puede no definirse si la instrucción 830 STSI se ejecuta en un nivel máquina básico.

Un programa que se ejecuta en un hilo, tal como el hilo2 de un núcleo 800B, puede traer también una instrucción 25 834 LLAMADA DE SERVICIO (SERVC) desde la memoria 801 de la configuración 850, donde la instrucción especifica un comando de información del programa de control del sistema de lectura (información SCP de lectura, o RSCPI). La ejecución del comando RSCPI puede provocar que se almacene en 836 un bloque 810 de control de llamada de servicio (SCCB) en la memoria 801. En una realización ejemplar, el SCCB 810 almacenado por la ejecución del comando RSCPI proporciona información similar y adicional que puede no estar disponible en el 30 SYSIB 802. En el ejemplo de la FIG. 8, el SCCB 810 incluye una identificación 812 de MT instalado que indica si el núcleo 800B soporta multihilo. El SCCB 810 puede incluir una identificación de hilo máximo del hilo más alto soportado por el núcleo 800B que se puede proporcionar como la máxima TID para el núcleo 814 para los núcleos especiales y la máxima TID para los núcleos 816 generales. Los valores 812-816 del SCCB 810 son equivalentes a los valores 804-808 que pueden ser accesibles en el SYSIB 802. De manera adicional, el SCCB 810 puede incluir 35 una identificación de hilo máximo especificado por el programa en la última configuración de un hilo más alto soportado por el núcleo 800B, que es también referido como la identificación 818 de hilo máximo especificado por el programa en la última configuración (PSMTID). El SCCB 810 puede incluir también una máscara de valores del PSMTID aceptables en la orden de configuración del MT como la máscara 820 que soporta PSMTID. La máscara 820 que soporta PSMTID se puede usar para identificar las CPU/hilos cuando se desean menos que el número 40 definido por el TID máximo por núcleo 814.

Será entendido que los núcleos 800A y 800B incluyen otros aspectos que no están representados en este ejemplo. Además, el SYSIB 802 y el SCCB 810 pueden incluir valores adicionales más allá de los representados en el ejemplo de la FIG. 8.

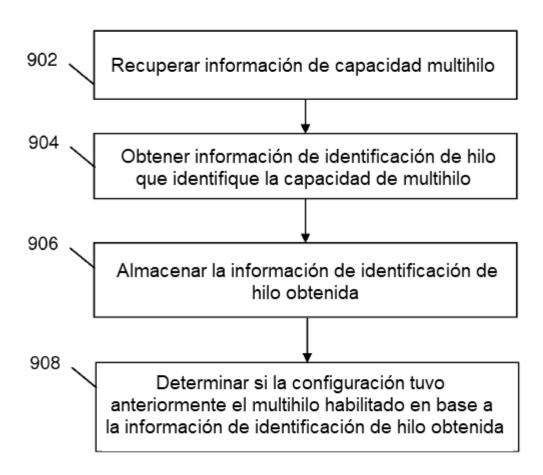

La FIG. 9 representa un flujo 900 de proceso para determinar la capacidad multihilo de acuerdo con una realización.

En el bloque 902, el núcleo ejecuta la recuperación de una instrucción de la información de capacidad multihilo (RMTCI), que puede ser, por ejemplo, cualquiera de entre una instrucción SERVC o una instrucción STSI. En el bloque 904, se obtiene la información de identificación de hilo que identifica la capacidad multihilo de una configuración. En el bloque 906, se almacena la información de identificación del hilo. En el bloque 908, se determina si la configuración tuvo anteriormente el multihilo habilitado en base a la información de identificación de hilo.

Como se describió anteriormente, la instrucción SERVC se configura para almacenar la información de identificación del hilo en un bloque de respuesta en memoria (por ejemplo, el SCCB 810 de la FIG. 8), y la instrucción STSI se configura para almacenar la información de identificación del hilo en un SYSIB en memoria (por ejemplo, el SYSIB 802 de la FIG. 8). La información de hilo obtenida puede incluir una identificación de MT instalado (por ejemplo, la identificación 804 o 812 de MT instalado de la FIG. 8) que indica si el núcleo soporta el multihilo. La información de hilo obtenida puede incluir también una identificación de hilo máximo de un hilo máximo portado por el núcleo (por ejemplo, valores máximos TID 806, 808, 814 o 816 de la FIG.8). La información de hilo obtenida puede incluir también una identificación de hilo máximo especificado por el programa actual (por ejemplo, una PSMTID 809 actual de la FIG. 8) y una identificación de hilo máximo especificado por el programa en la última configuración (por ejemplo, la PSMTID 818 actual de la FIG. 8). El bloque de respuesta puede incluir una máscara de bits que indica las identificaciones de hilo específicas que se soportan de manera individual (por ejemplo la máscara 820 que

soporta la PSMTID de la FIG. 8). La determinación de que la configuración anteriormente tuvo MT habilitado se puede basar en un valor distinto de cero en la identificación de hilo máximo especificado por el programa en la última configuración (por ejemplo, la PSMTID de última configuración >0). En una realización ejemplar, la configuración soporta una pluralidad de tipos de núcleos.

En realizaciones ejemplares, los registros y valores tales como los valores de los contadores de programa, que pueden ser incluidos en los registros o gestionados de manera separada, se capturan como contexto de hilo. Cuando se produce la expansión de dirección en el modo MT, resulta accesible el contexto de hilo adicional. Como se describió anteriormente en referencia a la FIG. 6, la dirección de la CPU está formada por cada núcleo de la configuración. La dirección de la CPU puede ser revisada por la instrucción de dirección de la CPU almacenada, aparece en otras estructuras, y se usa en varias órdenes SIGP. Cuando no está habilitado el MT, este esquema de direccionamiento se mantiene sin cambios. Cuando el MT está habilitado, la dirección de la CPU experimenta un proceso de expansión. Como se describió anteriormente, la parte no habilitada al MT de la dirección de la CPU se puede desplazar a la izquierda los suficientes bits para acomodar la TID. Por ejemplo, si un sistema operativo emite la orden de configuración MT del SIGP con un valor de la PSMTID de 1, la dirección de la CPU se desplazaría a la izquierda 1 bit; si la PSMTID fuera 2 o 3, la dirección de la CPU se desplazaría a la izquierda 2 bits, si la PSMTID es 4-7 la dirección de la CPU se desplazaría a la izquierda 3 bits, y así sucesivamente.

20

25

30

35

40

45

50

55

60

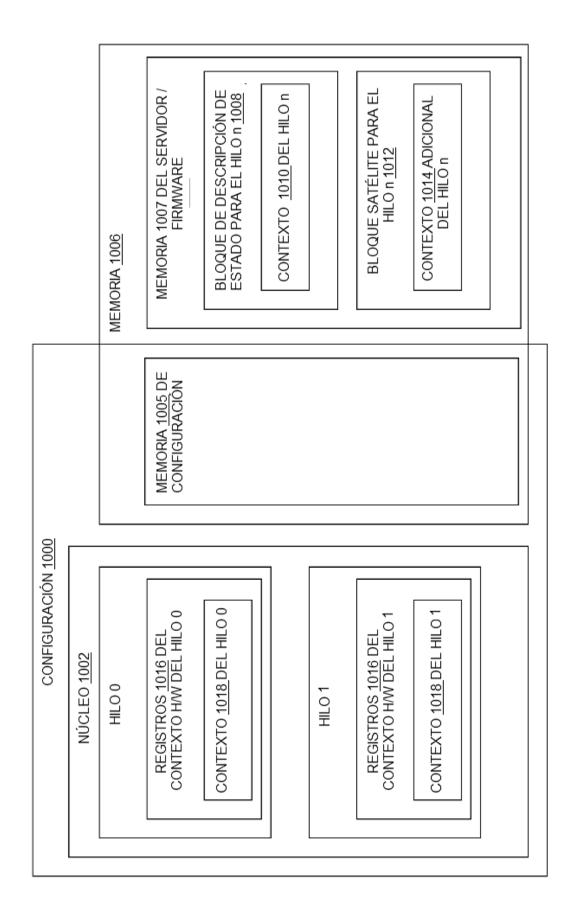

Cuando posteriormente se deshabilita el multihilo (como resultado de un reinicio con borrado o un reinicio de la CPU provocado por una operación de normal de carga), se produce la contracción de la dirección de la CPU. La dirección de la CPU con MT habilitado se puede desplazar a la derecha el mismo número de bits PSMTID usados en la orden de configuración MT del SIGP que habilita el MT, y la parte de la ID de hilo de la dirección desaparece. El contexto de hilo que está accesible durante el modo MT puede residir en una o más ubicaciones, tales como el ejemplo representado en la FIG. 10. En el ejemplo de la FIG. 10, una configuración 1000 incluye un núcleo 1002 y puede incluir otros núcleos (no representados). La memoria 1006 puede incluir la memoria 1005 de configuración como parte de la configuración 1000 y la memoria 1007 de servidor/firmware que está separada de la configuración 1000. La memoria 1007 servidor/firmware puede incluir un bloque 1008 de descripción de estado mantenido por un servidor, que puede almacenar un contexto 1010 de hilo para un hilo (por ejemplo, un hilo n en la FIG. 10). Un bloque 1012 satélite se puede anclar al bloque 1008 de descripción de estado en la memoria 1006 como parte de la memoria 1007 de servidor/firmware, donde el bloque 1012 satélite puede incluir un contexto 1014 de hilo como una alternativa al contexto 1010 de hilo o en combinación con el contexto 1010 de hilo. Cada hilo puede tener un bloque 1008 de descripción de estado correspondiente y de manera opcional un bloque 1012 satélite, donde se pueden almacenar el contexto 1010 de hilo o el contexto 1014 de hilo. Como una alternativa adicional, los registros 1016 de contexto hardware se pueden usar para almacenar un contexto 1018 de hilo, por ejemplo, en el núcleo 1002. Los ejemplos del contexto 1010, 1014, y 1018 de hilo se pueden usar en combinación o de manera separada como opciones de almacenamiento. Las opciones de almacenamiento alternativas se pueden emplear en las realizaciones. Independientemente de donde se mantenga el contexto de hilo, tras la contracción de la dirección el contexto de hilo no será más accesible de manera directa, pero se puede conservar el acceso mediante un programa de volcado.

Cuando el MT está deshabilitado, el proceso de contracción de la dirección de la CPU hace que los hilos 1-n de un núcleo no sean más direccionables; de manera similar, el contexto de hilo que incluye los registros de arquitectura no será más visible al programa. Si se deshabilitó el MT como resultado de un reinicio de la CPU que resulta de una operación de carga con borrado, el contexto de registro de los hilos 1-n se conserva; estos datos se pueden inspeccionar posteriormente si la configuración vuelve al modo MT. El contexto de registro para cada hilo invitado puede ser mantenido por un servidor en el bloque 1008 de descripción de estado del hilo (o como en el caso de los registros de vectores, en un bloque 1012 satélite anclado en la descripción de estado) como se representa en la FIG. 10.

La conservación del contexto de los hilos 1-n durante el proceso de deshabilitar el MT es una característica diagnóstica para el estado de los hilos a ser volcados después de un fallo del OS. Después de un fallo del OS, un operador puede elegir ejecutar un programa de volcado independiente (SADMP) para capturar la memoria y el contexto de hilo del sistema en el momento del fallo. Sin embargo, la carga del programa SADMP puede provocar que la configuración vuelva a un modo de arquitectura por defecto con el modo ST habilitado, por lo tanto se deshabilita el MT. Pero, ya que el SADMP es cargado por una operación de carga sin borrado, el contexto de registro de los hilos 1-n de cada núcleo se conserva. El SADMP puede determinar si el MT estaba habilitado en la configuración que es volcada examinando los resultados del bloque de respuesta del comando de información SCP de lectura del SERVC. Este número se puede usar posteriormente como entrada a la orden de configuración MT del SIGP para rehabilitar el MT en el mismo nivel que antes.

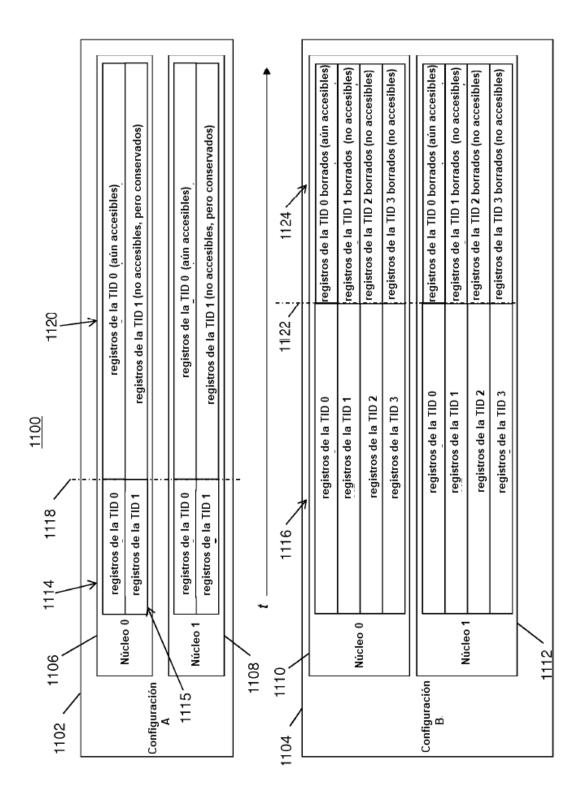

La FIG. 11 representa un ejemplo de conservación del registro de multihilo de acuerdo con una realización. Un sistema, tal como el sistema 1100 informático de la FIG. 11, puede incluir múltiples configuraciones 1102 y 1104. En el ejemplo de la FIG. 11, la configuración 1102 incluye el núcleo 1106 y el núcleo 1108, y la configuración 1104 incluye el núcleo 1110 y el núcleo 1112. Cada una de las configuraciones 1102 y 1104 se pueden cambiar independientemente entre los modos ST y MT en diferentes momentos. Cada una de las configuraciones 1102 y 1104 del sistema 1100 informático es configurable con un número diferente de ID de hilo máximo para soportar

habilitar de manera simultánea un número diferente de hilos en cada una de las configuraciones 1102 y 1104. En el ejemplo de la FIG. 11, los núcleos 1106 y 1108 soportan cada uno un máximo de dos hilos mientras la configuración 1102 está en el modo 1114 MT, mientras que los núcleos 1110 y 1112 soportan cada uno un máximo de cuatro hilos mientras la configuración 1104 esté en el modo 1116 MT.

- Mientras que esté habilitado el modo 1114 MT en la configuración 1102, tanto la TID 0 como la TID 1 son accesibles como contextos de hilo separados, así como ejemplos separados de contextos 1115 de hilo. En el momento 1118, el modo 1114 MT puede ser deshabilitado por una operación normal de carga o un reinicio sin borrado para la configuración 1102 que cambia ambos núcleos 1106 y 1108 en el modo 1120 ST. Debido a la contracción de la dirección como se describió anteriormente, los registros de la TID0 son accesibles en el modo 1120 ST; sin embargo, los registros de la TID1 que eran accesible en el modo 1114 MT se conservan pero no son más accesibles. Por ejemplo, los registros de la TID1 se pueden incrustar como el contexto 1010, 1014, o 1018 de hilo de la FIG. 10, donde una dirección que estaba disponible con la expansión de la dirección no es más accesible después de la contracción de la dirección tras cambiar al modo 1120 ST.

- Mientras que la configuración 1104 tenga el modo 1116 MT habilitado, los registros del TID0, TID1, TID2, y TID3 son 15 accesibles como un contexto de hilo separado, tal como ejemplos separados de los contextos 1010, 1014, o 1018 de hilo de la Flg. 10. En este ejemplo, la TID0 representa un hilo principal y la TID1-TID3 representan hilos secundarios que se mantienen de manera separada para cada uno de los núcleos 1110 y 1112. En el momento 1122, el modo 1116 MT puede ser deshabilitado mediante un reinicio con borrado para la configuración 1104, que cambia ambos núcleos 1110 y 1112 dentro del modo 1124 ST. El reinicio con borrado en el momento 1122 puede borrar todos los 20 registros de la TID0, TID1, TID2, y TID3. Debido a la contracción de la dirección como se describió anteriormente, los registros de la TID0 son accesibles en el modo 1124 ST; sin embargo, los registros de la TID1, TID2, y TID3 que eran accesibles en el modo 1116 MT se conservan en un estado borrado pero no más accesible. Como se representa en la FIG. 11, se pueden realizar las operaciones de manera independiente en cada configuración 1102 y 1104 en los diferentes momentos 1118 y 1122 con los efectos localizados a cada configuración 1102 y 1104. Por 25 tanto, la configuración 1102 puede estar en un modo 1120 ST mientras la configuración 1104 está en el modo 1116 MT, y los modos ST/MT no necesitan estar alineados para todas las configuraciones del sistema 1100 informático.

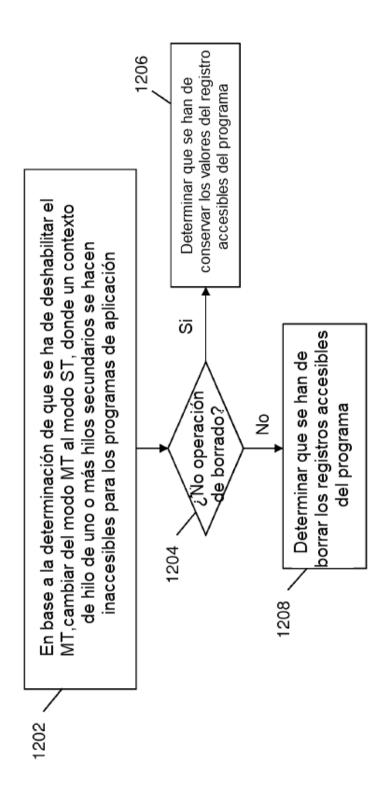

- La FIG. 12 representa un flujo 1200 de procesos para la conservación de registros de multihilo de acuerdo con una realización. En el bloque 1202, en base a la determinación por un núcleo en el modo MT, se ha de deshabilitar el MT en el núcleo, se realiza el cambio desde el modo MT al modo ST. El hilo principal del modo MT se puede mantener como el único hilo del modo ST. Uno o más contextos de hilo que incluyen valores de registros accesibles por el programa y valores de contadores del programa de los hilos secundarios se hacen inaccesibles a los programas de aplicación. En el bloque 1204, en base al cambio, se determina un tipo de operación (por ejemplo borrado contra no borrado) para bien realizar el borrado de los valores de los registros accesibles por el programa o conservar los valores de los registros accesibles por el programa. En el bloque 1206, en base a la operación de no borrado, se determinar que los valores de los registros accesibles por el programa se han de conservar. En el bloque 1208, en base a la operación de borrado, se determina que los registros accesibles por el programa se han de borrar.

30

35

40

45

50

- Como se describió anteriormente, los valores de los registros accesibles por el programa y los valores de los contadores del programa del contexto de hilo pueden incluir registros de programa de propósito general, registros de punto flotante, registros de control, registros de acceso, un registro de prefijo, y registros programables TOD. Los registros de control pueden incluir un registro de control en punto flotante, controles de instrumentación en tiempo de ejecución, controles de medición de la CPU, y similares. Otros ejemplos de registros que se pueden incluir en el contexto de hilo incluyen una palabra de estado de programa (por ejemplo, que incluye una dirección de contador/instrucción de programa, un código de condición, y otra información para controla la secuencia de instrucciones y para determinar el estado de la CPU), registros de vector, un temporizador de la CPU, un comparador de reloj, un registro de dirección de evento de ruptura, y otros registros conocidos en la técnica. Como se describió anteriormente, la PSMTID se configura en base a una instrucción del procesador de señal ejecutada con éxito que provocó que se habilitara el MT. En base al cambio al modo MT, los valores de registro accesibles por el programa se hacen accesibles a los programas de aplicación en base a los hilos secundarios correspondientes que se vuelven a habilitar. Por ejemplo, el cambio desde el modo 1120 ST de vuelta al modo 1114 MT en la FIG. 11 habilita que los registros de la TID1 sean accedidos, y la TID1 se puede volver a habilitar. El contexto de hilo se puede mantener en cualquiera de: un bloque de descripción de estado, un bloque satélite anclado al bloque de descripción de estado en la memoria, o un registro de contexto, tal como el contexto 1010, 1014, o 1018 de hilo de la FIG. 10.

- Un contexto de hilo principal puede incluir unos valores de registro accesibles por el programa y unos valores de contador del programa de un hilo principal, por ejemplo los registros de la TID0 y la TID0 para la configuración 1104 de la FIG. 11, donde el contexto de hilo principal es accesible para los programas de aplicación en tanto el modo 1124 ST como el modo 1116 MT. Un contexto secundario de hilo puede incluir los valores de registro accesibles por el programa y los valores del contador del programa de un hilo secundario, por ejemplo los registros de las TID1-TID3 y la TID1-TID3 para la configuración 1104 de la FIG. 11.

La FIG. 13 representa un ejemplo de restauración del registro de multihilo de acuerdo con una realización. El ejemplo de la FIG. 13 incluye un sistema 1300 informático con una configuración 1302 única. La configuración 1302 incluye el núcleo 1304, el núcleo 1306, y el núcleo 1308. Cada uno de los núcleos 1304-1308 incluye un máximo de cuatro hilos (TID0, TID1, TID2, y TID3) en este ejemplo. En el modo 1310 MT, todos los contextos de los hilos TID0-TID3 están disponibles en los núcleos 1304-1308. En el momento 1312, el modo 1310 MT puede ser deshabilitado por una operación normal de carga o un reinicio sin borrado de la configuración 1302, que cambia los núcleos 1304-1308 en el modo 1314 ST. En el modo 1314 ST, los registros de la TID0 permanecen accesibles, y los registros del TID1-TID3 están inaccesibles per se conservan para cada uno de los núcleos 1304- 1308. En el momento 1316, el MT se puede volver a habilitar mediante la ejecución de una orden de configuración de MT del SIGP para entrar a un modo 1318 MT reanudado. En el modo 1318 MT reanudado, se restaura el acceso al contexto de los hilos de los registros de la TID1-TID3 para cada uno de los núcleos 1304-1308. Esto habilita la inspección de todos los registros de los hilos, incluyendo los registros de la TID1-TID3, mediante un programa de volcado, tal como un programa 1320 de volcado independiente, para salvar la información de contexto del hilo para su análisis.

5

10

15

20

25

30

35

40

45

50

55

La FIG. 14 representa un flujo 1400 de proceso para la restauración de un registro multihilo de acuerdo con una realización tal como se puede emplear por un programa de volcado independiente (SADMP), tal como el programa 1320 de volcado independiente de la FIG. 13, para capturar el contexto del registro de arquitectura de los hilos que siguen al fallo de un sistema operativo. En el bloque 1405, se carga un programa SADMP a través de una operación de carga sin borrado (por ejemplo, una carga normal o una carga con volcado). La operación de carga sin borrado provoca implícitamente que la configuración vuelva al modo ST, tal como al modo 1314 ST para la configuración 1302 de la FIG. 13. El programa SADMP puede consultar después si la facilidad MT está disponible en la configuración en el bloque 1410 usando la instrucción STSI o SERVC. Si el MT está instalado, el programa SADMP consulta la configuración de la identificación de hilo máximo especificado por el programa en la última configuración del programa (PSMTID) en busca de la configuración en el bloque 1415. Si el MT nunca se hubo configurado anteriormente para la configuración, el valor de la PSMTID de la última configuración será cero. El programa SADMP puede ejecutar entonces la instrucción para volver a habilitar el multihilo en el bloque 1420 cualquiera que fuera la PSMTID de la última configuración (incluso si esta fue cero). Si la consulta en el bloque 1410 revela que el MT no está instalado, entonces no se hacen intentos para consultar el valor de la PSMTID de la última configuración en el bloque 1415 o para volver a habilitar el MT en el bloque 1420.

El programa SADMP intenta señalizar cada otra CPU (hilo) en la configuración para salvar su contexto del registro de arquitectura en una ubicación predefinida en memoria. Si el MT no se habilitó anteriormente antes de cargar el SADMP; las direcciones de la PCU son las normales, con el formato no expandido. Si el MT se habilitó anteriormente, las direcciones de la CPU tienen el formato expandido que incluye una ID de núcleo y una ID de hilo. El SADMP comienza con una dirección (N) de CPU de cero en el bloque 1425, y determina si la dirección de la CPU representa la CPU sobre la cual el SADMP se está ejecutando en el bloque 1430. Si es así, se salta esa CPU/hilo, y N se incremente al siguiente valor en el bloque 1450. Si N difiere de la dirección de la CPU actual, entonces esa CPU/hilo se señaliza para almacenar su contexto de registro de arquitectura en memoria, por ejemplo, mediante la ejecución de bien una orden para almacenar el estado en la dirección del SIGP o una orden para detenerse y almacenar el estado del SIGP en el bloque 1435. Si la configuración incluye una facilidad de vector, se puede ejecutar también una orden para almacenar el estado adicional en la dirección del SIGP para almacenar los contenidos de los registros de vector de la CPU/hilo. Se toma la determinación según si la señal del bloque 1435 fue exitosa en el bloque 1440. Si fue exitosa, el programa SADMP puede salvar el contexto del registro de la CPU/hilo en un archivo de volcado en cinta o disco en el bloque 1445, y el procesamiento continúa aumentando N en el bloque 1450. Si la señal del bloque 1435 no fue exitosa (por ejemplo, si el hilo no es operacional) según se determine por el bloque 1440, entonces se salta, y el procesamiento continúa aumentando N en el bloque 1450. El valor de la dirección de CPU usado en la señalización (N) es aumentado en el bloque 1450, y se toma la determinación según si N es ahora mayor que la dirección de CPU más alta posible para la configuración en el bloque 1455. SI N no es mayor que la dirección de la CPU más alta posible para la configuración, entonces el procesamiento continúa determinando si N representa la CPU/hilo actual bajo la cual el programa SADMP se está ejecutando en el bloque 1430. Si N es mayor que la dirección más alta posible de la CPU para la configuración, entonces la restauración del contexto del registro de arquitectura y el volcado se completan en el bloque 1460.