# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

①Número de publicación: 2 686 699

51 Int. Cl.:

H04N 21/2343 (2011.01) H04N 19/44 (2014.01) H04N 19/187 (2014.01) H04N 21/45 (2011.01) H04N 21/81 (2011.01) H04N 19/70 (2014.01) H04N 19/66 (2014.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 01.05.2015 PCT/US2015/028841

(87) Fecha y número de publicación internacional: 05.11.2015 WO15168591

96) Fecha de presentación y número de la solicitud europea: 01.05.2015 E 15722859 (4)

(97) Fecha y número de publicación de la concesión europea: 13.06.2018 EP 3138290

(54) Título: Procedimiento y dispositivo para descodificar datos de vídeo de múltiples capas determinando la capacidad del descodificador basándose en el perfil, grado y nivel asociados con la partición que contiene una o más capas

(30) Prioridad:

01.05.2014 US 201461987463 P 15.05.2014 US 201461993980 P 30.04.2015 US 201514701004

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 19.10.2018 (73) Titular/es:

QUALCOMM INCORPORATED (100.0%) Attn: International IP Administration, 5775 Morehouse Drive San Diego, CA 92121-1714, US

(72) Inventor/es:

RAMASUBRAMONIAN, ADARSH KRISHNAN; WANG, YE-KUI; HENDRY, FNU y RAPAKA, KRISHNAKANTH

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

## **DESCRIPCIÓN**

Procedimiento y dispositivo para descodificar datos de vídeo de múltiples capas determinando la capacidad del descodificador basándose en el perfil, grado y nivel asociados con la partición que contiene una o más capas

#### CAMPO TÉCNICO

[0001] Esta divulgación se refiere a la codificación y descodificación de vídeo.

#### 10 ANTECEDENTES

5

15

20

25

30

35

40

55

60

65

[0002] Las capacidades del vídeo digital pueden incorporarse en una amplia gama de dispositivos, incluyendo televisores digitales, sistemas de radiodifusión directa digital, sistemas de radiodifusión inalámbrica, asistentes digitales personales (PDA), ordenadores portátiles o de escritorio, ordenadores de tableta, lectores de libros electrónicos, cámaras digitales, dispositivos de grabación digital, reproductores de medios digitales, dispositivos de videojuegos, consolas de videojuegos, teléfonos celulares o de radio por satélite, los denominados "teléfonos inteligentes", dispositivos de videoconferencia, dispositivos de transmisión continua de vídeo y similares. Los dispositivos de vídeo digitales implementan técnicas de compresión de vídeo, tales como las descritas en los estándares definidos por MPEG-2, MPEG-4, ITU-T H.264, ITU-T H.264/MPEG-4, Parte 10, Codificación Avanzada de Vídeo (AVC), el estándar de Codificación de Vídeo de Alta Eficacia (HEVC) actualmente en desarrollo y las ampliaciones de dichos estándares. Los dispositivos de vídeo pueden transmitir, recibir, codificar, descodificar y/o almacenar información de vídeo digital más eficazmente, implementando dichas técnicas de compresión de vídeo.

[0003] Las técnicas de compresión de vídeo realizan la predicción espacial (intra-imagen) y/o la predicción temporal (entre imágenes) para reducir o eliminar la redundancia intrínseca en las secuencias de vídeo. Para la codificación de vídeo basada en bloques, un fragmento de vídeo (es decir, una trama de vídeo o una parte de una trama de vídeo) puede dividirse en bloques de vídeo. Los bloques de vídeo en un fragmento intra-codificado (I) de una imagen se codifican mediante predicción espacial con respecto a muestras de referencia en bloques contiguos en la misma imagen. Los bloques de vídeo en un fragmento inter-codificado (P o B) de una imagen pueden usar predicción espacial con respecto a muestras de referencia en bloques contiguos en la misma imagen, o predicción temporal con respecto a muestras de referencia en otras imágenes de referencia. Las imágenes pueden denominarse tramas, y las imágenes de referencia pueden denominarse tramas de referencia.

[0004] La predicción espacial o temporal da como resultado un bloque predictivo para un bloque a codificar. Los datos residuales representan diferencias de píxeles entre el bloque original a codificar y el bloque predictivo. Un bloque intercodificado se codifica de acuerdo con un vector de movimiento que apunta a un bloque de muestras de referencia que forman el bloque predictivo, y los datos residuales indican la diferencia entre el bloque codificado y el bloque predictivo. Un bloque intra-codificado se codifica de acuerdo con un modo de intra-codificación y los datos residuales. Para una mayor compresión, los datos residuales pueden transformarse desde el dominio del píxel a un dominio de transformación, dando como resultado coeficientes residuales, los cuales pueden cuantificarse posteriormente. Los coeficientes cuantificados, inicialmente dispuestos en una formación bidimensional, pueden recorrerse con el fin de producir un vector unidimensional de coeficientes, y puede aplicarse la codificación por entropía para lograr aún más compresión.

[0005] Un flujo de bits de codificación de múltiples visualizaciones puede generarse codificando visualizaciones, por ejemplo, desde múltiples perspectivas. Se han desarrollado algunos estándares de vídeo tridimensionales (3D) que hacen uso de aspectos de codificación de múltiples visualizaciones. Por ejemplo, diferentes visualizaciones pueden transmitir visualizaciones de ojo izquierdo y derecho para soportar vídeo 3D. De forma alternativa, algunos procesos de codificación de vídeo 3D pueden aplicar la denominada codificación de múltiples visualizaciones más profundidad. En la codificación de múltiples visualizaciones más profundidad, un flujo de bits de vídeo 3D puede contener no solo componentes de visualización de textura, sino también componentes de visualización de profundidad. Por ejemplo, cada visualización puede comprender un componente de visualización de textura y un componente de visualización de profundidad.

## RESUMEN

[0006] En general, esta divulgación describe técnicas de descripción de propiedades de flujo de bits de vídeo usadas para determinar, basándose en el perfil, grado y nivel de información especificada para las respectivas particiones de flujo de bits de vídeo, la capacidad de un descodificador de vídeo para descodificar un flujo de bits de vídeo.

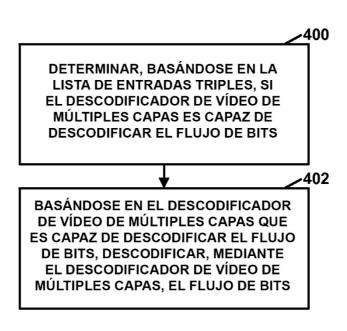

[0007] En otro ejemplo, esta divulgación describe un procedimiento de descodificación de datos de vídeo de múltiples capas, comprendiendo el procedimiento: determinar, basándose en una lista de entradas triples, si un descodificador de vídeo de múltiples capas es capaz de descodificar un flujo de bits que comprende una representación codificada de los datos de vídeo de múltiples capas, en el que cada entrada triple respectiva en la lista de entradas triples indica un perfil, un grado y un nivel para un descodificador de capa única respectivo en el

descodificador de vídeo de múltiples capas; y basándose en que el descodificador de vídeo de múltiples capas es capaz de descodificar el flujo de bits, descodificar, mediante el descodificador de vídeo de múltiples capas, el flujo de bits.

- [0008] En otro ejemplo, esta divulgación describe un dispositivo para descodificar datos de vídeo de múltiples capas, comprendiendo el dispositivo: uno o más medios de almacenamiento legibles por ordenador configurados para almacenar los datos de vídeo de múltiples capas; y uno o más procesadores configurados para: determinar basándose en una lista de entradas triples, si un descodificador de múltiples capas es capaz de descodificar un flujo de bits que comprende una representación codificada de los datos de vídeo de múltiples capas, en el que cada entrada triple respectiva en la lista de las entradas triples indica un perfil, un grado y un nivel para un descodificador de capa única respectivo en el descodificador de vídeo de múltiples capas.

- [0009] En otro ejemplo, esta divulgación describe un dispositivo para descodificar datos de vídeo, comprendiendo el dispositivo: medios para determinar, basándose en una lista de entradas triples, si el dispositivo es capaz de descodificar un flujo de bits que comprende una representación codificada de los datos de vídeo de múltiples capas, en el que cada entrada triple respectiva en la lista de entradas triples indica un perfil, un grado y un nivel para un descodificador de capa única respectivo en el dispositivo; y un medio para descodificar, basándose en que el dispositivo es capaz de descodificar el flujo de bits, el flujo de bits.

- 20 [0010] En otro ejemplo, esta divulgación describe un medio de almacenamiento de datos legible por ordenador que comprende instrucciones almacenadas en el mismo que, cuando se ejecutan, hacen que un descodificador de vídeo de múltiples capas: determine, basándose en la lista de entradas triples, si el descodificador de vídeo de múltiples capas es capaz de descodificar un flujo de bits que comprende una representación codificada de datos de vídeo de múltiples capas, en el que cada entrada triple respectiva en la lista de entradas triples indica un perfil, un grado y un nivel para un descodificador de capa única respectivo en el descodificador de vídeo de múltiples capas; y basándose en que el descodificador de vídeo de múltiples capas es capaz de descodificar el flujo de bits, descodificar el flujo de bits.

- [0011] Los detalles de uno o más ejemplos de la divulgación se exponen en los dibujos adjuntos y la descripción siguiente. Otras características, objetivos y ventajas resultarán evidentes a partir de la descripción, los dibujos y las reivindicaciones.

#### **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

## 35 **[0012]**

55

65

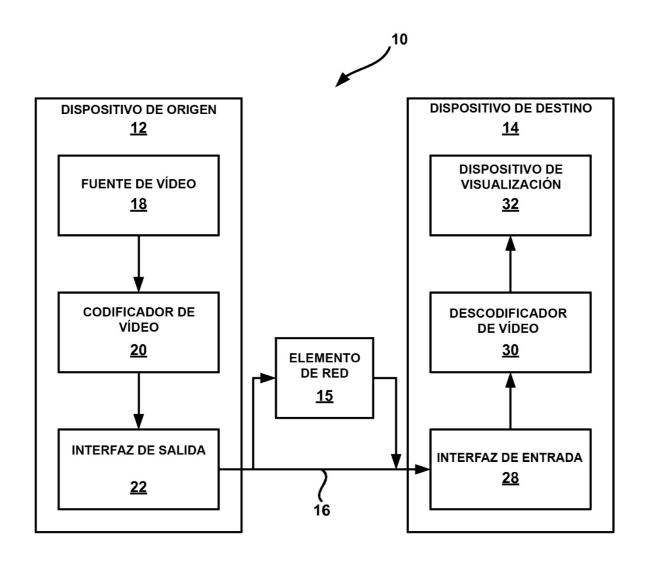

- La FIG. 1 es un diagrama de bloques que ilustra un sistema de codificación de vídeo de ejemplo que puede utilizar las técnicas descritas en esta divulgación.

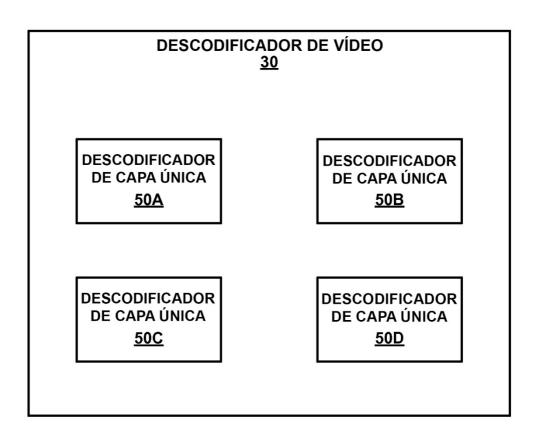

- 40 La FIG. 2 es un diagrama de bloques que ilustra un ejemplo de implementación de un descodificador de vídeo, que comprende una pluralidad de descodificadores de capa única, de acuerdo con una técnica de esta divulgación.

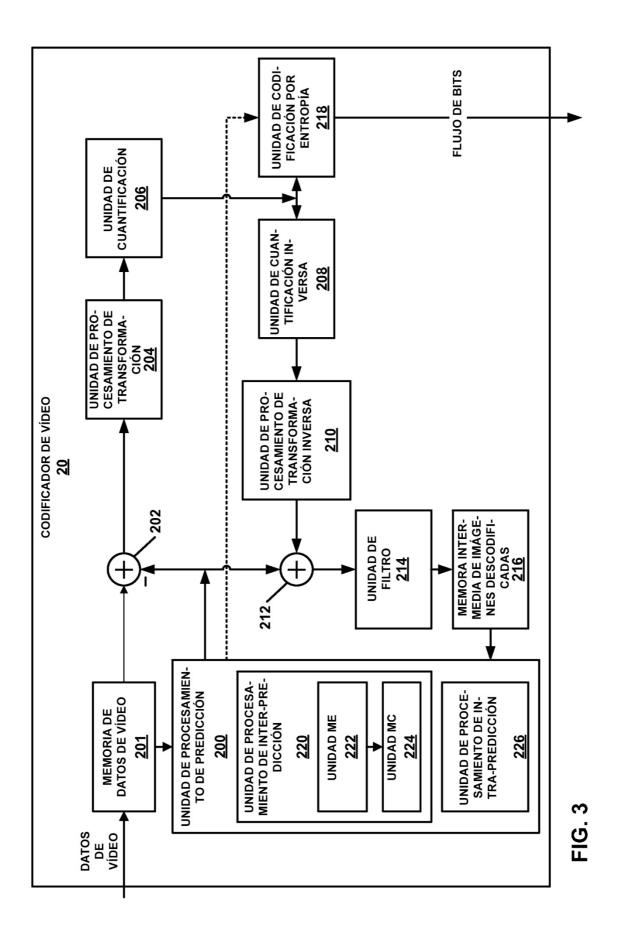

- La FIG. 3 es un diagrama de bloques que ilustra un ejemplo de codificador de vídeo que puede implementar las técnicas descritas en esta divulgación.

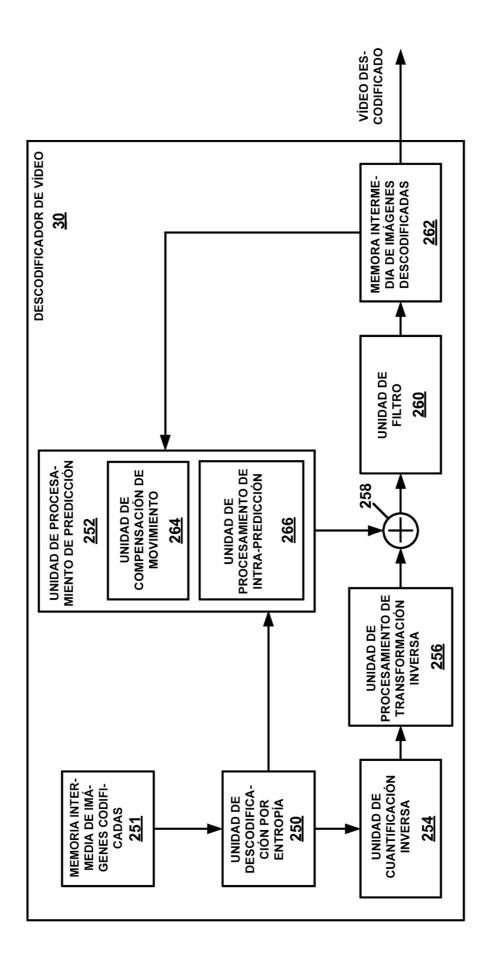

- La FIG. 4 es un diagrama de bloques que ilustra un ejemplo de descodificador de vídeo que puede implementar las técnicas descritas en esta divulgación.

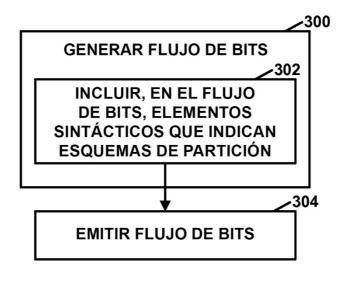

- La FIG. 5A es un diagrama de flujo que ilustra un ejemplo de funcionamiento de un codificador de vídeo, de acuerdo con una técnica de esta divulgación.

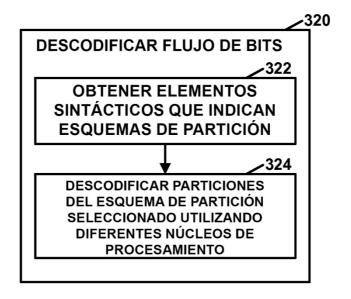

- La FIG. 5B es un diagrama de flujo que ilustra un ejemplo de funcionamiento de un descodificador de vídeo de acuerdo con una técnica de esta divulgación.

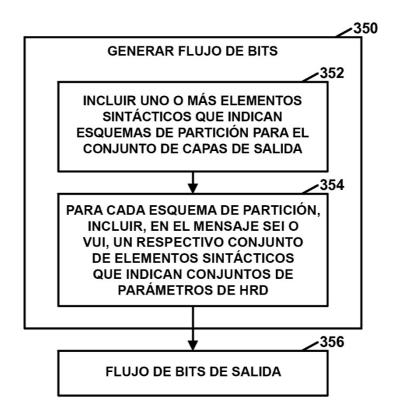

- La FIG. 6A es un diagrama de flujo que ilustra un ejemplo de funcionamiento de un codificador de vídeo, de acuerdo con una técnica de esta divulgación.

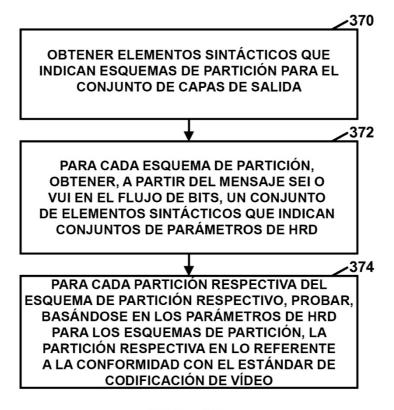

- La FIG. 6B es un diagrama de flujo que ilustra un ejemplo de funcionamiento de un descodificador de vídeo de acuerdo con una técnica de esta divulgación.

- La FIG. 7 es un diagrama de flujo que ilustra un ejemplo de funcionamiento de un descodificador de vídeo de acuerdo con una técnica de esta divulgación.

## DESCRIPCIÓN DETALLADA

[0013] Un flujo de bits (es decir, un flujo de bits de vídeo) puede comprender una representación codificada de datos de vídeo. Más específicamente, el flujo de bits puede comprender una serie de unidades de capa de abstracción de red (NAL). Cada una de las unidades NAL puede incluir una cabecera de unidad NAL y una carga útil de secuencia de bytes sin procesar (RBSP). En la codificación de vídeo de múltiples capas, las unidades NAL pueden corresponder a varias capas de datos de vídeo. En la codificación de vídeo escalable, las capas pueden incluir una capa base y una o más capas de mejora. En la codificación de múltiples visualizaciones, cada una de las capas puede corresponder a diferentes visualizaciones, tales como diferentes visualizaciones de una escena de vídeo.

[0014] Ciertos estándares de codificación de vídeo, tales como codificación de vídeo de alta eficiencia (HEVC), definen varios perfiles, grados y niveles diferentes. En general, un "perfil" de un estándar de codificación de vídeo es un subconjunto de las características y herramientas presentes en el estándar de codificación de vídeo. En otras palabras, un perfil define qué herramientas de codificación pueden usarse. Por ejemplo, para un codificador de vídeo, se puede establecer un perfil de herramientas de codificación que el codificador de vídeo puede usar para generar flujos de bits codificados que conforman dicho perfil. Para un descodificador de vídeo, un perfil puede significar el conjunto de herramientas de codificación que el descodificador de vídeo debe tener para poder descodificar flujos de bits que se dice que se ajustan a dicho perfil.

20

25

30

35

40

45

50

55

60

65

[0015] Un nivel es un conjunto definido de restricciones de los valores que pueden ser adoptadas por los elementos sintácticos y las variables de un estándar de compresión de vídeo. Un grado es una categoría específica de restricciones de nivel impuestas a valores de los elementos sintácticos en el flujo de bits o valores de variables, donde las restricciones de nivel están agrupadas dentro de un grado y un descodificador conforme a un cierto grado y nivel sería capaz de descodificar todos los flujos de bits que se ajustan al mismo grado o al grado inferior de ese nivel o cualquier nivel por debajo de ese nivel. De este modo, un nivel de un grado es un conjunto especificado de restricciones impuestas en los valores de los elementos sintácticos en el flujo de bits o variables utilizadas en la descodificación del flujo de bits.

[0016] Diferentes descodificadores de vídeo pueden tener diferentes capacidades. Por ejemplo, un descodificador de vídeo puede ser capaz de descodificar flujos de bits que se ajustan a un primer perfil, pero puede que no sea capaz de descodificar flujos de bits que se ajustan a un segundo perfil. En este ejemplo, otro descodificador de vídeo puede descodificar flujos de bits que se ajustan al primer perfil y al segundo perfil. Por ejemplo, con capas escalables de codificación de vídeo, el nivel de calidad de vídeo que se puede lograr puede escalarse a través de capas de modo que algunos dispositivos solo pueden descodificar y presentar un nivel básico de calidad de vídeo, mientras que otros dispositivos pueden descodificar y presentar una calidad de vídeo mejorada. Además, las capas escalables pueden permitir una recepción de datos de vídeo más fiable cuando el ancho de banda de canal es limitado; por ejemplo, un ancho de banda limitado puede ser suficiente para la comunicación de datos de vídeo de la capa base y canales de ancho de banda más robusto pueden permitir la comunicación de datos de vídeo de capas base y de mejora. En general, si un primer procesador puede descodificar flujos de bits que se ajustan a perfiles, grados y niveles que son un superconjunto de perfiles, grados y niveles que pueden ser descodificados por un segundo procesador, el primer procesador es más complejo y por lo tanto tiende a ser más caro.

[0017] De forma similar, con la codificación de múltiples visualizaciones, algunos dispositivos pueden descodificar múltiples visualizaciones, mientras que otros dispositivos pueden solo pueden tener la capacidad de descodificar un número limitado de visualizaciones. Las restricciones del ancho de banda del canal también pueden utilizarse de manera más efectiva mediante la codificación de múltiples visualizaciones, de modo que un número limitado de visualizaciones puede descodificarse cuando el ancho de banda es limitado y un mayor número de visualizaciones puede descodificarse cuando lo permite el ancho de banda.

[0018] En algunos casos, un descodificador de vídeo comprende múltiples núcleos de hardware (por ejemplo, unidades de procesamiento o módulos de procesamiento). En otras palabras, un descodificador de vídeo puede construirse utilizando una pluralidad de núcleos de hardware. Cada uno de los núcleos de hardware puede ser capaz de descodificar independientemente al menos elementos sintácticos de bajo nivel de un flujo de bits. Los diferentes núcleos pueden ser similares o diferentes en sus capacidades de procesamiento, pero, independientemente de ello, la presencia de múltiples núcleos puede proporcionar ventajas de procesamiento respecto a los descodificadores de núcleo único. En algunos ejemplos, un descodificador de vídeo que comprende múltiples núcleos de hardware puede descodificar múltiples partes de un flujo de bits en paralelo. Por ejemplo, algunos núcleos de procesamiento pueden implementar un descodificador de capa única. Un descodificador de capa única puede descodificar una capa única de un flujo de bits, tal como una capa base de vídeo escalable o una visualización particular en vídeo de múltiples visualizaciones. Por el contrario, un descodificador de múltiples capas puede descodificar múltiples capas de un flujo de bits simultáneamente (es decir, en paralelo). En un ejemplo, un solo núcleo de hardware es capaz de descodificar más de una capa.

[0019] Diferentes núcleos de hardware de un descodificador de vídeo pueden tener diferentes capacidades. Por ejemplo, un núcleo de hardware de un descodificador de vídeo puede descodificar flujos de bits que se ajusten a un primer perfil, pero no a un segundo perfil, mientras que un segundo núcleo de hardware de un descodificador de vídeo puede descodificar flujos de bits que se ajusten al primer perfil y al segundo perfil. Un descodificador de vídeo

puede tener núcleos de hardware que tienen diferentes capacidades con el fin de mantener el coste general del descodificador de vídeo lo más bajo posible, dado el propósito pretendido del descodificador de vídeo.

[0020] Típicamente, en casos donde un descodificador de vídeo comprende múltiples núcleos de hardware, el descodificador de vídeo determina, basándose en la información de perfil, grado y nivel señalado en un flujo de bits, si un núcleo de hardware con más capacidad del descodificador de vídeo puede descodificar el flujo de bits. Si es así, el descodificador de vídeo determina que es capaz de descodificar el flujo de bits. Este proceso no permite que el descodificador de vídeo determine si alguno de los núcleos de hardware con menos capacidad del descodificador de vídeo puede ayudar en el proceso de descodificación del flujo de bits. Como resultado, los núcleos de hardware con menos capacidad pueden estar inactivos, mientras que el núcleo de hardware con más capacidad descodifica todo el flujo de bits. Sin embargo, los núcleos de hardware con menos capacidad del descodificador de vídeo pueden, de hecho, ser capaces de descodificar capas particulares del flujo de bits en paralelo con el núcleo de hardware con más capacidad del descodificador de vídeo. Como resultado, no usar los núcleos de hardware con menos capacidad puede prolongar innecesariamente los tiempos de descodificación.

5

10

15

20

25

30

35

40

45

50

55

60

65

[0021] Algunas técnicas de esta divulgación pueden facilitar reducciones en los tiempos de descodificación en descodificadores de vídeo que tienen núcleos de hardware con diferentes capacidades. Por ejemplo, algunas técnicas de esta divulgación pueden disminuir los tiempos de descodificación en los descodificadores de vídeo construidos basándose en múltiples descodificadores de capa única que tienen diferentes capacidades. Esta reducción en los tiempos de descodificación en relación con las técnicas más convencionales se puede lograr sin cambiar los núcleos de hardware en sí (por ejemplo, sin modificar las estructuras físicas de los núcleos de hardware). Además, cuando los núcleos de hardware tienen las mismas capacidades, algunas técnicas de esta divulgación pueden permitir a los descodificadores de vídeo descodificar más capas en paralelo.

[0022] De acuerdo con una técnica de ejemplo de esta divulgación, un descodificador de vídeo puede descodificar un flujo de bits que comprende una representación codificada de datos de vídeo. En este ejemplo, el flujo de bits comprende una pluralidad de capas. Como parte de la descodificación del flujo de bits, el descodificador de vídeo puede obtener, a partir del flujo de bits, uno o más elementos sintácticos que indican uno o más esquemas de partición. Para cada esquema de partición respectivo del uno o más esquemas de partición, el esquema de partición respectivo especifica un conjunto respectivo de particiones disjuntas cuya unión forma un conjunto de capas de salida. Cada partición respectiva del conjunto respectivo de particiones disjuntas contiene una o más de las capas. Por lo tanto, una partición puede ser un tipo particular de sub-flujo de bits del flujo de bits. El conjunto de capas de salida puede consistir en todas las capas de la pluralidad de capas o un subconjunto adecuado de la pluralidad de capas. Además, el descodificador de vídeo puede descodificar cada una de las particiones de un esquema de partición particular usando diferentes núcleos de procesamiento en una pluralidad de núcleos de hardware, siendo el esquema de partición particular uno de los uno o más esquemas de partición.

[0023] En algunos ejemplos, para cada partición respectiva de cada esquema de partición respectivo del uno o más esquemas de partición, el descodificador de vídeo obtiene, del flujo de bits, un elemento sintáctico respectivo que indica información de perfil, grado y nivel (PTL) respectiva para la partición respectiva. En algunos casos, el descodificador de vídeo puede seleccionar, basándose en la información de PTL para las particiones de los esquemas de partición, un esquema de partición del uno o más esquemas de partición. En algunos casos, el descodificador de vídeo puede recibir el flujo de bits de acuerdo con un esquema de partición particular como lo determinan los recursos de red disponibles. El descodificador de vídeo puede descodificar cada partición respectiva del esquema de partición particular usando uno respectivo de los núcleos de hardware. Cada uno de los respectivos núcleos de hardware puede implementar un descodificador de capa única respectivo. En algunos casos, un núcleo de hardware del descodificador de vídeo puede ser capaz de descodificar más de una capa.

[0024] Las técnicas adicionales de esta divulgación pueden proporcionar pruebas de conformidad de flujo de bits usando las particiones de flujo de bits. Por ejemplo, un dispositivo de procesamiento de vídeo (tal como un codificador de vídeo, descodificador de vídeo u otro dispositivo) puede descodificar un flujo de bits que comprende una representación codificada de datos de vídeo. El flujo de bits puede comprender una pluralidad de capas. Como parte de la descodificación del flujo de bits, el descodificador de vídeo puede obtener, a partir del flujo de bits, uno o más elementos sintácticos que indican uno o más esquemas de partición para un conjunto de capas de salida. En estos tipos de ejemplos, el conjunto de capas de salida puede consistir en todas las capas de la pluralidad de capas o un subconjunto adecuado de la pluralidad de capas (por ejemplo, no todas las capas de la pluralidad de capas). Además, para cada esquema de partición respectivo del uno o más esquemas de partición, el esquema de partición respectivo puede especificar una división de la capa de salida establecida en una o más particiones. Cada capa en el conjunto de capas de salida puede pertenecer exactamente a una partición en el esquema de partición respectivo. Para cada esquema de partición respectivo del uno o más esquemas de partición, el descodificador de vídeo puede obtener, a partir de un mensaje de información de mejora suplementario (SEI) en el flujo de bits o información de usabilidad de vídeo (VUI) en un conjunto de parámetros de vídeo (VPS) en el flujo de bits; un conjunto respectivo de elementos sintácticos que indican conjuntos de parámetros de descodificador de referencia hipotético (HRD) para el esquema de partición. Además, para cada partición respectiva del esquema de partición, el dispositivo de procesamiento de vídeo puede probar, basándose en los conjuntos de parámetros de HRD para el esquema de

partición respectivo, la partición respectiva en cuanto a conformidad con un estándar de codificación de vídeo, tal como MV-HEVC o SHVC.

[0025] De acuerdo con algunas técnicas de esta divulgación, un descodificador de vídeo de múltiples capas puede determinar, basándose en una lista de entradas triples, si el descodificador de vídeo de múltiples capas es capaz de descodificar (es decir, está configurado para descodificar) un flujo de bits que comprende una representación codificada de los datos de vídeo de múltiples capas. El número de entradas triples en la lista puede ser menor o igual que una cantidad de descodificadores de capa única en el descodificador de vídeo de múltiples capas. Cada entrada triple respectiva en la lista de entradas triples indica un perfil, un grado y un nivel que un descodificador de capa única respectivo en el descodificador de vídeo de múltiples capas es capaz de descodificar (es decir, está configurado para descodificar). Basándose en que el descodificador de vídeo de múltiples capas es capaz de descodificar el flujo de bits, el descodificador de vídeo de múltiples capas puede descodificador de múltiples capas es capaz de descodificar el flujo de bits determinando que el flujo de bits especifica un esquema de partición donde la información PTL de cada partición del esquema de partición indica que la partición puede descodificarse al menos uno de los descodificadores de capa única. Esto puede permitir que un descodificador de vídeo de múltiples capas que tenga múltiples descodificadores de capa única determine si el descodificador de vídeo de múltiples capas es capaz de descodificar el flujo de bits.

10

15

25

30

35

50

55

60

65

[0026] La FIG. 1 es un diagrama de bloques que ilustra un sistema de codificación de vídeo 10 de ejemplo que puede utilizar las técnicas de esta divulgación. Tal como se utiliza en el presente documento, el término "codificador de vídeo" se refiere genéricamente tanto a codificadores de vídeo como a descodificadores de vídeo. En esta divulgación, los términos "codificación de vídeo" o "codificación" pueden referirse genéricamente a la codificación de vídeo o la descodificación de vídeo.

[0027] Como es muestra en la FIG. 1, el sistema de codificación de vídeo 10 incluye un dispositivo de origen 12, un dispositivo de destino 14 y un elemento de red 15. El dispositivo de origen 12 genera datos de vídeo codificados. En consecuencia, el dispositivo de origen 12 puede denominarse dispositivo de codificación de vídeo o aparato de codificación de vídeo. El dispositivo de destino 14 puede descodificar los datos de vídeo codificados, generados por el dispositivo de origen 12. En consecuencia, el dispositivo de destino 14 puede denominarse dispositivo de descodificación de vídeo o aparato de descodificación de vídeo. El dispositivo de origen 12 y el dispositivo de destino 14 pueden ser ejemplos de dispositivos de codificación de vídeo o aparatos de codificación de vídeo.

[0028] El dispositivo de origen 12 y el dispositivo de destino 14 pueden comprender una amplia gama de dispositivos, incluyendo ordenadores de sobremesa, dispositivos informáticos móviles, ordenadores plegables (es decir, portátiles), ordenadores de tableta, descodificadores, equipos telefónicos de mano tales como los denominados teléfonos "inteligentes", televisores, cámaras, dispositivos de visualización, reproductores de medios digitales, consolas de videojuegos, ordenadores de coche o similares.

40 [0029] El elemento de red 15 puede recibir datos de vídeo codificados y emitir datos de vídeo codificados procesados. El elemento de red 15 puede ser un elemento de red compatible con medios (MANE), un dispositivo de red de entrega de contenido (CDN) u otro tipo de dispositivo (por ejemplo, un dispositivo informático). El dispositivo de red 15 puede realizar una o más técnicas de esta divulgación. Por ejemplo, el dispositivo de red 15 puede realizar una o más pruebas de conformidad de flujo de bits, de acuerdo con una o más técnicas de esta divulgación. El elemento de red 15, el dispositivo de origen 12, el dispositivo de destino 14 y otros tipos de dispositivo que procesan datos de vídeo pueden considerarse dispositivos de procesamiento de vídeo.

[0030] El dispositivo de destino 14 puede recibir datos de vídeo codificados desde el dispositivo de origen 12 a través de un canal 16. El canal 16 puede comprender uno o más medios o dispositivos capaces de desplazar los datos de vídeo codificados desde el dispositivo de origen 12 al dispositivo de destino 14. En un ejemplo, el canal 16 puede comprender uno o más medios de comunicación que permiten al dispositivo de origen 12 transmitir datos de vídeo codificados directamente al dispositivo de destino 14 en tiempo real. En este ejemplo, el dispositivo de origen 12 puede modular los datos de vídeo codificados de acuerdo con un estándar de comunicación, tal como un protocolo de comunicación inalámbrica, y puede transmitir los datos de vídeo modulados al dispositivo de destino 14. Los uno o más medios de comunicación pueden incluir medios de comunicación inalámbricos y/o alámbricos, tales como un espectro de radiofrecuencia (RF) o una o más líneas de transmisión física. Los uno o más medios de comunicación pueden formar parte de una red basada en paquetes, tal como una red de área local, una red de área extensa o una red global (por ejemplo, Internet). Los uno o más medios de comunicación pueden incluir routers, conmutadores, estaciones base u otros equipos que faciliten la comunicación desde el dispositivo de origen 12 al dispositivo de destino 14.

[0031] En otro ejemplo, el canal 16 puede incluir un medio de almacenamiento que almacena datos de vídeo codificados, generados por el dispositivo de origen 12. En este ejemplo, el dispositivo de destino 14 puede acceder al medio de almacenamiento, por ejemplo, mediante el acceso a disco o el acceso a tarjeta. El medio de almacenamiento puede incluir varios medios de almacenamiento de datos de acceso local, tales como discos Blu-

ray, DVD, CD-ROM, memoria flash u otros medios adecuados de almacenamiento digital para almacenar datos de vídeo codificados.

[0032] En un ejemplo adicional, el canal 16 puede incluir un servidor de ficheros u otro dispositivo de almacenamiento intermedio que almacene los datos de vídeo codificados, generados por el dispositivo de origen 12. En este ejemplo, el dispositivo de destino 14 puede acceder a datos de vídeo codificados almacenados en el servidor de ficheros u otro dispositivo de almacenamiento intermedio mediante transmisión continua o descarga. El servidor de ficheros puede ser un tipo de servidor capaz de almacenar datos de vídeo codificados y transmitir los datos de vídeo codificados al dispositivo de destino 14. Entre los ejemplos de servidores de ficheros se incluyen servidores de la Red (por ejemplo, para una sede de la Red), servidores del protocolo de transferencia de ficheros (FTP), dispositivos de almacenamiento conectados a red (NAS) y unidades de disco local.

5

10

15

20

25

50

65

[0033] El dispositivo de destino 14 puede acceder a los datos de vídeo codificados a través de una conexión de datos estándar, tal como una conexión a Internet. Entre los ejemplos de tipos de conexiones de datos pueden incluirse canales inalámbricos (por ejemplo, conexiones Wi-Fi), conexiones alámbricas (por ejemplo, línea de abonados digital (DSL), módem de cable, etc.), o combinaciones de ambos que sean adecuadas para acceder a datos de vídeo codificados almacenados en un servidor de ficheros. La transmisión de datos de vídeo codificados desde el servidor de ficheros puede ser una transmisión continua, una transmisión de descarga o una combinación de ambas.

[0034] Las técnicas de esta divulgación no están limitadas a aplicaciones o configuraciones inalámbricas. Las técnicas pueden aplicarse a la codificación de vídeo, en soporte de una diversidad de aplicaciones multimedia, tales como difusiones de televisión por el aire, transmisiones de televisión por cable, transmisiones de televisión por satélite, transmisiones continuas de vídeo, por ejemplo, mediante Internet, codificación de datos de vídeo para su almacenamiento en un medio de almacenamiento de datos, descodificación de datos de vídeo almacenados en un medio de almacenamiento de datos u otras aplicaciones. En algunos ejemplos, el sistema de codificación de vídeo 10 puede configurarse para soportar la transmisión de vídeo unidireccional o bidireccional para soportar aplicaciones tales como la radiodifusión de vídeo, la reproducción de vídeo, la radiodifusión de vídeo y/o la videotelefonía.

[0035] La FIG. 1 es meramente un ejemplo y las técnicas de esta divulgación pueden aplicarse a configuraciones de codificación de vídeo (por ejemplo, codificación de vídeo o descodificación de vídeo) que no incluyan necesariamente ninguna comunicación de datos entre los dispositivos de codificación y descodificación. En otros ejemplos, los datos (por ejemplo, datos de vídeo) se recuperan de una memoria local, se transmiten por una red o similar. Un dispositivo de codificación de vídeo puede codificar y almacenar datos (por ejemplo, datos de vídeo) en la memoria, y/o un dispositivo de descodificación de vídeo puede recuperar y descodificar datos (por ejemplo, datos de vídeo) desde la memoria. En muchos ejemplos, la codificación y descodificación se realiza mediante dispositivos que no se comunican entre sí, sino que simplemente codifican datos en la memoria y/o recuperan y descodifican datos (por ejemplo, datos de vídeo) desde la memoria.

40 [0036] En el ejemplo de la FIG. 1, el dispositivo de origen 12 incluye una fuente de vídeo 18, un codificador de vídeo 20 y una interfaz de salida 22. En algunos ejemplos, la interfaz de salida 22 puede incluir un modulador/desmodulador (módem) y/o un transmisor. El origen de vídeo 18 puede incluir un dispositivo de captura de vídeo, por ejemplo, una videocámara, un fichero de vídeo que contiene datos de vídeo previamente capturados, una interfaz de alimentación de vídeo para recibir datos de vídeo desde un proveedor de contenido de vídeo y/o un sistema de gráficos por ordenador para generar datos de vídeo, o una combinación de dichos orígenes de datos de vídeo. Por lo tanto, en algunos ejemplos, el dispositivo de origen 12 comprende una cámara configurada para capturar datos de vídeo.

[0037] El codificador de vídeo 20 puede codificar datos de vídeo procedentes del origen de vídeo 18. En algunos ejemplos, el dispositivo de origen 12 directamente transmite los datos de vídeo codificados al dispositivo de destino 14 mediante la interfaz de salida 22. En otros ejemplos, los datos de vídeo codificados también pueden almacenarse en un medio de almacenamiento o un servidor de ficheros para un acceso posterior mediante el dispositivo de destino 14 para su descodificación y/o reproducción.

[0038] En el ejemplo de la FIG. 1, el dispositivo de destino 14 incluye una interfaz de entrada 28, un descodificador de vídeo 30 y un dispositivo de visualización 32. En algunos ejemplos, la interfaz de entrada 28 incluye un receptor y/o un módem. La interfaz de entrada 28 puede recibir los datos de vídeo codificados por el canal 16. El codificador de vídeo 30 puede descodificar datos de vídeo codificados. El dispositivo de visualización 32 puede mostrar los datos de vídeo descodificados. El dispositivo de visualización 32 puede estar integrado con, o ser externo a, el dispositivo de destino 14. El dispositivo de visualización 32 puede comprender varios dispositivos de visualización, tales como una pantalla de cristal líquido (LCD), una pantalla de plasma, una pantalla de diodos orgánicos emisores de luz (OLED) u otro tipo de dispositivo de visualización.

[0039] El codificador de vídeo 20 y el descodificador de vídeo 30 pueden, cada uno, implementarse como cualquiera entre varios circuitos adecuados, tales como uno o más microprocesadores, procesadores de señales digitales (DSP), circuitos integrados específicos de la aplicación (ASIC), conjuntos de puertas programables sobre el

terreno (FPGA), lógica discreta, hardware o cualquier combinación de los mismos. Si las técnicas se implementan parcialmente en software, un dispositivo puede almacenar instrucciones para el software en un medio adecuado de almacenamiento no transitorio legible por ordenador, y puede ejecutar las instrucciones en hardware usando uno o más procesadores para realizar las técnicas de esta divulgación. Cualquiera de los anteriores (incluyendo hardware, software, una combinación de hardware y software, etc.) puede considerarse como uno o más procesadores. Cada uno del codificador de vídeo 20 y del descodificador de vídeo 30 puede estar incluido en uno o más codificadores o descodificadores, cualquiera de los cuales puede estar integrado como parte de un codificador/descodificador (CODEC) combinado en un respectivo dispositivo.

[0040] Esta divulgación puede referirse en general al codificador de vídeo 20 que "señala" cierta información a otro dispositivo, tal como el descodificador de vídeo 30. El término "indicar" puede referirse en general a la comunicación de elementos sintácticos y/u otros datos usados para descodificar los datos de vídeo comprimidos. Dicha comunicación puede producirse en tiempo real o casi real. De forma alternativa, dicha comunicación puede producirse durante un tramo de tiempo, tal como podría ocurrir cuando se almacenan elementos sintácticos en un medio de almacenamiento legible por ordenador en un flujo de bits codificado en el momento de la codificación, que a continuación un dispositivo de descodificación puede recuperar en cualquier momento tras haber sido almacenado en este medio.

20

25

30

35

40

45

50

55

60

[0041] En algunos ejemplos, el codificador de vídeo 20 y el descodificador de vídeo 30 funcionan de acuerdo con un estándar de compresión de vídeo, tal como ISO/IEC MPEG-4 Visual e ITU-T H.264 (también conocido como ISO/IEC MPEG-4 AVC), incluida su extensión de codificación de vídeo escalable (SVC), extensión de codificación de vídeo de múltiples visualizaciones (MVC) y extensión 3DV basada en MVC. En algunos casos, cualquier flujo de bits que se ajuste a la extensión 3DV basada en MVC de H.264/AVC siempre contiene un sub-flujo de bits que es compatible con la extensión MVC de H.264/AVC. El último borrador conjunto de MVC se describe en "Codificación de vídeo avanzada para servicios audiovisuales genéricos", Recomendación ITU-T H.264, marzo de 2010. Además, actualmente se están emprendiendo unas iniciativas para generar una ampliación de codificación de vídeo tridimensional (3DV) para H.264/AVC, en concreto, 3DV basada en AVC. En otros ejemplos, el codificador de vídeo 20 y el descodificador de vídeo 30 pueden funcionar de acuerdo con ITU-T H.261, ISO/IEC MPEG-1 Visual, ITU-T H.262 o ISO/IEC MPEG-2 Visual, ITU-T H.263 e ISO/IEC MPEG-4 Visual.

[0042] En otros ejemplos, el codificador de vídeo 20 y el descodificador de vídeo 30 pueden funcionar de acuerdo con el estándar de Codificación de Vídeo de Alta Eficiencia (HEVC) elaborado por el Equipo de Colaboración Conjunta en Codificación de Vídeo (JCT-VC) del Grupo de Expertos en Codificación de Vídeo (VCEG) de ITU-T y el Grupo de Expertos en Imágenes en Movimiento (MPEG) de ISO/IEC. Un borrador del estándar HEVC, denominado "Memoria descriptiva de borrador de HEVC" se describe en el documento Bross et al. "Informe 3 Predeterminado de Codificación de Vídeo de Alta Eficiencia (HEVC)", Equipo de Colaboración Conjunta en Codificación de Vídeo (JCT-VC) de ITU-T SG16 WP3 e ISO/IEC JTC1/SC29/WG11, 16.ª reunión, San José, Estados Unidos, enero de 2014, n.º de documento JCTVC-P1003\_v1. La memoria descriptiva de borrador de HEVC está disponible en http://phenix.itsudparis.eu/jct/doc\_end\_user/documents/16\_San%20Jose/wg11/JCTVC-P1003-v1.zip.

[0043] Además, actualmente se están dedicando esfuerzos a la elaboración de una extensión de codificación de vídeo para HEVC. La extensión de codificación de vídeo escalable de HEVC puede denominarse SHEVC o SHVC. Adicionalmente, un Equipo de Colaboración Conjunta en Codificación de Vídeo 3D (JCT-3C) de VCEG y MPEG está elaborando un estándar 3DV basado en HEVC. Parte de los esfuerzos de estandarización para el estándar 3DV basado en HEVC incluyen la estandarización de un códec de vídeo de múltiples visualizaciones basado en HEVC (es decir, MV-HEVC). Otra parte de los esfuerzos de estandarización para el estándar 3DV basado en HEVC incluye la estandarización de una codificación de vídeo 3D basada en HEVC (es decir, 3D-HEVC). Para 3D-HEVC, se pueden incluir y soportar nuevas herramientas de codificación, incluyendo aquellas a nivel de unidad de codificación (CU) o unidad de predicción (PU), tanto para las visualizaciones de textura como de profundidad.

[0044] Un reciente Borrador de Trabajo (WD) de MV-HEVC, denominado MV-HEVC WD8 de aquí en adelante, está disponible en http://phenix.it-sudparis.eu/jct2/doc\_end\_user/documents/8\_Valencia/wg11/JCT3V-H1002-v1.zip. La extensión escalable a HEVC, llamada SHVC, también está siendo desarrollada por el JCT-VC. Un borrador de trabajo (WD) reciente de SHVC, denominado SHVC WD6 de aquí en adelante, está disponible en http://phenix.it-sudparis.eu/jct/doc end user/documents/17 Valencia/wg11/JCTVC-Q1008-v1.zip.

[0045] En la HEVC y otras especificaciones de codificación de vídeo, una secuencia de vídeo incluye típicamente una serie de imágenes. Las imágenes también pueden denominarse "tramas". Una imagen puede incluir tres formaciones de muestras, denominadas  $S_L$ ,  $S_{Cb}$  y  $S_{Cr}$ .  $S_L$  es una formación bidimensional (es decir, un bloque) de muestras de luma.  $S_{Cb}$  es una formación bidimensional de muestras de croma Cb.  $S_{Cr}$  es una formación bidimensional de muestras de croma Cr. Las muestras de croma también se pueden denominar en el presente documento muestras de "croma". En otros casos, una imagen puede ser monocromática y puede solo incluir una formación de muestras de luma.

65 **[0046]** Para generar una representación codificada de una imagen, el codificador de vídeo 20 puede generar un conjunto de unidades de árbol de codificación (CTU). Cada una de las CTU puede comprender un bloque de árbol

de codificación de muestras de luma, dos bloques de árbol de codificación correspondientes de muestras de croma y estructuras sintácticas usadas para codificar las muestras de los bloques de árbol de codificación. En imágenes monocromáticas o imágenes que tienen tres planos de color separados, una CTU puede comprender un solo bloque de árbol de codificación y estructuras sintácticas usadas para codificar las muestras del bloque de árbol de codificación. Un bloque de árbol de codificación puede ser un bloque de muestras de tamaño NxN. Una CTU también puede denominarse "bloque de árbol" o una "máxima unidad de codificación" (LCU). Las CTU de la HEVC pueden ser análogas en gran medida a los macrobloques de otros estándares, tales como H.264/AVC. Sin embargo, una CTU no está limitada necesariamente a un tamaño particular y puede incluir una o más unidades de codificación (CU). Un fragmento puede incluir un número entero de CTU ordenadas consecutivamente en un orden de escaneado cuadriculado.

[0047] Esta divulgación puede usar el término "unidad de vídeo", "bloque de vídeo" o "bloque" para referirse a uno o más bloques de muestras y estructuras sintácticas usadas para codificar muestras del uno o más bloques de muestras. Los tipos de ejemplo de unidades de vídeo pueden incluir CTU, CU, PU, unidades de transformación (TU), macrobloques, particiones de macrobloque, etc. En algunos contextos, el análisis de PU puede intercambiarse con el análisis de macrobloques o particiones de macrobloques.

[0048] Para generar una CTU codificada, el codificador de vídeo 20 puede llevar a cabo de forma recursiva una partición de árbol cuaternario en los bloques de árbol de codificación de una CTU para dividir los bloques de árbol de codificación en bloques de codificación, de ahí el nombre "unidades de árbol de codificación". Un bloque de codificación es un bloque de muestras de tamaño NxN. Una CU puede comprender un bloque de codificación de muestras de luma y dos bloques de codificación correspondientes de muestras de croma de una imagen que tiene una matriz de muestras de luma, una matriz de muestras de Cb y una matriz de muestras de Cr y estructuras sintácticas usadas para codificar las muestras de los bloques de codificación. En imágenes monocromáticas o imágenes que tienen tres planos de color separados, una CU puede comprender un único bloque de codificación y estructuras sintácticas usadas para codificar las muestras del bloque de codificación.

[0049] El codificador de vídeo 20 puede dividir un bloque de codificación de una CU en uno o más bloques de predicción. Un bloque de predicción es un bloque rectangular (es decir, cuadrado o no cuadrado) de muestras en las que se aplica la misma predicción. Una unidad de predicción (PU) de una CU puede comprender un bloque de predicción de muestras de luma, dos bloques de predicción correspondientes de muestras de croma y estructuras sintácticas usadas para predecir los bloques de predicción. En imágenes monocromáticas o imágenes que tienen tres planos de color separados, una PU puede comprender un solo bloque de predicción y estructuras sintácticas usadas para predecir el bloque de predicción. El codificador de vídeo 20 puede generar bloques predictivos (por ejemplo, bloques predictivos de luma, Cb y Cr) para bloques de predicción (por ejemplo, bloques de predicción de luma, Cb y Cr) de cada PU de la CU.

**[0050]** El codificador de vídeo 20 puede usar intra-predicción o inter-predicción para generar los bloques predictivos para una PU. Si el codificador de vídeo 20 utiliza intra-predicción para generar los bloques predictivos de una PU, el codificador de vídeo 20 puede generar los bloques predictivos de la PU basándose en muestras descodificadas de la imagen que incluye la PU.

[0051] Después de que el codificador de vídeo 20 genera bloques predictivos (por ejemplo, bloques predictivos de luma, Cb y Cr) para una o más PU de una CU, el codificador de vídeo 20 puede generar uno o más bloques residuales para la CU. Por ejemplo, el codificador de vídeo 20 puede generar un bloque residual de luma para la CU. Cada muestra en el bloque residual de luma de la CU indica una diferencia entre una muestra de luma en uno de los bloques predictivos de luma de la CU y una muestra correspondiente en el bloque de codificación de luma original de la CU. Además, el codificador de vídeo 20 puede generar un bloque residual de Cb para la CU. Cada muestra en el bloque residual de Cb de la CU puede indicar una diferencia entre una muestra de Cb en uno de los bloques predictivos de Cb de la CU y una muestra correspondiente en el bloque de codificación de Cb original de la CU. El codificador de vídeo 20 también puede generar un bloque residual de Cr para la CU. Cada muestra en el bloque residual de Cr de la CU puede indicar una diferencia entre una muestra de Cr en uno de los bloques de Cr predictivos de la CU y una muestra correspondiente en el bloque de codificación de Cr original de la CU.

[0052] Además, el codificador de vídeo 20 puede usar la partición en árbol cuádruple para descomponer los bloques residuales (por ejemplo, los bloques residuales de luma, Cb y Cr) de una CU en uno o más bloques de transformación (por ejemplo, bloques de transformación de luma, Cb y Cr). Un bloque de transformación es un bloque rectangular (por ejemplo, cuadrado o no cuadrado) de muestras a las que se aplica la misma transformación. Una unidad de transformación (TU) de una CU puede comprender un bloque de transformación de muestras de luma, dos bloques de transformación correspondientes de muestras de croma y estructuras sintácticas utilizadas para transformar las muestras de bloques de transformación. De este modo, cada TU de una CU puede tener un bloque de transformación de luma, un bloque de transformación de Cb y un bloque de transformación de Cr. El bloque de transformación de luma de la TU puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cr puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cr puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cr puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cr puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cr puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cr puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cb puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cb puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cb puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cb puede ser un sub-bloque del bloque residual de Cb de la CU. El bloque de transformación de Cb puede ser un sub-bloque del bloque residual de Cb de la CU.

tienen tres planos de color separados, una TU puede comprender un solo bloque de transformación y unas estructuras sintácticas usadas para transformar las muestras del bloque de transformación.

[0053] El codificador de vídeo 20 puede aplicar una o más transformaciones a un bloque de transformación de TU para generar un bloque de coeficientes para la TU. Por ejemplo, el codificador de vídeo 20 puede aplicar una o más transformaciones a un bloque de transformación de luma de una TU con el fin de generar un bloque de coeficientes de luma para la TU. Un bloque de coeficientes puede ser una formación bidimensional de coeficientes de transformación. Un coeficiente de transformación puede ser una cantidad escalar. El codificador de vídeo 20 puede aplicar una o más transformaciones a un bloque de transformación de Cb de una TU para generar un bloque de coeficientes de Cb para la TU. El codificador de vídeo 20 puede aplicar una o más transformaciones a un bloque de transformación de Cr de una TU para generar un bloque de coeficientes de Cr para la TU.

5

10

15

20

25

30

50

55

60

65

[0054] Después de generar un bloque de coeficientes (por ejemplo, un bloque de coeficientes de luma, un bloque de coeficientes de Cb o un bloque de coeficientes de Cr), el codificador de vídeo 20 puede cuantificar el bloque de coeficientes. La cuantificación se refiere, en general, a un proceso en el que los coeficientes de transformación se cuantifican para reducir posiblemente la cantidad de datos usados para representar los coeficientes de transformación, proporcionando una compresión adicional. Después de que el codificador de vídeo 20 cuantifique un bloque de coeficientes, el codificador de vídeo 20 puede codificar por entropía elementos sintácticos que indican los coeficientes de transformación cuantificados. Por ejemplo, el codificador de vídeo 20 puede realizar la Codificación Aritmética Binaria Adaptativa al Contexto (CABAC) en los elementos sintácticos que indican los coeficientes de transformación cuantificados.

[0055] El codificador de vídeo 20 puede emitir un flujo de bits que incluye una secuencia de bits que forman una representación de imágenes codificadas y datos asociados. Por lo tanto, el flujo de bits comprende una representación codificada de datos de vídeo. El flujo de bits puede comprender una secuencia de unidades de capa de abstracción de red (NAL). Una unidad NAL es una estructura sintáctica que contiene una indicación del tipo de datos en la unidad NAL y los bytes que contienen dichos datos en forma de una carga útil de secuencia de bytes sin procesar (RBSP) intercalados según sea necesario con bits de prevención de emulación. Cada una de las unidades NAL incluye una cabecera de la unidad NAL y encapsula una RBSP. La cabecera de la unidad NAL puede incluir un elemento sintáctico que indica un código de tipo de unidad NAL. El código de tipo de unidad NAL especificado por la cabecera de unidad NAL de una unidad NAL indica el tipo de la unidad NAL. Una RBSP puede ser una estructura sintáctica que contiene un número entero de bytes que se encapsula dentro de una unidad NAL. En algunos casos, una RBSP incluye cero bits.

[0056] Diferentes tipos de unidades NAL pueden encapsular diferentes tipos de las RBSP. Por ejemplo, diferentes 35 tipos de unidades NAL pueden encapsular diferentes RBSP para conjuntos de parámetros de vídeo (VPS), conjuntos de parámetros de secuencia (SPS), conjuntos de parámetros de imagen (PPS), fragmentos codificados, información de mejora suplementaria (SEI), etc. Las unidades NAL que encapsulan las RBSP para datos de codificación de vídeo (a diferencia de las RBSP para conjuntos de parámetros y mensajes SEI) pueden denominarse 40 unidades NAL de la capa de codificación de vídeo (VCL). En HEVC (es decir, HEVC no de múltiples capas), una unidad de acceso puede ser un conjunto de unidades NAL que son consecutivas en orden de descodificación y que contienen exactamente una imagen codificada. Además de las unidades NAL de fragmento codificado de la imagen codificada, la unidad de acceso también puede contener otras unidades NAL que no contienen fragmentos de la imagen codificada. En algunos ejemplos, la descodificación de una unidad de acceso siempre da como resultado una imagen descodificada. La información de mejora suplementaria (SEI) contiene información que no es necesaria 45 para descodificar las muestras de imágenes codificadas de las unidades NAL VCL. Un SEI RBSP contiene uno o más mensajes SEI.

[0057] El descodificador de vídeo 30 puede recibir un flujo de bits generado por el codificador de vídeo 20. Además, el descodificador de vídeo 30 puede analizar el flujo de bits para obtener elementos sintácticos del flujo de bits. El descodificador de vídeo 30 puede reconstruir las imágenes de los datos de vídeo basándose, al menos en parte, en los elementos sintácticos obtenidos a partir del flujo de bits. El proceso para reconstruir los datos de vídeo puede ser en general recíproco al proceso realizado por el codificador de vídeo 20. Por ejemplo, el descodificador de vídeo 30 puede usar vectores en movimiento de las PU para determinar bloques predictivos para las PU de una CU actual. Además, el descodificador de vídeo 30 puede cuantificar inversamente bloques de coeficientes de TU de la CU actual. El descodificador de vídeo 30 puede realizar transformaciones inversas en los bloques de coeficientes para reconstruir los bloques de transformación de las TU de la CU actual. El descodificador de vídeo 30 puede reconstruir los bloques de codificación de la CU actual añadiendo las muestras de los bloques predictivos para las PU de la CU actual a las muestras correspondientes de los bloques de transformación de las TU de la CU actual. Mediante la reconstrucción de los bloques de codificación para cada CU de una imagen, el descodificador de vídeo 30 puede reconstruir la imagen.

[0058] Las técnicas de esta divulgación son potencialmente aplicables a la codificación de múltiples visualizaciones y/o estándares y especificaciones 3DV, incluyendo MV-HEVC y 3D-HEVC. En la codificación de múltiples visualizaciones, tal como la definida en MV-HEVC y 3D-HEVC, puede haber varias visualizaciones de la misma escena desde diferentes puntos de visualización. En el contexto de la codificación de múltiples

visualizaciones y codificación de vídeo escalable, el término "unidad de acceso" puede usarse para referirse a un conjunto de imágenes que corresponden a la misma instancia de tiempo. En algunos casos, en el contexto de codificación de múltiples visualizaciones y codificación de vídeo escalable, una unidad de acceso puede comprender un conjunto de unidades NAL que están asociadas entre sí de acuerdo con una regla de clasificación especificada, son consecutivas en orden de descodificación y contienen las unidades NAL VCL de todas las imágenes codificadas asociadas con el mismo tiempo de salida y sus unidades NAL no VCL asociadas. Así, los datos de vídeo pueden conceptualizarse como una serie de unidades de acceso que se producen a lo largo del tiempo.

[0059] En codificación 3DV, como la definida en 3D-HEVC, una "componente de visualización" puede ser una representación codificada de una visualización en una única unidad de acceso. Un componente de visualización puede contener un componente de visualización en profundidad y un componente de visualización en textura. Un componente de visualización de profundidad puede ser una representación codificada de la profundidad de una visualización en una única unidad de acceso. Un componente de visualización de textura puede ser una representación codificada de la textura de una visualización en una única unidad de acceso. En esta divulgación, una "vista" puede referirse a una secuencia de componentes de visualización asociadas con el mismo identificador de visualización.

10

15

20

25

30

35

40

45

50

65

[0060] La componente de visualización de textura y la componente de visualización de profundidad de un conjunto de imágenes de una visualización pueden considerarse como correspondientes entre sí. Por ejemplo, la componente de visualización de textura de un conjunto de imágenes de una visualización se considera correspondiente al componente de visualización de profundidad del conjunto de las imágenes de la visualización, y viceversa (es decir, la componente de visualización de profundidad corresponde a su componente de visualización de textura en el conjunto, y viceversa). Como se usa en esta divulgación, una componente de visualización de textura que corresponde a una componente de visualización de profundidad puede considerarse como la componente de visualización de textura y la componente de visualización de profundidad que son parte de una misma visualización de una única unidad de acceso.

[0061] La componente de visualización de textura incluye el contenido de imagen real que se muestra. Por ejemplo, la componente de visualización de textura puede incluir las componentes de luma (Y) y croma (Cb y Cr). El componente de visualización de profundidad puede indicar profundidades relativas de los píxeles en su componente de visualización de textura correspondiente. Como un ejemplo, el componente de visualización de profundidad puede comprender una imagen de escala de grises que incluye solo valores de luma, pero los valores de luma en un componente de visualización de profundidad pueden representar un nivel de profundidad de un píxel o conjunto de píxeles, a diferencia de un nivel de intensidad de píxel que sería transmitido por un componente de luma de una visualización de textura. En otras palabras, la componente de visualización de profundidad tal vez no transmita ningún contenido de imagen, pero en lugar de eso proporcione una medida de las profundidades relativas de los píxeles en la componente de visualización de textura. La componente de visualización de profundidad que utiliza solo valores de luma (por ejemplo, valores de intensidad) para identificar la profundidad se proporciona con fines ilustrativos y no debe considerarse limitativa. En otros ejemplos, puede utilizarse cualquier técnica para indicar las profundidades relativas de los píxeles en la componente de visualización de textura.

[0062] En la codificación de múltiples visualizaciones y la codificación SVC, un flujo de bits puede tener una pluralidad de capas. En codificación de múltiples visualizaciones, cada una de las capas puede corresponder a una visualización diferente. Una capa puede denominarse "capa base" si un descodificador de vídeo (por ejemplo, descodificador de vídeo 30) puede descodificar imágenes en la capa sin referencia a imágenes de ninguna otra capa. Una capa puede denominarse "capa no base" o "capa dependiente" si la descodificación de la capa depende de la descodificación de las imágenes de una o más capas diferentes. Cuando se codifica una imagen en una de las capas no base, un codificador de vídeo (como el codificador de vídeo 20 o el descodificador de vídeo 30) puede agregar una imagen a una lista de imágenes de referencia si la imagen está en una visualización diferente pero en la misma instancia de tiempo (es decir, unidad de acceso) que la imagen que el codificador de vídeo está codificando actualmente. Al igual que otras imágenes de referencia de inter-predicción, el codificador de vídeo puede insertar una imagen de referencia de predicción entre visualizaciones en cualquier posición de una lista de imágenes de referencia.

[0063] En SVC, las capas distintas de la capa base pueden denominarse "capas de mejora" y pueden proporcionar información que mejora la calidad visual de los datos de vídeo descodificados a partir del flujo de bits. La SVC puede mejorar la resolución espacial, la relación señal-ruido (es decir, la calidad) o la velocidad temporal. En la codificación de vídeo escalable (por ejemplo, SHVC), una "representación de capa" puede ser una representación codificada de una capa espacial en una única unidad de acceso. Para facilitar la explicación, esta divulgación puede referirse a componentes de visualización y/o representaciones de capa como "componentes de visualización/representaciones de capa" o simplemente "imágenes".

[0064] Para implementar las capas, las cabeceras de las unidades NAL pueden incluir elementos sintácticos nuh\_reserved\_zero\_6bits, que también pueden denominarse elementos sintácticos "nuh\_layer\_id". Las unidades NAL que tienen nuh\_reserved\_zero\_6bit elementos sintácticos que especifican valores diferentes que pertenecen a diferentes capas de un flujo de bits. Por lo tanto, en la codificación de múltiples visualizaciones (por ejemplo, MV-

HEVC), 3DV (por ejemplo, 3D-HEVC) o SVC (por ejemplo, SHVC), el elemento sintáctico nuh\_reserved\_zero\_6bits de una unidad NAL especifica un identificador de capa (es decir, una ID de capa) de la unidad NAL. En algunos ejemplos, el elemento sintáctico nuh\_reserved\_zero\_6bits de una unidad NAL es igual a 0 si la unidad NAL se relaciona con una capa base en codificación de múltiples visualizaciones (por ejemplo MV-HEVC), codificación 3DV (por ejemplo, 3D-HEVC) o SVC (por ejemplo, SHVC). Los datos en una capa base de un flujo de bits pueden descodificarse sin referencia a los datos en cualquier otra capa del flujo de bits. Si la unidad NAL no se relaciona con una capa base en codificación de múltiples visualizaciones, 3DV o SVC, el elemento sintáctico nuh\_reserved\_zero\_6bits del elemento sintáctico puede tener otros valores distintos de cero. Como se indicó anteriormente, en la codificación de múltiples visualizaciones y codificación 3DV, diferentes capas de un flujo de bits pueden corresponder a diferentes visualizaciones.

10

15

20

25

45

[0065] Además, algunos componentes de visualización/representaciones de capa dentro de una capa pueden descodificarse sin referencia a otros componentes de visualización/representaciones de capa dentro de la misma capa. Por lo tanto, las unidades NAL que encapsulan datos de ciertos componentes de visualización/representaciones de una capa pueden eliminarse del flujo de bits sin afectar a la capacidad de descodificación de otros componentes de visualización/representaciones de capa en la capa. La eliminación de unidades NAL que encapsulan datos de tales componentes de visualización/representaciones de capa puede reducir la velocidad de tramas del flujo de bits. Un subconjunto de componentes de visualización/representaciones de capa dentro de una capa que puede descodificarse sin referencia a otros componentes de visualización/representaciones de capa dentro de la capa se puede denominar en el presente documento una "sub-capa" o una "sub-capa temporal".

[0066] Las unidades NAL pueden incluir elementos sintácticos temporal\_id que especifiquen identificadores temporales (es decir, Temporallds) de las unidades NAL. El identificador temporal de una unidad NAL identifica una subcapa a la que pertenece la unidad NAL. Por lo tanto, cada subcapa de un flujo de bits puede tener un identificador temporal diferente. En general, si el identificador temporal de una primera unidad NAL es menor que el identificador temporal de una segunda unidad NAL, los datos encapsulados por la primera unidad NAL pueden descodificarse sin referencia a los datos encapsulados por la segunda unidad NAL.

[0067] Tal como se indica brevemente más arriba, las unidades NAL pueden encapsular RBSP para conjuntos de parámetros de vídeo (VPS), conjuntos de parámetros de secuencia (SPS), conjuntos de parámetros de imagen (PPS). Un VPS es una estructura sintáctica que comprende elementos sintácticos que se aplican a cero o más secuencias de vídeo codificadas completas (CVS). Un SPS también es una estructura sintáctica que comprende elementos sintácticos que se aplican a cero o más CVS completos. Un SPS puede incluir un elemento sintáctico que identifica un VPS que está activo cuando el SPS está activo. Por lo tanto, los elementos sintácticos de un VPS pueden ser más en general aplicables que los elementos sintácticos de un SPS. Un PPS es una estructura sintáctica que comprende elementos sintácticos que se aplican a cero o más imágenes codificadas. Un PPS puede incluir un elemento sintáctico que identifica un SPS que está activo cuando el PPS está activo. Una cabecera de fragmento de un fragmento puede incluir un elemento sintáctico que indica un PPS que está activo cuando el fragmento está siendo codificado.

[0068] Los conjuntos de parámetros, tales VPS, SPS y PPS pueden incluir estructuras sintácticas de extensión específicas para las extensiones del estándar HEVC. Por ejemplo, los conjuntos de parámetros pueden incluir extensiones específicas para SHVC, MV-HEVC, 3D-HEVC, etc. Las estructuras sintácticas de extensión pueden incluir elementos sintácticos aplicables a las extensiones del estándar HEVC. La Tabla 1 a continuación muestra una parte de la extensión de VPS definida en SHVC WD6 y MV-HEVC WD8.

#### TABLA 1

| os_extension( ) {                                                              | Descriptor |

|--------------------------------------------------------------------------------|------------|

| avc_base_layer_flag                                                            | u(1)       |

|                                                                                | u(1)       |

| vps_num_profile_tier_level_minus1                                              | ue(v)      |

| for(ptlldx = 1; ptlldx <= vps_num_profile_tier_level_Minus1; ptlldx ++) {      |            |

| vps_profile_present_flag[ptlldx]                                               | u(1)       |

| profile_tier_level(vps_profile_resent_flag[ptlldx], vps_max_sub_layers_minus1) |            |

| }                                                                              |            |

|                                                                                |            |

| for(i = 1; i < NumOutputLayerSets; i++) {                                      |            |

| vps_extension( ) {                                                     | Descriptor |

|------------------------------------------------------------------------|------------|

| if(i > vps_num_layer_sets_minus1)                                      |            |

| output_layer_set_idx_minus1[i]                                         | u(v)       |

| if( i > vps_num_layer_sets_minus1    defaultTargetOutputLayerIdc == 2) |            |

| for (j=0; j < NumLayersInIdList[LayerSetIdxForOutputLayerSet[i]]; j++) |            |

| output_layer_flag[i][j]                                                | u(1)       |

| profile_level_tier_idx[i]                                              | u(v)       |

| if(NumOutputLayersInOutputLayerSet[i] == 1                             |            |

| && NumDirectRefLayers[OlsHighestOutputLayerId[i]] > 0)                 |            |

| alt_output-layer_flag[i]                                               | u(1)       |

| }                                                                      |            |

|                                                                        |            |

| vps_vui_present_flag                                                   |            |

| if(vps_vui_present_flag) {                                             |            |

| while(!byte_aligned( ))                                                |            |

| vps_vui_alignment_bit_equal_to_one                                     | u(1)       |

| vps_vui( )                                                             |            |

| }                                                                      |            |

|                                                                        |            |

**[0069]** En el ejemplo de la Tabla 1 anterior y en otras tablas sintácticas de esta divulgación, los elementos sintácticos con descriptor de tipo ue(v) pueden ser números enteros de longitud variable sin signo codificados utilizando codificación Golomb exponencial (Exp-golomb) de orden 0 con el bit izquierdo primero. En el ejemplo de la Tabla 1 y las siguientes tablas, los elementos sintácticos que tienen descriptores de la forma u(n), donde n es un entero no negativo, son valores sin signo de longitud n.

[0070] La parte de la extensión de VPS definida en la Tabla 1 incluye elementos sintácticos que definen uno o más conjuntos de capas de salida. Un conjunto de capas de salida es un conjunto de capas que consta de las capas de uno de los conjuntos de capas especificados en el VPS, donde se indica que una o más capas del conjunto de capas serán capas de salida. Como se define en SHVC WD6, una capa de salida es una capa de un conjunto de capas de salida que se emite cuando TargetOptLayerSetIdx es igual al índice del conjunto de capas de salida. TargetOptLayerSetIdx especifica una lista de identificadores de capa de un punto de funcionamiento en uso y un conjunto de capas de salida objetivo. Un punto de funcionamiento puede referirse a un subconjunto (por ejemplo, un subconjunto adecuado) de unidades NAL en el flujo de bits. Además, como se define en SHVC WD6, una capa de salida objetivo es una capa que se va a emitir y es una de las capas de salida del conjunto de capas de salida con el índice olsIdx de forma que TargetOptLayerSetIdx sea igual a olsIdx. Por lo tanto, en general, el conjunto de capas de salida objetivo puede ser uno de los conjuntos de capas de salida en particular. Cada capa del conjunto de capas de salida objetivo se emite (por ejemplo, se proporciona como salida de un descodificador de vídeo). En algunos casos, el descodificador de vídeo 30 puede descodificar una capa particular de un flujo de bits, pero no emite datos de vídeo descodificados de la capa particular. En lugar de eso, el descodificador de vídeo 30 puede usar los datos de vídeo descodificados de la capa particular para descodificar los datos de vídeo de las capas que están en el conjunto de capas de salida objetivo.

10

15

20

35

25 [0071] Además, la parte de la extensión de VPS definida en la Tabla 1 incluye elementos sintácticos que definen una o más estructuras sintácticas de perfil, grado y nivel (PTL). Cada estructura sintáctica de PTL especifica un perfil, grado y nivel para cada secuencia de vídeo codificada. Como se muestra adicionalmente en la Tabla 1, la extensión de VPS incluye profile\_level\_tier\_idx elementos sintácticos que identifican las estructuras sintácticas PTL aplicables a los conjuntos de capas de salida respectivos. De esta forma, la extensión VPS especifica información PTL para cada uno de los conjuntos de capas de salida.

[0072] En general, un "perfil" es un subconjunto de las características y herramientas presentes en un estándar de codificación de vídeo (por ejemplo, HEVC o una extensión del mismo). Dentro de los límites impuestos por un perfil dado, todavía es posible requerir una gran variación en el rendimiento de los codificadores y descodificadores, dependiendo de los valores tomados por los elementos sintácticos en el flujo de bits, tales como el tamaño especificado de las imágenes descodificadas. En muchas aplicaciones, puede no ser ni práctico ni económico

# ES 2 686 699 T3

implementar un descodificador capaz de tratar con todos los usos hipotéticos de la sintaxis dentro de un perfil particular. Para tratar con este problema, se especifican "grados" y "niveles" dentro de cada perfil.

5

10

15

20

25

30

35

40

45

50

65

[0073] En algunos ejemplos, un nivel es un conjunto definido de restricciones en los valores que pueden ser tomados por los elementos sintácticos y variables de un estándar de codificación de vídeo (por ejemplo, HEVC o una extensión del mismo). Además, en algunos ejemplos, un grado es una categoría especificada de restricciones de nivel impuestas a los valores de los elementos sintácticos en el flujo de bits o valores de variables, donde las restricciones de nivel están agrupadas dentro de un grado y un descodificador conforme a un cierto grado y nivel sería capaz de descodificar todos los flujos de bits que se ajusten al mismo grado o al grado inferior de ese nivel o cualquier nivel debajo del mismo. De este modo, un nivel de un grado es un conjunto especificado de restricciones impuestas en los valores de los elementos sintácticos en el flujo de bits o los valores de variables. Estas restricciones pueden ser simples limitaciones de valores. De forma alternativa, pueden adoptar la forma de restricciones sobre combinaciones aritméticas de valores (por ejemplo, el ancho de imagen multiplicado por la altura de la imagen multiplicada por el número de imágenes descodificadas por segundo). Un nivel especificado para un grado inferior es más restringido que un nivel especificado para un grado superior. En algunos contextos, el término "nivel" también se puede usar para referirse al valor de un coeficiente de transformación antes del escalado.

[0074] Como se muestra adicionalmente en la Tabla 1 anterior, la extensión VPS puede incluir una vps\_vui() estructura sintáctica. La vps\_vui() estructura sintáctica contiene parámetros de información de usabilidad de vídeo (VUI). El párrafo F.7.3.2.1.4 de SHVC WD6 describe la sintaxis de una vps\_vui() estructura sintáctica. Como se especifica en la memoria descriptiva de borrador de HEVC, los parámetros VUI no son necesarios para construir las muestras de luma o croma mediante el proceso de descodificación. No se requieren descodificadores conformes para procesar esta información para el cumplimiento de la orden de salida de esta memoria desciptiva (ver el Anexo C para la especificación de la conformidad de la orden de salida). Se requieren algunos parámetros VUI para comprobar la conformidad del flujo de bits y la conformidad del descodificador de sincronización de salida. En algunos casos, los parámetros VUI también se pueden especificar en SPS.

[0075] Una vps\_vui() la estructura sintáctica puede incluir una vps\_vui\_bsp\_hrd\_parameters() estructura sintáctica. La vps\_vui\_bsp\_hrd\_parameters() la estructura sintáctica incluye elementos sintácticos que especifican parámetros hipotéticos de descodificador de referencia (HRD) para las particiones de flujo de bits. Como se define en SHVC WD6, una partición de flujo de bits es una secuencia de bits en la forma de un flujo de unidad NAL o un flujo de bytes, que es un subconjunto de un flujo de bits de acuerdo con una partición.

[0076] Al menos algunos estándares de codificación de vídeo especifican modelos de memoria intermedia de vídeo. En H.264/AVC y HEVC, un modelo de almacenamiento en memoria intermedia se denomina "descodificador de referencia hipotético" o "HRD". En la memoria descriptiva de borrador de HEVC se describe el HRD en el anexo C. El HRD describe cómo se almacenarán en memoria intermedia los datos para la descodificación y cómo se almacenan en memoria intermedia los datos descodificados para la emisión. Por ejemplo, el HRD describe el funcionamiento de una memoria intermedia de imágenes codificadas ("CPB"), una memoria intermedia de imágenes descodificadas ("DBP") y un proceso de descodificación de vídeo. La CPB es una memoria intermedia de primero en entrar, primero en salir, que contiene unidades de acceso en un orden de descodificación especificado por HRD. La DPB es una memoria intermedia que contiene imágenes descodificadas para referencia, reordenamiento de salida o retardo de salida especificado por el HRD. Los comportamientos de la CPB y DPB se pueden especificar matemáticamente. El HRD puede imponer directamente restricciones en el tiempo, los tamaños de la memoria intermedia y las velocidades de transferencia de bits. Además, el HRD puede imponer restricciones indirectamente a varias características y estadísticas de flujo de bits.

[0077] En la H.264/AVC y la HEVC, la conformidad del flujo de bits y la conformidad del descodificador se especifican como partes de la especificación del HRD. En otras palabras, el modelo de HRD especifica pruebas para determinar si un flujo de bits cumple con el estándar y pruebas para determinar si un descodificador cumple con el estándar. Aunque el HRD se denomina como algún tipo de descodificador, los codificadores de vídeo típicamente usan el HRD para garantizar la conformidad del flujo de bits, mientras que los descodificadores de vídeo típicamente no necesitan el HRD.