# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 690 844

51 Int. Cl.:

**H03M 3/00** (2006.01) **H03M 7/30** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 15.12.2012 PCT/EP2012/005182

(87) Fecha y número de publicación internacional: 20.06.2013 WO13087221

96 Fecha de presentación y número de la solicitud europea: 15.12.2012 E 12816649 (3)

(97) Fecha y número de publicación de la concesión europea: 11.07.2018 EP 2812997

54 Título: Dispositivo con un modulador delta-sigma y un amplificador de conmutación conectado al mismo

(30) Prioridad:

15.12.2011 DE 102011121139

Fecha de publicación y mención en BOPI de la traducción de la patente: 22.11.2018

(73) Titular/es:

iAd Gesellschaft für Informatik, Automatisierung und Datenverarbeitung mbH (100.0%) Unterschlauersbacher Hauptstrasse 10 90613 Grosshabersdorf, DE

(72) Inventor/es:

HAMPEL, HERMANN; BEROLD, ULRICH; HANOUN, ABDULRAHMAN; BÄNISCH, ANDREAS; HAMPEL, JOHANNES; ECKHOF, OLIVER y DEINZER, MANFRED

(74) Agente/Representante:

**LEHMANN NOVO, María Isabel**

#### **DESCRIPCIÓN**

Dispositivo con un modulador delta-sigma y un amplificador de conmutación conectado al mismo

- La invención se refiere (según las dos reivindicaciones 1 y 2 independientes) a un dispositivo con un modulador delta-sigma y a un amplificador de conmutación conectado al mismo, en particular para el procesamiento de la señal de entrada con una relación de sobremuestreo OSR reducida y una relación señal a ruido SNR elevada.

- Debido al hecho de que un amplificador de conmutación, en particular una etapa de potencia MOSFET, en el funcionamiento de conmutación sólo consume una potencia muy reducida en el estado de corte ("Cut-off state") y el estado de saturación, ésta ofrece una mejor eficiencia que los amplificadores de funcionamiento lineal. En teoría sólo se consume potencia al conmutar entre estos estados.

- A menudo a un amplificador de conmutación (amplificador digital) en el funcionamiento de conmutación le precede un módulo PDM (modulación por duración de pulso) y/o un módulo DSM (modulador delta-sigma), que convierte la señal de alta resolución en una señal con menor resolución (secuencia de impulsos de 1 bit) con una frecuencia mucho mayor. A la etapa de potencia le sigue a menudo un filtro de reconstrucción de paso bajo, que restablece la señal de banda base amplificada.

- Los moduladores delta-sigma, denominados en lo sucesivo de manera breve DSM, conforman la relación señal a ruido (SNR) de tal modo que eliminan el ruido en el intervalo de frecuencia de la señal. En el libro técnico "Understanding Delta-Sigma Data Converters" de Richard Schreier, Gabor Temes, Wiley Interscience Publication 2005, ISBN 0-471-46585-2 se presentan varias estructuras DSM convencionales. Las estructuras descritas en el mismo se refieren a señales de banda base con tasas de muestreo bajas. Se utilizan relaciones de sobremuestreo relativamente elevadas con un orden alto del DSM (por ejemplo por encima de 16) para garantizar una SNR aceptable de las señales de salida. Sin embargo, en el caso de tasas de muestreo muy elevadas de la señal de banda base (por encima de 2 msps (megamuestras por segundo)) técnicamente sólo son posibles relaciones de sobremuestreo bajas para la amplificación de potencia. Las propiedades eléctricas de la mayoría de transistores de amplificación de potencia producen, para impulsos de entrada de alta frecuencia, un empeoramiento considerable de la calidad de la señal de salida y de la eficiencia de amplificación.

- El DSM diseñado para tasas de muestreo bajas (RSR; reduced sampling rate, tasa de muestreo reducida) (RSR-DSM) ofrece el mismo orden de magnitud de SNR con una OSR mucho menor. En el artículo "A Reduced-Sample-Rate Sigma-Delta-Pipeline ADC Architecture for High-Speed High-Resolution Applications" de Vahid Majidzadeh, Omid Shoaei publicado en IEICE Transactions 89-C(6): 692-701 (2006) se presentaron dos ejemplos prácticos para filtros de bucle RSR. Los RSR-DSM de 4º y 6º orden proporcionan SNR mayores para una OSR baja en comparación con los filtros de bucle DSM convencionales.

35

- El uso de cuantificación multibit en el DSM aumenta la SNR y mejora la estabilidad del DSM como se discute en el artículo "Delta-Sigma Modulators: modeling, design and application" de George Bouropoulos publicado en Imperial College Press 2003, ISBN1-86094-369-1 y en la tesis doctoral "Stability Analysis and Design of Bandpass Sigma Delta Modulators" de Jurgen van Engelen, Universidad Técnica de Eindhoven, 1999, ISBN 90-386-1580-9. Sin embargo, cada bit de la salida multibit del DSM requiere un canal de etapa de potencia separado con una fuente de alimentación ponderada. La solución mencionada anteriormente es muy costosa y no se recomienda por motivos técnicos.

- Un remedio fundamental para este inconveniente es colocar un convertidor paralelo a serie en la salida del DSM multibit y antes de la etapa de potencia MOSFET en el funcionamiento de conmutación del CDA y así alimentar un flujo de impulsos de 1 bit al CDA. Este concepto se explica brevemente en la tesis doctoral "Stability Analysis and Design of Bandpass Sigma Delta Modulators" de Jurgen van Engelen, utilizándose este concepto por ejemplo en algunas solicitudes de patente como los documentos GB-A 2 438 774, GB-A 2 435 559 o GB-A 2 406 008.

- Para encontrar los coeficientes óptimos para el filtro de bucle en el DSM puede utilizarse un algoritmo de búsqueda como se explica por ejemplo en el artículo "An Automatic Coefficient Design Methodology for High-Order Bandpass Sigma-Delta modulator with Single-Stage Structure" de Hwi-Ming Wang publicado en IEEE Transactions on Circuits and Systems II, julio de 2006, páginas 580-584 o de Wan-Rone Liou, "A Low-Power Multi-Bit Delta-sigma Modulator with Data Weighted Averaging Technique", Workshop on Consumer Electronics and Signal Processing, 2005, Taiwán.

- En el estado de la técnica a menudo se utiliza un DSM con una señal multibit en la salida y a menudo deben amplificarse señales de audio, por tanto en este caso existe un intervalo de frecuencia claramente menor, un ancho de banda menor y en consecuencia tasas de muestreo menores. En el caso de las soluciones descritas en las solicitudes de patente GB-A 2 438 774, GB-A 2 435 559 o GB-A 2 406 008 la conversión P/S influye considerablemente en la estructura del filtro de bucle y sus parámetros. Además el control del giro en estas solicitudes de patente GB-A 2 438 774, GB-A 2 435 559 o GB-A 2 406 008 requiere de un control/lógica complejos.

Además por el documento US-A 5.815.102 se conoce un convertidor digital a analógico (D/A), en particular un convertidor delta-sigma, para señales de audio y una conmutación reducida. Las frecuencias de audio del campo auditivo del ser humano se sitúan en el intervalo de 16 Hz a 20 kHz. Se considera que un convertidor D/A de este tipo es en particular útil para aquellos audífonos que, para recibir un sonido del entorno, presentan un receptor de audio con un convertidor analógico a digital para convertir las secuencias de sonidos o el sonido en una señal digital de tasa reducida y alta resolución, un circuito de procesamiento digital, para modificar la calidad de la señal digital de tasa reducida y alta resolución, un circuito de interpolación, para convertir la señal digital de tasa reducida y alta resolución en una señal de alta resolución y tasa media, y un convertidor de digital a analógico, para convertir la señal digital modificada de tasa media y alta resolución de nuevo en un sonido analógico. Para poner a disposición un convertidor digital a analógico (D/A) que presente un consumo de potencia reducido debido a una reducción en el número de transiciones de señal de emisión, mientras se mantiene una distorsión reducida, en el audífono según el documento US-A 5.815.102 un demodulador de ciclo de activación formatea la señal digital de baja resolución y tasa elevada con un formato predeterminado de una tasa de transición reducida. Para ello se determina un valor multibit según cada valor introducido o de entrada de la señal digital de resolución media y tasa media y se emiten los valores así determinados como una señal digital de baja resolución y tasa elevada. Por ejemplo el demodulador de ciclo de activación puede almacenar un valor según cada posible valor de entrada de la señal digital de resolución media y tasa media (por ejemplo en la ROM) y consultar el valor almacenado correspondiente para cada señal digital introducida de resolución media y tasa media. Por tanto, la conversión de los valores de entrada en valores de salida se produce mediante el denominado "formateo" de la señal de entrada, que se realiza mediante la búsqueda de valores almacenados. En este formato alternante los ciclos impares crecen desde la derecha y los ciclos pares desde la izquierda.

10

15

20

25

30

50

55

60

65

Finalmente, por el documento US 2010/0066580 A1 se conoce un convertidor de audio digital a analógico (D/A) que convierte señales de audio digitales en señales de audio analógicas. Normalmente se utilizan técnicas de sobremuestreo en un convertidor de audio D/A para mejorar la precisión de la señal de salida analógica, de modo que represente exactamente la señal digital en la entrada del convertidor D/A. El procedimiento utilizado en el documento US 2010/0066580 A1 requiere de una tabla con varias secuencias por cada nivel de cuantificación de la señal de entrada y en este sentido en cada caso una secuencia positiva y negativa. Además en cada caso se alterna entre secuencias con "energía en modo común" (common mode energy) positiva y negativa, comenzando todas las secuencias de la misma "frase" con el mismo valor binario y terminando todas con el mismo valor binario. Como de este modo ya se fijan en cada caso 2 bits por cada secuencia, es necesaria una frecuencia de reloj mayor de la señal de salida, no teniendo esto un efecto interferente para las señales de audio de baja frecuencia, consideradas en el documento US 2010/0066580 A1.

El problema principal es la implementación de frecuencias elevadas en la etapa de salida. En principio sería deseable una cuantificación lo más elevada posible en el DSM para una mejor calidad de señal (SNR) en la salida, es decir, una resolución lo más elevada posible del cuantificador y con ello el mayor número de bits posible en la salida del DSM. Sin embargo, cuanto mayor es la cuantificación mayor es también la frecuencia necesaria para hacer funcionar la etapa de salida (siempre que la resolución de la etapa de salida sea menor que la del cuantificador, como ocurre en el caso considerado aquí). Además los puntos de conexión del chip (más exactamente: los puntos de conexión de la pastilla) también tienen una característica de paso bajo, dependiendo la frecuencia de corte de este paso bajo de la tecnología de chip utilizada en cada caso. Cuanto mayor es la relación de sobremuestreo (OSR) y con ello la frecuencia de reloj del punto de conexión, mayor se hace el intervalo de frecuencia en el que debido al filtrado de los pulsos por la característica de paso bajo se producen problemas en el punto de conexión del chip. Una disminución de la relación de sobremuestreo (OSR) lleva obligatoriamente a una pérdida de potencia y una distorsión de señal reducida en el amplificador de conmutación.

Resumiendo puede afirmarse que en el estado de la técnica, en el que se considera la amplificación de señales de audio, existen anchos de banda de señal útil y frecuencias de muestreo considerablemente menores, de modo que la implementación de las frecuencias necesarias es más bien poco problemática incluso con una relación de sobremuestreo OSR elevada. Como ejemplo puede remitirse al documento WO 2010/109453 A1 siendo las señales de interés señales de audio y siendo para estas señales de audio el objetivo principal la reducción de las transiciones en la señal PWM para aumentar la efectividad y minimizar las pérdidas en dispositivos dispuestos aguas abajo, en particular amplificadores de clase D y a este respecto también la reducción de la fluctuación y el aumento de la SNR de la señal. El procedimiento se caracteriza por que en cada caso se combinan los pulsos de un número N predefinido de tramas y con ello se minimiza el número de transiciones dentro de este número de tramas. La señal resultante tiene en promedio como máximo dos transiciones por cada N tramas. Como puede utilizarse un número mayor de dos, dado el caso puede reducirse adicionalmente el número de transiciones. Sin embargo, para no distorsionar la fase de la señal, a continuación en cada caso todavía es necesario un nuevo posicionamiento del pulso resultante, más ancho. En el objeto del documento WO 2010/109453 A1 el procedimiento para la reducción del número de transiciones es meramente sistemático con respecto a un número de tramas predeterminado y en este caso el control no se produce con memoria. Según esto la memoria incluye sólo un número predeterminado de tramas, en las que se combinan y posicionan los pulsos, pero no las tramas previas. La latencia en el procesamiento de señales introducida por el procedimiento en el objeto del documento WO 2010/109453 A1 es relativamente elevada y aumenta proporcionalmente al número de tramas a combinar, añadiéndose aquí también el tiempo para la

determinación y conversión del nuevo posicionamiento de pulsos. Finalmente se utilizan OSR mayores (>=16), lo que resulta menos problemático con las bajas frecuencias en el rango de audio.

Además puede remitirse al documento DE 699 19185 T2, que hace referencia a DAC para frecuencias de audio, más precisamente a la corrección de una distorsión de emisión o salida no lineal en DAC delta-sigma. A este respecto, se describe un cuantificador delta-sigma de 2º orden o un DAC de sobremuestreo que se basa en el mismo, en el que se utilizan relaciones de sobremuestreo elevadas (como factores típicos se mencionan de 32 a 1024) para el rango de audio en cuestión con frecuencias de hasta aproximadamente 20 kHz. Además se utiliza un formato alternante, en el que los ciclos pares en la señal de salida crecen desde la izquierda y los impares desde la derecha, o también al revés. A este respecto, el número de transiciones de datos en la señal de salida ya se reduce a la mitad con respecto al crecimiento regular desde la misma dirección. El uso de un formato con señales que crecen de manera alternante desde la izquierda o derecha, puede implementarse mediante el uso de tablas ROM. La selección de la respectiva tabla se produce sólo sistemáticamente y en el rango de audio con frecuencias de hasta aproximadamente 20 kHz. Finalmente se describe el uso de una etapa de salida de clase D mediante el DAC, concretamente para hacer funcionar un altavoz de salida.

10

15

20

25

30

35

40

45

50

55

60

Finalmente, por el documento US 2010/085118 A1 se conoce un circuito de enclavamiento con tiempo de retardo con varios comparadores para señales en el rango de audio con frecuencias de hasta aproximadamente 20 kHz, que en una entrada de un comparador utiliza la señal de salida de un generador de señales triangulares. El objetivo del circuito de enclavamiento con tiempo de retardo reivindicado en el documento US 2010/085118 A1 consiste así en garantizar y optimizar el tiempo de retardo de los elementos de conmutación en la salida del amplificador de conmutación. A este respecto, el circuito de enclavamiento con tiempo de retardo requiere en cada caso de un circuito completo para bloquear el tiempo de retardo en caso de un flanco de señal descendente o en caso de un flanco de señal ascendente, de modo que es necesario un mayor número de comparadores, detectores de fase y elementos de conmutación.

Para la electrónica de potencia las frecuencias superiores (con respecto al rango de audio) son un gran reto porque en este caso, debido a las frecuencias de conmutación superiores, se producen distorsiones de señal en la entrada de los amplificadores.

La invención se basa en el objetivo de configurar un dispositivo con un modulador delta-sigma para un amplificador de conmutación y para frecuencias superiores (con respecto al rango de audio) de tal modo que sea posible una disminución de la relación de sobremuestreo (OSR) y de la frecuencia de reloj necesaria con una pérdida de potencia y distorsión de señal reducida en el amplificador de conmutación, en particular evitando la sobrecarga del amplificador de conmutación, así como el recorte de la señal útil.

Este objetivo, según la reivindicación 1, se alcanza mediante un dispositivo con un modulador delta-sigma y un amplificador de conmutación conectado al mismo, en el que se alimenta una señal de audio a la entrada del modulador delta-sigma y en el que en la salida multibit del modulador delta-sigma está conectado un circuito con un convertidor paralelo a serie y un elemento de rotación, convirtiéndose una señal de entrada alimentada al modulador delta-sigma en una señal de salida ya2 de un bit similar a PDM con como máximo un cambio entre unos y ceros o ceros y unos binarios, por que en la salida multibit del modulador delta-sigma está conectado un convertidor paralelo a serie SPS con un circuito en serie de un convertidor paralelo a serie y un elemento de rotación dispuesto aguas abajo para la señal de salida ya2 en serie del convertidor paralelo a serie y el convertidor paralelo a serie SPS como modulador de duración de pulso convierte cada valor de M bits en una palabra a partir de N<sub>ps</sub> valores binarios, y por que el elemento de rotación en función del último valor de bit 0 o 1 de una palabra anterior en cada caso en la señal de salida ya3 resultante cambia el orden de los ceros y unos binarios de la palabra actual (en caso de existir), de tal modo que para la reducción adicional de los flancos de pulso en la señal de salida ya2[i] del convertidor paralelo a serie del convertidor paralelo a serie SPS ésta se transfiere sin cambios a la señal de salida ya3[i] resultante del elemento de rotación del convertidor paralelo a serie SPS, cuando ya3[i-l] termina con el mismo valor binario con el que comienza ya2[i], e ya2[i] se transfiere rotada a ya3[i], cuando ya3[i-1] termina con el valor binario opuesto con el que comienza ya2[i].

Además este objetivo, según la reivindicación 2, se alcanza mediante un dispositivo con un modulador delta-sigma y un amplificador de conmutación conectado al mismo, en el que se alimenta una señal de audio a la entrada del modulador delta-sigma y en el que en la salida multibit del modulador delta-sigma está conectado un circuito con un convertidor paralelo a serie y un elemento de rotación, convirtiéndose una señal de entrada alimentada al modulador delta-sigma en una señal de salida ya2 de un bit similar a PDM con como máximo un cambio entre unos y ceros o ceros y unos binarios, por que en la salida multibit del modulador delta-sigma está conectado un convertidor paralelo a serie SPS\* con un circuito en serie a partir de un elemento de rotación para la señal de salida yb1 paralela del modulador delta-sigma y un convertidor paralelo a serie dispuesto aguas abajo y el convertidor paralelo a serie SPS como modulador de duración de pulso convierte cada valor de M bits en una palabra a partir de N<sub>ps</sub> valores binarios, y por que el elemento de rotación en función del último valor de bit 0 o 1 de una palabra anterior en cada caso en la señal de salida yb3 resultante cambia el orden de los ceros y unos binarios de la palabra actual (en caso de existir), de tal modo que para la reducción adicional de los flancos de pulso en la señal de salida del convertidor paralelo a serie SPS\* en la señal de salida yb2[i] del elemento de rotación ésta se transfiere sin cambios a yb3[i], cuando yb3[i], cuando yb3[i], cuando yb3[i], cuando yb3[i], cuando yb3[i], cuando yb3[i].

- 1] termina con el mismo valor binario con el que comienza yb2 [i], e yb2[i] se transfiere rotada a yb3[i], cuando yb3[i-1] termina con el valor binario opuesto con el que comienza yb2[i].

- Los dispositivos según la invención permiten un aumento evidente de la eficiencia energética, una reducción de la pérdida de potencia y un rango de tensión de alimentación variable y con ello una adaptación de la dinámica con la misma SNR. A este respecto, el modulador delta-sigma funciona como convertidor, que convierte señales con una determinada resolución en otras señales con otra resolución o que convierte las señales de entrada presentes con una determinada forma en señales de salida con otra forma, conservando las señales su información. En particular la conversión de señales analógicas de resolución infinita en señales digitales de resolución finita. A este respecto, la conversión se produce de tal modo que se optimizan las propiedades de la señal para el amplificador de conmutación posterior.

A este respecto, la invención no está limitada a un tipo de moduladores delta-sigma DSM, sino que puede implementarse con cualquier DSM, que por lo menos cumpla con un criterio determinado. Este criterio es una tasa de muestreo baja, porque entre el modulador sigma-delta y el amplificador de conmutación (amplificador digital) se produce una conversión paralelo a serie, cuya frecuencia de reloj necesaria (con la tecnología considerada en cada caso) debe poder implementarse, al igual que la del amplificador de conmutación.

A partir de la siguiente descripción de una forma de realización preferida de la invención, haciendo referencia al dibujo, pueden deducirse ventajas y detalles adicionales. En el dibujo muestran:

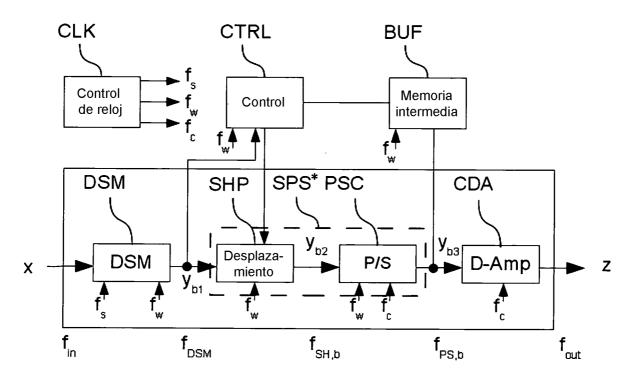

las figuras 1a, 1b dos configuraciones de la arquitectura del dispositivo según la invención,

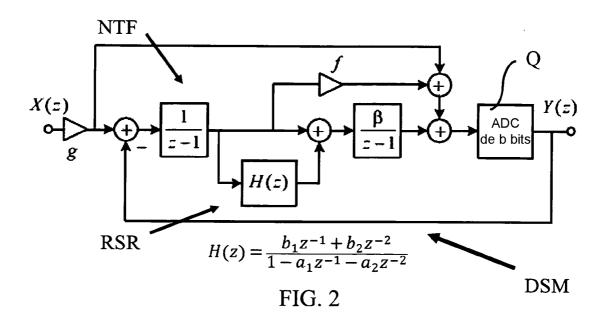

la figura 2 una configuración de la arquitectura del DSM según la figura 1,

25

30

35

40

45

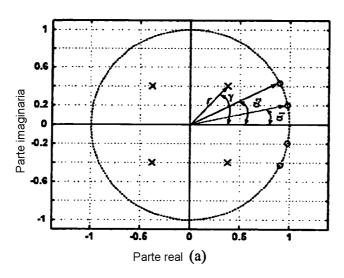

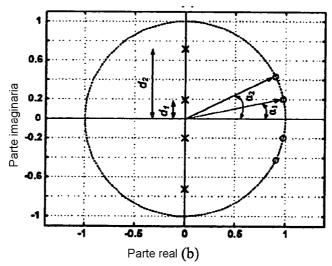

la figura 3 dos puntos óptimos para los polos y ceros del DSM según la figura 2,

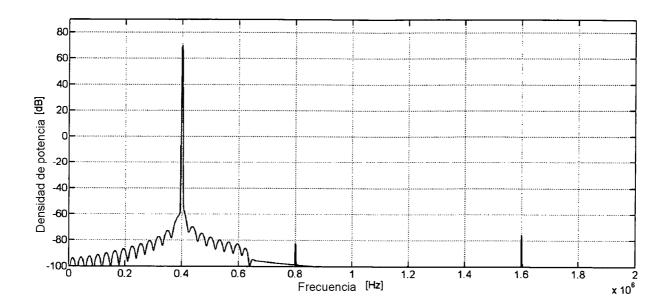

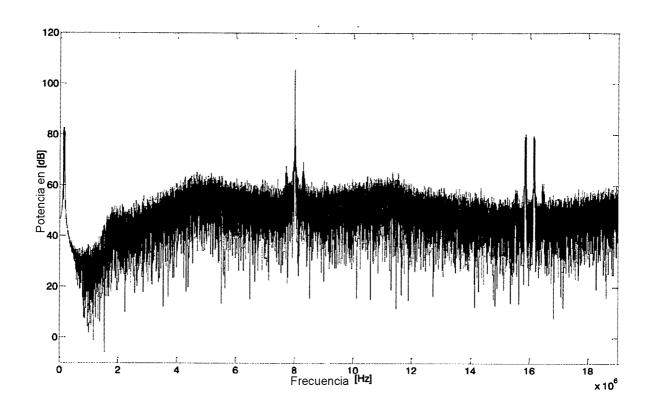

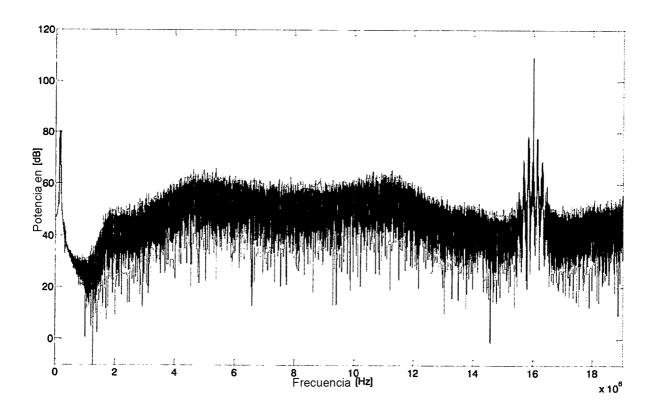

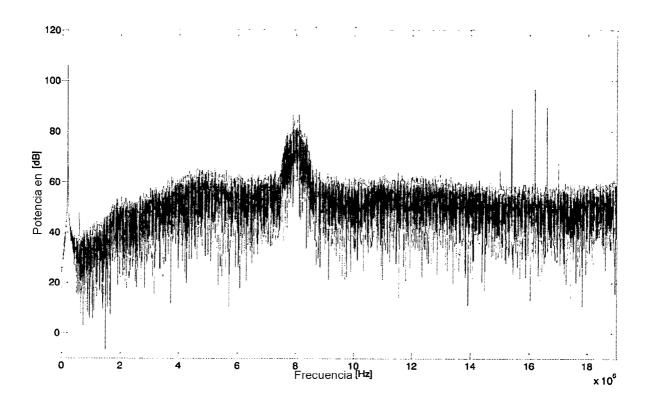

las figuras 4a, 4b, 4c los espectros de densidad de potencia en la entrada del sistema, salida del cuantificador y salida del sistema,

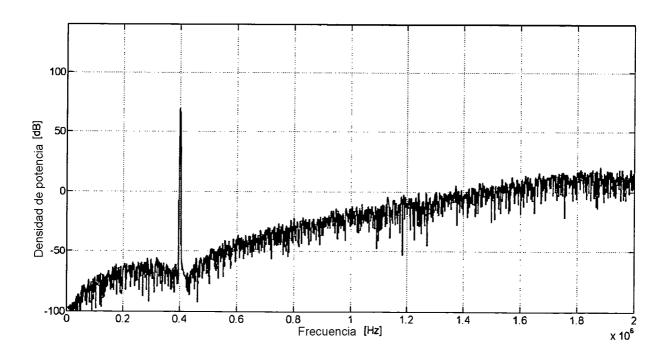

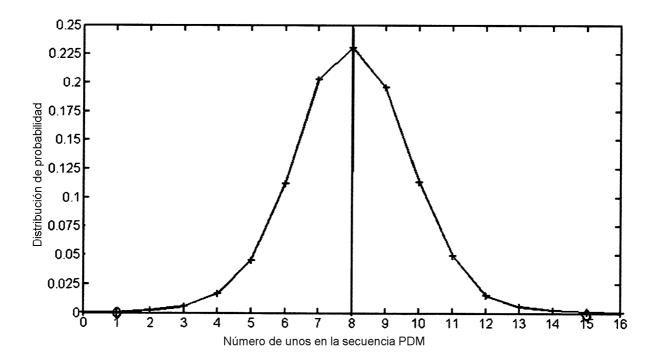

la figura 5 la distribución de probabilidad del número de pulsos para una señal OFDM tras DSM,

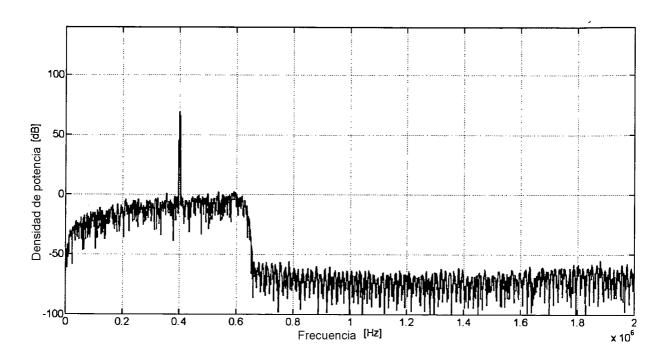

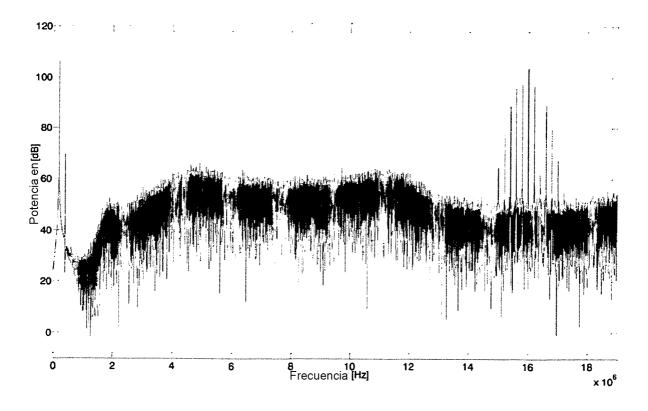

las figuras 6a, 6b el espectro de potencia de la señal de salida de un PDM con o sin rotación de palabra para una señal OFDM,

las figuras 7a, 7b el espectro de potencia de la señal de salida de un PDM con o sin rotación de palabra para una señal senoidal,

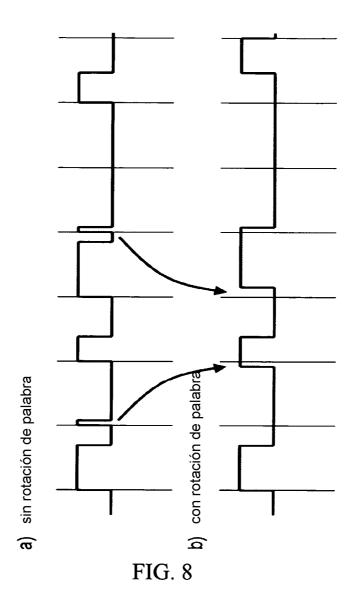

la figura 8 el principio de la rotación de pulso en el ejemplo de un fragmento de señal según la invención,

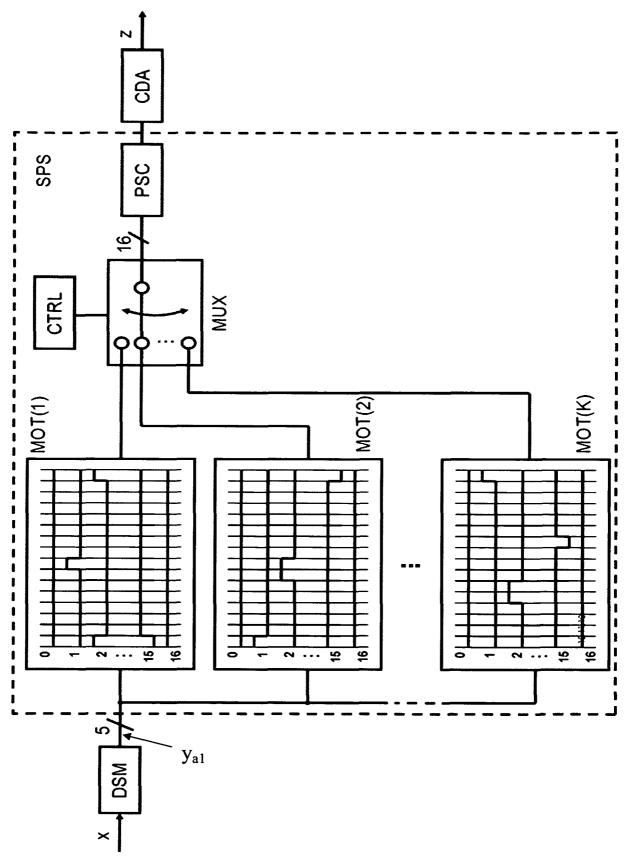

la figura 9 una configuración adicional de la arquitectura del dispositivo según la invención,

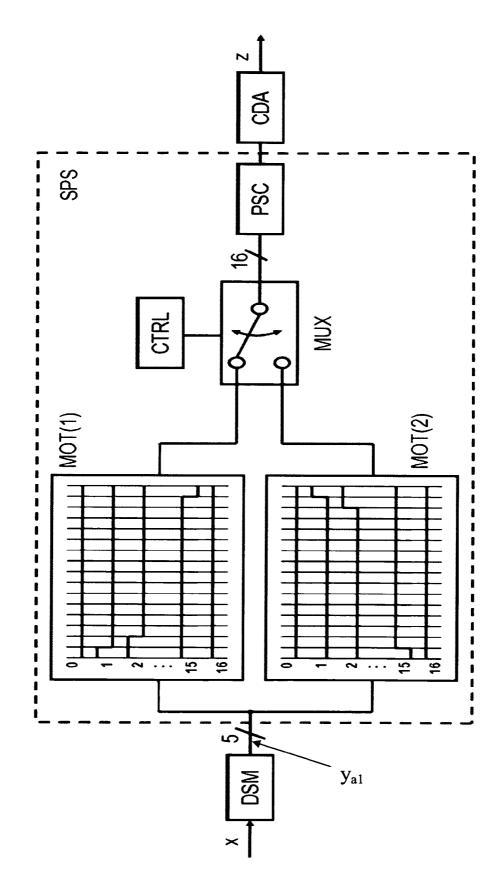

la figura 10 una configuración de la arquitectura del dispositivo según la invención según la figura 9 para el caso de la rotación de palabra,

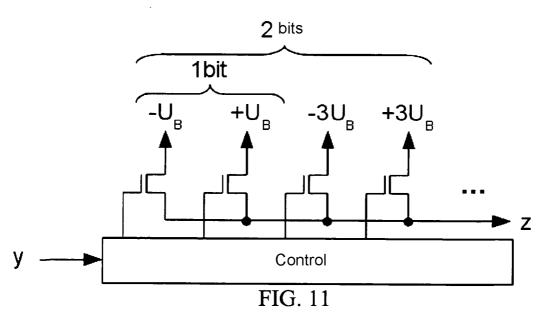

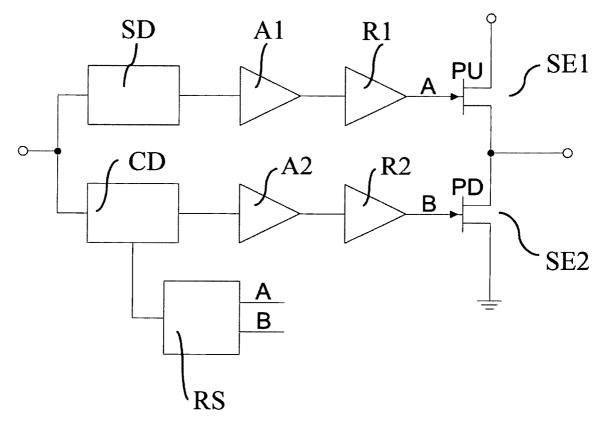

la figura 11 un ejemplo de realización para un amplificador de conmutación multibit CDA.

la figura 12 un ejemplo de realización para un amplificador CDA con un bucle de control de tipo DDL,

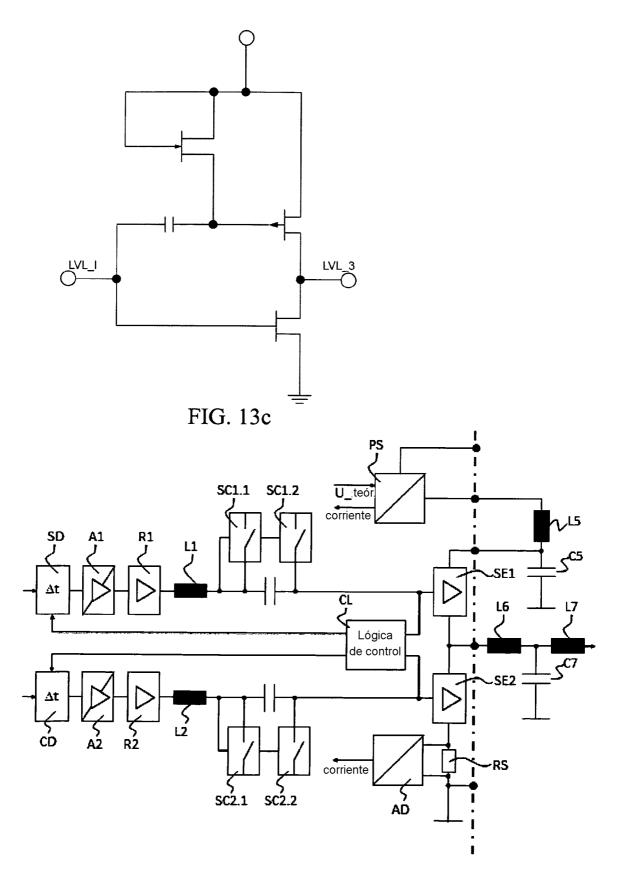

50 las figuras 13a, 13b y 13b tres configuraciones de un elemento de adaptación y

la figura 14 una configuración para un circuito para la generación de un rango de tensión de alimentación variable para un amplificador de conmutación.

Las figuras 1a, 1b muestran dos y la figura 9 una configuración adicional de la arquitectura del dispositivo según la invención con un modulador delta-sigma DSM y un amplificador de conmutación conectado al mismo (amplificador digital) CDA en particular para el caso de aplicación PLC (*PowerLine Communication*-(PLC)). Los sistemas PLC son sistemas de transmisión de mensajes, que distribuyen información a través del medio de cable de energía eléctrica incluyendo el enlace de transmisión entre estación de transformación en la red de baja tensión y la instalación del cliente en el domicilio. Para este caso de aplicación PLC, en particular para el caso de la PLC de banda estrecha en el intervalo de frecuencia de aproximadamente 9 a 500 kHz, en la actualidad, teniendo en cuenta las normas aplicables en cada caso (por ejemplo la norma europea (CENELEC EN 50065) o la norma estadounidense FCC parte 15 subparte B), están disponibles técnicas que permiten la transmisión de datos bidireccional con tasas de algunos cientos de kBit/s. En la norma EN 50065 por ejemplo se especifican cuatro intervalos de frecuencia, las amplitudes de emisión permitidas como máximo en este caso y los derechos de uso. En la banda A, en Europa las empresas de suministros energéticos utilizan el intervalo de 9 ... 95 kHz con una amplitud de emisión máxima de 10

V. En el lado del consumidor en Europa está disponible el intervalo de 95 ... 148,5 kHz con una amplitud de emisión máxima de 1,2 V (banda B hasta banda D). En la transmisión de datos los módulos de acoplamiento de bus, que cumplen con las funciones de transmisión y recepción del sistema de transmisión de red, deben considerar las particularidades dadas por la línea de suministro eléctrico de 230 V como bus. Se trata en primer lugar de la necesidad del aislamiento galvánico entre bus y aplicación, en segundo lugar el problema de la impedancia variable del punto respectivo en la red de suministro, al que está conectado el módulo de acoplamiento de bus, en tercer lugar las diferencias relacionadas en el nivel de transmisión presente en la red y el alcance de transmisión relacionado y en cuarto lugar la recepción de señal en presencia de diferentes interferencias de red en la banda de frecuencia de transmisión, como por ejemplo impulsos de sobrevoltaje y ráfagas así como diferentes formas de ruido, así como las distorsiones del canal.

En la primera configuración (véase la figura 1a) en la salida multibit del modulador delta-sigma DSM está conectado un convertidor paralelo a serie SPS, compuesto por un circuito en serie de un convertidor paralelo a serie PSC y un elemento de rotación dispuesto aguas abajo SHS y en la segunda configuración (véase la figura 1b) está conectado un convertidor paralelo a serie SPS\*, compuesto por un circuito en serie de un elemento de rotación SHP y el convertidor paralelo a serie dispuesto aguas abajo PSC, con lo que se procesa una señal de entrada alimentada al modulador delta-sigma DSM con una relación de sobremuestreo reducida y una relación señal a ruido elevada. A este respecto, en la entrada del amplificador de conmutación CDA hay una señal de un bit. Un amplificador de elemento de conmutación de un bit presenta con respecto a los amplificadores de elemento de conmutación multibit menos pérdidas de corriente. Los elementos de conmutación pueden estar realizados por ejemplo por MOSFET, IGBT (insulated-gate bipolar transistor, transistor bipolar de puerta aislada) o CMOS (componentes semiconductores en los que se utilizan tanto MOSFET de canal p como de canal n sobre un sustrato común).

La base del amplificador de conmutación CDA según la invención descrito a continuación es construir un circuito 25 resonante a partir de la capacidad de puerta del transistor de salida y una bobina a integrar. Una gran ventaja de esta estructura es que puede almacenarse energía durante la conmutación, con lo que aumenta la eficiencia. No obstante cabe indicar que para alcanzar una eficiencia elevada del 90% tiene que almacenarse la mayor cantidad de energía posible. Sin embargo, esto requeriría una gran inductancia, que no obstante presenta una resistencia de carga mayor y prácticamente no puede integrarse en el chip. Además, las bobinas integradas ocupan superficies 30 grandes lo que aumenta el tamaño del chip. Por tanto, es necesario un compromiso entre bobina de controlador de puerta y controlador de salida, que puede llevar a que posiblemente tengan que construirse varias etapas de resonancia para poder cumplir con el requisito con respecto al ancho de pulso hasta el controlador de salida. Preferiblemente el amplificador de conmutación CDA está compuesto por dos ramas paralelas con en cada caso un circuito de retardo SD, CD en serie, un elemento de adaptación A1, A2 para la adaptación de la tensión de alimentación de un elemento de conmutación S1, S2 y un controlador de resonancia R1, R2 para la conmutación del 35 elemento de conmutación S1. S2. Además en un bucle de control de tipo DLL se toman los flancos de conmutación en la salida del controlador de resonancia R1, R2 y se alimentan a un comparador de fase y a partir de la diferencia, por medio de un circuito de control, se determina el tiempo de retardo y de manera correspondiente se ajusta el circuito de retardo CD. En la forma de realización representada en la figura 12 el circuito de retardo SD presenta un 40 tiempo de retardo fijo, mientras que el tiempo de retardo del circuito de retardo CD puede ajustarse de manera variable, es decir, se produce un control dinámico del desplazamiento de señal. Así, de manera ventajosa, pueden compensarse la temperatura, envejecimiento, varianzas de componentes (dispersión de los parámetros de proceso) y fluctuaciones de tensión. Mediante el control de tensión también se modifica el comportamiento de conmutación, de modo que se consigue un control (control de tensión) en el control (control de flancos adaptado). Los elementos 45 de conmutación S1, S2 tienen que controlarse con una precisión determinada, para que en la medida de lo posible no aparezcan corrientes cruzadas entre los elementos de conmutación S1, S2 y al mismo tiempo, en la medida de lo posible, se cumpla con tiempos de retardo reducidos, en los que ambos transistores están cerrados. Para ello es necesario adaptar los flancos de las señales de control exactamente uno respecto a otro. Esto se lleva a cabo según la invención mediante medición y posterior recorte. El enfoque según la invención se basa en el diseño de un bucle 50 de control de tipo DLL, que adapta los flancos y anchos de pulso de tal modo que los dos criterios se cumplan de la mejor manera posible. Además, el enfoque se basa en elementos de retardo controlables (circuito de retardo CD) y un detector de fase. A este respecto, debe garantizarse que se evite el caso en el que ambos elementos de conmutación/transistores S1. S2 son al mismo tiempo conductores, porque este estado operativo lleva a daños en los componentes y que puedan utilizarse las formas de señal, que sirven para controlar el amplificador de 55 conmutación CDA.

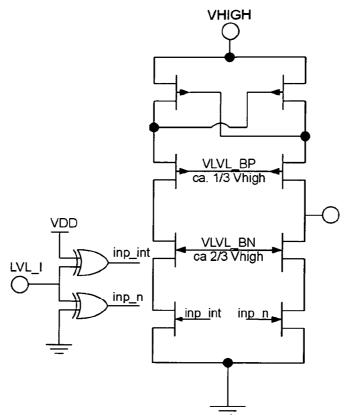

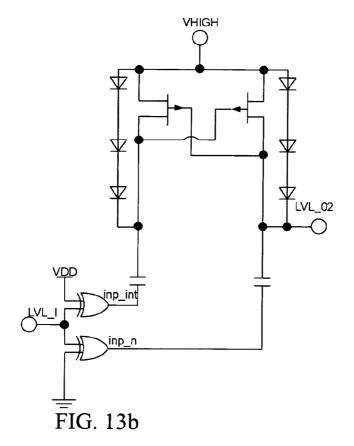

Las señales de entrada para el amplificador de conmutación CDA las proporciona un IC digital con nivel lógico de 3,3 V (salida del convertidor paralelo a serie SPS). Por tanto, es necesario cambiar el nivel lógico para controlar los controladores de resonancia R1, R2. Mediante la especificación se obtienen requisitos estrictos con respecto al elemento de adaptación A1, A2:

- · poco consumo eléctrico y

- cambio rápido de 3,3 V a tensiones < 40 V

65

60

10

15

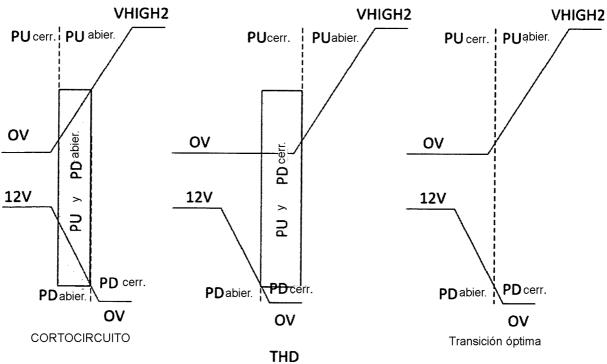

Todos los enfoques mostrados a continuación en las figuras 12a, b y c muestran un comportamiento comparable, tanto con respecto al comportamiento en el tiempo como en el consumo eléctrico. Por el contrario, aparecen diferencias en la complejidad. De manera inherente se produce el problema de la regeneración de flancos una vez que la tensión de alimentación > 24 V. En este caso debe considerarse de nuevo la limitación mediante U<sub>GS(MAX)</sub>. Para el control de los transistores *pull-down* sólo son necesarios transistores de 12 V, lo que es favorable para el uso de superficie y la velocidad.

En general el elemento de adaptación A1, A2 sólo es necesario cuando la tensión de alimentación supera un determinado nivel. En particular, para el caso del suministro mínimo de 2 V puede prescindirse de la conversión.

Para garantizar un control apropiado también en este caso es necesario prever una comunicación entre el suministro eléctrico y la ruta de la señal. Así, en función de la tensión de alimentación seleccionada puede seleccionarse la ruta óptima de la señal para el control.

Mediante el concepto según la invención es posible conectar también anchos de pulso mínimos de 3,9 ns. A este respecto la eficiencia, determinada por medio de medición de potencia de los transistores individuales, se sitúa entre el 91% y el 93%. Para la etapa de potencia pueden seleccionarse transistores, obtenidos a partir de variantes de 40 V, con lo que puede ahorrase aproximadamente un 30-40% de superficie y los requisitos con respecto al control pueden ser más convenientes.

En los dos casos del tipo de etapa de potencia son necesarias tensiones de alimentación adicionales. El concepto NN requiere una alimentación aumentada para el *pull-up*, una tensión situada 12 V por debajo para el controlador de puerta, así como una tensión de 12 V para el *pull-down*. El enfoque PN requiere también los 12 V así como la alimentación reducida en 12 V. Cuál se utilice depende del dimensionamiento de la etapa de salida y de la eficiencia obtenida de este modo.

En un ejemplo de realización representado en la figura 11 para un CDA de etapa de potencia MOSFET multibit según el número de bits (en este caso: M-\_CDA=2) se alimentan  $2^{M-\_CDA}=2^2=4$  potenciales a través de conmutadores MOSFET en la salida z. Según la respectiva señal de entrada y (de manera correspondiente  $y_{a3}$  o  $y_{b3}$  en las figuras 1a/b), un control (control CTRL) conmuta en el reloj de chip  $f_c$  el respectivo potencial en la salida z.

Además en el DSM o en la entrada del DSM se produce un sobremuestreo con un determinado factor de sobremuestreo (OSR). En general ocurre que la relación señal a ruido (SNR) que puede alcanzarse aumenta según aumenta el factor de sobremuestreo (OSR). Por consiguiente, para conseguir una SNR lo más elevada posible sería deseable un factor de sobremuestreo (OSR) lo más elevado posible. Sin embargo, por otro lado los factores de sobremuestreo (OSR) que pueden utilizarse están limitados con vistas a la frecuencia de conmutación resultante en la entrada del amplificador de conmutación y la dificultad de implementación relacionada.

Después del sobremuestreo tiene lugar el filtrado de la señal en un filtro de bucle (*Loop-Filter*). El filtro de bucle contiene en principio un filtro de transferencia de señal (*Signal-Transfer-Filter*) para la señal de entrada del DSM y un filtro de transferencia de ruido (*Noise-Transfer-Filter*) para la señal retroalimentada de la salida de un cuantificador Q del modulador delta-sigma DSM. En este sentido, los filtros convencionales tienen el problema de que en el intervalo de los factores de sobremuestreo (OSR) considerados no alcanzan la relación señal a ruido (SNR) necesaria o deseada. Por tanto, en este caso, no se emplea un filtro convencional sino un filtro diseñado para tasas de muestreo reducidas, un denominado filtro RSR (RSR: *Reduced-Sampling-Rate*). Los filtros convencionales o su uso se describen por ejemplo en el libro técnico "Understanding Delta-Sigma Data Converters" de Richard Schreier y Gabor Temes, Wiley Interscience Publication 2005, ISBN 0-471-46585-2 página 91 y siguientes; los filtros RSR se conocen por ejemplo por el artículo "Low-Voltage Sigma-Delta Modulator Topologies For Broadband Applications" de Mohammed Yavari y Omid Shoaei publicado en IEEE International Symposium on Circuits and Systems, ISCAS 2004, páginas 465-468.

Para el uso considerado se tienen en cuenta como filtros RSR aquellos filtros que están optimizados con respecto a los parámetros de sistema respectivos (ancho de banda de señal, frecuencia de muestreo, factor de sobremuestreo (OSR)).

En el caso de utilizar filtros RSR las relaciones señal a ruido (SNR), en el intervalo de los factores de sobremuestreo (OSR) considerados, se sitúan claramente por encima con respecto a los filtros convencionales. La implementación de la solución según la invención muestra que así el uso de filtros RSR en la salida del convertidor paralelo a serie PSC lleva a una frecuencia de conmutación claramente inferior (por ejemplo por un factor de 3).

60 El DSM está realizado preferiblemente de manera reconfigurable para permitir una adaptación flexible a diferentes parámetros de sistema (por ejemplo parámetros de transmisión como la banda de frecuencia utilizada); para ello se escriben los coeficientes en un registro especial (no representado en el dibujo). Ejemplos de los parámetros de sistema almacenados en el registro son:

65 - tasa de muestreo f<sub>s</sub>

25

30

35

40

45

- tasa de palabra fw

- tasa de chip fc

10

15

20

25

30

35

40

45

65

- parámetros a1, a2, b1, b2 del filtro de bucle (en particular filtro RSR).

En el caso del amplificador de potencia considerado en el marco de la invención se trata de electrónica de potencia, por ejemplo de transistores C-MOS, que debido a sus flancos de conmutación relativamente largos (inherentes a la tecnología) está sometido a una limitación importante con respecto a las frecuencias de reloj utilizadas. Éstas tienen como consecuencia que, a partir de una determinada frecuencia, ya no se detectan pulsos de duración muy corta y por tanto se producen errores en el procesamiento de señal que llevan a un empeoramiento de la SNR en la salida.

Como en la salida del DSM existe una señal multibit y el CDA según la invención espera una señal de un bit, entre los bloques funcionales correspondientes es necesaria una conversión de señal. Esta conversión de señal la realiza el convertidor paralelo a serie SPS o SPS\* de tal modo que con condiciones de implementación lo más favorables posible se produce una SNR lo más elevada posible en la salida del amplificador de conmutación CDA.

La implementación de este convertidor paralelo a serie SPS o SPS\* según la invención puede producirse, como ya se explicó anteriormente, mediante el bloque P/S PSC y el bloque de rotación dispuesto aguas abajo SHS (véase la figura 1a) o alternativamente según la figura 1b mediante el bloque de rotación SHP y el bloque P/S PSC dispuesto aguas abajo. La siguiente descripción se refiere a la configuración según la figura 1a.

El bloque P/S PSC está con el modulador delta-sigma DSM y convierte la señal de salida y<sub>a1</sub> multibit del cuantificador Q del DSM con la frecuencia de muestreo f<sub>DSM</sub> con M bits en una señal y<sub>a2</sub> de un bit similar a PDM (PDM modulación de duración de pulso) con la frecuencia de muestreo f<sub>PS,a,</sub>. A este respecto, en función del valor multibit existente en cada caso de la señal de entrada y<sub>a1</sub>, a una frecuencia constante se modula el ciclo de trabajo (ancho) de la señal de salida y<sub>a2</sub>. Es decir, cada valor de M bits se convierte en una palabra de N<sub>PS</sub> valores binarios consecutivos, que según la invención representan el valor de M bits de manera similar a un valor PDM. Esto significa que por cada palabra de la señal de salida y<sub>a2</sub> como máximo puede aparecer un cambio entre unos y ceros o ceros y unos binarios.

En la representación entre valor multibit de la entrada y<sub>a1</sub> y de la salida y<sub>a2</sub> resulta decisivo que se lleve a cabo de manera lineal. A partir de esta conversión paralelo a serie resulta por consiguiente una señal que como mucho contiene una transición entre valores binarios (unos y ceros o a la inversa) en cada caso en los límites de palabra y/o una transición entre valores binarios en cada caso dentro de una palabra.

La multiplicación de reloj necesaria en la conversión P/S se produce con un factor, que es igual a la longitud de palabra  $N_{PS}$  (longitud de palabra de la señal similar a PDM en la salida del convertidor P/S PSC). A este respecto, la longitud de palabra  $N_{PS}$  y con ello también el factor para la multiplicación de reloj se seleccionan en función del intervalo de valores utilizado de  $y_{a1}$  o del número de  $N_{DSM}$  (número de posibles valores adoptados por  $y_{a1}$  en la salida del DSM; corresponde al factor de sobremuestreo (OSR)) de posibles valores adoptados por  $y_{a1}$ . En la selección de  $N_{PS}$  debe tenerse en cuenta que por un lado todos los  $N_{DSM}$  posibles valores de  $y_{a1}$  pueden representarse de la manera mencionada anteriormente de manera reversible y unívoca en una palabra de la salida  $y_{a2}$  y que por otro lado, con vistas a la implementación resulta un factor lo más reducido posible para la multiplicación de reloj  $N_{PS}$ .

Preferiblemente se realiza la selección teniendo en cuenta estos dos criterios

$$N_{PS} = N_{DSM} - 1$$

Ahora, según la invención, para la reducción de la frecuencia de conmutación en una etapa adicional, concretamente en el bloque SHS, se lleva a cabo una rotación adaptiva y de memoria de los pulsos y a este respecto, se transforma la señal de entrada y<sub>a2</sub> por palabras en la señal de salida y<sub>a3</sub>. En función del último valor de bit (0 o 1) de la palabra anterior en cada caso en la señal de salida y<sub>a3</sub> resultante dado el caso se rota el pulso actual o se transfiere sin cambios a la señal de salida y<sub>a3</sub>, de tal modo que se minimiza el número de los flancos de pulso (es decir, cambio del valor de bit 0 a 1 o a la inversa) en y<sub>a3</sub>. La primera palabra se transfiere preferiblemente sin cambios, sin embargo en el marco de la invención la rotación también puede realizarse aquí. El control de reloj (véase la figura 1a) proporciona los relojes fs (reloj de muestreo), fw (reloj de palabra) y fc (reloj de chip/bit), de los cuales los respectivamente necesarios se sitúan en los bloques funcionales individuales. Así, en el reloj de palabra se almacena de manera intermedia el último bit en cada caso de la palabra anterior de la señal y<sub>a3</sub> en la memoria intermedia BUF. A su vez el control CTRL controla en función del valor de bit en la memoria intermedia BUF y la palabra actual en la salida del DSM, en particular el 1<sup>er</sup> bit, el desplazamiento en el bloque SHS.

A este respecto, por rotación del pulso se entiende que se cambia el orden de los ceros y unos binarios de este pulso (en caso de existir). Es decir, a partir de una palabra (pulso) que comienza con k unos binarios seguido de (N<sub>PS</sub>-k) ceros binarios en el caso de una rotación se obtiene una palabra (pulso) que comienza con (N<sub>PS</sub>-k) ceros

binarios seguido de k unos binarios. Así, el número de ceros y unos de un pulso no cambia por la rotación, sólo varía su orden.

Por tanto, mediante este tipo de conversión paralelo a serie según la invención con rotación adaptiva y de memoria de los pulsos desaparecen los flancos de pulso en los límites de palabra, mientras que permanecen los flancos de pulso dentro de los límites de palabra, aunque dado el caso desplazados, de modo que en última instancia se reduce claramente el número de los flancos de pulso en la entrada del amplificador de conmutación CDA (amplificador digital) mediante la rotación (más precisamente: aproximadamente se divide por la mitad). Esta reducción se produce en la misma medida para la frecuencia de conmutación de los elementos semiconductores en la etapa de potencia así como para las señales existentes en los puntos de conexión del chip.

10

15

20

25

30

35

40

45

50

55

Los efectos de esta rotación sobre la forma de señal pueden pasarse por alto, ello no distorsiona la señal de manera relevante/importante. Sin embargo, por otro lado, la división por la mitad alcanzada de la frecuencia de conmutación con la misma tecnología permite una frecuencia de muestreo mayor en la entrada del DSM o un factor de sobremuestreo (OSR) mayor, con lo que puede conseguirse una SNR mayor en la salida.

Una ventaja adicional de esta rotación es que con un modulador de duración de pulso PDM convencional la frecuencia portadora está presente como componente de señal marcada en la señal de salida, porque el flanco ascendente dentro de una palabra (más precisamente: en los límites de palabra) siempre aparece en el mismo punto (es decir, a la misma distancia). Por el contrario, en el procedimiento según la invención ya no hay flancos de la señal PDM en puntos fijos. De este modo, con la frecuencia portadora ya no aparece ninguna componente significativa, sino que se distribuye ("se extiende") por varias frecuencias (alrededor de la frecuencia portadora). Esto permite un cumplimiento simplificado de los valores límite en las mediciones del espectro de transmisión para cumplir con las normas.

Mediante el siguiente ejemplo de realización se describirá y explicará adicionalmente el procedimiento según la invención. Se amplificará una señal útil dentro de un intervalo de frecuencia de aproximadamente 10 kHz a 500 kHz, que puede asumir anchos de banda de desde 10 kHz hasta 400 kHz. La señal a amplificar está en la entrada con una tasa de muestreo de aproximadamente 2 msps con una resolución de 12 bits. La señal de entrada, que en el caso considerado es una señal OFDM, tiene un rango dinámico de aproximadamente el 87% de la resolución de 12 bits. Ahora, por medio del dispositivo según la invención con un factor de sobremuestreo (OSR) reducido de 8 se alcanzará una SNR total de más de 60 dB. La frecuencia de conmutación buscada para la salida del DSM (es decir, en la entrada del amplificador de conmutación) es de aproximadamente 8 MHz. A este respecto, se distinguirá entre dos frecuencias, concretamente la frecuencia portadora y el armónico más alto. La frecuencia portadora se calculará de la siguiente manera:

Frecuencia de muestreo de la señal de entrada • factor de sobremuestreo del DSM/2

El factor ½ procede de la rotación de palabras, de modo que en el ejemplo de realización la frecuencia portadora se sitúa en 2 MHz • 8/2 = 8 MHz.

Como DSM se emplea en este caso una arquitectura de  $4^{\circ}$  orden, como se representa en la figura 2, que en sí misma se conoce por el artículo "A Reduced-Sample-Rate Sigma-Delta-Pipeline ADC Architecture for High-Speed High-Resolution Applications" de Vahid Majidzadeh y Omid Shoaei publicado en IEICE Transactions 89-C(6): 692-701 (2006).

A este respecto, un filtro de bucle especial de la clase de los filtros RSR (*Reduced-Sampling-Rate-Filter*), con un filtro NTF de orden más alto, proporciona valores de SNR mayores con relaciones de sobremuestreo (OSR) reducidas. La función de transmisión H(z) es la siguiente:

$$H(z) = \frac{b_1 z^{-1} + b_2 z^{-2}}{1 - a_1 z^{-1} - a_2 z^{-2}}$$

El cuantificador distingue aquí  $N_{DSM}=17$  etapas en la entrada y las convierte en cada caso en un valor de 5 bits (es decir, M=5). Cada valor de 5 bits en la entrada del convertidor paralelo a serie PSC se convierte con el mismo en una palabra binaria de longitud  $N_{PS}=N_{DSM}-1=16$ . Para la siguiente representación puede suponerse para simplificar que los valores de 5 bits de la señal  $y_{a1}$  están en el intervalo de valores [0; 16]. La conversión P/S del valor  $y_{a1}[n]$  puede producirse entonces por ejemplo mediante  $y_{a1}[n]$  unos binarios y ( $N_{PS}-y_{a1}[n]$ ) ceros posteriores. Esto se representa en el siguiente ejemplo para los valores  $y_{a1}[n]$  de 9, 4 y 10, que para simplificar se denominan  $y_{a1}[1]$ ,  $y_{a1}[2]$  e  $y_{a1}[3]$ . El valor  $y_{a1}[1]=9$  se representa por ejemplo en  $y_{a2}$  por 9 unos binarios y 7(=16-9) ceros binarios. Para facilitar la lectura, en este sentido, los límites de palabra se ilustran mediante '|' y para aclarar los flancos de señal en cada caso el '1' tiene una raya por encima y el '0' por debajo.

La formación de la señal  $y_{a3}$  se produce según la invención de la siguiente manera: como el primer valor  $y_{a1}[1]$  no tiene ningún valor anterior, la secuencia de bits correspondiente se transfiere sin cambios de  $y_{a2}$  a  $y_{a3}$ . Para el valor

$y_{a1}[1]$  la secuencia correspondiente de  $y_{a3}$  termina con '0'. Como la secuencia correspondiente a  $y_{a1}[2]$  en  $y_{a2}$  comienza con '1', ahora esta secuencia se transfiere según la invención rotada a  $y_{a3}$ , es decir, comenzando con sus ceros binarios. Así, para el valor  $y_{a1}[2]$  la secuencia correspondiente de  $y_{a3}$  termina con '1'. Como la secuencia correspondiente a  $y_{a1}[3]$  en  $y_{a2}$  también comienza con '1', ahora esta secuencia se transfiere sin cambios a  $y_{a3}$ . Así, en comparación con la señal  $y_{a2}$  en  $y_{a3}$  se eliminan los flancos de pulso (transiciones 1-0 o 0-1) en los límites de palabra entre  $y_{a1}[1]$  e  $y_{a1}[2]$  así como entre  $y_{a1}[2]$  e  $y_{a1}[3]$ .

- 10 Mediante la rotación de palabra según la invención se alcanzan las siguientes ventajas:

- 1- Se extiende la frecuencia portadora, que se genera mediante los pulsos PDM que comienzan en puntos fijos (véase el espectro de potencia de la señal de salida del modulador de duración de pulso PDM con/sin rotación de palabra en la comparación de las figuras 6a y 6b).

- 2- Las frecuencias de conmutación en los pulsos de salida se dividen por la mitad → pérdidas de potencia reducidas.

- 3- Los pulsos cortos (o hendiduras ("Notches")) son cada vez menos frecuentes.

15

50

- En comparación con los filtros NTF convencionales, los polos y ceros en este filtro están colocados de otra manera, lo que da como resultado una mejor estabilidad. La figura 3 muestra dos puntos óptimos para los polos y ceros según el artículo citado anteriormente "A Reduced-Sample-Rate Sigma-Delta-Pipeline ADC Architecture for High-Speed High-Resolution Applications" de Vahid Majidzadeh y Omid Shoaei obra citada para la arquitectura de 4º orden según la figura 2.

- La figura 4 muestra para un ejemplo el espectro de densidad de potencia para la señal DSM multibit en tres puntos del dispositivo según la invención, concretamente en la entrada del sistema, en la salida del cuantificador y en la salida del sistema. Para una mejor comparabilidad en este caso se ha utilizado un seno.

- 30 Además se utilizó un filtro de tasa de muestreo reducida de 4º orden y el DSM utilizó una relación de sobremuestreo de 8, de modo que con la señal de entrada existente con una tasa de muestreo de 2 msps en la salida del DSM había una señal con una tasa de reloj de 16 msps. El cuantificador en la salida del DSM generó con una distinción de 17 estados una secuencia de valores de 5 bits.

- A partir de este ejemplo resulta evidente que a pesar del factor de sobremuestreo reducido (OSR) utilizado de 8 en la salida del sistema se alcanza la SNR deseada de más de 60 dB. A partir de aquí puede reconocerse la ventaja clara del procedimiento/dispositivo según la invención con respecto a los sistemas convencionales, con los que esto no sería alcanzable.

- 40 La figura 5 muestra una distribución de probabilidad del número de pulsos dentro de la representación de PDM en el ejemplo de una secuencia de señales OFDM real (frecuencia portadora fc=150 KHz, ancho de banda B=50 KHz) tras su procesamiento mediante el modulador delta-sigma RSR y la posterior conversión paralelo a serie SPS según la invención. A partir de aquí puede reconocerse que los pulsos críticos (pulsos con un uno a partir de en total 16 ranuras o 15 unos a partir de en total 16 ranuras en la secuencia PDM de manera correspondiente a un pulso muy corto (positivo) o una interrupción muy corta) en la señal OFDM sólo se producen con muy poca probabilidad. Esta probabilidad es claramente superior sin el procedimiento según la invención (no se representa en la figura 5) y con ello también la probabilidad de un empeoramiento de la señal.

- Al mismo tiempo, en el caso convencional (es decir, sin tasa de muestreo reducida) se produce una mayor frecuencia de conmutación en la entrada del amplificador de conmutación CDA. Debido a la característica de paso bajo ya mencionada de los puntos de conexión del chip de este modo se agravaría el problema de la detección fiable de flancos de conmutación cortos. Éste es el caso porque con una frecuencia ascendente también aumenta el intervalo, con respecto al ancho de los flancos de conmutación, en el reloj de muestreo, en el que ya no pueden detectarse pulsos de manera fiable. Si a consecuencia de la tecnología de chip utilizada con una frecuencia de reloj de 128 MHz en el amplificador de conmutación CDA ya sólo se detectan pulsos de un ancho de 1 reloj de muestreo de manera poco fiable, entonces esto también es aplicable con una frecuencia superior (a partir de aproximadamente 256 MHz) para pulsos con un ancho de dos relojes de muestreo. Esta distorsión de la señal de salida también es concebible cuando se consideran las características de los puntos de conexión del chip. Para

pulsos cortos (o hendiduras cortas) los retardos típicos llevan con flancos ascendentes (flancos descendentes) a distorsiones de la señal de salida.

El empleo de frecuencias de reloj inferiores, como es posible mediante el procedimiento según la invención, tiene adicionalmente un efecto positivo sobre la SNR por la reducción resultante de distorsiones de señales. A partir de aquí resulta evidente que el uso de una OSR reducida tiene una gran importancia.

La figura 6a muestra el espectro de potencia de la señal de salida de un PDM con o la figura 6b sin rotación de palabra en el ejemplo de una señal OFDM con una frecuencia portadora (o también: frecuencia central) de 150 kHz y un ancho de banda útil de 50 kHz. En este sentido se utilizó una relación de sobremuestreo (OSR) de 8 y una longitud de palabra de 16 en la salida del convertidor P/S.

10

15

65

En la figura 6b puede verse claramente la frecuencia portadora PDM (16 MHz) como pico sobresaliente así como componentes adicionales alrededor de esta frecuencia portadora. A este respecto, la frecuencia portadora PDM supera las frecuencias de señal propiamente dichas en aproximadamente 30 dB. Las componentes de ruido alrededor de la señal OFDM están desplazadas hacia arriba por el DSM en el intervalo de frecuencia, de modo que en el intervalo de frecuencia de interés existe una SNR de poco menos de 50 dB.

En la figura 6a puede reconocerse que, por la conversión P/S especial y la división por la mitad conseguida de este modo del reloj de conmutación, la componente con la frecuencia portadora PDM se desplazó en su mayor parte hasta la mitad de la frecuencia portadora (8 MHz). Lo mismo ocurre para algunas componentes claramente inferiores alrededor de la frecuencia portadora. Mediante un paso bajo de reconstrucción posterior (en el presente ejemplo con una frecuencia de corte de 700 kHz) se filtran estas componentes de señal. Además con respecto al caso representado en la figura 6b se obtienen las ventajas de que por un lado la componente marcada, procedente de la frecuencia portadora (en la figura 6b con 16 MHz; en la figura 6a desplazada 8 MHz) ya es algunos dB inferior, y por otro lado también las componentes en la frecuencia inferior de 8 MHz son más convenientes con respecto a la radiación.

Las figuras 7a, 7b muestran esencialmente el mismo resultado que las figuras 6a, 6b, aunque en el ejemplo de una señal sencidal con 200 kHz. En este caso, en la comparación de las dos figuras 7a y 7b puede reconocerse que mediante el procedimiento según la invención el pico sobresaliente con la frecuencia portadora se desplazó y "extendió" hasta un intervalo más ancho por la mitad de la frecuencia portadora. Además, la componente interferente con el doble de la frecuencia de señal sencidal se extendió por un lado hacia el intervalo de frecuencia circundante, una componente marcada restante se ha desplazado además hacia arriba en la frecuencia y se debilitó claramente (en más de 20 dB).

Así, a partir de las figuras 7a, 7b y las figuras 6a, 6b resultan evidentes las siguientes ventajas esenciales del procedimiento según la invención:

- Las componentes en el intervalo de frecuencia alto disminuyen claramente, lo que tiene un efecto claramente positivo sobre el funcionamiento de los transistores.

- Se reducen claramente las componentes interferentes en el entorno de las frecuencias de señal.

- La figura 8 muestra el principio de la rotación adaptiva y de memoria según la invención de los pulsos en el ejemplo de un fragmento de señal en la salida del convertidor P/S especial. La figura 8a muestra la secuencia de los pulsos antes de (o sin) rotación y la figura 8b tras la rotación. A partir de aquí puede reconocerse la clara reducción en el número de flancos de señal producida por la rotación.

- El funcionamiento de la configuración de la conversión de señal por medio del elemento de rotación SHP y el convertidor paralelo a serie dispuesto aguas abajo PSC entre el modulador delta-sigma DSM y el amplificador de conmutación conectado al mismo CDA según la figura 1b es análogo, de modo que puede prescindirse de una explicación más detallada. A este respecto, la señal de salida y<sub>b1</sub> paralela del cuantificador (Q) en el elemento de rotación SHP se procesa mediante una rotación adaptiva y de memoria de los pulsos de tal manera que se cambia el orden de los ceros y unos binarios de este pulso (en caso de existir) y a este respecto, la señal de entrada y<sub>b1</sub> se transforma por palabras en la señal de salida y<sub>b2</sub>. A continuación, en el convertidor paralelo a serie PSC conectado al elemento de rotación SHP se convierte la señal de salida y<sub>b2</sub> multibit del elemento de rotación SHP con la frecuencia de muestreo f<sub>DSM</sub> con M bits en una señal y<sub>b3</sub> de un bit similar a PDM con la frecuencia de muestreo f<sub>PS,b</sub>, modulándose en función del valor multibit existente en cada caso de la señal de entrada y<sub>b2</sub> a una frecuencia constante el ciclo de trabajo de la señal de salida y<sub>b3</sub> de tal modo que por cada palabra de la señal de salida y<sub>b3</sub> aparece como máximo un cambio entre unos y ceros o ceros y unos binarios.

La figura 9 muestra una configuración adicional de la arquitectura del dispositivo según la invención. A este respecto, el convertidor paralelo a serie SPS está compuesto por K tablas de modulación conectadas en paralelo MOT(k) con un multiplexador dispuesto aguas abajo MUX así como un convertidor paralelo a serie PSC dispuesto aguas abajo del mismo. En las tablas de modulación MOT(k) se representa cada valor de entrada multibit (del DSM) en una

disposición (por regla general) diferente de unos y ceros binarios, es decir, cada valor de M bits se convierte en una palabra de N<sub>PS</sub> valores binarios consecutivos. El multiplexador dispuesto aguas abajo MUX representa un medio para la selección que en función de un control CTRL para cada reloj de un valor de entrada en cada caso pone la salida de una tabla de modulación MOT(k), es decir, la palabra formada en la misma, en la salida. Entonces, en el convertidor paralelo a serie dispuesto aguas abajo PSC se produce una conversión de las palabras binarias en valores binarios en serie.

En el ejemplo de la figura 9 se convierte cada valor de 5 bits en la salida del DSM en cada una de las K tablas de modulación dispuestas aguas abajo MOT(k) en una palabra binaria de longitud N<sub>PS</sub>= N<sub>DSM</sub>-1=16. Para la siguiente representación puede suponerse de nuevo para simplificar que los valores de 5 bits de la señal y<sub>a1</sub> se encuentran en el intervalo de valores [0: 16].

10

15

20

25

35

40

45

55

60

La conversión del valor  $y_{a1}[n]$  en una tabla de modulación MOT(k) se produce preferiblemente mediante  $y_{a1}[n]$  unos binarios y ( $N_{PS^-}$   $y_{a1}[n]$ ) ceros, resultando en función de la respectiva tabla de modulación MOT(k) una diferente representación en o disposición de unos y ceros binarios. Al contrario que el caso especial también descrito de la rotación de palabra, la disposición de estos unos y ceros binarios es en principio aleatoria, es decir, ya no tienen que estar correlacionados obligatoriamente. Por un lado se renuncia a la búsqueda de una minimización del número de flancos de conmutación, por otro lado, sin embargo, mediante la selección adecuada de las tablas de modulación MOT(k) y su control por el multiplexador MUX pueden alcanzarse propiedades espectrales mejoradas.

El control/elemento de control CTRL lleva a cabo el control del multiplexador MUX y con ello la selección de qué salida de qué tabla de modulación MOT(k) se conmuta en cada caso al convertidor paralelo a serie PSC y así, qué representación del valor de M bits en la salida del DSM en una palabra binaria se conmutará a la entrada del PSC. Este control por medio de un control/elemento de control CTRL puede llevarse a cabo tanto con memoria, como de manera sistemática o también de manera aleatoria. En la implementación de un control aleatorio para cada palabra se genera un número aleatorio y con ello se produce la selección de la tabla de modulación que se aplicará para la respectiva palabra o la decisión de si deberá realizarse una rotación. El beneficio reside en que mediante la selección aleatoria del tipo de conversión utilizado de un valor de salida DSM en una secuencia de bits concreta, por ejemplo mediante la selección aleatoria para cada palabra de una de las tablas de modulación, se consigue una distribución espectral de componentes interferentes de la conmutación del amplificador D, convirtiéndose en particular líneas de interferencia discretas con amplitud de interferencia elevada en componentes interferentes de banda ancha con una densidad de potencia espectral reducida.

El número K de las tablas de modulación a utilizar MOT(k), sus contenidos (patrón de representación) así como el tipo de control del multiplexador mediante el control/elemento de control CTRL se seleccionan en función de las propiedades a alcanzar de la señal de salida y las posibilidades en la implementación del amplificador de conmutación CDA. Así, por ejemplo, en la respectiva configuración de la invención puede considerarse si la reducción del número de flancos de conmutación existentes en la entrada del siguiente CDA o las propiedades espectrales de la señal de salida del CDA son más importantes para la respectiva aplicación e implementación.

La figura 10 muestra un caso especial del caso general descrito en la figura 9. La tabla de modulación superior MOD(1) representa el valor de 5 bits en la entrada en cada caso en una señal PDM de un bit, por el contrario, la tabla de modulación inferior MOD(2) realiza con respecto a MOD(1) una representación rotada, es decir, en este caso las palabras representadas están rotadas en cada caso con respecto a MOD(1). De este modo resulta evidente que este caso especial al utilizar un control de memoria del multiplexador MUX corresponde al procedimiento ya descrito de la rotación adaptiva y de memoria de los pulsos. La figura 10 corresponde así a otra representación de la figura 1b.

Así, las configuraciones de la invención descritas hasta ahora con un circuito en serie de un convertidor paralelo a serie y de un elemento de rotación (SHS o SHP) representan casos especiales del dispositivo según la invención según la reivindicación 3.

La invención no está limitada a los procedimientos o bloques funcionales descritos sino que comprende también otros procedimientos que tienen el mismo efecto esencial para la invención. Así, en el marco de la invención, en lugar de una conversión P/S y una rotación de memoria, como se representa en la figura 1a y la figura 1b, también puede llevarse a cabo una conversión P/S con representación de memoria directa de los valores. La generación del pulso de salida puede producirse para ello por ejemplo mediante un contador (no representado en el dibujo). Éste se reinicia al inicio de cada palabra. Cuando se alcanza un estado predeterminado del contador se conmuta la salida en cada caso.

En un ejemplo de realización concreto esto se implementa de la siguiente manera: en el orden normal (es decir, sin rotación de palabra) se activa la salida al inicio de cada palabra y al alcanzar el estado del contador según el valor de la salida DSM (es decir,  $y_{a1}$  o  $y_{a2}$  según la figura 1a o la figura 1b) se desactiva la salida.

En el orden inverso (es decir, con rotación de palabra) se desactiva la salida al inicio de cada palabra y al alcanzar el estado del contador de [salida N<sub>PS</sub> - DSM] (es decir [N<sub>PS</sub> - y<sub>a1</sub>] según la figura 1a o [N<sub>PS</sub> - y<sub>a2</sub>] según la figura 1b) se

activa la salida (N<sub>PS</sub>=relación palabra/tasa de bits). La selección del respectivo modo operativo (con/sin rotación de palabra) se produce al inicio de cada palabra basándose en el último bit de la palabra anterior.

Los dispositivos según la invención permiten un aumento evidente de la eficiencia energética, una reducción de la pérdida de potencia y un rango de tensión de alimentación variable y con ello una adaptación de la dinámica con una SNR óptima con impedancia de red variable y con ello una potencia de transmisión variable adaptada. La adaptación de la tensión de alimentación y la potencia de transmisión relacionada permite evitar la sobrecarga del amplificador CDA, así como el recorte de la señal útil y su distorsión por efectos de saturación (inductancias, diferencia residual con respecto a tensión de alimentación, sobremodulación, correspondiente a faltas de linealidad o un control 10 deficiente en la reducción del alcance). La determinación de la potencia de transmisión, potencia de salida del amplificador de conmutación CDA, como muestra la figura 14, puede determinarse con una medición de corriente a través de una carga (shunt) RS en el elemento de conmutación SE1, SE2 con una Ri conocida, o en el suministro de potencia para el CDA, o a través del canal de recepción RXD del sistema de comunicación durante la transmisión activa. A este respecto, el circuito de retardo SD, CD y el elemento de adaptación A1, A2 corresponden a los de la 15 figura 12 y en la figura 14 R1 y R2 son controladores con bobina en la salida de la última etapa de potencia de condensador de refuerzo (SC1.1, SC1.2, SC2.1, SC2.2), que funciona como precontrolador de resonancia para la generación de flancos.

#### REIVINDICACIONES

- 1. Dispositivo con un modulador delta-sigma (DSM) y un amplificador de conmutación (CDA) conectado al mismo, en el que puede alimentarse una señal de audio a la entrada del modulador delta-sigma (DSM), convirtiéndose una señal de entrada alimentada al modulador delta-sigma (DSM) en una señal de salida ya2 de un bit similar a PDM con como máximo un cambio entre unos y ceros o ceros y unos binarios, caracterizado por que en la salida multibit del modulador delta-sigma (DSM) está conectado un convertidor paralelo a serie SPS con un circuito en serie de un convertidor paralelo a serie PSC y un elemento de rotación dispuesto aguas abajo (SHS) para la señal de salida ya2 en serie del convertidor paralelo a serie PSC y el convertidor paralelo a serie SPS como modulador de duración de pulso convierte cada valor de M bits en una palabra a partir de N<sub>ps</sub> valores binarios, y por que el elemento de rotación (SHS) en función del último valor de bit 0 o 1 de una palabra anterior en cada caso en la señal de salida ya3 resultante cambia el orden de los ceros y unos binarios de la palabra actual, en caso de existir, de tal modo que para la reducción adicional de los flancos de pulso en la señal de salida ya2[i] del convertidor paralelo a serie SPS del convertidor paralelo a serie SPS ésta se transfiere sin cambios a la señal de salida ya3[i] resultante del elemento de rotación (SHS) del convertidor paralelo a serie SPS, cuando ya3[i-1] termina con el mismo valor binario con el que comienza ya2[i], e ya2[i] se transfiere rotada a ya3[i], cuando ya3[i-1] termina con el valor binario opuesto con el que comienza ya2[i].

- 2. Dispositivo con un modulador delta-sigma (DSM) y un amplificador de conmutación (CDA) conectado al mismo, en 20 el que puede alimentarse una señal de audio a la entrada del modulador delta-sigma (DSM), convirtiéndose una señal de entrada alimentada al modulador delta-sigma (DSM) en una señal de salida ya2 de un bit similar a PDM con como máximo un cambio entre unos y ceros o ceros y unos binarios, caracterizado por que en la salida multibit del modulador delta-sigma (DSM) está conectado un convertidor paralelo a serie SPS\* con un circuito en serie a partir de un elemento de rotación (SHP) para la señal de salida yb1 paralela del modulador delta-sigma (DSM) y un convertidor paralelo a serie dispuesto aguas abajo PSC y el convertidor paralelo a serie SPS como modulador de 25 duración de pulso convierte cada valor de M bits en una palabra a partir de N<sub>ps</sub> valores binarios, y por que el elemento de rotación (SHP) en función del último valor de bit 0 o 1 de una palabra anterior en cada caso en la señal de salida yb3 resultante cambia el orden de los ceros y unos binarios de la palabra actual, en caso de existir, de tal modo que para la reducción adicional de los flancos de pulso en la señal de salida del convertidor paralelo a serie 30 SPS\* en la señal de salida yb2[i] del elemento de rotación (SHP) ésta se transfiere sin cambios a yb3[i], cuando yb3[i-1] termina con el mismo valor binario con el que comienza yb2 [i], e yb2[i] se transfiere rotada a yb3[i], cuando yb3[i-1] termina con el valor binario opuesto con el que comienza yb2[i].

- 3. Dispositivo según la reivindicación 1, caracterizado por que en la salida del modulador delta-sigma (DSM) está dispuesto un cuantificador (Q), por que el convertidor paralelo a serie (PSC) conectado al modulador delta-sigma (DSM) convierte la señal de salida y<sub>a1</sub> multibit del cuantificador (Q) con la frecuencia de muestreo f<sub>DSM</sub> con M bits en una señal y<sub>a2</sub> de un bit similar a PDM con la frecuencia de muestreo f<sub>PS,a</sub>, modulándose en función del valor multibit existente en cada caso de la señal de entrada y<sub>a1</sub> a una frecuencia constante el ciclo de trabajo de la señal de salida y<sub>a2</sub> de tal modo que por cada palabra de la señal de salida y<sub>a2</sub> aparece como máximo un cambio entre unos y ceros o ceros y unos binarios.

- 4. Dispositivo según la reivindicación 3, caracterizado por que para la reducción de la frecuencia de conmutación en el elemento de rotación (SHS) conectado al convertidor paralelo a serie (PSC) se lleva a cabo una rotación adaptiva y de memoria de pulsos (palabras) de tal modo que se cambia el orden de los ceros y unos binarios del pulso (en caso de existir) y a este respecto, se transforma la señal de entrada y<sub>a2</sub> por palabras en la señal de salida y<sub>a3</sub>.

- 5. Dispositivo según la reivindicación 2, caracterizado por que en la salida del modulador delta-sigma (DSM) está dispuesto un cuantificador (Q), por que la señal de salida y<sub>b1</sub> paralela del cuantificador (Q) en el elemento de rotación (SHP) se procesa mediante una rotación adaptiva y de memoria de pulsos (palabras) de tal manera que se cambia el orden de los ceros y unos binarios del pulso (en caso de existir) y a este respecto, se transforma la señal de entrada y<sub>b1</sub> por palabras en la señal de salida y<sub>b2</sub>.

- 6. Dispositivo según la reivindicación 5, caracterizado por que el convertidor paralelo a serie (PSC) conectado al elemento de rotación (SHP) convierte la señal de salida y<sub>b2</sub> multibit del elemento de rotación (SHP) con la frecuencia de muestreo f<sub>DSM</sub> con M bits en una señal y<sub>b3</sub> de un bit similar a PDM con la frecuencia de muestreo f<sub>PS,b</sub>, modulándose en función del valor multibit existente en cada caso de la señal de entrada y<sub>b2</sub> a una frecuencia constante el ciclo de trabajo de la señal de salida y<sub>b3</sub> de tal modo que por cada palabra de la señal de salida y<sub>b3</sub> aparece como máximo un cambio entre unos y ceros o ceros y unos binarios.

- 7. Dispositivo según la reivindicación 1, caracterizado por que en la entrada del modulador delta-sigma (DSM) tiene lugar un sobremuestreo con un factor de sobremuestreo que puede fijarse y por que tras el sobremuestreo tiene lugar el filtrado de la señal en un filtro de bucle, que presenta un filtro de transferencia de señal (Signal-Transfer-Filter) para la señal de entrada del modulador delta-sigma (DSM) y un filtro de transferencia de ruido (Noise-Transfer-Filter) para la señal retroalimentada de la salida de un cuantificador Q del modulador delta-sigma DSM.

45

50

10

8. Dispositivo según la reivindicación 7, caracterizado por que el filtro de bucle de la clase de los filtros RSR con un filtro NTF de orden más alto presenta la función de transmisión

$$H(z) = \frac{b_1 z^{-1} + b_2 z^{-2}}{1 - a_1 z^{-1} - a_2 z^{-2}}$$

- 9. Dispositivo según la reivindicación 1, caracterizado por que el modulador delta-sigma (DSM) presenta un registro, en el que para la reconfiguración se escriben diferentes parámetros de sistema para permitir una adaptación flexible.

- 10. Dispositivo según una de las reivindicaciones 1 a 2, caracterizado por que el amplificador de conmutación (CDA) está compuesto por dos ramas paralelas con en cada caso un circuito de retardo (SD, CD) en serie, un elemento de adaptación (A1, A2) para la adaptación de la tensión de alimentación de un elemento de conmutación (S1, S2) y un controlador de resonancia (R1, R2) para la conmutación del elemento de conmutación (S1, S2), por que en un bucle de control de tipo DLL se toman los flancos de conmutación en la salida del controlador de resonancia (R1, R2) y se alimentan a un comparador de fase y por que a partir de la diferencia, por medio de un circuito de control (RS), se determina el tiempo de retardo y de manera correspondiente se ajusta el circuito de retardo (CD).

- Dispositivo según la reivindicación 10, caracterizado por que para la determinación de la potencia de transmisión y la potencia de salida del amplificador de conmutación (CDA) se produce una medición de corriente a través de una carga (shunt) (RS) en el elemento de conmutación (SE1, SE2) con una Ri conocida, o en un suministro de potencia para el amplificador de conmutación (CDA) o a través de un canal de recepción RXD de un sistema de comunicación en la transmisión activa, de modo que se genera un rango de tensión de alimentación variable para el amplificador de conmutación (CDA).

FIG. 1b

FIG. 3

FIG. 4a

FIG. 4b

FIG. 4c

FIG. 5

FIG. 6a

FIG. 6b

FIG. 7a

FIG. 7b

FIG. 9

FIG. 10

FIG. 12

FIG. 13a

FIG. 14