(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 694 168**

(51) Int. Cl.:

**G06F 13/42** (2006.01)

**G11C 29/12** (2006.01)

**G06F 13/40** (2006.01)

**G11C 29/02** (2006.01)

**G11C 29/04** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- (86) Fecha de presentación y número de la solicitud internacional: **24.03.2015 PCT/IB2015/052141**

(87) Fecha y número de publicación internacional: **01.10.2015 WO15145347**

(96) Fecha de presentación y número de la solicitud europea: **24.03.2015 E 15723553 (2)**

(97) Fecha y número de publicación de la concesión europea: **22.08.2018 EP 3123348**

---

(54) Título: **Módulo de control para gestión de múltiples recursos de señales mixtas**

(30) Prioridad:

**24.03.2014 PT 10753714**

(45) Fecha de publicación y mención en BOPI de la traducción de la patente:

**18.12.2018**

(73) Titular/es:

**INESC TEC - INSTITUTO DE ENGENHARIA DE SISTEMAS E COMPUTADORES, TECNOLOGIA E CIENCIA (100.0%)

Campus da FEUP Rua Dr Roberto Frias 378

4200-465 Porto, PT**

(72) Inventor/es:

**PEIXOTO MACHADO DA SILVA, JOSÉ ALBERTO;

PAIVA VELHOTE CORREIA, MIGUEL FERNANDO y

SALAZAR ESCOBAR, ANTÓNIO JOSÉ**

(74) Agente/Representante:

**ARIAS SANZ, Juan**

ES 2 694 168 T3

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Módulo de control para gestión de múltiples recursos de señales mixtas

**5 Campo técnico**

La presente invención se refiere a un módulo y su método de operación que puede implementarse como un PLD (dispositivo de lógica programable, FPGA (campo de matriz de puertas programables), un circuito integrado, o sustrato similar.

**10 Antecedentes de la técnica**

Los circuitos componentes y sensores son vulnerables al envejecimiento, uso, problemas ambientales y físicos, diversos factores imprevistos, ya sea con configuraciones controladas por laboratorio o escenarios de aplicación en el campo, que representan una preocupación creciente para la fiabilidad de los datos. Esto es un problema particular en aplicaciones de seguridad crítica, en concreto, de sistemas electrónicos médicos y de automóviles.

Tales problemas de fiabilidad de datos se han tratado a través de un número de estrategias ad hoc o una mezcla de normas en su mayoría dirigidas a escenarios digitales; sin embargo, los escenarios de múltiples sensores rara vez se benefician de tales enfoques.

El documento CN102866967 desvela un método de gestión de equipo de I2C (circuito inter-integrado). De acuerdo con dicho documento, múltiples equipos de I2C en un equipo de máquina anfitrión pueden gestionarse eficazmente. Sin embargo, esta solución tiene como objetivo el problema de direcciones de bus de I2C limitadas, en particular en escenarios donde un número de dispositivos del mismo tipo necesitan accederse de manera individual mientras comparten la misma dirección de I2C (o un subconjunto limitado). Por lo tanto, la solución anteriormente mencionada está limitada a problemas de gestión de accesibilidad y no permite sincronización de intra e inter módulo y/o tiene un conjunto de instrucciones de I2C ampliado asociado.

El documento US 2012/066423 A1 describe una solución para facilitar la expansión de un único bus de I2C a múltiples dispositivos. Esta solución presenta varios problemas, tal como la centralización de las accesibilidades del dispositivo a través de un módulo expansor común. Aunque tal enfoque permite capacidades de multi-difusión y difusión a dispositivos con una dirección común, el enfoque metodológico crea un cuello de botella a través del módulo expansor descrito. Tal limitación no permite escalabilidad distribuida y agrupar físicamente dispositivos a un módulo expansor específico. Adicionalmente, la solución presentada no permite intra e inter sincronización de módulo, puesto que tiene como objetivo únicamente flexibilidad de accesibilidad de comunicación.

En general, las soluciones de la técnica anterior no permiten direccionalidad flexible, configurable y ampliable granular a través de un enfoque descentralizado. Además, el conjunto asociado de mecanismos e instrucciones descritos por la presente, introducen intra- e inter- sincronización y/o gestión de módulo, ampliable a circuitos de señal mixta, sensores, y todo tipo de dispositivos y ampliación mientras sean compatibles con I2C.

El documento US6237112B1 desvela un dispositivo SCSI disponible para predicción de avería y auto-examinación o un método de predicción de avería y auto-examinación por este dispositivo que aumenta el rendimiento del sistema global a través de la reducción de la carga de un procesador de I2C maestro y bus SCSI, informando al procesador de I2C maestro únicamente cuando sea necesario, después de que un procesador de I2C lee el estado del dispositivo SCSI. El dispositivo SCSI disponible para predicción de avería y auto-examinación incluye un sensor de accionamiento de temperatura y motor, que monitoriza el estado de accionamiento de temperatura y motor del dispositivo SCSI; un sensor de potencia y un conmutador de encendido/apagado, que monitoriza la potencia del dispositivo SCSI y recibe un comando desde el procesador de I2C maestro para encender/apagar la potencia del dispositivo SCSI a través del procesador de I2C; un sensor SMART, que monitoriza el estado del dispositivo SCSI: una lógica de control de dispositivo, que informa todos los informes de estado anteriores, informes de error y funciones SMART al procesador de I2C maestro a través del controlador SCSI; un procesador de I2C, que informa al procesado de I2C maestro 130 a través de un canal SCSI o canal de I2C, cuando sea necesario, analizando una información detectada por la temperatura, sensor de accionamiento de motor, sensor de potencia, conmutador de encendido/apagado y sensor SMART.

**Divulgación de la invención**

La presente solución tiene por objeto escenarios intra e inter modulares y otros escenarios de recursos independientes o inter-dependientes pretendidos para gestión de recursos como parte de una metodología aplicable a un número de escenarios de sistema tales como, pero sin limitación, monitorización a largo plazo de sensor/componentes para calibración, pruebas, mediciones y/o estrategias de sincronización de grupo para análisis de datos.

Se describe una ampliación a instrumentos compatibles con I2C. Se describe un módulo integrado, denominado de ahora en adelante como módulo de Configuración, Captura, Proceso y Exploración (SCPS). Los mismos módulos de SCPS han de subdividirse en cuatro secciones:

- 5 - un intérprete de I2C, que sigue el modo convencional UM10204, "especificación de bus de I2C y manual de usuario", modo convencional con capacidades de dirección esclava de 10 bits;

- 10 - un intérprete de SCPS, un superconjunto de instrucciones para ampliar la funcionalidad de I2C, introducir capacidades de direccionamiento de grupo e instrucciones embebidas dentro de la referencia de grupo de módulo objetivo;

- una sección de conmutación/control, pretendida para gestión de encaminamiento de aspectos de control asociados opcionales, tales como un bus analógico; y

- 15 - un banco de registros, para control de secuencia de respuesta, declaración de bandera y otros aspectos de capacidad de observación y capacidad de control.

El mecanismo propuesto está estructurado alrededor de cuatro tipos de operación. Tales operaciones se han de gestionar a través de un conjunto de registros e instrucciones accedidas a través de un bus de I2C.

20 Una vista general de las operaciones anteriormente mencionadas se presenta a continuación:

- Configuración: pretendida para configuración independiente de evento intra-modular de ajustes/registros de los dispositivos objetivo; considerada para configuración de dispositivo. Acciones de ejemplo incluyen: precarga de señal/patrón, ajustes de muestreo, agrupamiento de componentes, procedimiento de manejo BIST, y parámetros definidos por la entrada de usuario.

- Captura: pretendida para gestionar escenarios dependientes de evento inter-modular, tales como carga/generación de señal/patrón, colección de datos y activación BIST.

- 25 - Proceso: pretendido para escenarios dependientes de evento intra-modular, tales como procesamiento de datos y activaciones de algoritmos de toma de decisiones. Un ejemplo de tales operaciones es la comparación de datos recopilados reflejados a través de actualizaciones de registros objetivo que pueden usarse para seguir el historial de sensor, mantenimiento de referencia global o comparación de referencia específica. Puede activarse algoritmo/heurística localizados tales como rutinas de procesamiento de señal generadas, estrategias de media de mínimos cuadrados (LMS), filtros de Kalman, cadenas de Markov, etc., a través de estas operaciones.

- 30 - Exploración: pretendida para distribución de datos e instrucciones, como para cubrir tareas independientes de evento inter-modular. Las posibilidades de interactuar con elementos externos para modos de configuración y recogida de datos se consideran en esta etapa.

- 35 -

- 40 -

La presente solución representa una ampliación a un intérprete de un bus de I2C, con características ampliadas que mantiene compatibilidad hacia atrás completa. También constituye una estructura con flexibilidad para adaptarse a unos fines del diseñador de electrónica.

45 Posibilita a un maestro en un bus de I2C común leer o escribir, así como controlar a través de un conjunto de instrucciones dadas, todos los módulos esclavos, grupos de módulos esclavos o cualquier módulo esclavo de manera individual que esté conectado al bus de I2C común: por lo tanto añade accesibilidad granular a I2C.

50 Posibilita también un maestro en un bus de I2C común con acceso sincronizado a múltiples módulos esclavos conectados al bus de I2C común.

55 Adicionalmente, con el módulo de extensión de manejador de SCPS, también permite que se amplíen los mismos efectos que en los efectos 1 y 2 a elementos analógicos y/o digitales del sistema asimismo, añadiendo una fuente de gestión de capacidad de control y capacidad de observación a través del módulo de SCPS.

60 Acelera la comunicación, en ciertos escenarios, entre un maestro y varios esclavos reduciendo la longitud de las secuencias implicadas. Particularmente en casos donde el registro de LECTURA/ESCRITURA objetivo tenga la misma dirección entre los módulos implicados, reduciendo la operación a una secuencia de grupo (SWA o SRA dependiendo del caso) en lugar de múltiples secuencias específicas de dispositivo.

65 También acelera y simplifica la transferencia de datos de esclavo a esclavo, añadiendo la capacidad de una transferencia controlada por maestro de un registro desde un esclavo (que proporciona el registro) a otro (que recibe el registro) en una única operación.

Adicionalmente facilita la sincronización de acciones inter-módulo desde una perspectiva específica global y de grupo, proporcionando banderas, registros y elementos de control opcionales que facilitan la coordinación de acciones inter-módulo a través de un formato de conjunto de instrucciones común y recursos.

- 5 Facilita la implementación de estrategias de testigo a través del uso del conjunto de instrucciones global para solicitud de recursos, que genera instancias a un mecanismo para verificación de disponibilidad de recursos.

10 También proporciona mecanismo de bloqueo de operación, es decir, un sub-conjunto de instrucciones permite reducir la funcionalidad del módulo de SCPS en cuanto a limitar una respuesta del módulo. Esto se pretende que sirva como un mecanismo para aislar un miembro de grupo en caso de mal-funcionamiento o fallo detectado.

15 Adicionalmente, amplía el conjunto de instrucciones de SOLICITUD GENERAL establecido de I2C para permitir acciones de RESTEO o de impacto global (tal como aislamiento de módulos, omisión, etc., requerido durante un evento de inicialización o de re-calibración).

20 15 Facilita operaciones secuenciales e instantáneas inter-módulo para un sub-conjunto de instrucciones (es decir, instrucciones de CAPTURA), que cuando se utilizan apropiadamente pueden sincronizar las acciones de módulo individuales para permitir una operación de grupo, que puede actualizarse secuencialmente a través de parámetros definidos por el usuario y flujo de instrucciones específicas, reduciendo de esta manera las secuencias de comunicación y reduciendo posiblemente recursos permitiendo la re-utilización sincronizada.

25 20 También reduce, en ciertos escenarios, los recursos que se requerirían para realizar las mismas operaciones en múltiples módulos permitiendo la reutilización de recursos a través de la sincronización y gestión de acción inter-módulo.

30 25 Adicionalmente, reduce la necesidad de direcciones de I2C de 7 bits individuales a través del uso de una dirección de grupo compartido, 10 bits u 8 bits, y la dirección de miembro, proporcionando de esta manera flexibilidad en el esquema de direccionamiento individual y reduciendo la dependencia al dominio de direcciones de 7 bits disponible.

35 30 La presente solución proporciona flexibilidad de implementación, mientras permite compatibilidad con numerosos sensores comerciales a través del uso de I2C como el bus de comunicación. Tal enfoque permite también la inclusión de sensores comercialmente disponibles (compatibles con I2C) en las estrategias de prueba/calibración ampliando su funcionalidad; ofreciendo en consecuencia una infraestructura de prueba y medición de señal mixta. Adicionalmente, la solución trata las especificidades de soluciones de monitorización basadas en sensor a largo plazo continuas.

#### **Breve descripción de los dibujos**

40 Las siguientes figuras proporcionan realizaciones preferidas para ilustrar la descripción y no deberían observarse como que limitan el alcance de la invención.

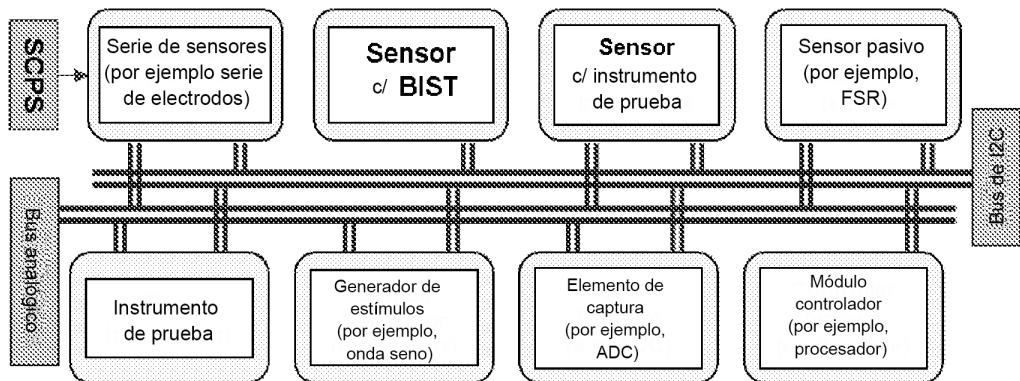

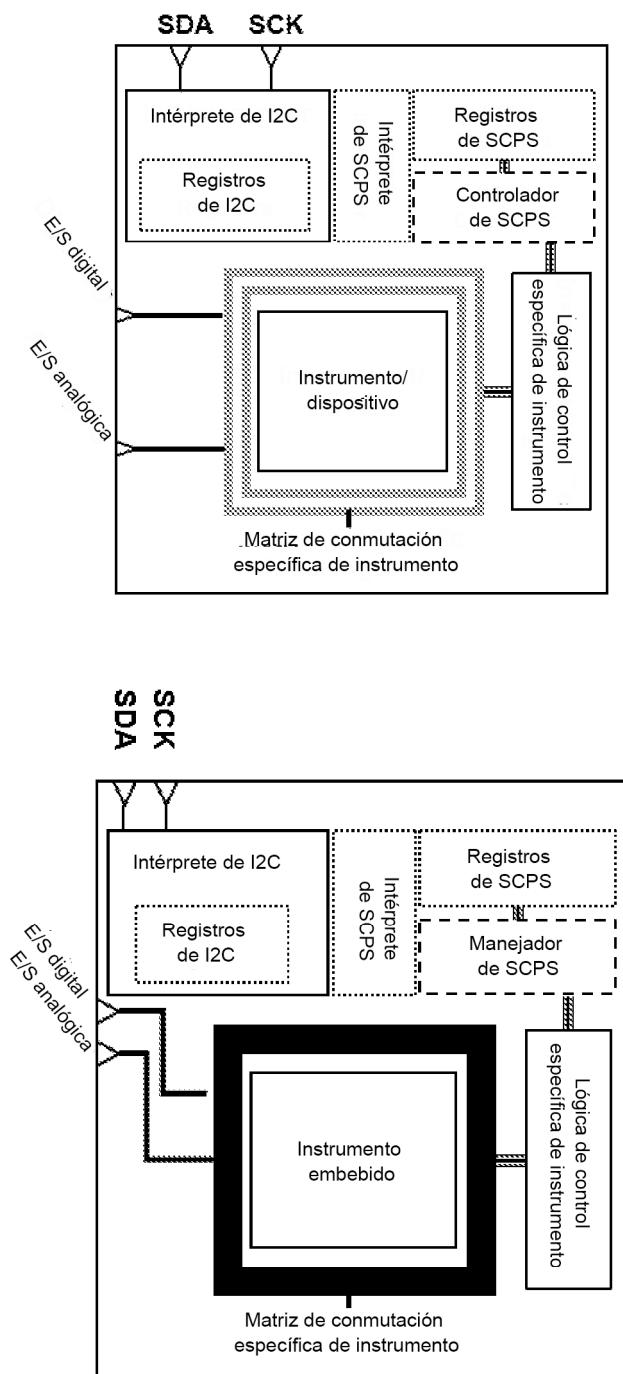

45 La Figura 1 muestra una representación esquemática de una realización de ejemplo de módulos de SCPS como parte de un esquema de gestión de recursos.

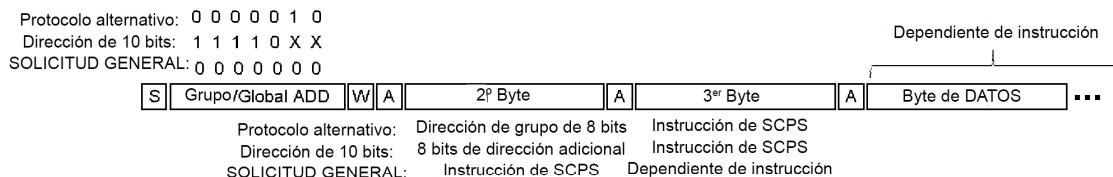

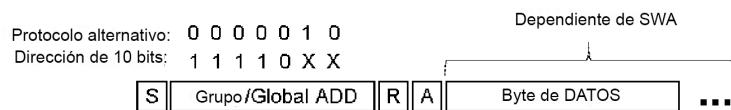

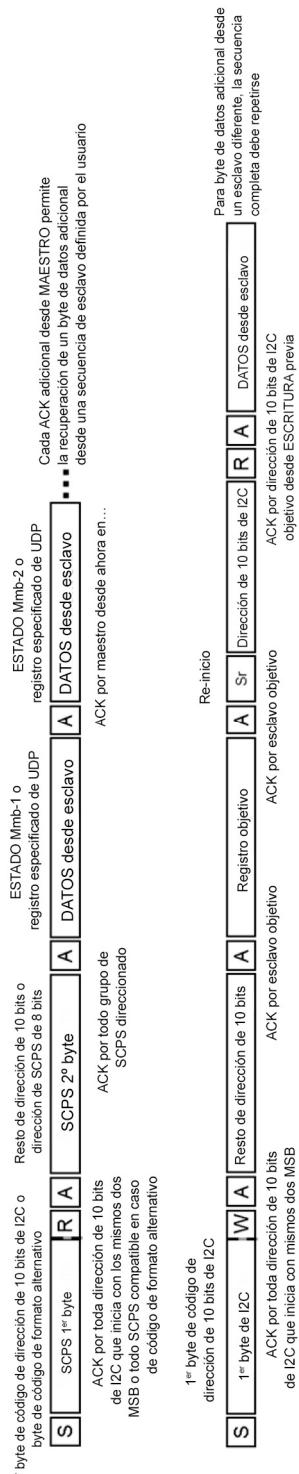

50 La Figura 2 muestra una representación esquemática de secuencias de tipo de Acción de Escritura de SCPS (SWA) y Acción de Lectura de SCPS (SRA) que permiten la escritura y lectura en una manera en grupo, así como acciones inter-dependientes e independientes sincronizadas entre instrumentos compatibles con SCPS.

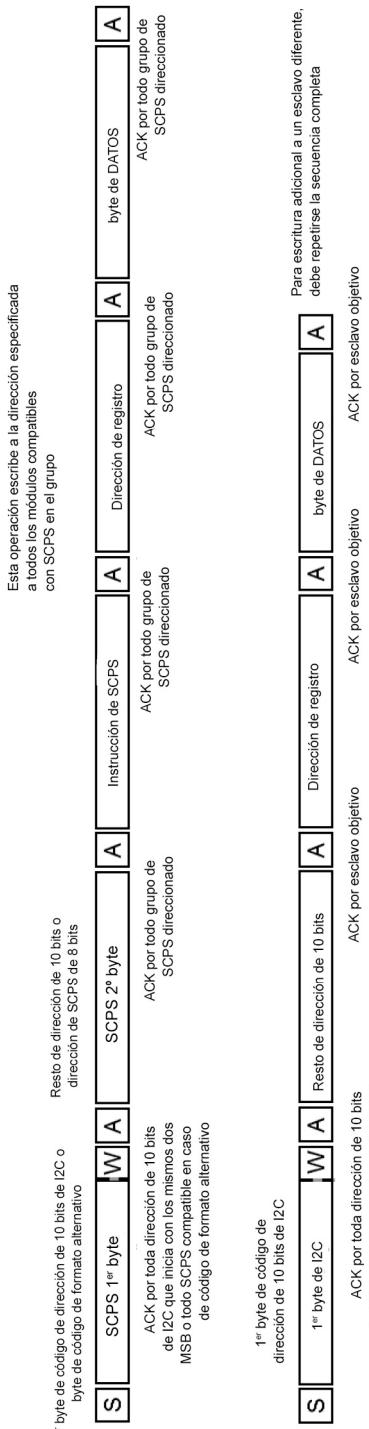

55 La Figura 3 muestra una representación esquemática de una representación modular de una implementación de módulo de SCPS genérico.

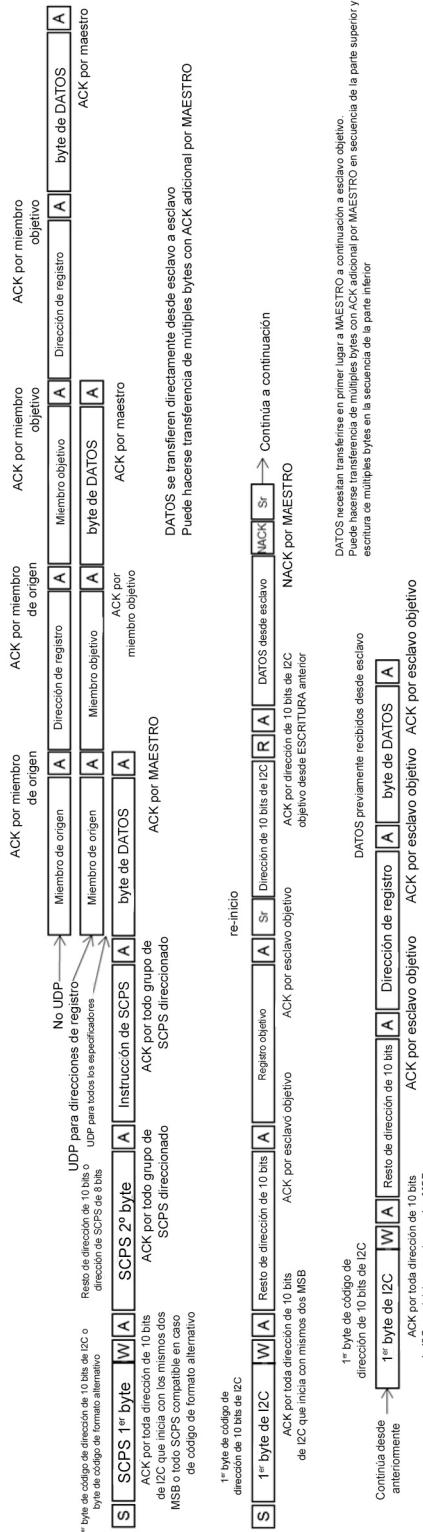

La Figura 4 muestra un flujo de datos y operación genérico para múltiples lecturas de dispositivo.

55 La Figura 5 muestra un flujo de datos y operación genérico para múltiples escrituras de dispositivo.

55 La Figura 6 muestra un flujo de datos y operación genérico para múltiples transferencias de dispositivo.

#### **Mejor modo para llevar a cabo la invención**

60 En el presente documento se describen realizacionesopcionales en más detalle, que, sin embargo, no están pretendidas para limitar el alcance de la presente solicitud.

#### **Módulo de SCPS**

65 En una realización, el módulo de SCPS está compuesto de dos secciones de módulo de extensión para diseños compatibles con I2C actuales: un módulo de extensión de intérprete de I2C (intérprete de SCPS), y un módulo de

extensión de banco de registros (registros de SCPS). Opcionalmente, un tercero está también comprendido por el módulo de SCPS: un módulo de extensión de banco de elementos (manejador de SCPS).

El módulo de extensión de intérprete de I2C (intérprete de SCPS) cuenta con el mecanismo para que un identificador de secuencia reconozca secuencia de comandos asociados con SCPS, así como el correspondiente mecanismo de respuesta para actualizar banderas, registros y elementos del módulo de SCPS, y respuestas de señal de I2C que están asociadas con SCPS (por ejemplo, acuses de recibo apropiados a instrucciones de SCPS); tanto para secuencias de I2C de escritura como de lectura, que, de ahora en adelante, se denominarán como Acción de Escritura de SCPS (SWA) y Acción de Lectura de SCPS (SRA), respectivamente, cuando tales secuencias de I2C están asociadas a una secuencia de SCPS.

El intérprete identifica tres tipos de formatos de direccionamiento: global (denominado como SOLICITUD GENERAL en las especificaciones de I2C UM10204), grupo (alcanzable a través de dos tipos de alternativas seleccionables) y específico (asociado al formato de dirección de 7 bits de I2C o a través del uso de un identificador de miembro de grupo a través de instrucciones de SCPS). La dirección de 7 bits de I2C tradicional permanece completamente compatible para tales instrumentos que tienen una dirección de 7 bits asociada, y provocará que el intérprete de SCPS ignore cualquier secuencia adjunta de este tipo, permitiendo de esta manera que el instrumento sea accesible a través de medios de I2C directos (por lo tanto no se incluirán referencias adicionales en este documento a tal tipo de direccionamiento).

Para direccionamiento global, el intérprete de SCSP esperará una Instrucción Global de SCPS (SGI) formateada después de una SOLICITUD GENERAL (todo ceros según se definen por especificaciones de I2C, es decir, 8h00) y acuse de recibo en consecuencia. Una vista general de las correspondientes SGI y sus acciones pueden hallarse en la sección de conjunto de instrucciones a continuación y una descripción del flujo de secuencia puede hallarse en la sección de flujo de trabajo.

Con respecto al direccionamiento de grupo, para flexibilidad se permiten dos formatos de direccionamiento de grupo: formato de direccionamiento de 10 bits o formato de protocolo alternativo. Los formatos de direccionamiento de 10 bits consideran que los módulos compatibles con SCPS que conforman un grupo tienen una dirección de I2C de 10 bits compartida denominada como Dirección de Grupo de 10 bits (10GA).

En el caso del formato de protocolo alternativo, se usa la dirección de I2C de 7 bits reservada 7b0000010 (reservada para usar diferentes protocolos y formatos) como un iniciador de secuencia que el protocolo de SCPS ha de utilizar y una se espera a continuación una Dirección de Grupo de 8 bits (8GA) como un segundo byte en el caso de una secuencia de escritura. Para una secuencia de lectura se espera un acceso de escritura anterior a una 8GA específica siguiendo el mismo flujo que la lectura de I2C de 10 bits. Ambos formatos de direccionamiento de grupo, acceden a las mismas secuencias de tipo SWA y SRA. Las secuencias de SCPS siguen formatos de secuencias de escritura/lectura compatibles con I2C, permaneciendo por lo tanto completamente compatibles con los dispositivos compatibles con I2C, y las variaciones observadas en el formato esperado no deben afectar a los dispositivos compatibles con I2C (asegurado por el siguiente cumplimiento con I2C UM10204). Las secuencias denominadas pueden describirse en general como en la Figura 2.

El módulo de extensión de banco de registros (registros de SCPS) es la segunda sección de módulo de extensión para diseños compatibles con I2C actuales. Las secuencias SWA/SRA acceden a registros asociados, denominados por la presente como registros de SCSP, para su correspondiente recuperación y actualización, algunos de los cuales se actualizan de una manera secuencial y se denominarán como punteros. Los punteros tienen un número reservado 00h. El tamaño por defecto de los registros de SCPS es 8 bits (opcionalmente se prevén tamaños de múltiples bytes opcionales para futura compatibilidad). Aunque no los registros mismos, un conjunto de PARÁMETROS DEFINIDOS POR EL USUARIO o UDP están asociados a los registros de SCPS. UDP hace referencia a todos los parámetros que son específicos de instrumento, tales como las posiciones de puntero de inicio por defecto y valores de registro (por ejemplo, el valor de replegio por defecto de un registro después de un RESETEO o la dirección de puntero de inicio preestablecida para instrucciones específicas).

Los registros obligatorios son:

- un REGISTRO DE INSTRUCCIÓN o INSTR, actualizado a través de secuencias de SWA, para almacenar la última instrucción introducida de SWA válida, y configurada para resetear al valor 8h00 por defecto, como una indicación de que no se ha recibido instrucción de SCPS válida o se ha solicitado una acción de RESETEO;

- un REGISTRO DE ESTADO o ESTADO, con el fin general de servir como un registro de control de instrumento que permite configuración de ajuste interno del instrumento, que se usa por instrucciones específicas para definir el "estado" de instrumento seleccionado para una acción específica, estando configurado dicho REGISTRO de ESTADO para almacenar el estado de acción actual de la instrucción, recuperándose dicho estado desde una biblioteca de estados definidos por el usuario opcional (que contiene UDP) o a través de bytes de datos de ciertas instrucciones;

- un REGISTRO de ESTADO o STATU, que es el registro de salida de LECTURA por defecto, es decir, cuando se recibe una secuencia de SRA por un grupo sin especificación del registro objetivo (permitido para ciertas instrucciones o si únicamente se envía secuencia de SWA de 2 bytes), estando dicho REGISTRO de ESTADO compuesto por defecto por una agrupación de banderas internas definidas, que reflejan el estado interno del módulo de SCPS;

- una DIRECCIÓN de GRUPO o GADDR, que puede estar en el formato 10GA o 8GA anteriormente mencionados, conteniendo tal registro la información de dirección de grupo del módulo y puede ser dinámico (es decir programable), donde la dirección 8h00 se reserva como una dirección NULA y no puede asignarse a ningún grupo;

- un registro de DIRECCIÓN de MIEMBRO o MADDR que contiene la información de la dirección de miembro del módulo, es decir la posición relativa del módulo en el grupo. El registro puede ser dinámico, donde se reserva la dirección 8h00 como una dirección NULA y no puede asignarse a ningún módulo;

- un registro de PUNTERO DE REGISTRO de ESCRITURA o WRP configurado para almacenar la dirección de registro objetivo a la que se va a escribir, actualizándose posiblemente dicho registro a través de ciertas instrucciones y especificadores de instrucciones, o extendiéndose una secuencia de escritura para ciertas instrucciones (es decir, como cuando se envían unos pulsos ACK y SCK adicionales después del primer byte de escritura de datos de una secuencia de escritura de I2C), donde se reserva el valor 8h00 como una dirección NULA y significa que no tendrá lugar acción al puntero durante esta secuencia de instrucciones, donde el valor inicial del puntero durante una instrucción específica se establece por UDP, si ninguno debiera ponerse por defecto a 00h, y donde todos los asuntos relacionados con el incremento y decremento del puntero se han de tratar por el usuario a través de interacción con la sección de registro de SCPS;

- un PUNTERO de REGISTRO de LECTURA o RRP que almacena la dirección de registro objetivo desde la que se va a leer, actualizándose posiblemente dicho registro a través de la utilización de ciertos comandos o extendiéndose a una secuencia de lectura (es decir, como cuando se envían pulsos de acuse de recibo y SCK adicionales después del primer byte leído de una secuencia de lectura de I2C), donde se reserva el valor 8h00 como una dirección NULA y significa que no tendrá lugar acción al puntero durante esta secuencia de instrucciones, donde el valor inicial del puntero durante una instrucción específica se establece por UDP, si ninguno debiera ponerse a por defecto a 00h, y donde todos los asuntos relacionados con el incremento y decremento del puntero se han de tratar por el usuario a través de interacción con la sección de registro de SCPS;

- un PUNTERO de ESCRITURA de GRUPO o GWP que almacena la dirección de miembro a la que se va a escribir, donde la coincidencia del GWP a la MADDR indica el módulo en el que ha de almacenarse el BYTE de DATOS en la dirección de WRP, donde la actualización de la GWP es específica de instrucción y su valor inicial depende de la instrucción y de UDP, donde ciertas instrucciones pueden auto incrementar el puntero en un estilo reflectante del puntero de registro de I2C (se deja al usuario en la norma de I2C), que se utiliza por la mayoría de los mecanismos compatibles con I2C para simplificar múltiples operaciones de lectura y escritura, donde el valor 8h00 se reserva como una dirección NULA y significa que no tendrá lugar acción en el puntero durante esta secuencia de instrucciones. La respuesta del módulo para un GWP 8h00 es equivalente a un escenario de NO coincidencia, donde el valor inicial del puntero durante una instrucción específica se establece por UDP, si ninguno debiera establecerse por defecto a 00h, y donde todos los asuntos relacionados con el incremento y decremento del puntero han de tratarse por el usuario a través de interacción con la sección de registro de SCPS; y

- un PUNTERO de LECTURA de GRUPO o GRP que almacena la dirección de miembro desde la que se ha de leer, donde la coincidencia del GRP a la MADDR indica que el BYTE de DATOS del registro de RRP del módulo es para servir como una SALIDA en la siguiente secuencia de LECTURA de I2C, donde ciertas instrucciones pueden auto incrementar el puntero en un estilo reflectante del puntero de registro de I2C (se deja al usuario en la norma de I2C), que se utiliza por la mayoría de los mecanismos compatibles con I2C para simplificar múltiples operaciones de lectura y escritura, donde el valor 8h00 se reserva como una dirección NULA y significa que no tendrá lugar acción en el puntero durante esta secuencia de instrucciones, donde el comportamiento del módulo para un GRP 8h00 es equivalente a un escenario de NO coincidencia, y donde tal registro puede incrementarse también ampliando una secuencia de lectura (es decir, como cuando se

envían pulsos de acuse de recibo y de SCK adicionales después del primer byte leído de una secuencia de lectura de I2C); sin embargo, como en I2C el incremento o decremento se deja al usuario.

Los registros opcionales son:

- un REGISTRO O REGISTROS de TESTIGO o TKR, que sirven como un espacio de testigo donde cada bit, o conjunto de bits, representa un testigo específico, que almacena la información de los recursos asociados que se han asignado a un módulo específico, donde en el caso de únicamente un recurso compartido (tal como un bus analógico) entonces la simplificación puede conseguirse mediante el uso de la bandera RQST; y

- unos REGISTROS DEFINIDOS POR EL USUARIO o UDR, que se refieren a todos los registros asociados al mismo instrumento/dispositivo y por lo tanto definidos por su diseñador, donde tales registros incluyen todos los registros accesibles por I2C de instrumento que se han definido por el usuario, donde si se pretende el acceso a través del módulo de SCPS por el usuario, entonces se espera la asignación en los registros de SCPS proporcionando recuperación y actualización direccionable a su localización definida por el usuario, y donde tales UDR son por definición no convencionales, permaneciendo por lo tanto la responsabilidad del diseñador para establecer los elementos necesarios y el flujo si se pretende para acciones de módulo cruzado.

El módulo de extensión de banco de elementos (manejador de SCPS) es un módulo de extensión opcional que puede estar integrado en el módulo de SCPS para servir como biblioteca de conmutación/elemento, en cuanto a gestionar la capacidad de control y capacidad de observación a través de conmutadores y la funcionalidad de otros elementos. Tales elementos pueden ser digitales o analógicos y su configuración es la responsabilidad del diseñador. El manejador de SCPS se ha de controlar principalmente a través del ESTADO, permitiendo preestablecer la configuración para gestionar la capacidad de enrutamiento y funcionalidad del instrumento. Un ejemplo de tal módulo de extensión sería un diccionario de encaminamiento conectado a las patillas de activación de conmutadores analógicos, que permite el acceso a un bus analógico. El diccionario traduciría a continuación un ESTADO a un esquema de conexión objetivo; adicionalmente, tal biblioteca podría activar también un mecanismo de auto-prueba integrado (BIST) u otro aspecto funcional del instrumento. Tal módulo de extensión es opcional, debido al uso directo de banderas y los registros de módulo de SCPS (accesibles internamente por el instrumento) pueden usarse directamente para los mismos fines para escenarios sencillos.

Los módulos de extensión anteriormente mencionados se ilustran y destacan en la Figura 3.

#### Descripción del flujo de trabajo

Existe flexibilidad con respecto al flujo de trabajo asociado de la implementación anteriormente descrita, sin embargo, la intención es la simplificación de acciones inter-modulares y gestión de eventos. Aunque, aparentemente complejo mientras se compara con la simplicidad de una estrategia de dos operaciones tal como la presentada por el I2C UM10204 (a través del uso de operación de escritura y lectura, ignorando operaciones especiales opcionales tales como SOLICITUD GENERAL, BYTE de INICIO, etc.), el conjunto de instrucciones de SCPS sigue un enfoque similar con su SWA y SRA, ampliando las capacidades funcionales de las operaciones de escritura y lectura de I2C convencionales.

El uso de una estructura de interfaz común entre instrumentos permite que las banderas, registros, punteros y respuestas funcionales asociados sirvan un papel de normalización que minimiza el conocimiento del mecanismo interno requerido para interconectar instrumentos que se pretende que se usen por múltiples módulos, reduciendo de esta manera la necesidad global de recursos (a través de la reutilización de instrumento) y de tara de comunicación (simplificando el esquema de comunicación). En las Figuras 4 a 6, existen algunos ejemplos de la operación de datos y flujo, en comparación con I2C, en cuanto a percibir mejor los beneficios de la compatibilidad de SCPS en el nivel de comunicación.

La estrategia de granularidad direccionalizada presentada permite lecturas de múltiples esclavos en una secuencia comprimida según se presenta en la Figura 4, que reduce significativamente la tara de comunicación cuando se compara con las secuencias de I2C convencionales.

La Figura 5 ilustra la representación genérica de la instrucción de SCPS secuenciada, en comparación con secuencias de escritura de I2C convencionales. Cabe señalar que las estrategias de difusión presentadas por otras soluciones permiten accesibilidad donde únicamente pueden conseguirse secuencias de bloques; que se diferencia del enfoque presentado que permite secuencias coordinadas y lecturas coordinadas de múltiples esclavos.

Finalmente, la Figura 6 presenta la representación genérica de secuencias de transferencia que claramente presenta la ventaja del enfoque presentado, puesto que las operaciones de lectura/escritura entre miembros esclavo pueden coordinarse sin la necesidad de lecturas y escrituras de datos secuenciales.

Desde un punto de vista más práctico, el módulo de SCPS permite no únicamente la ampliación funcional de las operaciones de I2C convencionales, a través de su conjunto de instrucciones, sino que cuando se asocia a un

manejador de SCPS, sirve para sincronizar y gestionar aspectos funcionales y de encaminamiento de los instrumentos también; introduciendo la noción de acciones de grupo.

#### Conjunto de instrucciones

- 5 Las instrucciones asociadas, que se introducen a través de SWA y se dividen en cuatro categorías: CONFIGURACIÓN, CAPTURA, PROCESO y EXPLORACIÓN (tales categorías están así denominadas debido a la metodología de estructura de SCPS, sin embargo, representan cuatro tipos de instrucciones distintos de manera independiente del esquema utilizado). Cada instrucción sigue actualizaciones específicas de las banderas 10 asociadas, registros y punteros, que se describen en esta sección de instrucción. Las SRA tienen respuestas específicas dependiendo de la instrucción válida actual (introducida por SWA) para permitir una simplificación de la transferencia de datos, se describe una descripción general del flujo de instrucciones y de datos en la sección de flujo de trabajo.

- 15 Pueden introducirse instrucciones futuras a través del uso del formato de instrucción de SCPS que no se ha de reservar para instrucciones obligatorias. Instrucciones opcionales pueden hacer uso también de las opciones libres en el dominio de instrucción, sin embargo no se puede esperar respuesta por los registros de SCPS, banderas y otros elementos. Es decir, la instrucción puede interpretarse directamente por el instrumento tras la examinación de 20 los datos de I2C en el registro. Conjuntos de instrucciones personalizados pueden por lo tanto formularse usando el espacio de dominio de instrucciones vacante, con actualizaciones particulares a los registros de SCPS, banderas y elementos; tales conjuntos de instrucciones, personalizados en naturaleza, tendrían que considerar su particularidad cuando se coordinan acciones inter-modulares. En todos los casos, la respuesta de instrumento específica no se define para ninguna SGI, SWA o SRA, de manera que se ha de especificar por el diseñador del instrumento 25 basándose en las banderas obligatorias y opcionales, registros y punteros, con el entendimiento del comportamiento normalizado a través de instrumentos compatibles con SCPS puede sincronizarse por lo tanto únicamente a través de coordinación inter-módulo.

- 30 Las instrucciones se describirán basándose en el tipo de dirección, ya sean globales (de una SOLICITUD GENERAL), de grupo o específicas. Aunque se denominó el direccionamiento específico en este escenario al acceso de un instrumento a través del uso de una dirección de 7 bits de I2C, también es posible seleccionar un miembro específico de un grupo para una acción aislada, que es de utilización cuando los miembros del grupo no tienen una dirección de 7 bits de I2C asociada a los mismos. Desde este punto de vista, tal estilo de direccionamiento se denominará como direccionamiento específico de miembro o MSAaddr, que conlleva una 35 subsección de las instrucciones permisibles.

- 35 El conjunto de instrucciones global se pretende para acciones que afectan a todos los módulos receptores de SCPS de manera simultánea (por ejemplo, una solicitud de RESETEO o de inicialización), aunque la respuesta de instrumento específica depende de las particularidades del diseño, por ejemplo, en el caso de una instrucción de RESETEO, no todos los instrumentos se espera que reseteen sus registros y elementos internos de la misma 40 manera (por ejemplo, el registro de SCPS se reseteará basándose en UDP específicos). Cuando el manejador de SCPS está presente y se están utilizando commutadores analógicos para configuraciones de encaminamiento de señal, alguna posible solicitud global puede ser OMITIR y AISLAR, que hacen referencia a transparencia de tiempo de operación y aislamiento de módulo de buses analógicos respectivamente. La instrucción global se introduce 45 después de una SOLICITUD GENERAL (todo ceros en el primer byte, es decir, 8h00), y usa el espacio de SOLICITUD GENERAL de software teniendo el bit menos significativo establecido a 'cero'. Para evitar entrar en conflicto con instrucciones establecidas de I2C UM10204, el bit más significativo se establece a 'uno'.

El conjunto de instrucciones global comprende las siguientes instrucciones:

- 50 - la instrucción ESTADO modifica el registro de estado para permitir que tenga lugar una acción general tal como configuración de RESETEO, AISLAMIENTO u OMISIÓN. La instrucción despeja los punteros y INSTR a 8h00, ESTADO se actualiza con el correspondiente UDP de instrucción asociada, que tiene el valor por defecto de 8h00. Las banderas internas se despejan y todas las banderas de TESTIGO se liberan, excepto una bandera global que se establece. Todos los módulos de SCPS receptores realizan ACK para tal instrucción. Pueden 55 seguir bytes adicionales; sin embargo, serán ignorados por el módulo de SCPS.

- la instrucción BLOQUEO establece los módulos de SCPS en el correspondiente nivel de BLOQUEO. Por BLOQUEO se pretende diferentes niveles de limitación funcional del módulo de SCPS para proporcionar un mecanismo para limitar las acciones de un miembro de grupo o miembros (tal como en el caso de funcionamiento incorrecto o fallo detectado), donde el BLOQUEO de nivel 0 significa: no bloqueo, todas las 60 instrucciones y operaciones están permitidas.

Debería observarse que las instrucciones de BLOQUEO no afectan a los registros o banderas excepto para aquellas específicas a instrucciones de BLOQUEO, por lo que debe tenerse cuidado. Pueden introducirse niveles adicionales usando el espacio restante en el dominio de instrucción.

- 65 Todos los módulos de SCPS receptores realizan ACK a tal instrucción. Pueden seguir bytes adicionales, sin embargo serán ignorados por el módulo de SCPS.

- la instrucción de SOLICITUD tiene el fin de que múltiples maestros puedan coordinar el uso de recursos compartidos a través de verificación de disponibilidad. La secuencia de instrucción de SOLICITUD se diferencia de los dos tipos anteriores, puesto que únicamente los miembros que tienen el TESTIGO asignado asociado a ellos producen un ACK (asignado a los mismos de una solicitud anterior), si no se recibe ACK el MAESTRO continúa con un segundo byte con el resto de la dirección de grupo de 10 bits (en caso de 10GA que usa YY para los primeros dos MSB) o el 8GA (en este caso el YY se vuelve sin importancia). El grupo especificado a continuación establece su bandera RQST y correspondiente TKR.

5 El conjunto de instrucciones de grupo se pretende para acciones inter-módulo y para acciones específicas de 10 miembro también (la MSAaddr denominada anteriormente). La INSTRUCCIÓN se introduce en el tercer byte de una SWA.

15 El byte de INSTRUCCIÓN indica el tipo de instrucción, en caso de una instrucción formada incorrectamente debería ignorarse por el módulo de SCPS. En un caso de este tipo la bandera de GRUPO permanecería establecida como en el caso de una SWA de dos bytes, usada en general para preceder una SRA. Si la instrucción corresponde a una 20 instrucción específica de miembro, el cuarto byte se supondría que es la dirección de miembro y cualquier byte de datos después de ese se asociaría a especificadores de instrucción. Las instrucciones no basadas en especificadores están relacionadas con estrategias preestablecidas basadas en UDP, y utilizadas para simplificación de acciones repetitivas y evitar instrucciones y repeticiones largas y complejas. Cualquier byte de datos adicional 25 después del byte de INSTRUCCIÓN para una instrucción no de especificadores se ignoraría por el módulo de SCPS. Los bytes de INSTRUCCIÓN adicionales pueden considerarse para ampliar de manera significativa el dominio de comando. Sigue una descripción del conjunto de instrucciones de grupo por tipo.

30 El conjunto de instrucciones de configuración o SIS, es el reflejo de las operaciones pretendidas para escribir o actualizar los registros de los módulos implicados. Esto puede hacerse a través del uso de ESTADOS dependientes de UDP preestablecidos o a través de ESCRITURA directa de un registro o registros. Adicionalmente, proporciona los estados de LIBERACIÓN o BLOQUEO o de recursos compartidos (limpiando el bit específico de registro de testigo). Los módulos implicados realizan ACK al byte de INSTRUCCIÓN; sin embargo en el caso de instrucciones 35 específicas de miembro, únicamente el miembro objetivo realizará ACK a su MADDR y especificadores.

35 El conjunto de instrucciones de configuración comprende las siguientes instrucciones:

- la instrucción de RESETEO limpia los punteros, banderas y restaura registros a su valor por defecto (8h00 por defecto si no hay UDP). Únicamente la bandera GRP permanece establecida para permitir una SRA de continuación.

- la instrucción de ESTADO actualiza el registro de estado y el registro de INSTR, las únicas banderas actualizadas son la bandera de GRUPO que identifica si es una instrucción dirigida específica de grupo o de miembro. Se pretende que sirvan para acceso de configuración preestablecido a través de UDP.

- ESCRITURA: estas instrucciones se usan para dirigir la escritura de registro a través del uso de la dirección de registro como un especificador, de la misma manera que se escribiría a un registro asociado con I2C, la diferencia radica en que para instrucciones de grupo, la ESCRITURA tiene lugar en múltiples módulos, permitiendo la actualización de múltiples módulos de manera simultánea. La estrategia para auto incrementar o reducir la dirección de registro (de una manera consistente con la mayoría de los dispositivos compatibles con I2C) se deja al diseñador como se ha establecido anteriormente (manteniéndose acorde con I2C UM10204).

- BLOQUEO: permite el cambio del nivel de BLOQUEO del módulo (información almacenada en las banderas de BLOQUEO). Los niveles de BLOQUEO siguen el mismo comportamiento que la instrucción de BLOQUEO GLOBAL.

- LIBERACIÓN DE RQST: permite la liberación de un recurso compartido específico, a través de la liberación de los bits de TESTIGO del soporte de grupo y la bandera de RQST, que también es conseguible a través del uso de un RESETEO o ESTADO GLOBAL.

55 El conjunto de instrucciones de captura o CIS, es el reflejo de las operaciones pretendidas para sincronizar acciones inter-módulo que tienen dependencia entre módulos, por ejemplo, mediciones sincronizadas desde múltiples módulos o una medición que requiere que participen múltiples módulos. Esto puede hacerse a través del uso de ESTADOS dependientes de UDP preestablecidos o a través de configuraciones "al vuelo" a través del uso de 60 especificadores.

Las instrucciones se subdividen en dos tipos: en espera (STBY) y captura (CAPT). Dependiendo del módulo y la respuesta de instrumento las dos instrucciones podrían servir funciones idénticas, se diferencian principalmente en el ajuste de bandera y en su fin conceptual. La instrucción STBY se pretende para acciones que requieren un periodo de espera, por ejemplo, un periodo de ajuste para un estímulo para permitir una medición apropiada. La instrucción CAPT se pretende que indique el inicio de una medición o ensayo (siguiendo posiblemente un STBY).

Adicionalmente, se ha incluido una instrucción FIN-CAPT para señalizar un fin del evento de captura, útil en casos donde el evento de captura no es instantáneo y requiere una interrupción intencionada del proceso. Los módulos implicados realizan ACK al byte de INSTRUCCIÓN; sin embargo en el caso de instrucciones específicas de miembro, únicamente el miembro objetivo realizará ACK a su MADDR y especificadores. La limpieza de las banderas relacionadas con STBY y CAPT únicamente tiene lugar después de una instrucción de estilo FIN-CAPT o un RESETEO (permite acciones de configuración, proceso y exploración en paralelo).

El conjunto de instrucciones de captura comprende las siguientes instrucciones:

- 10 - STBY: la instrucción puede incluir o no especificadores, utilizando por lo tanto el UDP por defecto para el último caso. Una instrucción Nxt-STBY actualiza el registro de estado para permitir acceso a configuraciones de STBY secuenciales (por ejemplo, para modificar el encaminamiento para una serie de sensores para permitir mediciones secuenciales de sus elementos o realizar una medición de múltiples etapas como en el caso de un barrido de frecuencia). La instrucción STBY con especificadores puede diferenciarse del formato de instrucción normal no teniendo longitud preestablecida, y únicamente el miembro pertinente realizará ACK después de su MADDR y el siguiente byte de DATOS. Es decir, todos los miembros leen los bytes de datos entrantes en grupos de dos, representando el 1<sup>er</sup> byte la MADDR, y el 2<sup>o</sup> byte el especificador.

- 15 - CAPT: la instrucción puede incluir o no especificadores. Si no sigue ningún especificador que una configuración haya establecido previamente a través de una instrucción STBY. También es posible usar la instrucción CAPT sin un STBY anterior en casos donde no se requiera configuración. Como se ha descrito anteriormente, una FIN-CAPT permite finalizar la acción de captura. De manera similar a la STBY las instrucciones CAPT pueden permitir configuración y captura “al vuelo”, siendo diferente que las banderas de CAPT que se establecen para indicar el inicio de la acción de captura en lugar de la bandera STBY.

25 El conjunto de instrucciones de proceso o PrIS, es el reflejo de las operaciones pretendidas para sincronizar acciones inter-módulo que no tienen dependencia inter-módulo directa, por ejemplo, operaciones de módulo internas sincronizadas para múltiples módulos o el procesamiento de un estado de FALLO por los módulos implicados (para permitir el estado de FALLO global de un grupo). Esto puede hacerse a través del uso de ESTADOS dependientes de UDP preestablecidos o a través del uso de especificadores, ambos a un nivel de grupo o específico de miembro; por ejemplo, las instrucciones de proceso pueden seguir una captura satisfactoria para actualizar apropiadamente las banderas de FALLO; sin embargo, no se hace restricción del uso de secuencia de instrucción.

30 El conjunto de instrucciones de proceso comprende las siguientes instrucciones:

- 35 - PSET: la instrucción tiene varias versiones, con o sin especificadores y a nivel específico de grupo y de miembro. Es similar a CAPT en comportamiento aunque actualizando las banderas FALLO y PROC en lugar de las banderas de CAPT. Las banderas de FALLO se actualizan directamente por el instrumento y se pretende que sirvan como un indicador de estado de FALLO, sin embargo los detalles y uso se dejan al diseñador del instrumento. Adicionalmente, el PrIS no actualiza el registro de estado, por lo tanto podría tener lugar una operación de captura y proceso en paralelo. En caso de que las banderas de FALLO o la determinación de estado de FALLO interna del instrumento requiera una acción que afecte el “estado” del módulo, puede realizarse una omisión de registro de ESTADO a un UDP específico de respuesta, fuera del intérprete de SCSP (en el mismo instrumento o interceptando la ruta de manejador del intérprete de SCSP a SCPS). Si se requiere, pueden estar opcionalmente disponibles patillas de BLOQUEO externas para forzar un estado de BLOQUEO a través de hardware externo. Debería mencionarse que la acción de proceso puede realizarse a nivel de ESTADO, así como utilizar las banderas de SCPS para inicializar acciones de proceso únicamente en los módulos de interés, por ejemplo, actualizar el estado de FALLO del módulo que es un objetivo de prueba mientras está en un proceso STBY.

40 El conjunto de instrucciones de exploración o ScIS, es el reflejo de operaciones pretendidas para leer o transferir (leer desde y escribir en) registros de los módulos implicados. Esto puede hacerse a través del uso de UDP preestablecidos o el uso de especificadores. Los módulos implicados realizan ACK al byte de INSTRUCCIÓN; sin embargo en el caso de instrucciones específicas de miembro, únicamente el miembro objetivo realizará ACK a su MADDR y especificadores.

45 El conjunto de instrucciones de exploración comprende las siguientes instrucciones:

- 50 - LECTURA: la instrucción de lectura permite que se lea un registro desde múltiples módulos o un módulo específico de miembro a través del bus de I2C común. Se diferencia de estrategias de I2C convencionales en que simplifica la operación de lectura a través del bit de R/W en el primer byte de la transacción, permitiendo selección de registro a través de la última operación de lectura. En este caso, la variación permite la cadena leída desde múltiples módulos, reduciendo significativamente los bytes de transacción puesto que no deben realizarse instrucciones de lectura y escritura de ida y vuelta. Esto se consigue usando los punteros para determinar el módulo objetivo y registro objetivo desde los que se va a leer; sin embargo, en lugar de la modificación de incremento o decremento al registro objetivo como en estrategias de I2C convencionales en este punto el módulo

5 objetivo puede actualizarse permitiendo que una instrucción de LECTURA contenga información encadenada desde múltiples módulos. Como alternativa una LECTURA puede usar UDP para leer registros preestablecidos e incluso cambiar el módulo desde el que se está leyendo, puesto que el incremento o decremento de los módulos se deja al diseñador. La instrucción de LECTURA con especificadores permite la selección del registro objetivo desde el que leerse, mientras que el N° de REG adicional permite controlar el número de incrementos por módulo que se leerán.

- 10 - TRNF: la instrucción de transferencia permite que se lea un registro desde un módulo y se escriba en una localización o módulo diferente o (dependiendo del UDP). Se diferencia de estrategias de I2C convencionales que únicamente consideran operación maestro-esclavo y no transferencia de datos de esclavo a esclavo. Como con la LECTURA, la TRNF permite transferencias preestablecidas. La variación del especificador permite la elección del módulo de origen y de destino. Durante una transferencia el ACK de 9 bits se controla por una tercera parte maestra para evitar los módulos de RX y TX a los mismos ACK, impidiendo por lo tanto un re-inicio de evento de parada, y bloqueando el bus de I2C común. Si uno de los módulos implicados está sirviendo como el maestro, entonces debería seguirse el comportamiento de ACK apropiado para evitar ciclos infinitos.

15 Las operaciones de SRA por defecto leen el registro de estado desde los módulos en un grupo, en el orden determinado por el UDP; sin embargo, la actualización de los punteros se deja al diseñador (como se ha establecido anteriormente) por lo que la información desde las banderas SCPS y el registro de ESTADO pueden usarse para permitir lecturas definidas por el usuario, que se denominan como lecturas rápidas. Esto se permite de manera deliberada, y puede ampliarse para permitir operaciones de transferencia también (los punteros de escritura no necesitan establecerse a 8h00 tras el inicio de un SRA, aunque es un valor por defecto), que se denominan como transferencias rápidas. Un ejemplo de una transferencia rápida útil es cuando un módulo es responsable de la digitalización de una medición (contiene un ADC, por ejemplo), sin embargo los datos necesitan asignarse en un módulo diferente (el objetivo de la medición, por ejemplo), de esta manera una transferencia rápida permite mantener elementos en un STBY, transferir los datos y continuar con una medición diferente (a través de una instrucción STBY- SIGUIENTE o CAPT).

#### 30 Otras realizaciones

35 En algunas realizaciones, el módulo de SCPS supone que dispositivos no compatibles con SCPS conectados al bus I2C compartido son compatibles con la norma UM10204 I2C.

40 En algunas realizaciones, todas las consideraciones eléctricas y de temporización son la responsabilidad del diseñador de CI y deberían cumplir con la norma UM10204 I2C y cualquier norma adicional que se aplique.

45 En algunas realizaciones, en el caso de usar un formato de dirección de I2C de 10 bits para la identificación de los grupos de sistemas, se supone que la dirección es única en el sistema y no coincide con dispositivos no compatibles con SCPS conectados al bus I2C compartido.

50 En algunas realizaciones, en el caso de usar un formato de dirección de I2C de 8 bits para la identificación del grupo de sistemas, se supone que el uso de la dirección de 7 bits reservada del protocolo alternativo no entrará en conflicto con protocolos alternativos adicionales conectados al bus I2C compartido, es decir los únicos dispositivos que responderán a la dirección de protocolo alternativa son compatibles con SCPS.

55 En algunas realizaciones, características de I2C opcionales tales como arbitración, compresión de reloj, etc., son la responsabilidad del diseñador de CI y deberían implementarse de tal manera que no entren en conflicto con operaciones de SCPS.

60 En algunas realizaciones, el intérprete de I2C se implementa de tal manera que proporciona al módulo de SCPS con suficiente capacidad de control y capacidad de observación de las líneas de SDA y SCK.

65 En algunas realizaciones, los registros asociados al intérprete de I2C (aquellos accesibles a través de secuencias de I2C) cuando se consideran en el registro de SCPS deben ser accesibles directamente para el módulo de SCPS.

En algunas realizaciones, los registros y parámetros definidos por el usuario están formateados apropiadamente.

En algunas realizaciones, la respuesta de CI a operaciones de SCPS es la única responsabilidad del diseñador.

En algunas realizaciones, cualquier conflicto de encaminamiento que pueda tener lugar debido a configuración imprevista aplicada a través del módulo de SCPS es la única responsabilidad del diseñador del sistema.

En algunas realizaciones, cuando se usa el módulo de SCPS para estrategias de testigo, se supone que los módulos implicados verificarán la disponibilidad del recurso antes del uso y su responsabilidad del diseñador para implementar cualesquier salvaguardas relacionadas.

En algunas realizaciones, las salvaguardas relacionadas con la seguridad de sistema y/o usuario son la responsabilidad del diseñador de sistema.

5 En algunas realizaciones, la coordinación de acción inter-módulo supone un entendimiento o definición de tiempo de operación preestablecida de respuestas, entre los diseñadores de los instrumentos implicados.

En algunas realizaciones, las consideraciones eléctricas y de temporización que puede necesitarse considerar durante operaciones inter módulo son la responsabilidad del diseñador de sistema.

10 En algunas realizaciones, el módulo de SCPS, las operaciones y estructura se pretenden para facilitar operaciones, mediciones y pruebas de datos inter módulo e intra módulo; sin embargo, las acciones específicas de los instrumentos implicados son la responsabilidad del diseñador, incluyendo consideraciones eléctricas y de temporización. Cualquier daño o perjuicio que pudiera tener lugar mientras se tienen los módulos de SCPS implementados es por lo tanto la responsabilidad del diseñador.

15

**REIVINDICACIONES**

1. Un módulo, designado por la presente como Configuración, Captura, Proceso y Exploración, definido posteriormente como módulo de SCPS, que comprende:

- un submódulo de intérprete; y

- un módulo de banco de registros que comprende:

- un registro de instrucción para almacenar la última instrucción válida;

- un registro de estado para almacenar el estado de acción actual de la instrucción;

- un registro de estado para almacenar el estado interno de dicho módulo de SCPS;

- un registro de dirección de grupo para almacenar la dirección de grupo de dicho módulo de SCPS;

- un registro de dirección de miembro para almacenar la dirección específica en el grupo de dicho módulo de SCPS;

- un registro de puntero de registro de escritura para almacenar la dirección de registro objetivo en la que se va a escribir;

- un registro de puntero de registro de lectura para almacenar la dirección de registro objetivo desde la que se va a leer;

- un registro de puntero de escritura de grupo para almacenar la dirección de miembro en la que se va a escribir;

- un registro de puntero de lectura de grupo para almacenar la dirección de registro objetivo desde la que se va a leer;

- al menos un registro de testigo para almacenar un espacio de testigo de los recursos asociados que se han asignado a dicho módulo de SCPS;

en el que el submódulo intérprete está configurado para recibir y responder a secuencias de I2C, complementado con secuencias de SCPS, en la recepción de una instrucción precedida por cualquiera de:

- una dirección de I2C;

- una dirección de SCPS global que comprende una solicitud de dirección global de I2C seguida por una instrucción global de SCPS, definida posteriormente como SGI;

- una dirección de SCPS de grupo que comprende una dirección de I2C de 10 bits seguida por una dirección de SCPS de grupo de 8 bits y por una instrucción de grupo; o

- una dirección de SCPS específica de miembro que comprende una dirección de SCPS de grupo, seguida por una dirección de miembro y una instrucción específica de miembro.

2. El módulo de acuerdo con la reivindicación anterior, en el que el módulo de banco de registros comprende al menos un registro definido por el usuario.

3. El módulo de acuerdo con cualquiera de las reivindicaciones anteriores, que comprende un submódulo de manejador de SCPS adicional del banco de elementos para servir como biblioteca de elementos de conmutación.

4. El módulo de acuerdo con cualquiera de las reivindicaciones anteriores, en el que la instrucción global de SCPS, en lo sucesivo denominada como SGI, comprende:

- una instrucción de estado;

- una instrucción de bloqueo; o

- una instrucción de solicitud.

5. El módulo de acuerdo con cualquiera de las reivindicaciones anteriores, en el que la instrucción específica de grupo o de miembro comprende:

- un conjunto de instrucciones de configuración;

- un conjunto de instrucciones de captura;

- un conjunto de instrucciones de proceso;

- un conjunto de instrucciones de exploración.

6. Un dispositivo, que comprende el módulo de SCPS descrito en cualquiera de las reivindicaciones 1 a 5.

7. Un bus de señal mixta, que comprende al menos uno del dispositivo, y una conexión al mismo, descrito en la reivindicación anterior que se considera como un recurso compartido.

8. Método de operación de un módulo de SPCS de acuerdo con cualquiera de las reivindicaciones anteriores, que comprende las etapas:

- almacenar la última instrucción introducida válida, en el registro de instrucción;

- almacenar el estado de acción actual de la instrucción, en el registro de estado;

- almacenar el estado interno del módulo de SCPS, en el registro de estado;

- almacenar la dirección de grupo del módulo actual, en el registro de dirección de grupo;

- almacenar la dirección específica del módulo en el grupo del módulo actual, en el registro de dirección de miembro;

- almacenar la dirección de registro objetivo en la que se va a escribir, en el registro de puntero de registro de escritura;

- almacenar la dirección de registro objetivo desde la que se va a leer, en el registro de puntero de registro de lectura;

- almacenar la dirección de miembro en la que se va a escribir, en el registro de puntero de escritura de grupo;

- almacenar la dirección de miembro desde la que se va a leer, en el registro de puntero de lectura de grupo.

- almacenar un espacio de testigo de los recursos asociados que se ha asignado a un módulo específico, en el al menos un registro de testigo,

- 5 en el que cada uno de los bits del registro de testigo representa un testigo específico para un recurso compartido específico.

9. Método de acuerdo con cualquiera de las reivindicaciones 8 a 9, que comprende la etapa:

- el submódulo de manejador de SCPS adicional del banco de elementos conmutando la capacidad de encaminamiento y funcionalidades de dispositivos direccionados.

10. Método de acuerdo con cualquiera de las reivindicaciones 8 a 10, que comprende las etapas:

- ejecutar una instrucción de estado modificando el registro de estado, limpiando los registros de puntero, banderas internas y registro de testigo, si están presentes, excepto una bandera global si está presente;

- 15 - ejecutar una instrucción de bloqueo estableciendo un nivel de bloqueo para el módulo de SCPS;

- ejecutar una instrucción de solicitud coordinando el uso de recursos compartidos a través de la verificación de disponibilidad.

11. Método de acuerdo con cualquiera de las reivindicaciones 8 a 11, que comprende las etapas:

- 20 - ejecutar una instrucción de configuración limpiando punteros, banderas o registros, escribiendo o actualizando registros, bloqueando o liberando recursos de registro de testigo;

- ejecutar una instrucción de captura inicializando múltiples configuraciones secuenciales de etapa, accediendo de manera directa a configuraciones pre-dispuestas, enviando parámetros de configuración, iniciando una captura o finalizando una captura;

- 25 - ejecutar una instrucción de proceso sincronizando acciones inter-modulo que no tienen dependencia inter-módulo directa, a través de la utilización de ESTADOS dependientes preestablecidos o a través de la utilización de especificadores, tanto a un nivel de grupo o específicos de miembro;

- ejecutar una instrucción de exploración leyendo o transfiriendo desde registros de los módulos direccionados.

- 30 12. El módulo de acuerdo con cualquiera de las reivindicaciones 1 a 5, en el que dicho módulo está configurado para implementar el método descrito en cualquiera de las reivindicaciones 8 a 11.

Fig. 1

# ES 2 694 168 T3

## ○ SWA:

## ○ SRA:

Fig. 2

Fig. 3

**Fig. 4**

Fig. 5

Fig. 6