# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 694 554

(51) Int. Cl.:

**G06F 13/42** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 24.04.2015 PCT/US2015/027479

(87) Fecha y número de publicación internacional: 05.11.2015 WO15167954

(96) Fecha de presentación y número de la solicitud europea: 24.04.2015 E 15724811 (3)

(97) Fecha y número de publicación de la concesión europea: 22.08.2018 EP 3138015

(54) Título: Bus global de sensores

(30) Prioridad:

28.04.2014 US 201461985276 P 23.04.2015 US 201514694618

Fecha de publicación y mención en BOPI de la traducción de la patente: 21.12.2018

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121-1714, US

(72) Inventor/es:

PITIGOI-ARON, RADU; WIETFELDT, RICHARD DOMINIC Y HOFFMAN, DOUGLAS WAYNE

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

## **DESCRIPCIÓN**

Bus global de sensores

#### 5 CAMPO TÉCNICO

[0001] La presente divulgación se refiere en general a una interfaz entre un procesador central y un dispositivo periférico y, más particularmente, a una interfaz de conexión de sensores.

#### 10 ANTECEDENTES

15

20

25

30

35

40

60

65

[0002] El documento WO0042740 describe un procedimiento y un sistema para el intercalado de interfaces. Los fabricantes de dispositivos móviles, como los teléfonos celulares, pueden obtener componentes de los dispositivos móviles de diversas fuentes, incluidos diferentes fabricantes. Por ejemplo, un procesador de aplicaciones en un dispositivo informático móvil puede obtenerse de un primer fabricante, mientras que los sensores empleados por el dispositivo informático móvil pueden obtenerse de uno o más fabricantes. Se han definido varias interfaces basadas en normas o patentadas para interconectar dispositivos de circuitos integrados (CI) en dispositivos móviles y otros aparatos, y estas interfaces en general se dirigen a una aplicación o tipo de aplicación específico. Por ejemplo, los teléfonos celulares pueden usar una interfaz de comunicaciones que sea compatible con o cumpla con una norma de interfaz en serie de cámara especificada por Mobile Industry Processor Interface Alliance (MIPI).

[0003] Las interfaces convencionales optimizadas para una aplicación específica pueden no ser adecuadas para su uso en otras aplicaciones. Por ejemplo, las normas MIPI definen una interfaz de control de cámara (CCI) que utiliza una interfaz en serie de dos cables, bidireccional, semidúplex configurada como un bus que conecta un dispositivo principal y uno o más dispositivos secundarios. CCI está optimizado para manejar los requisitos de comunicaciones de datos asociados con las pantallas, cuyos requisitos en general están más allá de las capacidades del bus de Circuito Inter-Integrado (I2C), que se usa ampliamente para una variedad de diferentes tipos de dispositivos. La señalización y los protocolos CCI pueden ser compatibles con los dispositivos que emplean el bus I2C para comunicarse utilizando los protocolos CCI. Es decir, el protocolo CCI utiliza las líneas de Reloj Serie I2C (SCL) y Datos Serie (SDA), y los dispositivos CCI y los dispositivos I2C pueden implementarse en el mismo bus, de modo que dos o más dispositivos CCI pueden comunicarse utilizando protocolos CCI, mientras que cualquier comunicación que involucra un bus I2C utiliza protocolos I2C.

[0004] Las versiones posteriores de CCI pueden proporcionar mayores rendimientos utilizando protocolos modificados para soportar velocidades de señalización más rápidas. En un ejemplo, se puede usar un bus de extensión CCI (CCIe) para proporcionar velocidades de datos más altas para dispositivos que son compatibles con las operaciones del bus CCIe. Dichos dispositivos pueden denominarse dispositivos CCIe, y los dispositivos CCIe pueden alcanzar velocidades de datos más altas cuando se comunican entre sí mediante la codificación de datos como símbolos transmitidos tanto en la línea SCL como en la línea SDA de un bus CCI convencional. Los dispositivos CCIe y los dispositivos I2C pueden coexistir en el mismo bus CCIe, de manera que una pluralidad de dispositivos pueden intercambiar datos utilizando la codificación CCIe, mientras que los intercambios de datos que involucran dispositivos I2C heredados pueden transmitirse de acuerdo con las convenciones de señalización I2C.

[0005] Existe una necesidad continua de proporcionar comunicaciones optimizadas en las interfaces en serie configuradas como un bus de conexión de diferentes tipos de periféricos o dispositivos de cooperación a un procesador.

#### **SUMARIO**

[0006] Los modos de realización divulgados en el presente documento, cuyas características se exponen en las reivindicaciones adjuntas, proporcionan sistemas, procedimientos y aparatos que pueden mejorar el rendimiento de un bus en serie que acople dispositivos configurados para comunicarse a través del bus en serie utilizando diferentes protocolos y/o esquemas de señalización. La siguiente divulgación expone aspectos ilustrativos de los modos de realización y aspectos ilustrativos de sistemas, procedimientos y aparatos relacionados para facilitar la comprensión de los modos de realización. En un aspecto de la divulgación, se proporcionan un procedimiento, un dispositivo de almacenamiento legible por ordenador y un aparato.

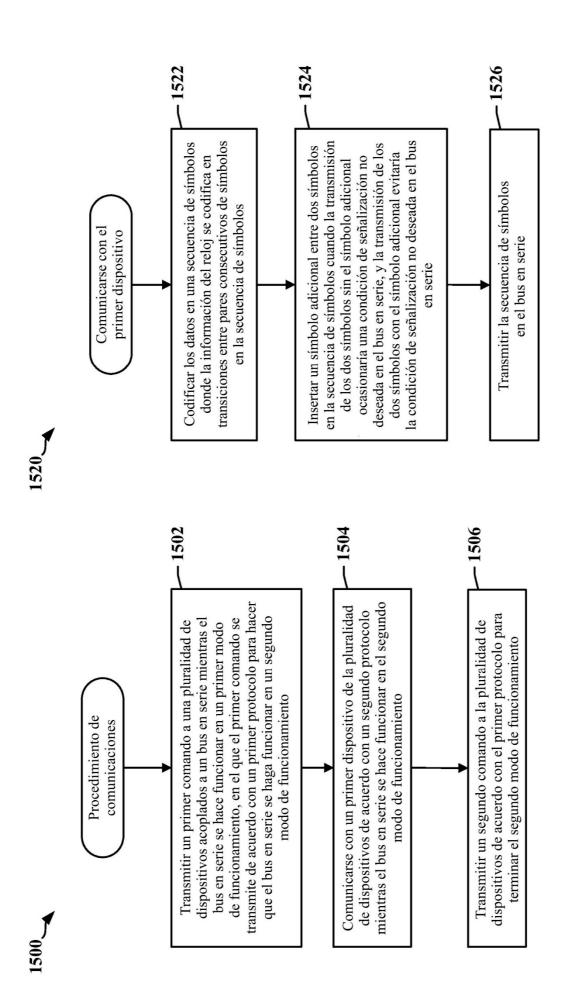

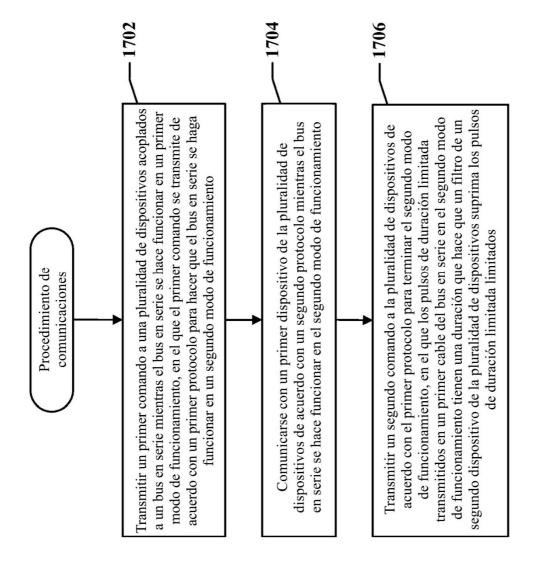

[0007] En un aspecto de la divulgación, un procedimiento de comunicaciones de datos incluye la transmisión de un primer comando a una pluralidad de dispositivos acoplados a un bus en serie, mientras que el bus en serie se hace funcionar en un primer modo de funcionamiento, en el que el primer comando se transmite de acuerdo con un primer protocolo para hacer que el bus en serie se haga funcionar en un segundo modo de funcionamiento, comunicándose con un primer dispositivo de la pluralidad de dispositivos de acuerdo con un segundo protocolo mientras que el bus en serie se hace funcionar en el segundo modo de funcionamiento, y transmitir un segundo comando a la pluralidad de dispositivos de acuerdo con el primer protocolo para terminar el segundo modo de funcionamiento. La comunicación con el primer dispositivo puede incluir datos de codificación en una secuencia de símbolos donde la información del reloj se codifica en transiciones entre pares consecutivos de símbolos en la secuencia de símbolos, insertando un

símbolo adicional entre dos símbolos en la secuencia de símbolos cuando la transmisión de los dos símbolos sin el símbolo adicional ocasionaría una condición de señalización no deseada en el bus en serie, y la transmisión de los dos símbolos con el símbolo adicional evitaría la condición de señalización no deseada en el bus en serie, y la transmisión de la secuencia de símbolos en el bus en serie.

[0008] En un aspecto de la divulgación, un aparato para la comunicación de datos incluye un transceptor que acopla el aparato a un bus en serie, y un circuito de procesamiento. El circuito de procesamiento puede configurarse para transmitir un primer comando a una pluralidad de dispositivos acoplados a un bus en serie mientras el bus en serie se hace funcionar en un primer modo de funcionamiento. El primer comando puede transmitirse de acuerdo con un primer protocolo para hacer que el bus en serie se haga funcionar en un segundo modo de funcionamiento. El circuito de procesamiento puede configurarse para codificar datos en una secuencia de símbolos de acuerdo con un segundo protocolo, donde la información del reloj se codifica en transiciones entre pares consecutivos de símbolos en la secuencia de símbolos. El circuito de procesamiento puede configurarse para insertar un símbolo adicional entre dos símbolos en la secuencia de símbolos cuando la transmisión de los dos símbolos sin el símbolo adicional ocasionaría una condición de señalización no deseada en el bus en serie, y la transmisión de los dos símbolos con el símbolo adicional evitaría la condición de señalización no deseada en el bus en serie. El circuito de procesamiento puede configurarse para transmitir la secuencia de símbolos en el bus en serie de acuerdo con el segundo protocolo, y transmitir un segundo comando a la pluralidad de dispositivos de acuerdo con el primer protocolo para terminar el segundo modo de funcionamiento.

[0009] En un aspecto de la divulgación, un procedimiento realizado en una interfaz de comunicación de datos incluye la transmisión de un primer comando a una pluralidad de dispositivos acoplados a un bus en serie, mientras que el bus en serie se hace funcionar en un primer modo de funcionamiento donde el primer comando es transmitido de acuerdo con un primer protocolo para hacer que el bus en serie se haga funcionar en un segundo modo de funcionamiento, la comunicación con un primer dispositivo de la pluralidad de dispositivos de acuerdo con un segundo protocolo mientras que el bus en serie se hace funcionar en el segundo modo de funcionamiento, y la transmisión de un segundo comando a la pluralidad de dispositivos de acuerdo con el primer protocolo para terminar el segundo modo de funcionamiento. Los pulsos de duración limitada transmitidos en un primer cable del bus en serie en el segundo modo de funcionamiento pueden tener una duración que hace que un filtro de un segundo dispositivo de la pluralidad de dispositivos suprima los pulsos de duración limitada.

[0010] En un aspecto de la divulgación, un aparato incluye medios para transmitir un primer comando a una pluralidad de dispositivos acoplados a un bus en serie, mientras que el bus en serie se hace funcionar en un primer modo de funcionamiento, donde el primer comando se transmite de acuerdo con un primer protocolo para hacer que el bus en serie se haga funcionar en un segundo modo de funcionamiento, medios para comunicarse de acuerdo con un segundo protocolo con un primer dispositivo de la pluralidad de dispositivos mientras el bus en serie se hace funcionar en el segundo modo de funcionamiento, y medios para transmitir un segundo comando a la pluralidad de dispositivos de acuerdo con el primer protocolo para terminar el segundo modo de funcionamiento. Los pulsos de duración limitada transmitidos en un primer cable del bus en serie en el segundo modo de funcionamiento pueden tener una duración que hace que un filtro de un segundo dispositivo de la pluralidad de dispositivos suprima los pulsos de duración limitada.

## **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

## 45 **[0011]**

5

10

15

20

25

30

35

40

- La FIG. 1 representa un aparato que emplea un enlace de datos entre dispositivos de CI, que funciona selectivamente de acuerdo con una entre una pluralidad de normas disponibles.

- La FIG. 2 ilustra una arquitectura de sistema para un aparato que emplea un enlace de datos entre dispositivos de CI.

- La FIG. 3 ilustra un transmisor y un receptor de acuerdo con ciertos aspectos divulgados en el presente documento.

- La FIG. 4 ilustra un primer ejemplo de un esquema de codificación de acuerdo con ciertos aspectos divulgados en el presente documento.

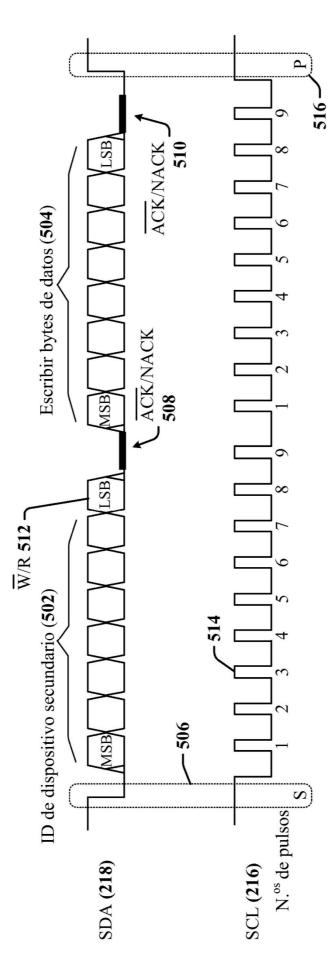

- La FIG. 5 ilustra un diagrama de temporización de una operación de datos de escritura de un byte I2C.

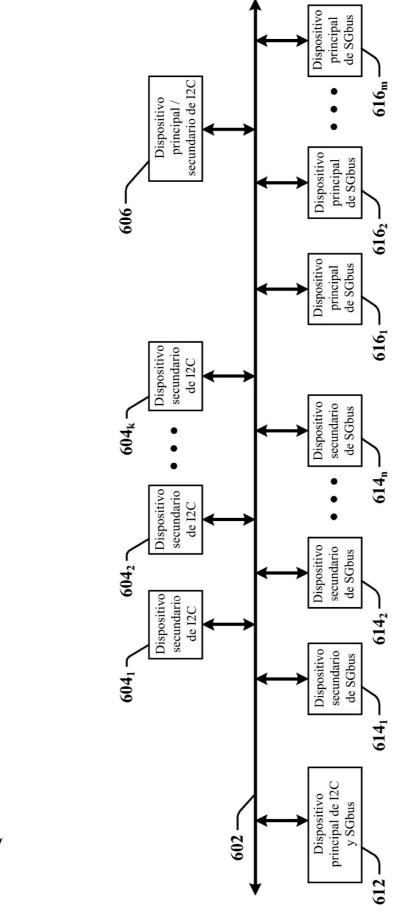

- 60 La FIG. 6 ilustra una configuración de dispositivos I2C y dispositivos de bus global de sensores (SGbus) conectados a un bus en serie común.

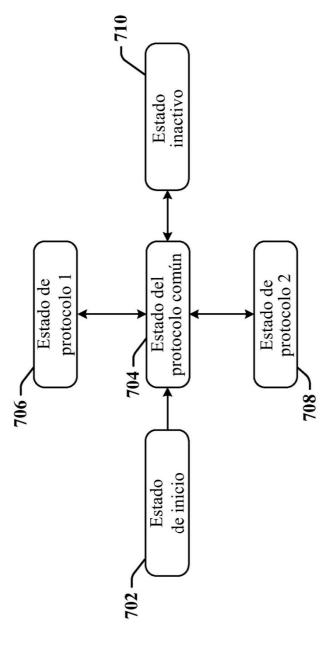

- La FIG. 7 ilustra un esquema generalizado para la transición entre los modos de funcionamiento de un bus en serie y/o entre múltiples protocolos que se pueden usar en el bus en serie de acuerdo con ciertos aspectos divulgados en el presente documento.

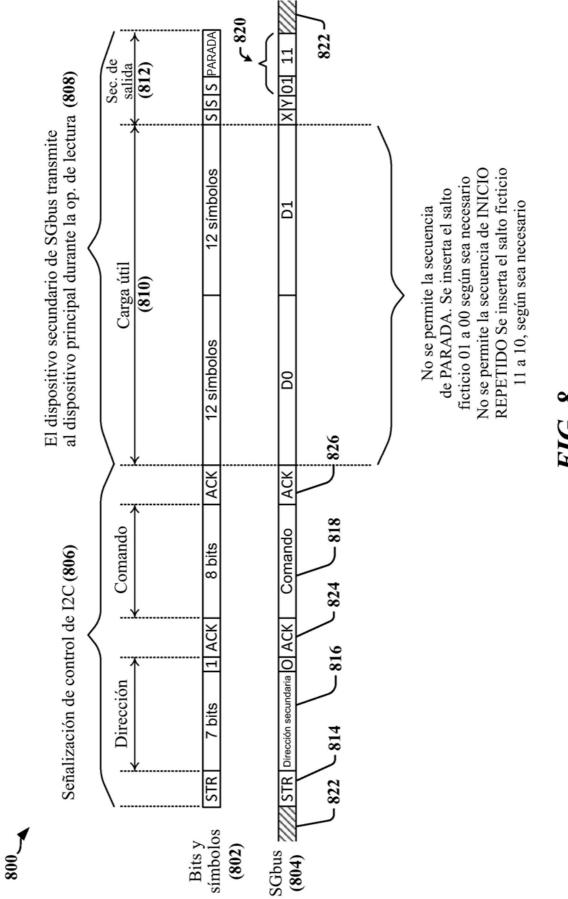

- La FIG. 8 ilustra la iniciación y terminación de transacciones en la interfaz en serie de SGbus.

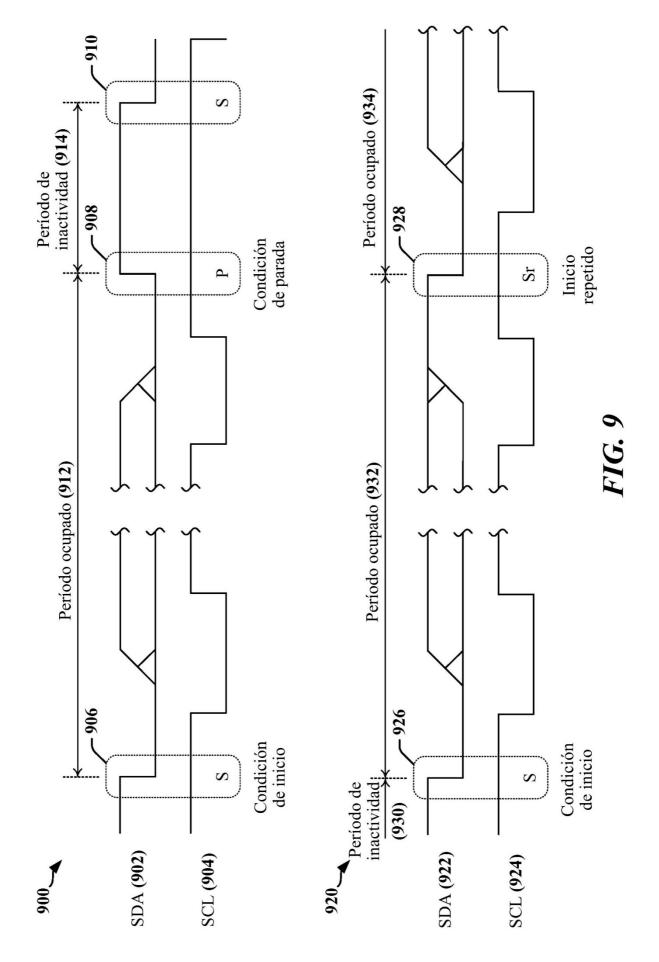

- La FIG. 9 es un diagrama que ilustra el tiempo asociado con múltiples tramas transmitidas de acuerdo con los protocolos I2C.

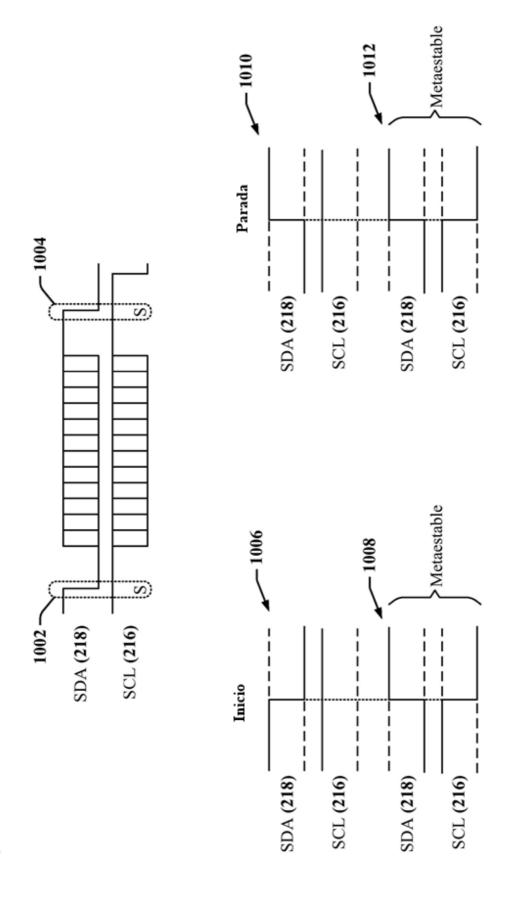

- La FIG. 10 ilustra la aparición de condiciones de INICIO y PARADA no deseadas.

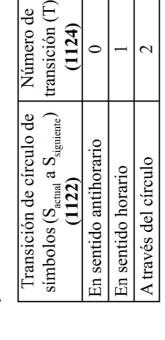

- La FIG. 11 ilustra un segundo ejemplo de un esquema de codificación para transmitir datos en un bus compartido de acuerdo con ciertos aspectos divulgados en el presente documento.

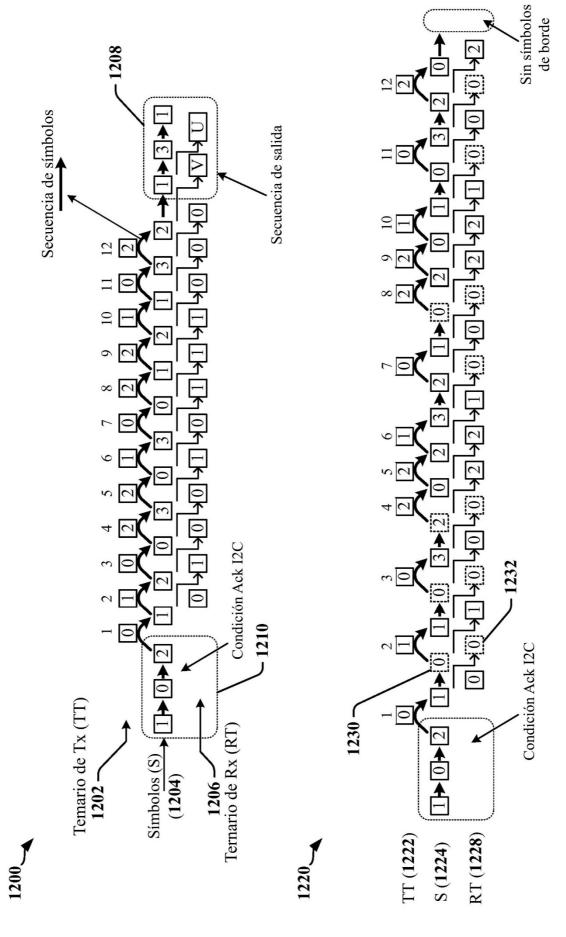

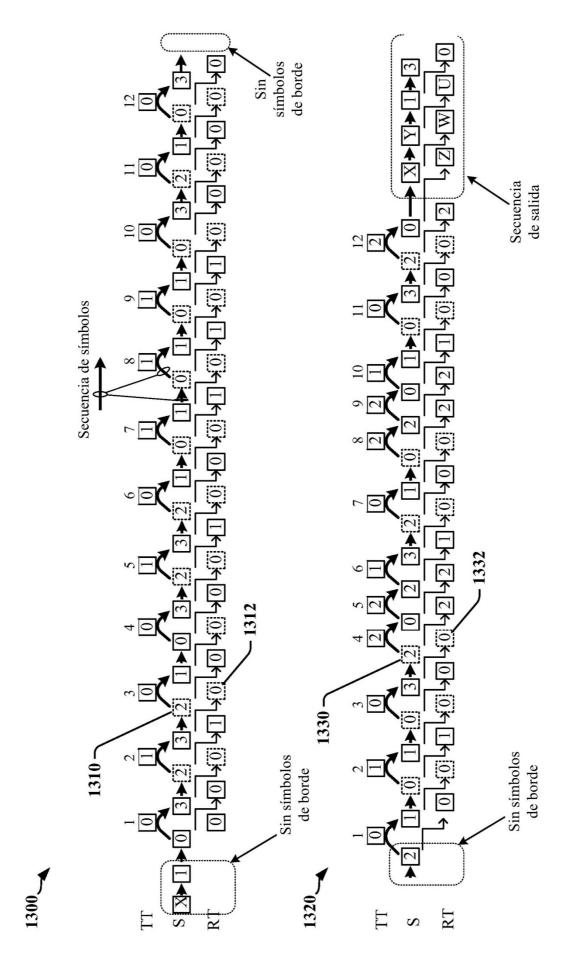

- La FIG. 12 ilustra ejemplos de codificación SGbus de acuerdo con ciertos aspectos divulgados en el presente documento.

- La FIG. 13 ilustra ejemplos adicionales de codificación SGbus de acuerdo con ciertos aspectos divulgados en el presente documento.

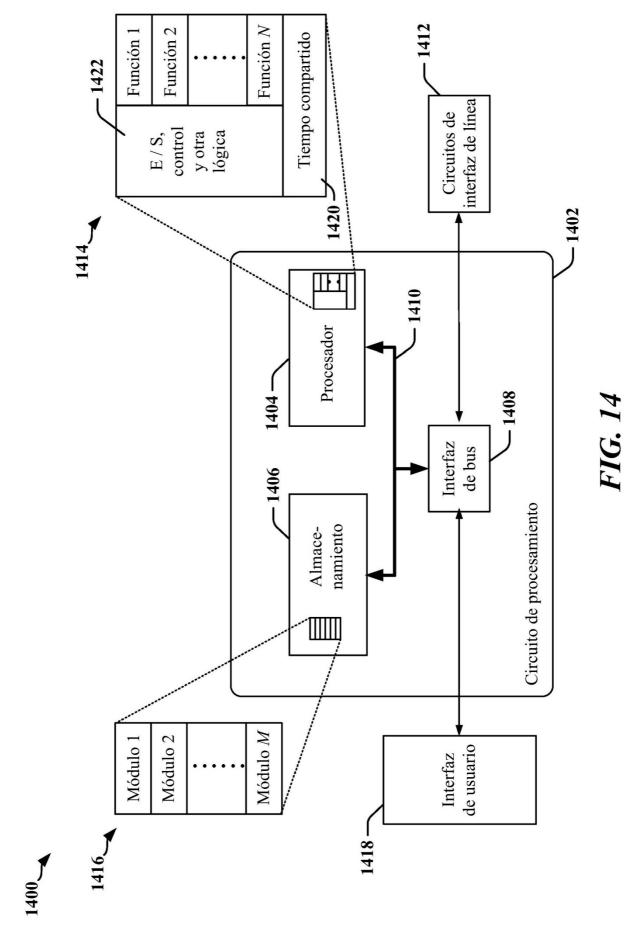

- La FIG. 14 es un diagrama de bloques que ilustra un ejemplo de un aparato que emplea un circuito de procesamiento que puede adaptarse de acuerdo con ciertos aspectos divulgados en el presente documento.

- La FIG. 15 es un diagrama de flujo de un primer ejemplo de un procedimiento para comunicarse utilizando un SGbus de acuerdo con uno o más aspectos divulgados en el presente documento.

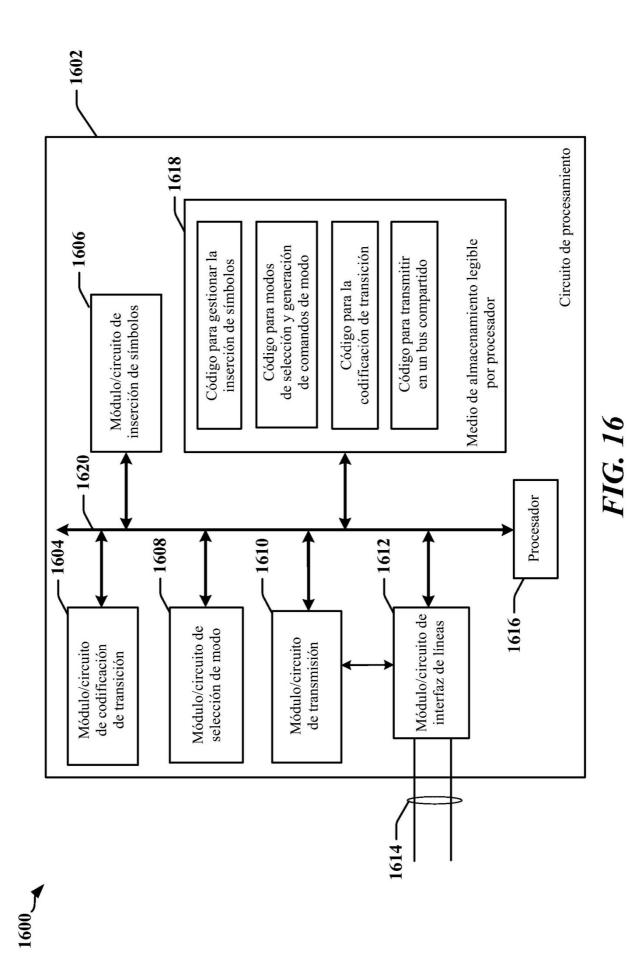

- La FIG. 16 es un diagrama que ilustra un primer ejemplo de una implementación de hardware para un aparato que emplea un circuito de procesamiento adaptado de acuerdo con determinados aspectos divulgados en el presente documento.

- La FIG. 17 es un diagrama de flujo de un segundo ejemplo de un procedimiento para comunicarse utilizando un SGbus de acuerdo con uno o más aspectos divulgados en el presente documento.

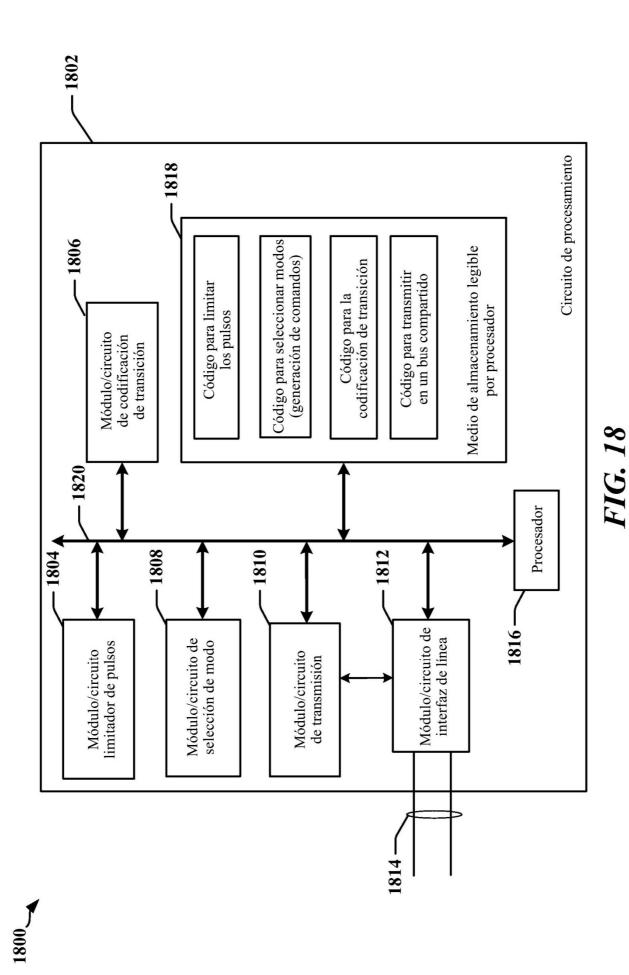

- La FIG. 18 es un diagrama que ilustra un segundo ejemplo de una implementación de hardware para un aparato que emplea un circuito de procesamiento adaptado de acuerdo con determinados aspectos divulgados en el presente documento.

#### **DESCRIPCIÓN DETALLADA**

5

10

25

35

40

55

- [0012] La descripción detallada expuesta a continuación en relación con los dibujos adjuntos, está concebida como una descripción de diversas configuraciones y no está concebida para representar las únicas configuraciones en las cuales pueden llevarse a la práctica los conceptos descritos en el presente documento. La descripción detallada incluye detalles específicos para el propósito de proporcionar un entendimiento profundo de diversos conceptos. Sin embargo, resultará evidente para los expertos en la materia que estos conceptos pueden llevarse a la práctica sin estos detalles específicos. En algunos ejemplos, se muestran estructuras y componentes bien conocidos en forma de diagrama de bloques para evitar oscurecer dichos conceptos.

- [0013] A continuación se presentarán varios aspectos de los sistemas de comunicación con referencia a varios aparatos y procedimientos. Estos aparatos y procedimientos se describirán en la siguiente descripción detallada y se ilustrarán en los dibujos adjuntos mediante varios bloques, módulos, componentes, circuitos, pasos, procesos, algoritmos, etc. (denominados conjuntamente "elementos"). Estos elementos pueden implementarse usando hardware electrónico, software informático o cualquier combinación de los mismos. Si tales elementos se implementan como hardware o software depende de la aplicación particular y de las limitaciones de diseño impuestas sobre todo el sistema.

- [0014] Tal y como se utilizan en esta solicitud, los términos "componente", "módulo", "sistema" y similares pretenden incluir una entidad relacionada con la informática, tal como, pero sin limitarse a, hardware, firmware, una combinación de hardware y software, software o software en ejecución. Por ejemplo, un componente puede ser, pero no se limita a ser, un proceso que se ejecuta en un procesador, un procesador, un objeto, un módulo ejecutable, un hilo de ejecución, un programa y/o un ordenador. A modo de ilustración, tanto una aplicación que se ejecute en un dispositivo informático como el dispositivo informático pueden ser un componente. Uno o más componentes pueden residir dentro de un proceso y/o hilo de ejecución, y un componente puede estar localizado en un ordenador y/o distribuirse entre dos o más ordenadores. Además, estos componentes pueden ejecutarse desde diversos medios legibles por ordenador que tengan diversas estructuras de datos almacenadas en los mismos. Los componentes pueden comunicarse mediante procesos locales y/o remotos, tales como de acuerdo con una señal que tiene uno o más paquetes de datos, tales como datos de un componente que interactúa con otro componente en un sistema local, un sistema distribuido y/o a través de una red, tal como Internet, con otros sistemas por medio de la señal.

- [0015] Además, el término "o" pretende referirse a un "o" incluyente en lugar de un "o" excluyente. Es decir, a no ser que se indique lo contrario o que resulte claro a partir del contexto, la frase "X emplea A o B" pretende significar

cualquiera de las permutaciones inclusivas naturales. Es decir, la frase "X emplea A o B" se satisface en cualquiera de los siguientes casos: X emplea A; X emplea B; o X emplea tanto A como B. Además, los artículos "un" y "uno", según se utilizan en esta solicitud y en las reivindicaciones adjuntas, deberían ser interpretados, en general, con el significado de "uno o más", a no ser que se especifique lo contrario, o que sea claro a partir del contexto que se orientan a una forma singular.

## Resumen del bus global de sensores

5

10

15

20

25

30

35

40

45

50

55

60

65

[0016] Ciertos aspectos aplicables a una amplia gama de interfaces de comunicación se divulgan en el presente documento y se describen en el contexto de un bus global de sensores (SGbus). El SGbus puede implementarse como una interfaz de bus de dos cables utilizada para acoplar sensores y dispositivos de procesamiento. Ciertos ejemplos de SGbus proporcionan compatibilidad hacia atrás con el bien conocido bus I2C, en la medida en que ciertos dispositivos I2C heredados pueden comunicarse a través del mismo par de cables utilizado por el SGbus. Los dispositivos que se comunican utilizando las especificaciones y los protocolos de SGbus pueden contar con un mayor rendimiento, producción, fiabilidad y robustez que los que se pueden proporcionar utilizando otras interfaces, incluida una interfaz I2C.

[0017] El SGbus puede reducir los requisitos de energía del sistema, mediante la implementación de una interfaz de baja potencia, y puede aumentar la eficiencia de transferencia de bits. El SGbus emplea uno o más protocolos que están asociados con una sobrecarga baja y un uso eficiente del bus, y el SGbus puede habilitar transacciones de alta velocidad y un porcentaje de tiempo bajo correspondiente en el que la interfaz está activa. Mientras está inactivo, el SGbus en general consume una potencia relativamente baja, lo cual puede atribuirse en parte a un pequeño espacio de utilización de silicio. Un conjunto de sensores conectados a través de un SGbus se puede configurar y gestionar localmente, según sea necesario o deseado, para minimizar las complejidades en el nivel del sistema, por ejemplo.

## Ejemplos de dispositivos que emplean un bus en serie

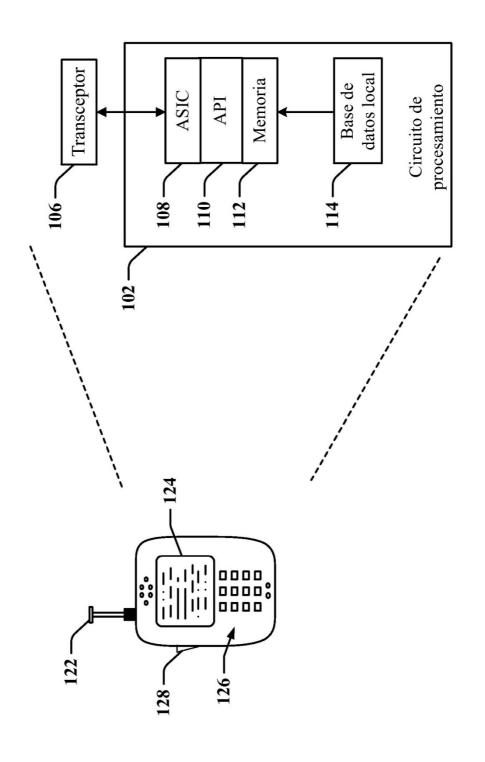

[0018] Ciertos aspectos divulgados en el presente documento pueden ser aplicables a los enlaces de comunicaciones desplegados entre dispositivos electrónicos que pueden incluir subcomponentes de un aparato tal como un teléfono, un dispositivo informático móvil, un dispositivo informático portátil, un aparato, la electrónica del automóvil, sistemas de aviónica, etc. La FIG. 1 representa un aparato que puede emplear un enlace de comunicación entre dispositivos de CI. En un ejemplo, el aparato 100 puede incluir un dispositivo de comunicación inalámbrica que se comunica a través de un transceptor de radiofrecuencia (RF) con una red de acceso radioeléctrico (RAN), una red de acceso central, Internet y/u otra red. El aparato 100 puede incluir un transceptor de comunicaciones 106 acoplado de manera operativa al circuito de procesamiento 102. El circuito de procesamiento 102 puede incluir uno o más dispositivos de CI, tales como un CI específico de la aplicación (ASIC) 108. El ASIC 108 puede incluir uno o más dispositivos de procesamiento, circuitos lógicos, etc. El circuito de procesamiento 102 puede incluir y/o acoplarse a un almacenamiento legible por procesador tal como una memoria 112 que puede mantener instrucciones y datos que pueden ser ejecutados por el circuito de procesamiento 102. El circuito de procesamiento 102 puede ser controlado por un sistema operativo y/o a través de una capa de interfaz de programación de aplicaciones (API) 110 que da soporte y permite la ejecución de módulos de software que residen en medios de almacenamiento, tales como el dispositivo de memoria 112 del dispositivo inalámbrico. El dispositivo de memoria 112 puede incluir memoria de solo lectura (ROM) o memoria de acceso aleatorio (RAM), ROM programable borrable eléctricamente (EEPROM), tarjetas de memoria flash o cualquier dispositivo de memoria que pueda usarse en sistemas de procesamiento y plataformas informáticas. El circuito de procesamiento 102 puede incluir o acceder a una base de datos local 114 que puede mantener parámetros operativos y otra información utilizada para configurar y hacer funcionar el aparato 100. La base de datos local 114 puede implementarse utilizando uno o más entre un módulo de base de datos, memoria flash, medios magnéticos, EEPROM, medios ópticos, cinta, disco flexible o rígido, o similares. El circuito de procesamiento también puede estar acoplado operativamente a dispositivos externos tales como una antena 122, un visor 124, controles de operador, tales como un botón 128 y un teclado numérico 126, entre otros componentes.

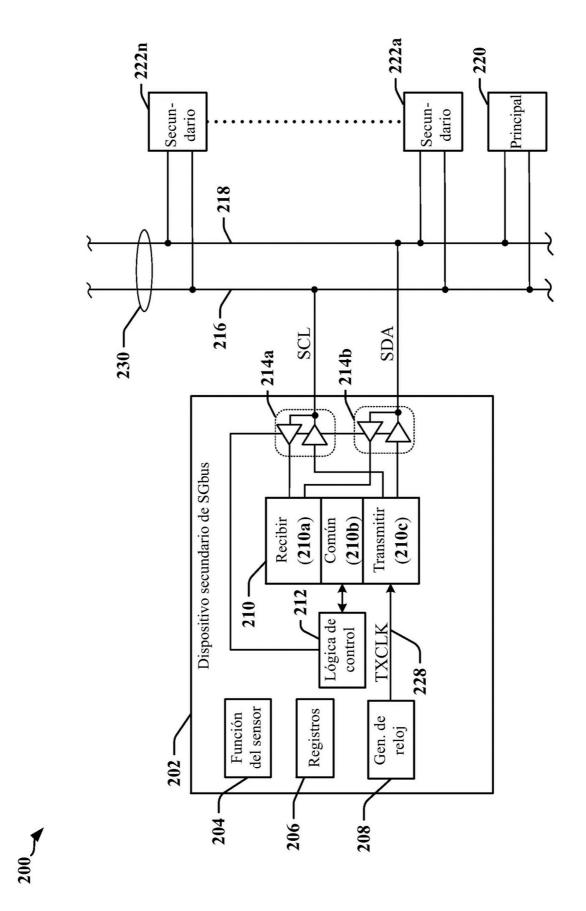

[0019] La FIG. 2 es un diagrama de bloques que ilustra ciertos aspectos de un aparato 200 conectado a un bus de comunicaciones, donde el aparato puede incorporarse en uno o más de un dispositivo móvil inalámbrico, un teléfono móvil, un sistema informático móvil, un teléfono inalámbrico, un ordenador portátil, un dispositivo tipo tableta, un reproductor multimedia, un dispositivo de juegos, un asistente digital personal (PDA) u otro dispositivo de mano, un netbook, un ordenador portátil, una televisión, un dispositivo de entretenimiento, un dispositivo portátil o similar. El aparato 200 puede incluir múltiples dispositivos 202, 220 y 222a-222n, que se comunican usando un bus en serie 230. El bus en serie 230 puede extender las capacidades de un bus de I2C convencional para dispositivos que están configurados para características mejoradas soportadas por el bus en serie 230. Por ejemplo, el bus en serie 230 puede dar soporte a una velocidad de bits mayor que un bus de I2C.

[0020] En el ejemplo ilustrado en la FIG. 2, un dispositivo 202 puede configurarse para funcionar como dispositivo secundario en el bus en serie 230. El dispositivo 202 puede adaptarse para proporcionar una función de sensor 204 que incluye y/o gestiona uno o más sensores genéricos, sensores de alta velocidad, sensores de huellas dactilares, sensores de imagen (por ejemplo, cámaras), sensores de pantalla táctil, etc. Además, el dispositivo 202 puede incluir registros de configuración u otros dispositivos de almacenamiento 206, lógica de control 212, un transceptor 210 y

controladores/receptores de línea 214a y 214b. La lógica de control 212 pueden incluir un circuito de procesamiento tal como una máquina de estados, un secuenciador, un procesador de señales o un procesador de uso general. El transceptor 210 puede incluir un receptor 210a, un transmisor 210c y ciertos circuitos comunes 210b, que incluyen circuitos y/o dispositivos de temporización, lógicos y de almacenamiento. En un ejemplo, el transmisor 210c codifica y transmite datos basándose en la temporización proporcionada por un circuito de generación de reloj 208.

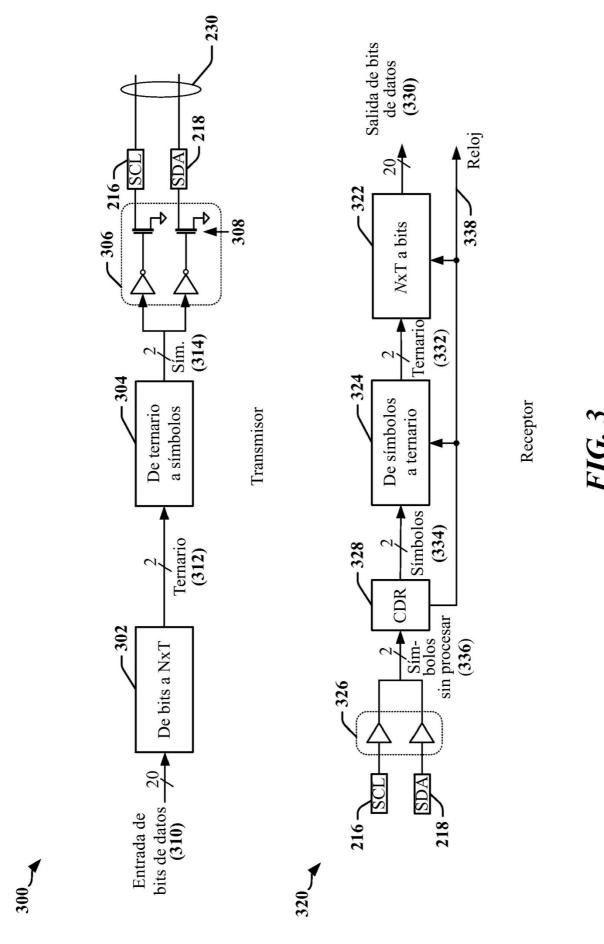

[0021] La FIG. 3 es un diagrama de bloques que ilustra un ejemplo de un transmisor 300 y un receptor 320 configurados de acuerdo con ciertos aspectos divulgados en el presente documento. Para operaciones SGbus, el transmisor 300 puede transcodificar los datos de entrada 310 en números ternarios (base 3) que están codificados en símbolos para ser transmitidos en los cables de señal SCL 216 y SDA 218. En el ejemplo representado, cada elemento de datos (también denominado palabra de datos) de los datos de entrada 310 puede tener un número predefinido de bits, como 8, 12, 16, 19 o 20 bits. Un transcodificador 302 puede recibir los datos de entrada 310 y producir una secuencia de números ternarios de un solo dígito 312 para cada elemento de datos. En algunos casos, la secuencia de números ternarios de un solo dígito 312 puede expresarse como un número ternario de varios dígitos. Un número ternario de un solo dígito puede codificarse en dos bits y puede haber 12 dígitos en cada secuencia de números ternarios de un solo dígito 312. Un codificador, como el convertidor ternario a símbolos 304, produce un flujo de símbolos de 2 bits 314 que se proporcionan a un par de controladores de línea 306. En el ejemplo que se muestra, los controladores de línea 306 incluyen transistores de salida de drenaje abierto 308 que accionan los cables de señal SCL 216 y SDA 218. En ciertos ejemplos, los controladores de línea 306 pueden incluir o estar acoplados a controladores push-pull que conducen los cables de señal SCL 216 y SDA 218. El flujo de salida de los símbolos de 2 bits 314 generados por el convertidor ternario a símbolos 304 provoca una transición en el estado de señalización de al menos uno de los cables de señal SCL 216 y SDA 218 entre cada par de símbolos consecutivos 314. Estas transiciones se proporcionan al garantizar que ningún par de símbolos consecutivos incluya dos símbolos idénticos. La disponibilidad de una transición en el estado de señalización en al menos un cable 216 y/o 218 permite que un receptor 320 extraiga un reloj de recepción 338 del flujo de símbolos de datos 314.

[0022] En una interfaz SGbus, el receptor 320 puede incluir o cooperar con una recuperación de reloj y datos (CDR) de circuito 328. El receptor 320 puede incluir circuitos de interfaz de línea 326 que proporcionan un flujo de símbolos sin procesar de 2 bits 336 al circuito CDR 328. El circuito CDR 328 extrae un reloj de recepción 338 de los símbolos sin procesar 336 y proporciona un flujo de símbolos de 2 bits 334 y el reloj de recepción 338 a otros circuitos 324 y 322 del receptor 320. En algunos ejemplos, el circuito CDR 328 puede producir múltiples relojes. Un descodificador, tal como el convertidor de símbolos a ternario 324, puede usar el reloj de recepción 338 para descodificar el flujo de símbolos 334 en secuencias de 12 números ternarios 332. Los números ternarios 332 pueden codificarse utilizando dos bits. Un transcodificador 322 puede convertir cada secuencia de 12 números ternarios 332 en elementos de datos de salida de 8, 12, 16, 19 o 20 bits 330.

## Ejemplo de un esquema de codificación de transición con un reloj incorporado

5

10

15

20

25

30

35

50

55

60

65

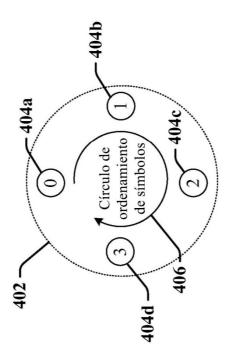

[0023] La FIG. 4 es un dibujo que ilustra un esquema de codificación 400 que puede ser utilizado por el convertidor ternario a símbolos 304 para producir una secuencia de símbolos 314 con un reloj integrado para transmisión en el bus en serie 230. El esquema de codificación 400 también puede ser utilizado por el convertidor de símbolos a ternario 324 del receptor 320 para extraer los números de transición ternarios de los símbolos recibidos desde el bus en serie 230. En el esquema de codificación de SGbus 400, los dos cables del bus en serie 230 permiten la definición de 4 símbolos básicos S: {0, 1, 2, 3}. Cualquiera de los dos símbolos consecutivos en la secuencia de símbolos 314, 334 producen diferentes estados de señalización en el bus en serie 230, y las secuencias de símbolos 0,0; 1,1; 2,2; y 3,3 son combinaciones no válidas de símbolos consecutivos. En consecuencia, solo están disponibles 3 transiciones de símbolo válidas en cada límite de símbolo, donde el límite del símbolo está determinado por el reloj de transmisión y representa el punto en el que un primer símbolo (símbolo anterior Ps) 422 termina y un segundo símbolo (símbolo actual Cs) 424 comienza.

[0024] De acuerdo con ciertos aspectos divulgados en el presente documento, a las tres transiciones disponibles se les asigna un número de transición (T) 426 para cada símbolo Ps 422. El valor de T 426 puede representarse por un número ternario. En un ejemplo, el valor del número de transición 426 se determina asignando un círculo de ordenación de símbolos 402 para el esquema de codificación. El círculo de ordenación de símbolos 402 asigna las ubicaciones 404a-404d en el círculo 402 para los cuatro símbolos posibles, y una dirección de rotación 406 entre las ubicaciones 404a-404d. En el ejemplo representado, la dirección de rotación 406 es en el sentido horario. El número de transición 426 puede representar la separación entre los símbolos de corriente válidos 424 y el símbolo inmediatamente anterior 422. La separación se puede definir como el número de pasos a lo largo de la dirección de rotación 406 en el círculo de ordenación de símbolos 402 requerido para alcanzar el símbolo actual Cs 424 desde el símbolo anterior 422. El número de pasos se puede expresar como un número base 3 de un solo dígito. Se apreciará que una diferencia de tres pasos entre los símbolos se puede representar como un 0<sub>base-3</sub>. La tabla 420 en la FIG. 4 resume un esquema de codificación que emplea este enfoque.

[0025] En el transmisor 300, la tabla 420 se puede usar para buscar un símbolo actual 424 para ser transmitido, dado el conocimiento del símbolo generado previamente 422 y un número ternario de entrada, que se utiliza como un número de transición 426. En el receptor 320, la tabla 420 puede usarse como una búsqueda para determinar un

número de transición 426 que representa la transición entre el símbolo recibido anteriormente 422 y el símbolo recibido actualmente 424. El número de transición 426 puede emitirse como un número ternario.

#### Coexistencia en un bus en serie

10

[0026] Una pluralidad de dispositivos de SGbus pueden coexistir en el mismo bus 230 con uno o más dispositivos I2C heredados. En consecuencia, la interfaz SGbus define esquemas de señalización que pueden ignorarse, no detectarse o que de otro modo los dispositivos I2C heredados no los tienen en cuenta. Por ejemplo, los dispositivos de SGbus pueden transmitir información de control en la señalización que es coherente con la señalización en modo I2C, y pueden transmitir la carga útil de datos codificada de acuerdo con los protocolos CCIe para obtener velocidades de transmisión más rápidas. Los dispositivos de SGbus pueden usar otros modos de codificación para transmitir la carga útil de datos, incluidos los modos I2C heredados. Los modos de codificación alternativos pueden emplear codificación de transición para codificar datos en una secuencia de símbolos con información de reloj incorporada en las transiciones entre símbolos consecutivos en la secuencia de símbolos. Es decir, los datos pueden transcodificarse a un número ternario, donde cada dígito del número ternario selecciona un símbolo siguiente basándose en el estado de señalización anterior (es decir, el símbolo anterior) del bus.

15

5

[0027] Ciertos aspectos divulgados en el presente documento se refieren a la coexistencia en un bus en serie de dispositivos que se comunican usando diferentes protocolos de comunicación y/o señalización. En algunos ejemplos, un dispositivo configurado para comunicarse a través de un bus en serie utilizando un primer protocolo puede ignorar las comunicaciones entre otros dispositivos que usan un segundo protocolo cuando el segundo protocolo emplea señalización que genera eventos reconocidos por el primer protocolo. Ciertos aspectos se describirán ahora usando ejemplos en los que el primer protocolo es un protocolo compatible o que cumple con I2C, y el segundo protocolo es un CCIe, SGbus u otro protocolo.

25

30

35

20

[0028] La FIG. 5 es un diagrama de temporización 500 que ilustra una operación de datos de escritura de un byte I2C. Se inicia una transmisión cuando un nodo principal proporciona una condición de INICIO 506 llevando el SDA 218 a un nivel bajo, mientras que el SCL 216 permanece alto. Un nodo principal I2C envía una ID de dispositivo secundario de 7 bits 502 en el SDA 218 para indicar a qué nodo secundario en el bus I2C desea acceder el nodo principal, seguido de un bit de lectura/escritura 512 que indica si la operación es una operación de lectura o una operación de escritura, donde el bit 512 de lectura/escritura está en la lógica 0 para indicar una operación de escritura y en la lógica 1 para indicar una operación de lectura. Solo el nodo secundario cuyo ID coincide con el ID de dispositivo secundario de 7 bits 502 puede responder a la operación de escritura (u otra). Para que un nodo secundario I2C detecte su propia ID de dispositivo secundario 502, el nodo principal transmite al menos 8 bits en el SDA 218, junto con 8 pulsos de reloj en el SCL 216. El nodo principal proporciona una condición de PARADA 516 para terminar la transacción al elevar el SDA 218 mientras que el SCL 216 permanece alto. Se considera que la interfaz I2C está en un estado "bus ocupado" después de una condición de INICIO 506 y en un estado de "bus libre" después de una condición de PARADA 516. Este comportamiento puede ser explotado para evitar que los nodos secundarios I2C heredados reaccionen a las transmisiones de acuerdo con ciertos protocolos, incluido el protocolo CCIe.

40

45

[0029] Las comunicaciones CCIe pueden usar la combinación de la SCL 216 y la SDA 218 de un bus I2C para la transmisión de datos. Un símbolo CCIe puede transmitirse en un momento correspondiente a cada conmutación de un pulso de señal de reloi 514 transmitido en el SCL 216 para una transmisión I2C. El número de interruptores de reloi transmitidos en cada período de transmisión de trama puede, por lo tanto, definir el número de símbolos que pueden transmitirse para cada transmisión CCIe. Por consiguiente, pueden proporcionarse transmisiones de 12 símbolos en los 12 estados de señalización disponibles durante una secuencia de pulsos 6-SCL.

50

[0030] El SCL 216 y/o la SDA 218 de un bus I2C se pueden utilizar para la transmisión de datos en el modo CCIe cuando una señal de reloj se ha incorporado dentro de las transiciones de símbolos. En consecuencia, el SDA 218 y el SCL 216 se pueden usar para transmitir 12 símbolos arbitrarios cualesquiera sin afectar a la funcionalidad del nodo secundario I2C heredado y sin usar un dispositivo puente para separar los nodos secundarios I2C heredados de los nodos compatibles con CCIe. En el modo I2C, una condición de INICIO 506 puede ser proporcionada solo por un dispositivo principal I2C. En el modo CCIe, el nodo que va a transmitir una palabra de 12 símbolos proporciona una condición de INICIO 506.

55

60

65

[0031] De acuerdo con ciertos aspectos divulgados en el presente documento, dispositivos I2C pueden coexistir en un bus en serie con los dispositivos que emplean un protocolo de comunicación diferente, cuando se explotan ciertas características de señalización de la SCL 216. Por ejemplo, la especificación I2C de que los picos y/o pulsos con una duración de 50 ns o menos se filtran mediante dispositivos que son compatibles o que cumplen con el modo I2C Fast (Fm) o Fm+. Por consiguiente, un protocolo que se usa en un bus en serie compartido con dispositivos I2C puede incluir un modo de funcionamiento en el que los pulsos en el SCL 216 están limitados a una duración que es inferior a 50 ns. La limitación en la duración del pulso se puede imponer controlando la generación de pulsos de reloj del estado alto en el SCL 216, implementando un esquema de señalización de retorno a cero para el SCL 216, y/o insertando un símbolo adicional que evite que el SCL 216 permanezca en un estado alto durante 50 ns. El símbolo adicional se puede denominar un símbolo ficticio en el presente documento. En un ejemplo, varios símbolos pueden transmitirse dentro de un período de 50 ns y, cuando el codificador detecta que es probable que una secuencia de

símbolos mantenga el SCL 216 en un estado alto durante 50 ns, el codificador puede insertar un símbolo ficticio que haga que el SCL 216 baje antes de que se complete el período de 50 ns.

[0032] La inserción de un símbolo ficticio puede hacer que un pulso adicional (pulso ficticio) se transmita en uno o más cables de señal del bus en serie. En el ejemplo I2C descrito anteriormente, se puede insertar un símbolo ficticio para forzar un estado lógico bajo en el SCL 216 cuando de otra forma dos símbolos consecutivos mantendrían el SCL 216 en el estado lógico alto. Después de la transmisión del símbolo ficticio, el SCL 216 vuelve a un estado lógico alto correspondiente al segundo símbolo en los dos símbolos consecutivos. En algunos casos, la señalización de retorno a cero (RZ) se puede usar en el SCL 216 para evitar pulsos positivos de larga duración en el SCL 216. En algunos casos, la lógica del hardware puede configurarse para controlar el SCL 216 insertando un pulso bajo de lógica de corta duración cuando el SCL 216 permanece en un estado alto durante un período de tiempo predefinido.

[0033] Un pulso ficticio se puede insertar en uno o más cables de señal del bus en serie para fines distintos de la limitación de duraciones de pulso de reloj aparentes cuando se utiliza codificación de símbolo de transición. Se puede proporcionar un pulso ficticio para evitar la aparición de estados no deseados que pueden indicar eventos o condiciones de sincronización. Por ejemplo, las condiciones de INICIO y PARADA de I2C pueden indicarse cuando el SCL 216 baja, mientras que el SDA 218 permanece sin cambios, y se puede insertar un pulso ficticio en el SDA 218 para evitar dicha indicación cuando el bus en serie se utiliza para las comunicaciones de acuerdo con un protocolo distinto de I2C.

## Transición entre protocolos de comunicación

[0034] La FIG. 6 ilustra una configuración en la que un bus compartido 602 acopla dispositivos I2C 604<sub>I</sub>-604<sub>k</sub>, 606 y dispositivos CCIe 612, 614<sub>I</sub>-614<sub>n</sub> y 616<sub>I</sub>-616<sub>m</sub>. Los dispositivos de SGbus 612, 614<sub>I</sub>-614<sub>n</sub> y 616<sub>I</sub>-616<sub>m</sub> pueden coexistir con dispositivos I2C configurados de manera convencional 604<sub>I</sub>-604<sub>k</sub>, 606 y algunos de los dispositivos de SGbus 612, 614<sub>I</sub>-614<sub>n</sub> y 616<sub>I</sub>-616<sub>m</sub> puede comunicarse utilizando los protocolos I2C convencionales, según se desee o se necesite.

[0035] La transferencia de datos en el bus compartido 602, incluyendo la configuración y otros mensajes de control de bus, pueden iniciarse y realizarse utilizando un primer protocolo, tal como una versión modificada de un protocolo I2C o una variante del protocolo I2C. En un ejemplo, todas las transacciones pueden iniciarse utilizando protocolos I2C convencionales para iniciar la transacción.

[0036] De acuerdo con ciertos aspectos divulgados en el presente documento, las comunicaciones en un bus compartido 602 puede estar en contenedores eficazmente de tal manera que las transferencias de datos entre los dispositivos acoplados al bus compartido 602 se encapsulan en las transacciones (contenedores) que se producen entre la gestión del bus y/o comandos de control. Típicamente, los dispositivos que están configurados para comunicarse utilizando el protocolo empleado por los dispositivos involucrados en una transacción actual pueden ignorar o ser ajenos a la transacción.

[0037] La FIG. 7 es un diagrama de flujo 700 que ilustra un esquema generalizado para la transición entre contenedores o modos de funcionamiento de un bus compartido 602. Cada contenedor, modo de funcionamiento y/o protocolo puede estar asociado con un estado operativo correspondiente 702, 704, 706, 708, 710 del bus compartido 602. Los modos de funcionamiento del bus pueden distinguir entre esquemas de señalización, rendimiento de datos, formatos de transmisión y similares. Se pueden definir diferentes modos de funcionamiento para un protocolo. Por ejemplo, los modos de 12 símbolos y 20 símbolos se pueden definir para el protocolo CCIe.

[0038] En funcionamiento, un estado de protocolo común 704 se utiliza para intercambiar comandos de gestión de bus utilizando un protocolo común que es entendido por todos los dispositivos principales de bus y/o por todos los dispositivos en el bus. En un ejemplo, un dispositivo secundario de protocolo único puede ser incapaz de comunicarse utilizando el protocolo común y, en consecuencia, puede ignorar los comandos de gestión del bus. En este último ejemplo, un dispositivo principal de bus puede tomar el control del bus compartido 602 y comunicarse con el dispositivo secundario de protocolo único utilizando el protocolo entendido por el dispositivo secundario de protocolo único.

[0039] En algunos ejemplos, un protocolo I2C se utiliza en el estado de protocolo común 704. En otros ejemplos, se puede utilizar un protocolo diferente en el estado de protocolo común 704. El bus compartido 602 se puede inicializar en un estado de inicio 702, por lo que los dispositivos acoplados al bus compartido 602 se configuran para el protocolo común. En las implementaciones de un dispositivo principal de un único bus del protocolo común, el dispositivo principal de bus designado puede descubrir y/o configurar otros dispositivos acoplados al bus compartido 602 de acuerdo con los procedimientos definidos por el protocolo común. En implementaciones de múltiples dispositivos principales, uno o más dispositivos principales pueden participar en un proceso de descubrimiento, configuración y/o arbitraje para determinar qué dispositivo principal de bus controla el bus compartido 602 al entrar en el estado de protocolo común 704. Se puede adoptar un concepto jerárquico de bus, donde un dispositivo principal de bus tiene el control activo del bus compartido 602 en cualquier momento, y otros dispositivos principales de bus solicitan y esperan un control de concesión del bus compartido 602.

65

5

10

15

20

25

30

35

50

55

[0040] En el estado de protocolo común 704, uno o más dispositivos puede competir por el control del bus compartido 602. El bus compartido 602 puede hacerse funcionar en un estado de protocolo deseado o arbitrado 706, 708 para permitir una transacción de comunicación entre dispositivos acoplados al bus compartido 602. Al finalizar la transacción, el bus compartido 602 se devuelve al estado de protocolo común 704. Cuando ningún dispositivo solicita acceso al bus compartido 602, el bus compartido 602 puede entrar en un estado inactivo 710. En el estado inactivo, uno o más dispositivos pueden entrar en un modo de funcionamiento de apagado. Un dispositivo principal de bus puede hacer que el bus compartido 602 entre periódicamente en el estado de protocolo común 704 para determinar si algún dispositivo solicita acceso al bus compartido 602. En algunos casos, el bus compartido 602 puede devolverse al estado del protocolo común 704 en respuesta a una interrupción u otro evento.

10

[0041] La entrada en un estado de protocolo 704, 706, 708 y la salida de los estados de protocolo 704, 706, 708 puede efectuarse usando comandos de gestión de bus. Estos comandos pueden implementarse utilizando señalización, mensajería o alguna combinación de señalización y mensajería seleccionada basándose en la arquitectura y el diseño del bus compartido 602.

15

**[0042]** Las transferencias de datos pueden ocurrir en el estado de protocolo común 704 o uno de los estados de protocolo 706, 708 utilizados por subconjuntos de los dispositivos acoplados al bus compartido 602. Los estados de protocolo 706, 708 utilizados por subconjuntos de dispositivos pueden ser cualquier protocolo compatible con el bus compartido 602. Los datos pueden transferirse en unidades de palabras, tramas y/o paquetes, y se contemplan modos flexibles de transferencia de datos.

20

[0043] En algunos casos, las direcciones pueden asignarse dinámicamente a dispositivos acoplados al bus compartido 602. En un ejemplo, la asignación dinámica de direcciones se realiza en el estado de protocolo común 704 para proporcionar una identificación única de los dispositivos que se comunican mediante el protocolo común y para asignar clasificaciones de prioridad para dichos dispositivos. En algunos casos, la asignación dinámica de direcciones se realiza en uno o más de los otros estados de protocolo 706, 708 para proporcionar una identificación única de los dispositivos que se comunican utilizando protocolos distintos al protocolo común, y para asignar clasificaciones de prioridad para dichos dispositivos.

25

[0044] En algunos casos, un esquema de control de excepciones se define para el estado del protocolo común 704. Por ejemplo, se puede proporcionar un procedimiento de interrupción en banda compatible con I2C cuando el protocolo común es I2C o un derivado de I2C.

30

[0045] En algunos casos, puede implementarse un procedimiento "de conexión rápida", donde dicho procedimiento de conexión rápida incluye y/o utiliza interrupción en banda y los procedimientos de asignación dinámica de direcciones.

35

40

[0046] La FIG. 8 ilustra una transacción 800 realizada en el bus compartido 602 para un ejemplo en el que el bus compartido 602 soporta transacciones de comunicación que involucran bits y símbolos 802 transmitidos por los protocolos I2C y SGbus, respectivamente, de acuerdo con ciertos aspectos descritos en el presente documento. Inicialmente, el bus compartido 602 puede estar en un estado libre de bus 822, y la señalización de control 806 se maneja de acuerdo con un protocolo I2C comúnmente entendido. Después de que la señalización de control 806 se confirma como 824, 826, puede ocurrir un intercambio de datos SGbus 808, durante el cual se transmite una carga útil de datos 810 al dispositivo principal de SGbus 612. Una secuencia de salida 812 proporciona una transición desde el intercambio de datos SGbus 808 (es decir, la señalización de acuerdo con los protocolos SGbus) a la señalización reconocida como una condición de PARADA 820, 516 coherente con los protocolos I2C. A continuación se puede obtener un estado libre de bus 822 (véase también el estado inactivo 710 de la FIG. 7).

45

50

[0047] En el ejemplo representado, una transacción 800 en el bus compartido 602 puede ser iniciada por una condición I2C INICIO 814 (véase también, la condición de INICIO 506 de la FIG. 5) que precede a una dirección 816 (véase la ID de dispositivo secundario I2C 502, por ejemplo) seguida de una sucesión de códigos de comando 818. Los códigos de comando 818 pueden tener una longitud variable que puede incluir una cantidad de bytes predefinidos por un protocolo de comunicación SGbus utilizado para el bus compartido 602.

55

[0048] En un ejemplo, puede transmitirse un código de comando 818 para definir un protocolo de transferencia de datos seleccionado y/o ciertas características del protocolo de transferencia de datos. Este último código de comando puede identificar uno de una pluralidad de protocolos de transferencia de datos disponibles que se utilizarán para transferencias de datos posteriores. El protocolo de transferencia de datos identificado puede controlar las transacciones hasta que se inserte un comando de protocolo de transferencia de datos diferente en el bus.

60

65

[0049] Después de la condición de INICIO 814 el bus compartido 602 se considera ocupado hasta la siguiente condición de PARADA 820 (véase también, la condición de PARADA 516 de la FIG. 5). Un estado libre de bus 822 puede definirse como que ocurre cuando el SCL 216 y el SDA 218 están en un estado lógico alto durante un período de tiempo predeterminado. El estado de ocupado/libre del bus compartido 602 se puede definir o identificar basándose en la aparición de las condiciones de INICIO 814, 506 y las condiciones de PARADA 820, 516. El estado de bus libre 822 tiene una duración que incluye el período de tiempo después de una condición de PARADA 820, 516, durante el

cual el SCL 216 y el SDA 218 están en un estado lógico alto, independientemente de si los datos se transfieren utilizando protocolos compatibles con SGbus o I2C. En un ejemplo, el período de tiempo durante el cual el SCL 216 y el SDA 218 están en un estado lógico alto puede configurarse para que duplique el período del reloj más lento usado en el bus compartido 602. Por ejemplo, en el modo rápido I2C, la señal de reloj transmitida en el SCL 216 tiene una frecuencia de al menos 400 kHz, con un período de reloj de 2,5 µs, y un período de 5 µs puede ser suficiente para indicar el estado de bus libre 822.

5

10

15

20

25

30

35

40

45

50

55

60

65

[0050] Como se muestra en la FIG. 6, el bus compartido 602 puede soportar un dispositivo principal I2C heredado 606, dispositivos secundarios I2C heredados 604<sub>I</sub>-604<sub>k</sub>, un dispositivo principal de SGbus principal 612, dispositivos secundarios de SGbus 614<sub>I</sub>-614<sub>n</sub> y dispositivos principales secundarios de SGbus 616<sub>I</sub>-616<sub>m</sub>. El dispositivo principal de SGbus principal 612 típicamente está preconfigurado con cierta información operativa relacionada con los dispositivos I2C heredados 606, 604<sub>I</sub>-604<sub>k</sub> residentes en el bus compartido 602. El dispositivo principal de SGbus principal 612 puede incluir una memoria no volátil en la que la información operativa y de otro tipo puede preconfigurarse y/o actualizarse en respuesta a las comunicaciones recibidas desde un dispositivo principal de la aplicación.

[0051] Cada uno de los dispositivos principales de SGbus secundarios 616<sub>I</sub>-616<sub>m</sub> y los dispositivos secundarios de SGbus 614<sub>I</sub>-614<sub>n</sub> puede estar configurado para generar internamente una dirección aleatoria de cualquier longitud deseada, configurada o predefinida. En un ejemplo, la dirección aleatoria puede tener 48 bits. Estos dispositivos 614<sub>I</sub>-614<sub>n</sub>, 616<sub>I</sub>-616<sub>m</sub> pueden ser capaces de ocasionar una interrupción al usar una dirección reservada que puede usarse para identificar la existencia de dispositivos que no tienen direcciones locales asignadas.

[0052] En funcionamiento, el dispositivo principal de SGbus principal 612 puede transmitir una llamada general seguida de un código de comando de asignación dinámica de direcciones. El dispositivo principal de SGbus principal 612 puede entonces activar una señal de reloj en el SCL 216 del bus compartido 602 mientras libera el SDA 218, que puede llevarse a un nivel lógico alto. A continuación se lleva a cabo un proceso de arbitraje, en el que los dispositivos de SGbus 614<sub>I</sub>-614<sub>n</sub>, 616<sub>I</sub>-616<sub>m</sub> manejan el SDA 218 de acuerdo con su correspondiente dirección de 48 bits seleccionada aleatoriamente. El dispositivo de SGbus 614<sub>I</sub>-614<sub>n</sub>, 616<sub>I</sub>-616<sub>m</sub> con la dirección más baja gana el arbitraje, de manera similar a lo especificado por el protocolo I2C.

[0053] El dispositivo principal de SGbus principal 612 continúa activando una señal de reloj en la SCL 216 con el SDA 218 liberado. El dispositivo ganador de entre los dispositivos de SGbus 614<sub>I</sub>-614<sub>n</sub>, 616<sub>I</sub>-616<sub>m</sub> puede transferir uno o más bytes característicos. El byte característico incluye información que identifica ciertas características del dispositivo ganador, incluyendo si el dispositivo funciona solo como dispositivo secundario, tipo de dispositivo (por ejemplo, acelerómetro), anchura de datos (por ejemplo, 16 o 12 bits de anchura) y otras características.

[0054] El dispositivo principal de SGbus principal 612 puede transferir una dirección local de 7 bits de anchura para el dispositivo ganador. Esta dirección incorpora el nivel de prioridad que el dispositivo principal de SGbus principal 612 asigna al dispositivo identificado. El dispositivo principal de SGbus principal 612 puede repetir este procedimiento hasta que no reciba respuesta de un dispositivo que busca el arbitraje de direcciones. El dispositivo principal de SGbus principal 612 puede terminar el procedimiento de arbitraje enviando un código de comando específico que termina el código de comando de asignación dinámica de direcciones que permitió la entrada en el procedimiento.

[0055] Un dispositivo principal de SGbus secundario 616<sub>I</sub>-616<sub>m</sub> conectado al bus compartido 602 puede supervisar el proceso de arbitraje y capturar el intercambio de información durante el proceso, de manera que el dispositivo principal de SGbus secundario 616<sub>I</sub>-616<sub>m</sub> tiene una copia de la información de direccionamiento, prioridad y configuración para el bus compartido 602. Sin embargo, el dispositivo principal de SGbus principal 612 puede transferir la información recibida desde los dispositivos secundarios de SGbus 614<sub>I</sub>-614<sub>n</sub> al dispositivo principal de SGbus secundario 616<sub>I</sub>-616<sub>m</sub>.

[0056] Cada uno de los dispositivos de SGbus 614<sub>1</sub>-614<sub>n</sub>, 616<sub>1</sub>-616<sub>m</sub> puede tener uno o más registros de retención que pueden ser utilizados para el almacenamiento de direcciones dinámicas, de tal manera que la configuración SGbus puede reservarse para el uso después de un encendido en frío. Si dos dispositivos de SGbus 614<sub>1</sub>-614<sub>n</sub> y/o 616<sub>1</sub>-616<sub>m</sub> seleccionan la misma dirección aleatoria de 48 bits y tienen el mismo byte característico, los dos dispositivos pueden almacenar la misma dirección local. La doble asignación puede permanecer vigente hasta que el dispositivo principal de SGbus 612 requiera una transferencia de datos y los datos transmitidos simultáneamente por los dos dispositivos secundarios de SGbus 614<sub>I</sub>-614<sub>n</sub> diferentes sean diferentes. Al menos uno de los dos dispositivos secundarios de SGbus 614<sub>I</sub>-614<sub>n</sub> puede reconocer que tiene la misma dirección que otro dispositivo secundario de SGbus 614<sub>I</sub>-614<sub>n</sub> conectado al bus compartido 602 y puede abandonar el bus compartido 602. En el siguiente estado de bus libre 822, el dispositivo secundario de SGbus abandonado 614-614n puede solicitar una nueva dirección local, utilizando el código de control dedicado para este requisito. Otros procedimientos para identificar asignaciones dobles de la misma dirección local pueden estar disponibles, incluidos los procedimientos existentes que pueden adaptarse de acuerdo con ciertos aspectos divulgados en el presente documento. Por ejemplo, un dispositivo principal o más importante puede ser informado de la cantidad de dispositivos que necesitan una dirección local, y si se asignan o conceden menos direcciones locales, el dispositivo principal más importante puede iniciar y/o realizar un procedimiento de recuperación. En un ejemplo de un procedimiento de recuperación, el procedimiento dinámico de asignación de

direcciones puede reiniciarse desde cero. Otros ejemplos de procedimientos de soporte fiables están disponibles para su uso en la recuperación de instancias donde dos o más dispositivos tienen direcciones duplicadas.

[0057] A cada uno de los dispositivos de SGbus 614<sub>I</sub>-614<sub>n</sub> y/o 616<sub>I</sub>-616<sub>m</sub> se le asigna un rango de prioridad por parte del dispositivo principal de SGbus principal 612. El rango de prioridad puede ser definido por el dispositivo principal de SGbus 612 usando el nivel de la dirección local asignada dinámicamente, por lo que los valores de dirección más bajos tienen rangos de prioridad más altos.

5

25

30

35

40

45

55

60

65

[0058] Cada uno de los dispositivos de SGbus 614<sub>I</sub>-614<sub>n</sub>, 616<sub>I</sub>-616<sub>m</sub> puede valer una solicitud de interrupción en banda (IRQ) en cualquier momento durante el estado de bus libre. El procedimiento de afirmación de IRQ corresponde a procedimientos similares utilizados para el arbitraje de bus en I2C y otras interfaces relacionadas con I2C. Sin embargo, de acuerdo con ciertos aspectos divulgados en el presente documento, se pueden emplear ciertos refinamientos y mejoras para los procedimientos de IRQ.

[0059] En un ejemplo, un dispositivo secundario de SGbus 614<sub>I</sub>-614<sub>n</sub> puede afirmar una IRQ en banda tirando de la SDA 218 hasta un estado bajo de señalización lógica. El dispositivo principal 612 de SGbus principal puede comenzar a conducir una señal de reloj en el SCL 216, mientras deja el SDA 218 sin conducir. El SDA 218 se puede tirar hacia el estado lógico de alta señalización. El dispositivo secundario de SGbus 614<sub>I</sub>-614<sub>n</sub> puede controlar el SDA 218 para transmitir su propia dirección. El dispositivo principal de SGbus principal 612 confirma la IRQ y luego realiza un INICIO repetido utilizando la dirección recibida desde el dispositivo secundario de SGbus 614<sub>I</sub>-614<sub>n</sub>. Se proporciona una condición de INICIO repetida 928 (véase la FIG. 9) conduciendo el cable de señal SDA 922 bajo, mientras que el cable de señal SCL 924 es alto durante un estado de bus ocupado, y cuando se esperaría una condición de PARADA 908. Los dispositivos 614<sub>I</sub>-614<sub>n</sub>, 616<sub>I</sub>-616<sub>m</sub> y/o 604<sub>I</sub>-604<sub>k</sub> pueden supervisar el bus para sus direcciones respectivas después de detectar una condición de INICIO repetida 928.

[0060] El dispositivo principal de SGbus principal 612 puede configurar opcionalmente el modo de transferencia de datos utilizando el byte de protocolo de transferencia de datos, si el modo previamente definido es diferente de un modo actualmente deseado o requerido. A continuación, el dispositivo principal de SGbus principal 612 y el dispositivo secundario de SGbus de interrupción 614i-614n pueden comenzar a comunicarse. La contención del bus se lleva a cabo durante la evaluación de la dirección, y cualquier dispositivo de SGbus adicional 614i-614n, 616i-616m y cualquier dispositivo I2C heredado 604i-604k que intente ganar el bus al mismo tiempo perderá el arbitraje y puede volver a intentarlo en el siguiente estado de bus libre 822.

[0061] En otro ejemplo, el dispositivo principal de SGbus secundario 616i-616m puede afirmar una IRQ dentro de banda usando un procedimiento que es similar a la de los dispositivos secundarios de SGbus 614i-614n. Cuando el dispositivo principal de SGbus principal 612 reconoce que la IRQ es confirmada por un dispositivo principal de SGbus secundario de 616i-616m, el dispositivo principal 612 de SGbus principal libera el SCL 216 y el dispositivo principal de SGbus secundario de 616i-616m realiza una condición de INICIO repetido inmediato 928 para dirigirse a un dispositivo objetivo para la comunicación.

[0062] En otro ejemplo, un dispositivo principal I2C heredado 606 puede hacer valer una IRQ en un procedimiento que es similar a la descrita para los dispositivos principales SGbus secundarios 616i-616m. El dispositivo principal I2C heredado 606 típicamente no es consciente de cuándo compite con un dispositivo principal de SGbus 612, ya que el dispositivo principal de SGbus 612 tiene una dirección superior equivalente (por ejemplo, 111 1111) y perdería el arbitraje. Se apreciará que en ciertas aplicaciones puede ser deseable excluir los dispositivos heredados más lentos, como los dispositivos I2C, de SGbus. Por ejemplo, los dispositivos heredados pueden ser excluidos debido a la velocidad del bus (requisitos de rendimiento) o debido a la complejidad de los procedimientos necesarios para permitir la coexistencia.

[0063] Un dispositivo principal de SGbus principal 612 que inicia una transacción de comunicación evalúa el procedimiento de arbitraje de dirección, durante una llamada de dirección. Cualquier dispositivo secundario de SGbus 614-614n, dispositivo principal de SGbus secundario 616-616m o dispositivo principal I2C heredado 606 que intenta interrumpir el dispositivo principal de SGbus principal 612 típicamente tiene éxito. Sin embargo, cualquier dispositivo que tenga un rango de prioridad más bajo puede tener que esperar al próximo estado de bus libre 822.

[0064] En algunos casos, puede haber una competencia entre un dispositivo principal I2C heredado 606 y un dispositivo secundario de SGbus 614<sub>I</sub>-614<sub>n</sub>. El dispositivo principal de SGbus principal 612 inicia la señal de reloj en el SCL 216 cuando ve una condición de INICIO (es decir, cuando el SDA 218 baja). En consecuencia, un dispositivo secundario de SGbus 614<sub>I</sub>-614<sub>n</sub> que tiene un rango de prioridad más alto presumiblemente gana el proceso de arbitraje. El dispositivo principal de SGbus principal 612 es consciente del resultado del proceso de arbitraje, incluida la dirección ganadora.

[0065] De acuerdo con ciertos aspectos divulgados en el presente documento, un SGbus puede ser un bus multi-dominado en el que uno o más dispositivos principales de SGbus 612, 616i-616m y un dispositivo principal I2C heredado 606 proporcionan funciones de control y de gestión de bus para los dispositivos secundarios correspondientes. Ciertos procedimientos de control de bus y arbitraje de múltiples dispositivos principales empleados

en un SGbus pueden seguir una regla global tal como se describe para los procedimientos de IRQ. Por consiguiente, las reglas I2C pueden aplicarse cuando un dispositivo principal I2C heredado 606 compite con uno o más dispositivos principales secundarios de SGbus de 616-616<sub>m</sub>.

5 [0066] Cuando un dispositivo principal secundario de SGbus 616<sub>I</sub>-616<sub>m</sub> adquiere el control de bus compartido 602 para llevar a cabo una transacción, el dispositivo principal de SGbus secundario 616<sub>I</sub>-616<sub>m</sub> mantiene el control del bus compartido 602 solamente durante el tiempo que se requiera para realizar la transacción. Después de la transacción respectiva, una condición de PARADA 820 hace que el control del bus regrese al dispositivo principal de SGbus principal 612.

10

15

20

25

30

35

50

55

[0067] Un dispositivo principal I2C heredado 606 en general transfiere datos a los dispositivos secundarios I2C heredados 604i-604k, y emplea protocolos compatibles con I2C, incluso cuando otros protocolos de transferencia de datos, tales como el protocolo de transferencia de datos CCIe están disponibles. Las comunicaciones entre un dispositivo principal I2C heredado 606 y los dispositivos de SGbus 614i-614n, 616i-616m se pueden gestionar a nivel del sistema. En un ejemplo, el dispositivo principal de SGbus principal 612 puede informar al dispositivo principal I2C heredado 606 de la presencia de los dispositivos secundarios de SGbus 614i-614n. El dispositivo principal de SGbus principal 612 puede proporcionar información sobre las direcciones locales y las características de los dispositivos secundarios de SGbus 614i-614n. Cualquier comunicación resultante entre el dispositivo principal I2C heredado 606 y los dispositivos secundarios de SGbus 614i-614n puede ser coherente con los protocolos I2C.

[0068] De acuerdo con ciertos aspectos divulgados en el presente documento, un SGbus puede soportar una capacidad de conexión rápida en la que un dispositivo de SGbus 612, 614<sub>I</sub>-614<sub>n</sub>, o 616<sub>I</sub>-616<sub>m</sub> se puede insertar en un bus 602 que ya se haya configurado dinámicamente y esté en funcionamiento. Un dispositivo de SGbus 612, 614<sub>I</sub>-614<sub>n</sub>, o 616<sub>I</sub>-616<sub>m</sub> con conexión rápida se enciende en el bus y asume una condición similar a un encendido en frío, y el dispositivo de SGbus 612, 614<sub>I</sub>-614 con conexión rápida 612, 614<sub>I</sub>-614<sub>n</sub>, o 616<sub>I</sub>-616<sub>m</sub> inicialmente no tiene una dirección local asignada. Un dispositivo 612, 614<sub>I</sub>-614<sub>n</sub>, o 616<sub>I</sub>-616<sub>m</sub> que no tiene una dirección local asignada puede realizar una IRQ utilizando un byte predefinido como indicador de que necesita una dirección local. Al detectar la IRQ y la presencia en el bus compartido 602 del dispositivo de SGbus de conexión rápida 612, 614<sub>I</sub>-614<sub>n</sub>, o 616<sub>I</sub>-616<sub>m</sub>, el dispositivo principal de SGbus principal 612 puede realizar un procedimiento dinámico de asignación de direcciones, tal como se describe en el presente documento.

[0069] De acuerdo con ciertos aspectos divulgados en el presente documento, un SGbus puede soportar una pluralidad de protocolos de transferencia de datos, incluidos los protocolos I2C, protocolos CCI y variantes de los mismos, y otros protocolos. En un ejemplo, se puede usar un bus de extensión CCI (CCIe) para proporcionar un transporte de datos en el SGbus. Las comunicaciones CCIe e I2C pueden realizarse en el bus compartido 602, de manera que en un primer intervalo de tiempo, los datos pueden transmitirse utilizando la codificación CCIe y otros datos pueden transmitirse en un intervalo de tiempo diferente de acuerdo con las convenciones de señalización I2C. El SGbus emplea protocolos de capa física que garantizan que las transmisiones CCIe no violen los protocolos I2C.

40 [0070] La FIG. 9 incluye diagramas de temporización 900 y 920 que ilustran el tiempo asociado con múltiples transmisiones de datos en un bus I2C. En un primer ejemplo básico, el período de tiempo (el período de inactividad 914) que transcurre entre una condición de PARADA 908 y una condición de INICIO consecutiva 910 puede prolongarse, haciendo que el bus I2C convencional esté inactivo durante este período de inactividad 914. En funcionamiento, un período ocupado 912 comienza cuando el dispositivo principal de bus I2C transmite una primera condición de INICIO 906, seguida de datos. El período ocupado 912 finaliza cuando el dispositivo principal de bus I2C transmite una condición de PARADA 908 y se produce un período de inactividad 914. El período de inactividad 914 finaliza con la transmisión de una segunda condición de INICIO 910.

[0071] Con referencia también al diagrama de temporización 920, en algunos casos, los períodos de reposo 914 entre sucesivas transmisiones de datos en el bus I2C pueden reducirse en número o eliminarse mediante la transmisión de una condición de INICIO repetida (Sr) 928 en lugar de un estado de PARADA 908. La repetida condición de INICIO 928 termina la transmisión de datos precedente e indica simultáneamente el comienzo de una próxima transmisión de datos. La transición de estado en el cable de señal SDA 922 es idéntica para una condición de INICIO 926 que se produce después de un período de inactividad 930 y la condición de INICIO repetida 928. Específicamente, el cable de señal SDA 922 pasa de alto a bajo, mientras que el cable de señal SCL 924 es alto. Cuando se usa una condición de INICIO 928 repetida entre las transmisiones de datos, un primer período de ocupado 932 es seguido inmediatamente por un segundo período de ocupado 934.

[0072] En un SGbus, el segmento de transferencia de datos puede utilizar cualquier I2C, CCIe u otro protocolo de codificación de transición, o variantes de los mismos. El tipo de protocolo de transferencia de datos que se utilizará puede ser indicado por el dispositivo principal de SGbus 612, o 616<sub>I</sub>-616<sub>m</sub>, al comienzo de la comunicación con un dispositivo secundario de SGbus 614<sub>I</sub>-614<sub>n</sub>. La selección de un protocolo de transferencia de datos para cada dispositivo secundario de SGbus 614<sub>I</sub>-614<sub>n</sub> permanece vigente hasta que sea modificada por el dispositivo principal de SGbus 612, o 616<sub>I</sub>-616<sub>m</sub>. En algunos casos, el dispositivo principal de SGbus principal 612 puede configurar cualquier dispositivo que pueda comunicarse en los modos I2C y CCIe para usar el modo I2C como modo predeterminado.

[0073] Una salida de la transferencia de datos se puede efectuar mediante la inserción de una condición de PARADA 820, 908 en el bus compartido 602, en cuyo caso el bus compartido 602 puede entrar en un estado bus libre 822. Ciertas secuencias de símbolos transmitidos en una transacción en el bus compartido 602 pueden producir estados de señalización que pueden identificarse como una condición de PARADA 820, 908 o una condición de INICIO repetida 928 mediante la lógica de detección de uno o más dispositivos 604-604n, 614-614n, 616-616m que no son participantes en la transacción.

[0074] La FIG. 10 ilustra la aparición de condiciones de INICIO no deseadas 1008 y de PARADA no deseadas 1012, que pueden surgir durante el intercambio normal de datos y/o debido a los problemas de metaestabilidad ilustrados en la lógica síncrona. Las condiciones de PARADA no deseadas 1012 y las condiciones de INICIO no deseadas 1008 pueden evitarse configurando el codificador para identificar secuencias de símbolos que pueden ocasionar las condiciones de PARADA no deseadas 1012 y las condiciones de INICIO no deseadas 1008. El codificador puede modificar el flujo de símbolos transmitidos para evitar generar las condiciones de PARADA no deseadas y no intencionadas 1012 y/o las condiciones de INICIO no deseadas 1008. En un ejemplo, el protocolo de codificación puede proporcionar una inserción del símbolo ficticio "00" binario después de cualquier símbolo "01" binario para evitar las condiciones de PARADA no deseadas 1012 mientras se encuentra en el modo de transferencia de datos. En otro ejemplo, el protocolo de codificación puede proporcionar una inserción del símbolo ficticio "10" binario después de cualquier aparición de un símbolo "11" binario para evitar las condiciones de INICIO 1008 no deseadas, lo cual puede hacer que un dispositivo I2C heredado compruebe su dirección después de una condición de INICIO falsa o no deseada 1008. Se apreciará que el dispositivo I2C heredado puede responder a una condición de INICIO falsa o no deseada 1008 si encuentra una coincidencia de dirección y, por lo tanto, afecta adversamente a los controladores activos de CCIe.

[0075] En las transferencias de datos en modo CCIe, la sincronización de trama puede realizarse basándose en un recuento de los símbolos transmitidos en el bus compartido 602, comenzando con el primer símbolo enviado después del punto de entrada en el modo de transferencia de datos. Para operaciones SGbus, no es necesario enviar una condición de INICIO repetida 928 delante de cada secuencia de 12 símbolos o secuencia de 20 símbolos en la trama. La ausencia de la condición de INICIO repetida 928 puede aumentar el rendimiento de los datos.

[0076] En algunos casos, la sincronización de trama se puede verificar adicionalmente mediante la comprobación de los últimos tres bits menos significativos (LSB), "000", que se utilizan para la detección de errores. Se puede detectar un solo error al verificar los últimos tres LSB del número descodificado binario. El error único puede estar relacionado con un error de símbolo en cualquier palabra de 12 símbolos, donde no hay dos símbolos consecutivos que sean idénticos. Los símbolos pueden codificarse como números binarios [SDA: SCL], donde el bit correspondiente al estado de señalización del SDA 218 se encuentra en la posición del bit más significativo (MSB). Un error de símbolo puede ser el resultado de un error en el estado de señalización muestreado de uno o ambos, el SDA 218 o el SCL 216.

[0077] Con referencia a la FIG. 11, y como se analizó en relación con las FIGs. 3 y 4, los números ternarios generados por un transcodificador 302 de un transmisor 300 pueden representarse como un valor de desplazamiento en y a través de un círculo 402. En un ejemplo, un desplazamiento en el sentido horario puede representarse como un valor ternario T=1, un desplazamiento en el sentido antihorario puede representarse como un valor ternario T=0, y un desplazamiento a través del círculo 402 (es decir, 2 pasos en el sentido horario o en sentido antihorario) se representará como un valor ternario T=2.

[0078] Como consecuencia inmediata, un error de línea que produce un símbolo idéntico a cualquiera de los símbolos adyacentes en el círculo 402 no se considera un nuevo símbolo, y el error puede identificarse a nivel de palabra. Sin embargo, un solo error de símbolo que da como resultado la modificación de dos números ternarios adyacentes.

[0079] De acuerdo con ciertos aspectos divulgados en el presente documento, se puede proporcionar corrección de errores para las comunicaciones SGbus. Para transferir datos, la cadena de información binaria se puede transformar en un valor numérico igual, codificado como un número base 3 (ternario). Como tal, es necesario que se transmitan menos caracteres entre los nodos para la misma información. Los números ternarios transformados son una suma polinomial, donde los factores son la potencia de 3 y los coeficientes son [0, 1, 2].

$$\sum_{i=0}^{mbinario} B_i 2^i = \sum_{k=0}^{mternario} T_k 3^k$$

donde:  $T_k$  = coeficientes ternarios,  $\in$  [0, 1, 2].

5

10

15

20

30

35

40

45

55

60 **[0080]** Un error de símbolo puede producir una alteración de dos valores de *Tκ* adyacentes, y la suma final puede ser alterada por la fórmula:

$$\pm a \times 3^n \pm b \times 3^{(n-1)} \tag{1}$$

donde:

5

10

15

20

25

"n" = el rango del símbolo erróneo, y

"a" y "b" son coeficientes de diferencia.

[0081] Los "a" y "b" coeficientes respetan lo siguiente:

$$a \in [0, \pm 1, \pm 2]$$

$$b \in [0, \pm 1, \pm 2]$$

[0082] La fórmula (1) se puede escribir como:

$$(\pm 3a \pm b) \times 3^{(n-1)} \tag{2}$$

[0083] Con el fin de que los últimos bits de la LSB se dejen sin cambios por el error, la fórmula (2) debe ser un múltiplo de la potencia de 2. El primer rango de potencia de 2 que no es un múltiplo entero denota cuántos bits finales de LSB deben conocerse de antemano para que se identifique un error de símbolo. El factor 3<sup>(n-1)</sup> es un múltiplo de 3 y cambiará los bits LSB, si no se modifican.

[0084] Un análisis del factor relevante (±3a ±b) puede basarse en la observación de que el diagrama de codificación de símbolo a ternario tiene una simetría circular. Por lo tanto, un análisis de un punto cubre los cuatro puntos. Por ejemplo, si "2" es el símbolo correcto, entonces para cualquier otra situación de símbolo correcto, es suficiente reemplazar las posiciones respectivas por sus valores rotados. La Tabla 1 a continuación muestra los posibles coeficientes "a" resultantes, y la Tabla 2 muestra los posibles coeficientes "b" resultantes.

Tabla 1

30

35

| Símbolo correcto | Símbolo<br>pasado | Ternario<br>correcto | Símbolo de<br>ERROR | Ternario de<br>ERROR | Coeficiente de ERROR "a" |

|------------------|-------------------|----------------------|---------------------|----------------------|--------------------------|

| 2                | 1                 | 1                    | 3                   | 2                    | 1                        |

|                  |                   |                      | 0                   | 0                    | -1                       |

|                  | 0                 | 2                    | 3                   | 0                    | -2                       |

|                  |                   |                      | 1                   | 1                    | -1                       |

|                  | 3                 | 0                    | 1                   | 2                    | 2                        |

|                  |                   |                      | 0                   | 1                    | 1                        |

Tabla 2

| Símbolo correcto | Nuevo<br>símbolo | Ternario<br>correcto | Símbolo de<br>ERROR | Ternario de<br>ERROR | Coeficiente de ERROR "b" |

|------------------|------------------|----------------------|---------------------|----------------------|--------------------------|

| 2                | 1                | 0                    | 3                   | 2                    | 2                        |

|                  |                  |                      | 0                   | 1                    | 1                        |

|                  | 0                | 2                    | 3                   | 1                    | -1                       |

|                  |                  |                      | 1                   | 0                    | -2                       |

|                  | 3                | 1                    | 1                   | 2                    | 1                        |

|                  |                  |                      | 0                   | 0                    | -1                       |

[0085] La tabla 3 a continuación muestra las posibles combinaciones resultantes de los coeficientes "a" y "b".

Tabla 3

| Símbolo correcto | Símbolo de ERROR | а  | а  | b  | b  |

|------------------|------------------|----|----|----|----|

| 2                | 3                | 1  | -2 | 2  | -1 |

|                  | 1                | -1 | 2  | -2 | 1  |

|                  | 0                | -1 | 1  | 1  | -1 |

[0086] Los posibles pares (a; b) se muestran en la misma fila de fondo, en relación con el mismo posible "símbolo de ERROR". Una inspección directa revela que hay combinaciones que harán, respectivamente:

$$(\pm 3a \pm b) = 2$$

, por ejemplo (1;-1) y (-1;1),

$$(\pm 3a \pm b) = 4$$

, por ejemplo (-2;2) y (2;-2),

No hay pares que produzcan ( $\pm 3$  a  $\pm b$ ) = 8; eso hubiera sido posible solo para (2; 2) o (-2;-2).

5

10

15

20

25

30

35

50

55

[0087] Por lo tanto, cualquiera de los conocidos tres bits en el extremo de LSB puede detectar cualquier error de símbolo individual. Por ejemplo, se puede usar "000", aunque otros tres bits conocidos pueden desempeñar el mismo papel. Cualquier error en el SDA 218, o el SCL 216 puede detectarse mediante los últimos tres bits.