# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 697 473

51 Int. Cl.:

H03L 7/091 (2006.01) G01R 19/25 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 14.10.2015 PCT/EP2015/073735

(87) Fecha y número de publicación internacional: 21.04.2016 WO16059088

(96) Fecha de presentación y número de la solicitud europea: 14.10.2015 E 15781336 (1)

(97) Fecha y número de publicación de la concesión europea: 20.06.2018 EP 3207634

(54) Título: Procedimiento de detección de fases que se basa en una pluralidad de valores consecutivos de una señal de recepción

(30) Prioridad:

14.10.2014 DE 102014015127

Fecha de publicación y mención en BOPI de la traducción de la patente: **24.01.2019**

(73) Titular/es:

SONOVUM AG (100.0%) Perlickstr. 5 04103 Leipzig, DE

(72) Inventor/es:

WROBEL, MIROSLAW y KOLANY, ADAM

(74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

#### **DESCRIPCIÓN**

Procedimiento de detección de fases que se basa en una pluralidad de valores consecutivos de una señal de recepción

La presente invención se refiere a un procedimiento de detección de fases y a un procesador para determinar una fase de una señal de recepción que se basa en una pluralidad de valores consecutivos de una señal de recepción.

La determinación precisa de la fase de una señal de salida en la salida de un medio de transmisión durante la estimulación en la entrada con una señal de entrada de frecuencia conocida es importante para una pluralidad de aplicaciones. Por ejemplo, la información de fase en procedimientos de codificación de la ingeniería de telecomunicación puede aprovecharse para transmitir mensajes en forma de señales eléctricas, magnéticas o electromagnéticas a través de un canal de comunicación. En el ámbito de la ciencia de los materiales, la medición de la fase de una onda acústica proporciona información sobre las propiedades del material del medio de transmisión. En sistemas de análisis químicos y físicos, se aprovechan detectores de fases para determinar temperatura, densidad, cambios de fase de reacciones químicas, dimensiones del objeto y concentración de líquido en medios químicos y físicos. En procedimientos de diagnóstico médico, las propiedades de los tejidos se determinan por medición de la fase de señales ultrasónicas y acústicas acopladas. Aplicaciones para ello son la supervisión de la circulación sanguínea en el cuerpo para detectar estados patológicos, en particular en el cerebro, y la ecografía mamaria.

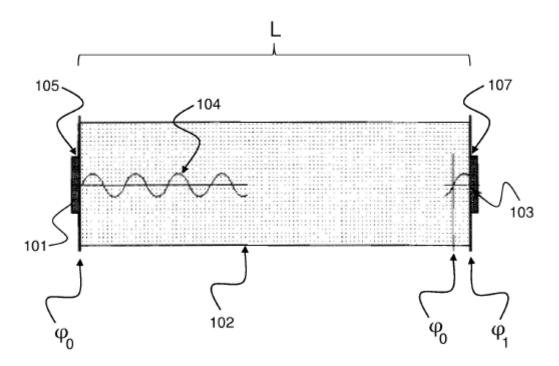

La fig. 1 muestra una representación esquemática de un sistema 100 para medir relaciones de fase de ondas acústicas en un vaso 102. El sistema 100 comprende un vaso 102 que va a medirse, por ejemplo, una célula somática, un vaso sanguíneo o una vena con una longitud de vaso L y un emisor 101 y receptor 103 de ondas ultrasónicas. El emisor 101 acopla una onda ultrasónica 104 de una frecuencia  $f_0$  conocida con fase  $\phi_0$  en una entrada 105 del vaso 102 en el vaso 102, donde se propaga y se recibe en la salida 107 por el receptor 103. Como puede verse por la fig. 1, la onda ultrasónica 104 presenta en el vaso 102 un número entero de períodos de oscilación P así como un período parcial, que puede representarse como diferencia de fase  $\phi_1$  -  $\phi_0$ . Entre el tiempo de propagación  $T_0$  de la onda acústica 104 y la diferencia de fase  $\phi_1$  -  $\phi_0$ , se aplica la siguiente relación:

$$2\pi \cdot f_0 T_P = 2\pi P + (\varphi_1 - \varphi_0) \tag{1}$$

Para la velocidad de fase V en el vaso 102 se aplica, por una parte, la relación

5

10

15

20

25

30

35

45

50

$$V = \lambda \cdot f_0 \,, \tag{2}$$

designando  $f_0$  la frecuencia de emisión conocida y designando  $\lambda$  la longitud de onda en el vaso 102. Por otra parte, para la velocidad de fase V en el vaso 102, se aplica la relación

$$V = \sqrt{\frac{K}{\rho}} , \qquad (3)$$

indicando K la elasticidad del vaso e indicando  $\rho$  su densidad. Por lo tanto, a partir de la velocidad de fase V se pueden determinar las propiedades del vaso 102. La longitud de onda  $\lambda$  se puede determinar a partir del número de los períodos P y de la diferencia de fase  $\varphi_1$ - $\varphi_0$ , y la velocidad de fase V se puede calcular mediante la frecuencia de emisión  $f_0$  conocida con la que se pueden caracterizar las propiedades del material del vaso 102.

Habitualmente, para determinar la diferencia de fase  $\varphi_1$ - $\varphi_0$ , el receptor se sincroniza con el emisor y la señal recibida se explora a través de un convertidor analógico-digital. El valor de exploración de la señal recibida puede relacionarse con el momento de sincronización y de ello se puede determinar la diferencia de fase. No obstante, la precisión de medición depende de una pluralidad de parámetros del sistema como, por ejemplo, la precisión de la exploración, la precisión del ajuste de frecuencia de la señal de emisión, la precisión del acoplamiento y desacoplamiento de la señal acústica, interferencias de la señal de emisión a causa de reflexiones en los extremos del vaso y en los lados del vaso, efectos Doppler, etc. El documento «WO 2011/107801 A1» revela un procedimiento de detección de fases y un procesador de acuerdo con el preámbulo de las respectivas reivindicaciones 1 y 7. El objetivo de la presente invención es crear un concepto para una determinación sencilla y precisa de la fase en la salida de un medio de transmisión durante la estimulación con una señal de emisión de característica de señal conocida.

Este objetivo se resuelve por las características de las reivindicaciones independientes. Perfeccionamientos ventajosos son objeto de las reivindicaciones dependientes.

Los procedimientos, dispositivos y sistemas presentados en lo sucesivo pueden ser de distintos tipos. Los elementos individuales descritos pueden estar realizados por componentes de *hardware* o de *software*, por ejemplo, componentes electrónicos que pueden prepararse por distintas tecnologías y comprender, por ejemplo, chips semiconductores, circuitos integrados para aplicaciones específicas (ASIC, por sus siglas en inglés),

## ES 2 697 473 T3

microprocesadores, procesadores de señales digitales, circuitos eléctricos integrados, circuitos electroópticos y/o elementos constructivos pasivos.

De acuerdo con un primer aspecto, la invención se refiere a un procedimiento de detección de fases, con las siguientes etapas: recepción de una pluralidad de valores consecutivos de una señal de recepción con frecuencia de exploración f<sub>s</sub> conocida como reacción a una señal de emisión con frecuencia de emisión f<sub>w</sub> conocida; determinación de dos valores diferenciales a partir de respectivamente dos valores consecutivos de tres valores consecutivos de la señal de recepción; y determinación de una parte real de fase y de una parte imaginaria de fase de la señal de recepción que se basa en una relación lineal entre la parte real de fase, la parte imaginaria de fase y los dos valores diferenciales.

- Esto tiene la ventaja de que la fase puede determinarse de manera sencilla y precisa en la salida de un medio de transmisión durante la estimulación con una señal de emisión de característica de señal conocida. En el caso de la frecuencia de emisión y frecuencia de exploración conocidas, la relación lineal entre la parte real de fase, la parte imaginaria de fase y los dos valores diferenciales puede determinarse con poco esfuerzo y ofrece valores precisos para la fase de la señal de recepción.

- De acuerdo con una forma de realización del procedimiento de detección de fases, la relación lineal entre la parte real de fase, la parte imaginaria de fase y los dos valores diferenciales puede representarse por un sistema de ecuaciones lineal bidimensional que se basa en los dos valores diferenciales como variables de entrada y la parte real de fase y la parte imaginaria de fase como variables de salida.

- Esto tiene la ventaja de que el sistema de ecuaciones lineal bidimensional puede resolverse fácilmente y los términos para la parte real de fase y la parte imaginaria de fase pueden representarse de manera sencilla y, con ello, determinarse de manera sencilla. Por lo tanto, la fase puede determinarse de modo exacto con poco esfuerzo.

25

30

De acuerdo con una forma de realización del procedimiento de detección de fases, el sistema de ecuaciones lineal se resuelve por ponderación de las variables de entrada con coeficientes de Fourier, que se basan en una frecuencia angular  $\Omega$ , dependiendo la frecuencia angular conocida de la frecuencia de emisión y de la frecuencia de exploración.

Esto tiene la ventaja de que, en el caso de los valores conocidos de la frecuencia de emisión  $f_w$  y de la frecuencia de exploración  $f_s$ , el sistema de ecuaciones lineal se puede resolver de manera sencilla mediante los coeficientes de Fourier.

De acuerdo con una forma de realización del procedimiento de detección de fases, la frecuencia angular conocida satisface la relación  $\Omega=2\pi(f_w/f_s)$ .

De acuerdo con una forma de realización, el procedimiento de detección de fases comprende la determinación de los coeficientes de Fourier dependiendo de la frecuencia angular  $\Omega=2\pi(f_w/f_s)$  conocida antes de la determinación de la parte real de fase y de la parte imaginaria de fase de la señal de recepción (Y).

Esto tiene la ventaja de que, en el caso de los valores conocidos de la frecuencia de emisión f<sub>w</sub> y de la frecuencia de exploración f<sub>s</sub>, los coeficientes de Fourier pueden determinarse ya de antemano y pueden almacenarse como parámetros, de manera que el procedimiento puede llevarse a cabo de modo muy eficiente.

De acuerdo con una forma de realización, el procedimiento de detección de fases comprende una determinación de un bias de la señal de recepción que se basa en una relación lineal entre la parte real de fase, la parte imaginaria de fase, el bias y los tres valores consecutivos de la señal de recepción.

- Esto tiene la ventaja de que el bias puede determinarse de manera sencilla y precisa en la salida del medio de transmisión durante la estimulación con una señal de emisión de característica de señal conocida. En el caso de la frecuencia de emisión y frecuencia de exploración conocidas, la relación lineal entre la parte real de fase ya determinada, la parte imaginaria de fase ya determinada, el bias y los dos valores diferenciales puede determinarse con poco esfuerzo y ofrece valores precisos para el bias de la señal de recepción.

- De acuerdo con un segundo aspecto, la invención se refiere a un procesador para determinar una fase de una señal de recepción, recibida como reacción a una señal de emisión con frecuencia de emisión f<sub>w</sub> conocida, con frecuencia de exploración f<sub>s</sub> conocida, con: un primer, segundo y tercer registro de entrada, que están diseñados para almacenar respectivamente uno detrás de otro tres valores consecutivos de una pluralidad de valores consecutivos de la señal de recepción; un primer y segundo registro interno, que están diseñados para almacenar un primer valor diferencial como diferencia del contenido del segundo registro de entrada y del contenido del primer registro de entrada y un segundo valor diferencial como diferencia del contenido del tercer registro de entrada y del contenido del segundo registro de entrada; un primer y segundo registro de salida, que están diseñados para facilitar una parte real de fase y una parte imaginaria de fase de la señal de recepción; y una unidad aritmético-lógica, que está diseñada para determinar la parte real de fase y la parte imaginaria de fase de la señal de recepción que se basa en una relación lineal entre la parte real de fase, la parte imaginaria de fase y los dos valores diferenciales.

Esto tiene la ventaja de que el procesador puede determinar de manera sencilla y precisa la fase en la salida de un medio de transmisión durante la estimulación con una señal de emisión de característica de señal conocida. En el caso de la frecuencia de emisión y frecuencia de exploración conocidas, el procesador puede determinar la relación lineal entre la parte real de fase, la parte imaginaria de fase y los dos valores diferenciales con poco esfuerzo y, por lo tanto, puede ofrecer valores precisos para la fase de la señal de recepción.

De acuerdo con una forma de realización, el procesador comprende un tercer registro de salida, que está diseñado para facilitar un bias de la señal de recepción, estando diseñada la unidad aritmético-lógica para determinar el bias de la señal de recepción que se basa en una relación lineal entre la parte real de fase, la parte imaginaria de fase, el bias y los tres valores consecutivos de la señal de recepción.

- Esto tiene la ventaja de que el procesador puede determinar de manera sencilla y precisa el bias en la salida del medio de transmisión durante la estimulación con una señal de emisión de característica de señal conocida. En el caso de la frecuencia de emisión y frecuencia de exploración conocidas, el procesador puede determinar la relación lineal entre la parte real de fase ya determinada, la parte imaginaria de fase ya determinada, el bias y los dos valores diferenciales con poco esfuerzo y puede ofrecer valores precisos para el bias de la señal de recepción.

- De acuerdo con una forma de realización, el procesador comprende un primer, segundo, tercer y cuarto registro de coeficientes, que están diseñados para almacenar coeficientes de Fourier, determinando los coeficientes de Fourier la relación lineal entre la parte real de fase, la parte imaginaria de fase y los dos valores diferenciales.

- Esto tiene la ventaja de que, en el caso de los valores conocidos de la frecuencia de emisión f<sub>w</sub> y de la frecuencia de exploración f<sub>s</sub>, el procesador puede determinar de manera sencilla la relación lineal mediante los coeficientes de Fourier y, por lo tanto, puede calcular de modo eficiente la fase.

20

25

30

35

50

De acuerdo con una forma de realización, el procesador comprende una primera memoria de parámetros, que está diseñada para almacenar el coseno de la mitad de una frecuencia angular  $\Omega$  conocida, que depende de la frecuencia de emisión y de la frecuencia de exploración; una segunda memoria de parámetros, que está diseñada para almacenar el seno de la mitad de la frecuencia angular  $\Omega$  conocida; una tercera memoria de parámetros, que está diseñada para almacenar el coseno de la frecuencia angular  $\Omega$  conocida; y una cuarta memoria de parámetros, que está diseñada para almacenar el seno de la frecuencia angular  $\Omega$  conocida.

Esto tiene la ventaja de que el procesador puede calcular ya de antemano las magnitudes necesarias para la determinación de la relación lineal y puede almacenarlas en las cuatro memorias de parámetros, o que estas magnitudes ya se han calculado externamente y están presentes en las cuatro memorias de parámetros al iniciar el procesador. Con ello, la determinación de la fase puede realizarse de manera muy eficiente.

De acuerdo con una forma de realización del procesador, la frecuencia angular conocida satisface la relación  $\Omega=2\pi(f_w/f_s)$ .

De acuerdo con una forma de realización del procesador, la unidad aritmético-lógica está diseñada para determinar la parte real de fase y la parte imaginaria de fase de la señal de recepción que se basa en los contenidos de los cuatro registros de coeficientes y los contenidos de las cuatro memorias de parámetros.

Esto tiene la ventaja de que la unidad aritmético-lógica para determinar la fase puede trabajar con magnitudes ya determinadas y presentes en los correspondientes registros, de manera que el procesador puede realizar la determinación de la fase con poco esfuerzo de cálculo.

- De acuerdo con una forma de realización, el procesador comprende una unidad de instrucción, que está diseñada para inicializar, en respuesta a una señal de reposición, el primer registro de coeficientes con el contenido de la primera memoria de parámetros y el segundo registro de coeficientes con el contenido de la segunda memoria de parámetros; y para restaurar, en respuesta a una señal de reloj, el primer registro de coeficientes con el contenido del tercer registro de coeficientes y el segundo registro de coeficientes con el contenido del cuarto registro de coeficientes.

- Esto tiene la ventaja de que el procesador puede desplazarse a un estado inicial predefinido por la señal de reposición y puede llevar a cabo una determinación de la fase en cada reloj, de manera que la fase puede determinarse de manera muy precisa y rápida.

- De acuerdo con una forma de realización del procesador, la unidad de instrucción está diseñada para cargar, en respuesta a la señal de reloj, el cuarto registro de coeficientes con el valor  $C_1wS + S_1wC$  y para cargar el tercer registro de coeficientes con el valor  $C_1wC S_1wS$ , indicando wS el contenido de la cuarta memoria de parámetros, indicando wC el contenido de la tercera memoria de parámetros, indicando  $C_1$  el contenido del primer registro de coeficientes, indicando  $S_1$  el contenido del segundo registro de coeficientes y designando  $\Omega$  la frecuencia angular  $\Omega = 2\pi (f_w/f_s)$  conocida.

- Esto tiene la ventaja de que el procesador puede determinar rápidamente la fase por las sencillas reglas de actualización  $C_1wS + S_1wC$  y  $C_1wC S_1wS$ , que pueden realizarse mediante operaciones de multiplicación y adición

en cada reloj.

15

20

55

De acuerdo con una forma de realización del procesador, la unidad aritmético-lógica está diseñada para determinar

$\text{la parte real de fase como} \quad \frac{\Delta Y_1 \cdot S_2 - \Delta Y_2 \cdot S_1}{4hS \cdot hS \cdot hC} \quad \text{y la parte imaginaria de fase como} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad hS \quad \text{el} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \text{, indicando} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_2}{4hS \cdot hC} \quad \frac{\Delta Y_1 \cdot$

contenido de la segunda memoria de parámetros, indicando hC el contenido de la primera memoria de parámetros, indicando  $C_2$  el contenido del tercer registro de coeficientes, indicando  $S_2$  el contenido del cuarto registro de coeficientes y designando  $\Omega$  la frecuencia angular  $\Omega=2\pi(f_w/f_s)$  conocida.

Esto tiene la ventaja de que el procesador puede calcular la fase por ecuaciones sencillas anteriormente designadas, que la unidad aritmético-lógica puede determinar rápidamente mediante operaciones de multiplicación y adición y una normalización con factor de escala.

De acuerdo con una forma de realización del procesador, la unidad aritmético-lógica está diseñada para determinar el bias como  $Y_2$  - $(U \cdot (S_1hC + C_1hS) + V \cdot (C_1hC - S_1hS))$ , indicando U la parte real de fase, indicando V la parte imaginaria de fase e indicando  $Y_2$  el contenido del segundo registro de entrada.

Esto tiene la ventaja de que el procesador puede calcular el bias por la ecuación sencilla anteriormente designada, que la unidad aritmético-lógica puede determinar rápidamente mediante operaciones de multiplicación y adición y de almacenamiento.

De acuerdo con una forma de realización, el procesador comprende un primer registro auxiliar, un segundo registro auxiliar; y un contador, que se incrementa con cada restauración de los tres registros de entrada dependiendo de la señal de reloj, estando diseñada la unidad aritmético-lógica para determinar la parte real de fase como  $\Delta Y_1S_2$  -  $\Delta Y_2S_1$  y la parte imaginaria de fase como  $\Delta Y_1$   $C_2$  -  $\Delta Y_2C_1$ , para añadir la parte real de fase al primer registro auxiliar, y para añadir la parte imaginaria de fase al segundo registro auxiliar, estando diseñada la unidad de instrucción para emitir, en respuesta a una señal de interrupción, los valores de los dos registros auxiliares divididos por el valor  $2 \cdot wS \cdot hS = 4hS \cdot hS \cdot hC$  y divididos por un valor del contador, indicando  $\Delta Y_1$  el contenido del primer registro interno, indicando  $\Delta Y_2$  el contenido del segundo registro interno, indicando  $C_2$  el contenido del tercer registro de coeficientes, indicando  $S_2$  el contenido del cuarto registro de coeficientes, indicando  $S_2$  el contenido del cuarto registro de coeficientes, indicando  $S_2$  el contenido del cuarto registro de coeficientes, indicando  $S_2$  el contenido del cuarto registro de coeficientes, indicando  $S_2$  el contenido del cuarto registro de coeficientes, indicando  $S_2$  el contenido del cuarto registro de coeficientes, indicando  $S_2$  el contenido del cuarto registro de coeficientes, indicando  $S_2$  el contenido de la primera memoria de parámetros, y designando  $S_2$  la frecuencia angular  $S_2$  conocida.

Esto tiene la ventaja de que el procesador puede aprovechar los registros auxiliares para almacenar resultados intermedios, de manera que puede calcular de manera muy eficiente la fase mediante el acceso a los resultados intermedios y de modo controlado por la señal de interrupción.

La determinación de la fase y del bias según los aspectos y ejemplos de realización descritos en este caso son importantes para una pluralidad de aplicaciones. Por ejemplo, la fase así determinada o el bias así determinado en procedimientos de codificación de la ingeniería de telecomunicación puede aprovecharse para transmitir mensajes en forma de señales eléctricas, magnéticas o electromagnéticas a través de un canal de comunicación. En el ámbito de la ciencia de los materiales, la fase así determinada o el bias así determinado puede proporcionar información sobre las propiedades del material del medio de transmisión con respecto a una onda acústica. En sistemas de análisis químicos y físicos, la fase así determinada o el bias así determinado puede aprovecharse para determinar temperatura, densidad, cambios de fase de reacciones químicas, dimensiones del objeto y concentración de líquido en medios químicos y físicos.

En procedimientos de diagnóstico médico, en el caso de señales ultrasónicas y acústicas acopladas, la fase o bias determinados según los aspectos y ejemplos de realización descritos en este caso puede aprovecharse para determinar propiedades de los tejidos. Ejemplos de realización de la invención se emplean, por ejemplo, en el caso de la supervisión de la circulación sanguínea en el cuerpo para detectar estados patológicos, en particular en el cerebro, y en la ecografía mamaria. La información de fase puede proporcionar información en este caso tanto acerca de un estado sano como de un estado patológico del tejido. Por ejemplo, mediante mediciones de la fase según los procedimientos presentados en este caso o con los procesadores presentados en este caso en pacientes sanos, pueden obtenerse informaciones sobre un estado sano del tejido que pueden servir como un tipo de valor de referencia. En el caso de mediciones en pacientes en los que la información de fase se desvía en comparación con el valor de referencia determinado, puede deducirse un estado patológico del paciente.

Otros ejemplos de realización se explican con referencia a los dibujos adjuntos. Muestran:

- fig. 1 una representación esquemática de un sistema 100 para medir relaciones de fase de ondas acústicas en un vaso 102;

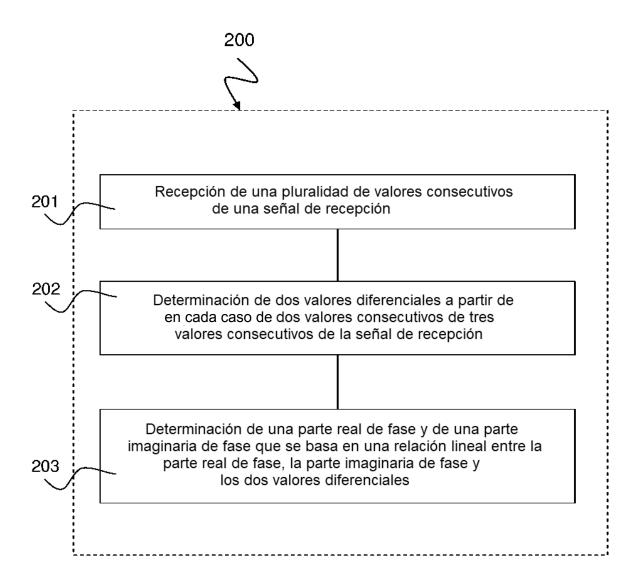

- fig. 2 una representación esquemática de un procedimiento de detección de fases 200 de acuerdo con una forma de realización;

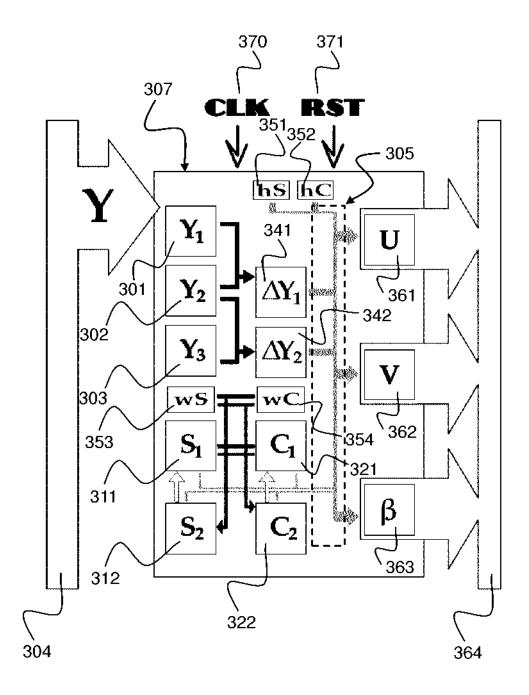

- fig. 3 una representación esquemática de un procesador 300 para determinar una fase de una señal de recepción de acuerdo con una primera forma de realización; y

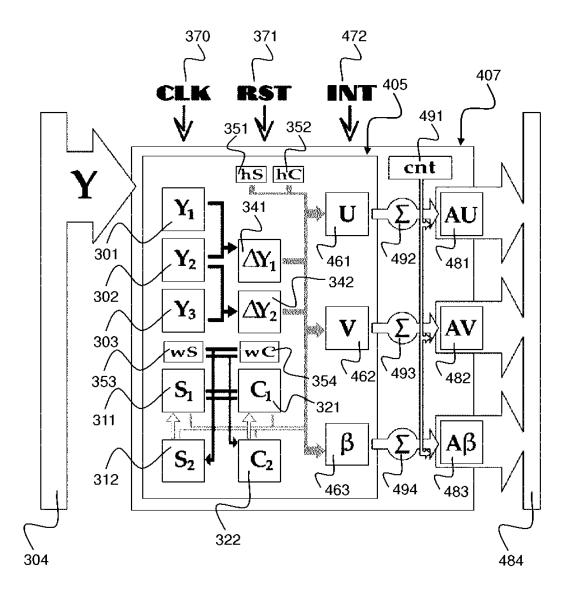

fig. 4 una representación esquemática de un procesador 400 para determinar una fase de una señal de recepción de acuerdo con una segunda forma de realización.

En la siguiente descripción detallada se hace referencia a los dibujos adjuntos, que forman una parte de esto y en los que están mostradas como aclaración formas de realización específicas en las que puede realizarse la invención. Se entiende que también pueden aprovecharse otras formas de realización o efectuarse modificaciones lógicas sin desviarse del concepto de la presente invención. Por este motivo, la siguiente descripción detallada no debe entenderse en un sentido limitativo. Aparte de eso, se entiende que las características de los distintos ejemplos de realización descritos en el presente documento pueden combinarse entre sí, siempre que no esté indicado específicamente lo contrario.

Los aspectos y formas de realización se describen con referencia a los dibujos, refiriéndose las mismas referencias generalmente a los mismos elementos. En la siguiente descripción, se representan con fines ilustrativos numerosos detalles específicos para proporcionar una comprensión exhaustiva de uno o varios aspectos de la invención. Sin embargo, para un experto puede ser evidente que uno o varios aspectos o formas de realización pueden realizarse con un menor grado de detalles específicos. En otros casos, se representan estructuras y elementos en forma esquemática para facilitar la descripción de uno o varios aspectos o formas de realización. Se entiende que pueden aprovecharse otras formas de realización o efectuarse modificaciones lógicas sin desviarse del concepto de la presente invención.

Si bien puede haberse revelado una característica determinada o un aspecto determinado de una forma de realización con respecto a solo una de varias implementaciones, una característica de este tipo o un aspecto de este tipo puede combinarse además con una o varias otras características u aspectos de las otras implementaciones, como puede ser deseado y ventajoso para una aplicación dada o determinada. Además, en la medida en que las expresiones «contener», «tener», «con» u otras variantes de las mismas deberían usarse o bien en la descripción destallada o bien en las reivindicaciones, tales expresiones deberían estar incluidas de una manera similar a la expresión «comprender». Las expresiones «acoplado» y «unido» pueden haberse usado junto con derivados de las mismas. Se entiende que las expresiones de este tipo se usan para indicar que dos elementos cooperan o interactúan independientemente entre sí si están en contacto físico o eléctrico directo o no están en contacto directo entre sí. Además, la expresión «de manera ejemplar» debe interpretarse únicamente como un ejemplo en lugar de la denominación para el mejor u óptimo. Por este motivo, la siguiente descripción no debe entenderse en un sentido limitativo.

La fig. 2 muestra una representación esquemática de un procedimiento de detección de fases 200 de acuerdo con una forma de realización. El procedimiento 200 comprende una recepción 201 de una pluralidad de valores consecutivos de una señal de recepción Y con frecuencia de exploración f<sub>s</sub> conocida como reacción a una señal de emisión con frecuencia de emisión f<sub>w</sub> conocida. El procedimiento 200 comprende una determinación 202 de dos valores diferenciales ΔΥ1, ΔΥ2 a partir de respectivamente dos valores consecutivos de tres valores consecutivos Y1, Y2, Y3 de la señal de recepción Y. El procedimiento 200 comprende una determinación 203 de una parte real de fase U y de una parte imaginaria de fase V de la señal de recepción Y que se basa en una relación lineal entre la parte real de fase U, la parte imaginaria de fase V y los dos valores diferenciales ΔΥ1, ΔΥ2.

La relación lineal entre la parte real de fase U, la parte imaginaria de fase V y los dos valores diferenciales  $\Delta Y1$ ,  $\Delta Y2$  puede representarse por un sistema de ecuaciones lineal bidimensional que se basa en los dos valores diferenciales  $\Delta Y1$ ,  $\Delta Y2$  como variables de entrada y la parte real de fase U y la parte imaginaria de fase V como variables de salida.

El sistema de ecuaciones lineal puede resolverse por ponderación de las variables de entrada con coeficientes de Fourier, que se basan en una frecuencia angular  $\Omega$ , dependiendo la frecuencia angular  $\Omega$  conocida de la frecuencia de emisión y de la frecuencia de exploración.

45 La frecuencia angular Ω conocida puede satisfacer la relación  $n=2\pi(f_w/f_s)$ .

Los coeficientes de Fourier pueden calcularse dependiendo de la frecuencia angular  $\Omega$  conocida antes de la determinación de la parte real de fase U y de la parte imaginaria de fase (V) de la señal de recepción (Y).

Un bias  $\beta$  de la señal de recepción Y puede determinarse basándose en una relación lineal entre la parte real de fase U, la parte imaginaria de fase V, el bias  $\beta$  y los tres valores consecutivos Y1, Y2, Y3 de la señal de recepción Y.

50 La siguiente representación describe los fundamentos teóricos del procedimiento 200.

Se dan tres valores Y<sub>0</sub>, Y<sub>1</sub>, Y<sub>2</sub> de una función

20

25

40

$$Y(\tau) = \beta + A\operatorname{sen}(2\pi \cdot f_{u}\tau + \varphi) \tag{4}$$

con los parámetros A,  $\beta$  y  $\phi$  desconocidos y la frecuencia de emisión  $f_w$  conocida.

Los tres valores Y<sub>0</sub>, Y<sub>1</sub>, Y<sub>2</sub> se han medido en tres momentos equidistantes

$$\tau_1$$

,  $\tau_2$  y  $\tau_3$  (5)

de manera que se aplica:

$$\Delta \tau = \tau_2 - \tau_1 = \tau_3 - \tau_2 < \frac{1}{2 \cdot f_w} \,. \tag{6}$$

Esta condición (6) garantiza (en el caso de precisión de medición absoluta) una reconstrucción exacta de los valores

$$U = A\cos(\varphi) \quad \mathsf{y} \tag{7a}$$

$$V = A \operatorname{sen}(\varphi) \tag{7b}$$

y, con ello, también de los valores

$$A = \sqrt{U^2 + V^2} \quad \text{y} \tag{8a}$$

$$\varphi = (\operatorname{arcsen}(V/A) \operatorname{mod} 2\pi), \tag{8b}$$

Los valores *U* y *V* resuelven el siguiente sistema de ecuaciones lineal:

$$Y_{1} = U \cdot S_{1} + V \cdot C_{1} + \beta$$

$$Y_{2} = U \cdot S_{2} + V \cdot C_{2} + \beta,$$

$$Y_{3} = U \cdot S_{3} + V \cdot C_{3} + \beta$$

(9)

10 en el que se aplica:

5

$$S_{i} = \text{sen}(2\pi \cdot f_{w} \cdot \tau_{i}), \quad j \in \{1, 2, 3\}$$

(10a)

$$C_{j} = \cos(2\pi \cdot f_{w} \cdot \tau_{j}), \quad j \in \{1, 2, 3\}$$

(10b)

Tras algunas modificaciones sencillas, el sistema de ecuaciones (9) puede representarse como sigue:

$$\begin{split} Y_2 - Y_1 &= U \cdot (S_2 - S_1) + V \cdot (C_2 - C_1) = 2 \operatorname{sen}(\frac{\Omega}{2}) (U \cdot \hat{C}_1 - V \cdot \hat{S}_1) \\ Y_3 - Y_2 &= U \cdot (S_3 - S_2) + V \cdot (C_3 - C_2) = 2 \operatorname{sen}(\frac{\Omega}{2}) (U \cdot \hat{C}_2 - V \cdot \hat{S}_2) \end{split} \tag{11}$$

en el que se aplica:

$$\Omega = 2\pi \cdot f_{\cdot \cdot \cdot} \Delta \tau \tag{12}$$

у

15

$$\hat{S}_{j} = \text{sen}(\Omega \cdot (j + \frac{1}{2})), \quad j \in \{1, 2\}$$

(13a)

$$\hat{C}_{j} = \cos(\Omega \cdot (j + \frac{1}{2})), \quad j \in \{1, 2\}$$

(13b)

Con la denominación

$$\Delta Y_j = Y_{j+1} - Y_j, \quad j \in \{1, 2\}$$

(14)

se produce como solución para el sistema (11):

$$U = \frac{\Delta Y_1 \cdot \hat{S}_2 - \Delta Y_2 \cdot \hat{S}_1}{2 \operatorname{sen}(\frac{\Omega}{2}) \operatorname{sen}(\Omega)},$$

(15a)

$$V = \frac{\Delta Y_1 \cdot \hat{C}_2 - \Delta Y_2 \cdot \hat{C}_1}{2 \operatorname{sen}(\frac{\Omega}{2}) \operatorname{sen}(\Omega)},$$

(15b)

Otra reducción de variables se puede lograr por la siguiente sustitución:

$$\hat{S}_2 = \hat{C}_1 \sin \Omega + \hat{S}_1 \cos \Omega, \tag{16a}$$

$$\hat{C}_2 = \hat{C}_1 \cos \Omega - \hat{S}_1 \sin \Omega, \tag{16b}$$

У

5

$$\sin \Omega = 2 \operatorname{sen}(\frac{\Omega}{2}) \cos(\frac{\Omega}{2}), \tag{17a}$$

$$\cos \Omega = 1 - 2 \operatorname{sen}^{2}(\frac{\Omega}{2}), \tag{17b}$$

A este respecto, las constantes  $sen(\frac{\Omega}{2})$  y  $cos(\frac{\Omega}{2})$  pueden tratarse como parámetros predeterminados.

A este respecto, el valor para  $\beta$  puede calcularse a partir de cada una de las siguientes ecuaciones:

$$\beta = Y_{j} - (U \cdot S_{j} + V \cdot C_{j}) = Y_{j} - [U \cdot (\hat{S}_{j-1} \cos(\frac{\Omega}{2}) + \hat{C}_{j-1} \sin(\frac{\Omega}{2})) + V \cdot (\hat{C}_{j-1} \cos(\frac{\Omega}{2}) - \hat{S}_{j-1} \sin(\frac{\Omega}{2})), \qquad (18)$$

$$j \in \{2,3\}$$

10

La recepción 201 de una pluralidad de valores consecutivos de una señal de recepción Y con frecuencia de exploración  $f_s$  conocida como reacción a una señal de emisión con frecuencia de emisión  $f_w$  conocida se puede describir con las ecuaciones (4) a (6).

La determinación 202 de dos valores diferenciales ΔΥ1, ΔΥ2 a partir de respectivamente dos valores consecutivos de tres valores consecutivos Y1, Y2, Y3 de la señal de recepción Y se puede describir por el sistema de ecuaciones (11).

La determinación 203 de una parte real de fase U y de una parte imaginaria de fase V de la señal de recepción Y que se basa en una relación lineal entre la parte real de fase U, la parte imaginaria de fase V y los dos valores diferenciales  $\Delta$ Y1,  $\Delta$ Y2 se puede describir por las ecuaciones (15a) y (15b).

La fig. 3 muestra una representación esquemática de un procesador 300 para determinar una fase de una señal de recepción de acuerdo con una primera forma de realización.

El procesador 300 comprende un primer registro de entrada 301, un segundo registro de entrada 302, un tercer registro de entrada 303, un primer registro interno 341, un segundo registro interno 342, un primer registro de salida 361, un segundo registro de salida 362, un tercer registro de salida 363, un primer registro de coeficientes 321, un

segundo registro de coeficientes 311, un tercer registro de coeficientes 322, un cuarto registro de coeficientes 312, una primera memoria de parámetros 352 o registro de parámetros, una segunda memoria de parámetros 351 o registro de parámetros, una tercera memoria de parámetros 354 o registro de parámetros, una cuarta memoria de parámetros 353 o registro de parámetros, una unidad aritmético-lógica 305 y una unidad de instrucción 307. Aparte de eso, el procesador 300 comprende una entrada para una señal de reloj CLK 370 y una entrada para una señal de reposición RST 371. En el lado de entrada, el procesador 300 está acoplado a un bus de datos de entrada 304 y, en el lado de salida, está acoplado a un bus de datos de salida 364. Sin embargo, el acoplamiento de las entradas y salidas también puede estar realizado de otra manera. Los tres registros de entrada 301, 302, 303 pueden estar realizados como memoria FIFO y en cada reloj puede recogerse respectivamente un nuevo valor de la señal de recepción Y y, al mismo tiempo, borrarse el valor registrado más antiguo.

El procesador 300 es apropiado para determinar una fase de una señal de recepción Y, recibida como reacción a una señal de emisión con frecuencia de emisión  $f_w$  conocida, con frecuencia de exploración  $f_s$  conocida.

El primer 301, segundo 302 y tercer 303 registro de entrada sirven para almacenar respectivamente uno detrás de otro tres valores consecutivos Y1, Y2, Y3 de una pluralidad de valores consecutivos de la señal de recepción Y, por ejemplo, en el caso de una pluralidad de cuatro valores consecutivos de la señal de entrada Y1, Y2, Y3, Y4, en un primer reloj se cargan los valores Y1, Y2 e Y3, en un segundo reloj se cargan los valores Y2, Y3 e Y4, sustituyéndose entonces Y1 por Y2, sustituyéndose Y2 por Y3 y sustituyéndose Y3 por Y4, etc.

El primer registro interno 341 sirve para almacenar un primer valor diferencial  $\Delta$ Y1 como diferencia del contenido Y2 del segundo registro de entrada 302 y del contenido Y1 del primer registro de entrada 301. El segundo registro interno 342 sirve para almacenar un segundo valor diferencial  $\Delta$ Y2 como diferencia del contenido Y3 del tercer registro de entrada 303 y del contenido Y2 del segundo registro de entrada 302.

El tercer registro de salida 361 sirve para facilitar una parte real de fase U de la señal de recepción Y. El segundo registro de salida 362 sirve para facilitar una parte imaginaria de fase V de la señal de recepción Y.

La unidad aritmético-lógica 305 sirve para determinar la parte real de fase U y la parte imaginaria de fase V de la señal de recepción Y que se basa en una relación lineal entre la parte real de fase U, la parte imaginaria de fase V y los dos valores diferenciales ΔΥ1, ΔΥ2, por ejemplo, correspondientemente al procedimiento 200 descrito en la fig. 2 o correspondientemente a la manera indicada más adelante.

La unidad aritmético-lógica 311 que, en este caso, solo está indicada como un cuadro de líneas discontinuas, puede presentar unidades aritmético-lógicas para realizar operaciones aritméticas.

30 Puede presentar sumadores, multiplicadores y otras unidades para realizar operaciones de cálculo.

El tercer registro de salida 363 sirve para facilitar un bias  $\beta$  de la señal de recepción Y.

10

15

20

40

45

50

Aparte de eso, la unidad aritmético-lógica 305 está diseñada para determinar el bias  $\beta$  de la señal de recepción Y que se basa en una relación lineal entre la parte real de fase U, la parte imaginaria de fase V, el bias  $\beta$  y los tres valores consecutivos Y1, Y2, Y3 de la señal de recepción Y.

Los cuatro registros de coeficientes 321, 311, 322, 312 sirven para almacenar coeficientes de Fourier, determinando los coeficientes de Fourier la relación lineal entre la parte real de fase U, la parte imaginaria de fase V y los dos valores diferenciales ΔΥ1, ΔΥ2.

La primera memoria de parámetros 352 sirve para almacenar el coseno hC de la mitad de la frecuencia angular  $\Omega$ =2 $\pi$ (f<sub>w</sub>/f<sub>s</sub>) conocida. La segunda memoria de parámetros 351 sirve para almacenar el seno hS de la mitad de la frecuencia angular  $\Omega$  conocida. La tercera memoria de parámetros 354 sirve para almacenar el coseno wC de la frecuencia angular  $\Omega$  conocida. La cuarta memoria de parámetros 353 sirve para almacenar el seno wS de la frecuencia angular  $\Omega$  conocida.

Aparte de eso, la unidad aritmético-lógica 305 sirve para determinar la parte real de fase U y la parte imaginaria de fase V de la señal de recepción Y que se basa en los contenidos C1, S1, C2, S2 de los cuatro registros de coeficientes 321, 311, 322, 312 y los contenidos hC, hS, wC, wS de las cuatro memorias de parámetros 352, 351, 354, 353.

La unidad de instrucción 307 está diseñada para inicializar, en respuesta a una señal de reposición 371, el primer registro de coeficientes 321 con el contenido hC de la primera memoria de parámetros 352 y el segundo registro de coeficientes 311 con el contenido hS de la segunda memoria de parámetros 351. La unidad de instrucción 307 sirve para restaurar, en respuesta a una señal de reloj 370, el primer registro de coeficientes 321 con el contenido C2 del tercer registro de coeficientes 322 y el segundo registro de coeficientes 311 con el contenido S2 del cuarto registro de coeficientes 312.

Aparte de eso, la unidad de instrucción 307 está diseñada para cargar, en respuesta a la señal de reloj 370, el cuarto registro de coeficientes 312 con el valor  $C_1wS + S_1wC$  y para cargar el tercer registro de coeficientes 322 con el

valor  $C_1wC$  -  $S_1wS$ , indicando wC el contenido de la cuarta memoria de parámetros 353, indicando wC el contenido de la tercera memoria de parámetros 354, indicando  $C_1$  el contenido del primer registro de coeficientes 321, indicando  $S_1$  el contenido del segundo registro de coeficientes 311 y designando  $\Omega$  la frecuencia angular  $\Omega$ =2 $\pi$ (f<sub>w</sub>/f<sub>s</sub>) conocida.

- La unidad aritmético-lógica 305 está diseñada para determinar la parte real de fase U como  $\frac{\Delta Y_1 \cdot S_2 \Delta Y_2 \cdot S_1}{4hS \cdot hS \cdot hC}$  y la parte imaginaria de fase V como  $\frac{\Delta Y_1 \cdot C_2 \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC}$ , indicando hS el contenido de la segunda memoria de parámetros 351, indicando hC el contenido de la primera memoria de parámetros 352, indicando  $C_2$  el contenido del tercer registro de coeficientes 322, indicando  $C_2$  el contenido  $C_2$  el

- Aparte de eso, la unidad aritmético-lógica 305 está diseñada para determinar el bias  $\beta$  como Y<sub>2</sub>- $(U \cdot (S_1 hC + C_1 hS) + V \cdot (C_1 hC S_1 hS))$ , indicando U la parte real de fase, indicando V la parte imaginaria de fase e indicando Y<sub>2</sub> el contenido del segundo registro de entrada 302. Sin embargo, el bias también puede determinarse según otra fórmula correspondientemente a la ecuación (18).

- El procesador 300 puede estar realizado en *hardware* o en *software*. El procesador 300 puede formar una unidad operativa en un chip o estar realizado como chip. El procesador 300 puede ser un procesador de señales digitales o un microcontrolador. El procesador 300 puede estar realizado como matriz de puertas programables (FPGA, por sus siglas en inglés), como circuito integrado, como ASIC o como parte de estos elementos constructivos. El procesador 300 puede estar realizado en un receptor o como parte de un circuito receptor, por ejemplo, un receptor 103 como está representado en la figura 1.

- 20 El modo de funcionamiento del procesador 300 puede describirse como sigue.

Tras conectar el procesador 300 o tras recibir la señal de reposición RST 322, se cargan tres valores consecutivos Y<sub>0</sub>, Y<sub>1</sub>, Y<sub>3</sub> de la señal de entrada Y desde el bus de datos de entrada 304 a los tres registros de entrada 301, 302, 303.

El tercer registro de coeficientes 322 y el cuarto registro de coeficientes 312 se borran. El primer registro de 25 coeficientes 321 se inicializa con el siguiente valor:

$$hC = \cos(\frac{\Omega}{2}) \tag{19a}$$

y el segundo registro de coeficientes 311 se inicializa con el siguiente valor:

$$hS = \operatorname{sen}(\frac{\Omega}{2}). \tag{19b}$$

En cada reloj de la señal de reloj 370, el tercer registro de coeficientes 322 se carga con el siguiente valor:

$$C_1 w C - S_1 w S \tag{20a}$$

y el cuarto registro de coeficientes 312 se carga con el siguiente valor:

$$C_1 wS + S_1 wC, (20b)$$

en el que se aplica:

30

$$wS = \operatorname{sen} \Omega$$

, (21a)

$$wC = \cos\Omega. \tag{21b}$$

35 El primer registro de salida 361 se carga con el siguiente valor:

$$U = \frac{\Delta Y_1 \cdot S_2 - \Delta Y_2 \cdot S_1}{4hS \cdot hS \cdot hC},$$

(22a)

y el segundo registro de salida 362 se carga con el siguiente valor:

$$V = \frac{\Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1}{4hS \cdot hS \cdot hC},\tag{22b}$$

y el valor

30

40

$$Y_{2} - (U \cdot (S_{1}hC + C_{1}hS) + V \cdot (C_{1}hC - S_{1}hS))$$

(23)

se carga en el tercer registro de salida 363.

Entonces, el primer registro de coeficientes 321 se sobreescribe con el contenido  $C_2$  del tercer registro de coeficientes 322 y el segundo registro de coeficientes 311 se sobreescribe con el contenido  $S_2$  del cuarto registro de coeficientes 312. El primer registro de entrada 301 se sobreescribe con el contenido  $Y_2$  del segundo registro de entrada 302, el segundo registro de entrada 302 se sobreescribe con el contenido  $Y_3$  del tercer registro de entrada 303 y un nuevo valor de entrada  $Y_4$  se carga desde el bus de datos de entrada 304 al tercer registro de entrada 303. Los valores U, V y β de los tres registros de salida 361, 362, 363 se transmiten al bus de datos de salida 364.

La fig. 4 muestra una representación esquemática de un procesador 400 para determinar una fase de una señal de recepción de acuerdo con una segunda forma de realización.

El procesador 400 está construido de manera similar al procesador 300 descrito respecto a la fig. 3. El procesador 400 comprende, correspondientemente al procesador 300, un primer registro de entrada 301, un segundo registro de 15 entrada 302, un tercer registro de entrada 303, un primer registro interno 341, un segundo registro interno 342, un primer registro de salida 461, un segundo registro de salida 462, un tercer registro de salida 463, un primer registro de coeficientes 321, un segundo registro de coeficientes 311, un tercer registro de coeficientes 322, un cuarto registro de coeficientes 312, una primera memoria de parámetros 352, una segunda memoria de parámetros 351, una tercera memoria de parámetros 354, una cuarta memoria de parámetros 353, una unidad aritmético-lógica 405 y una unidad de instrucción 407. Aparte de eso, el procesador 400 comprende una entrada para una señal de reloj CLK 370 y una entrada para una señal de reposición RST 471. En el lado de entrada, el procesador 400 está acoplado a un bus de datos de entrada 304 y, en el lado de salida, está acoplado a un bus de datos de salida 464. Con respecto al modo de funcionamiento de las unidades indicadas en este caso, se hace referencia a la descripción 25 respecto a la fig. 3, estando denominada la unidad aritmético-lógica, a causa del modo de funcionamiento adicional, con la referencia 405 y la unidad de instrucción, a causa del modo de funcionamiento adicional, con la referencia 407.

Adicionalmente al procesador 300, el procesador 400 comprende, aparte de eso, un cuarto registro de salida o un primer registro auxiliar 481, un quinto registro de salida o un segundo registro auxiliar 482, un sexto registro de salida o un tercer registro auxiliar 483, tres miembros sumadores 492, 493, 494, un contador 491 y una entrada para una señal de interrupción INT 472.

El contador 491 se incrementa con cada restauración de los tres registros de entrada 301,302, 303 dependiendo de la señal de reloi 370.

Aparte de eso, la unidad aritmético-lógica 405 está diseñada para determinar la parte real de fase U como  $\Delta Y_1S_2$  - 35  $\Delta Y_2S_1$  y la parte imaginaria de fase V como  $\Delta Y_1C_2$  - $\Delta Y_2C_1$ , para añadir la parte real de fase U al primer registro auxiliar 481, y para añadir la parte imaginaria de fase V al segundo registro auxiliar 482.

Aparte de eso, la unidad de instrucción 407 está diseñada para emitir, en respuesta a la señal de interrupción, los valores AU, AV de los dos registros auxiliares 481, 482 divididos por el valor  $2 \cdot wS \cdot hS = 4hS \cdot hS \cdot hC$  y divididos por un valor cnt del contador 491. A este respecto,  $\Delta Y_1$  indica el contenido del primer registro interno 341,  $\Delta Y_2$  indica el contenido del segundo registro interno 342,  $C_2$  indica el contenido del tercer registro de coeficientes 322,  $S_2$  indica el contenido del cuarto registro de coeficientes 312, hS indica el contenido de la segunda memoria de parámetros 351 y hC indica el contenido de la primera memoria de parámetros 352.  $\Omega$  designa la frecuencia angular  $\Omega = 2\pi (f_w/f_s)$  conocida.

El procesador 400 puede estar realizado en *hardware* o en *software*. El procesador 400 puede formar una unidad operativa en un chip o estar realizado como chip. El procesador 400 puede ser un procesador de señales digitales o un microcontrolador. El procesador 400 puede estar realizado como FPGA, como circuito integrado, como ASIC o como parte de estos elementos constructivos. El procesador 400 puede estar realizado en un receptor o como parte de un circuito receptor, por ejemplo, un receptor 103 como está representado en la figura 1.

El modo de funcionamiento del procesador 400 puede describirse como sique.

Tras conectar el procesador 400 o tras recibir la señal de reposición RST 322, se cargan tres valores consecutivos Y<sub>0</sub>, Y<sub>1</sub>, Y<sub>3</sub> de la señal de entrada Y desde el bus de datos de entrada 304 a los tres registros de entrada 301, 302, 303.

El tercer registro de coeficientes 322 y el cuarto registro de coeficientes 312 se borran. El primer registro de coeficientes 321 se inicializa con el siguiente valor:

$$hC = \cos(\frac{\Omega}{2}) \tag{24a}$$

y el segundo registro de coeficientes 311 se inicializa con el siguiente valor:

$$hS = \operatorname{sen}(\frac{\Omega}{2}). \tag{24b}$$

En cada reloj de la señal de reloj 370, el tercer registro de coeficientes 322 se carga con el siguiente valor:

$$C_1 w C - S_1 w S \tag{25a}$$

y el cuarto registro de coeficientes 312 se carga con el siguiente valor:

$$C_1 wS + S_1 wC, \tag{25b}$$

10 en el que se aplica:

5

$$wS = \operatorname{sen} \Omega$$

, (26a)

$$wC = \cos\Omega. \tag{26b}$$

El primer registro de salida 461 se carga con el siguiente valor:

$$U = \Delta Y_1 \cdot S_2 - \Delta Y_2 \cdot S_1, \tag{27a}$$

que también se añade al cuarto registro de salida 481, para lo cual se usa el primer miembro sumador 492. El segundo registro de salida 362 se carga con el siguiente valor:

$$V = \Delta Y_1 \cdot C_2 - \Delta Y_2 \cdot C_1, \tag{27b}$$

que también se añade al quinto registro de salida 482, para lo cual se usa el segundo miembro sumador 493.

El valor

25

30

$$Y_{2} - \frac{(U \cdot (S_{1}wC + C_{1}wS) + V \cdot (C_{1}wC - S_{1}wS))}{4 \cdot hS \cdot hS \cdot hC}$$

(28)

20 se carga en el tercer registro de salida 463.

Entonces, el primer registro de coeficientes 321 se sobreescribe con el contenido  $C_2$  del tercer registro de coeficientes 322 y el segundo registro de coeficientes 311 se sobreescribe con el contenido  $S_2$  del cuarto registro de coeficientes 312. El contador 491 se incrementa. El primer registro de entrada 301 se sobreescribe con el contenido  $Y_2$  del segundo registro de entrada 302, el segundo registro de entrada 302 se sobreescribe con el contenido  $Y_3$  del tercer registro de entrada 303 y un nuevo valor de entrada  $Y_4$  se carga desde el bus de datos de entrada 304 al tercer registro de entrada 303.

En cuanto se establece una interrupción, es decir, la señal de interrupción 472 señaliza una interrupción, el contenido AU del cuarto registro de salida 481 y el contenido AV del quinto registro de salida 482 se divide por el valor 2wShS(=4hShShC) y sus valores y también el valor  $\beta$  del tercer registro de salida 463, dividido respectivamente por el valor cnt del contador 491, se transmiten al bus de datos de salida 484.

Después, se envía una señal de reposición 371.

Tanto el procesador 300 de acuerdo con la descripción respecto a la figura 3 como el procesador 400 de acuerdo con la descripción respecto a la figura 4 son apropiados para implementar el procedimiento 200 descrito en la

## figura 2.

Un aspecto de la invención también comprende un producto de programa informático, que puede cargarse directamente en la memoria interna de un ordenador digital y comprende secciones de código de *software* con las que puede realizarse el procedimiento 200 descrito respecto a la fig. 2 cuando el producto se ejecuta en un ordenador. El producto de programa informático puede estar almacenado en un medio adecuado para ordenador y puede comprender lo siguiente: medios de programa legibles por ordenador, que inducen a un ordenador a recibir 201 una pluralidad de valores consecutivos de una señal de recepción Y con frecuencia de exploración  $f_s$  conocida como reacción a una señal de emisión con frecuencia de emisión  $f_w$  conocida; determinar 202 dos valores diferenciales  $\Delta Y1$ ,  $\Delta Y2$  a partir de respectivamente dos valores consecutivos de tres valores consecutivos Y1, Y2, Y3 de la señal de recepción Y; y determinar 203 una parte real de fase U y una parte imaginaria de fase V de la señal de recepción Y que se basa en una relación lineal entre la parte real de fase U, la parte imaginaria de fase V y los dos valores diferenciales  $\Delta Y1$ ,  $\Delta Y2$ .

El ordenador puede ser un ordenador personal (PC), por ejemplo, un PC de una red informática. El ordenador puede estar realizado como un chip, un ASIC, un microprocesador, un procesador de señales o en general como un procesador y puede estar implementado, por ejemplo, como procesador como está descrito en las figuras 3 a 5.

Resulta evidente que las características de las distintas formas de realización descritas en el presente documento de manera ejemplar pueden combinarse entre sí, excepto si se indica específicamente lo contrario. Como está representado en la descripción y los dibujos, los elementos individuales que se han representado en contacto no tienen que estar en contacto directamente entre sí; pueden estar previstos elementos intermedios entre los elementos unidos. Aparte de eso, resulta evidente que formas de realización de la invención pueden estar implementadas en circuitos individuales, circuitos parcialmente integrados o circuitos completamente integrados o medios de programación. El término «por ejemplo» se refiere únicamente a un ejemplo y no a lo mejor u óptimo. En el presente documento se han ilustrado y descrito formas de realización determinadas, pero para el experto es evidente que puede realizarse una pluralidad de implementaciones alternativas y/o similares en lugar de las formas de realización mostradas y descritas sin desviarse del concepto de la presente invención, que está definido por las reivindicaciones adjuntas.

#### Lista de referencias

- 100: sistema 100 para medir relaciones de fase de ondas acústicas en un vaso

- 101: emisor

- 30 102: vaso

15

20

25

50

- 103: receptor

- 104: onda ultrasónica

- 105: entrada

- 107: salida

- 35 200: procedimiento de detección de fases 200

- 201: 1. etapa de procedimiento: recepción

- 202: 2. etapa de procedimiento: determinación

- 203: 3. etapa de procedimiento: determinación

- 300: procesador, adecuado para determinar una fase de una señal de recepción

- 40 301: primer registro de entrada

- 302: segundo registro de entrada

- 303: tercer registro de entrada

- 304: bus de datos de entrada

- 305: unidad aritmético-lógica

- 45 307: unidad de instrucción

- 311: segundo registro de coeficientes

- 312: cuarto registro de coeficientes

- 321: primer registro de coeficientes

- 322: tercer registro de coeficientes

- 341: primer registro interno

- 342: segundo registro interno

- 351: segunda memoria de parámetros

- 352: primera memoria de parámetros

- 353: cuarta memoria de parámetros

- 55 354: tercera memoria de parámetros

- 361: primer registro de salida

- 362: segundo registro de salida

- 363: tercer registro de salida

- 364: bus de datos de salida

- 60 370: señal de reloi

# ES 2 697 473 T3

## 371: señal de reposición

- 400: procesador, adecuado para determinar una fase de una señal de recepción

- 405: unidad aritmético-lógica

- 407: unidad de instrucción 484: bus de datos de salida

- 472: señal de interrupción

- 481: cuarto registro de salida o primer registro auxiliar

- 482: quinto registro de salida o segundo registro auxiliar 483: sexto registro de salida o tercer registro auxiliar

- 491: contador

- 492: primer miembro sumador 493: segundo miembro sumador

- 494: tercer miembro sumador

#### REIVINDICACIONES

1. Un procedimiento de detección de fases (200), con las siguientes etapas:

5

35

45

- recepción (201) de una pluralidad de valores consecutivos de una señal de recepción (Y) con frecuencia de exploración  $f_s$  conocida como reacción a una señal de emisión con frecuencia de emisión  $f_w$  conocida; determinación (202) de dos valores diferenciales ( $\Delta$ Y1,  $\Delta$ Y2) a partir en cada caso dos valores consecutivos de tres valores consecutivos (Y1, Y2, Y3) de la señal de recepción (Y); y **caracterizado por** la determinación (203) de una parte real de fase (U) y de una parte imaginaria de fase (V) de la señal de recepción (Y) que se basa en una relación lineal entre la parte real de fase (U), la parte imaginaria de fase (V) y los dos valores diferenciales ( $\Delta$ Y1,  $\Delta$ Y2).

- 2. Procedimiento de detección de fases (200) según la reivindicación 1, pudiendo representarse la relación lineal entre la parte real de fase (U), la parte imaginaria de fase (V) y los dos valores diferenciales (ΔΥ1, ΔΥ2) por un sistema de ecuaciones lineal bidimensional que se basa en los dos valores diferenciales (ΔΥ1, ΔΥ2) como variables de entrada y la parte real de fase (U) y la parte imaginaria de fase (V) como variables de salida.

- 3. Procedimiento de detección de fases (200) según la reivindicación 2, resolviéndose el sistema de ecuaciones lineal por ponderación de las variables de entrada con coeficientes de Fourier, que se basan en una frecuencia angular Ω conocida, dependiendo la frecuencia angular Ω conocida de la frecuencia de emisión f<sub>w</sub> y de la frecuencia de exploración f<sub>s</sub>.

- 4. Procedimiento de detección de fases (200) según la reivindicación 3,

- 20 satisfaciendo la frecuencia angular Ω conocida la siguiente relación: Ω=2π(f<sub>w</sub>/f<sub>s</sub>)

- 5. Procedimiento de detección de fases (200) según las reivindicaciones 3 o 4, con: determinación de los coeficientes de Fourier dependiendo de la frecuencia angular  $\Omega$  conocida antes de la determinación de la parte real de fase (U) y de la parte imaginaria de fase (V) de la señal de recepción (Y).

- 6. Procedimiento de detección de fases (200) según una de las reivindicaciones anteriores, con:

determinación de un bias (β) de la señal de recepción (Y) que se basa en una relación lineal entre la parte real de fase (U), la parte imaginaria de fase (V), el bias (β) y los tres valores consecutivos (Y1, Y2, Y3) de la señal de recepción (Y).

- Procesador (300, 400) para determinar una fase de una señal de recepción (Y), recibida como reacción a una señal de emisión con frecuencia de emisión f<sub>w</sub> conocida, con frecuencia de exploración f<sub>s</sub> conocida, caracterizado

por:

- un primer registro de entrada (301), un segundo registro de entrada (302) y un tercer registro de entrada (303), que están diseñados para almacenar cada uno de ellos uno detrás de otro tres valores consecutivos (Y1, Y2, Y3) de una pluralidad de valores consecutivos de la señal de recepción (Y);

- un primer registro interno (341) y un segundo registro interno (342), que están diseñados para almacenar un primer valor diferencial ( $\Delta$ Y1) como diferencia del contenido (Y2) del segundo registro de entrada (302) y del contenido (Y1) del primer registro de entrada (301) y un segundo valor diferencial ( $\Delta$ Y2) como diferencia del contenido (Y3) del tercer registro de entrada (303) y del contenido (Y2) del segundo registro de entrada (302); un primer registro de salida (361, 481) y un segundo registro de salida (362, 482), que están diseñados para facilitar una parte real de fase (U) y una parte imaginaria de fase (V) de la señal de recepción (Y); y

- una unidad aritmético-lógica (305, 405), que está diseñada para determinar la parte real de fase (U) y la parte imaginaria de fase (V) de la señal de recepción (Y) basándose en una relación lineal entre la parte real de fase (U), la parte imaginaria de fase (V) y los dos valores diferenciales (ΔΥ1, ΔΥ2).

- 8. Procesador (300, 400) según la reivindicación 7, con un tercer registro de salida (363, 483), que está diseñado para facilitar un bias (β) de la señal de recepción (Y), estando diseñada la unidad aritmético-lógica (305, 405) para determinar el bias (β) de la señal de recepción (Y) basándose en una relación lineal entre la parte real de fase (U), la parte imaginaria de fase (V), el bias (β) y los tres valores consecutivos (Y1, Y2, Y3) de la señal de recepción (Y).

- 9. El procesador (300, 400) según la reivindicación 8, con un primer registro de coeficientes (321), un segundo registro de coeficientes (311), un tercer registro de coeficientes (322) y un cuarto registro de coeficientes (312), que están diseñados para almacenar coeficientes de Fourier, determinando los coeficientes de Fourier la relación lineal entre la parte real de fase (U), la parte imaginaria de fase (V) y los dos valores diferenciales (ΔΥ1, ΔΥ2).

- 10. Procesador (300, 400) según la reivindicación 9, con una primera memoria de parámetros (352), que está diseñada para almacenar el coseno (hC) de la mitad de una

frecuencia angular Ω conocida, que depende de la frecuencia de emisión f<sub>w</sub> y de la frecuencia de exploración f<sub>s</sub>;

una segunda memoria de parámetros (351), que está diseñada para almacenar el seno (hS) de la mitad de la frecuencia angular  $\Omega$  conocida;

una tercera memoria de parámetros (354), que está diseñada para almacenar el coseno (wC) de la frecuencia angular Ω conocida; y

- 5 una cuarta memoria de parámetros (353), que está diseñada para almacenar el seno (wS) de la frecuencia angular Ω conocida.

- 11. Procesador (300, 400) según la reivindicación 10, satisfaciendo la frecuencia angular  $\Omega$  conocida la siguiente relación:  $\Omega$ =2 $\pi$ (f<sub>w</sub>/f<sub>s</sub>).

- 12. Procesador (300, 400) según las reivindicaciones 10 u 11,

- estando diseñada la unidad aritmético-lógica (305, 405) para determinar la parte real de fase (U) y la parte imaginaria de fase (V) de la señal de recepción (Y) que se basa en los contenidos (C1, S1, C2, S2) de los cuatro registros de coeficientes (321, 311, 322, 312) y los contenidos (hC, hS, wC, wS) de las cuatro memorias de parámetros (352, 351, 354, 353).

- 13. Procesador (300, 400) según la reivindicación 12, con

- una unidad de instrucción (307, 407), que está diseñada

- para inicializar, en respuesta a una señal de reposición(371), el primer registro de coeficientes (321) con el contenido (hC) de la primera memoria de parámetros (352) y el segundo registro de coeficientes (311) con el contenido (hS) de la segunda memoria de parámetros (351); y

- para restaurar, en respuesta a una señal de reloj (370), el primer registro de coeficientes (321) con el contenido (C2) del tercer registro de coeficientes (322) y el segundo registro de coeficientes (311) con el contenido (S2) del cuarto registro de coeficientes (312);

- estando diseñada la unidad de instrucción (307, 407)

- para cargar, en respuesta a la señal de reloj (370), el cuarto registro de coeficientes (312) con el valor  $C_1wS + S_1wC$  y para cargar el tercer registro de coeficientes (322) con el valor  $C_1wC S_1wS$ ,

- indicando hS el contenido de la segunda memoria de parámetros (351), indicando hC el contenido de la primera memoria de parámetros (352), indicando  $C_2$  el contenido del tercer registro de coeficientes (322), indicando  $S_2$  el contenido del cuarto registro de coeficientes (312) y designando  $\Omega$  la frecuencia angular  $\Omega = 2\pi (f_w/f_s)$  conocida.

- 14. Procesador (300, 400) según la reivindicación 13,

- estando diseñada la unidad aritmético-lógica (305, 405) para determinar el bias ( $\beta$ ) como  $Y_2+(U\cdot(S_1hC+C_1hS)+V(C_1hC-S_1hS))$ ,

- indicando U la parte real de fase, indicando V la parte imaginaria de fase e indicando  $Y_2$  el contenido del segundo registro de entrada (302).

- 15. Procesador (400) según la reivindicación 12,

- con un primer registro auxiliar (481);

- 40 un segundo registro auxiliar (482); y

35

- un contador (491), que se incrementa con cada restauración de los tres registros de entrada (301, 302, 303) dependiendo de la señal de reloj (370),

- estando diseñada la unidad aritmético-lógica (405) para determinar la parte real de fase (U) como ΔY<sub>1</sub>S<sub>2</sub> -ΔY<sub>2</sub>S<sub>1</sub> y la parte imaginaria de fase (V) como ΔY<sub>1</sub>C<sub>2</sub> -ΔY<sub>2</sub>C<sub>1</sub>, para añadir la parte real de fase (U) al primer registro auxiliar (481), y para añadir la parte imaginaria de fase (V) al segundo registro auxiliar (482), estando diseñada la unidad de instrucción (407)

- para emitir, en respuesta a una señal de interrupción (472), los valores (AU, AV) de los dos registros auxiliares (481, 482) divididos por el valor  $2 \cdot wS \cdot hS = 4hS \cdot hS \cdot hC$  y divididos por un valor (cnt) del contador (491),

- indicando  $\Delta Y_1$  el contenido del primer registro interno (341), indicando  $\Delta Y_2$  el contenido del segundo registro interno (342), indicando  $C_2$  el contenido del tercer registro de coeficientes (322), indicando  $S_2$  el contenido del cuarto registro de coeficientes (312), indicando  $S_2$  el contenido de la segunda memoria de parámetros (351) e indicando  $S_2$  el contenido de la primera memoria de parámetros (352), y designando  $S_2$  la frecuencia angular  $S_2$  conocida.

Fig. 1

Fig. 2

Fig. 3

Fig. 4