OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 697 693

21 Número de solicitud: 201730963

(51) Int. Cl.:

G06N 3/00 (2006.01) G06F 17/16 (2006.01)

(12)

#### SOLICITUD DE PATENTE

Α1

(22) Fecha de presentación:

24.07.2017

(43) Fecha de publicación de la solicitud:

25.01.2019

71) Solicitantes:

UNIVERSIDAD DEL PAÍS VASCO / EUSKAL HERRIKO UNIBERTSITATEA (100.0%) Barrio Sarriena, S/N 48940 Leioa (Bizkaia) ES

(72) Inventor/es:

MARTÍNEZ CORRAL, Unai y BASTERRECHEA OYARZABAL, Koldobika

(74) Agente/Representante:

VALLEJO LÓPEZ, Juan Pedro

(54) Título: NÚCLEO IP, ARQUITECTURA QUE COMPRENDE UN NÚCLEO IP Y PROCEDIMIENTO DE DISEÑO DE UN NÚCLEO IP

(57) Resumen:

Núcleo IP, arquitectura que comprende un núcleo IP y procedimiento de diseño de un núcleo IP.

. Un núcleo IP configurable y programable de procesamiento para la computación de una pluralidad de productos matriciales, en el que tanto los datos a procesar como los resultados obtenidos se transfieren en serie, que comprende: El núcleo IP comprende: un bloque de entrada de datos para proporcionar un conjunto de vectores que representan una primera y una segunda matriz cuyo producto se quiere computar, donde dicho bloque de entrada de datos comprende: un primer sub-bloque y un segundo subbloque; un bloque de memoria que comprende N elementos de memoria asociados a una salida respectiva de dicho segundo sub-bloque del bloque de entrada de datos; un bloque multiplicador matrizvector en coma fija para implementar una operación de multiplicación-acumulación; un bloque que comprende al menos una función de activación configurada para ser aplicada a la salida de dicho bloque multiplicador matriz- vector en coma fija; un bloque para almacenar las salidas de la al menos una función de activación y para leer las salidas de dichos componentes de almacenamiento; un bloque FIFO y un bloque de salida de datos que comprende un contador de fila y un contador de columna. Sistema en chip que comprende al menos un núcleo IP.FPGA que comprende al menos un núcleo IP. Procedimiento de diseño de un núcleo IP.

FIG. 2

## **DESCRIPCIÓN**

# NÚCLEO IP, ARQUITECTURA QUE COMPRENDE UN NÚCLEO IP Y PROCEDIMIENTO DE DISEÑO DE UN NÚCLEO IP

#### CAMPO DE LA INVENCIÓN

5

10

15

20

25

30

35

La presente invención pertenece al campo delos sistemas embebidos de procesamiento de datos. Más concretamente, la invención pertenece al campo de los sistemas de procesamiento de datos embebidos, tales como los sistemas de procesamiento para computación de redes neuronales, especialmente para redes neuronales de prealimenación (feedforward). La invención tiene especial aplicación en el campo del diseño de sistemas de aceleración del procesamiento de datos, tales como en machine learning, sobre plataformas embebidas, tales como Sistemas en el Chip (SoC, System on Chip) y FPGAs (Field Programmable Gate Array).

#### ANTECEDENTES DE LA INVENCIÓN

El aprendizaje en máquinas (del inglés *machine learning*) es un área tecnológica que está experimentando un enorme desarrollo en los últimos años, debido principalmente a tres factores: (1) Disponibilidad de enormes cantidades de datos (debido al desarrollo del Internet of Things o IoT, a avances en la tecnología de sensores y al uso generalizado de vídeo y audio digital, entre otros); (2) Gran desarrollo de hardware (tecnología microelectrónica) y consiguiente aumento de la capacidad de computación; y (3) Avances en los propios algoritmos de inteligencia computacional (en este sentido, la aparición del concepto de *Deep Learning* y su éxito de aplicación, sobre todo en el campo de la visión artificial, ha generado un gran interés por el uso de redes neuronales en aplicaciones industriales).

Entre las diferentes opciones de procesamiento para el aprendizaje de máquinas, las redes neuronales artificiales (RNAs) constituyen uno de los modelos de predictor (clasificador, regresor) más populares y que está recibiendo mayor atención por su amplia aplicabilidad. Sin embargo, las aplicaciones del procesamiento neuronal (procesamiento basado en RNAs) para *machine learning* requieren de una gran capacidad de computación que, debido a su arquitectura fundamentalmente paralela y masivamente interconectada, sólo puede ser satisfecha utilizando procesadores específicos de alto rendimiento y alta eficiencia. En el caso de los sistemas de

5

10

15

20

25

30

35

procesamiento embebidos (en contraposición con los sistemas de procesamiento masivos basados en la computación en la nube o cloud computing y grandes computadores con un elevado volumen y consumo), cuyas áreas de aplicabilidad están en constante crecimiento (sistemas autónomos, plataformas móviles, IoT, automóvil inteligente/autónomo, etc.), estas exigencias computacionales suponen un reto mayor debido a la necesidad de ser implantadas en hardware de pequeño tamaño, bajo consumo y bajo coste. Las FPGAs son, en este sentido, una de las plataformas con más potencial en este campo, ya que permiten aplicar las más avanzadas técnicas de diseño digital (paralelismo, segmentación, diseño específico con granularidad fina, tanto en lógica como en memoria) en la implementación de sistemas de procesamiento complejos en un solo chip, de forma que pueden obtenerse los más altos rendimientos en términos de capacidad de procesamiento por unidad de potencia consumida. Sin embargo, el diseño de este tipo de sistemas es complejo y laborioso, con ciclos de diseño relativamente largos, lo que hace necesaria la implicación de diseñadores expertos y alarga la llegada de los productos al mercado (time to market). En consecuencia, la tendencia actual es ofrecer a los diseñadores librerías de unidades prediseñadas, preferiblemente configurables a sus necesidades, en forma de bloques de propiedad intelectual (bloques IP o núcleos IP), a menudo configurables y escalables, de forma que puedan integrarse en sus diseños ajustándose a las necesidades de sus aplicaciones finales. El concepto de núcleo IP está íntimamente ligado al concepto de reusabilidad y a la utilización de las herramientas de CAD (EDA) en el diseño y síntesis de sistemas digitales. Idealmente, los núcleos IP son completamente portables, es decir, que se ha utilizado algún lenguaje estándar de descripción para su diseño (o un formato de netlist lógico) y que no lleva asociada ninguna información referente a la tecnología final de implementación. De esta manera, los diseñadores de sistemas digitales pueden hacer uso de estos núcleos IP, que se organizan en librerías, integrándolos directamente en sus diseños como simples cajas negras, a menudo configurables definiendo ciertos parámetros, que únicamente exponen los puertos de entrada/salida para su interconexión con el resto del sistema, frecuentemente mediante buses.

A modo de ejemplo, dentro de las redes neuronales, las redes neuronales de convolución (CNN, del inglés *Convolutional Neuron Network*) y las redes neuronales profundas (DNN, del inglés *Deep Neural Network*) representan un modelo computacional que está ganando popularidad debido a su potencialidad para resolver problemas de la interfaz humano-computadora, tales como la interpretación de imágenes. Esto es debido a que estas redes pueden alcanzar gran precisión mediante la emulación del comportamiento

del nervio óptico. El núcleo del modelo es un algoritmo que recibe como entrada un amplio conjunto de datos (por ejemplo, píxeles de una imagen) y aplica a esos datos un conjunto de transformaciones (convoluciones en el caso de las CNN) de acuerdo con unas funciones predefinidas. Los datos transformados pueden llevarse a continuación a una red neuronal para detectar patrones. Como en el caso general de las RNAs, debido al patrón computacional específico de las CNN y DNN, los procesadores de propósito general no son eficientes en implementaciones basadas en CNN o en DNN.

5

10

15

20

25

30

35

La solicitud de patente US 2015/0170021 A1 describe un dispositivo procesador que incluye un núcleo de procesador y un número de módulos de cálculo, siendo cada uno de estos configurable para realizar operaciones de un sistema CNN. Un primer conjunto de módulos de cálculo del dispositivo procesador está configurado para realizar operaciones de convolución, un segundo conjunto de módulos de cálculo se reconfigura para realizar operaciones de promediado y un tercer conjunto de módulos de cálculo se reconfigura para realizar operaciones de producto escalar. Sin embargo, se trata de un procesador de precisión fija, seleccionable entre 8 bits y 16 bits, y no se puede indicar un tamaño de palabra diferente para cada etapa del circuito. En consecuencia, no es posible optimizar la precisión de computación del procesador, con el consiguiente impacto negativo en recursos consumidos (área ocupada).

Tianshi Chen et. Al. han propuesto un acelerador para machine learning (redes neuronales) formado por un búfer de entrada para neuronas de entrada, un búfer de salida para neuronas de salida y un tercer búfer para pesos sinápticos, conectados a un bloque computacional configurado para realizar computaciones sinápticas y neuronales. El acelerador tiene también una lógica de control ("DianNao: A Small-Footprint High-Throughput Accelerator for Ubiquitous Machine-Learning", SIGPLAN Not., vol. 49, no 4, pp. 269-284, Feb. 2014).En esta propuesta, los elementos de memoria dispuestos a la entrada/salida del núcleo son buffers con DMA (un buffer para los datos de entrada, otro buffer para los pesos y un tercer buffer para almacenar los resultados) conectados a una interfaz de memoria común, por lo que se necesitan direcciones absolutas para acceder a la memoria externa. Es decir, no existe jerarquía de memoria. En lo que respecta a los recursos aritméticos, están dispuestos para una máxima paralelización, utilizando uno o varios árboles de sumadores (en inglés, adder-tree). Asimismo, el formato numérico utilizado es fijo e invariable (16 bits en coma fija). Además, atendiendo a la lógica de control, se entiende que los tamaños de las diferentes capas que componen el modelo deben cumplir ciertas restricciones para que la elección de los parámetros de subdivisión arroje resultados enteros.

A su vez, en la propuesta de J. Qiu et. al ("Going deeper with embedded fpga platform for convolutional neural network", Proceedings of the 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, ser. FPGA'16, Monterrey, California, USA: ACM, 2016, pp 26 {35, isbn: 978-1-4503-3856-1. doi: 10.1145/2847263.2847265.), el diseño de la unidad aritmética es muy similar al de la propuesta de Tianshi Chen et. al. en "DianNao: A Small-Footprint High-Throughput Accelerator for Ubiquitous Machine-Learning", con la diferencia de que el buffer para cargar los pesos es de tipo FIFO.

5

10

15

20

25

30

A su vez, Chen Zhang et al. han propuesto un diseño de acelerador basado en FPGA para Redes Neuronales de Convolución profundas, en el que tratan de optimizar tanto los recursos lógicos como el ancho de banda de memoria ("Optimizing FPGA-based Accelerator Design for Deep Convolutional Neural Networks," FPGA'15, February 22-24, 2015, Monterey, California, USA, ACM 978-1-4503-3315-3/15/02). El acelerador propuesto es capaz de ejecutar trabajos de aceleración a lo largo de diferentes capas sin necesidad de reprogramar la FPGA. Esta divulgación se centra en la reordenación algorítmica y en la elección óptima de parámetros, teniendo en consideración las características de la plataforma objetivo. Para la descripción del sistema, esta propuesta utiliza la herramienta de síntesis automática de alto nivel HLS (Vivado). El uso de una herramienta de este tipo, comparado con un diseño realizado a más bajo nivel (RTL), conlleva varias limitaciones en lo referente a la optimización de la comunicación de los datos (alternativas al uso de memorias compartidas, lecturas no secuenciales en las FIFOs etc.) y, en particular, a la organización y los accesos a memoria (gestión de espacios de direccionamiento independientes, asignación dinámica de memoria etc.). Asimismo, el formato numérico utilizado es de 32 bits (en coma fija o flotante), sin opción a su configuración.

Por otra parte, M. Motamedi et al. profundizan("Design space exploration of fpga-based deep convolutional neural networks", in 2016 21<sup>st</sup> Asia and South Pacific Design Automation Conference (ASP-DAC), Jan. 2016, pp. 575 {580.Doi: 10.1109/ASPDAC.2016.7428073)en las posibilidades de máxima paralelización y aprovechamiento de la localidad, utilizando módulos denominados Parallel Convolution Engines (PCD), compuestos por múltiples multiplicadores y un adder-tree. Este diseño solo es provechoso en la computación de capas de convolución.

Por último, H. Li et. al., proponen ("A high performance fpga-based accelerator for large-scale convolutional neural networks", 2016, 26th International Conference on Field Programmable Logic and Applications (FLP), Aug. 2016, pp. 1 {9. doi: 10.1109/FLP.

2016.7577308) la utilización de una instancia del módulo aritmético para cada capa del modelo de la red neuronal, introduciendo buffers dobles entre cada etapa. En lo que respecta al diseño de cada módulo aritmético, se propone un array sistólico de MACCs, de longitud igual al filtro a aplicar. Los pesos se cargan mediante multiplexores y los datos a través de un registro de desplazamiento cuyo tamaño se limita a la longitud del filtro de convolución. Los datos no se utilizan hasta que el registro no está completamente lleno. También utilizan adder-trees para acumular resultados parciales computados en paralelo.

#### DESCRIPCIÓN DE LA INVENCIÓN

5

10

15

20

25

30

La presente invención proporciona un módulo de procesamiento que resuelve los inconvenientes de propuestas anteriores.

En el contexto de la presente divulgación, los términos "procesador", "procesador neuronal", "núcleo de procesamiento", "núcleo IP" (del inglés IP core), "bloque IP" (del inglés IP block) y módulo IP (del inglés IP module) son intercambiables. La presente divulgación describe un núcleo IP de un procesador neuronal totalmente configurable por el usuario final, es decir, por ejemplo por el diseñador de un Sistema en Chip (*System on Chip*, SoC). Este núcleo IP permite la aceleración de computación y es especialmente aplicable a la aceleración de computación en algoritmos de *machine learning*. Entre las características del procesador de la invención, se pueden destacar que:

-El procesador neuronal puede adecuarse automáticamente, durante el proceso de síntesis de la red neuronal que se vaya a implementar, a los recursos disponibles en el dispositivo objetivo seleccionado (por ejemplo, FPGA) mediante una técnica de plegado (en inglés, folding) y reutilización de las capas neuronales. A partir de las fuentes de descripción, por ejemplo en VHDL, un sintetizador (CAD) genera un netlist adecuado para la plataforma o tecnología objetivo (dependiendo de si es una FPGA o un ASIC). Es decir, se ha realizado una descripción totalmente parametrizada del procesador neuronal (núcleo IP) en la que el usuario final puede indicar, entre otras cosas, cuántos recursos quiere/puede utilizar para la implementación final del procesador de forma que el sistema realiza los ajustes necesarios para plegar la arquitectura de la red de forma que el procesador sintetizado finalmente sea más serie (lo que implica mayor reutilización de menor cantidad de recursos hardware, y por tanto, un poco más lento), o más paralelo (lo que implica menor reutilización, o ninguna, en el caso más extremo, de una mayor cantidad de recursos hardware, y por tanto, más rápido). Esta característica permite

10

15

20

25

30

35

empotrar el procesador (o núcleo IP) tanto en FPGAs de bajo coste (pequeño tamaño y consumo y reducidos recursos lógicos) como en FPGAs de alto rendimiento. Más aún, una vez sintetizado cierto tamaño de red, la utilización del número de neuronas en cada capa de red puede seleccionarse en tiempo de ejecución, haciendo innecesario el uso de técnicas de reconfiguración dinámica. Esto se consique mediante activación/desactivación de una señal de habilitación presente en cada elemento de procesamiento (DSP + función de activación). Es decir, en contraposición con la adecuación automática del número de recursos hardware (DSPs, etc.) que se van a sintetizar, es posible activar/desactivar neuronas que ya han sido implementadas ("programación" vs. "configuración" en fase de síntesis). Para realizar esta programación, el usuario no necesita gestionar todas las señales de habilitación de forma individual, sino que se genera un registro en el módulo de control que permite indicar cuántas neuronas de las sintetizadas se van a utilizar o activar en el último fold o plegado (ya que en todos los anteriores, si los hay, se utilizan todas las neuronas físicas). El sistema detecta cuándo se ha modificado el valor de ese registro, y se utiliza un contador junto con un registro de desplazamiento para generar secuencialmente todas las señales de (des)habilitación. En una posible implementación, en la que en la mayoría de ejecuciones el número de neuronas físicas utilizadas es mayor que el número de neuronas deshabilitadas, inicialmente todas están habilitadas. Así, la latencia de configuración es igual al número de neuronas deshabilitadas. La latencia máxima, por tanto, es uno menos que el número de neuronas físicas (cuando sólo se utiliza una). En otra posible implementación, se puede utilizar otro patrón predefinido: que por ejemplo la mitad estén habilitadas y la otra mitad no. De esta forma, la latencia máxima es la mitad, pero se incrementa la latencia media en elecciones de parámetros óptimas (que el número de neuronas del modelo de la capa sea múltiplo del número de neuronas físicas).

-El procesador (o núcleo IP) utiliza direcciones virtuales, de forma que sus componentes internos trabajan en términos de matrices, columnas y filas, lo que facilita el desarrollo de aplicaciones basadas en algoritmos que integren operaciones de álgebra matricial. El procesador neuronal (núcleo IP) incluye módulos "puente" para gestionar el propio núcleo IP directamente desde puertos externos, tales como puertos AXI, que son el estándar en algunos productos (chips, ASICs), como los de Xilinx y ARM. Además, puesto que la gestión de grandes volúmenes de datos (es decir, grandes matrices) es crítica en los sistemas actuales, el procesador se ha provisto de un bloque de interconexión configurable y programable (MAI, que se describe más adelante) específicamente diseñado que permite gestionar bloques de memoria tanto internos

como externos.

5

10

15

20

25

30

Como resultado, el diseñador de una arquitectura SoC puede integrar múltiples bloques de computación y almacenamiento, y realizar de forma transparente pruebas de rendimiento asignando dinámicamente la memoria, para obtener la solución más eficiente. Esto se consigue por medio de un conjunto de tablas y microbloques en la MAI que ofrecen una amplia variedad y granularidad a la hora de asignar no sólo las matrices, sino cada fila/columna.

Además, el módulo de procesamiento de la invención se basa en la reutilización de los bloques de multiplicación-acumulación (bloques MACC), que en ocasiones en este texto se denomina como plegado de capas. En este sentido, los parámetros del modelo de la capa (a veces llamados 'pesos' o 'ganancias' de las interconexiones neuronales), que se ajustan en una fase previa de entrenamiento o aprendizaje de la red, se cargan en los scratchpads a través del mismo puerto que los datos de entrada (vectores de entrada de la red). En implementaciones de la invención, el módulo de control puede mantener el scratchpad del vector de entrada en standby hasta que todos los parámetros hayan sido cargados, de forma que una vez iniciada la computación, no sea interrumpida por la carga de parámetros. Los resultados finales pueden simplemente guardarse en memoria a través del puerto de salida, o realimentarse al scratchpad de entrada. La elección depende del modelo concreto de capa que se esté implementando. Por ejemplo, en las soluciones más compactas donde sea aceptable un tiempo de ejecución más lento, un vector puede realimentarse varias veces para procesar el efecto de múltiples capas utilizando únicamente memoria local.

Aunque el diseño del módulo de procesamiento es independiente de la tecnología objetivo en la que se vaya a integrar, en realizaciones de la invención, el alto grado de parametrización de la descripción del diseño del núcleo IP y su enorme escalabilidad, hacen que el núcleo IP pueda ser integrado de varias maneras en distintas tecnologías. Por un lado, las ya mencionadas FPGAs y PSoCs, que son dispositivos "prefabricados" con una alta configurabilidad, de forma que el núcleo IP está diseñado para adecuarse de forma óptima a las características de la arquitectura de los sistemas-en-un-chip (SoC) sobre FPGA, y más concretamente a las características del bus AXI. Así, el núcleo IP puede ser incrustado tanto en FPGAs de pequeño tamaño y bajo coste como en FPGAs de mayor tamaño y rendimiento. Por otro lado, el código de descripción del procesador, descrito en el lenguaje estándar de descripción hardware VHDL (acrónimo que resulta de combinar VHSIC (Very High Speed Integrated Circuit) y HDL (Hardware Description

10

15

20

25

30

35

Language)), proporciona gran portabilidad, de forma que el módulo de procesamiento es no solo integrable en arquitecturas PSoCs o FPGAs (ya sea integrándolo con procesadores blandos (soft processors) o en los denominados PSoCs (Programmable SoC), que contienen un procesador duro (hard processor), tal como el Cortex-A9 de ARM integrado en un dispositivo Zyng de Xilinx), sino que es también integrable en un ASIC con arquitectura SoC junto con otros procesadores y módulos de aceleración. Es decir, aunque la tecnología objetivo preferente para la que ha sido diseñado el módulo de procesamiento (o procesador) de la invención es una FPGA, ya que el código de descripción del procesador se ha desarrollado con el objetivo de realizar un uso optimizado de los recursos propios de las FPGAs (tales como los bloques de memoria (BRAM), unidades aritméticas (bloques DSPs) y gestores/sintetizadores/divisores de reloj (Mixed-Mode Clock Manager, MCMM)),el módulo de procesamiento de la invención puede también destinarse a ASIC para su integración en SoC. Nótese que recientemente se están comercializando productos en el mercado que integran bloques IP de FPGAs en ASICs (es decir, bloques IP configurables y adaptables a distintas tecnologías de fabricación), denominados comúnmente como eFPGAs, para que los fabricantes de SoCs en ASIC integren dichos bloques IP en sus chips de forma que éstos dispongan de una zona de lógica reconfigurable al estilo de las FPGAs (es una FPGA a medida integrada como parte de un ASIC).

Una diferencia significativa del procesador de la invención, con respecto a los divulgados en el estado de la técnica, es que el procesador se ha diseñado para optimizar su funcionamiento en aplicaciones con entrada de datos de tipo streaming. Por ejemplo, el procesador es especialmente adecuado para el procesamiento de imágenes hiperespectrales. En consecuencia, no se ha buscado la paralelización máxima del procesamiento, cuestión que condiciona al uso de adder-trees y el broadcasting de parámetros a múltiples instancias al mismo tiempo, sino que el bucle (loop) más interno es secuencial. Este hecho tiene impacto tanto en el tamaño del sistema, como en el tiempo de ejecución y frecuencia máxima de operación. En comparación con los diseños conocidos, el presente procesador da como resultado soluciones que ocupan menos área (menos recursos en una FPGA) y requiere más ciclos de reloj de computación, pero a su vez permite trabajar a frecuencias mayores, con lo que se compensa en cierta medida la mayor latencia en ciclos. Esto se debe a que el objetivo buscado es adaptarse a las limitaciones impuestas por el streaming y aprovecharlo para sacar el máximo partido a las FPGAs de tamaño reducido. Además, la presente propuesta evita la imposición de relaciones inviolables entre parámetros, lo cual redunda en una mayor flexibilidad y escalabilidad.

5

10

15

20

25

30

Por otra parte, puesto que el presente núcleo IP está especialmente diseñado para sistemas con recursos limitados (dispositivos pequeños), el sistema de control del núcleo IP no impone restricciones en las relaciones entre los parámetros de configuración. Es común, por ejemplo, que las redes CNN más extendidas (y complejas) utilicen potencias de dos para establecer los tamaños de las capas de la red y de los conjuntos de datos a procesar. Sin embargo, en aplicaciones con SLFN, se ha detectado la necesidad de poder escoger tamaños de capa de hasta 2k con una granularidad mayor. Así, las herramientas de autoconfiguración generan una solución que garantiza el menor tiempo de ejecución de la arquitectura para cualquier tamaño de red, sin introducir datos de padding (relleno) para su control. Gracias a que las señales de habilitación se activan secuencialmente, se minimiza la complejidad adicional en los elementos de control de la arquitectura. A esto contribuye el hecho de que el bucle más interno (es decir, el producto vectorial) se procese de forma secuencial, reduciendo con ello una dimensión a gestionar de forma no lineal. Al mismo tiempo, debe considerarse que la omisión de los DMA de la arquitectura y la utilización de formatos de dirección optimizados ofrece un balance para compensar el uso de recursos.

Con respecto a los registros de desplazamiento para la entrada de datos, una diferencia significativa del procesador de la invención, con respecto a los divulgados en el estado de la técnica, es que se utiliza un número elevado de multiplicadores y al computar en modo "ola" los datos empiezan a utilizarse desde que llega el primero al primer multiplicador, sin esperar a que los registros estén llenos.

Otra ventaja destacable con respecto a otras propuestas es que la precisión de computación en el procesador de la invención es ajustable, es decir, configurable para cada conjunto de datos y, opcionalmente, seleccionable en tiempo de ejecución. En las propuestas convencionales la precisión es fija debido a que se presupone que la FPGA se va a reconfigurar para cada modelo de red neuronal (no hay configurabilidad en tiempo de ejecución).

Por otra parte, varios parámetros del presente procesador son configurables en tiempo de ejecución, es decir, tras la síntesis. Algunos de estos parámetros son el tamaño del bloque (*chunk*) de datos a ser procesado, número de entradas, número de neuronas en las capas ocultas a procesar, número de salidas y uso (o no) de las funciones de activación en cada capa. Esto hace que el procesador, una vez sintetizado e implementado, sea más flexible y pueda adaptarse a distintos modelos de red sin

necesidad de reconfigurar el hardware.

5

10

15

20

25

30

Además, la presente solución utiliza un módulo de internconexión (MAI) entre la memoria externa y el núcleo IP, específicamente diseñado para conectar de forma eficiente y sencilla varios núcleos IP en una arquitectura heterogénea de tipo SoC. En realizaciones de la invención, este módulo (MAI) está basado en Wishbone B4, asegurando su total portabilidad e independencia de la tecnología objetivo.

Otro aspecto destacable de la presente solución es que el núcleo IP ha sido totalmente descrito utilizando el lenguaje estándar VHDL, lo que lo hace agnóstico a las herramientas de diseño/síntesis y totalmente portable desde el punto de vista tecnológico, además de permitir un control total sobre todos y cada uno de los aspectos del diseño. Más aún, se han escrito un conjunto de paquetes en este lenguaje que han permitido la práctica total parametrización del diseño, por lo que en realidad se ha desarrollado una completa herramienta de diseño y configuración del núcleo IP que permite al diseñador de sistemas su fácil uso e integración. El conjunto de scripts e interfaces de usuario que componen estas herramientas de parametrización automática son multiplataforma (por ejemplo, Windows, Linux, mac) y generan VHDL estándar, por lo que puede utilizarse tanto para síntesis en FPGA como para semi-custom ASIC.

Por último, el módulo de procesamiento descrito en la presente invención cuenta con gestión de memoria integrada.

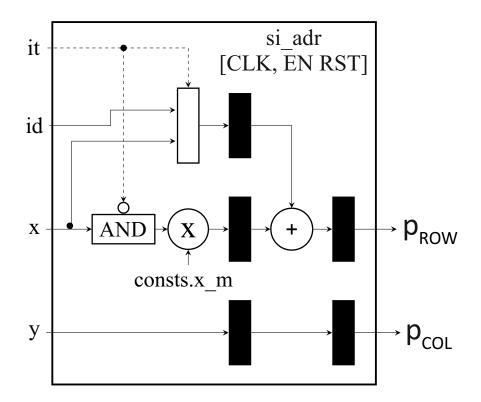

En un primer aspecto de la invención, se proporciona un núcleo IP configurable y programable de procesamiento para la computación de una pluralidad de productos matriciales, en el que tanto los datos a procesar como los resultados obtenidos se transfieren en serie, que comprende: un bloque de entrada de datos configurado para proporcionar, a partir de unos datos de entrada, un conjunto de vectores que representan una primera y una segunda matriz cuyo producto se quiere computar, utilizando un formato de dirección virtual compuesto por punteros a matriz, fila y columna, donde dicho bloque de entrada de datos comprende: un primer sub-bloque configurado para obtener un puntero de fila (p<sub>ROW</sub>) y un puntero de columna (p<sub>COL</sub>); y un segundo sub-bloque que comprende N componentes, donde N es un número natural > 1, cada uno de los cuales comprende dos contadores encadenados correspondientes al número de vectores a transferir y a la longitud de dichos vectores, donde cada componente utiliza direcciones locales; un bloque de memoria que comprende N elementos de memoria, estando cada uno de dichos elementos de memoria asociado a una salida respectiva de dicho segundo sub-bloque del bloque de entrada de datos; un bloque multiplicador matriz-vector en

coma fija configurado para implementar una operación de multiplicación-acumulación para multiplicar una matriz por múltiples vectores recibidos en serie de forma continua, donde dicho bloque multiplicador matriz-vector en coma fija comprende un conjunto de sub-bloques, donde cada uno de dichos sub-bloques comprende una pluralidad de módulos aritméticos; un bloque que comprende al menos una función de activación configurada para ser aplicada a la salida de dicho bloque multiplicador matriz-vector en coma fija; un bloque para almacenar en componentes de almacenamiento las salidas de la al menos una función de activación y para leer las salidas de dichos componentes de almacenamiento; y un bloque de salida de datos que utiliza un formato de dirección virtual compuesto por punteros a matriz, fila y columna, que comprende un contador de fila y un contador de columna.

5

10

20

25

30

En realizaciones de la invención, el primer componente de dicho segundo sub-bloque está configurado para proporcionar un número de vectores igual al número de productos matriz-vector consecutivos que se desean computar.

En realizaciones de la invención, los componentes segundo a último de dicho segundo sub-bloque están configurados para proporcionar un número de vectores igual al número de pasadas que se deben realizan con el DSP correspondiente.

En realizaciones de la invención, el bloque multiplicador matriz-vector en coma fija está basado en un array sistólico lineal con carga de parámetros en paralelo y ejecución tipo ola.

En realizaciones de la invención, dichos N elementos de memoria comprendidos en dicho bloque de memoria son N bloques BRAM.

En realizaciones de la invención, cada sub-bloque o grupo de dicho bloque multiplicador matriz-vector en coma fija comprende un multiplexor a su salida.

En realizaciones de la invención, cada sub-bloque o grupo de dicho bloque multiplicador matriz-vector en coma fija comprende a su salida tantos registros de desplazamiento como módulos aritméticos tiene cada sub-bloque.

En realizaciones de la invención, dichos módulos aritméticos operando en paralelo generan, cada z ciclos, tantos datos como número de módulos aritméticos haya, donde z es la longitud del vector.

En realizaciones de la invención, la ejecución en paralelo de dichos módulos aritméticos se controla mediante una máquina de estados que toma como referencia sólo el primer módulo aritmético. En este caso, la máquina de estados puede utilizar tres contadores de

apoyo: longitud del vector, número de repeticiones y latencia del módulo aritmético.

5

10

15

20

25

30

En realizaciones de la invención, dicho bloque multiplicador matriz-vector en coma fija representa al menos una capa oculta de una red neuronal artificial.

En realizaciones de la invención, el núcleo IP comprende medios para realimentar la salida de dicho bloque FIFO para efectuar al menos dos operaciones matriz-vector consecutivas con un filtrado intermedio, de forma que con una sola instancia del bloque multiplicador matriz-vector en coma fija se procesa tanto la al menos una capa oculta como la capa de salida de la red neuronal.

En realizaciones de la invención, se utilizan M módulos aritméticos para efectuar h multiplicaciones vectoriales, donde h es el número de filas de la matriz en el producto matriz-vector, por lo que si h >M, se requiere más de una pasada, iteración o repetición para procesar cada vector de entrada.

En realizaciones de la invención, el núcleo IP comprende además un núcleo de interconexión configurado para facilitar la integración del núcleo IP en un sistema heterogéneo con uno o varios módulos coprocesadores, estando dicho núcleo de interconexión configurado para gestionar bloques de memoria internos y externos al núcleo IP.

En realizaciones de la invención, todas las operaciones se realizan en coma fija de precisión ajustable, estando configurado para definir el tamaño de palabra utilizado en cada una de las matrices que intervienen en cada ejecución.

En un segundo aspecto de la invención, se proporciona una arquitectura SoC (*System on a Chip*) que incorpora una módulo de procesamiento como el descrito anteriormente. En realizaciones de la invención, el módulo de procesamiento se integra en una FPGA. Es decir, se proporciona un sistema en chip (SoC) que comprende al menos un núcleo IP como el descrito anteriormente.

En otro aspecto de la invención, se proporciona una FPGA que comprende al menos un núcleo IP como el descrito anteriormente.

En otro aspecto de la invención, se proporciona un procedimiento de diseño de un núcleo IP como el descrito anteriormente, adecuado para una tecnología objetivo, que comprende: generar un netlist que comprende una descripción parametrizada del núcleo IP adecuado para dicha tecnología objetivo; sintetizar una red neuronal que se desee implementar, adecuando el núcleo IP a los recursos disponibles en dicha tecnología objetivo, donde dicha adecuación se realiza mediante una técnica de plegado y

reutilización de capas neuronales; una vez sintetizado cierto tamaño de red neuronal, seleccionar en tiempo de ejecución un número de neuronas que se desea utilizar en cada capa de red.

El procesador neuronal de la invención es aplicable en cualquier aplicación de *machine learning* basada en RNAs en la que convenga realizar un procesamiento acelerado de grandes volúmenes de datos y, más particularmente, en sistemas embebidos autónomos con requerimientos de reducido tamaño y peso y gran integrabilidad. En consecuencia, la aplicabilidad del procesador neuronal de la invención es amplísima: entre otras, clasificación de objetos en sistemas de visión embebida (detección de tumores, detección e identificación de objetos, detección de peatones, coches autónomos, guiado de drones, detección de objetivos, procesamiento de imágenes hiperespectrales, etc.), ya que las aplicaciones de *machine learning* atraviesan todos los mercados verticales, desde el militar/aeroespacial, pasando por la automoción, el industrial, el de instrumentación médica, hasta los grandes centros de procesamiento de datos (internet, computación en la nube, IoT). El procesador neuronal de la invención puede usarse también en aplicaciones de *deep learning*, por ejemplo para visión embebida, ya que el procesador puede configurarse fácilmente para trabajar como una red neuronal con múltiples capas de procesamiento, incluso con capas de convolución o capas recurrentes.

En suma, entre las ventajas del núcleo IP propuesto, puede destacarse que se ha concebido y realizado para que sea de fácil integración como un núcleo IP en el diseño de arquitecturas SoC junto con otros módulos de procesamiento (incluidos, claro está, los microprocesadores). Así, es destacable que un diseñador de SoC que quiera utilizarlo, únicamente debe ajustar una serie de parámetros de configuración a nivel alto (aspectos del modelo de red que quiere implementar así como restricciones en los recursos hardware disponibles para su implementación) y el código se autoconfigura para generar una estructura de procesamiento adecuada a estos requerimientos (ajustes de nivel bajo). Más aún, el diseño permite que, una vez implementado el procesador, algunas de sus funcionalidades sean programables en tiempo de ejecución.

Ventajas y características adicionales de la invención serán evidentes a partir de la descripción en detalle que sigue y se señalarán en particular en las reivindicaciones adjuntas.

#### BREVE DESCRIPCIÓN DE LAS FIGURAS

5

10

15

20

25

30

Para complementar la descripción y con objeto de ayudar a una mejor comprensión de las características de la invención, de acuerdo con un ejemplo de realización práctica de la misma, se acompaña como parte integrante de la descripción, un juego de figuras en el que con carácter ilustrativo y no limitativo, se ha representado lo siguiente:

La figura 1 representa una red neuronal artificial (RNA) convencional. Concretamente, se ha ilustrado una arquitectura típica de una red neuronal artificial de tipo Single Hidden Layer Feedforward Network (SLFN), así como la representación matricial de las fases de inferencia y entrenamiento del modelo directo Extreme Learning Machine (ELM).

10

15

20

30

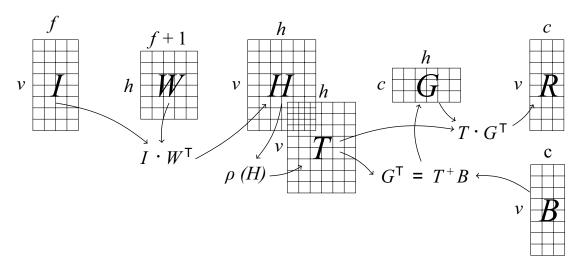

La figura 2 ilustra un diagrama de bloques de un núcleo IP de acuerdo con una posible realización de la invención.

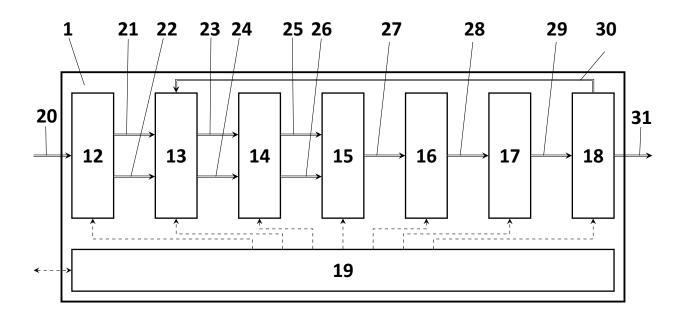

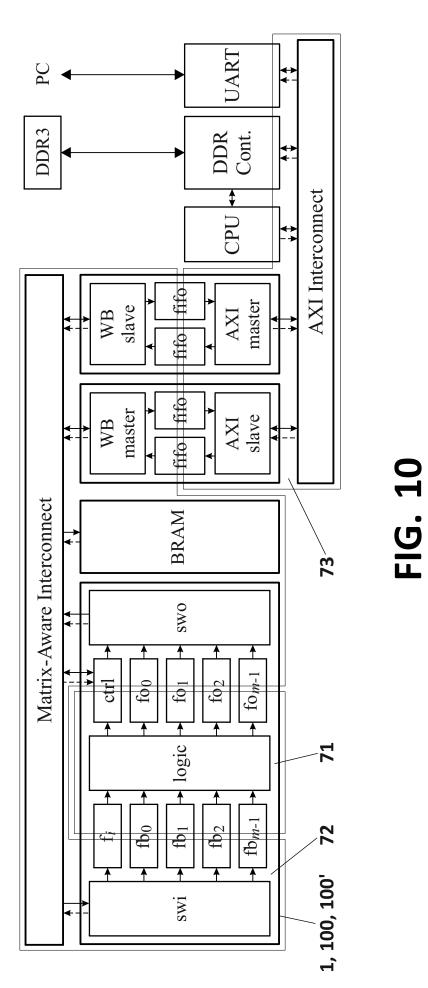

La figura 3 ilustra un diagrama de bloques de un posible sistema en el que puede integrarse el núcleo IP de la figura 2.

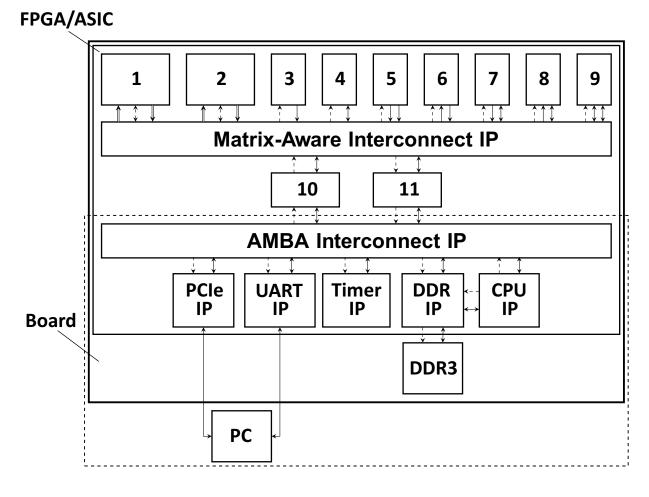

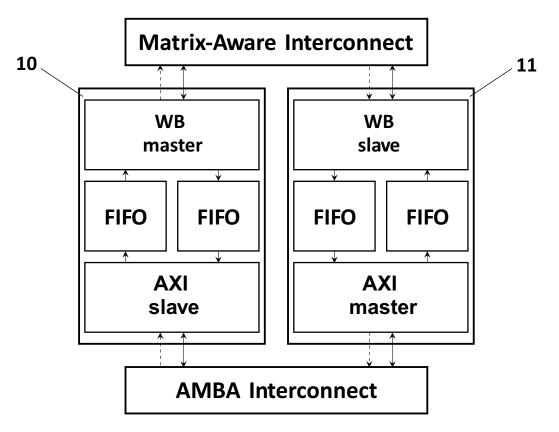

La figura 4 ilustra un diagrama de bloques de unos módulos puente para conectar módulos de interconexión basados en Wishbone B4 con módulos de interconexión basados en AMBA, de acuerdo con una posible realización de la invención.

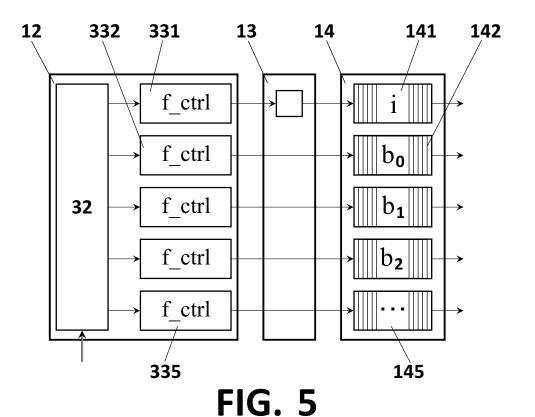

La figura 5 ilustra una posible implementación de varios módulos del diagrama de bloques de la figura 2, de acuerdo con la presente invención.

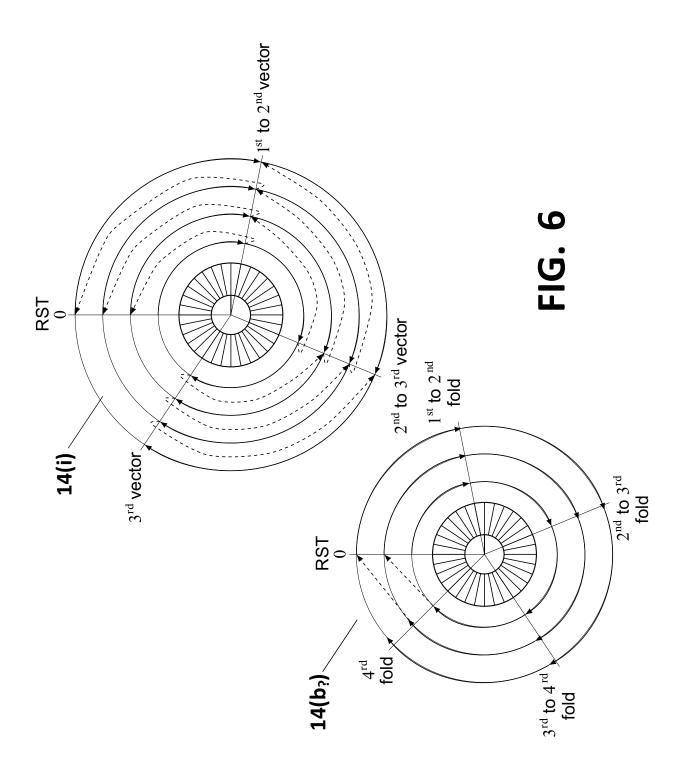

La figura 6 representa en detalle las modificaciones de las interfaces FIFO de lectura correspondientes a la matriz de entrada y a la matriz de pesos, de acuerdo con una posible realización de la invención. Es decir, se muestran gráficamente los patrones de acceso para el procesamiento de tres productos matriz-vector consecutivos en un problema de cuatro pasadas (olas).

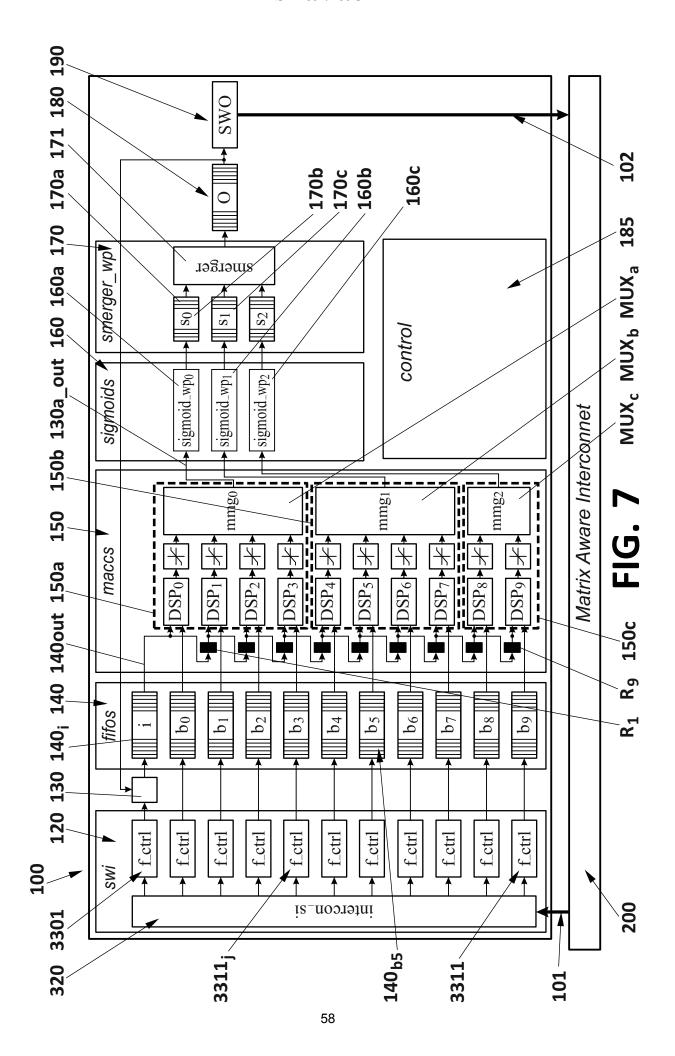

La figura 7 ilustra un ejemplo de implementación de un núcleo IP de acuerdo con una posible realización de la invención.

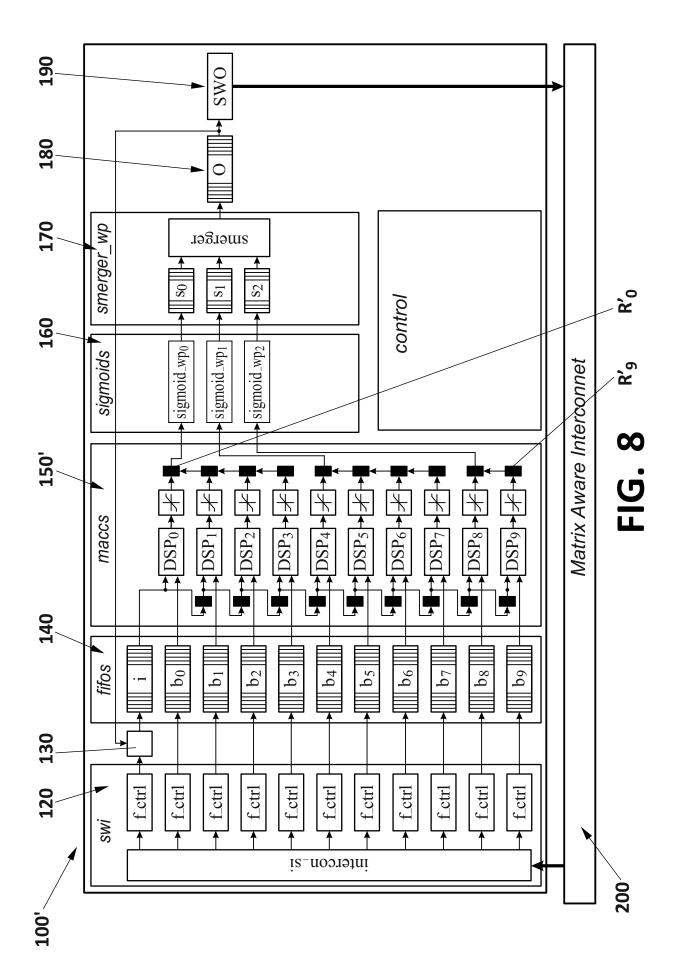

La figura 8 ilustra un diagrama de bloques de un núcleo IP de acuerdo con otraposible realización de la invención.

La figura 9 muestra un esquema del componente utilizado para obtener punteros de fila y columna en el sub-bloque intercon\_si, para decodificar la dirección local en base a la posición y los índices dados, de acuerdo con una posible implementación de la invención.

La figura 10 muestra tres posibles dominios de reloj utilizados por el núcleo IP de acuerdo con realizaciones de la invención.

La figura 11 ilustra un ejemplo de combinación de múltiples instancias (stack) de un

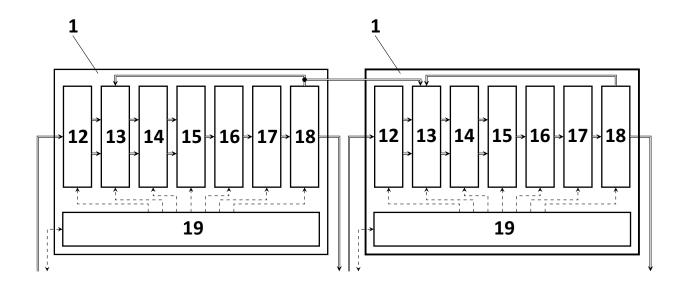

coprocesador neuronal de acuerdo con realizaciones de la invención, para reducir la latencia en aplicaciones con recursos lógicos suficientes. Se observa cómo se pueden instanciar varias copias del núcleo IP para computar múltiples capas al mismo tiempo.

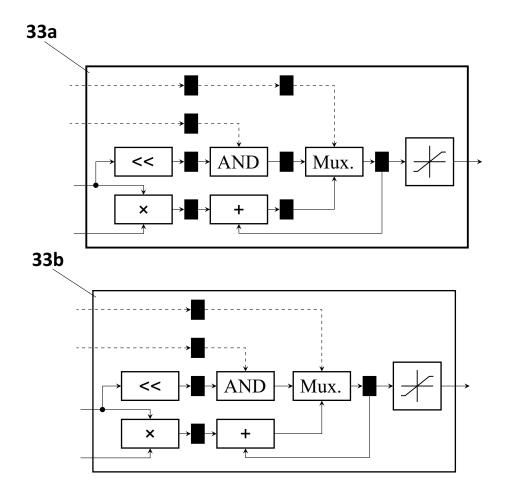

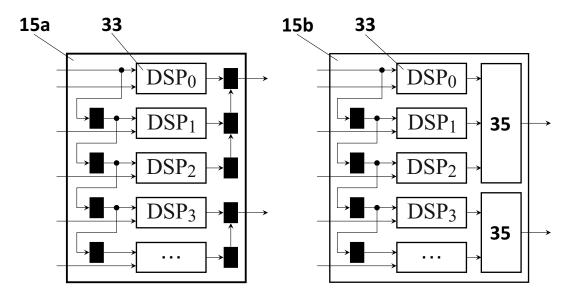

La figura 12 ilustra dos DSPs modificados, de acuerdo con posibles realizaciones de la invención.

5

10

15

20

25

30

La figura 13 muestra posibles implementaciones del módulo 15 de la figura 2, basado en DSPs con los correspondientes módulos de saturación, por tratarse de aritmética en coma fija. Se muestran dos variantes para gestionar las salidas: mediante registros de desplazamiento y mediante multiplexores.

La figura 14 representa de forma esquemática diferentes variantes de interconexión para adecuar el ancho de banda de entrada a los requerimientos de la aplicación.

La figura 15 representa la ejecución con un patrón de tipo ola y su posterior serialización a la salida, que es una característica relevante del funcionamiento del núcleo IP de la invención. Se trata de un cronograma, a modo de ejemplo, de la ejecución del núcleo IP, donde se observan dos características de diseño: i) los resultados se generan en un patrón tipo ola; y ii) la derivación automática de la mayoría de parámetros internos de la arquitectura minimiza el impacto de los cuellos de botella como el mostrado en este ejemplo.

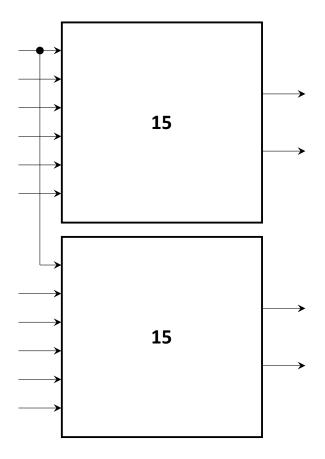

La figura 16 ilustra un ejemplo de combinación de múltiples instancias del módulo 15 de la figura 2 para reducir la latencia.

## DESCRIPCIÓN DE UN MODO DE REALIZACIÓN DE LA INVENCIÓN

La figura 1 representa una red neuronal artificial (RNA) convencional que representa un modelo computacional para cuyo procesamiento es necesaria una gran capacidad de computación que solo puede ser satisfecha usando procesadores específicos de alto rendimiento y alta eficiencia. El procesador o núcleo IP de la presente divulgación está especialmente diseñado para computar modelos computacionales complejos, tales como, pero de forma no limitativa, el representado en la figura 1. En la parte superior de la figura 1 se muestra la arquitectura típica de una red neuronal artificial de tipo Single Hidden Layer Feedforward Network (SLFN). Se trata de una red de tipo 'shallow', lo que quiere decir que no hay muchas capas ocultas (en este caso sólo hay una, referenciada en la arquitectura ilustrada como "capa oculta"), en contraposición con las redes neuronales profundas (DNN), que poseen muchas capas ocultas. En todo caso, con el diseño de la

presente divulgación pueden implementarse redes con cualquier número de capas. Nótese que cada una de las conexiones entre la capa de entrada y la capa oculta tiene asociado un valor, representado como  $w_{h,f}$ , mientras que cada una de las conexiones entre la capa oculta y la capa de salida tiene asociado un valor, representado comog<sub>c,h</sub>. Estos valores, denominados pesos o ganancias, representan una multiplicación y son los parámetros principales de la red. La red está además definida a través del número de nodos en cada capa. En el ejemplo ilustrado, la capa de entrada tiene 4+1 nodos (4 nodos de entrada + valor de bias (el valor de bias es realmente un parámetro de la capa oculta), la capa oculta tiene 6 nodos y la capa de salida tiene 3 nodos. Un experto entenderá que el número de nodos por capa puede variar de una red a otra. Además de los pesos y el número de nodos en cada una de las capas, a una SLFN la definen el tipo de funciones de activación utilizadas en las neuronas artificiales que se describen a continuación. En el contexto de la presente divulgación, una SLFN está compuesta por dos capas, puesto que no se realiza ninguna operación aritmética en la indicada como capa de entrada. No obstante, se utiliza también el término capa de forma genérica.

5

10

15

20

25

30

35

En la capa oculta, cada nodo es una neurona artificial. Una neurona artificial está formada por la suma de todas sus entradas y la aplicación de una transformación no lineal al resultado, denominada 'función de activación'. Hay múltiples funciones matemáticas que pueden utilizarse como función de activación para la computación de la activación. A modo de ejemplo, pero de forma no limitativa, citamos sigmoide logística (sig), tangente hiperbólica (tanh), base radial (RBF), lineal-rectificada (ReLu), entre otras. Nótese que a lo largo del presente texto se hace referencia a la función de activación como 'sigmoide', pero ello no ha de entenderse como una pérdida de generalización, ya que puede utilizarse cualquier función matemática adecuada para computar la activación. De hecho, el diseño contempla la síntesis de las funciones mencionadas. En algunas funciones de activación es recomendable utilizar uno o varios parámetros, denominados 'bias', para heterogeneizar las respuestas de los nodos, de forma que la proyección espacial implícita sea más rica en detalles. Esta característica se ilustra en la figura como un nodo adicional en la capa anterior con un valor constante. En el ejemplo ilustrado, la capa de salida no utiliza bias, por lo que no se ilustra en la capa oculta. En el núcleo IP de la presente divulgación, la utilización del bias puede activarse para cada capa modificando un bit correspondiente a la constante indicada. En la capa de salida, cada nodo es una suma de todas sus entradas, sin que se aplique ninguna función de activación. Por lo tanto, cada nodo de la capa de salida puede interpretarse como una neurona artificial con transformación nula a la salida. Así, del mismo modo que en la capa anterior, la capa de salida puede ser seleccionable de entre un conjunto de funciones. En aplicaciones de clasificación, es habitual añadir una capa adicional de un solo nodo a la salida de la capa de salida para identificar la salida con valor máximo. El núcleo IP de la presente divulgación contempla esta posibilidad. Sin embargo, no es parte del modelo SLFN de referencia (figura 1).

5

10

15

20

25

30

35

La parte inferior de la figura 1 representa desde el punto de vista algorítmico el modelo de red neuronal de la parte superior de la figura. Este modelo se representa como dos productos matriciales sucesivos, con una transformación no lineal (la definida por la función de activación) aplicada al resultado intermedio. Concretamente: 'I' es una matriz compuesta por filas correspondientes a los 'v' vectores de entrada. La longitud 'f' de estos vectores 'v'es igual al número de nodos en la capa de entrada, sin contar los bias; 'W' es la matriz de pesos de entrada, donde cada fila h corresponde a los parámetros de cada nodo en la capa oculta; 'H' es el producto matricial I\*W; 'T' es el resultado de la aplicación de la función no lineal a cada elemento de 'H'; 'G' es la matriz de pesos de salida, donde cada fila c corresponde a los parámetros de cada nodo en la capa de salida; 'R' es el producto matricial T \* G<sup>T</sup>. Por lo tanto, en adelante denominamos 'capa' a un producto matricial y una transformación no lineal opcional. En una versión básica de núcleo IP de la presente divulgación, el núcleo se centra en una única capa cada vez, por lo que la computación de la fase de inferencia de una SLFN implica dos ejecuciones sucesivas del núcleo. No obstante, se pueden instanciar varias copias del núcleo IP para computar múltiples capas al mismo tiempo, tal como se ilustra como ejemplo en la figura 11. Ambas soluciones permiten extrapolar su uso a redes con cualquier número de capas, ya que el diseño hardware es agnóstico al número de éstas; es decir, independiente de las operaciones anteriores o posteriores. Adicionalmente, en la figura se muestra la operación G<sup>T</sup>=T<sup>+</sup> \*B. Esta operación representa una fase de entrenamiento en caso de utilizar un método de entrenamiento concreto denominado Extreme Learning Machine (ELM). En la descripción del núcleo IP dela presente divulgación no se describe en detalle esta etapa, ya que la implementación de núcleo IP aquí descrita se centra en la etapa de inferencia o feedforward (no en la fase previa de entrenamiento). No obstante, se ilustra para exponer que el primer producto matricial y la transformación no lineal son operaciones compartidas en ambas fases. Por lo tanto, el diseño propuesto puede utilizarse junto con un resolvedor lineal para acelerar la etapa de entrenamiento. Además, la programabilidad en tiempo de ejecución permite utilizar la misma arquitectura en ambas fases, entrenamiento e inferencia, no siendo necesaria la síntesis e implementación de dos versiones de diferente tamaño. Alternativamente, como método de entrenamiento puede utilizarse el método Random Vector Functional-Link (RVFL), muy similar al ilustrado. La diferencia radica en que la matriz 'l' se añade a la derecha de 'T', de forma que cada nodo de entrada se conecta directamente a cada nodo de salida con un peso determinado, además de la propia capa oculta. Esta modificación se mantiene en las fases de entrenamiento e inferencia. La implementación del núcleo IP propuesta no diferencia las ELM de las RVFL desde el punto de vista de la arquitectura hardware, ya que se ha diseñado para soportar ambos modelos cambiando únicamente los espacios de memoria utilizados. Asimismo, el usuario puede realizar transformaciones adicionales entre etapas para soportar otros modelos de red.

En suma, cualquier red neuronal que pueda expresarse como una secuencia de productos matriciales con transformaciones no lineales intermedias opcionales(es decir, cualquier modelo de red neuronal de tipo feedforward), se puede 'mapear' al diseño de núcleo IP de la presente divulgación, que se describe a continuación. Una vez representado el modelo de red en capas, la selección de parámetros del núcleo IP propuesto se basa en la elección de los valores máximos para cada una de las tres dimensiones implicadas en los productos: el número de filas de dos matrices y el número de columnas de ambas (que debe ser igual). Por ejemplo, cuando se procesa una SLFN, estas parejas de matrices son 'I,W' y 'T,G', y los parámetros a definir son: v, max(f,h) y max(h,c). Adicionalmente, se debe(n) escoger las(s) función(es) de activación que se desea sintetizar.

A continuación se explica cómo se adapta el diseño e implementación de núcleo IP de la presente divulgación de forma automática para computar capas de una red neuronal de diferente tamaño con un número fijo (probablemente inferior al número de neuronas de las distintas capas del modelo) de bloques DSP (en adelante simplemente DSP). O lo que es lo mismo, cómo se mapea el esquema convencional de una red neuronal, probablemente multicapa, a la implementación propuesta de núcleo IP (hardware): El modelo de la red se divide en capas, siendo cada una de éstas un producto matricial con una función de activación no lineal opcionalmente aplicada al resultado. Las capas de la red neuronal pueden implementarse como operaciones de multiplicación-acumulación (multiply-accumulate operations), es decir, computando el producto de dos entradas y añadiendo ese producto a un acumulador. La unidad hardware que realiza esta operación es un MACC o unidad MACC (acumulación de multiplicación o Multiplier-ACCumulator). En una FPGA o ASIC, cada DSP realiza un producto vectorial. Por lo tanto, cada DSP equivale a la primera fase de cómputo de una 'neurona física' (operación Multiply-Accumulate o MACC). A esto hay que añadirle una transformación no lineal (por

ejemplo, normalmente de tipo sigmoidal, aunque esto también es configurable), que se realiza en un módulo situado a continuación en el datapath; a esta transformación no lineal se le denomina función de activación de la neurona. Sin embargo, el diseño está pensado de forma que los módulos de transformación no lineal no sean una limitación para el 'throughput' que puedan demandar los DSPs. Por un lado, el diseño está segmentado (pipeline) para aceptar un dato por cada ciclo de reloj. Por otro lado, hay tantas instancias como datos en paralelo puede generar el módulo anterior (15, maccs, que se describe en relación con la figura 2).

5

10

15

20

25

30

Se divide el número de neuronas del modelo de cada capa neuronal entre el número de neuronas físicas (o DSPs que se quieran utilizar en la implementación final), para obtener el número de 'folds' o plegados necesarios; esto supone una serialización parcial del procesamiento. Se carga un vector de entrada y se opera con todas las neuronas físicas en forma de ola. Si fuera necesario, el vector vuelve a leerse 'fold' veces, utilizando en cada caso todas las neuronas físicas con diferentes parámetros. Nótese que es necesario cuando el número de DSPs es inferior al número de neuronas de la capa que se está procesando. A eso se le llama plegado de la capa. Además, si hay más capas que procesar, posteriormente estos DSPs también se vuelven a utilizar para procesar la siguiente capa (que puede necesitar un plegado mayor o menor, o ninguno). No obstante, puede instanciarse varias copias del núcleo IP, en cuyo caso los DSP pueden no utilizarse para diferentes capas (sí para el plegado). Si el número de neuronas del modelo pendientes de computar en una ola es menor que el número de neuronas físicas, sólo se utilizan las necesarias. Esto es así incluso cuando 'fold' es cero. Es decir, cuando el modelo de la capa tiene un número de neuronas menor que el número de DSPs implementado/sintetizado (paralelismo máximo).

Por ejemplo, en una SLFN con k entradas, capa oculta con 3 neuronas ocultas y 1 salida, que se quiera implementar utilizando sólo 2 DSPs, el modelo se procesa de la siguiente manera: Para la capa oculta, se computan las dos primeras neuronas de la capa oculta [fold 0], se computa la neurona restante de la capa oculta [fold 1] y se aplica la función de activación no lineal a los tres resultados. Para la capa de salida, se computa la neurona de salida [fold 0] y se aplica la función de activación no lineal al resultado.

Nótese que la mayoría de las operaciones que afectan a una capa se realizan en paralelo (varios folds y la función de activación), a pesar de que la exposición en forma de lista exprese secuencia. Nótese también que el plegado (fold) es independiente del número de

nodos de la capa de entrada a la red, es decir, del número de elementos en cada producto vectorial.

La adecuación automática del procesador (núcleo IP) al modelo de red neuronal se realiza en dos fases: en síntesis, por el "plegado" de las capas para reutilizar los recursos hardware de forma optimizada (y la consiguiente adecuación del control y flujo de datos), y en tiempo de ejecución (una vez implementado el procesador) mediante el uso de unaserie de registros de configuración programables, lo que permite ajustar el tamaño de la capa a procesar y el tipo de función de activación, escribiendo en dichos registros.

5

10

15

20

25

30

A continuación se describe un núcleo IP de acuerdo con una implementación de la invención, que optimiza las operaciones de la red neuronal en términos del tiempo de acceso a memoria al aprovechar la localidad de los datos (memoria y registros internos), de forma que se evita el acceso continuo a los módulos de memoria de mayor capacidad pero menor ancho de banda (memoria externa). Al utilizar múltiples scratchpads, también se mejora el ancho de banda local. Se consigue también optimización energética, que es un compromiso entre área ocupada y el tiempo de computación requerido. La configurabilidad de este diseño permite buscar una relación deseada entre área y velocidad. Nótese que el consumo energético está asociado, principalmente, a la frecuencia de operación (consumo dinámico), pero también al área ocupada (consumo estático). Por lo tanto, el consumo energético depende del número de DSPs utilizado en la síntesis. A mayor número de DSPs utilizados, más operaciones en paralelo se realizan, por lo que no será necesario trabajar tan rápido como con un número reducido de DSPs.

La figura 2 ilustra un diagrama de bloques de un procesador neuronal (núcleo IP) 1 de acuerdo con una posible realización de la invención. El núcleo IP 1 es un acelerador computacional adecuado, entre otros, para el procesamiento de redes neuronales artificiales (RNA) de tipo "feedforward", en el que las operaciones se realizan con aritmética en coma fija, especialmente optimizado para aplicaciones donde los datos a procesar se transfieren en serie. El hecho de que todas las operaciones se realicen en coma fija significa que está optimizado para una utilización eficiente de los recursos lógicos y aritméticos (en el caso de una FPGA) o del área de silicio ocupada (en el caso de ASIC), así como de la latencia de los cálculos y, consiguientemente, del consumo de energía. El diagrama de bloques representa además un diseño altamente parametrizado, que se auto-configura en tiempo de síntesis y que es programable en tiempo de ejecución, como se explica a continuación. Esto significa que un diseñador que vaya a utilizar este núcleo IP 1 simplemente debe especificar las características del modelo de la

10

15

20

25

30

35

red y de la tecnología objetivo (recursos disponibles) en el momento de sintetizar, y el núcleo IP 1 se configurará convenientemente para ajustar aquellas (características del modelo de la red) a ésta (tecnología objetivo). El código fuente desarrollado en VHDL está completamente parametrizado por medio de sentencias 'generic', 'generate' y 'package'. Así, modificando un grupo reducido de parámetros, el código calcula automáticamente el tamaño de palabra (número de bits) necesario en cada señal y registro del circuito. Asimismo, se añaden o eliminan algunos módulos automáticamente, en función de la elección. Por ejemplo, si sólo se sintetiza una función de activación, no es necesaria la lógica de selección de la misma, y se elimina; o, en caso de utilizar doble juego de precisión en la representación numérica, los DSP y módulos de saturación se adecuan para gestionar ambos de forma adecuada. En resumen, el usuario tiene a su disposición un conjunto de parámetros, a nivel alto, que definen el modelo de la red que quiere implementar y ciertos aspectos del hardware que quiere utilizar, y el código asociado al núcleo IP y procedimiento de diseño de la presente invención, ajusta automáticamente todos los aspectos del diseño del procesador 1 (internos o a nivel bajo) para que este se sintetice de forma optimizada cumpliendo los requerimientos que el usuario le impone. Una vez implementado el procesador (núcleo IP) 1, la programación en tiempo de ejecución se consigue sustituyendo constantes 'hard-wired' por registros y, al mismo tiempo, facilitando un mecanismo de comunicación para su lectura/escritura. Concretamente, uno de los puertos Wishbone de entrada al procesador neuronal 1 accede a los registros de configuración en el módulo control. El protocolo utilizado es el mismo que en los puertos de datos, por lo que se pueden consultar/modificar los registros individualmente o en bloque. A mayores, los registros de control están multiplexados para optimizar el número de conexiones a los subcomponentes del procesador 1. Así, es parte de la máquina de estados principal la actualización de los registros en cada subcomponente, tan pronto como se recibe el 'trigger' y antes de iniciar efectivamente la computación.

Antes de entrar en los detalles de cada módulo o elemento del núcleo IP 1 de la figura 2, con objeto de considerar un posible contexto de utilización para el que se ha diseñado el núcleo IP 1, la figura 3 representa un diagrama de bloques de una posible realización de un diseño completo basado en So(P)C (Systemon (Programmable) Chip). Prácticamente todos los módulos/componentes ilustrados en la figura 3 pueden ser integrados en un solo chip (ya sea FPGA, ASIC u otro). Es probable que la memoria DDR (DDR3 en la figura 3) se diseñe para que sea externa al chip, aunque técnicamente es posible incluirla en el mismo. Nótese que los módulos referenciados como "AMBA Interconnect IP", "PCIe

10

15

20

25

30

35

IP", "UART IP", "Timer IP", "DDR IP", "CPU IP", "DDR3" y "PC" no forman parte de la presente invención, y por tanto no deben considerarse limitativos, y se indican a modo de ejemplo del contexto en el que se espera pueda ser utilizado el núcleo IP de la presente divulgación, pero ninguno de estos módulos es necesario para el uso de dicho núcleo IP. No obstante, el núcleo IP 1 está pensado para trabajar con una CPU principal (referenciada como "CPU IP" en la figura 3) y con una memoria externa de alta capacidad (a modo de ejemplo, pero de forma no limitativa, una DDR). Volviendo a la figura 3, los módulos/componentes 3-9 representan diferentes tipos posibles de bloques de memoria que pueden emplearse: ROM de puerto sencillo 3, RAM de puerto sencillo 4, ROM de puerto dual 5, RAM de puerto dual simple 6, RAM de puerto dual lectura/escritura y lectura 7; RAM de puerto dual lectura/escritura y escritura 8; y RAM de puerto dual verdadero 9. Cada uno de estos módulos incluye un submódulo para interpretar el protocolo Wishbone utilizado en la MAI (Matrix-Aware Interconnect). En la figura 3 se muestran también unos módulos/componentes puente 10, 11 que se detallan en la figura 4. Como las BRAM, cada módulo puente 10, 11 incluye submódulos maestros/esclavos para interpretar los protocolos Wishbone y AMBA. En concreto, el primer módulo puente 10 comprende un sub-módulo maestro para interpretar el protocolo Wishbone (WB master en la figura 4), dos FIFO y un sub-módulo esclavo para interpretar el protocolo AMBA (AXI slave en la figura 4). A su vez, el segundo módulo puente 11 comprende un sub-módulo esclavo para interpretar el protocolo Wishbone (WB slave en la figura 4), dos FIFO y un sub-módulo maestro para interpretar el protocolo AMBA (AXI master en la figura 4). Las FIFO se utilizan para maximizar el throughput. Estos módulos puente 10, 11 pueden ser parte opcional de la MAI. Lo que en las figuras 3 y 4 se ilustra como "Matrix-Aware-Interconnect" es el núcleo de la misma. Desde el punto de vista del código fuente, un módulo jerárquicamente superior puede incluir la MAI y los módulos puentes, además de algún MCMM. Los protocolos Wishbone y AMBA son la forma de comunicar el procesador neuronal con la CPU. Nótese que un procesador que entienda el protocolo Wishbone no requiere de ningún puente 10, 11 y podría conectarse directamente al núcleo de la MAI. Aunque en la figura 3, de forma esquemática solo se muestra una instancia de cada módulo/componente 3-11, es posible instanciar múltiples copias de cualquiera de ellos, o instanciar solo uno de ellos. Nótese que los módulos e interfaces enumeradas permiten mapear prácticamente cualquier periférico o coprocesador adicional a la MAI. Así, en la figura 3 el módulo/componente 2 representa otro procesador o núcleo IP, que podría incluirse para complementar al núcleo IP 1, como por ejemplo, pero no limitativamente, un resolvedor lineal.

10

15

20

25

30

35

Volviendo a la figura 2, el núcleo IP 1 incluye un módulo o elemento 15 en el que se realizan las operaciones aritméticas para computar productos vectoriales que conformen un producto matricial. El módulo 15 comprende una serie de módulos DSP, módulos de saturación a la salida y registros. Opcionalmente puede comprender multiplexores y el contador asociado a cada uno de ellos. Cada uno de estos DSP se puede implementar con un multiplicador y un sumador, además de recursos auxiliares como puertas lógicas, registros y multiplexores. Esto módulos son bloques de procesamiento habitualmente integrados en las arquitecturas de las FPGAs. En el presente diseño se les han añadido unos módulos de saturación compuesto por un comparador y un multiplexor. La figura 12 muestra dos posibles realizaciones de DSPs modificados 33a, 33b. A estos módulos DSP modificados se les ha llamado también DSP por asociación. El módulo 15 en sí, además de los DSPs, incluye un registro de desplazamiento a la entrada. Por último, a la salida pueden incluirse registros de desplazamiento o multiplexores. Estas dos variantes se muestran en la figura 13: a la izquierda (referencia 15a), mediante registros de desplazamiento y a la derecha (referencia 15b), mediante multiplexores 35. La figura 16 ilustra un ejemplo de combinación de múltiples instancias del módulo 15 de la figura 2 para reducir la latencia.

El módulo 16 es el módulo en el que se realiza la transformación no lineal, que es opcional. Los módulos 12-14 implementan la gestión de la información para leer los datos de entrada. La función de estos módulos es recibir los datos de las dos matrices con las que se debe calcular el producto. El módulo 12 es la interconexión (bus compartido o crossbar) y el controlador asociado a cada FIFO. Se detalla en la figura 5. El módulo 13 representa un conjunto de multiplexores. Su uso principal es la realimentación. El módulo 14 son las FIFOs/scratchpads.

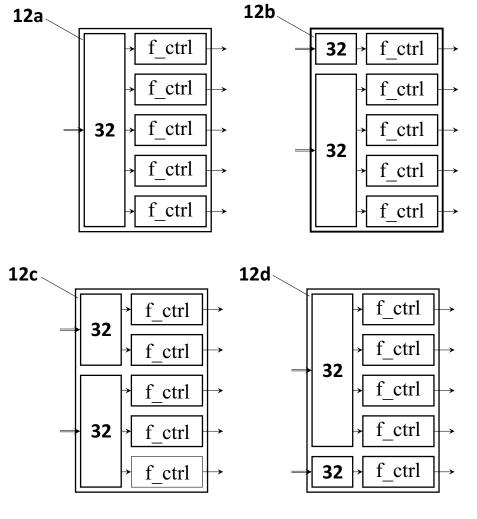

La figura 5 ilustra una posible implementación de los módulos de entrada 12-14 de acuerdo con la presente invención. El módulo 12 está formado por un primer bloque o submódulo 32, que es una interconexión de tipo bus compartido o crossbarswitch, a elección del integrador o diseñador, y por un conjunto de módulos controladores 331-335. Estos controladores son controladores de transferencia, y lo que hacen es adaptar el protocolo Wishbone a las interfaces FIFO. Por lo tanto, son 'controladores de memoria'. Todos 331-335 son arquitecturalmente iguales. En la figura 5, el número de bloques ctrl 331-335 y de sus FIFOs asociadas no es necesariamente 5, ya que esto depende de la implementación. De forma general, el número de bloques es #DSP+1 (número de DSPs utilizadas más uno). Esta misma consideración es aplicable a los módulos marcados como 142-145 (nótese que 141 sí es diferente del resto). Con respecto al módulo 12, la

10

15

20

25

30

35

figura 14 representa de forma esquemática diferentes variantes 12a, 12b, 12c, 12d de interconexión para adecuar el ancho de banda de entrada a los requerimientos de la aplicación. El bloque 14 está formado por un conjunto de módulos 141-145 que representan un conjunto de memorias FIFO circulares ligeramente modificadas: Hay un registro adicional en comparación con implementaciones convencionales. Este registro sustituye al puntero de lectura en la generación de la señal 'empty'. Estas memorias, junto con el controlador f ctrl 331-335 del módulo 12, controlador 331-335 asociado a cada una de ellas, actúan como almacenamiento temporal (scratchpads) de los datos que componen las matrices a procesar, de forma que se aprovecha la localidad tanto espacial como temporal de dichos datos. Un scratchpad es un tipo de memoria temporal, similar a una caché, pero con una lógica de control mucho más simple. Aún así, implica cierta lógica de gestión de direcciones. Típicamente las direcciones gestionadas pertenecen al espacio de memoria del microprocesador. En el caso del presente procesador, al interponer la MAI, el espacio de memoria no es el de ningún microprocesador, sino que tiene el tamaño necesario para diferenciar el volumen de datos concreto a gestionar. En suma, puede considerarse un conjunto de registros compartidos, sin mayor información sobre su procedencia o destino. El módulo 13 es, desde un punto de vista funcional, un multiplexor. Su función es dar paso a la realimentación 30 (figura 2). Es el módulo que permite transferir datos directamente del bloque 18 al 14 (figura 2). El patrón de acceso a las memorias FIFO 141-145 se ilustra más adelante en relación con la figura 6.

Los módulos 17-18 (figura 2) implementan la gestión de la información para guardar los resultados. El módulo 17 unifica en uno o varios streams los canales de salida del módulo 16. Lo hace de forma que el resultado esté ordenado como si el procesamiento se hubiera realizado en serie con un único DSP. El módulo 18 es una interconexión análoga al 12 (32). Es decir, un bus compartido o crossbar switch, con uno o varios controladores de transferencia. Como ya se ha dicho, los datos de realimentación salen del módulo 18, entran al módulo 13 y de ahí a su destino (módulo 14). Nótese que más adelante, en la figura 7, el elemento 180 está incluido en el módulo 17 (figura 2). A su vez, el elemento 190 en la figura 7 corresponde al bloque 18 en la figura 2. El módulo 19 es el módulo de control/orquestación. En la figura 7, más adelante, se representa como módulo de control 185. Éste contiene registros de configuración para programar el comportamiento del núcleo IP en tiempo de ejecución. A continuación se explican las conexiones entre módulos, qué información se transmite y qué protocolo puede usarse en cada conexión. La conexión 20 representa los puertos a través de los que se lee el contenido de las dos matrices utilizadas para computar el producto, de los periféricos (preferentemente

memorias) conectados a la MAI y/o a al AMBA Interconnect (ver figura 3). En una posible realización, estos puertos 20 son Maestros Wishbone B4 de solo lectura. Preferiblemente, los Maestros Wishbone B4 de solo lectura implementan el formato de direccionamiento virtual de la MAI, a través de los que leen el contenido de dichas matrices. El número de puertos 20 es definido por el usuario.

5

10

15

20

25

30

35

Entre los módulos 12 y 13 (el módulo 12 equivale al módulo swi 120 de la figura 7 y el módulo 13 corresponde a una generalización del módulo 130 de la figura 7) se establecen dos interfaces 21, 22 FIFO (First In First Out) de escritura. La interfaz 21 corresponde a la matriz de entrada y la interfaz 22 corresponde a la matriz de pesos. El número de puertos se deriva automáticamente de los parámetros definidos por el usuario. Entre los módulos 13 y 14 se establecen dos interfaces 23, 24 FIFO de escritura. Como en el caso de las interfaces 21, 22, la interfaz 23 corresponde a la matriz de entrada y la interfaz 24 corresponde a la matriz de pesos. En cuanto a las interfaces 25, 26 entre los módulos 14, 15, se trata de interfaces FIFO de lectura ligeramente modificadas que, como en los casos anteriores, corresponden respectivamente a la matriz de entrada y a la matriz de pesos. Las referidas modificaciones se detallan en la figura 6. El número de puertos se deriva automáticamente de los parámetros definidos por el usuario. Entre el módulo 15, en el que se realizan las operaciones aritméticas para computar productos vectoriales que conformen un producto matricial, y el módulo 16, en el que opcionalmente se realiza la transformación no lineal, se establecen unas interfaces 27 FIFO de escritura, a través de las que se transfiere el resultado del producto matricial de los DSP del módulo 15 a las funciones de activación, opcionales, del módulo 16. El número de puertos se deriva automáticamente de los parámetros definidos por el usuario. Entre el módulo 16, en el que opcionalmente se realiza la transformación no lineal, y el módulo 17, se establecen unas interfaces 28 FIFO de escritura. En implementaciones de la invención, el módulo de las funciones de activación 16 puede diseñarse de forma que sea transparente en lo que respecta a la interfaz 28. Los datos transmitidos en esta interfaz 28 son el resultado final de la capa (ya sea la capa oculta, que se computa primero; o la capa de salida, que se computa después). El número de puertos se deriva automáticamente de los parámetros definidos por el usuario. Entre el módulo 17 y el módulo 18 se establecen unas interfaces 29 FIFO de escritura. En implementaciones de la invención, el módulo 17 puede diseñarse de forma que sea transparente en lo que respecta a la interfaz 29. Los datos son transmitidos al módulo 17 a través de la interfaz 28. Estos datos pueden opcionalmente serializarse y/o reordenarse. El número de puertos es definido por el usuario. Entre el módulo 18 y el módulo 13 se establecen unas interfaces 30 FIFO de lectura y escritura que proporcionan realimentación al núcleo IP 1. Los datos son transmitidos al módulo 18 a través de la interfaz 29. El número de puertos es definido por el usuario.

5

10

15

20

25

30

35

La conexión 31 representa los puertos a través de los que se escribe, por ejemplo en módulos periféricos, el resultado de la computación ejecutada en el núcleo IP 1. Los periféricos en los que se escribe el resultado pueden ser, por ejemplo, memorias. Estos periféricos suelen estar conectados a la MAI y/o a al AMBA Interconnect (ver figura 3). En una posible realización, estos puertos 31 son Maestros Wishbone B4 de solo escritura. Preferiblemente, los Maestros Wishbone B4 de solo escritura implementan el formato de direccionamiento virtual de la MAI. El número de puertos es definido por el usuario. Por otro lado, las líneas discontinuas entre el módulo de control 19 y los módulos 12-18 representan conexiones ad-hoc para la distribución de parámetros de ejecución desde dicho módulo 19. El tipo de interfaz que implementa estas conexiones es preferentemente memoria/registros direccionables. Puesto que preferentemente su profundidad es de entre 2 y 6 direcciones, el impacto del direccionamiento es despreciable. Por último, la flecha bidireccional a la izquierda del módulo 19 es un puerto es escritura/lectura utilizado para programar el coprocesador (núcleo IP 1) en tiempo de ejecución. A través del mismo se modifican los registros del módulo/componente 19, que después son interpretados y distribuidos automáticamente al resto de componentes. En una posible realización, este puerto es un esclavo Wishbone B4. En otras palabras, la capacidad de programación en tiempo de ejecución se consigue proveyendo un puerto de escritura/lectura que permite interactuar con el módulo 19. Éste incluye una serie de registros y varias máquinas de estado básicas, tales como máquinas de estado basadas en dos o tres bits de estado, que permiten automatizar la modificación del comportamiento de la arquitectura.

La figura 6 ilustra el patrón de acceso a las memorias FIFO 141-145 mostradas en la figura 5, de acuerdo con una posible implementación de la invención. Concretamente, se ha representado el patrón de acceso a las memorias FIFO 141-145 en un ejemplo que corresponde a la multiplicación de una matriz de tres filas por otra de cuatro filas (siendo independiente del número de columnas, que debe ser igual) teniendo en cuenta la posibilidad de aplicar el plegado de una capa de un modelo de red neuronal en un número determinado de DSPs. La referencia 14(i) se refiere a la primera memoria FIFO 141 de la figura 5, mientras que la referencia 14(b<sub>?</sub>) se refiere al resto de memorias FIFO 142-145 de la figura 5. Como puede observarse, la memoria 141 (14(i) en la figura 6) muestra mayor localidad temporal de los datos, leyéndose un mismo vector varias veces

10

15

20

25

30

35

de forma consecutiva. En el caso de la memoria 142-145 (14(b<sub>2</sub>) en la figura 6), hay localidad espacial equivalente (en ambos casos la lectura es vectorial), pero se observa un comportamiento menos favorable al aprovechamiento temporal. Nótese que, en caso de utilizar FIFOs circulares sin modificar, cada vector sólo puede ser leído una sola vez antes de que pueda ser sobreescrito. Por ello, las modificaciones realizadas se basan en la duplicación del registro de lectura: En la memoria 141 (también llamada 14(i)), existen dos señales de un solo bit adicionales a una memoria FIFO corriente. Una primera de ellas guarda el valor del puntero de lectura en registro de respaldo, que es el utilizado para general la señal full. La segunda de esas señales permite retornar el puntero de lectura efectivo al valor registrado. En la memoria 142-145 (también llamada 14(b2)), existe una sola señal adicional. Ya que la lectura de los vectores correspondientes a múltiples pliegues (folds) consecutivos es secuencial, únicamente se dispone de la señal que permite volver al inicio. Adicionalmente, en aplicaciones que requieran procesar productos con diferentes matrices (tal es el caso, por ejemplo, cuando se usan kernels privados en vez de kernels públicos en redes profundas), las memorias 142-145 (también llamadas 14(b<sub>2</sub>)) se pueden implementar con las mismas modificaciones que la memoria 141 (también llamada 14(i)), de forma que se aproveche todo el espacio disponible, cargando kernels tan pronto como los anteriores dejan de utilizarse.

La figura 7 ilustra un posible ejemplo de implementación de un núcleo IP 100 de acuerdo con la invención. Este ejemplo responde a una implementación según cierta parametrización. Nótese que existen muchas posibilidades alternativas de síntesis. Los datos de entrada, que se transfieren a través del puerto 101 (20 en la figura 2) son los vectores que componen las dos matrices cuyo producto se va a computar. Los datos correspondientes a una de las matrices se transfieren únicamente a la FIFO 'i' (140i en la figura 7, 141 en la figura 5) del bloque 140 (bloque 14 en las figuras 2 y 5) mientras que los datos correspondientes a la otra matriz se distribuyen en las FIFOS 'b<sub>0</sub>...b<sub>9</sub>'  $(140_{b0}...140_{b9}$  en la figura 7) del bloque 140. El sub-módulo 320 (32 en la figura 5) del bloque 120 (bloque 12 en las figuras 2 y 5) puede ser un bus compartido o un crossbar switch, según se configure. En el caso de que sea un crossbar switch, se dispone de más de un puerto de entrada, por lo que se implementan varias instancias de los puertos para la entrada de datos 101. El árbitro de la interconexión, que se implementa en el bloque de intercon si (320 en la figura 7, 32 en la figura 5), actúa de doble maestro y convierte los índices facilitados por los módulos 3301-3311 del bloque 120 (convierte la interfaz Wishbone en interfaz FIFO). Nótese que actuar como doble maestro quiere decir que tanto la MAI 200 como los módulos 3301-3311 son esclavos, por lo que es el árbitro quien inicia y finaliza para transferencia. Los módulos 3301-3311 son conversores de protocolo, en este ejemplo, de esclavo Wishbone a interfaz FIFO. La dirección está compuesta por dos índices, que son contadores encadenados. El valor de límite de cuenta de cada uno de ellos depende del valor de los registros de control en tiempo de ejecución.

5

10

15

20

25

30