# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 701 833

(51) Int. CI.:

H03M 13/25 (2006.01) H03M 13/27 (2006.01) H03M 13/35 (2006.01) H03M 13/11 (2006.01) H03M 13/29 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

Fecha de presentación y número de la solicitud europea: 18.05.2012 E 15172081 (0)

Fecha y número de publicación de la concesión europea: 19.09.2018 EP 2940877

(54) Título: Entrelazador de bits para un sistema BICM con códigos de tipo QC LDPC

(30) Prioridad:

18.05.2011 EP 11004127

Fecha de publicación y mención en BOPI de la traducción de la patente: **26.02.2019**

(73) Titular/es:

PANASONIC CORPORATION (100.0%) 1006, Oaza Kadoma Kadoma-shi, Osaka 571-8501, JP

(72) Inventor/es:

PETROV, MIHAIL

74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

#### **DESCRIPCIÓN**

Entrelazador de bits para un sistema BICM con códigos de tipo QC LDPC

La presente divulgación se refiere al campo de las comunicaciones digitales, y más específicamente a un entrelazador de bits para un sistema de codificación y modulación de entrelazado de bits con códigos cuasi cíclicos de comprobación de paridad de baja densidad.

En los últimos años, los sistemas de codificación y modulación de entrelazado de bits (de aquí en adelante, BICM), se han usado en el campo de las comunicaciones digitales (véase, por ejemplo, las normas DVB-T2 ETSI EN 302 755 V1.2.1).

Los sistemas BICM incorporan generalmente las siguientes tres etapas.

- 10 (1) La codificación de bloques de datos en palabras de código que usan, por ejemplo, códigos cuasi cíclicos de comprobación de paridad de baja densidad (de aquí en adelante, QC LDPC) o similares.

- (2) La realización del entrelazado de bits en los bits de cada palabra de código.

- (3) División de cada palabra de código con entrelazado de bits en una constelación de palabras que tienen un cierto número de constelaciones de bits, y el mapeado de las palabras de la constelación a constelaciones.

- 15 Se describe un entrelazador convencional para modulación codificada entrelazada de bits de códigos de comprobación de paridad de baja densidad, por ejemplo, en el artículo "Macro Interleaver Design for Bit Interleaved Coded Modulation with Low-Density Parity-Check Codes" por Frank Kienle y Norbert Wehn (IEEE Vehicular Technology Conference, VTC, Spring 2008. Piscataway, NJ, Estados Unidos).

- Normalmente, se desea eficacia en un entrelazado aplicado a las palabras de código de códigos de comprobación de paridad de baja densidad casi cíclica.

- La presente invención aborda esta necesidad proporcionando un método de entrelazado de bits que permita que se aplique un entrelazado eficiente a las palabras de código de los códigos cuasi cíclicos de comprobación de paridad de baja densidad, así como a un entrelazador de bits correspondiente, un método de procesamiento de señal y un procesador de señal.

- La invención es establece en la primera realización con *N* no siendo un múltiple de *M* y en la tercera realización con *F*=1 (sin plegado). Las otras realizaciones son ejemplos que no forman parte de la invención pero que representan los antecedentes de la técnica, que es útil para entender la invención. El ámbito de la invención se define en las reivindicaciones adjuntas.

#### [Breve descripción de los dibujos]

35

45

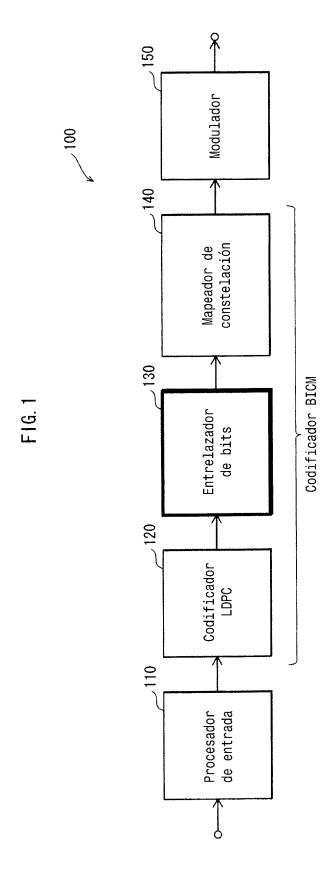

- 30 La Fig. 1 es un diagrama de bloques que muestra la configuración de un transmisor que incluye un codificador BICM típico.

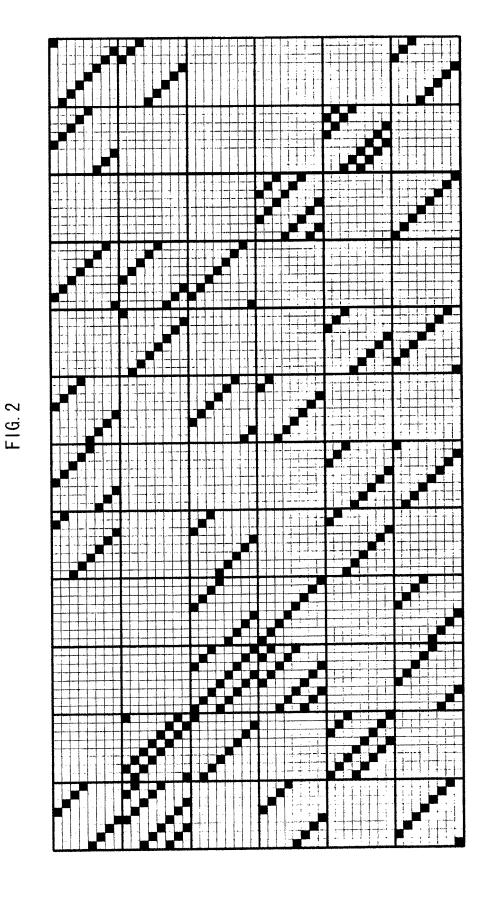

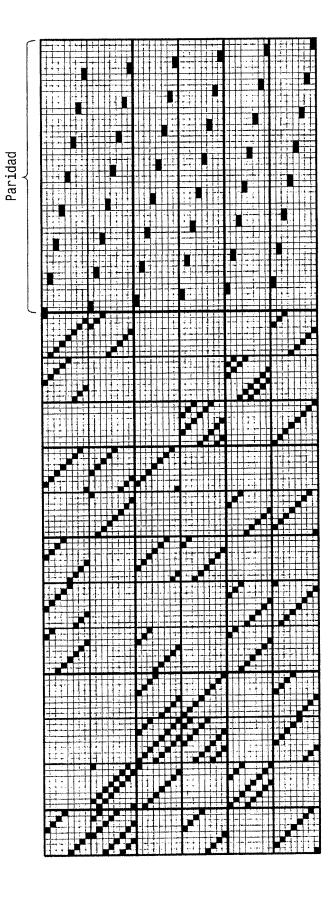

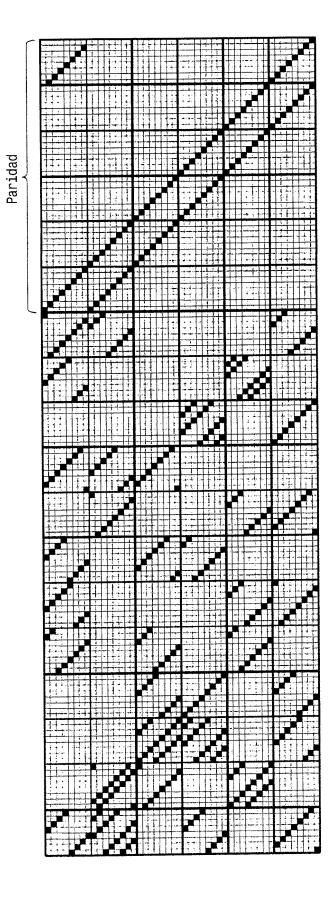

- La Fig. 2 ilustra un ejemplo de una matriz de comprobación de paridad para códigos cuasi cíclicos de comprobación de paridad de baja densidad que tengan una tasa decodificación de 1/2.

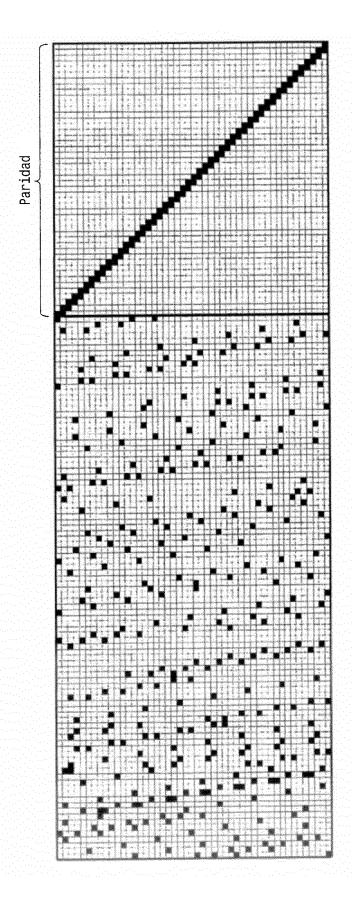

- La Fig. 3 ilustra un ejemplo de una matriz de comprobación de paridad para códigos cuasi cíclicos de comprobación de paridad de baja densidad de acumulación repetitiva que tengan una tasa de codificación de 2/3.

- La Fig. 4 ilustra una matriz de comprobación de paridad para los códigos cuasi cíclicos de comprobación de paridad de baja densidad de acumulación repetitiva de la Fig. 3 después de una permutación de filas.

- La Fig. 5 ilustra una matriz de comprobación de paridad para los códigos cuasi cíclicos de comprobación de paridad de baja densidad de acumulación repetitiva de la Fig. 3 después de una permutación de filas y una permutación de paridad.

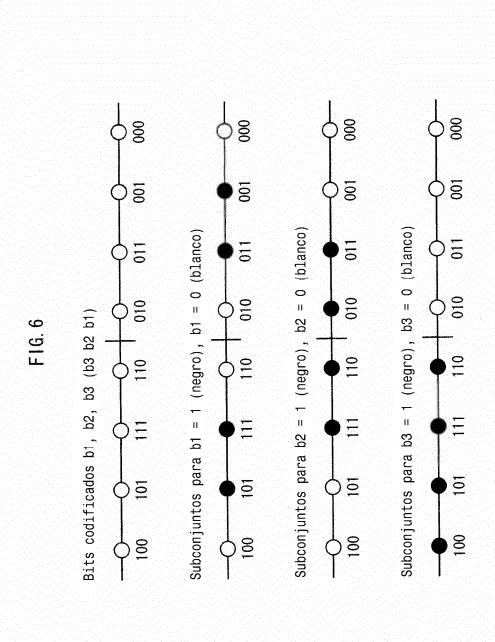

- La Fig. 6 describe niveles de robustez diferentes de los bits codificados en ocho símbolos PAM.

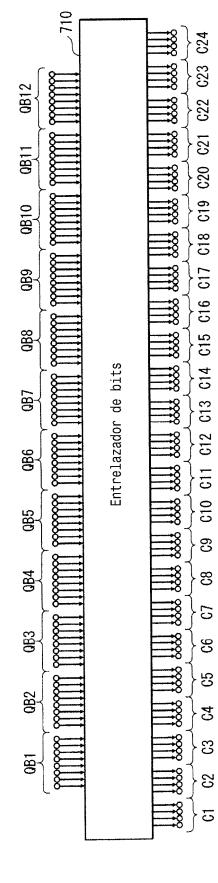

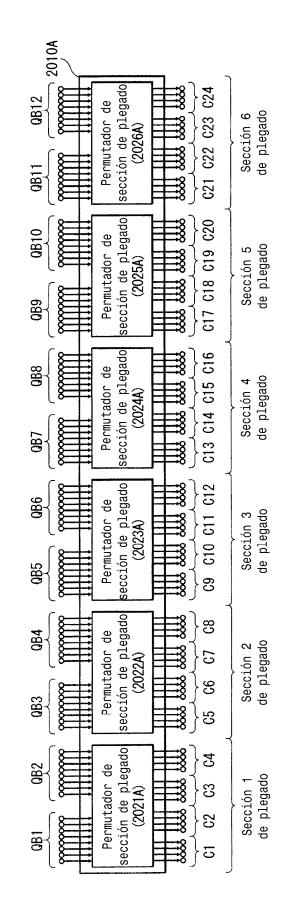

- La Fig. 7 es un diagrama de bloques que muestra la configuración de un entrelazador de bits típico en el que el factor cíclico Q es 8, el número de bloques cíclicos por palabra de código de comprobación de paridad de baja densidad N es 12 y el número de bits por constelación M es 4.

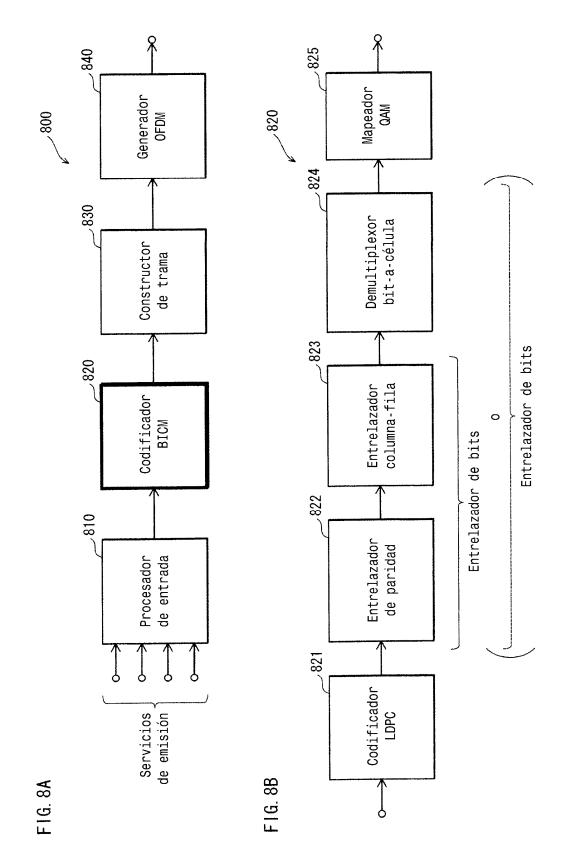

- La Fig. 8A es un diagrama de bloques que muestra la configuración de un modulador DVB-T2 usado en la norma DVB-T2, y la Fig. 8B es un diagrama de bloques que muestra la configuración de un codificador BICM para el modulador DVB-T2 de la Fig. 8A.

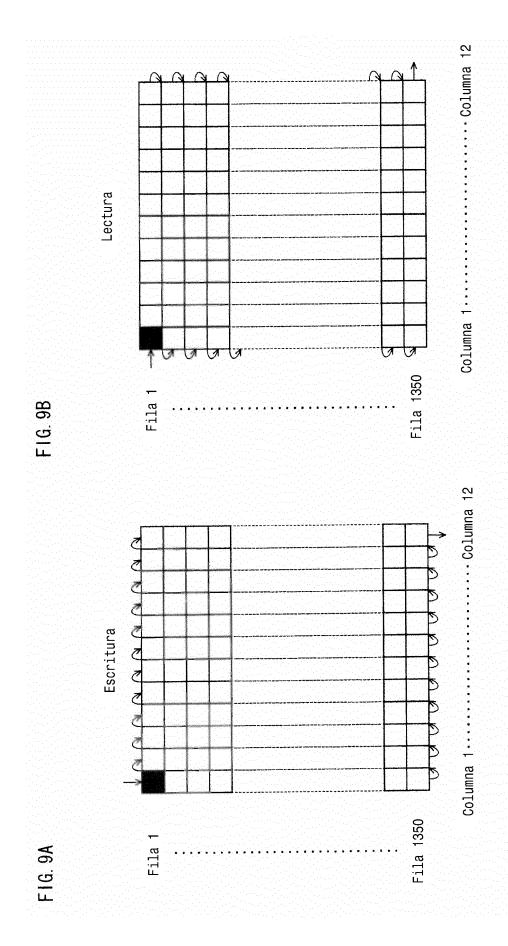

- la Fig. 9A ilustra un proceso de escritura para los bits de una palabra de código de 16K (es decir, un código LDPC en el que la longitud de la palabra de código LDPC es de 16200 bits) tal como se realiza por un entrelazador de columna-fila que tenga doce columnas, y la Fig. 9B ilustra un proceso de lectura para los bits de la palabra de código escrita en la forma indicada por la Fig. 9A tal como se ha realizado por el entrelazador de columna-fila.

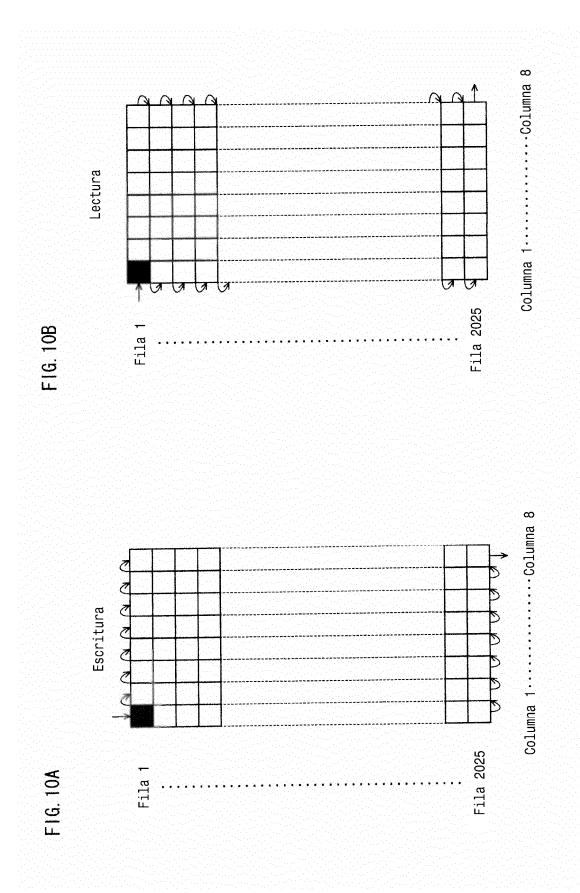

- La Fig. 10A ilustra un proceso de escritura para los bits de una palabra de código de 16K tal como se realiza por un entrelazador de columna-fila que tenga ocho columnas, y la Fig. 10B ilustra un proceso de lectura para los bits

- de la palabra de código escritos en la manera indicada por la Fig. 10A tal como se ha realizado por el entrelazador de columna-fila.

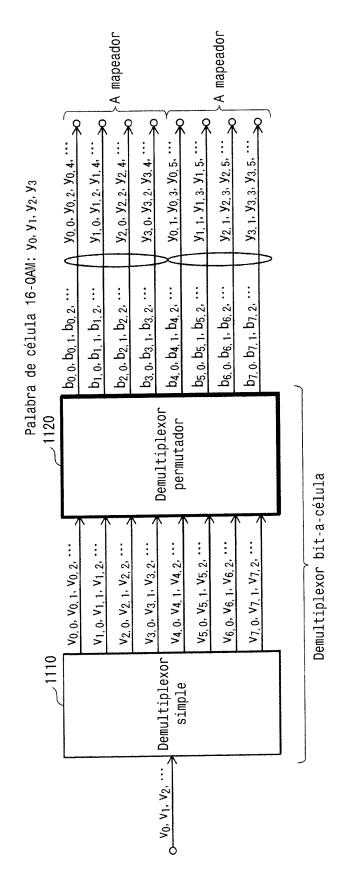

- La Fig. 11 es un diagrama de bloques que muestra la configuración de un demultiplexor de bits-a-célula usado para códigos de 16K 16-QAM en la norma DVB-T2.

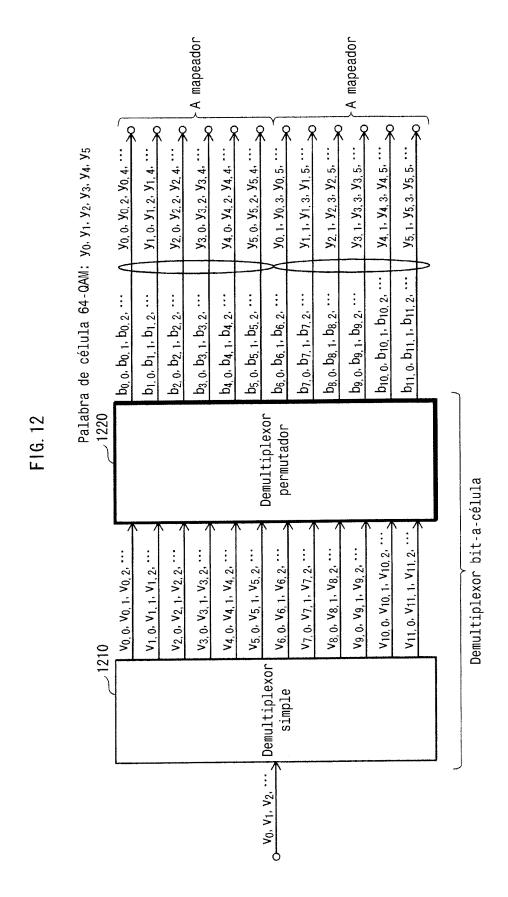

- La Fig. 12 es un diagrama de bloques que muestra la configuración de un demultiplexor de bits-a-célula usado para códigos de 16K 64-QAM en la norma DVB-T2.

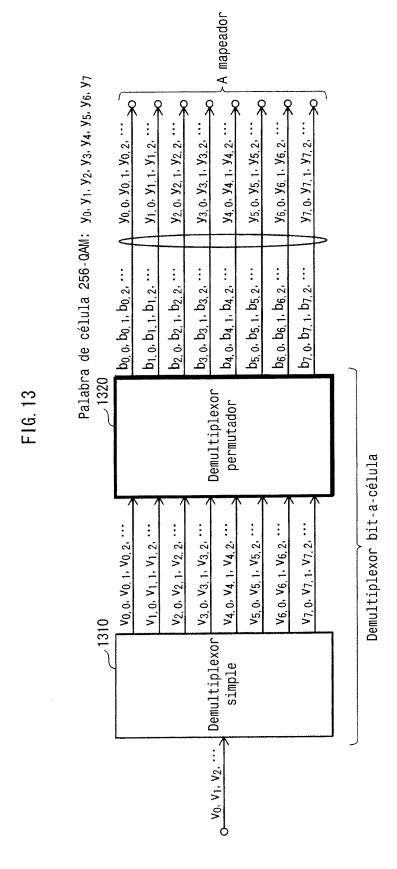

- La Fig. 13 es un diagrama de bloques que muestra la configuración de un demultiplexor de bits-a-célula usado para códigos de 16K 256-QAM en la norma DVB-T2.

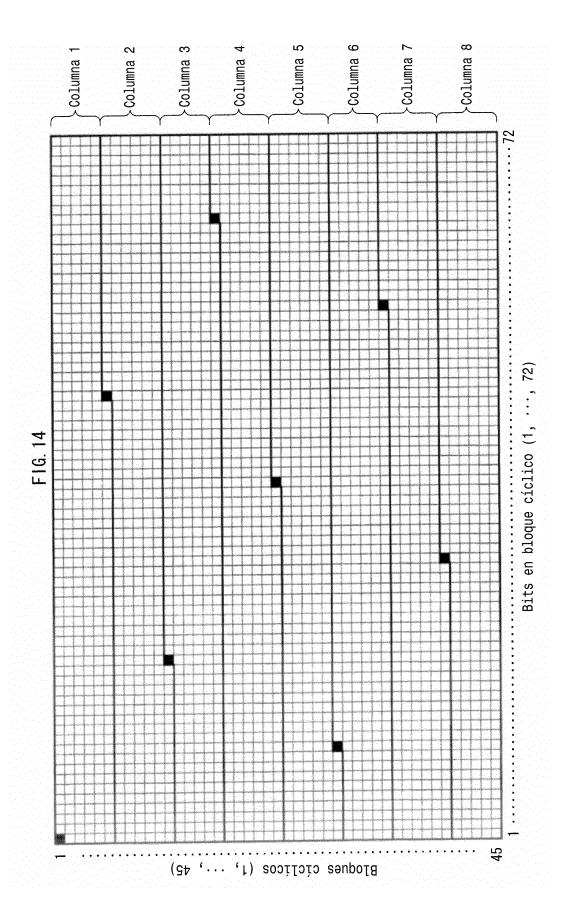

- La Fig. 14 ilustra un problema que ocurre para los códigos de 16K con un entrelazador de bits DVB-T2 de ocho columnas.

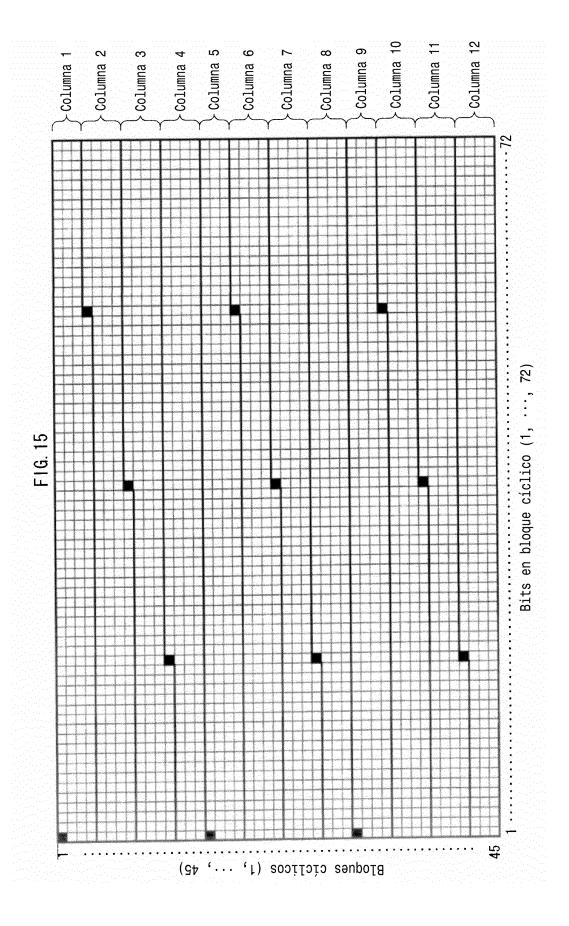

- La Fig. 15 ilustra un problema que ocurre para los códigos de 16K con un entrelazador de bits DVB-T2 de doce columnas.

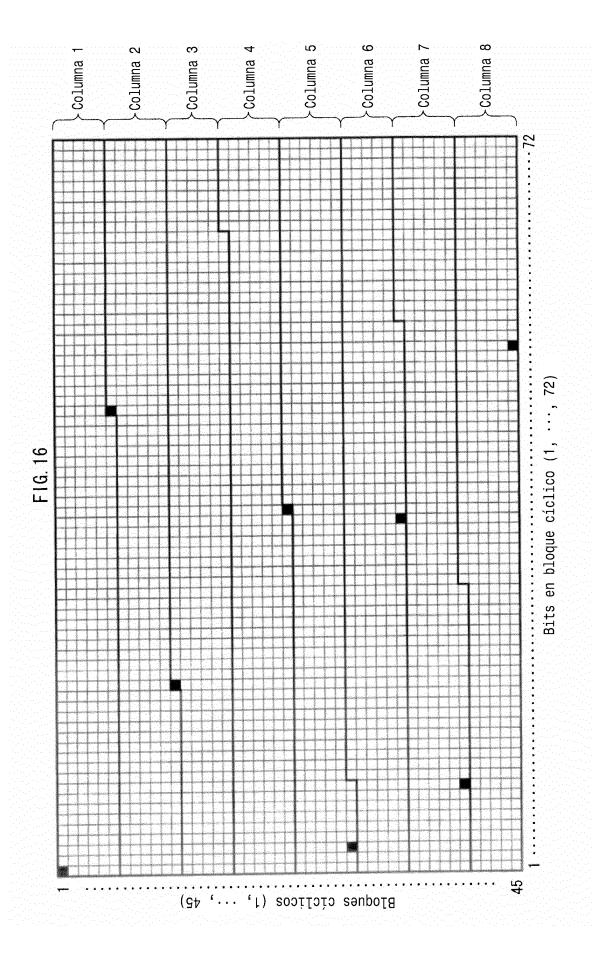

- La Fig. 16 ilustra un problema que ocurre para los códigos de 16K con un entrelazador de bits DVB-T2 de ocho columnas cuando se aplica giro de columna.

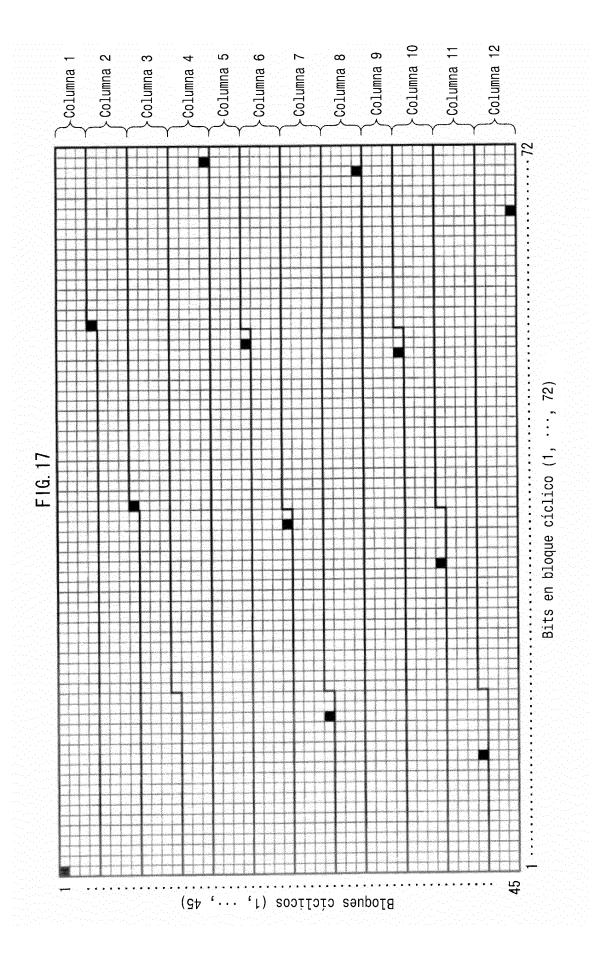

- La Fig. 17 ilustra un problema que ocurre para los códigos de 16K con un entrelazador de bits DVB-T2 de doce columnas cuando se aplica giro de columna.

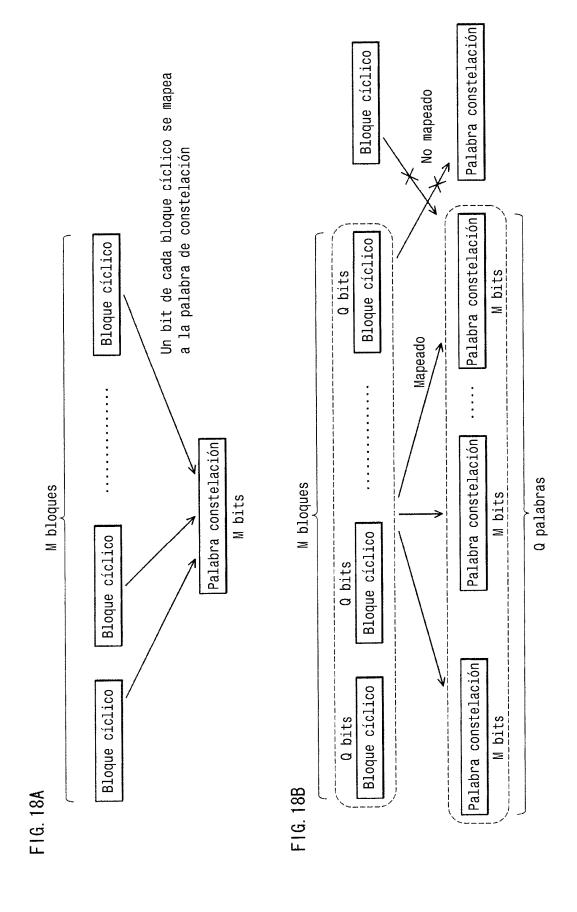

- Las Figs. 18A y 18B ilustran respectivamente una primera y segunda condición descubierta por los presentes inventores que permite que se proporcione un entrelazador extremadamente efectivo.

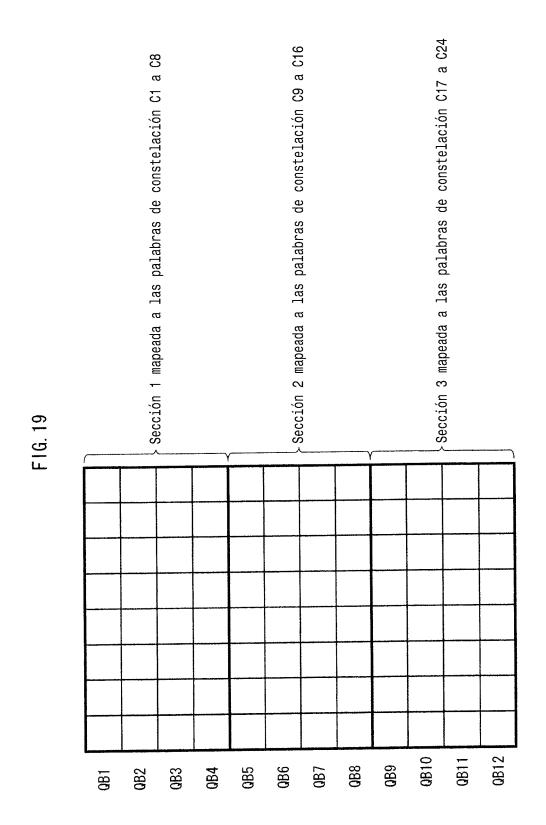

- La Fig. 19 ilustra una función de mapeado por un entrelazador que pertenece a una realización.

10

45

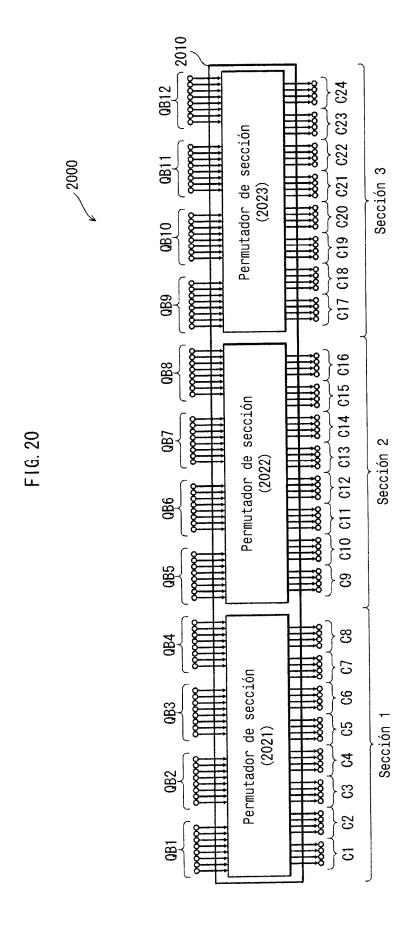

- La Fig. 20 es un diagrama de bloques que muestra la configuración de un entrelazador que pertenece a una Realización

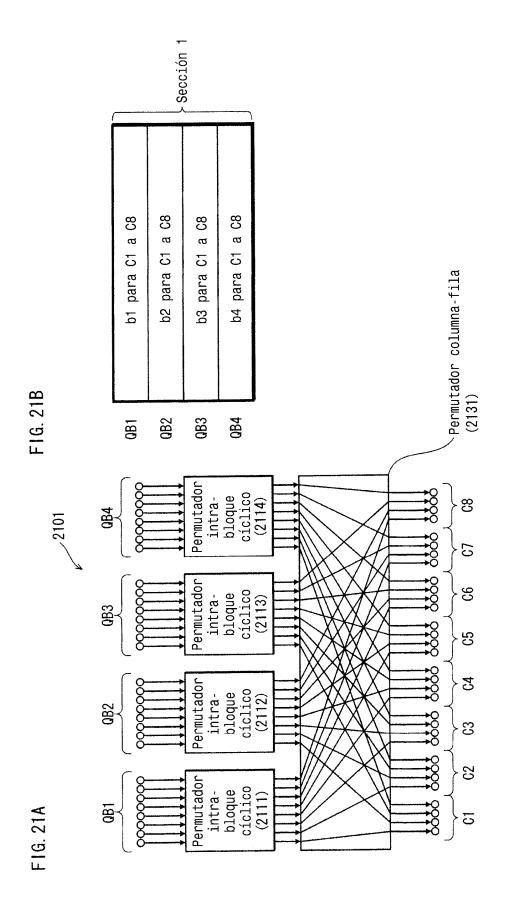

- La Fig. 21A es un diagrama de bloques que muestra la configuración de un permutador de sección que realiza la permutación de la sección ilustrada en la Fig. 20, y la Fig. 21B ilustra una función de mapeado del permutador de sección mostrado en la Fig. 21A.

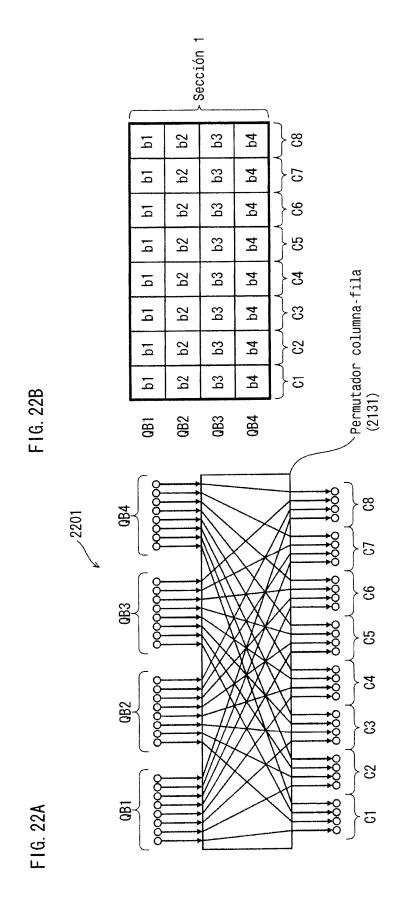

- La Fig. 22A es un diagrama de bloques que muestra una configuración alternativa de un permutador de sección que realiza la permutación de sección ilustrada en la Fig. 20, y la Fig. 22B ilustra una función de mapeado del permutador de sección mostrado en la Fig. 22A.

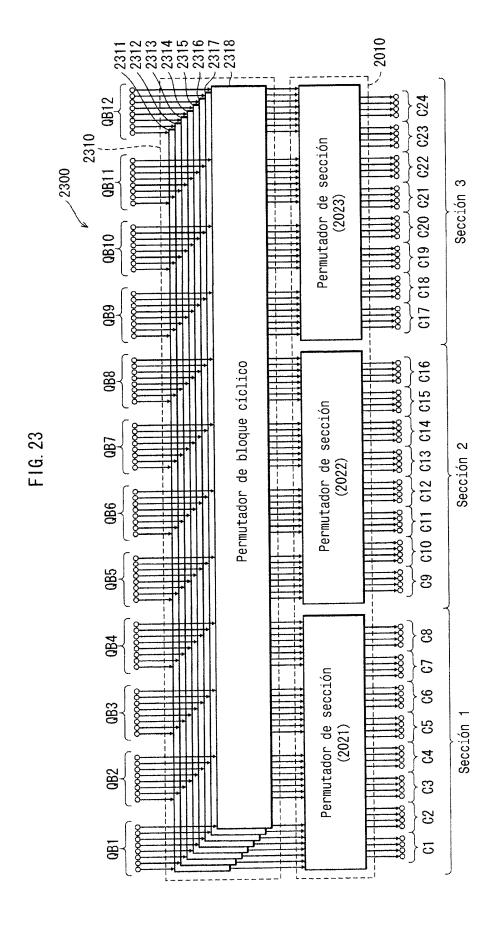

- La Fig. 23 es un diagrama de bloques que muestra la configuración de un entrelazador que pertenece a otra Realización.

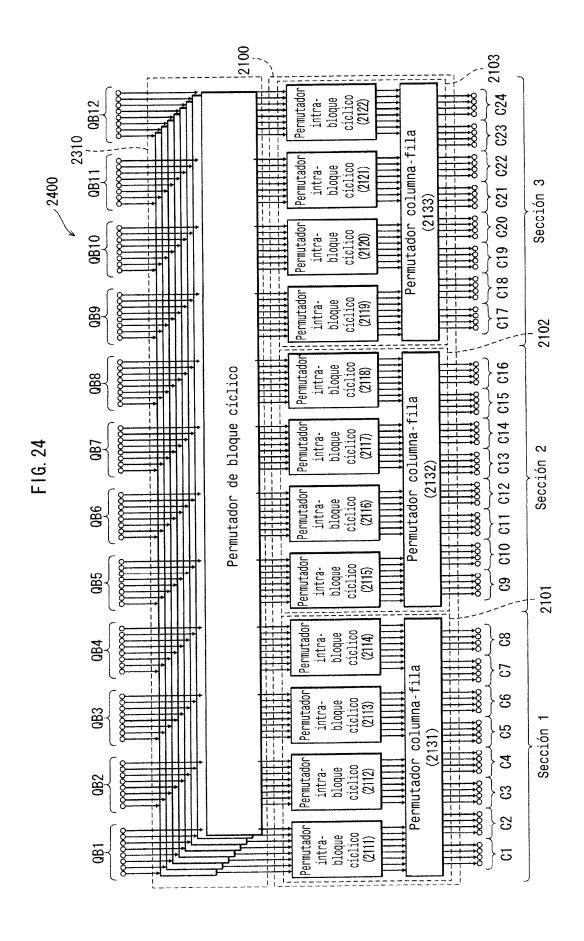

- La Fig. 24 es un diagrama de bloques que muestra la configuración del entrelazador de bits mostrado en la Fig. 23.

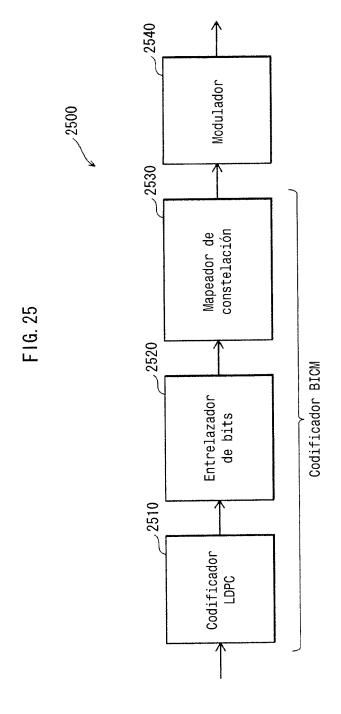

- La Fig. 25 es un diagrama de bloques que muestra la configuración de un transmisor que pertenece a una realización adicional.

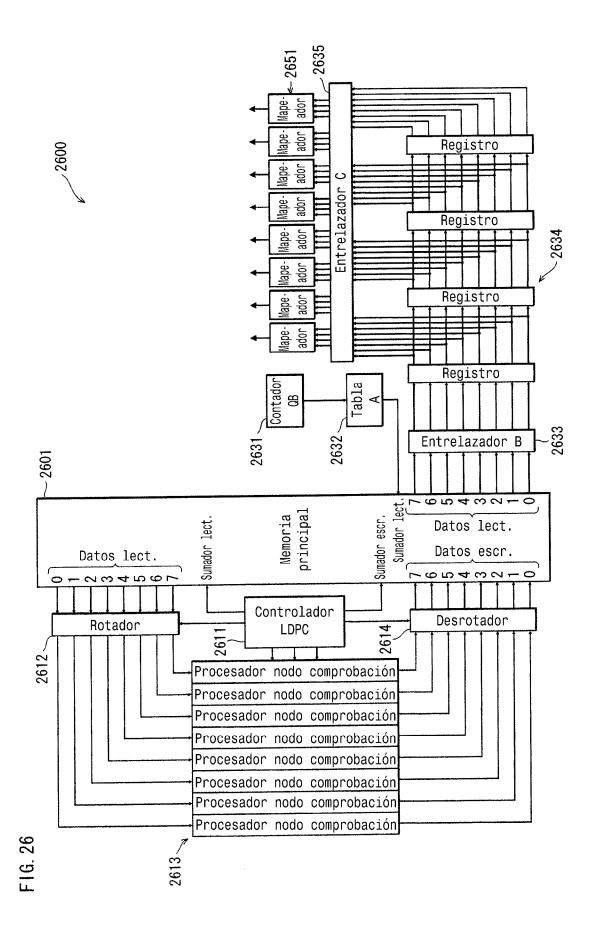

- La Fig. 26 es un diagrama de bloques que muestra la configuración de un codificador BICM que pertenece a una realización adicional.

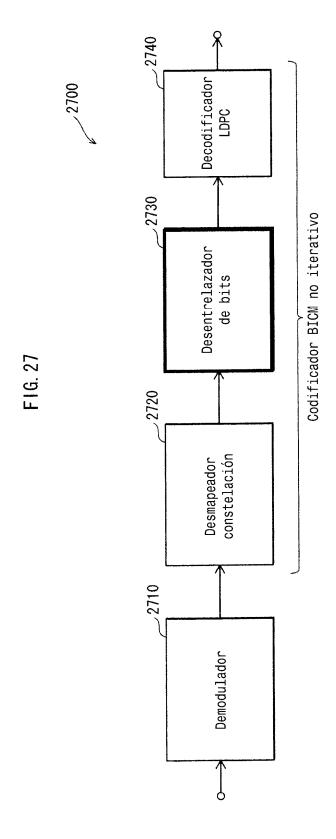

- La Fig. 27 es un diagrama de bloques de un receptor que incluye un decodificador BICM no iterativo, que pertenece a una realización adicional.

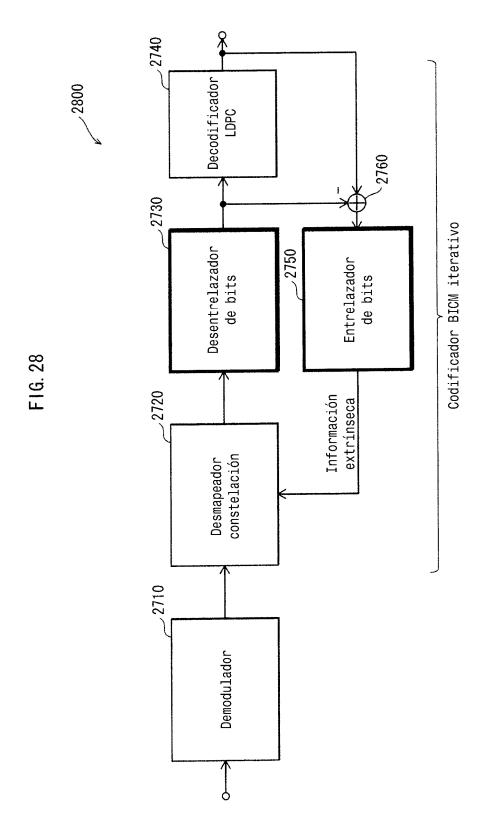

- La Fig. 28 es un diagrama de bloques que muestra la configuración de un receptor que incluye un decodificador BICM iterativo, que pertenece a una realización adicional.

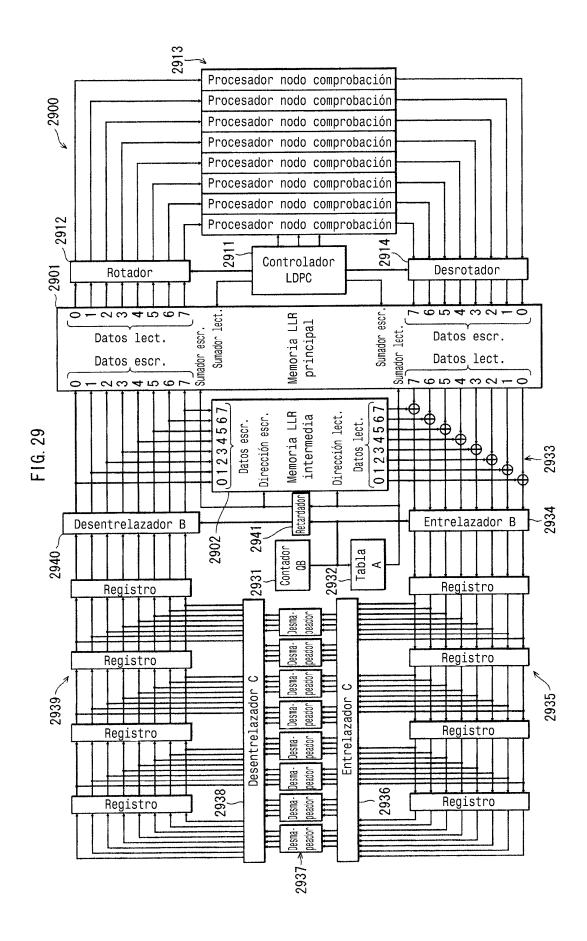

- 40 La Fig. 29 es un diagrama de bloques que muestra la configuración de un decodificador BICM iterativo que pertenece a una realización adicional.

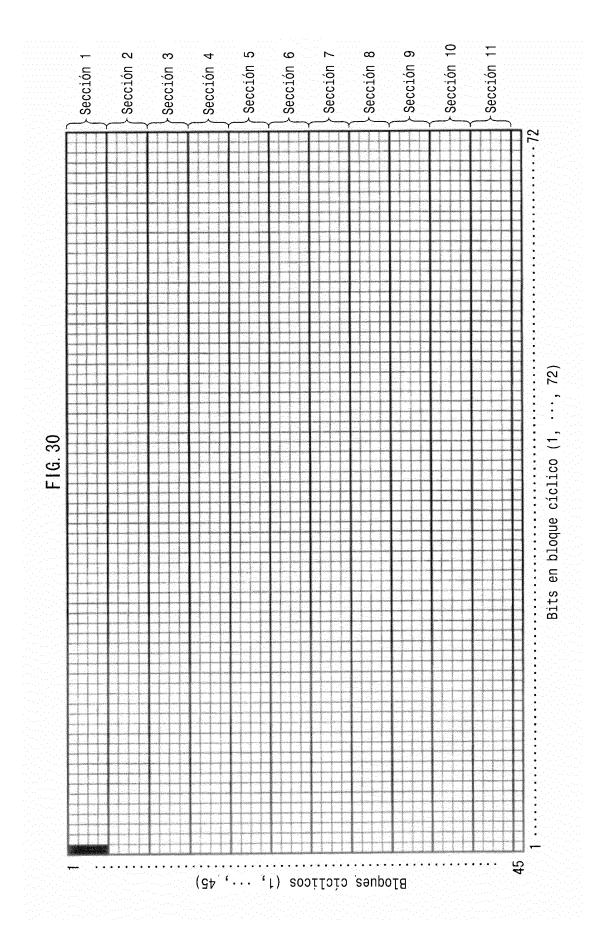

- La Fig. 30 ilustra un ejemplo de bloques cíclicos incluidos en, y excluidos de, un proceso de entrelazado en paralelo.

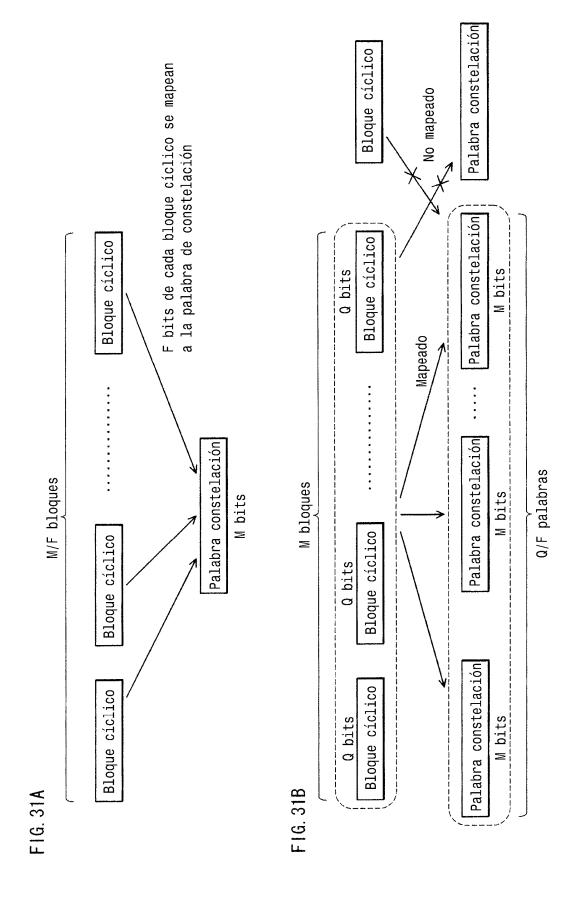

- Las Figs. 31A y 31B ilustran respectivamente una primera y segunda condiciones descubiertas por los presentes inventores que permiten que se proporcione un entrelazador extremadamente efectivo.

- La Fig. 32 es un diagrama de bloques que muestra la configuración de un entrelazador que pertenece a otra Realización.

- La Fig. 33A ilustra una función de mapeado para una situación sin plegado (F = 1), y la Fig. 33B ilustra una función de mapeado para una situación con plegado (F = 2).

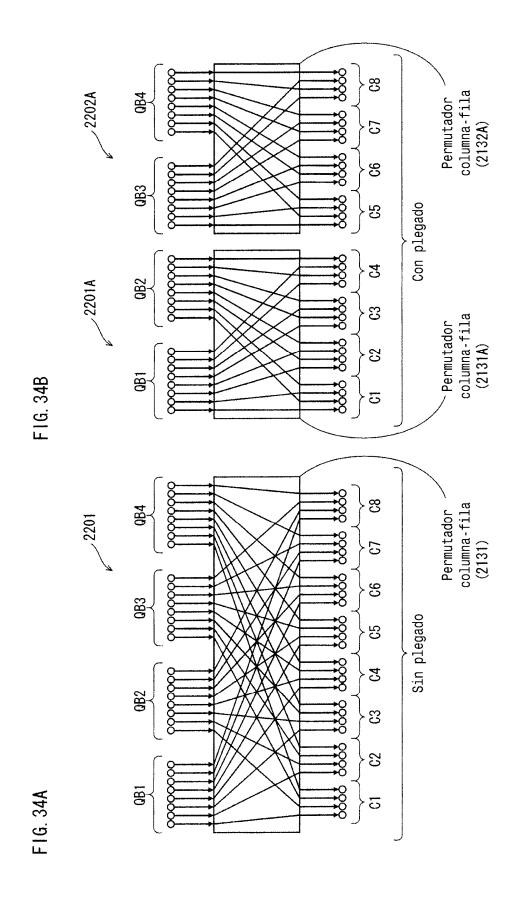

- La Fig. 34A es un diagrama de bloques que muestra la configuración de un permutador de sección (plegado) para la situación sin plegado (*F* = 1), y la Fig. 34B es un diagrama de bloques que muestra la configuración de un permutador de sección de plegado para la situación con plegado (*F* = 2).

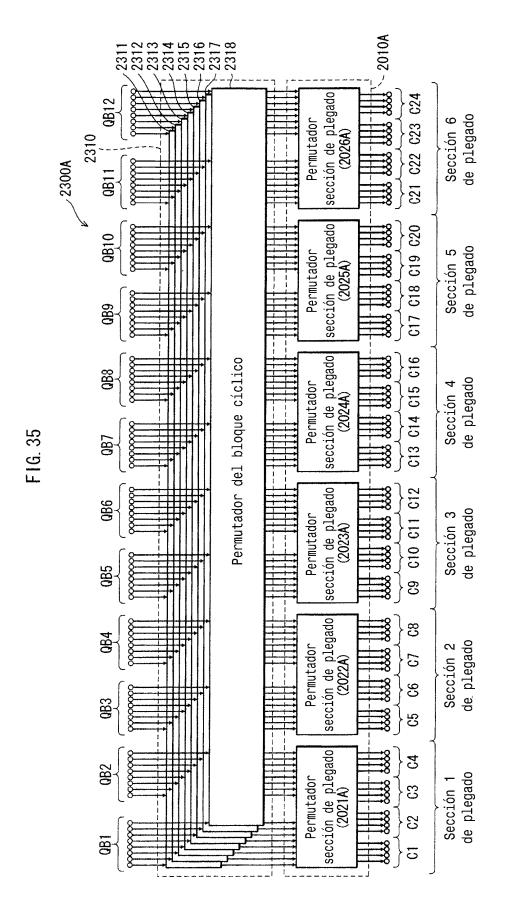

- La Fig. 35 es un diagrama de bloques que muestra la configuración de un entrelazador que pertenece a otra Realización.

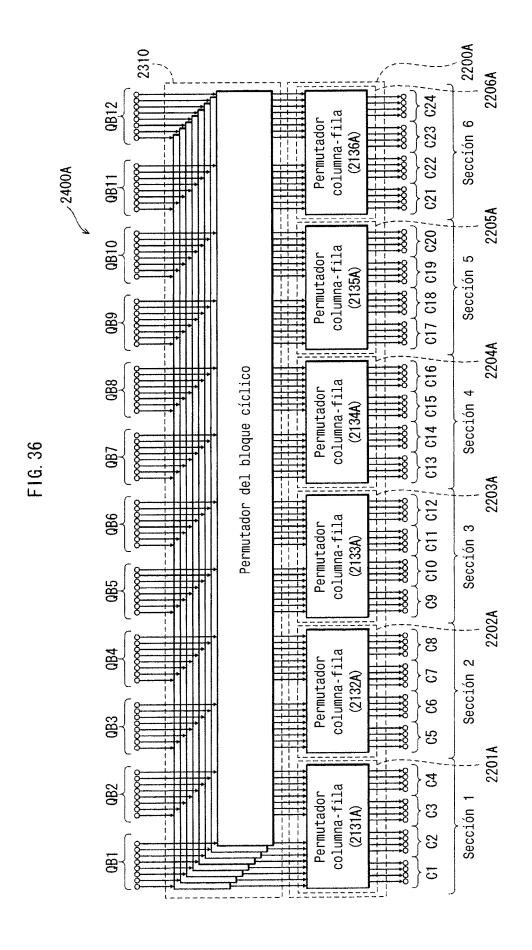

- La Fig. 36 es un diagrama de bloques que muestra la configuración del entrelazador de bits mostrado en la Fig. 35

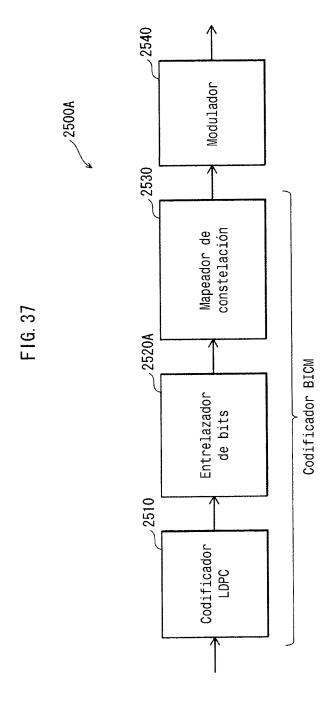

- La Fig. 37 es un diagrama de bloques que muestra la configuración de un transmisor que pertenece a una realización adicional.

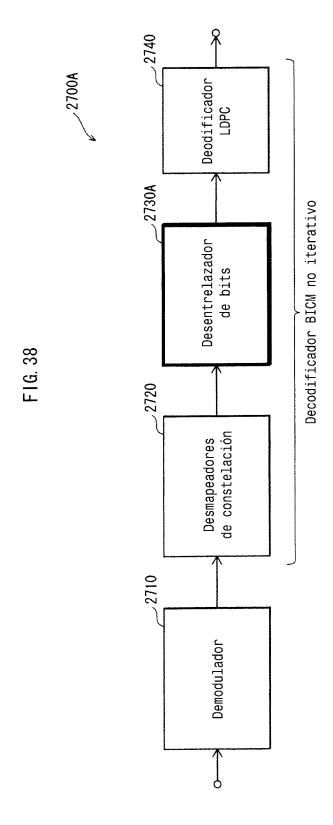

- La Fig. 38 es un diagrama de bloques de un receptor que incluye un decodificador BICM no iterativo, que pertenece a una realización adicional.

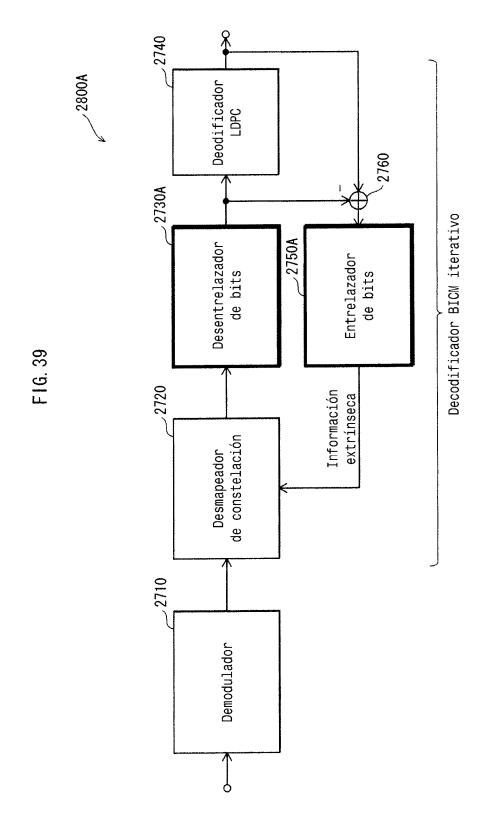

- La Fig. 39 es un diagrama de bloques que muestra la configuración de un receptor que incluye un decodificador BICM iterativo, que pertenece a una realización adicional.

- La Fig. 40 ilustra localizaciones de memoria LLR para plegado con F = 2, y posiciones de bits para la primera palabra de constelación.

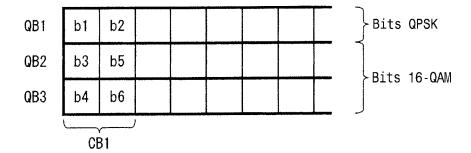

- La Fig. 41 representa esquemáticamente el mapeado de bloques de constelación que pertenecen a los códigos QPSK+16-QAM híbridos.

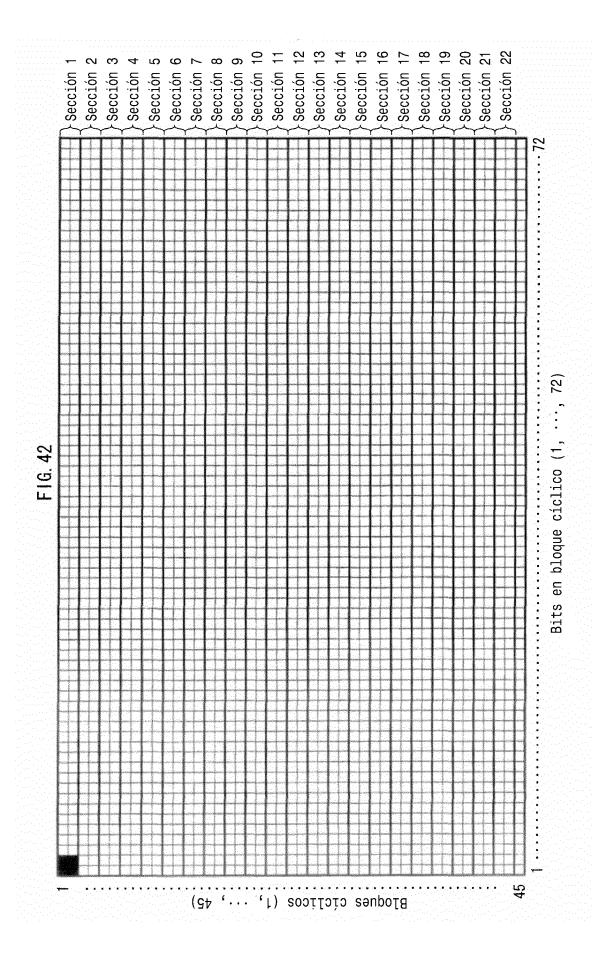

La Fig. 42 es un diagrama de bloques que muestra la configuración de un entrelazador que pertenece a otra realización.

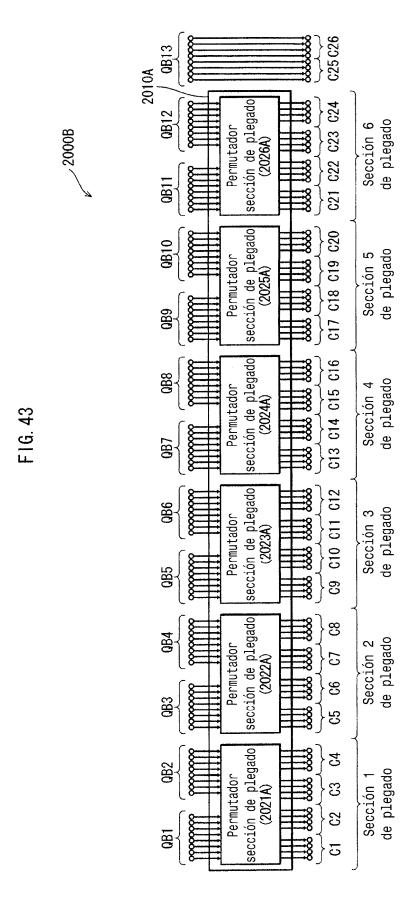

La Fig. 43 es un diagrama de bloques que muestra la configuración de un entrelazador que pertenece a otra realización.

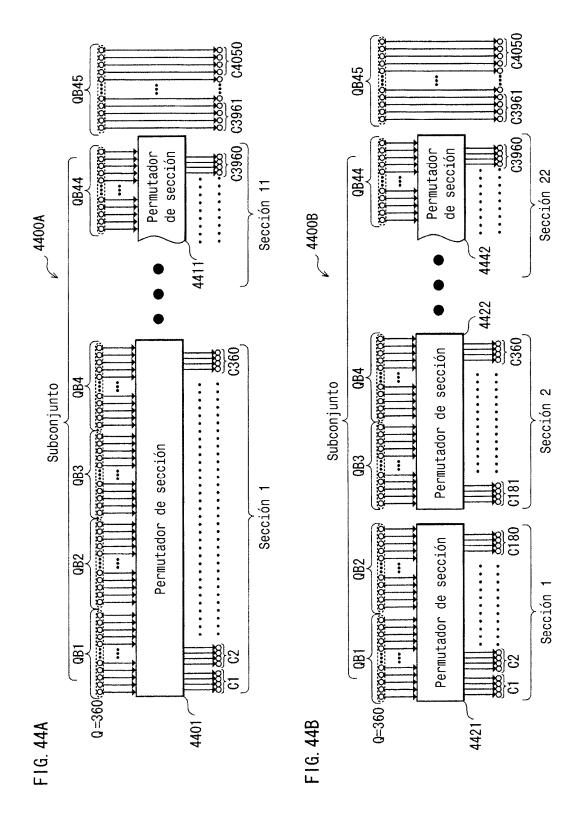

Las Figs. 44A y 44B son diagramas de bloques que muestran las configuraciones de ejemplo de entrelazadores que pertenecen a otra realización; teniendo la Fig. 44A N = 45, Q = 360, M = 6, y F = 1 (sin plegado), y teniendo la Fig. 44B N = 45, Q = 360, M = 6, y F = 2 (con plegado).

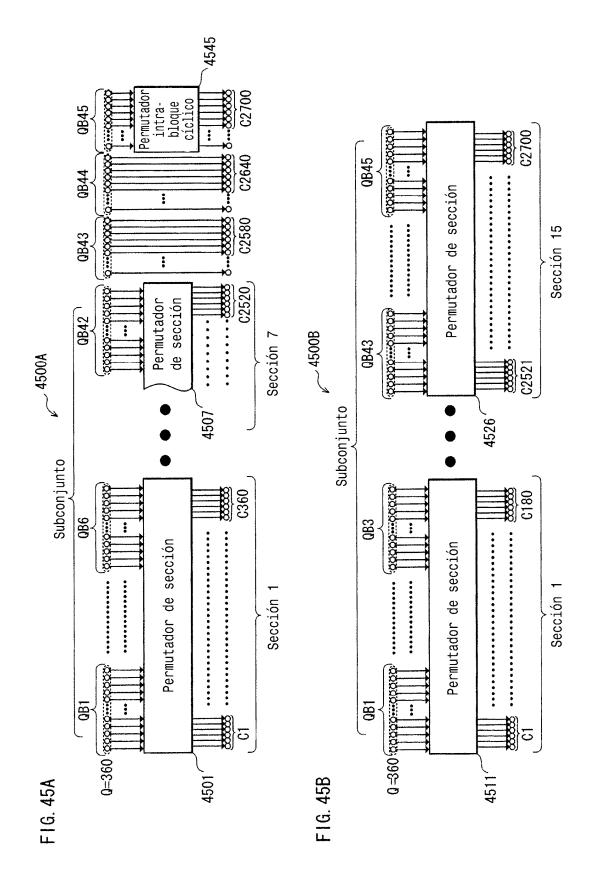

Las Figs. 45A y 45B son diagramas de bloques que muestran las configuraciones de ejemplo de entrelazadores que pertenecen a otra realización; teniendo la Fig. 45A N = 45, Q = 360, M = 6, y F = 1 (sin plegado), y teniendo la Fig. 45B N = 45, Q = 360, M = 6, y F = 2 (con plegado).

#### [Descripción de realizaciones]

(Información antecedente)

5

10

25

30

35

40

45

50

55

La Fig. 1 es un diagrama de bloques que muestra la configuración de un transmisor 100 que incluye un codificador de codificación y modulación de entrelazado de bits (de aquí en adelante, BICM) típico. Como se muestra, el transmisor 100 incluye un procesador de entrada 110, un codificador BICM (incluyendo a su vez un codificador 120 de comprobación de paridad de baja densidad (de aquí en adelante, LDPC), un entrelazador de bits 130, y un mapeador de constelación 140), y un modulador 150.

El procesador de entrada 110 convierte un flujo de bits de entrada en bloques de una longitud predeterminada. El codificador LDPC 120 codifica los bloques en palabras de código usando códigos LDPC, y transmite a continuación las palabras de código al entrelazador de bits 130. El entrelazador de bits 130 aplica un proceso de entrelazado a cada palabra de código LDPC, a continuación divide cada palabra de código entrelazada en una secuencia de palabras de célula (es decir, palabras de constelación). El mapeador de constelación 140 mapea cada palabra de célula (es decir, palabra de constelación) en una secuencia de constelaciones (por ejemplo, usando QAM). El modulador genérico 150 en la salida incluye todos los bloques de procesamiento desde la salida del codificador BICM a un amplificador de potencia de frecuencia de radio (de aquí en adelante, RF).

Un código LDPC es un código de corrección de error lineal que está completamente definido por una matriz de comprobación de paridad (de aquí en adelante, PCM). Una PCM es una matriz dispersa binaria que representa la conexión de los bits de la palabra de código (de aquí en adelante también denominados nodos de variable) con las comprobaciones de paridad (de aquí en adelante también denominados nodos de comprobación). Las columnas y las filas de la PCM corresponden respectivamente a los nodos de variable y los nodos de comprobación. En la PCM, una conexión entre un nodo de variable y un nodo de comprobación se representa mediante un elemento.

Los códigos cuasi cíclicos de comprobación de paridad de baja densidad (de aquí en adelante, QC LDPC) son una variedad de los códigos LDPC. Los códigos QC LDPC tienen una estructura que está particularmente adecuada para su implementación en hardware. De hecho, la mayor parte de las normas en uso hoy en día emplean códigos QC LDPC. La PCM de un código QC LDPC tiene una configuración especial compuesta por una pluralidad de matrices circulantes. Una matriz circulante es una matriz cuadrada en la que cada fila es un desplazamiento cíclico de los elementos en la fila previa, y tiene una, dos, o más diagonales plegadas. Cada matriz circulante tiene un tamaño de Q×Q. En este caso, Q representa el factor cíclico del QC LDPC. La configuración cuasi cíclica anteriormente descrita permite que se procesen Q nodos de comprobación en paralelo, lo que es claramente beneficioso para una eficiente implementación en hardware.

La Fig. 2 muestra la PCM de un código QC LDPC que tiene un factor cíclico Q de ocho, como un ejemplo. En la Fig. 2, así como en las Figs. 3 y 5 descritas posteriormente, los cuadrados más pequeños representan cada uno un elemento de la PCM, en donde los cuadrados negros son elementos unitarios y todos los otros cuadrados son elementos cero. La PCM muestra que tiene matrices circulantes con una o dos diagonales plegadas cada una. Este código QC LDPC codifica un bloque de 8×6 = 48 bits en una palabra de código de 8×12 = 96. En consecuencia, la tasa de codificación del QC LDPC es de 48/96 = 1/2. Los bits de la palabra de código se dividen en una pluralidad de bloques de Q bits cada uno. Los Q bloques de bits se denominan en el presente documento a continuación bloques cíclicos (o grupos cíclicos) por esta relación con el factor cíclico de Q.

Una variedad especial de los códigos QC LDPC son los códigos cuasi cíclicos de comprobación de paridad de baja densidad de acumulación repetida (de aquí en adelante, RA QC LDPC). Los códigos RA QC LDPC son bien conocidos como fáciles de codificar, y por lo tanto se usan en una amplia variedad de normas (por ejemplo, en las normas DVB de la segunda generación, que incluyen DVB-S2, DVB-T2, y DVB-C2). El lado derecho de la PCM corresponde a los bits de paridad. Los elementos unitarios en el presente documento se disponen en una estructura escalonada. La Fig. 3 muestra un ejemplo de una PCM para un RA QC LDPC que tiene una tasa de codificación de 2/3

Anteriormente, y a todo lo largo del documento, DVB-T es una abreviatura de Difusión de Video Digital - Terrestre, DVB-S2 es una abreviatura de Difusión de Video Digital - Segunda Generación por Satélite, DVB-T2 es una abreviatura de Difusión de Video Digital - Segunda Generación Terrestre, y DVB-C2 es una abreviatura de Difusión

de Video Digital - Segunda Generación por Cable.

10

35

40

Mediante la aplicación de una simple permutación de filas a la PCM mostrada en la Fig. 3, se revela la estructura cuasi cíclica de los códigos RA QC LDPC, con la excepción de la parte de paridad, mostrada en la Fig. 4. La permutación de filas es un cambio simple de la representación gráfica que no tiene influencia sobre la definición del código.

La estructura cuasi cíclica de la parte de paridad de la PCM es impartida mediante la aplicación de una permutación de filas adecuada solamente a los bits de paridad de la PCM mostrada en la Fig. 4. Esta técnica es ampliamente conocida en el campo y se usa en las normas tales como DVB-T2, bajo el nombre de entrelazado de paridad o de permutación de paridad. La Fig. 5 muestra la PCM obtenida como resultado de la aplicación de dicha permutación de paridad a la PCM mostrada en la Fig. 4.

Normalmente, los bits de una palabra de código LDPC varían en importancia, y los bits de una constelación varían en nivel de robustez. El mapeado de los bits de una palabra de código LDPC a una constelación directamente, es decir, sin entrelazado, conduce a un rendimiento sub-óptimo. De ese modo, los bits de la palabra de código LDPC requieren el entrelazado previo al mapeado en constelaciones.

- Para esta finalidad, el entrelazador de bits 130 está provisto entre el codificador LDPC 120 y el mapeador 140 de constelación, tal como se muestra en la Fig. 1. Mediante un diseño cuidadoso del entrelazador de bits 130, se mejora la asociación entre los bits de la palabra de código LDPC y los bits codificados por la constelación, conduciendo a un rendimiento del receptor mejorado. El rendimiento se mide normalmente usando la tasa de errores de bits (de aquí en adelante, BER) como una función de la relación señal a ruido (de aquí en adelante, SNR).

- Los bits de la palabra de código LDPC difieren en importancia principalmente debido a que no todos los bits están necesariamente implicados en el mismo número de comprobaciones de paridad. Cuantas más comprobaciones de paridad (nodos de comprobación) esté implicado un bit de palabra de código dado (nodo variable), más importante será el bit de la palabra de código en un proceso de decodificación LDPC iterativo. Una razón adicional es que los nodos de variable tienen cada uno diferente conectividad a los ciclos de un gráfico de Tanner que representa los códigos LDPC. Por lo tanto, los bits de la palabra de código es probable que difieran en importancia a pesar de estar implicados en el mismo número de comprobaciones de paridad. Estas ideas son bien entendidas en el campo. Como regla, la importancia de los nodos de variable se incrementa según se incrementa el número de nodos de comprobación conectados con ellos.

- En el caso particular de los códigos QC LDPC, todos los bits incluidos en un bloque cíclico de Q bits tienen el mismo número de comprobaciones de paridad aplicadas a los mismos, y tienen la misma conectividad a los ciclos del gráfico de Tanner. De ese modo, todos los bits tienen la misma importancia.

De modo similar, es ampliamente conocido que los bits codificados de una constelación tienen diferentes niveles de robustez. Por ejemplo, una constelación de modulación de amplitud en cuadratura (de aquí en adelante, QAM) está compuesta por dos símbolos de modulación de amplitud de pulsos (de aquí en adelante, PAM) independientes, correspondiendo un símbolo a la parte real y correspondiendo el otro símbolo a la parte imaginaria. Los dos símbolos PAM codifican cada uno M bits. La Fig. 6 muestra 8 símbolos PAM que usan codificación de Gray. Tal como se muestra, los bits codificados en cada símbolo PAM varían en términos de nivel de robustez. La diferencia en la robustez es un resultado de la distancia entre dos subconjuntos definidos por cada bit (por ejemplo, 0 o 1) siendo diferentes para cada uno de los bits. Cuanto mayor sea la distancia, más robusto y fiable será el bit. La Fig. 6 indica que el bit b3 tiene el nivel de robustez más alto, mientras que el bit b1 tiene el nivel de robustez más bajo.

De ese modo, una constelación 16-QAM codifica cuatro bits y tiene dos niveles de robustez. De la misma manera, una constelación 64-QAM codifica seis bits y tiene tres niveles de robustez. También, una constelación 256-QAM codifica ocho bits y tiene cuatro niveles de robustez.

Los siguientes parámetros se usan en el presente documento a continuación a todo lo largo de la presente 45 descripción.

Factor cíclico: Q = 8

Número de bloques de ciclos por palabra de código LDPC: N =12

Número de bits por constelación: M = 4 (es decir, 16-QAM)

Dados los parámetros anteriores, el número de constelaciones al que se mapea cada palabra de código LDPC es igual a Q×N/M = 24. Normalmente, los parámetros Q y N se seleccionan de manera que Q×N es igual a un múltiplo de M para todas las constelaciones soportadas por el sistema.

La Fig. 7 es un diagrama de bloques que muestra la configuración de un entrelazador típico cuando se aplican los parámetros anteriores. En la Fig. 7, los 12 bloques cíclicos están etiquetados QB1, ..., QB12, y las 24 constelaciones están etiquetadas C1, ..., C24. Un entrelazador de bits 710 entrelaza los 96 bits de la palabra de código LDPC.

55 Se conoce un entrelazador de bits convencional a partir de la norma DVB-T2 (véase ETSI EN 302 755). La norma

DVB-T2 es una norma de televisión estándar que presenta mejoras sobre la norma DVB-T, y describe un sistema de transmisión de línea base de segunda generación para la emisión de televisión digital. La norma DVB-T2 da los detalles de un sistema de codificación de modulación del canal para la emisión de servicios de televisión y datos genéricos. La norma anteriormente mencionada se explica a continuación.

La Fig. 8A es un diagrama de bloques que muestra la estructura de un modulador usado en la norma DVB-T2 (es decir, un modulador DVB-T2). El modulador DVB-T2 800 incluye un procesador de entrada 810, un codificador BICM 820, un constructor de trama 830, y un generador OFDM 840.

El procesador de entrada 810 convierte un flujo de bits de entrada en bloques de una longitud predeterminada. El codificador BICM 820 aplica un procesamiento BICM a la entrada. El constructor de trama 830 usa la entrada desde el codificador BICM 820 y similares para generar una estructura de trama de distribución en el formato DVB-T2. El generador OFDM 840 realiza una adición del piloto, la aplicación de una transformada de Fourier rápida, la inserción de un intervalo de guarda, y otros similares sobre la estructura de la trama de distribución, y a continuación produce la salida de una señal de transmisión en el formato DVB-T2.

El BICM usado en la norma DVB-T2 se describe en el capítulo 6 de la norma ETSI EN 302 755.

10

20

25

40

45

50

La Fig. 8B es un diagrama de bloques que muestra la estructura de un codificador BICM 820 en el modulador DVB-T2 800 ilustrado en la Fig. 8A. la Fig. 8B omite la codificación BCH exterior, la rotación de la constelación, el entrelazador de células, el entrelazador temporal, y otros similares.

El codificador BICM 820 incluye un codificador LDPC 821, un entrelazador de bits (que a su vez incluye un entrelazador de paridad 822 y un entrelazador columna-fila 823), un demultiplexor bit-a-célula 824, y un mapeador QAM 825.

El codificador LDPC 821 codifica los bloques en palabras de código que usan códigos LDPC. El entrelazador de bits (que incluye el entrelazador de paridad 822 y el entrelazador columna-fila 823) realiza el entrelazado sobre los bits de las palabras de código. El demultiplexor bit-a-célula 824 demultiplexa los bits entrelazados de las palabras de código en palabras de célula (palabras de constelación). El mapeador QAM 825 mapea las palabras de célula (palabras de constelación) a los símbolos QAM complejos. Los símbolos QAM complejos son también denominados células. De hecho, el demultiplexor bit-a-célula 824 se puede considerar también una parte del entrelazador de bits. En dichas situaciones, el codificador BICM de conformidad con la norma DVB-T2 se puede considerar que tiene la estructura básica mostrada en la Fig. 1.

Los códigos LDPC usados en la norma DVB-T2 son códigos RA QC LDPC que tienen un factor cíclico de Q = 360.

Se definen dos longitudes de palabra de código por la norma DVB-T2, siendo una de 16200 bits y la siendo la otra de 64800 bits. En el documento presente, los códigos LDPC que usan una longitud de palabra de código de 16200 bits son denominados como códigos 16K (o como códigos 16K LDPC), y los códigos LDPC que tienen una longitud de palabra de código de 64800 bits se denomina como códigos 64K (o como códigos 64K LDPC). El número de bloques cíclicos por palabra de código es de 45 para los códigos de 16K y de 180 para los códigos de 64K. Los códigos disponibles correspondientes a cada longitud de bloque (longitud de palabra de código) se dan en las tablas A1 a A6 de la ETSI EN 302 755 para la norma DVB-T2.

El entrelazador de bits se usa solo para constelaciones mayores que las constelaciones de modulación por desplazamiento de fase en cuadratura (de aquí en adelante, QPSK), e incluye el entrelazador de paridad 822, el entrelazador columna- fila 823, y el demultiplexor bit-a-célula 824. De acuerdo con la norma DVB-T2, el entrelazador de bits no incluye el demultiplexor bit-a-célula 824. Sin embargo, el presente documento pertenece al entrelazador según se aplica los códigos LDPC previamente al mapeado de la constelación. De ese modo, el demultiplexor bit-a-célula 824 es tratado como una parte del entrelazador de bits.

El entrelazador de paridad 822 realiza la permutación de paridad sobre los bit de paridad de cada palabra de código de modo que clarifique la estructura cuasi cíclica del mismo, tal como se ha descrito anteriormente (véanse las Figs. 4 y 5).

Conceptualmente, el entrelazador columna-fila 823 opera mediante la escritura de los bits de cada palabra de código LDPC en forma de columnas en una matriz de entrelazado, y a continuación leyendo los bits en forma de filas. El primer bit de la palabra de código LDPC se escribe primero, y se lee primero. Después de la escritura y antes de la lectura de los bits de la palabra de código LDPC, el entrelazador columna-fila 823 desplaza cíclicamente las columnas de bits en un número predeterminado de posiciones. Esto se domina giro de columnas en la norma DVB-T2. El número de columnas Nc y el número de filas Nr en la matriz del entrelazador se dan en la Tabla 1 para diversos tamaños de constelación, de acuerdo con las dos longitudes de palabra de código LDPC anteriormente mencionadas.

#### [Tabla 1]

| Longitud palabra de código LDPC | Tamaño constelación | Nº de columnas: Nc | Nº de filas: Nr |

|---------------------------------|---------------------|--------------------|-----------------|

|                                 | 16-QAM              | 8                  | 2025            |

| 16200                           | 64-QAM              | 12                 | 1350            |

|                                 | 256-QAM             | 8                  | 2025            |

|                                 | 16-QAM              | 8                  | 8100            |

| 64800                           | 64-QAM              | 12                 | 5400            |

|                                 | 256-QAM             | 16                 | 4050            |

El número de columnas Nc es dos veces el número de bits por constelación, con la excepción de los códigos 16K con una constelación 256-QAM. Esta excepción ocurre debido a que la longitud de la palabra de código LDPC de 16200 no es un múltiplo de 16, es decir no es el doble del número de bits por constelación 256-QAM.

El proceso de escritura de bits en la palabra de código y el proceso de lectura de bits para códigos de 16K realizados por el entrelazador columna-fila 823 se ilustra en las Figs. 9A y 9B para doce columnas, y en las Figs. 10A y 10B para ocho columnas. Cada uno de los cuadrados pequeños corresponde a un bit en la palabra de código LDPC. El cuadrado ennegrecido representa el primer bit de la palabra de código LDPC. Las flechas indican el orden en que se escriben los bits en, y se leen desde, la matriz del entrelazador. Por ejemplo, cuando la matriz del entrelazador tiene doce columnas, los bits de la palabra de código del código 16K se escriben en el orden dado en la Fig. 9A, concretamente (Fila 1, Columna 1), (Fila 2, Columna 1), ..., (Fila 1350, Columna 1), (Fila 1, Columna 2), ..., (Fila 1, Columna 2), ..., (Fila 1, Columna 2), ..., (Fila 1, Columna 12), (Fila 2, Columna 1), ..., (Fila 1350, Columna 12). Las Figs. 9A, 9B, 10A, y 10B no ilustran el proceso de giro de las columnas.

Previamente al mapeado QAM, el demultiplexor bit-a-célula 824 demultiplexa las palabras de código LDPC para tener una pluralidad de flujos de bits en paralelo. El número de flujos es el doble del número de bits codificados *M* por constelación QAM, es decir, 2×*M*, con la excepción de los códigos de 16K LDPC con una constelación 256-QAM. Para códigos de 16K LDPC con una constelación de 256-QAM, el número de flujos es igual al número de bits codificados *M* por constelación QAM. Los *M* bits codificados por constelación son denominados como una palabra de célula (palabra de constelación). Para los códigos de 16K de LDPC, el número de palabras de célula por palabra de código es 16200/M, tal como se da a continuación.

8100 células para QPSK, 4050 células para 16-QAM, 2700 células para 64-QAM, y 2025 células para 256-QAM.

35

De acuerdo con la Tabla 1, dada anteriormente, el número de flujos en paralelo es igual al número de columnas en el entrelazador columna-fila para constelaciones mayores de QPSK. Los demultiplexores bit-a-célula que corresponden a constelaciones 16-QAM, constelaciones 64-QAM y constelaciones 256-QAM para códigos de 16K LDPC se muestran respectivamente en las Figs. 11, 12 y 13. La notación de bits usada es la de la norma DVB-T2.

Como se muestra en la Fig. 11 (y las Figs. 12 y 13), el demultiplexor bit-a-célula 824 incluye un demultiplexor simple 1110 (también 1210, 1310) y un permutador de demultiplexado 1120 (también 1220, 1320).

Además de tener el demultiplexor simple 1110 (1210, 1310) que demultiplexa simplemente las palabras de código LDPC, a las que se ha aplicado entrelazado, el demultiplexor bit-a-célula 824 también tiene el permutador de demultiplexado 1120 (1220, 1320) que realiza la permutación sobre los flujos de bits en paralelo demultiplexados.

Sin embargo, cuando se usa el entrelazador columna-fila (es decir, para constelaciones 16-QAM o mayores), la permutación aplicada a los flujos de bits es idéntica a la permutación aplicada a los columnas del entrelazador columna-fila debido a que el número de flujos de bits en paralelo es igual al número de columnas. Por lo tanto, la permutación realizada por el demultiplexor bit-a-célula 824 se considera como una parte del entrelazador de bits.

El entrelazador de bits usado en la norma DVB-T2 tiene esencialmente dos problemas.

El primer problema es que se impide el paralelismo cuando el número de bloques cíclicos en la palabra de código LDPC no es un múltiplo del número de columnas en la matriz del entrelazador de bits. Un paralelismo reducido conduce a una latencia creciente. Esto es especialmente problemático cuando se usa la decodificación BICM iterativa por el receptor. Esta situación tiene lugar para varias combinaciones de longitud de palabra de código LDPC y tamaño de constelación en la norma DVB-T2.

Las Figs. 14 y 15 ilustran la situación anteriormente mencionada para los casos de código 16K LDPC en los que la matriz del entrelazador tiene ocho y doce columnas, respectivamente. Se usan ocho columnas en la matriz del entrelazador para constelaciones de 16-QAM y constelaciones de 256-QAM. Se usan doce columnas en la matriz del entrelazador para constelaciones de 64-QAM. En las Figs. 14 y 15, la rejilla representa una palabra de código LDPC, los pequeños cuadrados representan cada uno un bit de la palabra de código LDPC, correspondiendo las filas a los bloques cíclicos, y correspondiendo las columnas a bits del mismo índice de bits dentro de un bloque cíclico. Los cuadrados ennegrecidos representan el octavo y doceavo bits de la primera fila en la matriz del entrelazador. Para una facilidad de comprensión, el número de bits por bloque cíclico se ha reducido de 360 a 72. Sin embargo, esto no afecta a la comprensión.

El segundo problema es que, en la norma DVB-T2, el número de posibles configuraciones del entrelazador de bits está limitado por el número de columnas en la matriz del entrelazador de bits.

Un problema adicional del entrelazador de bits de DVB-T2 es que la regularidad y paralelismo de la permutación está impedida por el proceso de giro de columnas. Las Figs. 16 y 17 ilustran respectivamente las mismas

situaciones que las Figs. 14 y 15, con la adición del proceso de giro de columna. Cuando la matriz del entrelazador tiene ocho columnas para los códigos 16K LDPC, los valores de giro de columna para las columnas del entrelazador de bits DVB-T2 son (0, 0, 0, 1, 7, 20, 20, 21). De modo similar, cuando la matriz del entrelazador tiene doce columnas para los códigos 16K LDPC los valores del giro de columna para las columnas del entrelazador de bits de DVB-T2 son (0, 0, 0, 2, 2, 2, 3, 3, 3, 6, 7, 7).

En consecuencia, es deseado un entrelazador de bits que reduzca la latencia mientras mejora el paralelismo. Estas propiedades son particularmente importantes en la decodificación BICM iterativa.

(Descubrimientos del experimentador)

El presente inventor ha descubierto, como fruto de una prolongada experimentación, que un entrelazador que satisfaga las siguientes dos condiciones es extremadamente eficiente.

(Condición 1)

Los *M* bits de cada constelación se mapean cada uno a uno de *M* bloques cíclicos diferentes de la palabra de código LDPC. Esto es equivalente a mapear un bit desde *M* diferentes bloques cíclicos de la palabra de código LDPC a una palabra de constelación. Esto se ilustra esquemáticamente en la Fig. 18A.

15 (Condición 2)

Todas las palabras de constelación mapeadas a los M bloques cíclicos se mapean solo a ese bloque cíclico particular. Esto es equivalente a mapear todos los  $M \times Q$  bits de los M bloques cíclicos diferentes compuesto cada uno de Q bits a exactamente Q constelaciones. Esto se ilustra esquemáticamente en la Fig. 18B.

Las condiciones anteriores implican que se mapean exactamente Q constelaciones a cada conjunto de *M* bloques cíclicos.

(Realización 1)

25

30

45

50

A continuación se describen los detalles de un entrelazador de bits (es decir, un entrelazador de bits en paralelo) que satisface las condiciones 1 y 2 dadas anteriormente. En la descripción siguiente, el procesamiento y las unidades que realizan dicho procesamiento se etiquetan con los mismos números de referencia siempre que sea aplicable.

En el presente documento, cada grupo de *M* bloques cíclicos y cada grupo de *Q* palabras de constelación se denomina como una sección (o como una sección del entrelazador).

Las Figs. 19 y 20 son diagramas de bloques que ilustran respectivamente la función de mapeado de un entrelazador de bits que satisfaga las condiciones 1 y 2 y que corresponde a los parámetros anteriormente mencionados (es decir, Q = 8, M = 4, N = 12), y una configuración de muestra para un entrelazador de bits de ese tipo.

En las Figs. 19 y 20, las palabras de código QC LDPC están compuestas de N = 12 bloques cíclicos, compuesto a su vez cada uno de Q = 8 bits. Cada una de las 24 palabras de constelación está compuesta de M = 4 bits. Cada palabra de constelación indica uno de entre  $2^M = 16$  puntos de constelación. El entrelazador de bits se divide en N/M = 3 secciones. Las 24 palabras de constelación se asocian cada una a una de las tres secciones.

Un entrelazador de bits 2000 incluye un permutador de bits 2010, que a su vez incluye *N/M* (= 3) permutadores de sección 2021, 2022 y 2023, operando cada uno de modo independiente. Sin embargo, en lugar de proporcionar tres permutadores de sección, un único permutador de sección puede, por ejemplo, proporcionarse de modo que realice los tres procesos de permutación de sección descritos a continuación, conmutando entre ellos a lo largo del tiempo.

Los permutadores de sección (2021, 2022 y 2023) realizan cada uno de modo independiente una permutación de sección sobre los 32 bits que componen cada uno de los 4 bloques cíclicos, de modo que un bit de entre cada cuatro bloques cíclicos (es decir, de QB1 a QB4, de QB5 a QB8, y de QB9 a QB12) se mapean en cada grupo de ocho palabras de constelación (es decir, de C1 a C8, de C9 a C16, y de C17 a C24).

Las condiciones 1 y 2, descritas anteriormente, aseguran que cada entrelazador de bits es divisible en *N/M* secciones paralelas. Las permutaciones de sección aplicadas a las secciones paralelas pueden aplicar todas las mismas reglas de permutación, pueden aplicar cada una diferentes reglas de permutación o pueden implicar un subconjunto de las secciones que aplican idénticas reglas de permutación mientras otras difieren.

Por ejemplo, los permutadores de sección pueden mapear los Q bits de un bloque cíclico (en el que cada uno tiene la misma importancia en la decodificación LDPC) a bits que tengan el mismo índice de bit (es decir, que tengan el mismo nivel de robustez) en las Q palabras de constelación. Para cada bloque cíclico, los Q bits pueden estar en orden secuencial o permutado. Este último caso se describe con referencia a las Figs. 21A y 21B, mientras que el primer caso se describe con referencia las Figs. 22A y 22B.

La Fig. 21A ilustra estructuralmente el permutador de sección de la Fig. 20.

El permutador de sección 2101 incluye permutadores intra-bloques cíclicos 2111 a 2114 y un permutador columnafila 2131. En lugar de proporcionar cuatro permutadores intra-bloques cíclicos, por ejemplo, se puede proporcionar un único permutador intra-bloque cíclico y realizar los cuatro procesos de permutación intra-bloques cíclicos, descritos posteriormente, conmutando entre ellos a lo largo del tiempo.

Los permutadores intra-bloque cíclicos (2111-2114) realizan cada uno una permutación intra-bloque cíclico sobre los bloques cíclicos de Q-bits (8 bits) (QB1-QB4). Las permutaciones intra-bloque cíclico aplicadas a los bloques cíclicos en cada sección pueden aplicar todas las mismas reglas de permutación, pueden aplicar cada una diferentes reglas de permutación o pueden implicar un subconjunto de las secciones que aplican idénticas reglas de permutación mientras otras difieren.

El permutador columna-fila 2131 realiza una permutación columna-fila sobre cada grupo de  $M \times Q$  (= 32) bits. Específicamente, el permutador columna-fila 2131 escribe los  $M \times Q$  bits en forma de filas en una matriz  $M \times Q$  (8×4), a continuación lee los  $M \times Q$  bits en forma de columna a partir de los mismos, aplicando así la permutación columna-fila. La permutación columna-fila aplicada por el permutador columna-fila 2131 recuerda la permutación aplicada a la matriz 12×1350 mostrada en las Figs. 9A y 9B, en la que se usan Q columnas y M filas, el proceso de escritura tiene lugar en forma de columna, y el proceso de lectura tiene lugar en forma de fila.

La Fig. 21B es una representación estructural del permutador de sección mostrado en la Fig. 21A. En la Fig. 22B, las palabras de constelación de M = 4 bits están indicadas cada una por b1 a b4.

Sin embargo, es también plausible una variación en la que un proceso de permutación intra-bloque cíclico no es parte del proceso de permutación de la sección.

Por ejemplo, una permutación de sección implementada sin la ejecución de la permutación intra-bloque cíclico y una estructura de mapeado por el permutador de sección se muestra en las Figs. 22A y 22B. El permutador de sección 2201 incluye un permutador columna-fila 2131 y realiza una permutación simple columna-fila. En la Fig. 22B, las palabras de constelación de M=4 bits están indicadas cada una por b1 a b4.

25 La permutación de sección descrita en las Figs. 21A, 21B, 22A y 22B puede aplicarse a bloques cíclicos QB5-QB8 y QB9-QB12.

Ventajosamente, se puede aplicar una permutación de bloque cíclico adicional a los *N* bloques cíclicos antes de que el entrelazador de bits realice la permutación de sección. La Fig. 23 es un diagrama estructural de la permutación de bloque cíclico adicional aplicada por el entrelazador de bits. En este contexto, la permutación del bloque cíclico juega un papel similar al de la permutación realizada por el demultiplexor bit-a-célula en la norma DVB-T2.

El entrelazador de bits 2300 mostrado en la Fig. 23 incluye un permutador de bloque cíclico 2310 y un permutador de bits 2010 (que su vez incluye permutadores de sección 2021-2023).

El permutador de bloque cíclico 2310 realiza permutaciones de bloques cíclicos 2311-2318 sobre los bloques cíclicos QB1-QB12. En este caso, las permutaciones de bloques cíclicos 2311-2318 siguen todas las mismas reglas de permutación.

La permutación de bloque cíclico realizadas sobre los *N* bloques cíclicos es particularmente ventajosa porque habilita un mapeado optimizado de los bits de palabras de código LDPC sobre los bits de constelación, dando como resultado un rendimiento optimizado.

La Fig. 24 es un diagrama de bloques esquemático del entrelazador de bits 2300 mostrado en la Fig. 23. El entrelazador de bits 2400 mostrado en la Fig. 24 incluye tres etapas, A, B y C.

Etapa A: permutación (inter) bloque cíclico

Etapa B: permutación intra-bloque cíclico

Etapa C: permutación columna-fila

10

15

30

35

50

La permutación (inter) bloque cíclico se aplica a los *N* bloques cíclicos que componen la palabra de código, la permutación intra-bloque cíclico se aplica a los *Q* bits de cada bloque cíclico, y la permutación columna-fila se aplica a las *M*×*Q* secciones.

El entrelazador de bits 2400 mostrado en la Fig. 24 incluye el permutador de bloques cíclicos 2310 y el permutador de bits 2010 (que a su vez incluye los permutadores de sección 2101-2103). El permutador de sección 2101 (2102, 2013) incluye los permutadores intra-bloque cíclico 2111-2114 (2115-2118, 2119-2122) y el permutador columna-fila 2131 (2132, 2133).

En el entrelazador de bits 2400, la permutación (inter) bloque cíclico se realiza por el permutador de bloques cíclicos 2310 (etapa A), la permutación intra-bloque cíclico se realiza por los permutadores intra-bloques cíclicos 2111-2122 (etapa B), y la permutación columna-fila se realiza por los permutadores columna-fila 2131-2133 (etapa C).

Los permutadores intra-bloque cíclico 2111-2122 pueden eliminarse del entrelazador de bits 2400 mostrado en la Fig. 24, de modo que el entrelazador de bits se configura para no realizar la permutación intra-bloque cíclico. También, el entrelazador de bits 2400 puede realizar la permutación (inter) bloque cíclico antes de la permutación intra-bloque cíclico en lugar de después de la permutación intra-bloque cíclico, o puede realizar la permutación (inter) bloque cíclico antes y después de la permutación intra-bloque cíclico.

Los permutadores intra-bloque cíclico pueden tener estructuras similares. Esto es ventajoso porque los permutadores intra-bloque cíclico se pueden implementar así usando idénticos recursos (por ejemplo, bloques de hardware). Alternativamente, las permutaciones intra-bloque cíclico pueden consistir en desplazamientos cíclicos, lo que puede permitir una implementación en hardware eficiente usando desplazadores en barril. Una implementación que usa desplazadores en barril en el decodificador LDPC es también posible.

10

15

20

25

35

A continuación se describe un transmisor que incluye el entrelazador de bits que realiza un proceso de entrelazado de bits que satisface las condiciones 1 y 2, con referencia a la Fig. 25.

La Fig. 25 es un diagrama de bloques de un transmisor que pertenece a una realización adicional de la presente divulgación. Como se muestra en la Fig. 25, un transmisor 2500 incluye un codificador BICM (que a su vez incluye un codificador LDPC 2510, un entrelazador de bits 2520 y un mapeador de constelación 2530) y un modulador 2540.

El codificador LDPC 2510 codifica bloques de entrada en palabras de código que usan códigos QC-LDPC, y a continuación transmite las palabras de códigos al entrelazador de bits 2520.

El entrelazador de bits 2520 recibe la palabra de código en el código QC-LDPC desde el codificador LDPC 2510. La palabra de código está compuesta de *N* = 12 bloques cíclicos, incluyendo cada bloque cíclico Q = 8 bits. El entrelazador de bits 2520 realiza el entrelazado de los bits de las palabras de código. El entrelazador de bits 2520 divide la palabra de código entrelazada en una pluralidad de palabras de constelación, compuesta cada una de *M* = 4 bits y que indica uno de entre 2<sup>M</sup> =16 puntos de constelación, a continuación produce la salida de las palabras de constelación al mapeador de constelación 2530. El entrelazador de bits 2520 puede aplicar el proceso de entrelazado de bits explicado con referencia a las Figs. 19 a 22A y 22B, o puede aplicar una variante del proceso de permutación de bits. También, el entrelazador de bits 2520 puede aplicar un proceso de permutación de bloques cíclicos adicional, tal como el proceso explicado con referencia a las Figs. 23 y 24 o una variación del mismo.

El mapeador de constelación 2530 recibe las palabras de constelación desde el entrelazador de bits 2520 y realiza el mapeado de la constelación sobre las palabras de constelación así recibidas.

El modulador 2740 genera una señal de transmisión usando multiplexado por división de frecuencia ortogonal (de aguí en adelante, OFDM) o similar.

A continuación se describe el codificador BICM que incluye el entrelazador de bits que realiza un proceso de entrelazado de bits que satisface las condiciones 1 y 2, con referencia a la Fig. 26.

La Fig. 26 es un diagrama de bloques de un ejemplo de codificador BICM que pertenece a una realización adicional de la divulgación. En la Fig. 26, el codificador BICM 2600 corresponde a los parámetros dados anteriormente (es decir, Q = 8, N = 12, M = 4).

El codificador BICM 2600 mostrado en la Fig. 26 incluye una memoria principal 2601, un controlador LDPC 2611, un rotador 2612, un grupo procesador de nodo de comprobación 2613, un desrotador 2614, un contador QB 2631, una tabla A 2632, entrelazador B 2633, un grupo de registro 2634, entrelazador C 2635 y un grupo mapeador 2651.

En la Fig. 26, dado que *Q* = 8, la memoria principal 2601 lee ocho bits cada vez, el grupo del procesador de nodo de comprobación 2613 incluye ocho procesadores de nodo de comprobación, y el grupo mapeador 2651 incluye ocho mapeadores. También, dado que *M* = 4, el grupo de registro 2634 incluye cuatro registros.

La memoria principal 2601 recibe una secuencia de bits para transmisión desde, por ejemplo, el procesador de entrada (no diagramado), y almacena la secuencia de bits recibida.

El controlador LDPC 2611 produce la salida de una dirección de lectura hacia la memoria principal 2601. La memoria principal 2601 produce la salida en consecuencia de la secuencia de bits, ocho bits cada vez comenzando con el bit de mayor peso, al rotador 2612. El rotador 2612 es controlado por el controlador LDPC 2611 para realizar un número predeterminado de desplazamientos cíclicos sobre los ocho bits suministrados al mismo por la memoria principal 2601, y a continuación saca los ocho bits cíclicamente desplazados hacia los procesadores del nodo de comprobación del grupo procesador del nodo de comprobación 2613, uno cada vez, estando los bits y los procesadores del nodo comprobación en una correspondencia uno a uno. Cada procesador del nodo de comprobación del grupo procesador del nodo de comprobación 2613 está controlado por el controlador LDPC 2611 para realizar el procesamiento del nodo de comprobación sobre cada bit de entrada al mismo, a continuación produce la salida de los resultados al desrotador 2614. El desrotador 2614 está controlado por el controlador LDPC 2611 para realizar un número predeterminado de desplazamientos cíclicos sobre los ocho bits recibidos desde el grupo procesador del nodo de comprobación 2613 de modo que cancele el desplazamiento cíclico aplicado por el

rotador 2612, y a continuación produce la salida de los ocho bits desplazados hacia la memoria principal 2601. El controlador LDPC 2611 produce la salida de la dirección de escritura hacia la memoria principal 2601. La memoria principal 2601 almacena en consecuencia los ocho bits suministrados a la misma por el desrotador 2614. El controlador LDPC 2611, el rotador 2612, el grupo de procesador del nodo de comprobación 2613, y el desrotador 2614 componen el codificador BICM en el codificador LDPC 2510 mostrado en la Fig. 25.

El contador QB 2631 cuenta desde 0 a 11 y produce la salida del valor del contador a la Tabla A 2632. La operación de contaje del contador QB 2631 se define en consideración a *N* = 12.

La Tabla A 2632 es una tabla de búsqueda simple en la que se almacenan las reglas de permutación del bloque cíclico. Esto es, la Tabla A 2632 almacena *N* = 12 piezas de información del orden de lectura del bloque cíclico (información que asocia un bloque cíclico diferente con cada uno de los 12 valores de contador desde el contador QB 2631). La Tabla A 2632 produce la salida de una dirección de lectura hacia la memoria principal 2601 de modo que los bits de un bloque cíclico (es decir, *Q* = 8 bits) que corresponden al valor del contador suministrado por el contador QB 2631 son suministrados desde la memoria principal 2601 al entrelazador B 2633. De ese modo, la memoria principal 2601 produce la salida de los bits de un bloque cíclico que corresponde al valor del contador del contador QB 2631 al entrelazador B 2633. El procesamiento usando la Tabla A 2632 se ejecuta como el proceso de permutación de bloques cíclicos (etapa A).

El entrelazador B 2633 realiza un número predeterminado de desplazamientos cíclicos sobre los bits del bloque cíclico suministrado por la memoria principal 2601, y produce la salida de los resultados a un primer registro de enlace del grupo de registros 2634. El procesamiento por el entrelazador B 2633 se ejecuta como el proceso de permutación intra-bloque cíclico (etapa B). Cada registro en el grupo de registros 2634 almacena un bloque cíclico de bits con temporización que coincide con la recepción de un pulso de control, y produce la salida del bloque cíclico de bits antes de recibir el siguiente pulso de control.

20

40

50

55

Cuando el contador QB 2631 realiza el proceso anteriormente mencionado para valores de contador 0 a 3, los bits de los cuatro bloques cíclicos (es decir, 32 bits) se introducen en el entrelazador C 2635. En este momento, el entrelazador C 2635 entrelaza los bits de los cuatro bloques cíclicos introducidos al mismo, y los mapeadores del grupo de mapeado 2651 producen la salida de una palabra de constelación de bits (es decir, *M* = 4 bits). A través del proceso de entrelazado, se suministran cuatro bits, es decir uno desde cada uno de los cuatro registros en el grupo de registros 2634, a cada mapeador. Este procesamiento por el entrelazador C 2635 se ejecuta como el proceso de permutación columna-fila (etapa C).

30 El contador QB 2631, tabla A 2632, entrelazador B 2633, el grupo de registro 2634, y el entrelazador C 2635 componen el entrelazador de bits 2520 del codificador BICM mostrado en la Fig. 25.

Los mapeadores del grupo de mapeadores 2651 mapean cada uno cuatro bits suministrados a los mismos desde el entrelazador C 2635 a una constelación, a continuación producen la salida de los resultados. El grupo mapeador 2651 compone el mapeador de constelación 2530 del codificador BICM mostrado en la Fig. 25.

Para cada palabra de código, el conjunto descrito anteriormente de procesos se aplica tres veces, una por cada uno de los valores de contador 0-3, 4-7 y 8-11 del contador QB 2631.

La realización representada en la Fig. 26 incluye *Q* mapeadores operando en paralelo. Sin embargo, los mapeadores son realizables también como un codificador BICM de modo que se disminuya o incremente el paralelismo. Por ejemplo, el número de secciones del entrelazador paralelas en el entrelazador de bits, es decir, el cociente de *N/M*, puede incrementarse obviamente de modo que mejore fácilmente el paralelismo. Dichos métodos permiten que se optimice el paralelismo mediante la puesta en paralelo de los *Q×N/M* mapeadores. La implementación de dicho paralelismo, sin inconvenientes, en el entrelazador de bits es beneficiosa.

A continuación se describe un receptor que recibe señales desde un transmisor que incluye el entrelazador de bits que realiza un proceso de entrelazado de bits que satisface las condiciones 1 y 2, con referencia a la Fig. 27.

45 La Fig. 27 es un diagrama de bloques de un receptor de ejemplo, que incluye un decodificador BICM no iterativo, que pertenece a una realización adicional de la divulgación. El receptor realiza las operaciones del transmisor a la inversa.

El receptor 2700 mostrado en la Fig. 27 incluye un demodulador 2710 y un decodificador BICM no iterativo (que a su vez incluye un desmapeador de constelación 2720, un desentrelazador de bits 2730, y un decodificador LDPC 2740).

El demodulador 2710 se realiza un proceso de demodulación a través de OFDM, por ejemplo, y produce la salida de los resultados demodulados.

El desmapeador de constelación 2720 del decodificador BICM no iterativo genera una secuencia de bits suaves mediante la aplicación de un proceso de desmapeado a la entrada del demodulador 2710, y la salida de la secuencia de bits suaves así generados al desmapeador de constelación 2730. Los bits suaves son una medida de

la probabilidad de que un bit dado sea un bit cero o un bit uno. Normalmente, los bits suaves se representan como relaciones de registro-probabilidad (de aquí en adelante, LLR), definida como sigue.

$$LLR(b) = In[p(b = 0)/(b = 1)]$$

en la que p(b = 0) indica la probabilidad de que el bit dado b sea un bit cero, y p(b = 1) representa la probabilidad de que el bit dado b sea un bit uno. Naturalmente, p(b = 0) + p(b = 1) = 1.

El desentrelazador de bits 2730 realiza un proceso de entrelazado sobre una salida de la secuencia de bits suaves por el desmapeador de constelación (es decir, un proceso de desentrelazado de bits) de modo que cancele el proceso de entrelazado de bits aplicado a la secuencia de bits por el entrelazador de bits en el transmisor ilustrado en la Fig. 25.

10 El decodificador LDPC 2740 recibe la secuencia de bits suaves desentrelazada por el desentrelazador de bits 2730, y realiza un proceso de decodificación LDPC usando la secuencia de bits suaves así recibida.

Una técnica mejorada que ofrece ganancias de rendimiento significativas es la decodificación BICM iterativa. La Fig. 28 ilustra un decodificador BICM iterativo.

La Fig. 28 es un diagrama de bloques de un receptor de ejemplo, que incluye un decodificador BICM iterativo, que pertenece a una realización adicional de la divulgación. El receptor realiza las operaciones del transmisor a la inversa.

Como se muestra en la Fig. 28, un receptor 2800 incluye el demodulador 2710 y un decodificador BICM iterativo (que a su vez incluye el desmapeador de constelación 2720, el desentrelazador de bits 2730, el decodificador LDPC 2740, un sustractor 2760 y un entrelazador de bits 2750).

20 El receptor 2800 de la Fig. 28 tiene el desmapeador de constelación 2720 que realiza un proceso de desmapeado de la constelación, el desentrelazador de bits 2730 que realiza un proceso de desentrelazado de bits, y el decodificador LDPC 2740 que realiza un proceso de decodificación LDPC.

Después de una o más iteraciones de decodificación LDPC, se produce la salida de información extrínseca, obtenida por el sustractor 2760 que resta la entrada al decodificador LDPC 2740 de la salida del decodificador LDPC 2740, hacia el entrelazador de bits 2750. El entrelazador de bits 2750 realiza un proceso de entrelazado sobre la información extrínseca usando las mismas reglas de entrelazado que las aplicadas a la secuencia de bits por el entrelazador de bits del transmisor representado en la Fig. 25. El entrelazador de bits 2750 realimenta entonces la información extrínseca entrelazada al desmapeador de constelación 2720. El desmapeador de constelación 2720 usa la información extrínseca así realimentada como una información a priori para calcular valores LLR más fiables.

El desentrelazador de bits 2730 realiza entonces un proceso de entrelazado sobre los valores LLR nuevamente calculados (es decir, un proceso de un desentrelazado de bits) de modo que cancele el proceso de entrelazado de

bits aplicado a la secuencia de bits por el entrelazador de bits en el transmisor representado en la Fig. 25 y restaure el orden original de la secuencia de bits. El decodificador LDPC 2740 usa los valores LLR así desentrelazados en el proceso de decodificación LDPC.

Como se muestra en la Fig. 28, un bucle de decodificación iterativo se compone de cuatro elementos, concretamente el desmapeador de constelación 2720, el desentrelazador de bits 2730, el decodificador LDPC 2740 y el entrelazador de bits 2750. El desentrelazador de bits 2730 y el entrelazador de bits 2750 tienen beneficiosamente una latencia muy baja, idealmente cero, y baja complejidad. Esto da como resultado una implementación del receptor más eficiente. El desentrelazador de bits 2730 y el entrelazador de bits 2750 descritos anteriormente satisfacen ambos estas condiciones.

La Fig. 29 ilustra el decodificador BICM iterativo que realiza una implementación en paralelo muy eficiente.

La Fig. 29 es un diagrama de bloques de un decodificador BICM de ejemplo que pertenece una realización adicional de la divulgación. En la Fig. 29, el decodificador BICM 2900 corresponde a los parámetros anteriormente dados (es decir, Q = 8, N = 12, M = 4).

Tal como se muestra, el decodificador BICM 2900 incluye una memoria LLR principal 2901, una memoria LLR intermedia 2902, un controlador LDPC 2911, un rotador 2912, un grupo de procesador de nodo de comprobación 2913, un desrotador 2914, un contador QB 2931, una tabla A 2932, un grupo sustractor 2933, entrelazador B 2934, grupo de registro 2935, entrelazador C 2936, un grupo desmapeador 2937, desentrelazador C 2938, grupo de registro 2939, desentrelazador B 2940, y un retardador 2941.

En la Fig. 29, dado que Q = 8, la memoria LLR principal 2901 y la memoria LLR intermedia 2902 da cada una ocho valores LLR a la vez, el grupo procesador de nodo de comprobación 2913 incluye ocho procesadores de nodo de comprobación y el grupo desmapeador 2951 incluye ocho desmapeadores. También, dado que M =4, los grupos de registro 2935 y 2972 incluyen cada uno cuatro registros.

Los desmapeadores en el grupo desmapeador 2937 realizan cada uno un proceso de desmapeado sobre la salida

de un demodulador (no diagramado), a continuación produce la salida de los valores LLR así obtenidos al desentrelazador C 2938. El grupo desmapeador 2937 compone el desmapeador de constelación 2720 del decodificador BICM iterativo mostrado en la Fig. 28.

El desentrelazador C 2938 aplica un proceso de desentrelazado a los valores LLR (es decir, un nuevo proceso de entrelazado que cancela el proceso de entrelazado aplicado por el transmisor durante la etapa C), a continuación produce la salida de los valores LLR desentrelazados hacia los registros del grupo de registros 2939. Cada registro almacena un bloque cíclico de valores LLR (es decir, ocho valores LLR). En el grupo de registro 2939, el bloque cíclico de los valores LLR almacenados por cada registro es sacado secuencialmente a un último enlace de modo que el contenido de cada registro se actualice secuencialmente. El desentrelazador B 2940 aplica un proceso de desentrelazado al bloque cíclico de (ocho) valores LLR (es decir, un nuevo proceso de entrelazado que cancela el proceso de entrelazado aplicado por el transmisor durante la etapa B), a continuación escribe los resultados en la memoria LLR principal 2901 y la memoria LLR intermedia 2902 de acuerdo con la tabla A 2932 (explicada a continuación). Se consigue un proceso de entrelazado que cancela el proceso de entrelazado aplicado por el transmisor durante la etapa A mediante esta escritura en la memoria LLR principal 2901 y la memoria LLR intermedia 2902 de acuerdo con el contenido de la tabla A 2932.

De ese modo, la memoria LLR principal 2901 almacena los valores LLR posteriores al desentrelazado, y se usa también por el decodificador LDPC (es decir, el controlador LDPC 2911, el rotador 2912, el grupo de procesador de nodo de comprobación 2913, y el desrotador 2914). El proceso de decodificación LDPC es un proceso iterativo que implica una o más iteraciones. En cada iteración de decodificación LDPC, se actualizan los valores LLR en la memoria LLR principal 2901. Para calcular la información extrínseca necesaria para la decodificación BICM iterativa, se guardan los valores LLR antiguos en la memoria LLR intermedia 2902.

A continuación se describen las operaciones del decodificador LDPC.

15

20

45

El controlador LDPC 2911 produce la salida de la dirección de lectura de la memoria LLR principal 2901 de acuerdo con la matriz de comprobación de paridad de los códigos LDPC. De ese modo, la memoria LLR principal 2901 produce la salida secuencial de un bloque cíclico de valores LLR hacia el rotador 2912. El rotador 2912 está 25 controlado por el controlador LDPC 2911 para realizar un número predeterminado de desplazamientos cíclicos sobre el bloque cíclico de valores LLR suministrado secuencialmente por la memoria LLR principal 2901, a continuación produce la salida de los valores LLR así desplazados a los procesadores del nodo de comprobación del grupo procesador del nodo de comprobación 2913 uno cada vez. Los procesadores del nodo de comprobación del grupo 30 procesador del nodo de comprobación 2913 están controlados por el controlador LDPC 2911 para realizar un proceso en el nodo de comprobación sobre la secuencia de valores LLR secuencialmente introducidos en el mismo. A continuación, los procesadores del nodo de comprobación del grupo procesador del nodo de comprobación 2913 están controlados por el controlador LDPC 2911 para producir secuencialmente la salida de los valores LLR resultantes del proceso del nodo de comprobación. El desrotador 2914 está controlado por el controlador LDPC 35 2911 para realizar un número predeterminado de desplazamientos cíclicos que cancelen el desplazamiento cíclico aplicado al bloque cíclico secuencialmente recibido desde el grupo procesador del nodo de comprobación 2913 por el rotador 2912, a continuación produce la salida secuencialmente de los resultados desplazados hacia la memoria LLR principal 2901. El controlador LDPC 2911 produce la salida de la dirección de escritura hacia la memoria LLR principal 2901 de acuerdo con la matriz de comprobación de paridad de los códigos LDPC. De ese modo, la 40 memoria LLR principal 2901 almacena el bloque cíclico de resultados secuencialmente suministrados a la misma por el desrotador 2914. El controlador LDPC 2911 ejecuta repetidamente el procesamiento descrito anteriormente de acuerdo con la matriz de comprobación de paridad de los códigos LDPC.

Después de un número predeterminado de iteraciones LDPC, se realiza una iteración BICM. Las iteraciones LDPC y BICM son denominadas también respectivamente como iteraciones interior y exterior. Estos dos tipos de iteraciones también pueden solaparse en algunas implementaciones. Esto permite que se incremente la velocidad de convergencia. Los procesos de decodificación BICM y LDPC son bien conocidos en el campo, y los detalles de los mismos se omiten por ello.

El contador QB 2931 cuenta desde 0 a 11 y produce la salida del valor del contador a la tabla A 2932. La operación de contaje del contador QB 2931 se define en consideración a N = 12.

La Tabla A 2932 es una tabla de búsqueda simple en la que se almacenan las reglas de permutación del bloque cíclico. Esto es, la Tabla A 2932 almacena N = 12 piezas de información del orden de lectura (y escritura) del bloque cíclico (es decir, con información que asocia un bloque cíclico diferente con cada uno de los 12 valores de contador desde el contador QB 2631). La Tabla A 2932 produce la salida de direcciones de lectura hacia la memoria LLR principal 2901 y a la memoria LLR intermedia 2902 de modo que un bloque cíclico de valores LLR correspondientes al valor de contador suministrado por el contador QB 2931 se suministren al grupo sustractor 2933 por la memoria LLR principal 2901 y a la memoria LLR intermedia 2902. De ese modo, la memoria LLR principal 2901 y la memoria LLR intermedia 2902 produce cada una la salida de un bloque cíclico de valores LLR que corresponden al valor de contador del contador QB 2931 al sustractor 2934. El retardador 2941 realiza un ajuste del retardo de modo que la posición del valor LLR leído desde la memoria LLR principal 2901 y la memoria LLR intermedia 2902 coincida con la posición de escritura de los mismos valores LLR hacia la memoria LLR principal 2901 y la memoria LLR intermedia

2902. El procesamiento por la tabla A 2932 es ejecutado como el proceso de permutación del bloque cíclico (etapa A).

El sustractor 2933 en el grupo sustractor sustrae la salida de la memoria LLR intermedia 2902 de la salida de la memoria LLR principal 2901, a continuación produce la salida de información extrínseca para un bloque cíclico así obtenido (es decir, ocho piezas de información extrínseca) al entrelazador B 2934.

El entrelazador B 2634 realiza un número predeterminado de desplazamientos cíclicos sobre las piezas de información extrínseca para un bloque cíclico suministrado por el sustractor 2933, y produce la salida de los resultados a un primer registro de enlace del grupo de registros 2935. El procesamiento realizado por el entrelazador B 2934 corresponde a la permutación intra-bloque cíclico (etapa B). Cada registro del grupo de registros 2935 almacena ocho bits con tiempos coincidentes con la recepción de un pulso de control, y produce la salida de ocho bits antes de recibir el siguiente pulso de control.

Cuando el contador QB 2631 realiza el proceso anteriormente mencionado para el contaje de valores 0 a 3, la información extrínseca para cuatro bloques cíclicos (es decir, 32 piezas de información extrínseca) se introduce en el entrelazador C 2936. En este momento, el entrelazador C 2936 realiza un proceso de entrelazado sobre la información extrínseca introducida al mismo para cuatro bloques cíclicos, a continuación produce la salida de una palabra de constelación de información extrínseca (es decir, *M* = 4 piezas de información extrínseca) a cada desmapeador del grupo desmapeador 2937. A través del proceso de entrelazado, se suministran las cuatro piezas de información extrínseca a los desmapeadores del grupo desmapeador 2951 desde los cuatro registros en el grupo de registros 2935, uno cada vez. Este procesamiento por el entrelazador C 2936 se ejecuta como el proceso de permutación columna-fila (etapa C).

El contador QB 2931, la tabla A 2932, el entrelazador B 2934, el grupo de registro 2935, y el entrelazador C 2936 componen el entrelazador de bits 2750 del decodificador BICM mostrado en la Fig. 28.

Los desmapeadores del grupo desmapeador 2937 usan las cuatro piezas de información extrínseca suministradas por el entrelazador C 2936 como una información a priori para realizar un proceso de desmapeado, a continuación producen la salida de los valores LLR resultantes al desentrelazador C 2938.

El desentrelazador C 2938 aplica un proceso de desentrelazado a los valores LLR (es decir, un nuevo proceso de entrelazado que cancela el proceso de entrelazado aplicado por el transmisor durante la etapa C), a continuación produce la salida de los valores LLR desentrelazados a los registros del grupo de registro 2939. Cada registro almacena un bloque cíclico de valores LLR (es decir, ocho valores LLR). En el grupo de registro 2939, el bloque cíclico de valores LLR almacenados por cada registro se saca secuencialmente a un nivel de enlace de modo que el contenido de cada registro se actualice secuencialmente. El desentrelazador B 2940 aplica un proceso de desentrelazado al bloque cíclico de (ocho) valores LLR (es decir, un nuevo proceso de entrelazado que cancela el proceso de entrelazado aplicado por el transmisor durante la etapa B), a continuación escribe los resultados en la memoria LLR principal 2901 y la memoria LLR intermedia 2902. La memoria LLR principal 2901 y la memoria LLR intermedia 2902 reciben la dirección de escritura desde la tabla A 2932 a través del retardador 2941, a continuación almacenan un bloque cíclico de valores LLR (es decir, ocho valores LLR) recibidos desde el desentrelazador 2940 de acuerdo con la dirección de escritura recibida. Se consigue un proceso de entrelazado que cancela el proceso de entrelazado aplicado por el transmisor durante la etapa A (es decir, un proceso de desentrelazado) mediante esta escritura de acuerdo con el contenido de la tabla A 2932.

40 Para cada palabra de código, se aplica el conjunto de procesos descritos anteriormente tres veces, una vez para los valores del contador 0-3, 4-7 y 8-11 del contador QB 2931.

El contador QB 2931, la tabla A 2932, el desentrelazador B 2938, el grupo de registros 2939, el entrelazador C 2940 componen el entrelazador de bits 2730 del decodificador BICM mostrado en la Fig. 28.

El entrelazador B 2934 y el desentrelazador B 2940 son reconfigurables. Esto requiere un cierto coste de hardware, pero este coste se minimiza por un diseño cuidadoso. El entrelazador C 2936 y el desentrelazador 2938 implementan la permutación columna-fila. Esta permutación es uniforme para un tamaño de constelación predeterminado. De ese modo, se reduce el coste de la implementación.

La realización representada en la Fig. 29 incluye Q desmapeadores que operan en paralelo. Sin embargo, los desmapeadores se pueden realizar también como un decodificador BICM iterativo mediante la disminución o incremento del paralelismo. Por ejemplo, el número de secciones de entrelazador paralelas en el entrelazador de bits, es decir el cociente de *N/M*, obviamente se puede incrementar de modo que mejore fácilmente el paralelismo. Dichos métodos permiten que se optimice el paralelismo mediante el paralelizado de los desmapeadores Q×*N/M*. El entrelazador de bits anteriormente descrito tiene el mérito de poder ser implementado con dicho paralelismo sin perturbaciones.

55 (Descubrimientos de Experimentador Adicionales)

10

15

20

25

30

35

50

Los entrelazadores que satisfacen las Condiciones 1 y 2 dadas anteriormente (es decir, entrelazadores paralelos)

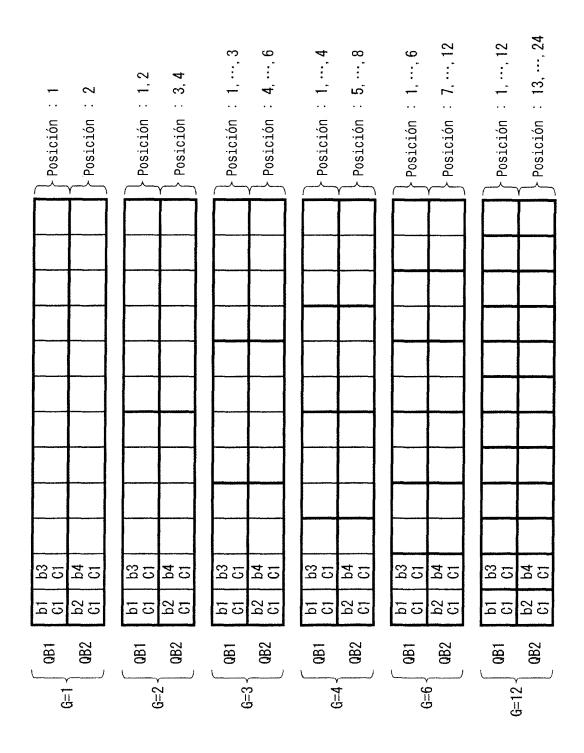

suponen que el número de bits por palabra de constelación M es un divisor del número de bloques cíclicos N. Sin embargo, M no es normalmente un divisor de N. Por ejemplo, los códigos 16K LDPC usados en la norma DVB-T2 tienen N = 45 bloques cíclicos por palabra de código de 16K LDPC. Cuando M no es un divisor de N, el mapeado de las constelaciones cuadradas, tales como las constelaciones QAM en donde M es par, no es directo.

Así, se propone una solución particular que implica la ejecución de uno o más de los *N* bloques cíclicos y la implementación del entrelazador explicado en el Realización 1 (es decir, el entrelazador paralelo) anteriormente, solo para los bloques cíclicos restantes.

En otras palabras, se seleccionan *N'* bloques cíclicos de entre los *N* bloques cíclicos de modo que *N'* sea un múltiplo del número de bits por palabras de constelación *M* en el entrelazador de bits. El entrelazador de bits divide los *N'* bloques cíclicos seleccionados en *N'*/*M* secciones de modo que cada sección incluye *M* bloques cíclicos, a continuación realiza una permutación de sección sobre cada sección. Los bits de los bloques cíclicos excluidos (es decir, no seleccionados) pueden o no ser entrelazados.

10

15

20

25

Específicamente, se pretende un método de entrelazado que pertenece a la divulgación para un sistema de comunicación que use códigos cuasi cíclicos de comprobación de paridad de baja densidad, y comprende: una etapa de recepción de la recepción de una palabra de código de los códigos cuasi cíclicos de comprobación de paridad de baja densidad compuestos de *N* bloques cíclicos incluyendo cada uno *Q* bits; una etapa de permutación de bits de aplicación de un proceso de permutación de bits a la palabra de código de modo que permute los bits en la palabra de código; una etapa de división de división de la palabra de código, tras el proceso de permutación de bits, en una pluralidad de palabras de constelación, estando compuesta cada una de las palabras de constelación de *M* bits e indicando uno de los 2<sup>M</sup> puntos de constelación predeterminados; y una etapa de selección para la selección de un subconjunto de *N'* de bloques cíclicos de entre los *N* bloques cíclicos de modo que *N'* sea un múltiplo de *M*, en el que previamente al proceso de permutación de bits, la palabra de código se divide en *N'IM* secciones, incluyendo cada una de las secciones *M* de los bloques cíclicos, y estando asociada cada una de las palabras de constelación con una de las *N'IM* secciones, y en la etapa de permutación de bits, el proceso de permutación de bits se aplica de modo que los *M* bits en cada una de las palabras de constelación incluye un bit de cada uno de los *M* diferentes bloques cíclicos en una sección dada asociada con una palabra de constelación dada, y de modo que todos los bits en la sección dada estén mapeados solo a Q de las palabras de constelación asociadas con la sección dada.

De modo similar, se pretende un entrelazador de bits que pertenece a la divulgación para su uso en un sistema de 30 comunicación que use códigos cuasi cíclicos de comprobación de paridad de baja densidad, y comprende: una unidad de permutación de bits que recibe una palabra de código de los códigos cuasi cíclicos de comprobación de paridad de baja densidad compuestos de N bloques cíclicos incluyendo cada uno Q bits; la aplicación de un proceso de permutación de bits a la palabra de código de modo que permute los bits en la palabra de código, y la división de división de la palabra de código, para la salida después del proceso de permutación de bits, en una pluralidad de palabras de constelación, estando compuesta cada una de las palabras de constelación de M bits e indicando uno 35 de los 2<sup>M</sup> puntos de constelación predeterminados; y una unidad de selección que selecciona un subconjunto de N' de bloques cíclicos de entre los N bloques cíclicos de modo que N' sea un múltiplo de M, en el que previamente al proceso de permutación de bits, la palabra de código se divide en N'/M secciones, incluyendo cada una de las secciones M de los bloques cíclicos, y estando asociada cada una de las palabras de constelación con una de las 40 N'/M secciones, y la unidad de permutación de bits aplica el proceso de permutación de bits de modo que los M bits en cada una de las palabras de constelación incluye un bit de cada uno de los M diferentes bloques cíclicos en una sección dada asociada con una palabra de constelación dada, y de modo que todos los bits en la sección dada estén mapeados solo a Q de las palabras de constelación asociadas con la sección dada.

También, los bits en la palabra de código incluyen un grupo de bits que es uno de entre: no incluido en el subconjunto seleccionado de *N'* bloques cíclicos y dejado tal como está sin redisposición; y no incluido en el subconjunto seleccionado de *N'* bloques cíclicos, y sometido a un proceso de redisposición que es independiente del proceso de permutación de bits y que se aplica solamente a cualquiera de los bloques cíclicos no seleccionados.

De acuerdo con esta configuración, el entrelazador de bits se aplica a un número maximizado de bloques cíclicos.

Por ejemplo, los bloques cíclicos excluidos pueden ser bloques cíclicos que tengan un nodo variable del peso más bajo. Por ejemplo, códigos RA QC LDPC (véase la Fig. 5), los bloques cíclicos excluidos son los bloques cíclicos de la sección de paridad (que tiene en un peso de nodo variable de dos), y son beneficiosamente el último o más bloques cíclicos de la palabra de código.

Más aún, la etapa de selección es también utilizable para la selección de los bloques cíclicos de acuerdo con la importancia de los bits incluidos en ellos.

La importancia de los bits incluidos en los bloques cíclicos se determina de acuerdo con el número de bits de paridad asociados con ellos.

Cuando la palabra de código es para códigos cuasi cíclicos de comprobación de paridad de baja densidad de acumulación repetida, los bloques cíclicos no seleccionados corresponden a la sección de paridad de la palabra de

código.

10

15

20

De acuerdo con esta configuración, la mayor parte de los bits que corresponden a la palabra de código están implicados en un entrelazado óptimo. La reducción del número de bits implicados en el entrelazado da como resultado en una gran mejora global de la eficacia.

5 Adicionalmente, el subconjunto de *N'* bloques cíclicos seleccionados puede formarse a partir de *N'* bloques cíclicos continuos que comienzan con el primer bit de la palabra de código.

De acuerdo con esta configuración, la implementación en hardware se simplifica adicionalmente. Particularmente, para el ejemplo de la matriz de comprobación de paridad en los códigos cuasi cíclicos de comprobación de paridad de baja densidad de acumulación repetida, el último bit de la palabra de código es el bit que tiene la menor asociatividad.