## OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 704 010

51 Int. Cl.:

H02M 7/49 (2007.01) H02M 1/32 (2007.01) H02M 7/483 (2007.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 02.08.2006 PCT/EP2006/064943

(87) Fecha y número de publicación internacional: 29.03.2007 WO07033850

(96) Fecha de presentación y número de la solicitud europea: 02.08.2006 E 06792641 (0)

(97) Fecha y número de publicación de la concesión europea: 03.10.2018 EP 1927182

(54) Título: Procedimiento de control para el uso de redundancia en el caso de fallo de un convertidor polifásico con acumuladores de energía distribuidos

(30) Prioridad:

21.09.2005 DE 102005045091

Fecha de publicación y mención en BOPI de la traducción de la patente: 13.03.2019

(73) Titular/es:

SIEMENS AKTIENGESELLSCHAFT (100.0%) Werner-von-Siemens-Straße 1 80333 München, DE

(72) Inventor/es:

SOMMER, RAINER y HILLER, MARC

(74) Agente/Representante:

**CARVAJAL Y URQUIJO, Isabel**

#### **DESCRIPCIÓN**

Procedimiento de control para el uso de redundancia en el caso de fallo de un convertidor polifásico con acumuladores de energía distribuidos

La presente invención hace referencia a un procedimiento para controlar un convertidor con al menos dos módulos de fase que presentan un ramal de válvula superior e inferior que presentan respectivamente al menos tres subsistemas bipolares conectados en serie en el caso de la avería de al menos un subsistema de un ramal de válvula.

10

15

20

45

50

55

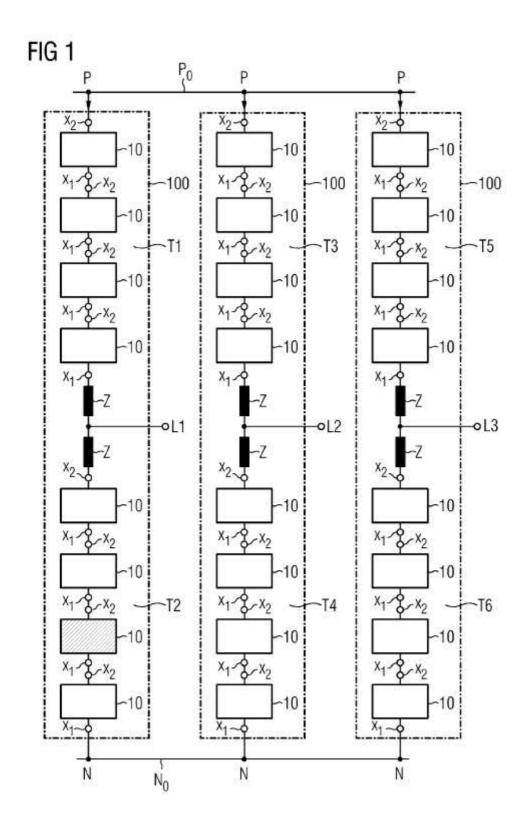

Un circuito de convertidor conforme al género, de esa clase, se conoce por la solicitud DE 101 03 031 A1 y en la figura 1 se representa en detalle un esquema de circuito equivalente de un circuito de convertidor de esa clase. De acuerdo con dicho esquema de circuito equivalente, ese circuito de convertidor conocido presenta tres módulos de fase que respectivamente están indicados con la referencia 100. Esos módulos de fase 100, del lado de tensión continua, están conectados de forma eléctricamente conductora con una barra colectora de tensión continua positiva y negativa P<sub>0</sub> y N<sub>0</sub>. Entre esas dos barras colectoras de tensión continua P<sub>0</sub> y N<sub>0</sub> se aplica una tensión continua no indicada en detalle. Cada módulo de fase 100 que forma un ramal en puente del convertidor polifásico presenta un ramal en puente superior y uno inferior que, puesto que esos ramales en puente parciales representan respectivamente una válvula de convertidor del convertidor polifásico con acumuladores de energía distribuidos, se denominan a continuación como ramal de válvula T1, así como T3, así como T5 y T2, sí como T4, así como T6. Cada uno de esos ramales de válvula T1 T6 presenta una cantidad de subsistemas bipolares 10 conectados eléctricamente en serie. En ese esquema de circuito equivalente están representados cuatro de esos subsistemas 10. Cada punto de vinculación de dos ramales de válvula T1 y T2, así como T3 y T4, así como T5 y T6, de un módulo de fase 100 forma una conexión L1, así como L2, así como L3, del lado de tensión alterna, de ese módulo de fase 100. Puesto que en esa representación el circuito de convertidor presenta tres módulos de fase 100, en sus conexiones L1. L2 v L3 del lado de tensión continua, denominadas también como conexiones de carga, puede conectarse una carga trifásica, por ejemplo un motor trifásico.

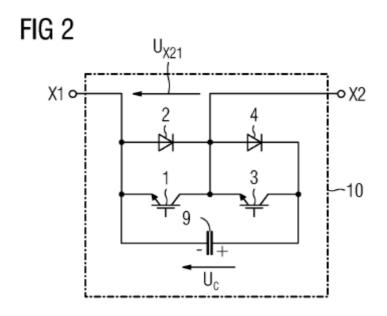

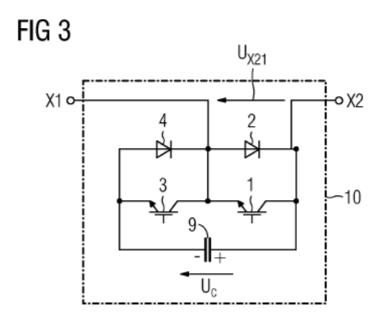

25 En la figura 2 se representa en detalle un esquema de circuito equivalente de una forma de ejecución conocida de un subsistema bipolar 10. La disposición de circuito según la figura 3 representa una variante funcionalmente por completo equivalente, la cual igualmente es conocida por la solicitud DE 101 03 031 A1. Ese subsistema bipolar 10 conocido presenta dos semiconductores 1 y 3 que pueden desconectarse, dos diodos 2 y 4 y un condensador de almacenamiento unipolar 9. Los dos semiconductores 1 y 3 que pueden desconectarse están conectados 30 eléctricamente en serie, donde ese circuito en serie está conectado de forma eléctricamente paralela con respecto al condensador de almacenamiento 9. A cada semiconductor 1 y 3 que puede desconectarse está conectado de forma eléctricamente paralela uno de los dos diodos 2 y 4, de modo que el mismo se encuentra conectado de forma antiparalela con respecto al semiconductor 1 ó 3 correspondiente que puede desconectarse. El condensador de almacenamiento unipolar 9 del subsistema 10 se compone de un condensador o de una batería de condensador 35 compuesta por varios condensadores de esa clase con una capacidad C0 resultante. El punto de conexión desde el emisor del semiconductor 1 que puede desconectarse 1 y el ánodo del diodo 2 forma un borne de conexión X1 del subsistema 10. El punto de conexión de los dos semiconductores 1 y 3 que pueden desconectarse y de los dos diodos 2 y 4 forman un segundo borne de conexión X2 del subsistema 10.

En la forma de ejecución del subsistema 10 según la figura 3 ese punto de conexión forma el primer borne de conexión X1. El punto de conexión desde el colector del semiconductor 1 que puede desconectarse 1 y el cátodo del diodo 2 forma el segundo borne de conexión X2 del subsistema 10.

En ambas representaciones de las dos formas de ejecución del subsistema 10, como semiconductores 1 y 3 que pueden desconectarse se utilizan transistores de puerta aislada (IGBT), tal como se representan en las figuras 2 y 3. Pueden utilizarse igualmente transistores de efecto de campo MOS, denominados también como MOSFET. Además, pueden utilizarse también tiristores desactivados por compuerta, denominados también tiristores GTO, o tiristores controlados por puerta integrada (IGCT).

De acuerdo con la solicitud DE 101 03 031 A1, los subsistemas 10 de cada módulo de fase 100 del circuito de convertidor según la figura 1 se controlan en un estado de conmutación I, II y III. En el estado de conmutación I el semiconductor 1 que puede desconectarse está conectado y el semiconductor 3 que puede desconectarse está desconectado Debido a ello una tensión en bornes Ux21 del subsistema 10 aplicada en los bornes de conexión X1 y X2 es igual a cero. En el estado de conmutación II el semiconductor 1 que puede desconectarse está desconectado y el semiconductor 3 que puede desconectarse está conectado. En ese estado de conmutación II, la tensión en bornes Ux21 aplicada es igual a la tensión del condensador Uc aplicada en el condensador de almacenamiento 9. En el estado de conmutación III ambos semiconductores 1 y 3 que pueden desconectarse están desconectados y la tensión del condensador Uc que se aplica en el condensador de almacenamiento 9 es constante.

Para que ese convertidor con acumuladores de energía 9 distribuidos según la figura 1 pueda trabajar de forma redundante, debe asegurarse que un subsistema 10 defectuoso esté cortocircuitado en sus bornes X1 y X2 de forma permanente. Es decir que la tensión en bornes  $U_{X21}$  del subsistema 10 averiado es cero, independientemente de la dirección de la corriente a través de los bornes X1 y X2.

5 A través de la avería de uno de los semiconductores 1 ó 3 que puede desconectarse, que se encuentra presente en el subsistema 10, o de un circuito de activación correspondiente, ese subsistema 10 se encuentra afectado en cuanto a su funcionamiento correcto. Otras causas posibles para fallas de funcionamiento son, entre otras, fallos en el circuito de activación asociado de los semiconductores, su abastecimiento de corriente, comunicación y registro de los valores de medición. Es decir que el subsistema 10 ya no puede controlarse del modo deseado en uno de los 10 posibles estados de conmutación I, II ó III. A través del cortocircuito del subsistema 10 en sus conexiones X1 y X2 a ese subsistema 10 ya no se suministra energía. Debido a ello se excluyen de forma segura daños secundarios como sobrecalentamiento e incendio en el caso de un funcionamiento posterior del convertidor. Una conexión conductora a modo de un cortocircuito, de esa clase, entre los bornes de conexión X1 y X de un subsistema 10 averiado debe conducir al menos la corriente de servicio de un ramal de válvula T1,..., T6 del módulo de fase 100, en el subsistema 15 10 averiado, de forma segura y sin un sobrecalentamiento. En la solicitud de patente nacional más antiqua con el número de referencia interno 2005P12103 DE se indica cómo un subsistema 10 averiado puede cortocircuitarse de forma segura, para que ese convertidor conocido pueda operarse posteriormente de forma redundante con acumuladores de energía distribuidos.

20

25

30

35

40

45

50

55

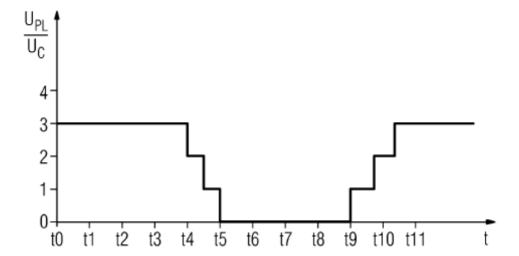

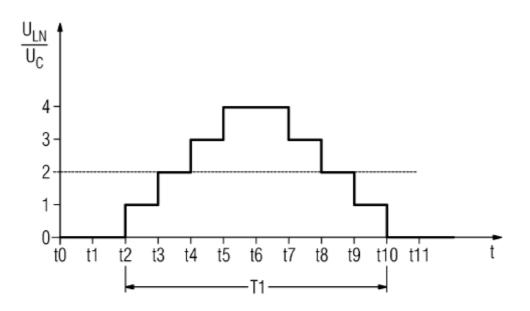

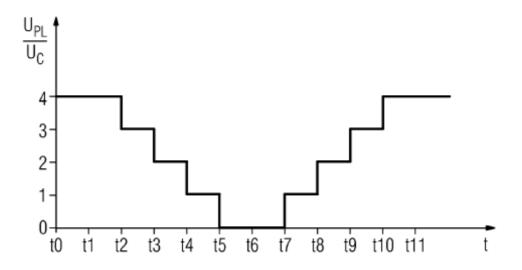

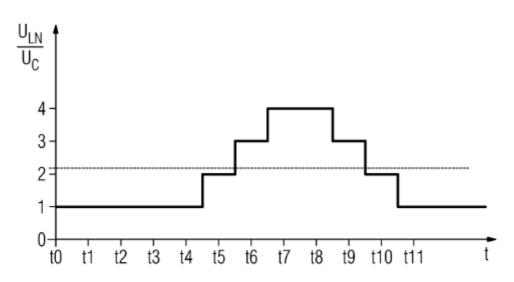

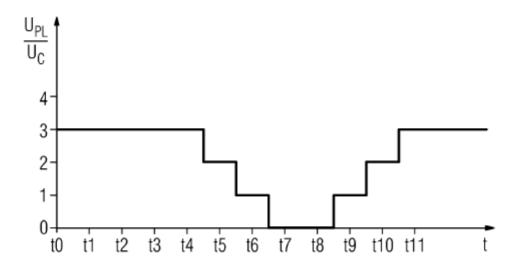

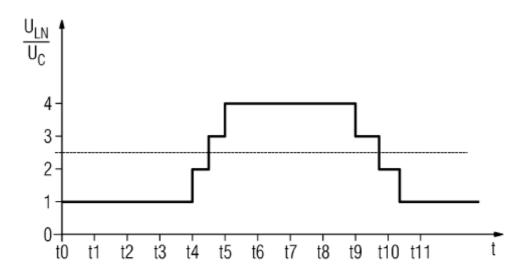

Para la siguiente explicación se supone que los condensadores de acumulación 9 de todos los subsistemas 10 presentan respectivamente la misma tensión Uc. Procedimientos para la producción inicial de ese estado y de su mantenimiento durante el funcionamiento se conocen igualmente por la solicitud DE 101 03 031 A1. En la figura 4, en un diagrama a lo largo del tiempo t se representa un desarrollo de la diferencia de potencial U<sub>LN</sub> del borne L de un módulo de fase 100 con respecto a un potencial de referencia N seleccionado. En la figura 5, en un diagrama a lo largo del tiempo t se representa un desarrollo de la diferencia de potencial UPL del borne P con respecto a una conexión de carga L. Los dos desarrollos de potencial ULN y UPL mencionados están estandarizados en la tensión Uc de los condensadores de acumulación 9 de los subsistemas 10. De acuerdo con esos desarrollos de potencial ULN/Uc(t) y UPL/Uc(t) estandarizados, en los tiempos t2, t3, t4, t5, así como t7, t8, t9 y t10, de los cuatro subsistemas 10 del ramal de válvula T2, así comoT1, se conecta y desconecta, así como se desconecta y conecta respectivamente un subsistema 10. Una conexión corresponde en este caso a un pasaje del estado de conmutación I al estado de conmutación II. Una desconexión corresponde a un pasaje del estado de conmutación II al estado de conmutación I. En esos dos diagramas se representa respectivamente un período Tp del desarrollo de potencial estandarizado U<sub>LN</sub>/U<sub>C</sub>(t) y U<sub>PL</sub>/U<sub>C</sub>(t). Las partes correspondientes de armónicos o componentes de tensión continua, respectivamente en las tensiones de salida U<sub>LN</sub> de los módulos de fase 100 del convertidor polifásico con acumuladores de energía 9 distribuidos, en el caso de un sistema de tensión trifásica simétrico, se eliminan en las tensiones diferenciales respectivamente de dos tensiones de salida ULIN, UL2N O UL3N desplazadas en cuanto a las fases. En base a esos dos desarrollos de potencial ULN/Uc(t) y UPL/Uc(t) estandarizados puede observarse además que la suma de los potenciales estandarizados es cuatro en todo momento. Es decir que la tensión continua entre las barras colectoras de tensión continua Po y No corresponde siempre a una cantidad constante de subsistemas 10 en el estado de conmutación II multiplicado por la tensión del condensador Uc aplicada en el condensador 9. En el caso representado a modo de ejemplo esa cantidad corresponde a la cantidad de subsistemas 10 del convertidor según la figura 1, la cual se encuentra presente en los ramales de válvula T1,..., T6. En el tiempo t0 y t1 los cuatro subsistemas 10, por ejemplo del ramal de válvula T1, se encuentran todos en el estado de conmutación II (Ux21 = Uc) y los cuatro subsistemas 10 del ramal de válvula T2 correspondiente al módulo de fase se encuentran todos en el estado de conmutación I ( $U_{X21} = 0$ ). En el tiempo t2, t3, t4 y t5, respectivamente un submódulo 10 del ramal de válvula T1 cambia el estado de conmutación de II a I, mientras que respectivamente un subsistema 10 del ramal de válvula T2 cambia el estado de conmutación de I a II. Si un subsistema 10 de un ramal de válvula T1, T2, así como T3, T4, así comoT5, T6 de un módulo de fase 100 del convertidor polifásico según la figura 1 se avería por cualquier fallo, entonces al menos una de las tres tensiones de salida ULIN, ULIN O ULIN de ese convertidor polifásico con acumuladores de energía 9 distribuidos presenta componentes armónicos y/o de tensión continua que, eventualmente, pueden conducir a una desconexión de ese convertidor según la figura 1.

En la solicitud US 5 986 909 se describe un procedimiento para controlar un convertidor en el caso de la avería de al menos un subsistema de un ramal de válvula. El mismo se basa en un suministro de energía polifásico con una pluralidad de celdas dispuestas en serie, así como con una derivación. Un nivel de salida elevado se alcanza a través de una pluralidad de celdas en los brazos individuales. Las celdas averiadas en un brazo son puenteadas (a modo de una derivación) para posibilitar una ruta de corriente en el brazo afectado. Las celdas no averiadas se utilizan para alcanzar un nivel idéntico y una relación de fases compensada en la tensión de salida.

El objeto de la invención consiste en proporcionar un procedimiento de control con el cual las condiciones de simetría puedan observarse también en el caso de una avería de al menos un subsistema de un módulo de fase de un convertidor con acumuladores de energía distribuidos.

Dicho objeto, según la invención, se soluciona con las características de la reivindicación 1. En la reivindicación 2 está definida una forma de ejecución preferente.

Debido a que según la invención, en los módulos de fase no averiados del convertidor polifásico con acumuladores de energía distribuidos respectivamente un subsistema de un ramal de válvula correspondiente al ramal de válvula con el subsistema averiado se activa de modo que sus tensiones en bornes son iguales a cero durante el caso de avería, todas las tensiones de salida del convertidor con acumuladores de energía distribuidos nuevamente son iguales, de manera que su tensión diferencial ya no presenta componentes de armónicos y/o de tensión continua que pueden dividirse por tres.

5

20

25

30

50

En un procedimiento ventajoso, un subsistema de un ramal de válvula correspondiente al ramal de válvula averiado, del módulo de fase averiado, se activa de modo que su tensión en bornes es igual a una tensión del condensador del subsistema. Debido a ello, la tensión de salida de ese módulo de fase averiado nuevamente es simétrica con respecto al valor medio de un componente fundamental de esa tensión de salida escalonada. En los módulos de fase no averiados se procede de modo correspondiente, de manera que las tres tensiones de salida de un convertidor trifásico con acumuladores de energía distribuidos forman nuevamente un sistema de tensión trifásica simétrico. Además, el valor de la tensión del circuito intermedio corresponde al valor de la tensión del circuito intermedio en el caso sin averías, debido a lo cual la carga de tensión de los semiconductores del sistema que pueden desconectarse corresponde igualmente a la carga de tensión en el caso sin averías.

En otro procedimiento ventajoso, los tiempos de conmutación de las señales de control para los subsistemas de los ramales de válvula de los módulos de fase del convertidor polifásico con acumuladores de energía distribuidos están temporalmente desplazados. A través de ese desplazamiento temporal de las señales de control para los subsistemas de cada módulo de fase se logra que el desarrollo de la amplitud no afectada de un componente fundamental de una tensión de salida de fases aproximadamente se mantenga en el caso de un fallo.

Con ese procedimiento de control según la invención, las tensiones de salida de los módulos de fase de un convertidor polifásico con acumuladores de energía distribuidos pueden mantenerse también en el caso de un fallo. Debido a ello, ese convertidor puede operarse de forma redundante. Para una carga polifásica conectada a ese convertidor polifásico con acumuladores de energía distribuidos no puede detectarse si se encuentran averiados subsistemas, ni cuántos, en un ramal de válvula de un módulo de fase de ese convertidor polifásico. Lo único que llama la atención es que ese sistema de tensión de salida polifásico, en el caso de un punto de funcionamiento no modificado, presenta una amplitud reducida, de lo contrario no existe ninguna diferencia con respecto al punto de funcionamiento averiado

Para continuar con la explicación de la invención se hace referencia al dibujo, en el cual se ilustran esquemáticamente varias formas de ejecución de un procedimiento según la invención para controlar un convertidor polifásico con acumuladores de energía distribuidos.

La figura 1 muestra un esquema de circuito equivalente de un circuito de convertidor conocido con acumuladores de energía distribuidos,

En la figura 2 se representa un esquema de circuito equivalente de una primera forma de ejecución de un subsistema conocido,

La figura 3 muestra un esquema de circuito equivalente de una segunda forma de ejecución de un subsistema conocido,

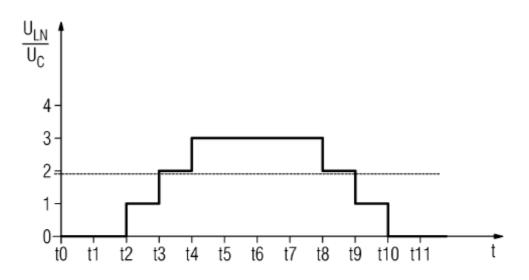

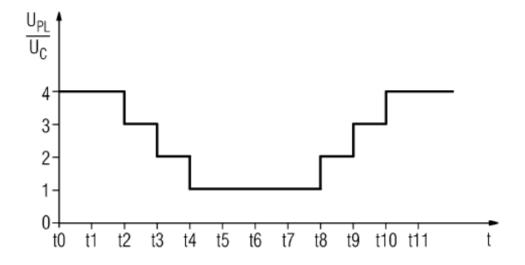

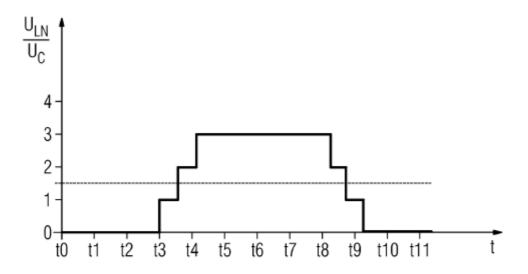

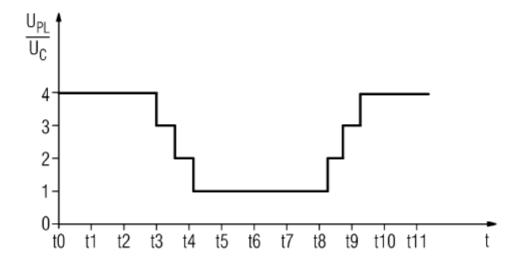

40 Las figuras 4 y 5, respectivamente en un diagrama a lo largo del tiempo t, representan desarrollos de potencial estandarizados en los dos ramales de válvula de un módulo de fase del convertidor según la figura 1,

En las figuras 6 y 7 se representan los desarrollos de potencial según las figuras 4 y 5, respectivamente en un diagrama a lo largo del tiempo t en el caso de una avería de un subsistema en un ramal de válvula inferior del convertidor según la figura 1,

En las figuras 8 y 9 se ilustran los desarrollos de potencial según las figuras 4 y 5, respectivamente en un diagrama a lo largo del tiempo t en el caso de una avería de un subsistema en un ramal de válvula superior del convertidor según la figura 1,

En las figuras 10 y 11 se representan desarrollos de potencial según las figuras 6 y 7, respectivamente en un diagrama a lo largo del tiempo t, donde adicionalmente los tiempos de conmutación de las señales de control están temporalmente desplazados,

En las figuras 12 y 13 se representan los desarrollos del potencial según las figuras 8 y 9, respectivamente en un diagrama a lo largo del tiempo t, donde adicionalmente los tiempos de conmutación de las señales de control están temporalmente desplazados.

5

10

15

20

25

30

35

40

45

50

55

60

Se supone que un subsistema 10 del ramal de válvula T2 del módulo de fase 100 del convertidor con acumuladores de energía 9 distribuidos según la figura 1 está cortocircuitado de forma segura a causa de alguna falla. Ese subsistema 10 averiado puede reconocerse en el esquema de circuito equivalente según la figura 1 mediante un rayado. Debido a ello, para generar el desarrollo temporal del potencial de salida estandarizado UL1N/Uc(t) sólo pueden utilizarse tres subsistemas 10, mientras que para generar el desarrollo temporal del potencial estandarizado UPL1 se utilizan sin embargo aún cuatro subsistemas 10. Esto significa que el desarrollo de potencial UL1N/Uc(t), en correspondencia con la figura 4, presenta una etapa de potencial menos. Es decir que ese desarrollo de potencial UL1N/UC(t) corresponde al desarrollo de potencial UL1N/UC(t) según el diagrama de la figura 6. En el desarrollo de potencial U<sub>PL1</sub>/U<sub>C</sub>(t), a través del sistema 10 averiado del ramal de válvula T2 no se ha modificado nada, de modo que ese desarrollo de potencial UPL1/UC(t), después del desarrollo de potencial UPL1/UC(t), se extiende según el diagrama de la figura 5. Debido a ello, en ese módulo de fase 100 averiado para dos unidades de tiempo t6 - t5 y t7 t6 la tensión continua aplicada entre las barras colectoras de tensión continua P<sub>0</sub> y N<sub>0</sub> es igual a 3·U<sub>c</sub>, en comparación con 4·Uc en los módulos de fase 100 no averiados. Puesto que entre las barras colectoras de tensión continua Po y No se imprime presión aplicada, en el módulo de fase 100 averiado circula una corriente de válvula más elevada que carga adicionalmente los componentes de cada subsistema 10 de ese módulo de fase 100 averiado. Si esa corriente de válvula supera valores de corriente admisibles de un componente de un subsistema 10 de ese módulo de fase 100, el convertidor polifásico con acumuladores de energía 9 distribuidos se desconecta debido a la corriente de sobrecarga.

Para evitar lo mencionado, el convertidor polifásico con acumuladores de energía 9 distribuidos se controla según la invención. Para ello primero debe determinarse qué ramal de válvula T1, T2, así como T3, T4, así como T5, T6 de un módulo de fase 100 presenta un subsistema 10 averiado. Un subsistema 10 de esa clase puede presentarse en el ramal de válvula T2, así como T4, así como T5. En el caso de que un subsistema 10 averiado se presente en el ramal de válvula T2, así como T4, así como T6, los respectivos desarrollos de potencial UL1N/Uc(t), así como UL2N/Uc(t), así como UL3N/Uc(t) se extienden en correspondencia con el desarrollo en el diagrama según la figura 6. Si un subsistema 10 averiado se presenta en el ramal de válvula T1, así como T3, así como T5, los desarrollos de potencial UPL1/Uc(t), así como UPL2/Uc(t), así como UPL3/Uc(t), así como UPL3/Uc(t), se extienden en correspondencia con el desarrollo en el diagrama correspondiente a la figura 9.

Después de que se asegura en cuál de los ramales de válvula T1,..., T6 un subsistema 10 está averiado, por ejemplo en los ramales de válvula T4 y T6, así como T3 y T5 correspondientes a ese ramal de válvula T2, así como T1 averiado, igualmente una cantidad respectivamente correspondiente de los subsistemas 10 averiados que se presentan en el ramal de válvula T2, así como T1, se activan de modo que su tensión en bornes es Ux21 = 0. Debido a ello, la tensión continua imprimida aplicada entre las barras colectoras de tensión continua P0 y N0, en todos los módulos de fase 100 del convertidor polifásico con acumuladores de energía 9 distribuidos se divide respectivamente en la misma cantidad de subsistemas 10. A través de ese control según la invención del convertidor polifásico con acumuladores de energía 9 distribuidos, las condiciones de simetría se observan también en el caso de una falla, de modo que las tensiones diferenciales entre las conexiones de carga L1, L2 y L3 no presentan componentes de armónico y de tensión continua que pueden dividirse por tres. Es decir que para una carga conectada no puede detectarse si el convertidor polifásico con acumuladores de energía 9 distribuidos trabaja en el funcionamiento averiado o no averiado. De este modo, el convertidor polifásico con acumuladores de energía 9 distribuidos es operado de forma redundante.

Si la tensión continua afectada entre las barras colectoras de tensión continua P0 y N0 y la carga de tensión de los semiconductores 1 y 3 que pueden desconectarse de los subsistemas 10 de los módulos de fase 100 de un convertidor polifásico con acumuladores de energía 9 distribuidos debe mantenerse también en el caso de una falla, de modo que en el módulo de fase 100 averiado un ramal de válvula T1, así como T3, así como T5 o T2, así como T4, así como T6, correspondiente al ramal de válvula T2, así como T4, así como T6 o T1, así como T3, así como T5 averiado, en correspondencia con la cantidad de los subsistemas 10 averiados, una cantidad correspondiente de subsistemas se activa de modo que para su tensión en bornes aplica  $U_{X21} = U_C$ . En los módulos de fase 100 no averiados del convertidor polifásico con acumuladores de energía 9 distribuidos se procede del modo correspondiente. A través de ese paso del procedimiento adicional del procedimiento según la invención, la cantidad de los subsistemas 10 utilizados en el caso averiado y no averiado de los módulos de fase 100 de ese convertidor polifásico con acumuladores de energía 9 distribuidos nuevamente es la misma. Debido a ello, los desarrollos de potencial UL1N/Uc(t) y UPL1/Uc(t), así como UL2N/Uc(t) y UPL2/Uc (t), así como UL3N/Uc(t) y UPL3/Uc(t) se extienden en correspondencia con los desarrollos en los diagramas de las figuras 6 y 7. Si un subsistema 10 se avería en el ramal de válvula T1, así como T3, así como T5 y el convertidor polifásico con acumuladores de energía 9 distribuidos es operado con el procedimiento de control ventajoso según la invención, entonces los desarrollos de potencial  $U_{L1N}/U_C(t) \ y \ U_{PL1}/U_C(t), \ asi \ como \ U_{L2N}/U_C(t) \ y \ U_{PL2}/U_C(t), \ asi \ como \ U_{L3N}/U_C(t) \ y \ U_{PL3}/U_C(t) \ se \ extienden \ en$ correspondencia con los desarrollos en los diagramas de las figuras 8 y 9. De este modo, los desarrollos de potencial en los diagramas de las figuras 6, 8 y 7, 9 corresponden a los desarrollos en los diagramas de las figuras 4

y 5, con la diferencia de que por ejemplo un subsistema 10 se utiliza menos para la generación de los desarrollos de potencial en el funcionamiento averiado. Es decir que las tensiones de salida U<sub>L1N</sub>, U<sub>L2N</sub> y U<sub>L3N</sub> del convertidor polifásico con acumuladores de energía 9 distribuidos, en el funcionamiento averiado, fallan un poco menos conforme a la amplitud. La diferencia con respecto al funcionamiento no averiado corresponde a la tensión del condensador U<sub>C</sub> de un subsistema 10. Cuantos más subsistemas 10 en el funcionamiento normal se utilicen para la generación de las tensiones de salida U<sub>L1N</sub>, U<sub>L2N</sub> y U<sub>L3N</sub> del convertidor polifásico con acumuladores de energía 9 distribuidos, tanto más reducida resulta la disminución conforme a la amplitud en el funcionamiento averiado.

5

10

25

Sin embargo, si la amplitud no alterada del componente original de cada tensión de salida U<sub>L1N</sub>, U<sub>L2N</sub> y U<sub>L3N</sub> generada del convertidor polifásico con acumuladores de energía 9 distribuidos tiene que mantenerse de forma aproximada, entonces el procedimiento de control ventajoso según la invención se modifica de modo que adicionalmente los tiempos de conmutación de las señales de control para los semiconductores 1 y 3 que pueden desconectarse de los subsistemas 10 de los ramales de válvula T1,..., T6 se desplazan temporalmente. En los diagramas de las figuras 10 y 11, así como 12 y 13 se representan los desarrollos de potencial generados de ese modo.

Ese procedimiento de control según la invención no está limitado al caso de que sólo un subsistema 10 falle en un ramal de válvula T1,..., T6 del convertidor polifásico con acumuladores de energía 9 distribuidos, como se explica a modo de ejemplo. Con este procedimiento de control, del modo antes descrito, se generan también tensiones de salida U<sub>L1N</sub>, U<sub>L2N</sub> y U<sub>L3N</sub> cuando fallan varios subsistemas 10 de un ramal de válvula T1, así como T2, así como T3, así como T4, así como T5, así como T6. Debe tomarse en cuenta que la cantidad restante de subsistemas 10 de un ramal de válvula T1,..., T6 no llega a ser menos que tres, para que los armónicos en las tensiones de salida U<sub>L1N</sub>, U<sub>L2N</sub> y U<sub>L3N</sub> se mantengan reducidos, conforme a la amplitud.

Este procedimiento de control según la invención tiene un efecto especialmente ventajoso en el caso de convertidores polifásicos con acumuladores de energía 9 distribuidos para redes de suministro de energía. A los convertidores de esa clase pertenecen convertidores para acoplamientos de red, para la compensación de potencia reactiva y para la estabilización de tensión en redes de suministro de energía. Debido a la tensión elevada en redes de suministro de energía usuales, un convertidor polifásico con acumuladores de energía distribuidos 9 presenta una cantidad elevada, por ejemplo de dos hasta más de cien, de subsistemas 10 por ramal de válvula T1,..., T6.

#### REIVINDICACIONES

1. Procedimiento para controlar un convertidor con al menos dos módulos de fase (100) que presentan un ramal de válvula superior e inferior (T1,..., T6) que presentan respectivamente al menos tres subsistemas bipolares (10) conectados en serie en el caso de la avería de al menos un subsistema (10) de un ramal de válvula (T1,..., T6), donde se determina el ramal de válvula (T1,..., T6) con el subsistema (10) averiado, donde respectivamente un subsistema (10) de un ramal de válvula (T1,..., T6) correspondiente al ramal de válvula (T1,..., T6) averiado, de cada módulo de fase (100) no averiado, se activa de modo que su tensión en bornes (Ux21) es respectivamente cero, donde un subsistema (10) de un ramal de válvula (T1,..., T6) correspondiente al ramal de válvula (T1,..., T6) averiado, del módulo de fase (100) averiado, se activa de modo que su tensión en bornes (Ux21) es igual a una tensión del condensador (Uc) del subsistema (10), y porque respectivamente un subsistema (10) de un ramal de válvula (T1,..., T6), de cada módulo de fase (100) no averiado, se activa de modo que su tensión del condensador (Uc) de ese subsistema (10).

5

10

2. Procedimiento de control según la reivindicación 1, donde los tiempos de conmutación (t<sub>1</sub>,..., t<sub>11</sub>) de las señales de control de los subsistemas (10) de los ramales de válvula (T1,..., T6) de los módulos de fase (100) del circuito de convertidor están temporalmente desplazados.

FIG 4

FIG 5

FIG 6

FIG 7

# FIG 9

FIG 10

FIG 11

FIG 12

FIG 13