# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 706 477

61 Int. Cl.:

H03K 3/037 (2006.01) H03K 3/356 (2006.01) H03K 3/012 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 14.03.2014 PCT/US2014/029721

(87) Fecha y número de publicación internacional: 18.09.2014 WO14145066

(96) Fecha de presentación y número de la solicitud europea: 14.03.2014 E 14723581 (6)

(97) Fecha y número de publicación de la concesión europea: 21.11.2018 EP 2974018

(54) Título: Arquitecturas de baja potencia

(30) Prioridad:

15.03.2013 US 201361800116 P

Fecha de publicación y mención en BOPI de la traducción de la patente: 29.03.2019

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121, US

(72) Inventor/es:

**BRUNOLLI, MICHAEL, JOSEPH**

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

### **DESCRIPCIÓN**

Arquitecturas de baja potencia

#### 5 SOLICITUD RELACIONADA

[0001] Esta solicitud reivindica prioridad según 35 USC § 119(e) a la Solicitud Provisional de Estados Unidos n.º 61/800 116, presentada el 15 de marzo de 2013.

#### 10 ANTECEDENTES

#### Campo

15

35

50

55

60

65

[0002] Los aspectos de la presente divulgación se refieren en general a dispositivos de baja potencia, y más particularmente a dispositivos de baja potencia en los que los transistores se hacen funcionar cerca o en la región subumbral para reducir el consumo de energía.

#### **Antecedentes**

- [0003] Los transistores en un dispositivo pueden hacerse funcionar cerca o en la región subumbral para reducir sustancialmente el consumo de energía del dispositivo. Por ejemplo, el funcionamiento subumbral permite minimizar el consumo de energía por ciclo.

- [0004] El documento IK Joon Chang et al.: "Robust Level Converter for Sub-Threshold/Super-Threshold Operation:

100mV to 2.5V [Convertidor de nivel robusto para funcionamiento subumbral/superumbral: 100 mV a 2,5 V]" se refiere

a un convertidor de nivel basado en un estilo de lógica dinámica para una parte de E/S subumbral, que tiene un amplio

rango dinámico de conversión. Para el convertidor de nivel, la señal de reloj de voltaje alto debe enviarse a través de

una ruta de reloj separada de la lógica del núcleo, lo cual ocasiona un problema de sincronización de reloj entre los

relojes de voltaje alto y voltaje bajo. Un chip de prueba se fabrica en tecnología CMOS de 130 nm para verificar la

técnica propuesta. Los resultados de las mediciones de hardware muestran que el convertidor de nivel convierte con

éxito el pulso de 0,3 V 8 MHz a la señal de 2,5 V.

- [0005] El documento Havard Pedersen Alstad et al.: "Seven subthreshold flip-flop cells [Siete células flip-flop subumbral]" se refiere a un estudio comparativo del rendimiento de siete células D-flip-flop que funcionan en la región subumbral, basándose en simulaciones en tecnología CMOS a90 nm. Las simulaciones se han realizado con un voltaje de alimentación de 150 mV a 350 mV. Los mejores números de PDP y EDP a 175 mV son 13 aJ y 10 yJs, respectivamente.

- [0006] El documento US 5 568 429 A se refiere al bloqueo de datos con una pérdida reducida de la señal de datos que incluye un circuito de bloqueo y un circuito de memoria intermedia de reloj que proporciona una señal de reloj diferencial a la puerta de transmisión de entrada del circuito de bloqueo. El circuito de la memoria intermedia del reloj está polarizado entre los potenciales de voltaje de alimentación superior e inferior, que son más altos y más bajos, respectivamente, que aquellos entre los cuales el circuito de bloqueo está polarizado.

#### 45 **SUMARIO**

**[0007]** De acuerdo con la presente invención, se proporciona un dispositivo, como se expone en la reivindicación 1, y un procedimiento, como se expone en la reivindicación 9. Modos de realización adicionales de la invención se reivindican en las reivindicaciones dependientes.

[0008] A continuación se ofrece un sumario simplificado de uno o más modos de realización con el fin de proporcionar un entendimiento básico de dichos modos de realización. Este resumen no es una visión general extensiva de todos los modos de realización contemplados y no está previsto para identificar ni elementos clave ni críticos de todos los modos de realización ni delimitar el alcance de algunos o de todos los modos de realización. Su único propósito es presentar algunos conceptos de uno o más modos de realización de una forma simplificada como preludio a la descripción más detallada que se presenta más adelante.

[0009] De acuerdo con un aspecto, se describe un dispositivo de baja potencia en el presente documento. El dispositivo de baja potencia comprende una ruta de reloj para propagar una señal de reloj, en el que la ruta de reloj incluye una pluralidad de transistores, y una fuente de reloj configurada para generar la señal de reloj, teniendo la señal de reloj un estado alto correspondiente a un voltaje alto por encima de los voltajes umbral de los transistores en la ruta de reloj. El dispositivo de baja potencia también comprende una ruta de datos para propagar una señal de datos, en el que la ruta de datos incluye una pluralidad de transistores, y una fuente de datos configurada para generar la señal de datos, teniendo la señal de datos un estado alto correspondiente a un voltaje bajo que está por debajo de los voltajes umbral de los transistores en la ruta de datos. El dispositivo comprende además un flop configurado para

recibir la señal de reloj desde la ruta de reloj, para recibir la señal de datos desde la ruta de datos, y para bloquear la señal de datos utilizando la señal de reloj.

[0010] Un segundo aspecto se refiere a un procedimiento para el funcionamiento de baja potencia. El procedimiento comprende enviar una señal de reloj a un flop a través de una ruta de reloj que comprende una pluralidad de transistores, en el que la señal de reloj tiene un estado alto correspondiente a un voltaje alto que está por encima de los voltajes umbral de los transistores en la ruta de reloj. El procedimiento también comprende enviar una señal de datos al flop a través de una ruta de datos que comprende una pluralidad de transistores, en el que la señal de datos tiene un estado alto correspondiente a un voltaje bajo que está por debajo de los voltajes umbral de los transistores en la ruta de datos. El procedimiento comprende además bloquear la señal de datos en el flop usando la señal de reloj.

[0011] Un tercer aspecto se refiere a un dispositivo para el ajuste de un voltaje. El dispositivo comprende una ruta de datos para propagar una señal de datos, un primer flop configurado para recibir la señal de datos de la ruta de datos, para recibir una señal de reloj y para bloquear la señal de datos utilizando la señal de reloj, y un segundo flop configurado para recibir la señal de datos de la ruta de datos, para recibir una versión retardada de la señal de reloj, y para bloquear la señal de datos utilizando la versión retardada de la señal de reloj. El dispositivo también comprende un circuito configurado para detectar una falta de coincidencia entre las salidas del primer y segundo flops, y un ajustador de voltaje configurado para ajustar el voltaje basándose en la falta de coincidencia detectada.

[0012] Un cuarto aspecto se refiere a un procedimiento para el ajuste de un voltaje. El procedimiento comprende enviar una señal de datos a los primeros y segundos flops a través de una ruta de datos, bloquear la señal de datos en el primer flop usando una señal de reloj y bloquear la señal de datos en el segundo flop usando una versión retardada de la señal de reloj. El procedimiento también comprende detectar una falta de coincidencia entre las salidas del primer y segundo flops y ajustar el voltaje en basándose en la falta de coincidencia detectada.

[0013] Para el cumplimiento de los objetivos anteriores y relativos, el uno o más modos de realización comprenden las características descritas con detalle de aquí en adelante y expuestas particularmente en las reivindicaciones. La descripción siguiente y los dibujos adjuntos exponen con detalle ciertos aspectos ilustrativos de los uno o más modos de realización. Sin embargo, estos aspectos son indicativos de apenas algunas de las diversas maneras en las que pueden emplearse los principios de diversos modos de realización, y los modos de realización descritos están concebidos para incluir todos dichos aspectos y sus equivalentes.

#### **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

### [0014]

5

10

15

20

25

30

35

50

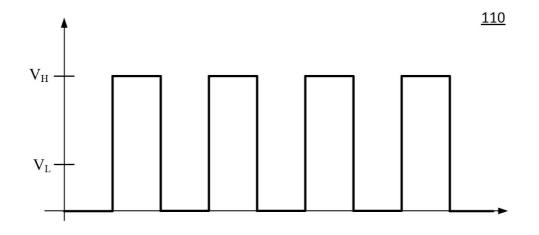

- La FIG. 1A muestra una señal de reloj de voltaje alto de acuerdo con un ejemplo de la presente divulgación.

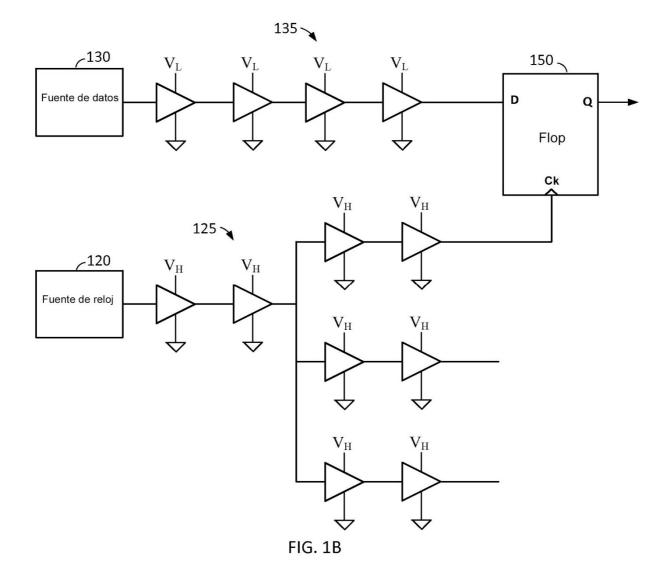

- 40 La FIG. 1B muestra un árbol de reloj de acuerdo con un ejemplo de la presente divulgación.

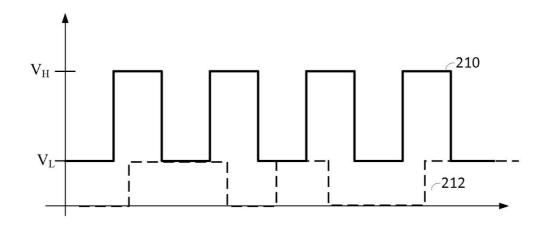

- La FIG. 2A muestra una señal de reloj de voltaje alto de acuerdo con un modo de realización de la presente divulgación.

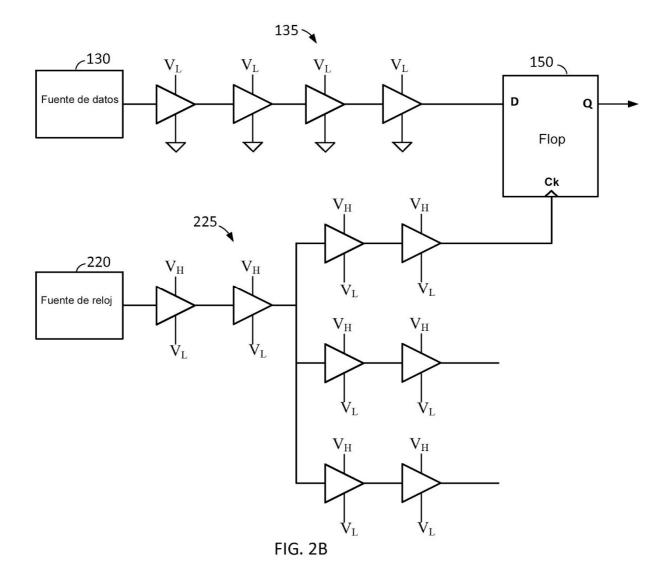

- 45 La FIG. 2B muestra un árbol de reloj de acuerdo con un modo de realización de la presente divulgación.

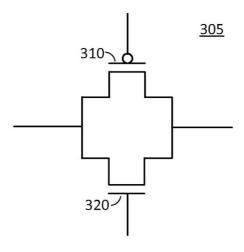

- La FIG. 3 muestra un ejemplo de una puerta de transferencia CMOS.

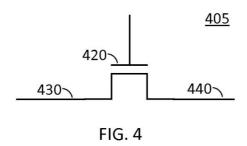

- La FIG. 4 muestra un ejemplo de una puerta de transferencia de un único NFET.

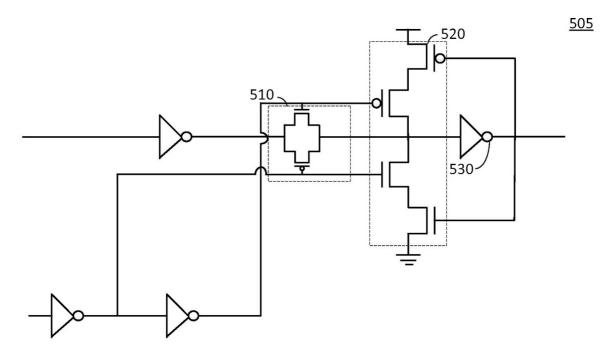

- La FIG. 5 muestra un ejemplo de un flop con una puerta de transferencia CMOS.

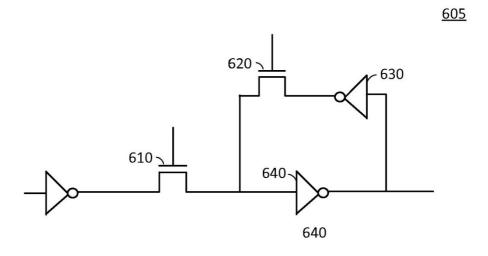

- La FIG. 6 muestra un ejemplo de un flop con una puerta de transferencia de un único NFET.

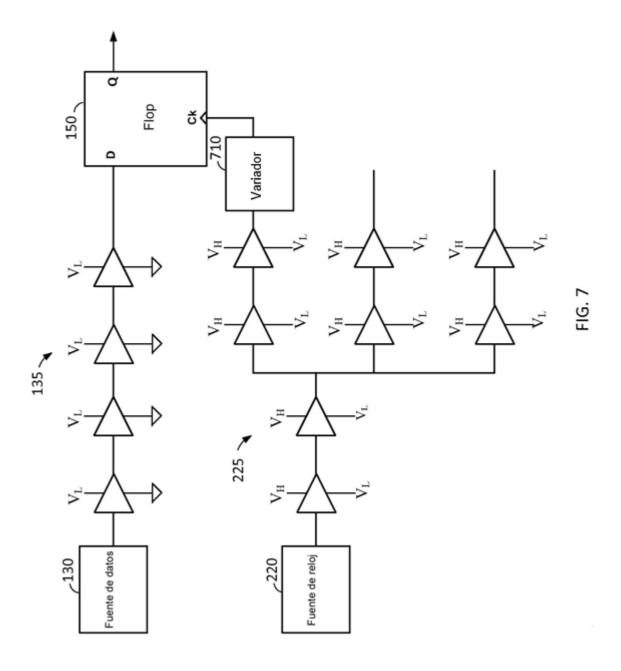

- La FIG. 7 muestra un ejemplo de un árbol de reloj con un variador de voltaje en un extremo del árbol de reloj de acuerdo con un modo de realización de la presente divulgación.

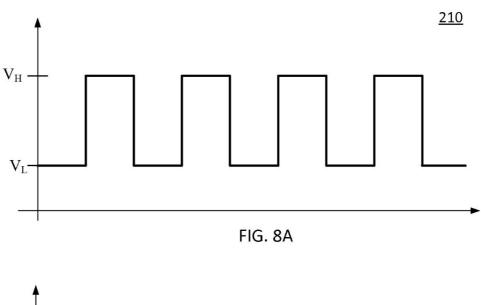

- La FIG. 8A muestra un ejemplo de una entrada de señal de reloj al variador de acuerdo con un modo de realización de la presente divulgación.

- La FIG. 8B muestra un ejemplo de una salida de señal de reloj variada a partir de la variación de acuerdo con un modo de realización de la presente divulgación.

- La FIG. 9 muestra una implementación a modo de ejemplo del variador de acuerdo con un modo de realización de la presente divulgación.

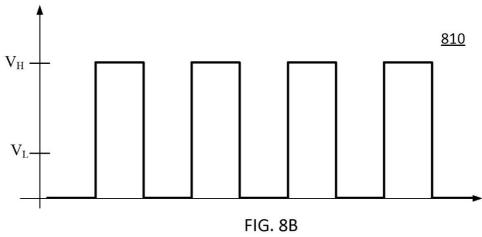

La FIG. 10 muestra un ejemplo de un regulador de desconexión (LDO).

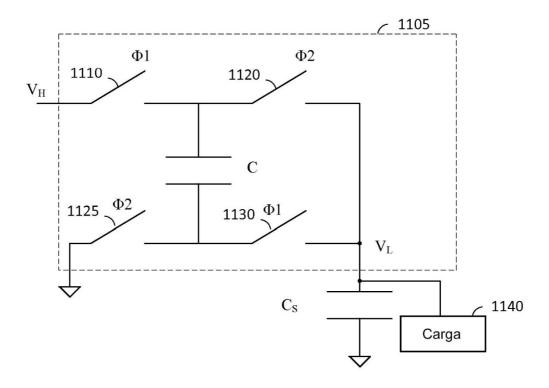

La FIG. 11 muestra un convertidor de CC a CC de condensador conmutado de acuerdo con un modo de realización de la presente divulgación.

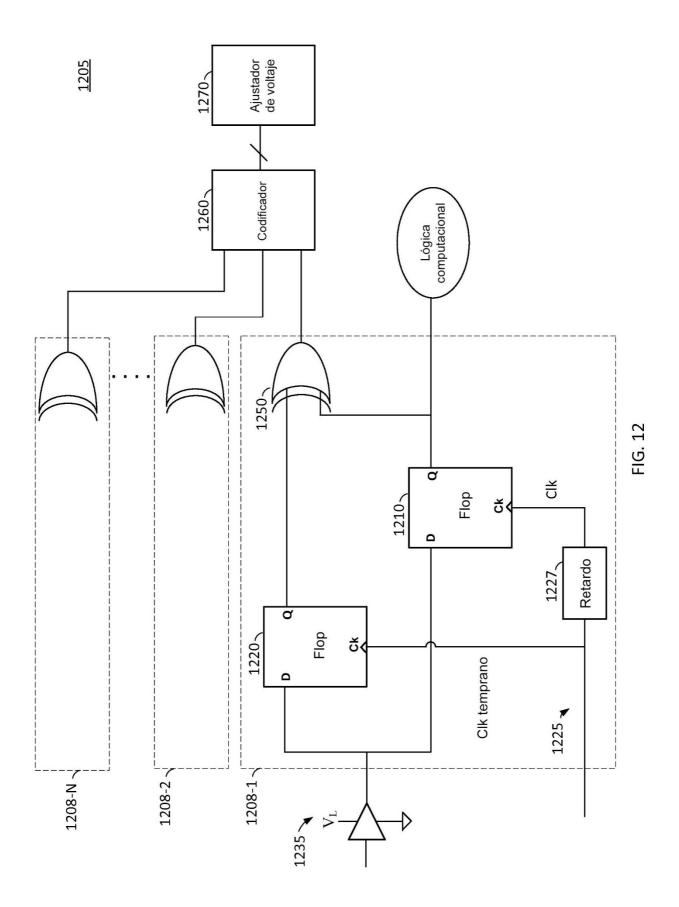

La FIG. 12 muestra un circuito de sintonización para ajustar un voltaje de alimentación de baja potencia de acuerdo con un ejemplo de la presente divulgación.

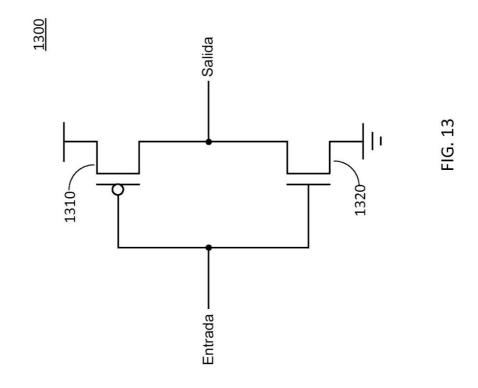

La FIG. 13 muestra una implementación a modo de ejemplo de un inversor.

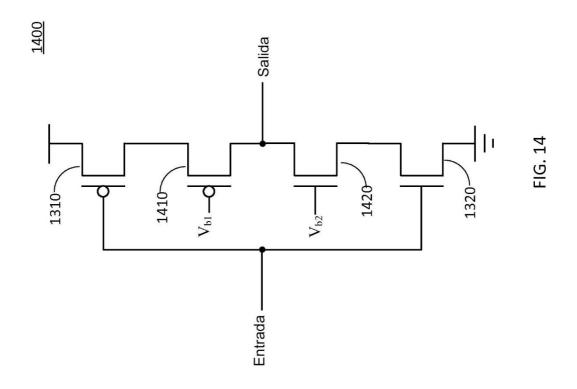

La FIG. 14 muestra otra implementación a modo de ejemplo de un inversor.

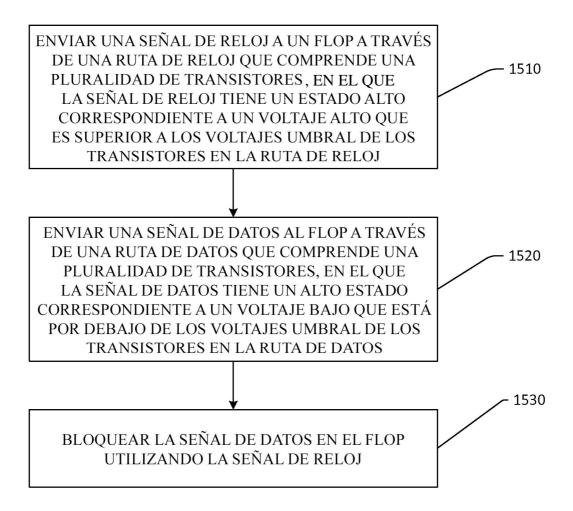

La FIG. 15 es un diagrama de flujo que ilustra un procedimiento 1500 para funcionamiento de baja potencia, de acuerdo con un modo de realización de la presente divulgación.

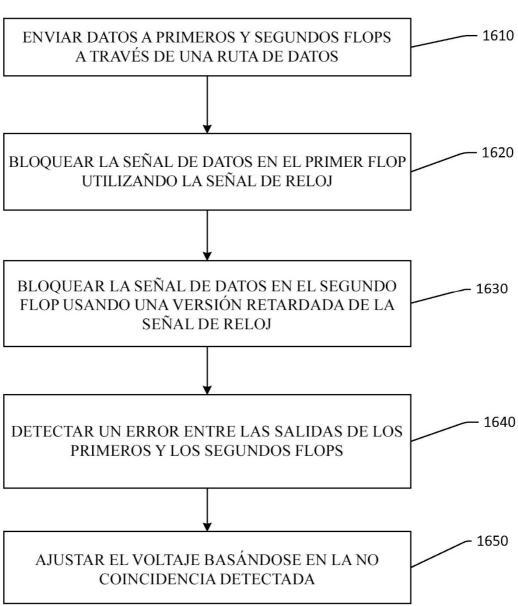

La FIG. 16 es un diagrama de flujo que ilustra un procedimiento 1600 para sintonizar un voltaje, de acuerdo con un ejemplo de la presente divulgación.

#### **DESCRIPCIÓN DETALLADA**

5

10

15

20

25

30

35

40

45

50

55

60

65

[0015] La descripción detallada expuesta a continuación en relación con los dibujos adjuntos está concebida como una descripción de diversas configuraciones y no está concebida para representar las únicas configuraciones en las cuales pueden llevarse a la práctica los conceptos descritos en el presente documento. La descripción detallada incluye detalles específicos con el propósito de proporcionar un entendimiento exhaustivo de los diversos conceptos. Sin embargo, resultará evidente para los expertos en la materia que estos conceptos pueden llevarse a la práctica sin estos detalles específicos. En algunos ejemplos, se muestran estructuras y componentes bien conocidos en forma de diagrama de bloques para evitar oscurecer dichos conceptos.

[0016] En un sistema, una señal de reloj puede generarse en una fuente de reloj y distribuirse a diferentes dispositivos (por ejemplo, flops) en el sistema a través de un árbol de reloj. El árbol del reloj puede ramificarse en una pluralidad de rutas de reloj para distribuir la señal de reloj a los diferentes dispositivos. El árbol del reloj puede incluir una o más memorias intermedias (por ejemplo, inversores) a lo largo de cada ruta de reloj.

[0017] Una señal de datos puede ser lanzada desde una fuente de datos en el sistema y propagarse por una ruta de datos hasta un dispositivo (por ejemplo, flop) en el sistema. El sistema puede incluir una o más memorias intermedias (por ejemplo, inversores) y/u otros tipos de lógica a lo largo de la ruta de datos. Para el ejemplo de un flop, el flop puede recibir la señal de datos de la ruta de datos y la señal de reloj del árbol del reloj. El flop puede usar la señal de reloj para sincronizar el tiempo de la señal de datos en el flop. Por ejemplo, el flop puede bloquear un valor lógico de la señal de datos en cada flanco ascendente o descendente de la señal de reloj. Para que el flop bloquee correctamente un valor lógico de la señal de datos, el valor lógico debe ser estable (no cambiar) durante un período de tiempo después de un flanco ascendente o descendente del reloj (denominado tiempo de espera). Si no se cumple esta condición de tiempo, se produce una infracción de bloqueo, lo cual puede hacer que el flop entre en un estado metaestable. En los sistemas convencionales, los retardos de propagación en el árbol del reloj y la ruta de los datos se ajustan (por ejemplo, utilizando memorias intermedias) para garantizar que se cumple esta condición de temporización.

[0018] Sin embargo, el control de la temporización de los datos y los retardos de propagación de reloj es muy difícil para los sistemas en los que los transistores se hacen funcionar a propósito en la región subumbral (es decir, sistemas en los que una puerta de voltaje máxima proporcionada a un transistor con la intención de activar el transistor es menor que el voltaje umbral del transistor). Esto se debe a que, cuando un transistor funcionar en la región subumbral, la corriente del transistor está relacionada exponencialmente con el voltaje de la puerta, lo cual hace que la corriente del transistor sea exponencialmente sensible al voltaje umbral (Vt) del transistor y/o voltaje de alimentación. Por lo tanto, incluso pequeñas variaciones en los voltajes umbral y/o voltajes de suministro entre los transistores que funcionar en la región subumbral pueden conducir a grandes variaciones en sus corrientes. Esto, a su vez, conduce a grandes variaciones en los retardos entre memorias intermedias y/u otra lógica implementada con los transistores, y por lo tanto a grandes variaciones en los retardos de propagación en el árbol del reloj y las rutas de datos. La gran variación en los retardos de propagación hace que sea muy difícil controlar la temporización de la señal de reloj en relación con una señal de datos en un flop para satisfacer la condición de espera. Por ejemplo, dos rutas con el mismo número de memorias intermedias pueden tener retardos drásticamente diferentes debido a las variaciones de voltaje Vt y/o de alimentación.

[0019] Los modos de realización de la presente divulgación abordan el problema anterior usando una señal de reloj de voltaje alto, mientras que todavía usan una señal de datos de voltaje bajo para reducir el consumo de energía (por ejemplo, una señal de datos que tiene un estado alto correspondiente a un voltaje subumbral). En este sentido, la FIG. 1A muestra un diagrama de voltaje-tiempo de una señal de reloj de voltaje alto 110 de acuerdo con un ejemplo. El voltaje de la señal de reloj de voltaje alto 110 puede oscilar entre un voltaje alto (V<sub>H</sub>) y tierra, donde V<sub>H</sub> puede ser

mayor que los voltajes umbral de los transistores en el árbol del reloj. Por ejemplo, V<sub>H</sub> puede estar varios cientos de milivoltios por encima de los voltajes umbral y puede ser el voltaje de una batería utilizada para alimentar un dispositivo portátil en el que se usa la señal de reloj de voltaje alto 110.

- [0020] La FIG. 1B muestra un ejemplo de una fuente de reloj 120 y un árbol de reloj 125 correspondientes. La fuente de reloj 120 genera la señal de reloj de voltaje alto 110, que se distribuye a los dispositivos a través del árbol del reloj 125. El árbol del reloj 125 puede incluir memorias intermedias alimentadas por V<sub>H</sub>, que pueden estar por encima de los voltajes umbral de los transistores en los memorias intermedias. Cuando V<sub>H</sub> está por encima de los voltajes umbral de los transistores en el árbol del reloj 125, estos transistores funcionan en la región de fuerte inversión y, por lo tanto, son mucho más rápidos que los transistores que funcionan en la región subumbral. Como resultado, el retardo de propagación de la señal de reloj de voltaje alto 110 es mucho más corto que el retardo de propagación de una señal de datos, como se analiza más adelante.

- [0021] La FIG. 1B también muestra un ejemplo de una fuente de datos 130 y una ruta de datos 135. La fuente de datos 130 lanza una señal de datos. El voltaje de la señal de datos puede tener un cambio entre un voltaje bajo (V<sub>L</sub>) y tierra, donde V<sub>L</sub> es aproximadamente igual o inferior a los voltajes umbral de los transistores en la ruta de datos 135. Por ejemplo, V<sub>L</sub> puede ser de aproximadamente 300 mV. La FIG. 1A muestra un ejemplo de V<sub>L</sub> en relación con V<sub>H</sub>. La ruta de datos 135 puede incluir una pluralidad de memorias intermedias, lógica computacional y/u otros tipos de dispositivos lógicos que son alimentados por V<sub>L</sub>. Esto hace que los transistores en la ruta de datos 135 funcionen en la región subumbral y, por lo tanto, sean mucho más lentos que los transistores en el árbol del reloj 125, que pueden funcionar en la región de inversión fuerte. Como resultado, el retardo de propagación de la señal de reloj de voltaje alto es mucho más corto que el retardo de propagación de la señal de datos.

- [0022] Debido a que los transistores en la ruta de datos 135 funcionan en la región subumbral, el retardo de propagación de la señal de datos puede variar en un amplio intervalo dependiendo de los voltajes umbral de los transistores y/u otros factores. Sin embargo, el retardo de propagación de la señal de reloj de voltaje alto es mucho más corto que incluso el retardo de propagación más corto dentro de este rango. Por lo tanto, cuando la señal de reloj de voltaje alto y la señal de datos se introducen en un flop 150 (un ejemplo de lo cual se muestra en la FIG. 1B), la señal de reloj de voltaje alto está prácticamente garantizada para propagarse al flop 150 por delante de la señal de datos por al menos el tiempo de espera. Por lo tanto, la señal de reloj de voltaje alto evita infracciones de bloqueo.

25

30

35

40

45

- [0023] La FIG. 2A muestra un diagrama de voltaje-tiempo de una señal de reloj de voltaje alto 210 de acuerdo con un modo de realización. El voltaje de la señal de reloj de voltaje alto 210 puede oscilar entre V<sub>H</sub> y V<sub>L</sub>. Como se analiza más adelante, esto permite que la carga del árbol del reloj se descargue en una alimentación de baja potencia que se utiliza para alimentar la lógica que funciona en la región subumbral. La diferencia de voltaje V<sub>H</sub> V<sub>L</sub> puede estar en o por encima de los voltajes umbral de los transistores en el árbol del reloj. La FIG. 2A también muestra un ejemplo de una señal de datos 212 que tiene una oscilación de voltaje entre V<sub>L</sub> y tierra, donde entre V<sub>L</sub> puede corresponder a uno lógico y tierra puede corresponder a un cero lógico. Debe apreciarse que las posiciones relativas de los límites de datos y los límites de reloj mostrados en la FIG. 2A son solo a modo de ejemplo y pueden variar (por ejemplo, dependiendo de los retardos de propagación relativos).

- [0024] La FIG. 2B muestra un ejemplo de una fuente de reloj 220 y un árbol de reloj 225 correspondientes. La fuente de reloj 220 genera la señal de reloj de voltaje alto 210, que se distribuye a los dispositivos a través del árbol del reloj 225. El árbol del reloj 125 puede incluir memorias intermedias que se alimentan entre V<sub>H</sub> y V<sub>L</sub>, como se muestra en la FIG. 2B. Debido a que la diferencia de voltaje V<sub>H</sub> V<sub>L</sub> está en o por encima de los voltajes umbral de los transistores en el árbol del reloj 225, estos transistores son mucho más rápidos que los transistores que funcionan en la región del subumbral. Como resultado, el retardo de propagación de la señal de reloj de voltaje alto 210 es mucho más corto que el retardo de propagación de la señal de datos en la ruta de datos 135, evitando así infracciones de bloqueo.

- [0025] La frecuencia de reloj de la señal de reloj de voltaje alto de 110/210 también se puede ajustar para evitar infracciones de configuración. Se puede producir una infracción de la configuración cuando la señal de datos no se propaga a un flop lo suficientemente rápido como para que la señal de datos se establezca en un valor estable en el flop antes de un límite del reloj en el que el flop se registra en la señal de datos. Cuando esto ocurre, la frecuencia de reloj puede reducirse para proporcionar a la señal de datos más tiempo para establecerse antes del límite del reloj.

Las transiciones del límite del reloj se comparan muy rápidamente con los datos porque la pendiente de transición del límite del reloj está determinada por V<sub>H</sub> y no V<sub>L</sub>.

- [0026] El funcionamiento de los datos y/o la lógica utilizando V<sub>L</sub> reduce sustancialmente el consumo de energía en comparación con V<sub>H</sub>. Esto amplía sustancialmente la vida útil de la batería de dispositivos de muy baja potencia, como dispositivos médicos alimentados por batería, dispositivos de rastreo y dispositivos "siempre activados" que pueden estar activados siempre durante un período prolongado de tiempo (por ejemplo, años) y que aun así funcionan con una batería debido al bajo consumo de energía del dispositivo.

- [0027] La señal de reloj de voltaje alto 110/210 se puede utilizar para reducir el número de puertas (número de transistores) en un flop mediante la sustitución de al menos una puerta de transferencia CMOS en el flop con un único NFET. En este sentido, la FIG. 3 muestra un ejemplo de una puerta de transferencia CMOS 305 que se usa

comúnmente en los flops para transferir un valor lógico de una señal de datos dentro del flop. La puerta de transferencia CMOS comprende un PFET 310 y un NFET 320 acoplados en paralelo. Las puertas del PFET 310 y del NFET 320 están controladas por señales complementarias. Por ejemplo, la puerta del NFET 320 puede ser activada por una señal de reloj y la puerta del PFET 310 puede ser activada por una inversa de la señal de reloj, o viceversa. El PFET 310 se utiliza para transferir un valor lógico alto, mientras que el NFET 320 se utiliza para transferir un valor lógico bajo.

5

10

25

30

35

40

45

50

55

60

65

[0028] La FIG. 4 muestra un ejemplo de una puerta de transferencia 405 que comprende un único NFET 420 sin PEFT. El único NFET 420 puede no ser capaz de transferir un valor lógico alto cuando el estado alto de la señal de reloj que maneja la puerta del NFET 420 corresponde aproximadamente al mismo voltaje que el valor lógico alto. Esto se debe a que el voltaje en la puerta del NFET 420 se reduce el voltaje de la puerta a la fuente del NFET 420 (por ejemplo, aproximadamente Vt cuando se activa el NFET 420) en la salida 440 de la puerta de transferencia 420. Si el valor lógico alto corresponde a un voltaje por debajo de Vt, entonces el voltaje en la salida 440 puede reducirse a cero.

[0029] La señal de reloj de voltaje alto 110/210 de acuerdo con modos de realización de la presente divulgación permite que el único NFET 420 transfiera un valor lógico alto. Esto se debe a que el estado alto de la señal de reloj de voltaje alto 110/210 corresponde a un voltaje mayor (V<sub>H</sub>) que el valor lógico alto de la señal de datos (V<sub>L</sub>). Como resultado, incluso cuando el voltaje (V<sub>H</sub>) en la puerta del NFET 420 se reduce por voltaje de puerta a fuente del NFET 420 en la salida 440, el voltaje en la salida 440 aún puede ser aproximadamente V<sub>L</sub>. Esto supone que la diferencia de voltaje V<sub>H</sub> - V<sub>L</sub> es lo suficientemente grande (por ejemplo, al menos tan grande como el voltaje umbral Vt de NFET 420) para absorber el voltaje de puerta a fuente del NFET 420 cuando el NFET 420 está activado.

[0030] A este respecto, las FIGs. 5 y 6 ilustran un ejemplo de reducción de recuento de puerta utilizando la señal de reloj de voltaje alto 110/210 de acuerdo con modos de realización de la presente divulgación. La FIG. 5 muestra un ejemplo de un flip-flop 505 que comprende una puerta de transferencia CMOS 510, un inversor de triple estado 520 y un inversor 530. El inversor de triple estado 520 y el inversor 530 forman un bloqueo conmutable, y la puerta de transferencia CMOS 510 se utiliza para transferir valores de datos lógicos al bloqueo.

[0031] La FIG. 6 muestra un ejemplo de un flop-flip 605, en el que la puerta de transferencia CMOS 510 se reemplaza por una primera puerta de transferencia de un único NFET 610, y el inversor de triple estado 520 se reemplaza por una segunda puerta de transferencia de un único NFET 620 y un inversor 630. Esto reduce el recuento de puertas del flip-flop 605 en al menos dos en comparación con el flip-flop 505 en la FIG. 5. Los inversores continuos 630 y 640 forman un bloqueo que se conmuta mediante la segunda puerta de transferencia de un único NFET 620. En este ejemplo, la señal de datos puede tener una oscilación de voltaje entre V<sub>L</sub> y tierra para reducir el consumo de energía, como se analizó anteriormente. Uno o más de los inversores en el flip-flop 605 pueden ser alimentados por V<sub>L</sub> para hacer funcionar los transistores correspondientes en la región del subumbral para conservar la energía. Las puertas de transferencia de un único NFET 610 y 620 están sincronizadas por la señal de reloj de voltaje alto o su inversa. Como se analizó anteriormente, la señal de reloj de voltaje alto permite el uso de puertas de transferencia de un único NFET para reducir el recuento de puertas.

[0032] El recuento de puertas en un multiplexor de escaneo también se puede reducir. Un multiplexor de escaneo convencional incluye PFET y NFET para cambiar el multiplexor entre una ruta de escaneo para probar la funcionalidad de uno o más flops y una ruta de datos para el funcionamiento normal. Dado que los datos funcionan en  $V_L$ , el recuento de la puerta del multiplexor puede reducirse reemplazando un par de PFET y NFET en el multiplexor con un único NFET y acoplando una puerta de un único NFET a  $V_H$  o tierra, dependiendo de si el único NFET se activa o desactiva. En el funcionamiento normal, el único NFET se activa o desactiva siempre, ya que el multiplexor siempre se cambia a la ruta de datos en el funcionamiento normal. Por lo tanto, el único NFET no consume energía dinámica asociada con el cambio del NFET, y la puerta del NFET puede estar cableada a  $V_H$  o tierra.

[0033] Como se analizó anteriormente (por ejemplo, con relación a las Figs. 2A y 2B), el voltaje de la señal de reloj de voltaje alto 210 puede oscilar entre V<sub>H</sub> y V<sub>L</sub>. Por lo tanto, la señal de reloj de voltaje alto 210 tiene un estado bajo correspondiente a un voltaje de V<sub>L</sub>. En algunas aplicaciones, es posible que V<sub>L</sub> no sea lo suficientemente bajo como para desactivar completamente una puerta de transferencia, lo cual da como resultado una corriente de fuga que puede ser demasiado alta. Por consiguiente, en un modo de realización, se puede colocar un variador de voltaje en un extremo del árbol del reloj antes de que la señal de reloj de voltaje alto 210 se introduzca al dispositivo correspondiente (por ejemplo, un flop). La FIG. 7 muestra un ejemplo de un variador de voltaje 710 al final del árbol de reloj 225 correspondiente al flop 150. El variador 710 varía la señal de reloj de voltaje alto 210 a una señal de reloj de voltaje alto variada que tiene un voltaje de estado bajo más bajo. La FIG. 8A muestra un ejemplo de la señal de reloj de voltaje alto 210, que tiene una oscilación de voltaje entre V<sub>H</sub> y V<sub>L</sub>. La FIG. 8B muestra la salida de la señal de reloj de voltaje alto variada 810 del variador de voltaje 810. La señal de reloj de voltaje alto variada 810 puede estar ligeramente retardada en comparación con la señal de reloj de voltaje alto 210 debido a retardos internos en el variador 710. En este ejemplo, la señal de reloj de voltaje alto variada 810 tiene una oscilación de voltaje entre V<sub>H</sub> y tierra (oscilación de voltaje completa). La señal de reloj de voltaje alto variada 810 se introduce en el flop 150, de modo que la lógica en el flop se sincroniza utilizando la señal de reloj variada. Por ejemplo, la señal de reloj variada 810 se puede usar para sincronizar las puertas de transferencia, en la que el voltaje de estado bajo más bajo de la señal de reloj variada 810 reduce la corriente de fuga de las puertas de transferencia en el estado desactivado.

[0034] La FIG. 9 muestra una implementación a modo de ejemplo de un variador de voltaje 910 de acuerdo con un modo de realización de la presente divulgación. El variador de voltaje 910 se puede usar para implementar el variador 710 que se muestra en la FIG. 7 para proporcionar una señal de reloj variada con una oscilación de voltaje completo. El variador 910 comprende un primer inversor 915, un segundo inversor 920, un primer PFET 925, un segundo PFET 930 y un primer NFET 935, y un segundo NFET 940. El primer y segundo inversores 915 y 920 están acoplados en serie y reciben alimentación entre V<sub>H</sub> y V<sub>L</sub>. Las fuentes del primer PFET 925 y el segundo PFET 930 están acopladas a V<sub>H</sub>, el drenaje del primer NFET 935 está acoplado al drenaje del primer PFET 925, el drenaje del segundo NFET 940 están acopladas a tierra. La puerta del segundo PFET 930, y las fuentes del primer NFET 935 y el segundo inversor 920 y la puerta del segundo PFET 930 es activada por la salida del segundo inversor 920 y la puerta del segundo PFET 930 es activada por la salida del primer inversor 915. La puerta del primer NFET 935 está acoplada en forma cruzada a los drenajes del segundo PFET 930 y el segundo NFET 940. La puerta del segundo NFET 940 está acoplada en forma cruzada a los drenajes del primer PFET 925 y el primer NFET 935. La salida del variador 950 se toma del nodo 945.

15

20

25

35

40

10

[0035] La señal de reloj de voltaje alto 210 puede introducirse en el primer inversor 915. Cuando la señal de reloj de entrada está en un estado alto, la puerta de la primera PFET 925 se activa alta con un voltaje de V<sub>H</sub> y la puerta de la segunda PFET 930 se activa baja con un voltaje de V<sub>L</sub>. Esto hace que el primer PFET 925 se desactive y el segundo PFET 930 se active (suponiendo que V<sub>H</sub> - V<sub>L</sub> es suficiente para activar el segundo PFET 930). Esto hace que el segundo PFET 930 aumente el voltaje en el nodo 945 a aproximadamente V<sub>H</sub>.

[0036] Cuando la señal de reloj de entrada está en un estado bajo, la puerta de la primera PFET 925 sea activa baja con un voltaje de V<sub>L</sub> y la puerta de la segunda PFET 930 se activa alta con un voltaje de V<sub>H</sub>. Esto hace que el primer PFET 925 se active y el segundo PFET 930 se desactive. Como resultado, el primer PFET 925 eleva el voltaje en el drenaje del primer PFET 925 a aproximadamente V<sub>H</sub>. Este voltaje está acoplado a la puerta del segundo NFET 940, que activa el segundo NFET 940. Esto hace que el segundo NFET 940 reduzca el voltaje en el nodo 945 aproximadamente a tierra.

[0037] Por lo tanto, la señal de reloj variada en la salida del variador 910 tiene aproximadamente una oscilación de voltaje máxima (entre V<sub>H</sub> y tierra). Se puede agregar un inversor adicional a la salida del variador 910 para invertir la señal de reloj variada. El inversor adicional puede recibir alimentación entre V<sub>H</sub> y tierra. Debe apreciarse que el circuito mostrado en la FIG. 9 es solo un ejemplo, y el variador puede implementarse utilizando otros diseños de circuitos.

[0038] El voltaje alto V<sub>L</sub> puede ser proporcionada por un regulador de desconexión (LDO). La FIG. 10 muestra un ejemplo de un LDO que comprende un amplificador 1010 y un FET 1020 (por ejemplo, PFET). Un voltaje de referencia Vref y el voltaje en el nodo 1025 se introducen en el amplificador 1010. Usando retroalimentación negativa, el amplificador 1010 activa la puerta del FET 1020 en una dirección que minimiza la diferencia entre Vref y el voltaje en el nodo 1025, y por lo tanto regula el voltaje en el nodo 1025 para que sea aproximadamente Vref. Vref se puede ajustar para proporcionar un deseado voltaje bajo V<sub>L</sub> (por ejemplo, utilizando una referencia de banda prohibida) para la lógica de funcionamiento en la región subumbral. Si bien el LDO puede ser adecuado para proporcionar una V<sub>L</sub> estable, el LDO puede ser ineficiente. Esto se debe a que la corriente para la carga 1030 de la lógica tiene que pasar a través del FET 1020. Esto crea una caída de IR a través del FET 1020 que disipa la potencia y, por lo tanto, desperdicia energía.

[0039] Por consiguiente, en algunos modos de realización, el voltaje bajo V<sub>L</sub> se proporciona mediante un convertidor de CC a CC de condensador conmutado. La FIG. 11 muestra un convertidor de CC a CC 1105 de acuerdo con un modo de realización de la presente divulgación. El convertidor 1105 comprende un primer interruptor 1110, un segundo interruptor 1120, un tercer interruptor 1125, un cuarto interruptor 1130 y un condensador C. El condensador C puede incluir capacidad del árbol de reloj. Por ejemplo, el condensador C puede incluir uno o más condensadores en el árbol del reloj. Esto permite que la carga utilizada para propagar la señal de reloj en el árbol del reloj se descargue a la alimentación de baja potencia para hacer funcionar la lógica en V<sub>L</sub>, lo cual brinda una mejor eficiencia energética.

[0040] En la FIG. 11, la fase Φ1 puede corresponder al estado alto de la señal de reloj y la fase Φ2 puede corresponder al estado bajo de la señal de reloj. En la fase Φ1, los interruptores primero y cuarto 1110 y 1130 están cerrados y los interruptores segundo y tercero 1120 y 1125 están abiertos. Como resultado, el condensador C se acopla a V<sub>H</sub>, y el terminal superior del condensador C se carga a V<sub>H</sub>. El voltaje a través del condensador C se carga a aproximadamente V<sub>H</sub> -V<sub>I</sub>

[0041] En la fase Φ2, el primer y cuarto conmutadores 1110 y 1130 están abiertos y el segundo y tercer conmutadores 1120 y 1125 están cerrados. Como resultado, el condensador C está acoplado entre la alimentación de baja potencia y tierra. Suponiendo que V<sub>H</sub>-V<sub>L</sub> > V<sub>L</sub>, esto hace que la carga del condensador C se descargue en un condensador de almacenamiento C<sub>S</sub> de la alimentación de baja potencia. La carga proporciona energía para la carga 1140 de la lógica que funciona a V<sub>L</sub>. La carga 1140 puede incluir la carga de lógica (por ejemplo, memorias intermedias) en una ruta de datos y/o la carga de lógica (por ejemplo, inversores) en un flop que se hace funcionar a V<sub>L</sub>.

65

[0042] Por lo tanto, el voltaje en el terminal de la parte superior del condensador C en el convertidor de CC-CC 1105 cambia entre aproximadamente V<sub>H</sub> y V<sub>L</sub>. Esto permite que el condensador C incluya condensadores del árbol del reloj, ya que los condensadores en el árbol del reloj también cambian entre V<sub>H</sub> y V<sub>L</sub> para propagar la señal de reloj de voltaje alto 210. Por lo tanto, la carga utilizada para propagar el reloj en el árbol del reloj puede reutilizarse para alimentar el suministro de voltaje bajo. Los condensadores en el árbol del reloj pueden incluir la capacidad del nodo de salida de cada inversor del árbol del reloj, donde cada inversor se utiliza como una memoria intermedia. Cada inversor puede cargar y descargar el nodo de salida respectivo entre V<sub>H</sub> y V<sub>L</sub> para propagar la señal de reloj. Cuando el nodo de salida se descarga a V<sub>L</sub>, la carga puede volcarse a la alimentación de baja potencia.

[0043] En algunos modos de realización, la capacidad del árbol de reloj puede estar efectivamente en paralelo con el condensador C. Para las verdaderas señales del reloj, los controladores PFET en el árbol de reloj pueden actuar como interruptor 1110 en fase Φ1, y en fase Φ2, los controladores NFET en el árbol del reloj pueden actuar como un interruptor 1120. Para las señales falsas del reloj, los interruptores pueden actuar efectivamente en las fases opuestas. La capacidad del árbol del reloj puede compartir la misma conexión superior que el condensador C, pero la placa inferior de la capacidad del árbol del reloj puede distribuirse entre V<sub>L</sub>, tierra y otras señales.

[0044] En el ejemplo anterior, cada inversor en el árbol de reloj puede implementarse utilizando un PFET y un NFET (un ejemplo del cual se muestra en la FIG. 13), en el que cada inversor activa el respectivo PFET para cargar la capacidad del árbol del reloj respectivo y activa el NFET respectivo para descargar la capacidad del árbol del reloj respectivo. Algunos o todos los controladores PFET descritos en el ejemplo anterior pueden corresponder a los PFET de los inversores, y algunos o todos los controladores NFET descritos en el ejemplo anterior pueden corresponder a los NFET de los inversores. Por lo tanto, el PFET de un inversor puede actuar como un interruptor que carga la capacidad respectiva (por ejemplo, a V<sub>H</sub>) y el NEFT de un inversor puede actuar como interruptor que descarga la capacidad respectiva (por ejemplo, a V<sub>L</sub>).

20

25

30

35

40

45

50

55

60

65

[0045] La capacidad del condensador C se puede ajustar de modo que la cantidad de carga descargada al condensador de almacenamiento C<sub>S</sub> de la baja potencia de alimentación por ciclo de reloj aproximadamente repone la cantidad de carga consumida por la carga 1140 por ciclo de reloj. Para hacer esto, el condensador C puede incluir un condensador variable (no mostrado) acoplado en paralelo con los condensadores del árbol del reloj. La capacidad del condensador variable se puede ajustar de modo que la cantidad de carga descargada al condensador de almacenamiento C<sub>S</sub> de la alimentación de baja potencia por ciclo de reloj reponga aproximadamente la cantidad de carga consumida por la carga 1140 por ciclo de reloj para mantener un voltaje bajo deseado. Si la capacidad del árbol de reloj no es capaz de proporcionar suficiente carga para la alimentación de baja potencia, entonces se pueden agregar uno o más condensadores adicionales al condensador C. Se debe apreciar que el convertidor de CC a CC que se muestra en la FIG. 11 es solo un ejemplo, y el convertidor de CC a CC se puede implementar utilizando otras configuraciones.

[0046] El funcionamiento de la ruta/lógica de datos en el voltaje subumbral ahorra una gran cantidad de energía en comparación con el funcionamiento por encima del voltaje umbral. Sin embargo, el cronometraje no es fiable como se analizó anteriormente. Los modos de realización de la presente divulgación usan un reloj de voltaje alto junto con una lógica/ruta de datos subumbral que resuelve los problemas de temporización descritos anteriormente. Sin embargo, correr el reloj a voltaje alto consume más energía. Parte de la energía adicional consumida por el reloj de voltaje alto se recupera como se ilustra en la FIG. 11 y como se ha analizado anteriormente y se utiliza para proporcionar el voltaje subumbral a la lógica/ruta de datos. El resultado es una solución muy eficiente desde el punto de vista energético sin los problemas de tiempo descritos anteriormente.

[0047] El consumo de energía puede reducirse mediante la reducción del voltaje de alimentación de baja potencia V<sub>L</sub>. Sin embargo, si V<sub>L</sub> se reduce demasiado, entonces el sistema deja de funcionar correctamente. Por ejemplo, para que un flop bloquee correctamente un valor lógico de una señal de datos, la señal de datos debe permanecer estable durante un período de tiempo antes de un límite de reloj utilizado por el flop para sincronizar la señal de datos (denominado tiempo de configuración). Sin embargo, a medida que V<sub>L</sub> se reduce, el retardo de propagación en la correspondiente ruta de datos aumenta. Esto es porque la velocidad de la lógica (por ejemplo, memorias intermedias) en la ruta de datos se ralentiza cuando se reduce V<sub>L</sub>. Finalmente, el retardo de propagación aumenta a un punto donde la señal de datos no se establece en un valor estable en el flop a tiempo para cumplir con la condición de tiempo de configuración. Como resultado, se produce una infracción de configuración y el flop puede entrar en un estado metaestable. Por lo tanto, el consumo de energía se puede minimizar reduciendo el voltaje de alimentación de baja potencia V<sub>L</sub> al voltaje mínimo que necesita el sistema para funcionar correctamente (el voltaje de trabajo más bajo).

[0048] La FIG. 12 muestra un circuito de sintonización de 1205, de acuerdo con un ejemplo, para sintonizar el voltaje de alimentación de baja potencia V<sub>L</sub> a un voltaje de cerca de o al voltaje mínimo necesario por un sistema para evitar infracciones de configuración a una frecuencia de reloj dada. El circuito de sintonización 1205 comprende una primera unidad de prueba 1208-1. La unidad de prueba 1208-1 comprende un flop normal 1210, un flop de prueba 1220 y una puerta XOR 1250. El flop normal 1210 es un flop que se utiliza para bloquear una señal de datos en el sistema y enviar los datos bloqueados a la lógica computacional en el sistema. El flop de prueba 1220 (flop de sombra) puede ser utilizado para aproximar el mínimo V<sub>L</sub> necesario por el flop normal de 1210 para evitar infracciones de configuración,

como se analiza más adelante. El flop de prueba 1220 y el flop normal 1210 pueden implementarse utilizando el mismo circuito, de modo que el flop de prueba 1220 imita el flop normal 1210.

[0049] El flop de prueba 1220 y el flop normal de 1210 están acoplados al extremo de la misma ruta de datos 1235. Como resultado, la temporización de la señal de datos en el flop de prueba 1220 y el flop normal 1210 es aproximadamente la misma. Las entradas de reloj del flop de prueba 1220 y el flop normal 1210 están acopladas a diferentes puntos a lo largo de una ruta de reloj 1225, en la que la señal de reloj en la ruta de reloj 1225 tiene que propagarse a través de un elemento de retardo 1227 antes de alcanzar el flop normal 1210 en comparación con el flop de prueba 1220. Como resultado, el flop de prueba 1220 recibe una versión anterior de la señal de reloj recibida por el flop normal 1210. La versión anterior de la señal de reloj está adelantada en una cantidad aproximadamente igual al retardo de tiempo del elemento de retardo 1227.

5

10

15

20

25

30

35

50

55

60

[0050] La salida del flop normal 1210 está acoplada a una primera entrada de la puerta XOR 1250 y la salida del flop de prueba 1220 está acoplada a una segunda entrada de la puerta XOR 1250. La salida del flop normal 1210 también está acoplada a la lógica computacional. La puerta XOR 1250 genera un cero lógico cuando las salidas del flop normal 1210 y el flop de prueba 1220 coinciden. Esto puede indicar que ambos flops 1210 y 1220 funcionan correctamente. La puerta XOR 1250 genera un cero lógico cuando las salidas del flop normal 1210 y el flop de prueba 1220 no coinciden. Esto puede indicar que se ha producido una infracción de configuración en el flop de prueba 1220, como se analiza más adelante.

[0051] Para determinar el mínimo V<sub>L</sub> en la que el flop normal de 1210 funciona correctamente, la salida de la puerta XOR 1250 puede supervisarse cuando V<sub>L</sub> se reduce. Inicialmente, la salida de la puerta XOR 1250 puede ser de cero lógico, lo cual indica que ambos flops 1210 y 1220 funcionan correctamente. A medida que se reduce V<sub>L</sub>, aumenta el retardo de propagación de la ruta de datos 1235. En cierto punto, las infracciones de configuración comenzarán a ocurrir en el flop de prueba 1220, pero no en el flop normal 1210. Esto se debe a que el flop de prueba 1220 sincroniza la señal de datos utilizando una versión anterior de la señal de reloj utilizada por el flop normal 1210. Por lo tanto, mientras que el flop de prueba 1220 puede comenzar a experimentar infracciones de configuración, el flop normal 1210 puede seguir funcionando correctamente. Sin embargo, esto puede indicar que el flop normal 1210 también comenzará a experimentar infracciones de configuración si V<sub>L</sub> se reduce más. Por lo tanto, el voltaje al que el flop de prueba 1220 comienza a experimentar infracciones de configuración se puede utilizar como una aproximación del voltaje de alimentación de baja potencia mínimo V<sub>L</sub> necesario por el flop normal de 1210 para evitar infracciones de configuración.

[0052] Cuando el flop prueba de 1220 comienza a experimentar infracciones de configuración, la salida del flop de prueba 1220 y el flop normal 1210 dejan de coincidir, y la puerta XOR 1250 emite un uno lógico. Por lo tanto, el voltaje al que la puerta XOR 1250 emite un uno lógico se puede utilizar como una aproximación del voltaje de alimentación de baja potencia mínimo V₁ necesario por el flop normal de 1210 para evitar infracciones de configuración.

[0053] Como se muestra en la FIG. 12, el circuito de sintonización 1205 puede incluir una pluralidad de unidades de prueba 1208-1 a 1208-N, en las que cada unidad de prueba comprende un flop de prueba emparejado con un flop normal en el sistema y una puerta XOR acoplada a las salidas del flop de prueba y el flop normal respectivos. Cada una de las unidades de prueba 1208-1 a 1208-N puede implementarse utilizando el circuito que se muestra en la FIG. 12 para la unidad de prueba 1208-1. Para facilitar la ilustración, solo se muestran las puertas XOR de las unidades de prueba 1208-2 y 1208-N en la FIG. 12. En funcionamiento, cada unidad de prueba 1208-1 a 1208-N puede generar un cero cuando las salidas del flop de prueba y el flop normal respectivos coinciden, y emitir un uno cuando las salidas del flop de prueba y el flop normal respectivos no coinciden.

[0054] La unidades de prueba 1208-1 y 1208-N se pueden propagar en un chip para probar diferentes áreas del chip, que pueden experimentar diferentes retardos de propagación debido a las variaciones en el chip proceso-voltaje-temperatura (PVT). Las unidades de prueba 1208-1 y 1208-N pueden tener diferentes rutas de datos y/o diferentes números de memorias intermedias de reloj.

[0055] El circuito de sintonización 1205 puede comprender además un codificador 1260 y un ajustador de voltaje de 1270. Las salidas de las unidades de prueba 1208-1 a 1208-N están acopladas al codificador 1260. El codificador 1260 puede configurarse para contar el número de unidades de prueba 1208-1 a 1208-N que emiten un uno lógico y enviar el valor de recuento al ajustador de voltaje 1270. El ajustador de voltaje 1270 puede utilizar el valor de recuento para determinar un voltaje de alimentación de baja potencia mínimo V<sub>L</sub>. Por ejemplo, el ajustador de voltaje 1270 puede reducir gradualmente V<sub>L</sub> mientras supervisa el valor de recuento. El ajustador de voltaje 1270 puede dejar de reducir V<sub>L</sub> cuando el valor de recuento alcanza un umbral. El ajustador de voltaje 1270 puede entonces continuar supervisando el valor de recuento. Si el valor de recuento sube por encima del umbral (por ejemplo, durante un cierto período de tiempo), entonces el ajustador de voltaje 1270 puede aumentar V<sub>L</sub> hasta que el valor de recuento vuelva al umbral. En este contexto, el umbral corresponde a una cierta tasa de error (por ejemplo, debido a infracciones de configuración), y no debe confundirse con el voltaje umbral de un transistor.

65 **[0056]** El ajustador de voltaje 1270 puede ajustar el voltaje de alimentación de baja potencia V<sub>L</sub> utilizando diversas técnicas. Por ejemplo, cuando V<sub>L</sub> es proporcionado por un regulador LDO, el ajustador de voltaje 1270 puede ajustar

$V_L$  ajustando la entrada Vref de voltaje de referencia al LDO. Cuando  $V_L$  es proporcionado por un convertidor de CC a CC (por ejemplo, el convertidor de CC a CC 1105), el ajustador de voltaje 1270 puede ajustar  $V_L$  ajustando la capacidad del condensador del convertidor de CC a CC (por ejemplo, un condensador C). Por ejemplo, el ajustador de voltaje 1270 puede reducir  $V_L$  reduciendo la capacidad y aumentar  $V_L$  aumentando la capacidad. En este ejemplo, el condensador convertidor de CC a CC puede incluir un condensador variable para ajustar la capacidad. El condensador convertidor de CC a CC también puede comprender uno o más condensadores fijos (por ejemplo, acoplados en paralelo con el condensador variable).

5

10

15

20

25

30

35

50

55

[0057] En un ejemplo, el condensador variable puede comprender una pluralidad de condensadores individuales y una pluralidad de interruptores para conmutar de forma independiente los condensadores individuales dentro y fuera de una batería de condensadores que establece la capacidad del condensador variable. En este ejemplo, el ajustador de voltaje 1270 puede ajustar la capacidad del condensador variable cambiando uno o más de los condensadores individuales al banco de condensadores utilizando los interruptores para lograr la capacidad deseada. Los condensadores individuales que son conmutados al banco de condensadores por los respectivos interruptores contribuyen a la capacidad del condensador variable, mientras que los condensadores individuales que son desconectados del banco de condensadores por los respectivos interruptores no lo hacen.

[0058] Ahora se describirá un procedimiento para sintonizar el voltaje de alimentación de baja potencia V<sub>L</sub> de acuerdo con un ejemplo de la presente divulgación. En primer lugar, la frecuencia de reloj se puede configurar para cumplir con la carga de trabajo deseada. La carga de trabajo puede depender de la aplicación particular del sistema correspondiente. Por ejemplo, para un sistema en un dispositivo médico, la carga de trabajo puede depender de la frecuencia con la que el dispositivo médico (por ejemplo, un marcapasos) supervisa la frecuencia cardíaca de un paciente. Para un sistema configurado para activar un dispositivo informático cuando se detecta una entrada de usuario en una interfaz de usuario (por ejemplo, un teclado o una pantalla táctil), la carga de trabajo puede depender de la frecuencia con la que el sistema verifica la interfaz de usuario para una entrada de usuario.

[0059] Después de que se establece la frecuencia de reloj, el voltaje de alimentación de baja potencia V<sub>L</sub> se puede ajustar al voltaje de trabajo más bajo para que la frecuencia de reloj. Esto se puede hacer, por ejemplo, utilizando el circuito de sintonización 1205. En este ejemplo, el ajustador de voltaje 1270 puede reducir gradualmente el voltaje de alimentación de baja potencia V<sub>L</sub> mientras se controla el valor de recuento del codificador 1260, y detener la reducción del voltaje de alimentación de baja potencia V<sub>L</sub> cuando el valor de recuento alcanza un umbral.

[0060] En un modo de realización, una memoria (por ejemplo, SRAM y/o DRAM) puede recibir alimentación entre el diferencial de voltaje (entre V<sub>H</sub> y V<sub>L</sub>) de la señal de reloj de voltaje alto 210. El diferencial de voltaje puede estar por encima de los voltajes umbral de los transistores en la memoria, permitiendo que la memoria funcione a velocidades más altas. En este modo de realización, uno o más de los NFET en la memoria pueden tener una polarización posterior para reducir la corriente de fuga. Por ejemplo, un NFET se puede tener una polarización posterior uniendo el cuerpo del NFET a tierra. Esto crea una polarización de fuente-a-cuerpo de V<sub>L</sub>, lo cual reduce la corriente de fuga del NFET.

40 **[0061]** Aunque el voltaje bajo V<sub>L</sub> se describe como que está por debajo del voltaje umbral en los ejemplos analizados anteriormente, es de apreciar que el voltaje bajo V<sub>L</sub> también puede ser aproximadamente al voltaje umbral, en cuyo caso los transistores funcionan cerca de la región subumbral. Esto todavía puede proporcionar ahorros de energía, aunque no tanto como lo que se puede lograr haciendo funcionar los transistores en la región subumbral. Como se usa en el presente documento, el voltaje umbral de un transistor puede referirse al voltaje de la puerta a la cual el transistor entra en la región de fuerte inversión.

[0062] La FIG. 13 muestra un inversor de par complementario 1300 a modo de ejemplo que se puede utilizar como memoria intermedia en la ruta de reloj y/o la ruta de datos. El inversor de par complementario 1300 incluye un PFET 1310 y un NFET 1320. La fuente del PFET 1310 está acoplado a una alimentación (por ejemplo, V<sub>H</sub> o V<sub>L),</sub> la fuente del NFET 1320 está acoplada a tierra o V<sub>L</sub>, los drenajes del PFET y NFET 1310 y 1320 están acoplados a la salida del inversor 1300 y las puertas del PFET y NFET 1310 y 1320 están acopladas a la entrada del inversor 1300.

[0063] Cuando el inversor 1300 se utiliza para un inversor de árbol de reloj, la fuente del PFET 1310 puede estar acoplado a V<sub>H</sub> y la fuente del NFET 1320 puede estar acoplada a la alimentación de baja potencia. Cuando el inversor 1300 se activa alto, el PFET 1310 se activa y carga la capacidad respectiva a V<sub>H</sub> y, cuando el inversor se activa bajo, el NFET 1320 se activa y descarga la capacidad respectiva a la alimentación de baja potencia, descargando así la carga a la alimentación de baja potencia. En este ejemplo, el PFET 1310 puede actuar como interruptor 1110 y el NFET 1320 puede actuar como interruptor 1120.

[0064] La FIG. 14 muestra otro inversor a modo de ejemplo 1400 que puede usarse como una memoria intermedia. El inversor 1400 es similar al inversor de par complementario 1300 en la FIG. 13, y además incluye un PFET 1410 de puerta común acoplado entre el drenaje del PFET 1310 y la salida del inversor, y un NFET 1420 de puerta común acoplado entre la salida del inversor y el drenaje del NFET 1320. La puerta del PFET 1410 de puerta común está polarizada por el voltaje de CC V<sub>b1 de</sub> y la puerta del NFET 1420 de puerta común está polarizada por el voltaje de CC

[0065] La FIG. 15 es un diagrama de flujo que ilustra un procedimiento 1500 para funcionamiento de baja potencia de acuerdo con un modo de realización de la presente divulgación.

[0066] En el paso 1510, una señal de reloj se envía a un flop través de una ruta de reloj que comprende una pluralidad de transistores, en el que la señal de reloj tiene un estado alto correspondiente a un voltaje alto que está por encima de voltajes umbral de los transistores en la ruta de reloj. Por ejemplo, la señal de reloj (por ejemplo, la señal de reloj (por ejemplo, la ruta de reloj (por ejemplo, la ruta de reloj 120/220). La ruta de reloj (por ejemplo, la ruta de reloj 125/225) puede incluir memorias intermedias (por ejemplo, inversores) que comprenden transistores (por ejemplo, los transistores 1310 y 1320), en los que el estado alto de la señal de reloj corresponde a un voltaje alto (por ejemplo, V<sub>H</sub>) que está por encima de los voltajes umbral de los transistores en la ruta de reloj.

5

10

15

20

25

45

50

55

60

[0067] En el paso 1520, una señal de datos se envía al flop través de una ruta de datos que comprende una pluralidad de transistores, en el que la señal de datos tiene un estado alto correspondiente a un voltaje bajo que está por debajo de los voltajes umbral de los transistores en la ruta de datos. Por ejemplo, la señal de datos (por ejemplo, la señal de datos (por ejemplo, la ruta de datos 130). La ruta de datos (por ejemplo, la ruta de datos 135) puede incluir memorias intermedias (por ejemplo, inversores) que comprenden transistores (por ejemplo, transistores 1310 y 1320), en los que el estado alto de la señal de datos corresponde a un voltaje bajo (por ejemplo, V<sub>L</sub>) que está por debajo de los voltajes umbral de los transistores en la ruta de datos. Esto permite que los transistores en la ruta de datos funcionen en la región subumbral para reducir el consumo de energía. Debe apreciarse que la pluralidad de transistores en el paso 1520 no es necesariamente todos los transistores en la ruta de datos.

[0068] En el paso 1530, la señal de datos se bloquea en el flop usando la señal de reloj. Por ejemplo, el flop (por ejemplo, el flop 150) puede bloquear valores de datos de la señal de datos en los límites ascendentes y/o descendentes de la señal de reloj.

[0069] La FIG.16 es un diagrama de flujo que ilustra un procedimiento 1600 para activar un voltaje de acuerdo con un ejemplo de la presente divulgación.

[0070] En el paso 1610, una señal de datos a enviarse a los flops primero y segundo a través de una ruta de datos. Por ejemplo, la señal de datos (por ejemplo, la señal de datos 212) puede enviarse a través de una ruta de datos (por ejemplo, la ruta de datos 1235) que comprende memorias intermedias (por ejemplo, inversores) alimentados por el voltaje que se está sintonizando.

[0071] En el paso 1620, la señal de datos se bloquea en el primer flop utilizando una señal de reloj. En el paso 1630, la señal de datos se bloquea en el segundo flop usando una versión retardada de la señal de reloj. Por ejemplo, la señal de reloj en el segundo flop (por ejemplo, flop 1210) puede retardarse con respecto a la señal de reloj en el primer flop (por ejemplo, flop 1220) un elemento de retardo (por ejemplo, elemento de retardo 1227). De manera equivalente, se puede decir que la señal de reloj en el primer flop (por ejemplo, 1220) es una versión temprana de la señal de reloj en el segundo flop (por ejemplo, 1210).

[0072] En el paso 1640, se detecta una falta de coincidencia entre las salidas del primer y el segundo flops. Por ejemplo, se puede detectar una falta de coincidencia entre las salidas del primer y el segundo flops (por ejemplo, los flops 1210 y 1220) al acoplar las salidas del primer y el segundo flops a una puerta XOR (por ejemplo, puerta XOR 1250). La puerta XOR emite un cero lógico cuando las salidas coinciden y un uno lógico cuando las salidas no coinciden. Por lo tanto, en este ejemplo, se detecta una falta de coincidencia cuando se emite un uno lógico desde la puerta XOR.

[0073] En el paso 1650 se ajusta el voltaje basándose en la falta de coincidencia detectada. En un modo de realización, un chip puede comprender una pluralidad de pares de flop que incluyen el primer y segundo flops, en los que los pasos 1610-1640 se pueden realizar en cada uno de los pares de flop. En este modo de realización, se puede contar una cantidad de faltas de coincidencia detectadas entre los pares de flop para producir un valor de recuento, y el voltaje puede ajustarse basándose en el valor de recuento. Por ejemplo, el voltaje puede reducirse si el valor de recuento está por debajo de un umbral.

**[0074]** La descripción previa de la divulgación se proporciona para permitir que cualquier experto en la técnica realice o use la divulgación. Diversas modificaciones para la divulgación resultarán fácilmente evidentes para los expertos en la técnica, y los principios genéricos definidos en el presente documento pueden aplicarse a otras variantes sin apartarse del alcance de la divulgación. Por tanto, la divulgación no pretende limitarse a los ejemplos descritos en el presente documento, sino que se le concede el alcance más amplio compatible con los principios y características novedosas divulgados en el presente documento.

#### REIVINDICACIONES

**1.** Un dispositivo de baja potencia, que comprende:

5

10

15

20

30

40

45

55

65

una ruta de reloj (125) para propagar una señal de reloj, en el que la ruta de reloj (125) incluye una pluralidad de transistores;

una fuente de reloj (120) configurada para generar la señal de reloj, teniendo la señal de reloj un estado alto correspondiente a un voltaje alto que está por encima de los voltajes umbral de los transistores en la ruta de reloj (125);

una ruta de datos (135) para propagar una señal de datos, en el que la ruta de datos (135) incluye una pluralidad de transistores;

una fuente de datos (130) configurada para generar la señal de datos, teniendo la señal de datos un estado alto correspondiente a un voltaje bajo que está por debajo de los voltajes umbral de los transistores en la ruta de datos (135); y

un flop (150) configurado para recibir la señal de reloj de la ruta de reloj (125), para recibir la señal de datos de la ruta de datos (135), y para bloquear la señal de datos utilizando la señal de reloj;

en el que la señal de reloj tiene una oscilación de voltaje entre el voltaje alto y el voltaje bajo, y en el que los voltajes alto y bajo son los valores de voltaje máximo y mínimo de la señal de reloj, respectivamente.

- 25 El dispositivo de baja potencia según la reivindicación 1, que comprende además un variador acoplado entre la ruta de reloj (125) y el flop (150), y configurado para variar la oscilación de voltaje de la señal de reloj desde la ruta de reloj (125) para producir un señal de reloj variada, en la que el flop (150) bloquea la señal de datos usando la señal de reloj variada, y en el que el variador está configurado preferentemente para aumentar la oscilación de voltaje de la señal de reloj.

- 3. El dispositivo de baja potencia según la reivindicación 1, en el que el flop (150) comprende una pluralidad de transistores que son alimentados por el voltaje bajo.

- 4. El dispositivo de baja potencia según la reivindicación 1, que comprende además un convertidor de CC a CC de condensador conmutado para convertir el voltaje alto en voltaje bajo en una alimentación de baja potencia, en el que la alimentación de baja potencia se utiliza para alimentar los transistores en la ruta de datos (135).

- 5. El dispositivo de baja potencia según la reivindicación 4, en el que el convertidor de CC a CC de condensador conmutado (1105) comprende:

un condensador (C); y

una pluralidad de interruptores (1110, 1120, 1125, 1130) configurados para cargar de forma alternativa el condensador (C) y descargar el condensador (C) a la alimentación de baja potencia.

- **6.** El dispositivo de baja potencia según la reivindicación 5, en el que el condensador (C) incluye la capacidad de la ruta de reloj (125).

- 7. El dispositivo de baja potencia según la reivindicación 5, en el que la pluralidad de interruptores (1110, 1120, 1125, 1130) están configurados para cargar el condensador (C) acoplando un terminal del condensador (C) a una alimentación de alta potencia que tiene un voltaje aproximado al voltaje alto.

- 8. El dispositivo de baja potencia según la reivindicación 7, en el que la pluralidad de interruptores (1110, 1120, 1125, 1130) están configurados para descargar el condensador (C) acoplando el terminal del condensador (C) a la alimentación de baja potencia.

- 9. Un procedimiento (1500) para funcionamiento de baja potencia, que comprende:

- enviar (1510) una señal de reloj a un flop (150) a través de una ruta de reloj (125) que comprende una pluralidad de transistores, en el que la señal de reloj tiene un estado alto correspondiente a un voltaje alto que está por encima de los voltajes umbral de los transistores en la ruta de reloj (125);

- enviar (1520) una señal de datos al flop (150) a través de una ruta de datos (135) que comprende una pluralidad de transistores, en el que la señal de datos tiene un estado alto correspondiente a un voltaje bajo que está por debajo de los voltajes umbral de los transistores en la ruta de datos (135); y

bloquear (1530) la señal de datos en el flop (150) usando la señal de reloj;

en el que la señal de reloj tiene una oscilación de voltaje entre el voltaje alto y el voltaje bajo, y en el que los voltajes alto y bajo son los valores de voltaje máximo y mínimo de la señal de reloj, respectivamente.

5

10. El procedimiento (1500) según la reivindicación 9, que comprende además variar la oscilación de voltaje en la señal de reloj para producir una señal de reloj variada, en el que la señal de datos se bloquea en el flop (150) utilizando la señal de reloj variada, y en el que variar la oscilación de voltaje de la señal de reloj comprende preferentemente aumentar la oscilación de voltaje de la señal de reloj.

10

- **11.** El procedimiento (1500) según la reivindicación 9, que comprende además alimentar una pluralidad de transistores en el flop (150) con el voltaje bajo.

- 12. El procedimiento (1500) según la reivindicación 9, que comprende además:

- convertir el voltaje alto en voltaje bajo en una alimentación de baja potencia; y

- alimentar la pluralidad de transistores en la ruta de datos (135) utilizando la alimentación de baja potencia.

- 20 **13.** El procedimiento (1500) según la reivindicación 12, en el que convertir el voltaje alto en voltaje bajo comprende cargar de forma de alternativa un condensador (C) y descargar el condensador (C) a la alimentación de baja potencia, y en el que el condensador (C) incluye preferentemente capacidad de la ruta de reloj (125).

- 14. El procedimiento (1500) según la reivindicación 13, en el que cargar el condensador (C) comprende acoplar un terminal del condensador (C) a una alimentación de alta potencia que tiene un voltaje aproximadamente al voltaje alto.

- **15.** El procedimiento según la reivindicación 14, en el que la descarga del condensador (C) comprende el acoplamiento del terminal del condensador (C) a la alimentación de baja potencia.

FIG. 1A

FIG. 2A

FIG. 3

FIG. 5

FIG. 6

FIG. 9

FIG. 10

FIG. 11

FIG. 15

<u>1600</u>

FIG. 16