OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 708 125

61 Int. Cl.:

| H04B 5/00   | (2006.01) | H04W 36/00 | (2009.01) | H04W 88/18 |

|-------------|-----------|------------|-----------|------------|

| H04B 17/318 | (2015.01) | H04W 40/00 | (2009.01) |            |

| H04J 3/16   | (2006.01) | H04W 52/02 | (2009.01) |            |

| H04J 11/00  | (2006.01) | H04W 52/04 | (2009.01) |            |

| H04L 1/18   | (2006.01) | H04W 72/00 | (2009.01) |            |

| H04L 5/00   | (2006.01) | H04W 74/00 | (2009.01) |            |

| H04L 12/24  | (2006.01) | H04W 80/10 | (2009.01) |            |

| H04W 4/00   | (2008.01) | H04W 84/12 | (2009.01) |            |

| H04W 8/08   | (2009.01) | H04W 88/02 | (2009.01) |            |

| H04W 28/00  | (2009.01) | H04W 88/08 | (2009.01) |            |

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(2009.01)

- Fecha de presentación y número de la solicitud europea: 17.09.2013 E 17165456 (9)

Fecha y número de publicación de la concesión europea: 31.10.2018 EP 3226434

- (54) Título: Decodificación ciega para un canal físico de control de enlace descendente mejorado (EPDCCH)

- (30) Prioridad:

28.09.2012 US 201261707784 P 28.06.2013 US 201313931102

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **08.04.2019**

(73) Titular/es:

INTEL CORPORATION (100.0%) 2200 Mission College Blvd. Santa Clara, CA 95052, US

(72) Inventor/es:

CHEN, XIAOGANG; HAN, SEUNGHEE; ZHU, YUAN; LI, QINGHUA y FWU, JONG-KAE

(74) Agente/Representante:

LEHMANN NOVO, María Isabel

#### **DESCRIPCIÓN**

Decodificación ciega para un canal físico de control de enlace descendente mejorado (EPDCCH)

#### Antecedentes

5

10

30

- La tecnología de comunicación móvil inalámbrica utiliza diversos estándares y protocolos para transmitir datos entre un nodo (p. ej., una estación de transmisión o un nodo transceptor) y un dispositivo inalámbrico (p. ej., un dispositivo móvil). Algunos dispositivos inalámbricos se comunican utilizando el acceso múltiple por división de frecuencia ortogonal (OFDMA) en una transmisión de enlace descendente (DL) y el acceso múltiple por división de frecuencia de portadora única (SC-FDMA) en una transmisión de enlace ascendente (UL). Los estándares y protocolos que utilizan la multiplexación por división de frecuencia ortogonal (OFDM) para la transmisión de señales, incluyen la evolución a largo plazo (LTE) del proyecto de asociación de tercera generación (3GPP), el estándar 802.16 del Instituto de Ingenieros Eléctricos y Electrónicos (IEEE) (p. ej., 802.16e, 802.16m), que es comúnmente conocido por los grupos de la industria como WiMAX (Interoperabilidad mundial para Acceso por Microondas) y el estándar IEEE 802.11, que es comúnmente conocido por los grupos de la industria como WiFi.

- En los sistemas de LTE de red de acceso de radio (RAN) de 3GPP, el nodo puede ser una combinación de Nodos B de Red de Acceso de Radio Terrestre Universal (E-UTRAN) (también denominados comúnmente como Nodos B evolucionados, Nodos B mejorados, eNodoB o eNB) y Controladores de Red de Radio (RNC), que se comunican con el dispositivo inalámbrico, conocido como equipo de usuario (UE). La transmisión de enlace descendente (DL) puede ser una comunicación desde el nodo (p. ej., eNodoB) al dispositivo inalámbrico (p. ej., UE) y la transmisión de enlace ascendente (UL) puede ser una comunicación desde el dispositivo inalámbrico al nodo.

- En LTE, los datos pueden transmitirse desde el eNodoB al UE a través de un canal físico compartido de enlace descendente (PDCCH). Se puede utilizar un canal físico de control de enlace descendente (PDCCH) para transferir información de control de enlace descendente (DCI) que informa al UE sobre las asignaciones de recursos o la planificación relacionada con las asignaciones de recursos de enlace descendente en el PDSCH, las concesiones de recursos de enlace ascendente. El PDCCH se puede transmitir antes del PDSCH en cada una de las subtramas transmitida desde el eNodoB al UE.

- El documento WO 2012/109542 A1 se refiere a métodos y sistemas para enviar y recibir un canal de control de enlace descendente mejorado (EPDCCH). El método incluye recibir información del canal de control a través del canal de control mejorado, utilizar la información del canal de control para recibir un canal compartido y detectar la presencia del canal de control mejorado en una subtrama determinada. El canal de control mejorado puede transmitirse a través de múltiples puertos de antena. Por ejemplo, se puede utilizar multiplexación y demultiplexación divisional de código y utilizar señales de referencia comunes y específicas del UE. Se pueden definir nuevos elementos del canal de control y se puede utilizar la retroalimentación de la información de estado de canal (CSI) de control mejorado. La presencia o ausencia de canales de control heredados puede afectar a la demodulación y/o a los métodos de decodificación.

- El documento Tdoc R1-123120 de 3GPP, "Search space design for ePDCCH", WG1 RAN TSG 3GPP Reunión # 70, agosto de 2012, propone que se utilice un índice global de elemento de canal de control mejorado (ECCE) para definir el espacio de búsqueda específico del UE (USS). El índice n de ECCE que se satisface de candidatos de EPDCCH con nivel L de agregación debe cumplir con el requisito n mod L = 0 y el ECCE inicial y los siguientes L 1 ECCE en el conjunto de correspondientes ECCE están dispuestos para un candidato de EPDCCH.

- 40 Breve descripción de los dibujos

- Las características y ventajas de la divulgación serán evidentes a partir de la descripción detallada que sigue tomada en conjunto con los dibujos adjuntos, que juntos ilustran, a modo de ejemplo, las características de la divulgación; y, en donde:

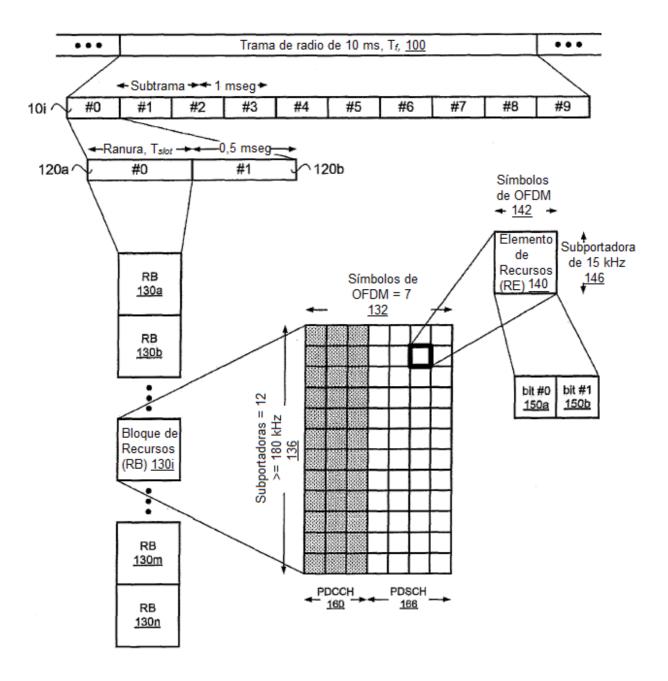

- la FIG. 1, ilustra un diagrama de recursos de trama de radio (p. ej., una tabla de recursos) para una transmisión de enlace descendente (DL) que incluye un canal físico de control de enlace descendente (PDCCH) heredado de acuerdo con un ejemplo;

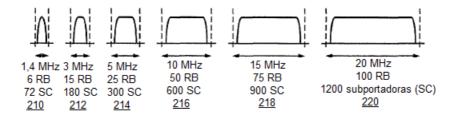

- la FIG. 2, ilustra un diagrama de diversos anchos de banda de portadora de componente (CC) de acuerdo con un ejemplo;

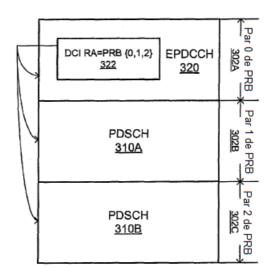

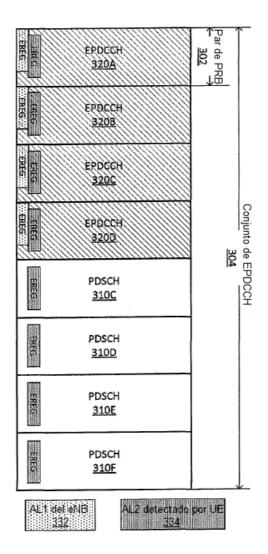

- la FIG. 3, ilustra un diagrama de multiplexación de canal físico de control de enlace descendente (EPDCCH) y de canal físico compartido de enlace descendente (PDSCH) de acuerdo con un ejemplo;

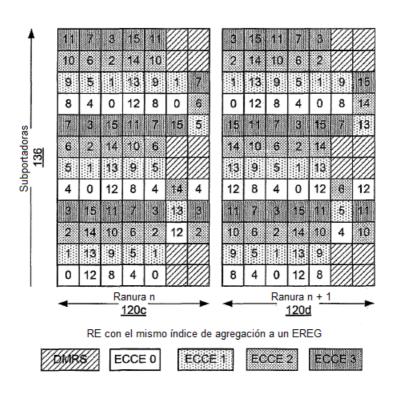

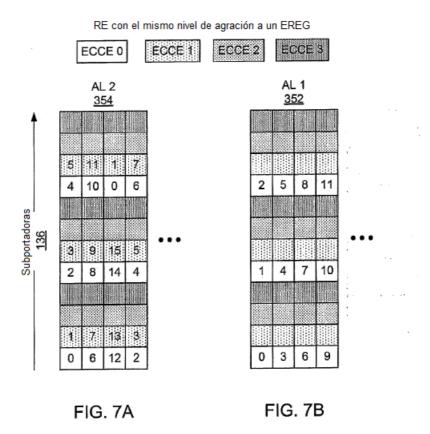

- la FIG. 4, ilustra un diagrama de cuatro elementos de canal de control mejorado (ECCE) en un par de bloques de recursos físicos (PRB) que muestra un índice de grupo de elementos de recursos mejorados (EREG) para cada uno de los elementos de recursos (RE) de acuerdo con un ejemplo;

- la FIG. 5, ilustra un ejemplo de ambigüedad del nivel de agregación (AL) para el canal físico de control de enlace descendente mejorado (EPDCCH) distribuido de acuerdo con un ejemplo;

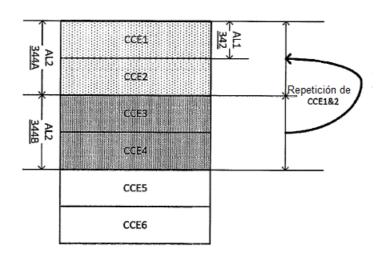

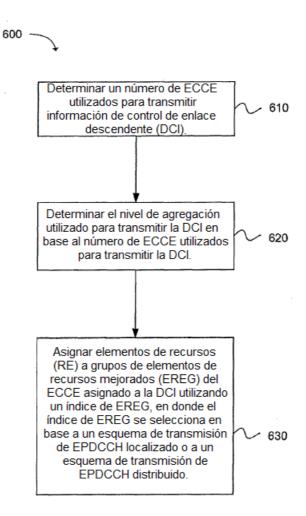

- la FIG. 6, ilustra un ejemplo de ambigüedad del nivel de agregación (AL) en la decodificación ciega de un equipo de usuario (UE) de acuerdo con un ejemplo;

- la FIG. 7A, ilustra un diagrama de la asignación de primero frecuencia específica del nivel de agregación (AL) para AL 2 de acuerdo con un ejemplo;

- 10 la FIG. 7B, ilustra un diagrama de la asignación de primero frecuencia específica del nivel de agregación (AL) para AL 1 de acuerdo con un ejemplo;

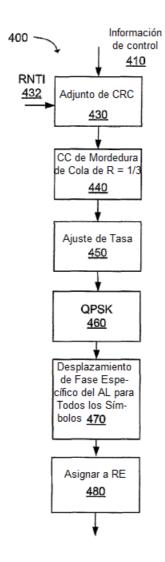

- la FIG. 8, ilustra un diagrama de flujo para el procesamiento del canal físico de control de enlace descendente mejorado (EPDCCH) en un nodo con desplazamiento de fase específico del nivel de agregación (AL) de acuerdo con un ejemplo;

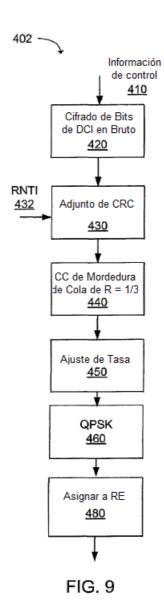

- la FIG. 9, ilustra un diagrama de flujo para el procesamiento del canal físico de control de enlace descendente mejorado (EPDCCH) en un nodo con aleatorización específica del nivel de agregación (AL) de la información de control de enlace descendente (DCI) de acuerdo con un ejemplo;

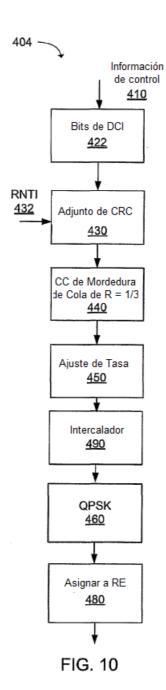

- la FIG. 10, ilustra un diagrama de flujo para el procesamiento del canal físico de control de enlace descendente mejorado (EPDCCH) en un nodo con un intercalador después del ajuste de tasa de acuerdo con un ejemplo;

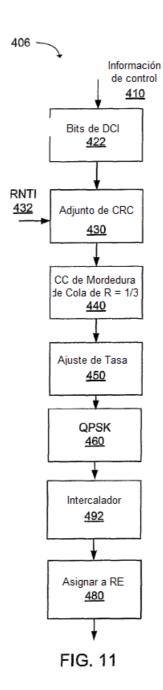

- la FIG. 11, ilustra un diagrama de flujo para el procesamiento del canal físico de control de enlace descendente mejorado (EPDCCH) en un nodo con un intercalador después de la modulación de acuerdo con un ejemplo;

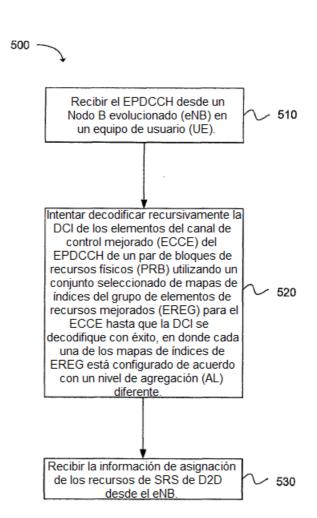

- la FIG. 12, representa un diagrama de flujo de un método para la decodificación ciega de la información de control de enlace descendente (DCI) de un canal físico de control de enlace descendente mejorado (EPDCCH) de acuerdo con un ejemplo;

- la FIG. 13, muestra la funcionalidad de la circuitería de computadora de un nodo operable para asignar elementos de recursos (RE) a elementos de canal de control mejorado (ECCE) de un canal físico de control de enlace descendente mejorado (EPDCCH) en base a un nivel de agregación (AL) de acuerdo con un ejemplo;

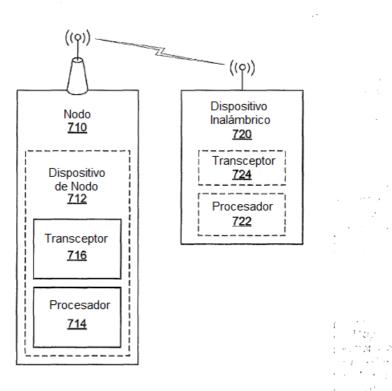

- la FIG. 14, ilustra un diagrama de bloques de un nodo (p. ej., eNB) y un dispositivo inalámbrico (p. ej., UE) de acuerdo con un ejemplo; y

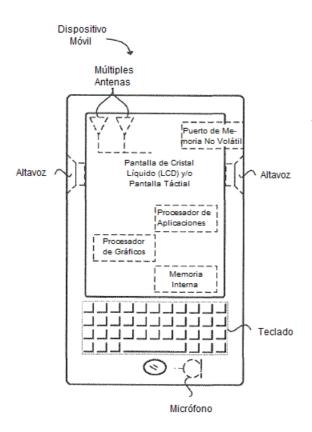

- 30 la FIG. 15, ilustra un diagrama de un dispositivo inalámbrico (p. ej., UE) de acuerdo con un ejemplo.

#### Resumen

La invención se define por la materia objeto de las reivindicaciones independientes. Las realizaciones ventajosas son sujeto de las reivindicaciones dependientes y se exponen en los siguientes párrafos a continuación.

#### Descripción detallada

- Se debe entender que la terminología empleada en el presente documento se utiliza con el propósito de describir solamente ejemplos particulares y no pretende ser limitante. Los mismos números de referencia en diferentes dibujos representan el mismo elemento. Los números proporcionados en los diagramas de flujo y los procesos, se proporcionan para mayor claridad al ilustrar los pasos y las operaciones y, no necesariamente, indican un orden o secuencia particular.

- 40 Realizaciones de ejemplo

A continuación se proporciona una descripción general inicial de las realizaciones tecnológicas y, luego, se describen con más detalle las realizaciones tecnológicas específicas. Este resumen inicial tiene la intención de ayudar a los lectores a comprender la tecnología más rápidamente, pero no pretende identificar características clave o características esenciales de la tecnología, ni pretende limitar el alcance de la materia objeto reivindicada.

La comunicación de datos en el canal físico compartido de enlace descendente (PDSCH) se puede controlar a través de un canal de control, denominado canal físico de control de enlace descendente (PDCCH). El PDCCH se puede utilizar para asignaciones de recursos de enlace descendente (DL) y de enlace ascendente (UL), transmitir comandos de potencia e indicadores de paginación. La concesión de planificación de PDSCH se puede designar a un dispositivo inalámbrico particular (p. ej., UE) para la asignación de recursos de PDSCH dedicados para transportar tráfico específico del UE, o la concesión de planificación de PDSCH se puede designar a todos los dispositivos inalámbricos en la célula para la asignación de recursos de PDSCH común a transportar información de control de difusión, tal como información del sistema o de paginación.

En un solo ejemplo, el PDCCH y el PDSCH pueden representar elementos de una estructura de trama de radio transmitida en la capa física (PHY) en una transmisión de enlace descendente entre un nodo (p. ej., eNodoB) y el dispositivo inalámbrico (p. ej., UE) utilizando una estructura de trama de evolución a largo plazo (LTE) de 3GPP genérica, como se ilustra en la FIG. 1.

La FIG. 1 ilustra una estructura de trama de radio de enlace descendente de tipo 1. En el ejemplo, una trama 100 de radio de una señal utilizada para transmitir los datos puede estar configurada para que tenga una duración, Tf, de 10 milisegundos (ms). Cada una de las tramas de radio puede estar segmentada o dividida en diez subtramas 110i que cada una es de 1 ms de duración. Cada una de las subtramas puede subdividirse adicionalmente en dos ranuras 120a y 120b, cada una con una duración, Tslot, de 0,5 ms. La primera ranura (#0) 120a puede incluir un canal 160 físico de control de enlace descendente (PDCCH) heredado y/o un canal 166 físico compartido de enlace descendente (PDSCH) y, la segunda ranura (#1) 120b, puede incluir datos transmitidos utilizando el PDSCH.

15

30

45

50

55

Cada una de las ranuras para una portadora de componente (CC) utilizada por el nodo y el dispositivo inalámbrico, puede incluir múltiples bloques 130a, 130b, 130i, 130m y 130n de recursos (RB) en base al ancho de banda de frecuencia del CC. El CC puede tener una frecuencia de portadora que tiene un ancho de banda y una frecuencia central. Cada una de las subtramas del CC puede incluir información de control de enlace descendente (DCI) que se encuentra en el PDCCH heredado. El PDCCH heredado en la región de control puede incluir de una a tres columnas de los primeros símbolos de OFDM en cada una de las subtramas o los RB físicos (PRB), cuando se utiliza un PDCCH heredado. Los símbolos 11 a 13 de OFDM restantes (o 14 símbolos de OFDM, cuando no se utiliza el PDCCH heredado) en la subtrama pueden asignarse al PDSCH para datos (para el prefijo cíclico normal o corto).

La región de control puede incluir un canal físico indicador de formato de control (PCFICH), un canal indicador de solicitud de repetición automática híbrida (ARQ-híbrida) (PHICH) y el PDCCH. La región de control tiene un diseño de control flexible para evitar sobrecargas innecesarias. El número de símbolos de OFDM en la región de control utilizado para el PDCCH se puede determinar mediante el indicador de formato de canal de control (CFI) transmitido en el canal físico indicador de formato de control (PCFICH). El PCFICH se puede ubicar en el primer símbolo OFDM de cada una de las subtramas. El PCFICH y el PHICH pueden tener prioridad sobre el PDCCH, por lo que el PCFICH y el PHICH se planifican antes del PDCCH.

Cada uno de los RB 130i (RB físico o PRB) puede incluir 12 subportadoras 136 de 15 kHz (en el eje de frecuencia) y 6 o 7 símbolos 132 de multiplexación por división de frecuencia ortogonal (OFDM) (en el eje de tiempo) por ranura. El RB puede utilizar siete símbolos de OFDM si se emplea un prefijo cíclico corto o normal. El RB puede utilizar seis símbolos de OFDM si se utiliza un prefijo cíclico extendido. El bloque de recursos se puede asignar a 84 elementos 140i de recursos (RE) utilizando un prefijo cíclico corto o normal, o el bloque de recursos se puede asignar a 72 RE (no mostrados) utilizando el prefijo cíclico extendido. El RE puede ser una unidad de un símbolo 142 de OFDM por una subportadora 146 (es decir, 15 kHz).

Cada uno de los RE puede transmitir dos bits 150a y 150b de información en el caso de modulación por desplazamiento de fase en cuadratura (QPSK). Se pueden utilizar otros tipos de modulación, como modulación de amplitud de cuadratura de 16 (QAM) o QAM de 64 para transmitir un mayor número de bits en cada uno de los RE, o modulación por desplazamiento de fase binaria (BPSK) para transmitir un menor número de bits (un único bit) en cada uno de los RE. El RB puede configurarse para una transmisión de enlace descendente desde el eNodoB al UE, o el RB puede configurarse para una transmisión de enlace ascendente desde el UE al eNodoB.

Cada uno de los dispositivos inalámbricos puede utilizar al menos un ancho de banda. El ancho de banda puede denominarse ancho de banda de señal, ancho de banda de portadora o ancho de banda de portadora de componente (CC), como se ilustra en la FIG. 2. Por ejemplo, los anchos de banda de CC de LTE pueden incluir: 1,4 MHz 310, 3 MHz 312, 5 MHz 314, 10 MHz 316, 15 MHz 318 y 20 MHz 320. El CC de 1,4 MHz puede incluir 6 RB que comprenden 72 subportadoras. El CC de 3 MHz puede incluir 15 RB que comprenden 180 subportadoras. El CC de 5 MHz puede incluir 25 RB que comprenden 300 subportadoras. El CC de 10 MHz puede incluir 50 RB que comprenden 600 subportadoras. El CC de 15 MHz puede incluir 75 RB que comprenden 900 subportadoras. El CC de 20 MHz puede incluir 100 RB que comprenden 1200 subportadoras.

Los datos transportados en el PDCCH pueden denominarse información de control de enlace descendente (DCI). Se pueden planificar múltiples dispositivos inalámbricos en una subtrama de una trama de radio. Por lo tanto, se pueden enviar múltiples mensajes de DCI utilizando múltiples PDCCH. La información de DCI en un PDCCH se puede transmitir utilizando uno o más elementos de canal de control (CCE). Un CCE puede estar compuesto por un grupo de grupos de elementos de recursos (REG). Un CCE heredado puede incluir hasta nueve REG. Cada uno de los REG heredados puede estar compuesto por cuatro elementos de recursos (RE). Cada uno de los elementos de recursos puede incluir dos bits de información cuando se utiliza la modulación en cuadratura. Por lo tanto, un CCE heredado puede incluir hasta 72 bits de información. Cuando se necesitan más de 72 bits de información para transmitir el mensaje de DCI, se pueden emplear múltiples CCE. El uso de múltiples CCE se puede denominar como un nivel de agregación. En un solo ejemplo, los niveles de agregación se pueden definir como 1, 2, 4 u 8 CCE consecutivos asignados a un PDCCH heredado.

10

15

20

25

30

35

40

45

50

55

El PDCCH heredado puede crear limitaciones a los avances realizados en otras áreas de la comunicación inalámbrica. Por ejemplo, la asignación de CCE a subtramas en símbolos de OFDM puede extenderse típicamente sobre la región de control para proporcionar diversidad de frecuencia. Sin embargo, no es posible una diversidad de formación de haz con los procedimientos de asignación actuales del PDCCH. Además, la capacidad del PDCCH heredado puede no ser suficiente para la señalización de control avanzado.

Para superar las limitaciones del PDCCH heredado, un PDCCH mejorado (EPDCCH) puede utilizar los RE en un PRB completo o par de PRB (donde un par de PRB puede ser dos PRB contiguos que utilicen la misma subtrama de la subportadora), en lugar de solo de la columna uno a la tres de símbolos de OFDM en un primera ranura de PRB en una subtrama como en el PDCCH heredado. En consecuencia, el EPDCCH puede estar configurado con una mayor capacidad para permitir avances en el diseño de redes celulares y para minimizar los desafíos y limitaciones conocidos actualmente.

A diferencia del PDCCH heredado, el EPDCCH puede asignarse a los mismos RE o región en un PRB como el PDSCH, pero en diferentes PRB. En un ejemplo, el PDSCH y el EPDCCH no puede multiplexarse dentro de un mismo PRB (o un mismo par de PRB). Por lo tanto, si un solo PRB (o un solo par de PRB) contiene un EPDCCH, los RE no utilizados en el PRB (o par de PRB) pueden estar en blanco, ya que los RE pueden no utilizarse para el PDSCH. El EPDCCH puede ser localizado (p. ej., EPDCCH localizado) o distribuido (p. ej., EPDCCH distribuido). El EPDCCH localizado puede referirse al EPDCCH completo (p. ej., EREG o ECCE) dentro del par de PRB. El EPDCCH distribuido puede referirse a EPDCCH (p. ej., EREG o ECCE) distribuidos en una pluralidad de pares de PRB.

Se puede utilizar la decodificación ciega para detectar una DCI del UE, que incluye la DCI transmitida en el PDCCH heredado. El UE puede ser informado solo del número de símbolos de OFDM dentro de la región de control de una subtrama y puede no ser proporcionado con una ubicación exacta del correspondiente PDCCH del UE. El PDCCH o el EPDCCH pueden proporcionar información de control a múltiples UE en una célula para cada una de las k subtramas. El UE puede realizar la decodificación ciega ya que el UE puede conocer la estructura detallada del canal de control, incluyendo el número de canales de control (CCH) y el número de elementos del canal de control (CCE) a los que se asigna cada uno de los canales de control. Se pueden transmitir múltiples PDCCH en una única subtrama k que puede o puede no ser relevante para un UE particular. Debido a que el UE no conoce la ubicación precisa de la información de DCI en un PDCCH, el UE puede buscar y decodificar los CCE en el PDCCH hasta que se encuentre la DCI para los CC del UE. Los PDCCH candidatos para la detección de la DCI se pueden denominar como un espacio de búsqueda. El UE puede encontrar el PDCCH específico para el UE (o los CC del UE) al monitorizar un conjunto de PDCCH candidatos (un conjunto de CCE consecutivos en los que se podría asignar el PDCCH) en un espacio de búsqueda de PDCCH en cada una de las subtramas.

En la especificación de LTE del 3GPP, tal como en las versiones 8, 9, 10 u 11, el UE puede utilizar un identificador temporal de red de radio (RNTI), que el eNB puede asignar al UE para intentar y decodificar los candidatos. El RNTI se puede utilizar para desenmascarar la comprobación de redundancia cíclica (CRC) de un PDCCH candidato que se ha enmascarado originalmente por el eNB utilizando el RNTI del UE. Si el PDCCH es para un UE específico, el CRC puede enmascararse con un identificador único del UE, por ejemplo, un RNTI de célula (C-RNTI) utilizado en un enlace descendente. Si no se detecta un error de CRC, el UE puede determinar que un PDCCH candidato transporta la DCI para el UE. Si se detecta un error de CRC, entonces el UE puede determinar que el PDCCH candidato no transporta la DCI para el UE y el UE puede aumentar al siguiente PDCCH candidato. El UE puede aumentar al siguiente PDCCH candidato en el espacio de búsqueda en base al nivel de agregación (AL) del CCE.

El número de CCE utilizados para transmitir una pieza de información de control se puede determinar de acuerdo con el modo de transmisión, la calidad de recepción del PDCCH asignado al UE o la calidad del canal del UE, y el número de CCE se conoce como un nivel de agregación de CCE, un nivel de agregación heredado  $L \in \{1,2,4,8\}$ , un nivel de agregación de elementos de canal de control mejorados (ECCE)  $L \in \{1,2,4,8,16,32\}$ , o simplemente nivel de

agregación (AL). El nivel de agregación se puede utilizar para determinar el tamaño de un espacio de búsqueda o el número de CCE (o ECCE) que forman un espacio de búsqueda y/o el número de candidatos del canal de control (CCH) en un espacio de búsqueda. El nivel de agregación de la DCI del UE puede no ser conocido en el UE, lo que se puede denominar ambigüedad del nivel de agregación. Durante la decodificación ciega, el UE puede asumir un AL. Para decodificar los ECCE, el UE también puede asumir un valor del ECCE más bajo utilizado para transmitir las DCI. El valor del ECCE más bajo de las DCI puede no conocerse en el UE, lo que se puede denominar como ambigüedad del ECCE más bajo. El ECCE y un grupo de elementos de recursos mejorados (EREG) pueden asociarse con EPDCCH y, el CCE y el REG, pueden asociarse con el PDCCH.

La ambigüedad del nivel de agregación (ALA) puede causar una degradación del rendimiento para PDSCH, especialmente, cuando los EPDCCH se transmiten con los PDSCH. Cuando un UE detecta la asignación de DL del UE que define una asignación de PDSCH que puede solaparse con el (los) par(es) de PRB que contiene(n) la asignación de DL (p. ej., EPDCCH), el UE puede asumir que el PDSCH planificado por la asignación de DL está ajustado en tasa en torno al (de los) par(es) de PRB que contiene(n) la asignación DL del UE, como se ilustra en la FIG. 3. Una asignación de recursos puede incluir tres pares de PRB (p. ej., dos ranuras contiguas). Un par 302A 0 de PRB puede incluir el EPDCCH 320 utilizado para transmitir la asignación 322 de recursos (RA) de la DCI para el par 0, 1 y 2 de PRB. Un par 302B 1 de PRB y un par 302C 2 de PRB pueden incluir el PDSCH 310A-B.

10

15

20

25

30

35

40

45

El proceso de ajuste de tasa (RM) puede adaptar la tasa de código de las transmisiones de datos de LTE, de tal manera que el número de bits de información y de paridad a transmitir coincida con la asignación de recursos. Por ejemplo, en base a una tasa de código madre de 1/3 del codificador turbo, el ajuste de tasa de LTE puede utilizar un búfer circular, bien para repetir los bits para disminuir la tasa de código o para pinchar bits para aumentar la tasa de código.

Si la DCI indica que los PRB 0, 1, 2 están asignados para el PDSCH y la propia DCI se detecta en el PRB 0, el UE puede ajustar la tasa en torno al PRB 0 y puede decodificar solo el PDSCH del PRB 1, 2. Un solo par de PRB puede contener 2 o 4 ECCE. La FIG. 4 ilustra un ejemplo de cuatro ECCE (p. ej., ECCE 0-4) en un solo par de PRB (p. ej., ranura 120c n y ranura 120d n + 1). La FIG. 4 ilustra la asignación secuencial de primero frecuencia del RE en todos los RE para los ECCE ocupados por la DCI. Los RE para el ECCE se pueden asignar en torno a las señales de referencia de demodulación (DMRS). El número etiquetado en cada uno de los RE es el índice de EREG. En un ejemplo, se puede utilizar el mismo índice de EREG para cada uno de los niveles de agregación. En otro ejemplo (no mostrado), se puede utilizar la asignación secuencial de primero tiempo del RE en todos los RE para los ECCE ocupados por la DCI.

La FIG. 3 ilustra un desafío debido a la ambigüedad del nivel de agregación. Para el EPDCCH localizado, si tanto el PRB 0 como el PRB 1 se asignan para la transmisión de EPDCCH y, si el eNB utiliza el tipo 0 o 2 de asignación de recursos para asignar pares de PRB para un UE, el eNB puede transmitir una DCI con nivel 4 de agregación (AL4) en el PRB 302A 0 y el UE puede decodificar con éxito la DCI con nivel 8 de agregación (AL8) a partir del PRB 302A 0 y del PRB1 302B. Con una DCI decodificada con éxito en el PRB 0 y el PRB1, el UE puede asumir que el PRB 0 y 1 se utilizan para EPDCCH, por lo que el UE solo puede intentar decodificar PDSCH a partir del PRB 2. Por lo tanto, el PDSCH en PRB 1 puede no decodificarse (p. ej., puede perderse), por lo que es posible que la información necesite reenviarse, lo que puede causar una degradación del rendimiento del PDSCH.

La FIG. 5 ilustra un desafío debido a la ambigüedad del nivel de agregación para la transmisión de EPDCCH distribuido. Para la transmisión de EPDCCH distribuido, cuando un número de pares de PRB en un conjunto de EPDCCH distribuido es mayor que un número de EREG que contiene un ECCE distribuido, el UE puede decodificar los EREG a partir de los pares de PRB en el conjunto de EPDCCH distribuido. Por ejemplo, como se muestra en la FIG. 5, un conjunto 304 de EPDCCH contiene ocho pares 302 de PRB y un ECCE puede contener cuatro EREG 332 en el EPDCCH 320A-D. Si el eNB transmite la DCI con el nivel 332 1 de agregación (AL1) y el UE decodifica la DCI con éxito, asumiendo el nivel 334 2 de agregación (AL2), AL4 o AL8, dado que un nivel de agregación mayor que AL1 (p. ej., AL2, AL4 o AL8), puede ocupar todos los pares de PRB en el conjunto de EPDCCH distribuido, entonces el UE puede ajustar la tasa en torno a todos los PRB para la decodificación del PDSCH. Por lo tanto, el PDSCH 310C-F puede no decodificarse (p. ej., puede perderse), por lo que es posible que la información necesite reenviarse, lo que nuevamente puede causar una degradación del rendimiento del PDSCH.

No solo la ambigüedad del nivel de agregación presenta algunos desafíos, sino que la ambigüedad del ECCE más bajo también puede generar algunas ineficiencias en la decodificación ciega. En base a una definición heredada del espacio de búsqueda de PDCCH (p. ej., como se define en la especificación técnica (TS) 36.213 versión 8 de estándar de LTE de 3GPP), los recursos de un nivel de agregación que el UE monitoriza para la detección ciega de PDCCH pueden solaparse con los recursos de otro nivel de agregación. Por ejemplo, la FIG. 6 muestra CCE solapados, donde el UE puede monitorizar los CCE {1,2,3,4,5,6} para detectar la DCI con nivel 1 de agregación y monitorizar los CCE {1&2,3&4,5&6} para detectar la DCI con nivel 2 de agregación.

Dado que el ajuste de tasa se puede utilizar para generar la DCI, las cargas útiles en CCE 2 (AL1 342), en un ejemplo, pueden ser una repetición exacta de las cargas útiles en CCE 1. Del mismo modo, las cargas útiles en CCE 3-4 (AL2 344B), en un ejemplo, pueden ser una repetición exacta de las cargas útiles en CCE 1-2 (AL2 344A). Puede producirse un problema de confusión de índice de CCE más bajo o de ambigüedad del ECCE más bajo. Para el PDCCH heredado, se pueden utilizar bits cero de relleno para hacer que el tamaño de la carga útil de DCI no sea igual a alguno de {12, 14, 16, 20, 24, 26, 32, 40, 44, 56} como se define en el TS 36.212 versión 8 de estándar de LTE de 3GPP. Los bits cero de relleno pueden no estar disponibles para EPDCCH.

5

10

El tamaño de la carga útil {12, 14, 16, 20, 24, 26, 32, 40, 44, 56} está optimizado en el TS 36.212 versión 8 de estándar de LTE de 3GPP con un supuesto de que el tamaño de CCE es de 36 RE. Sin embargo, en el diseño de EPDCCH, el tamaño de ECCE puede ser variable debido a la diferente configuración de las señales de referencia específicas de la célula (CRS), las señales de referencia de información de estado del canal (CSI-RS) y/o el control heredado. Por lo tanto, el tamaño de la DCI se puede optimizar para EPDCCH considerando diferentes tamaños de FCCE.

Por ejemplo, un tamaño de carga útil que puede resultar en problema de confusión del nivel de agregación, puede satisfacer los criterios representados por  $n*3/2*k=m*n\_cce$ , k donde y m son números enteros, y  $m=\{1\ 2\ 4\ 8\ 16\}$ , n representa un tamaño de carga útil, m representa un número de CCE ocupados, k representa un punto de inicio de repeticiones del bloque codificado,  $n\_cce$  representa un tamaño de un ECCE y n es menor que  $(16-m)*n\_cce*2*3/4$ . La tasa de codificación puede ser menor que 3/4, de lo contrario, el UE no puede decodificar la carga útil.

En base a los criterios del ejemplo, en la Tabla 1 se ilustran los tamaños de carga útil (p. ej., el tamaño de carga útil sin procesar 48 o 28) que pueden causar confusión del nivel de agregación para diferentes tamaños de ECCE (p. ej., 12, 24 o 33). La Tabla 1 ilustra tamaños de carga útil que pueden causar confusión de agregación para diferentes tamaños de ECCE (m = 1,2,4,8,16).

Tamaño de ECCECargas útiles incluyendo 16bits de CRCTamaño de carga útil en bruto126448246448334428

Tabla 1

Para ayudar a resolver cierta confusión del nivel de agregación, la Tabla 5.3.3.1.2-1 de la Especificación Técnica (TS) 36.212 versión 11 de estándar de LTE de 3GPP (p. ej., V11.1.0 (2012-12)) puede modificarse para incluir 28 y 48 bits de información para tamaños ambiguos, representados en la Tabla 2.

#### Tabla 2

{12, 14, 16, 20, 24, 26, 28, 32, 40, 44, 48, 56}

En otro ejemplo, se puede utilizar una tabla compatible hacia adelante para incluir m=1, 2, 3,..., 16, como se muestra en la Tabla 3, en lugar de los niveles de agregación que monitoriza el UE (m=1,2,4,8,16). La Tabla 3 ilustra los tamaños de carga útil que pueden causar confusión de agregación para diferentes tamaños de ECCE (m=1,2,3,...,16). La Tabla 2 se define incluyendo los tamaños de carga útil que pueden llevar a la ambigüedad del nivel de agregación dados los diferentes niveles de agregación.

Tabla 3

| Tamaño de ECCE | Cargas útiles incluyendo 16bits de CRC | Tamaño de carga útil en bruto |  |

|----------------|----------------------------------------|-------------------------------|--|

| 11             | 33,44,66                               | 17,28,50                      |  |

| 12             | 44,52,64                               | 28,36,48                      |  |

| 13             | 39,52                                  | 23,36                         |  |

| 15             | 35,45,50,55,65,70                      | 19,29,34,39,49,54             |  |

| 16             | 64                                     | 48                            |  |

| 17             | 34,51,68                               | 18,35,52                      |  |

| 18             | 33,39,44,52,54,66                      | 17,23,28,36,38,50             |  |

| 19             | 38,57                                  | 22,41                         |  |

| 21             | 35,49,63,70                            | 19,33,47,54                   |  |

| 22             | 33,44,66                               | 17,28,50                      |  |

| 23             | 46,69                                  | 30,53                         |  |

| 24             | 44,52,64                               | 28,36,48                      |  |

| 25             | 50                                     | 34                            |  |

| 26             | 39,52                                  | 23,36                         |  |

| 27             | 33,39,45,54,63,66                      | 17,23,29,38,47,50             |  |

| 28             | 35                                     | 19                            |  |

| 29             | 29,58                                  | 13,42                         |  |

| 30             | 35,44,45,50,52,55,65,70                | 19,28,29,34,36,39,49,54       |  |

| 31             | 31,62                                  | 15,46                         |  |

| 32             | 64                                     | 48                            |  |

| 33             | 33,44,55,66                            | 17,28,39,50                   |  |

| 34             | 34,51,68                               | 18,35,52                      |  |

| 35             | 35,50,70                               | 19,34,54                      |  |

Se pueden utilizar diversos métodos para resolver la ambigüedad del nivel de agregación y la ambigüedad del ECCE más bajo. Por ejemplo, para cada uno de los niveles de agregación (p. ej., uno alternativo) se puede utilizar una única asignación secuencial de primero frecuencia o primera de tiempo en todos los RE ocupados por la DCI. La FIG. 7A ilustra un mapa de índices de EREG para un AL 354 2. La FIG. 7B ilustra un mapa de índices de EREG para un AL 352 1. La FIG. 4 ilustra un mapa de índices de EREG que se puede utilizar para un AL 4 o AL 8. El mapa de índices de EREG (no mostrado) también puede utilizar un mapa de índices de EREG secuencial de primero tiempo separado para AL 1, AL 2, o AL 4 o AL 8.

En lugar de asignar símbolos modulados a los RE en un solo ECCE y luego asignarlos a los RE en otro ECCE como se utiliza para un PDCCH heredado, el eNB puede utilizar una asignación de primero frecuencia o de primero tiempo en todos los RE que se utilizan para transmitir la DCI (es decir, la asignación en todo el ECCE y el EREG). Dado que cada uno de los EREG/ECCE se puede distribuir en un par de PRB, la asignación del nivel de agregación puede resultar en un orden de asignación de símbolos diferente para diferentes niveles de agregación y diferentes EREG. Incluso si existe repetición en los bits codificados (ver la FIG. 6), el UE puede no decodificar la DCI correctamente con una suposición de AL incorrecta (p. ej., resolver la ambigüedad del AL) o una suposición inicial de ECCE incorrecta (p. ej., resolver la ambigüedad del ECCE más bajo). El uso de un mapa de índices de EREG del nivel de agregación, puede resolver tanto la ambigüedad del AL como la ambigüedad del ECCE más bajo.

10

15

20

En otro ejemplo, la ambigüedad del nivel de agregación se puede resolver utilizando un desplazamiento de fase específico del nivel de agregación para todos los símbolos 470 modulados (p. ej., alternativamente dos), como se ilustra en la FIG. 8. La FIG. 8 ilustra el procesamiento 400 de canal físico para un eNB. Como se discutió anteriormente, se puede utilizar un identificador único de UE, tal como una célula-RNTI (C-RNTI), para enmascarar la DCI. Se puede utilizar una comprobación de redundancia cíclica (CRC) para la detección de errores en los mensajes de DCI. La carga útil de PDCCH completa se puede utilizar para calcular un conjunto de bits de paridad de CRC. Los bits de paridad de CRC se pueden agregar al final de la carga útil del PDCCH. Durante la agregación 430 de CRC, la información 410 de control (p. ej., DCI) para un UE puede enmascararse con el RNTI 432 del UE.

- El RNTI se puede utilizar para cifrar la comprobación de redundancia cíclica (CRC) agregada a un formato de DCI específico. La comprobación de redundancia cíclica (CRC) puede ser un código de detección de errores que se agrega a un bloque de datos a ser transmitido. El valor del CRC se puede calcular a partir del bloque de datos. La longitud del CRC puede determinar el número de errores que pueden detectarse en el bloque de datos en la recepción de los datos. Es posible que un CRC no pueda corregir errores o determinar qué bits son erróneos.

- Luego, el mensaje de DCI con el adjunto de CRC puede someterse a una codificación de canal, como la codificación 440 convolucional (CC) de mordedura de cola, por un codificador de canal. La codificación convolucional es una forma de corrección de errores hacia adelante. La codificación convolucional puede mejorar la capacidad del canal agregando información redundante cuidadosamente seleccionada. Por ejemplo, LTE puede utilizar un codificador de tasa de 1/3 de bits de cola con una longitud k = 7 de restricción, lo que significa que uno de cada tres bits de la salida contiene información 'útil' mientras que los otros dos agregan redundancia. Un codificador convolucional de mordedura de cola puede inicializar su registro de desplazamiento interno a los últimos k bits del bloque de entrada actual, en lugar de a un estado de 'todo ceros', lo que significa que los estados de inicio y de fin pueden ser los mismos, sin la necesidad de rellenar con ceros el bloque de entrada. La sobrecarga de "terminar" el codificador puede eliminarse, por lo que el bloque de salida puede contener menos bits que un codificador convolucional estándar.

En el UE, el diseño del decodificador convolucional de mordedura de cola puede ser más complicado ya que el estado inicial puede ser desconocido, pero el decodificador sabe que los estados de inicio y de fin son los mismos. En otro ejemplo, un decodificador de canal puede implementarse utilizando un algoritmo de Viterbi.

- Un módulo 450 de ajuste de tasa puede crear un flujo de bits de salida con una tasa de código deseada, como se discutió previamente. Se puede utilizar un modulador para modular el flujo de bits de salida. El modulador puede utilizar diversos esquemas de modulación y de codificación (MCS), como la modulación 460 por desplazamiento de fase en cuadratura (QPSK). La modulación es el proceso de variar una o más propiedades de una forma de onda periódica, llamada señal portadora, con una señal de modulación que típicamente contiene información para ser transmitida (p. ej., DCI).

- Un módulo (p. ej., desplazador de fase específica de AL) puede proporcionar desplazamiento de fase específico del nivel de agregación para todos los símbolos 470 modulados. Por ejemplo, se puede añadir el desplazamiento de fase específica del AL además de un procedimiento de generación de EPDCCH. Por ejemplo, si se pueden utilizar cuatro niveles de agregación para la transmisión de EPDCCH, a cada uno de los AL se le puede asignar uno de los cuatro factores de desplazamiento de fase (p. ej., {1 j -1 -j}). El eNB puede seleccionar un factor de desplazamiento

de acuerdo con el nivel de agregación y multiplicarse en todos los símbolos modulados (p. ej., símbolos modulados de QPSK). El factor de desplazamiento de fase se puede utilizar para resolver el problema de ambigüedad del AL.

En otro ejemplo, además del desplazamiento de fase específico del AL, también puede utilizarse el desplazamiento de fase específico del EREG para los EREG dentro de un par de PRB. El desplazamiento de fase específico del EREG para los EREG puede resolver el problema de la ambigüedad del ECCE más bajo. El factor de desplazamiento del EREG puede ser el mismo o diferente con factores de desplazamiento específicos del nivel de agregación.

Después del desplazamiento de fase específico del nivel de agregación, los símbolos modulados por desplazamiento de fase se pueden asignar a los elementos 480 de recursos mediante un asignador en una o diversas capas (p. ej., los RE se pueden mostrar en la FIG. 4).

En otro ejemplo, la ambigüedad del nivel de agregación se puede resolver utilizando una cifrado específico del nivel de agregación en los bits 420 de DCI no codificados (p. ej., en bruto) (p. ej., alternativa tres) utilizando un cifrador específico del nivel de agregación, como se ilustra en la FIG. 9. La FIG. 9 ilustra el procesamiento 402 del canal físico para un eNB. La secuencia de cifrado puede tener la misma longitud que los bits de DCI no codificados. Por ejemplo, para cuatro niveles de agregación, las secuencias podrían ser:

```

[0 0 ... 0]

[1 1 ... 1]

[0 1 0 1 .... 0 1]

[1 0 1 0 ... 1 0].

```

5

10

15

25

30

35

40

45

50

También se pueden utilizar otros patrones (no mostrados) de secuencia de cifrado. Cada uno de los niveles (p. ej., 1, 2, 4, 8, 16 o 32) de agregación puede utilizar un patrón de secuencia de cifrado diferente y único. Después del cifrado 420 específico del nivel de agregación de bits de DCI en bruto, los bits de DCI pueden someterse al adjunto 430 de CRC y a otras operaciones de procesamiento 402 del canal físico, como se describió anteriormente.

En otra configuración (p. ej., alternativa cuatro), para la transmisión de EPDCCH distribuido, la ambigüedad del AL solamente puede producirse cuando el eNB transmite con AL1 y el UE decodifica correctamente con AL2, AL4 o AL8, en el caso donde el número de pares de PRB en el conjunto de EPDCCH distribuido es mayor que el número de EREG que incluye un solo ECCE. Por lo tanto, se pueden utilizar dos factores específicos del AL para la transmisión de EPDCCH distribuido (p. ej., {1 -1}) para el desplazamiento de fase (p. ej., similar a la alternativa dos excepto el número de factores de desplazamiento) o utilizar dos secuencias para cifrar la DCI (p. ej., similar a la alternativa tres, excepto el uso de dos secuencias de cifrado). Por ejemplo, una de las dos secuencias de cifrado puede utilizar una secuencia todo "ceros" (p. ej., secuencia A) y la otra secuencia de cifrado puede utilizar una secuencia todo "unos" (p. ej., secuencia B). La alternativa cuatro puede combinar y utilizar las alternativas dos y tres. La alternativa cuatro puede proporcionar optimización de reducción de complejidad para un tamaño de conjunto de EPDCCH distribuido particular. Las diversas alternativas (p. ej., alternativas 1, 2, 3 y 4) también se pueden aplicar directamente tanto al conjunto de EPDCCH localizado como distribuido, independientemente de un número de pares de PRB por conjunto y de un número de EREG por ECCE.

En otro ejemplo, la ambigüedad del nivel de agregación o la ambigüedad del ECCE más bajo se puede resolver utilizando un intercalador 490 después del ajuste 450 de tasa (p. ej., alternativa cinco) donde los bits 422 de DCI se proporcionan para el adjunto 430 de CRC, como se ilustra en la FIG. 10. El intercalador se puede utilizar para intercalar contra un fenómeno de desvanecimiento. Para hacer que el UE no pueda decodificar el EPDCCH correctamente bajo un supuesto de nivel de agregación incorrecto, se puede insertar un intercalador 490 de nivel de bits entre el bloque 450 de ajuste de tasa y el bloque 460 de modulación, como se muestra en la FIG. 10. Puede ser aplicable cualquier intercalador siempre que el intercalado destruya una cadena de codificación si el UE asume un nivel de agregación incorrecto en la decodificación ciega. Como el PDCCH heredado puede utilizar un intercalador para el intercalado de REG, el mismo intercalador puede reutilizarse por simplicidad (es decir, se puede reutilizar un intercalador de subbloques). En un ejemplo, los elementos <NULL> en la salida sn del intercalador se pueden eliminar antes de la modulación.

En otro ejemplo, la ambigüedad del nivel de agregación o la ambigüedad del ECCE más bajo se puede resolver utilizando un intercalador 492 después de la modulación (p. ej., QPSK 460) (p. ej., alternativa seis), como se ilustra en la FIG. 11. Similar a la alternativa cinco, se puede insertar un intercalador de nivel de símbolo entre el bloque de modulación de QPSK 460 y el bloque 480 de asignación de símbolo a RE, como se muestra en la FIG. 11. Por

ejemplo, se puede reutilizar un intercalador de subbloques. Por ejemplo, los elementos <NULL> en la salida del intercalador pueden eliminarse antes de la asignación de RE.

Otro ejemplo proporciona un método 500 para la decodificación ciega de la información de control de enlace descendente (DCI) de un canal físico de control de enlace descendente mejorado (EPDCCH), como se muestra en el diagrama de flujo en la FIG. 12. El método puede ejecutarse como instrucciones en una máquina o circuitería de computadora, donde las instrucciones se incluyen en al menos un medio legible por computadora o un medio de almacenamiento legible por máquina no transitorio. El método incluye la operación de recibir el EPDCCH desde un Nodo B evolucionado (eNB) en un equipo de usuario (UE), como en el bloque 510. La operación de intentar decodificar recursivamente la DCI de los elementos del canal de control mejorado (ECCE) del EPDCCH de un par de bloques de recursos físicos (PRB) utilizando un conjunto seleccionado de mapas de índices del grupo de elementos de recursos mejorados (EREG) para el ECCE hasta que la DCI se decodifique con éxito, en donde cada uno de los mapas de índices de EREG está configurado de acuerdo con un nivel de agregación (AL) diferente, como en el bloque 520. La siguiente operación del método puede ser decodificar correctamente la DCI cuando se utiliza el mapa de índices de EREG asociado con un nivel de agregación especificado, en donde el nivel de agregación especificado se utiliza para codificar la DCI, como en el bloque 530.

5

10

15

20

25

30

35

40

45

50

55

Cada una de las asignaciones de índices de EREG se puede utilizar para determinar qué elementos de recursos (RE) en un par de bloques de recursos físicos (PRB) están asociados con cada uno de los ECCE. Por ejemplo, los RE de un par de bloques de recursos físicos (PRB) incluyen un bloque de símbolos y(0), ...,  $y(M_{symb}$  -1) de valores complejos asignados en secuencia comenzando con y(0) hasta los elementos de recursos (k,l) en un puerto de antena asociado cuando los RE son parte de los EREG asignados para la transmisión de EPDCCH, donde  $M_{symb}$  es un número de símbolos de modulación para transmitir en un canal físico y la asignación a elementos de recursos (k,l) en el puerto p de antena es un orden creciente de primero un índice k y luego un índice l, comenzando con una primera ranura y terminando con una segunda ranura en una subtrama.

En un ejemplo, cada uno de los ECCE se puede distribuir con otros ECCE en frecuencia o tiempo en el par de PRB o múltiples pares de PRB, o cada uno de los EREG se puede distribuir con otros EREG en frecuencia o tiempo en el par de PRB o múltiples pares de PRB. La operación de decodificar correctamente la DCI puede incluir además determinar el nivel de agregación y determinar el valor del ECCE más bajo.

En otro ejemplo, el método puede incluir, además, omitir decodificar la DCI cuando un nivel de agregación asumido difiere de un nivel de agregación codificado. Un equipo de usuario (UE) puede intentar decodificar con un mapa de índices de EREG asociado con el supuesto nivel de agregación, y el nivel de agregación codificado puede ser el nivel de agregación utilizado por un Nodo B evolucionado (eNB) para codificar la DCI para la transmisión en el EPDCCH. El método puede incluir además intentar decodificar la DCI utilizando otro mapa de índices de EREG asociado con otro nivel de agregación.

Otro ejemplo proporciona la funcionalidad 600 de la circuitería de computadora de un nodo operable para asignar elementos de recursos (RE) a elementos de canal de control mejorado (ECCE) de un canal físico de control de enlace descendente mejorado (EPDCCH) en base a un nivel de agregación (AL), como se muestra en la diagrama de flujo en la FIG. 13. La funcionalidad puede implementarse como un método o la funcionalidad puede ejecutarse como instrucciones en una máquina, donde las instrucciones se incluyen en al menos un medio legible por computadora o un medio de almacenamiento legible por máquina no transitorio. La circuitería de computadora puede estar configurada para determinar un número de ECCE utilizados para transmitir información de control de enlace descendente (DCI), como en el bloque 610. La circuitería de computadora puede estar configurada además para determinar el nivel de agregación utilizado para transmitir la DCI en base al número de ECCE utilizados para transmitir la DCI, como en el bloque 620. La circuitería de la computadora también puede estar configurada para asignar elementos de recursos (RE) a grupos de elementos de recursos mejorados (EREG) del ECCE asignado a la DCI utilizando un índice de EREG, en donde el índice de EREG se selecciona en base a un esquema de transmisión de EPDCCH localizado o a un esquema de transmisión de EPDCCH distribuido, como en el bloque 630.

En un ejemplo, la circuitería de computadora configurada para asignar el RE puede estar configurada además para asignar el RE a un par de bloques de recursos físicos (PRB) para un esquema de transmisión de EPDCCH localizado utilizando una asignación secuencial de primero frecuencia en todos los RE ocupados por la DCI, o asignar el RE a una pluralidad de pares de PRB para un esquema de transmisión de EPDCCH distribuido utilizando una asignación secuencial de primero frecuencia en todos los RE ocupados por la DCI, donde se transporta una sola DCI para el esquema de transmisión de EPDCCH distribuido utilizando los EREG de la pluralidad de pares de PRB. En otro ejemplo, la circuitería de computadora configurada para asignar el RE puede estar configurada además para asignar el RE a un par de bloques de recursos físicos (PRB) para un esquema de transmisión de EPDCCH localizado utilizando una asignación secuencial de primero tiempo en todos los RE ocupados por la DCI, o asignar el RE a una pluralidad de pares de PRB de un esquema de transmisión de EPDCCH distribuido utilizando una

asignación secuencial de primero tiempo en todos los RE ocupados por la DCI, donde se transporta una sola DCI para el esquema de transmisión de EPDCCH distribuido utilizando los EREG de la pluralidad de pares de PRB.

En una configuración, el ECCE puede transmitirse en un par de bloques de recursos físicos (PRB), donde cada uno de los pares de PRB incluye cuatro ECCE o dos ECCE. Los RE de un par de bloques de recursos físicos (PRB) pueden incluir un bloque de símbolos  $y(0),...,y(M_{symb}-1)$  de valores complejos asignados en secuencia comenzando con y(0) a los elementos (k,l) de recursos en un puerto de antena asociado cuando los RE son parte de los EREG asignados para la transmisión de EPDCCH, donde  $M_{symb}$  es un número de símbolos de modulación para transmitir en un canal físico y la asignación a los elementos (k,l) de recursos en el puerto p de antena es un orden creciente de primero un índice k y luego un índice l, comenzando con una primera ranura y terminando con una segunda ranura en una subtrama.

5

10

35

La circuitería de computadora puede estar configurada además para asignar recursos a un canal físico compartido de enlace descendente (PDSCH) con el recursos asignado de EPDCCH a un canal físico compartido de enlace descendente (PDSCH) con el EPDCCH y transmitir el PDSCH en la asignación de recurso. El EPDCCH puede ser un EPDCCH localizado o un EPDCCH distribuido

La FIG. 14 ilustra un nodo 710 (p. ej., eNB) de ejemplo y un dispositivo 720 inalámbrico (p. ej., UE) de ejemplo. El nodo puede incluir un dispositivo 712 de nodo. El dispositivo de nodo o el nodo puede estar configurado para comunicarse con el dispositivo inalámbrico (p. ej., UE). El dispositivo de nodo puede incluir un procesador 714 y un transceptor 716. El procesador 714 y/o el transceptor 716 pueden estar configurados para asignar elementos de recursos (RE) a elementos de canal de control mejorado (ECCE) de un canal físico de control de enlace descendente mejorado (EPDCCH) en base a un nivel de agregación (AL), como se describe en 600 de la FIG. 13.

El dispositivo 720 inalámbrico (p. ej., UE) puede incluir un transceptor 724 y un procesador 722. El dispositivo inalámbrico (es decir, dispositivo) puede estar configurado para la decodificación ciega de información de control de enlace descendente (DCI) de un canal físico de control de enlace descendente mejorado (EPDCCH), como se describe en 500 de la FIG. 12.

Con referencia de nuevo a la FIG. 14, el procesador 722 puede estar configurado para: intentar decodificar recursivamente la DCI de los elementos del canal de control mejorado (ECCE) del EPDCCH a partir de los candidatos de región del bloque de recursos físicos (PRB) en un conjunto de PRB utilizando un conjunto seleccionado mapas de índices de grupo de elementos de recursos mejorados (EREG) para el ECCE hasta que la DCI se decodifique con éxito; y decodificar la DCI con un mapa de índices de EREG asociado con un mismo nivel de agregación utilizado para codificar la DCI. Cada una de las asignaciones de índices de EREG puede estar configurado para un nivel de agregación (AL) diferente.

Cada una de las asignaciones de índices de EREG se puede utilizar para determinar qué elementos de recursos (RE) en un par de bloques de recursos físicos (PRB) están asociados con el ECCE para el nivel de agregación. Por ejemplo, los RE de un par de bloques de recursos físicos (PRB) pueden incluir un bloque de símbolos  $y(0),...,y(M_{symb}-1)$  de valores complejos asignados en secuencia comenzando con y(0) a los elementos (k,l) de recursos en un puerto de antena asociado cuando los RE son parte de los EREG asignados para la transmisión de EPDCCH, donde  $M_{symb}$  es un número de símbolos de modulación para transmitir en un canal físico y la asignación a elementos (k,l) de recursos en el puerto p de antena es un orden creciente de primero un índice k y luego un índice l, comenzando con una primera ranura y terminando con una segunda ranura en una subtrama.

- 40 En otro ejemplo, el procesador 714 puede estar configurado además para omitir decodificar la DCI cuando un nivel de agregación asumido difiere de un nivel de agregación codificado. El procesador puede intentar decodificar con un mapa de índices de EREG asociado con el nivel de agregación asumido y el nivel de agregación codificado puede ser el mismo nivel de agregación utilizado por un Nodo B evolucionado (eNB) para codificar la DCI para la transmisión en el EPDCCH.

- 45 El transceptor 716 puede estar configurado para recibir el EPDCCH desde un nodo. El nodo puede incluir una estación base (BS), un Nodo B (NB), un Nodo B evolucionado (eNB), una unidad de banda base (BBU), un cabezal de radio remoto (RRH), un equipo de radio remoto (RRE), un unidad de radio remota (RRU) o un módulo de procesamiento central (CPM).

- En otra configuración, el transceptor 716 puede estar configurado para recibir un canal físico compartido de enlace descendente (PDSCH) con el EPDCCH en una asignación de recursos (RA). La RA es una RA tipo 0, RA tipo 1 o una RA tipo 2 definida en el estándar de Evolución a Largo Plazo (LTE) versión 11 del Proyecto de Asociación de Tercera Generación (3GPP).

En otro ejemplo, se utiliza el mismo nivel de agregación para codificar la DCI en 1, 2, 4, 8, 16, o 32 ECCE. En otra configuración, el procesador configurado para decodificar la DCI, puede estar configurado además para resolver una ambigüedad del nivel de agregación; y resolver una ambigüedad del ECCE más bajo.

5

10

15

20

25

30

35

40

45

La FIG. 15 proporciona una ilustración de ejemplo del dispositivo inalámbrico, tal como un equipo de usuario (UE), una estación móvil (MS), un dispositivo inalámbrico móvil, un dispositivo de comunicación móvil, una tableta, un teléfono u otro tipo de dispositivo inalámbrico. El dispositivo inalámbrico puede incluir una o más antenas configuradas para comunicarse con un nodo o estación de transmisión, tal como una estación base (BS), un Nodo B evolucionado (eNB), una unidad de banda base (BBU), un cabezal de radio remoto (RRH), un equipo de radio remoto (RRE), una estación de retransmisión (RS), un equipo de radio (RE), una unidad de radio remota (RRU), un módulo de procesamiento central (CPM) u otro tipo de punto de acceso de red inalámbrica de área amplia (WWAN). El dispositivo inalámbrico puede estar configurado para comunicarse utilizando al menos un estándar de comunicación inalámbrica que incluya LTE de 3GPP, WiMAX, Acceso a paquetes de alta velocidad (HSPA), Bluetooth y WiFi. El dispositivo inalámbrico puede comunicarse utilizando antenas separadas para cada uno del os estándares de comunicación inalámbrica o antenas compartidas para múltiples estándares de comunicación inalámbrica puede comunicarse en una red de área local inalámbrica (WLAN), una red de área personal inalámbrica (WPAN) y/o una WWAN.

La FIG. 15 también proporciona una ilustración de un micrófono y uno o más altavoces que pueden utilizarse para la entrada y salida de audio desde el dispositivo inalámbrico. La pantalla de visualización puede ser una pantalla de cristal líquido (LCD), u otro tipo de pantalla de visualización, tal como una pantalla de diodo orgánico emisor de luz (OLED). La pantalla de visualización puede estar configurada como una pantalla táctil. La pantalla táctil puede utilizar tecnología capacitiva, resistiva u otro tipo de tecnología de pantalla táctil. Un procesador de aplicaciones y un procesador gráfico pueden estar acoplados a la memoria interna para proporcionar capacidades de procesamiento y de visualización. También se puede utilizar un puerto de memoria no volátil para proporcionar opciones de entrada/salida de datos para un usuario. El puerto de memoria no volátil también se puede utilizar para ampliar las capacidades de memoria del dispositivo inalámbrico. Un teclado puede estar integrado con el dispositivo inalámbrico o conectado de manera inalámbrica al dispositivo inalámbrico para proporcionar entrada de usuario adicional. También se puede proporcionar un teclado virtual utilizando la pantalla táctil.

Diversas técnicas, o ciertos aspectos o partes de los mismos, pueden tomar la forma de código de programa (es decir, instrucciones) incorporado en medios tangibles, como disquetes, memoria de discos compactos de solo lectura (CD-ROM), discos duros, medios de almacenamiento legibles por computadora no transitorios o cualquier otro medio de almacenamiento legible por máquina, en donde, cuando se le carga el código de programa y se ejecuta por una máquina, tal como una computadora, la máquina se convierte en un aparato para practicar las diversas técnicas. La circuitería puede incluir hardware, firmware, código de programa, código ejecutable, instrucciones de computadora, y/o software. Un medio de almacenamiento legible por computadora no transitorio puede ser un medio de almacenamiento legible por computadora que no incluye señal. En el caso de ejecución del código de programa en computadoras programables, el dispositivo de computación puede incluir un procesador, un medio de almacenamiento legible por el procesador (incluidos los elementos de memoria y/o de almacenamiento volátiles y no volátiles), al menos un dispositivo de entrada y al menos un dispositivo de salida. Los elementos de memoria y/o de almacenamiento volátiles y no volátiles pueden ser una memoria de acceso aleatorio (RAM), una memoria de solo lectura programable y borrable (EPROM), una unidad flash, una unidad óptica, una unidad de disco duro magnética, una unidad de estado sólido u otro medio para almacenar datos electrónicos. El nodo y el dispositivo inalámbrico también pueden incluir un módulo transceptor (es decir, un transceptor), un módulo contador (es decir, contador), un módulo de procesamiento (es decir, un procesador) y/o un módulo de reloj (es decir, reloj) o un módulo de temporizador (es decir, temporizador). Uno o más programas que pueden implementar o utilizar las diversas técnicas descritas en el presente documento pueden utilizar una interfaz de programación de aplicaciones (API), controles reutilizables y similares. Dichos programas pueden implementarse en un lenguaje de programación de alto nivel procedimental u orientado a objetos para comunicarse con un sistema informático. Sin embargo, el (los) programa(s) puede(n) implementarse en ensamblador o en lenguaje máquina, si se desea. En cualquier caso, el lenguaje puede ser un lenguaje compilado o interpretado, y combinado con implementaciones de hardware.

Se debe entender que muchas de las unidades funcionales descritas en esta memoria descriptiva han sido etiquetadas como módulos, con el fin de enfatizar más particularmente su independencia de implementación. Por ejemplo, un módulo puede implementarse como un circuito de hardware que comprende circuitos personalizados de integración a gran escala (VLSI) o matriz de puertas, semiconductores estándar tales como chips lógicos, transistores u otros componentes discretos. Un módulo también puede implementarse en dispositivos de hardware programables tales como matrices de puertas programables, lógica de matriz programable, dispositivos lógicos programables o similares.

Los módulos también pueden implementarse en software para ejecución por diversos tipos de procesadores. Un módulo identificado de código ejecutable puede, por ejemplo, comprender uno o más bloques físicos o lógicos de instrucciones de computadora, que, por ejemplo, pueden organizarse como un objeto, procedimiento o función. Sin embargo, los ejecutables de un módulo identificado no necesitan estar físicamente ubicados juntos, sino que pueden comprender instrucciones dispares almacenadas en diferentes ubicaciones que, cuando se unen lógicamente, comprenden el módulo y logran el propósito establecido para el módulo.

5

10

25

30

35

40

45

50

De hecho, un módulo de código ejecutable puede ser una sola instrucción, o muchas instrucciones, y puede incluso distribuirse en varios segmentos de código diferentes, entre diferentes programa y a través de varios dispositivos de memoria. De manera similar, los datos operacionales pueden identificarse e ilustrarse en el presente documento dentro de módulos, y pueden incorporarse en cualquier forma adecuada y organizarse dentro de cualquier tipo adecuado de estructura de datos. Los datos operacionales pueden recopilarse como un único conjunto de datos, o pueden distribuirse en diferentes ubicaciones, incluyendo en diferentes dispositivos de almacenamiento, y pueden existir, al menos parcialmente, simplemente como señales electrónicas en un sistema o red. Los módulos pueden ser pasivos o activos, incluyendo los agentes operables para realizar las funciones deseadas.

El Ejemplo 1 Adicional proporciona un equipo de usuario (UE) configurado para la decodificación ciega de la información de control de enlace descendente (DCI) de un canal físico de control de enlace descendente mejorado (EPDCCH), que comprende: un procesador para: intentar decodificar recursivamente la DCI de los elementos del canal de control mejorados (ECCE) del EPDCCH de los candidatos de región del bloque de recursos físicos (PRB) en un conjunto de PRB utilizando un conjunto seleccionado de asignaciones de índices del grupo de elementos de recursos mejorados (EREG) para el ECCE hasta que la DCI se decodifique con éxito, en donde cada una de las asignaciones de índices de EREG está configurado para un nivel de agregación (AL) diferente; y decodificar la DCI con un mapa de índices de EREG asociado con un mismo nivel de agregación utilizado para codificar la DCI.

El Ejemplo 2 Adicional se refiere al UE del Ejemplo 1 Adicional, en donde cada una de las asignaciones de índices de EREG se utiliza para determinar qué elementos de recursos (RE) en un par de bloques de recursos físicos (PRB) están asociados con el ECCE para el nivel de agregación.

El Ejemplo 3 Adicional se refiere al UE del Ejemplo 2 Adicional, en donde los RE de un par de bloques de recursos físicos (PRB) incluyen un bloque de símbolos de valores complejos asignados en secuencia, comenzando con los elementos de recursos en un puerto de antena asociado cuando los RE son parte del EREG asignado para la transmisión de EPDCCH, donde, hay una cantidad de símbolos de modulación para transmitir en un canal físico y la asignación a los elementos de recursos en el puerto p de antena es un orden creciente de primero un índice k y luego un índice I, comenzando con una primera ranura y terminando con una segunda ranura en una subtrama.

El Ejemplo 4 Adicional se refiere al UE del Ejemplo 1 Adicional, en donde el procesador está configurado además para: omitir decodificar la DCI cuando un nivel de agregación asumido difiere de un nivel de agregación codificado, en donde el procesador intenta decodificar con un mapa de índices de EREG asociado con el nivel de agregación asumido y el nivel de agregación codificado es el mismo nivel de agregación utilizado por un Nodo B evolucionado (eNB) para codificar la DCI para la transmisión en el EPDCCH.

El Ejemplo 5 Adicional se refiere al UE del Ejemplo 1 Adicional, que comprende además: un transceptor para: recibir el EPDCCH desde un nodo, en donde el nodo se selecciona del grupo que consiste en una estación base (BS), un Nodo B (NB), un Nodo B evolucionado (eNB), una unidad de banda base (BBU), un cabezal de radio remoto (RRH), un equipo de radio remoto (RRE), una unidad de radio remota (RRU) y un módulo de procesamiento central (CPM).

El Ejemplo 6 Adicional se refiere al UE del Ejemplo 1 Adicional, que comprende además: un transceptor para: recibir un canal físico compartido de enlace descendente (PDSCH) con el EPDCCH en una asignación de recursos (RA), en donde la RA es una RA tipo 0, RA tipo 1 o una RA tipo 2 definida en el estándar de Evolución a Largo Plazo (LTE) versión 11 del Proyecto de Asociación de Tercera Generación (3GPP); y en donde el procesador está configurado además para: ajustar la tasa del PDSCH en torno a un par de bloques de recursos físicos (PRB) que incluyen la DCI en el EPDCCH.

El Ejemplo 7 Adicional se refiere al UE del Ejemplo 1 Adicional, en donde el mismo nivel de agregación se utiliza para codificar la DCI en 1, 2, 4, 8, 16 o 32 ECCE.

El Ejemplo 8 Adicional se refiere al UE del Ejemplo 1 Adicional, en donde el procesador configurado para decodificar la DCI está configurado además para: resolver una ambigüedad del nivel de agregación; y resolver una ambigüedad del ECCE más bajo.

El Ejemplo 9 Adicional se refiere al UE del Ejemplo 1 Adicional, en donde el UE incluye al menos una de una antena, una pantalla táctil, un altavoz, un micrófono, un procesador gráfico, un procesador de aplicaciones, una memoria interna o un puerto de memoria no volátil.

El Ejemplo 10 Adicional proporciona un método para la decodificación ciega de la información de control de enlace descendente (DCI) de un canal físico de control de enlace descendente mejorado (EPDCCH), que comprende: recibir el EPDCCH desde un Nodo B evolucionado (eNB) en un equipo de usuario (UE); intentar decodificar recursivamente la DCI de los elementos del canal de control mejorado (ECCE) del EPDCCH de un par de bloques de recursos físicos (PRB) utilizando un conjunto seleccionado de asignaciones de índices del grupo de elementos de recursos mejorados (EREG) para el ECCE hasta que la DCI se decodifique con éxito, en donde cada una de las asignaciones de índices de EREG está configurada para un nivel de agregación (AL) diferente; y decodificar correctamente la DCI cuando se utiliza el mapa de índices de EREG asociado con un nivel de agregación especificado, en donde el nivel de agregación especificado se utiliza para codificar la DCI.

5

10

15

20

25

30

40

El Ejemplo 11 Adicional se refiere al método del Ejemplo 10 Adicional, en donde cada una de las asignaciones de índices de EREG se utiliza para determinar qué elementos de recursos (RE) en un par de bloques de recursos físicos (PRB) están asociados con cada uno de los ECCE.

El Ejemplo 12 Adicional se refiere al método del Ejemplo 11 Adicional, en donde los RE de un par de bloques de recursos físicos (PRB) incluyen un bloque de símbolos de valores complejos asignados en secuencia, comenzando con los elementos de recursos en un puerto de antena asociado cuando los RE son parte de los EREG asignados para la transmisión de EPDCCH, donde, hay una cantidad de símbolos de modulación para transmitir en un canal físico y la asignación a los elementos de recursos en el puerto p de antena es un orden creciente de primero un índice k y luego un índice I, comenzando con una primera ranura y terminando con una segunda ranura en una subtrama.

El Ejemplo 13 Adicional se refiere al método del Ejemplo 10 Adicional, en donde cada uno de los ECCE se distribuye con otros ECCE en frecuencia o en tiempo en el par de PRB o en múltiples pares de PRB o, cada uno de los EREG se distribuye con otros EREG en frecuencia o en tiempo en el par de PRB o en múltiples pares de PRB.

El Ejemplo 14 Adicional se refiere al método del Ejemplo 10 Adicional, en donde la decodificación correcta de la DCI comprende además: determinar el nivel de agregación; y determinar un valor del ECCE más bajo.

El Ejemplo 15 Adicional se refiere al método del Ejemplo 10 Adicional, que además comprende: omitir decodificar la DCI cuando un nivel de agregación asumido difiere de un nivel de agregación codificado, en donde un equipo de usuario (UE) intenta decodificar con un mapa de índices de EREG asociado con el nivel de agregación asumido y el nivel de agregación codificado es el nivel de agregación utilizado por un Nodo B evolucionado (eNB) para codificar la DCI para la transmisión en el EPDCCH; e intentar decodificar la DCI utilizando otro mapa de índices de EREG asociado con otro nivel de agregación.

El Ejemplo 16 Adicional se refiere a al menos un medio de almacenamiento legible por máquina no transitorio que comprende una pluralidad de instrucciones adaptadas para ejecutarse para implementar el método del Ejemplo 10 Adicional.

El Ejemplo 17 Adicional se refiere a un nodo operable para asignar elementos de recursos (RE) a elementos de canal de control mejorado (ECCE) de un canal físico de control de enlace descendente mejorado (EPDCCH) en base a un nivel de agregación (AL), que tiene circuitería de computadora configurada para: determinar un número de ECCE utilizados para transmitir la información de control de enlace descendente (DCI); determinar el nivel de agregación utilizado para transmitir la DCI en base al número de ECCE utilizados para transmitir la DCI; y asignar elementos de recursos (RE) a grupos de elementos de recursos mejorados (EREG) del ECCE asignado a la DCI utilizando un índice de EREG, en donde el índice de EREG se selecciona en base a un esquema de transmisión de EPDCCH localizado o un esquema de transmisión de EPDCCH distribuido.

El Ejemplo 18 Adicional se refiere a la circuitería de computadora del nodo del Ejemplo 17 Adicional, en donde la circuitería de computadora configurada para asignar el RE está configurada además para: asignar el RE a un par de bloques de recursos físicos (PRB) para el esquema de transmisión de EPDCCH localizado utilizando una asignación secuencial de primero frecuencia en todos los RE ocupados por la DCI; o asignar el RE a una pluralidad de pares de PRB para el esquema de transmisión de EPDCCH distribuido utilizando una asignación secuencial de primero frecuencia en todos los RE ocupados por la DCI, en donde se transporta una sola DCI para el esquema de transmisión de EPDCCH distribuido utilizando los EREG de la pluralidad de pares de PRB.

El Ejemplo 19 Adicional se refiere a la circuitería de computadora del nodo del Ejemplo 17 Adicional, en donde la circuitería de computadora configurada para asignar el RE está configurada además para: asignar el RE a un par de bloques de recursos físicos (PRB) para el esquema de transmisión de EPDCCH localizado utilizando una asignación secuencial de primero tiempo en todos los RE ocupados por la DCI; o asignar el RE a una pluralidad de pares de PRB para el esquema de transmisión de EPDCCH distribuido utilizando una asignación secuencial de primero tiempo en todos los RE ocupados por la DCI, en donde se transporta una sola DCI para el esquema de transmisión de EPDCCH distribuido utilizando los EREG de la pluralidad de pares de PRB.

El Ejemplo 20 Adicional se refiere a la circuitería de computadora del nodo del Ejemplo 17 Adicional, en donde el ECCE se transmite en un par de bloques de recursos físicos (PRB), en donde cada uno de los pares de PRB incluye cuatro ECCE o dos ECCE.

10

15

20

25

30

35

El Ejemplo 21 Adicional se refiere a la circuitería de computadora del nodo del Ejemplo 17 Adicional, en donde los RE de un par de bloques de recursos físicos (PRB) incluyen un bloque de símbolos de valores complejos asignados en secuencia, comenzando con los elementos de recursos en un puerto de antena asociado cuando los RE son parte de los EREG asignados para la transmisión de EPDCCH, donde hay una cantidad de símbolos de modulación para transmitir en un canal físico y la asignación a elementos de recursos en el puerto p de antena es un orden creciente primero de un índice k y luego un índice I, comenzando con una primera ranura y terminando con una segunda ranura en una subtrama.

El Ejemplo 22 Adicional se refiere a la circuitería de computadora del nodo del Ejemplo 17 Adicional, además configurada para: asignar recursos a un canal físico compartido de enlace descendente (PDSCH) con el EPDCCH; y transmitir el PDSCH en la asignación de recursos.

El Ejemplo 23 Adicional se refiere a la circuitería de computadora del nodo del Ejemplo 17 Adicional, en donde el EPDCCH es un EPDCCH localizado o un EPDCCH distribuido.

El Ejemplo 24 Adicional se refiere a la circuitería de computadora del nodo del Ejemplo 17 Adicional, en donde el nodo se selecciona del grupo que consiste en una estación base (BS), un nodo B (NB), un nodo evolucionado B (eNB), una unidad de banda base (BBU), un cabezal de radio remoto (RRH), un equipo de radio remoto (RRE), una unidad de radio remota (RRU) y un módulo de procesamiento central (CPM).

La referencia en esta memoria descriptiva a "un ejemplo" o "ejemplar" significa que una particularidad, estructura o característica particular descrita en relación con el ejemplo se incluye en al menos una sola realización de la presente invención. Por lo tanto, las apariencias de las frases "en un ejemplo" o la palabra "ejemplar" en diversos lugares a lo largo de esta memoria descriptiva no se refieren necesariamente a la misma realización.

Como se utiliza en el presente documento, una pluralidad de artículos, elementos estructurales, elementos de composición y/o materiales se pueden presentar en una lista común por conveniencia. Sin embargo, estas listas deben interpretarse como si cada uno de los miembros de la lista se identificara individualmente como un miembro separado y único. Por lo tanto, ningún miembro individual de dicha lista debe interpretarse como un equivalente de facto de ningún otro miembro de la misma lista únicamente en base a su presentación en un grupo común sin indicaciones de lo contrario. Además, varias realizaciones y ejemplos de la presente invención pueden referirse en el presente documento junto con alternativas para los diversos componentes de la misma. Se entiende que tales realizaciones, ejemplos y alternativas no deben interpretarse como hechos de facto equivalentes entre sí, pero deben considerarse representaciones separadas y autónomas de la presente invención.

Además, las particularidades, estructuras, o características descritas se pueden combinar de cualquier manera adecuada en una o más realizaciones. En la siguiente descripción, se proporcionan numerosos detalles específicos, tales como ejemplos de diseños, distancias, ejemplos de red, etc., para proporcionar una comprensión completa de las realizaciones de la invención.

#### REIVINDICACIONES

- 1. Un aparato para utilizar en un equipo de usuario (UE) configurado para la decodificación ciega de información de control de enlace descendente (DCI) de un canal físico de control de enlace descendente mejorado (EPDCCH), el aparato que comprende circuitería configurada para:

- 5 recibir, desde una estación base, el EPDCCH que incluye la DCI; y

10

intentar decodificar una o más veces la DCI de los elementos del canal de control mejorado (ECCE) del EPDCCH de los candidatos de la región del bloque de recursos físicos (PRB) en un conjunto de PRB utilizando un conjunto seleccionado de asignaciones de índices del grupo de elementos de recursos mejorados (EREG) para el ECCE hasta que la DCI se decodifique con éxito, en donde los elementos de recursos (RE) de un par de PRB incluye un bloque de símbolos asignados en secuencia a los elementos de recursos en un puerto asociado cuando los RE son parte de los EREG asignados para la transmisión de EPDCCH.

2. El aparato de la reivindicación 1, en donde la circuitería está configurada además para:

decodificar la DCI con un mapa de índices de EREG asociado con un mismo nivel de agregación utilizado para codificar la DCI; u

- omitir decodificar la DCI cuando un nivel de agregación asumido difiere de un nivel de agregación codificado, en donde el procesador intenta decodificar con un mapa de índices de EREG asociado con el nivel de agregación asumido y el nivel de agregación codificado es el mismo nivel de agregación utilizado por un Nodo evolucionado B (eNB) para codificar la DCI para la transmisión en el EPDCCH.

- 3. El aparato de cualquiera de las reivindicaciones 1 a 2, en donde: