OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 710 887**

⑮ Int. Cl.:

**G06F 13/12** (2006.01)

⑫

## TRADUCCIÓN DE PATENTE EUROPEA

T3

⑯ Fecha de presentación y número de la solicitud internacional: **25.05.2012 PCT/EP2012/059859**

⑰ Fecha y número de publicación internacional: **13.12.2012 WO12168099**

⑯ Fecha de presentación y número de la solicitud europea: **25.05.2012 E 12724327 (7)**

⑰ Fecha y número de publicación de la concesión europea: **09.01.2019 EP 2601586**

⑭ Título: **Utilización de palabras de dirección de datos indirectos de trasladador de datos asíncronos extendidos**

⑯ Prioridad:

**10.06.2011 US 201113157729**

⑮ Fecha de publicación y mención en BOPI de la traducción de la patente:

**29.04.2019**

⑮ Titular/es:

**INTERNATIONAL BUSINESS MACHINES CORPORATION (100.0%)

New Orchard Road

Armonk, NY 10504, US**

⑯ Inventor/es:

**OAKES, KENNETH, JAMES;

SUTTON, PETER, GRIMM;

DRIEVER, PETER, DANA;

YUDENFRIEND, HARRY y

GLASSEN, STEVEN, GARDNER**

⑮ Agente/Representante:

**ELZABURU, S.L.P**

**ES 2 710 887 T3**

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Utilización de palabras de dirección de datos indirectos de trasladador de datos asíncronos extendidos

### **Antecedentes**

Uno o más aspectos de la presente invención hacen referencia, en general, al almacenamiento auxiliar de un entorno informático y, en particular, a la gestión de aspectos del almacenamiento auxiliar.

Un entorno informático puede incluir un almacenamiento principal (conocido asimismo como memoria principal), así como un almacenamiento auxiliar. El almacenamiento principal es el almacenamiento accesible para un procesador al que se puede acceder de manera aleatoria, por ejemplo, mediante una dirección absoluta. El almacenamiento principal se considera almacenamiento de acceso rápido en comparación con el almacenamiento auxiliar, tal como los dispositivos de almacenamiento de acceso directo (DASD – Direct Access Storage Devices, en inglés) o la memoria de clase de almacenamiento. Además, el direccionamiento del almacenamiento principal se considera más simple que el direccionamiento de DASD o la memoria de clase de almacenamiento.

La memoria de clase de almacenamiento, que es un espacio de almacenamiento externo fuera del almacenamiento principal clásico, proporciona un acceso más rápido que los dispositivos de almacenamiento de acceso directo. A diferencia de los DASD, la memoria de clase de almacenamiento no se implementa típicamente como discos giratorios de brazo mecánico, sino, por el contrario, como partes de estado sólido no mecánicas. Típicamente, la memoria de clase de almacenamiento se implementa como grupos de dispositivos de estado sólido conectados a un sistema informático a través de varios adaptadores de entrada / salida (E/S), que se utilizan para asignar la tecnología de un dispositivo de E/S al bus de memoria de la unidad o unidades de procesamiento central.

### **Compendio**

La invención se expone en el conjunto de reivindicaciones adjuntas. Las reivindicaciones dependientes exponen realizaciones particulares. Las realizaciones o ejemplos de la siguiente descripción que no están cubiertos por las reivindicaciones adjuntas se considera que no forman parte de la invención de acuerdo con esta descripción.

Los productos y sistemas de programas informáticos relacionados con uno o más aspectos de la presente invención se describen y reivindican asimismo en el presente documento. Además, se describen y pueden ser reivindicados asimismo en el presente documento servicios relacionados con uno o más aspectos de la presente invención.

Características y ventajas adicionales se realizan por medio de las técnicas de la presente invención. Otras realizaciones y aspectos de la invención se describen en detalle en el presente documento y se consideran parte de la invención reivindicada.

### **Breve descripción de los dibujos**

A continuación, se describirán realizaciones de la invención, solo a modo de ejemplo, haciendo referencia a los dibujos adjuntos, en los que:

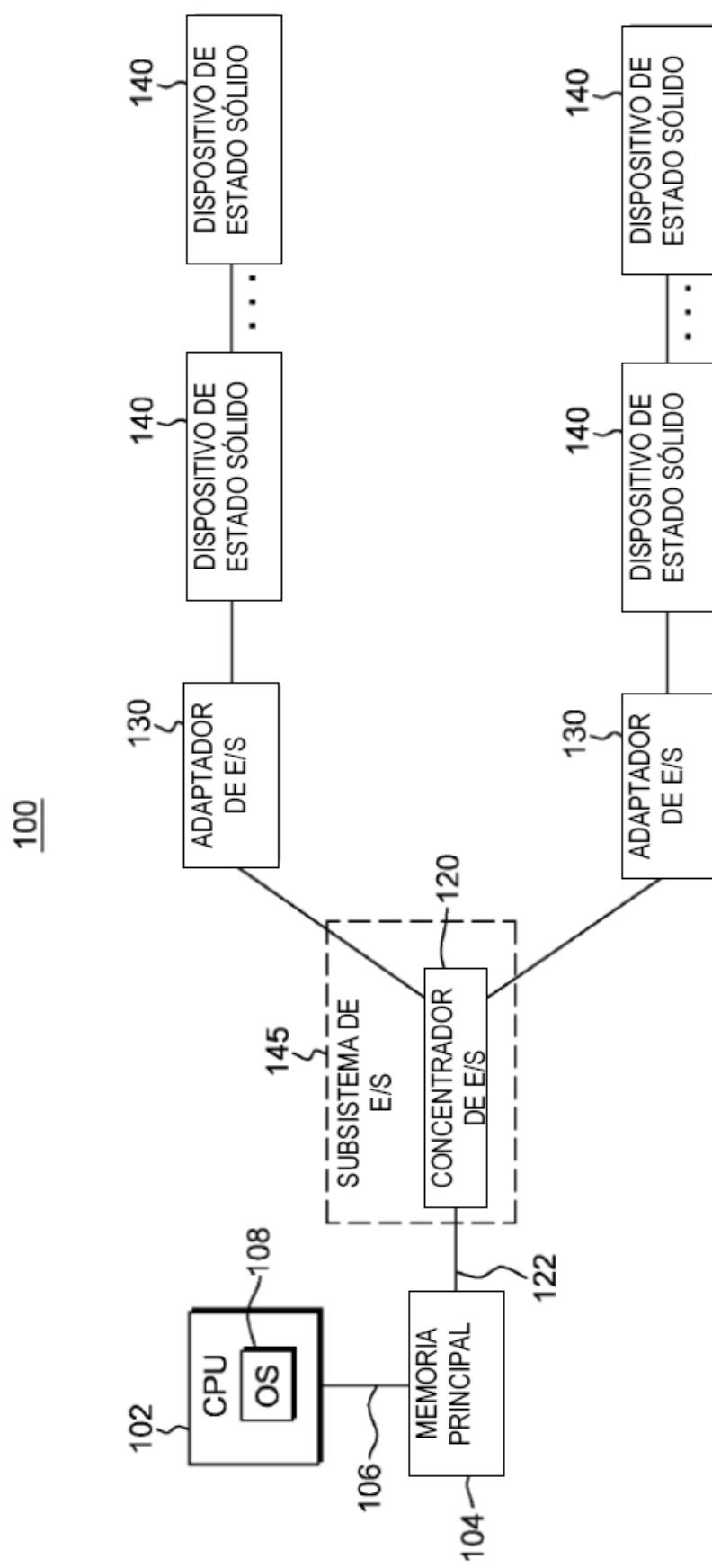

la figura 1A representa una realización de un entorno informático para incorporar y utilizar uno o más aspectos de la presente invención;

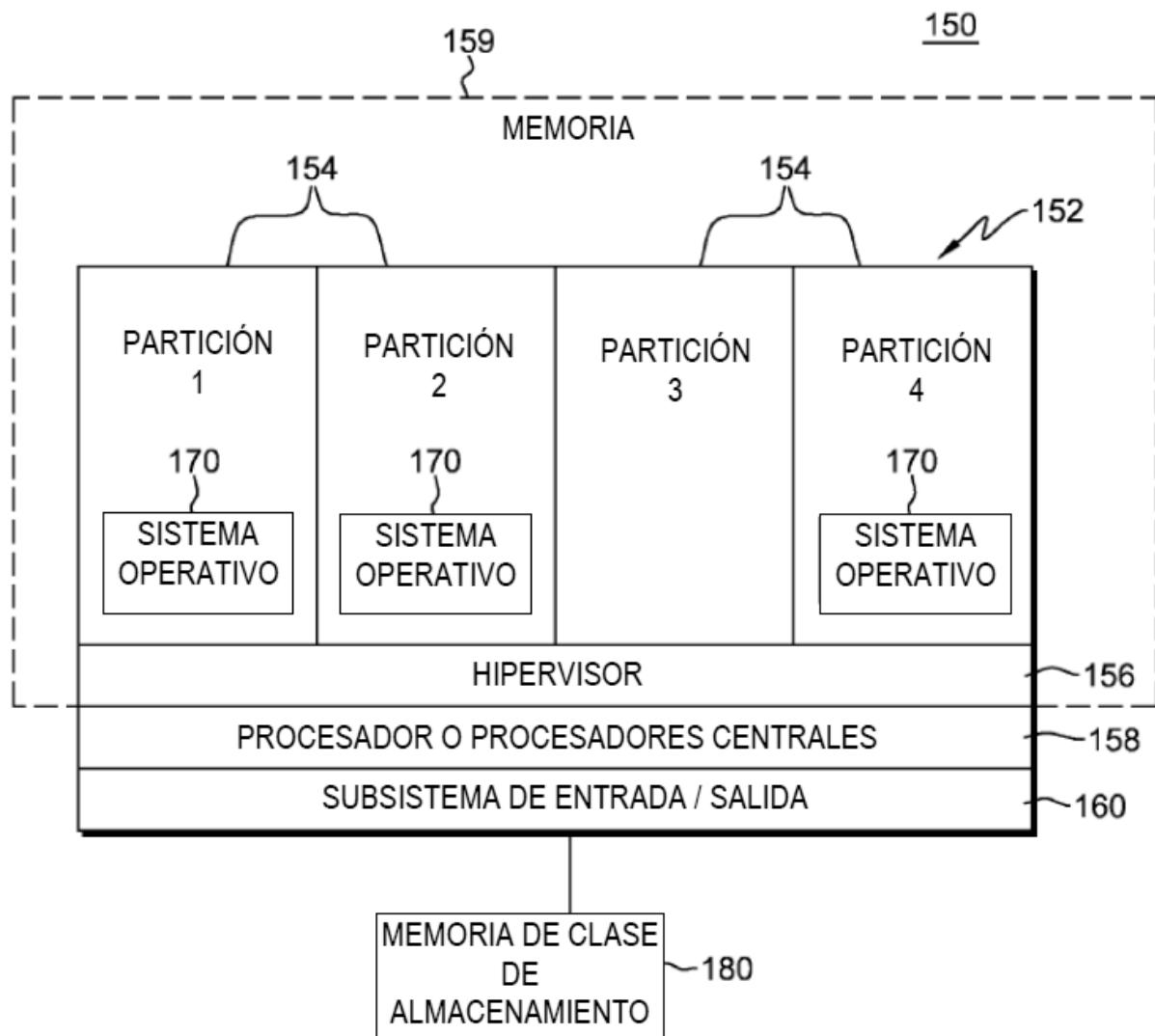

figura 1B representa otra realización de un entorno informático para incorporar y utilizar uno o más aspectos de la presente invención;

la figura 2A representa una realización de un bloque de solicitud de operación de trasladador de datos asíncronos extendidos utilizado, de acuerdo con un aspecto de la presente invención;

la figura 2B representa una realización de un bloque de operación de trasladador de datos asíncronos extendidos utilizado, de acuerdo con un aspecto de la presente invención;

la figura 2C representa una realización de un bloque de solicitud de trasladador de datos asíncronos extendidos utilizado, de acuerdo con un aspecto de la presente invención;

la figura 2D representa una realización de un bloque de respuesta de trasladador de datos asíncronos extendidos utilizado, de acuerdo con un aspecto de la presente invención;

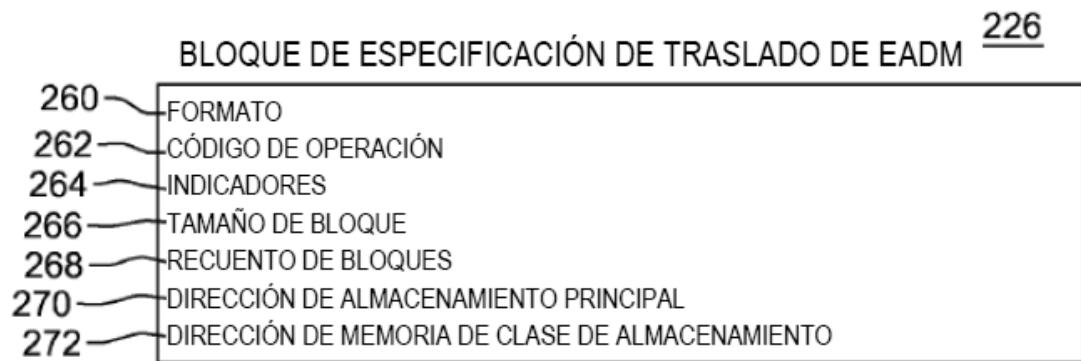

la figura 2E representa una realización de un bloque de especificación del trasladado del trasladador de datos asíncronos extendidos utilizado, de acuerdo con un aspecto de la presente invención;

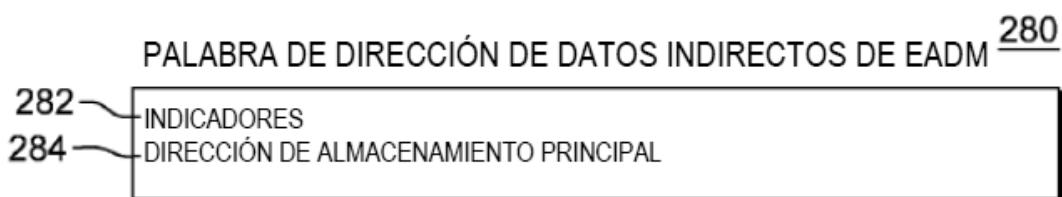

la figura 2F representa una realización de una palabra de dirección de datos indirectos de trasladador de datos asíncronos extendidos utilizada, de acuerdo con un aspecto de la presente invención;

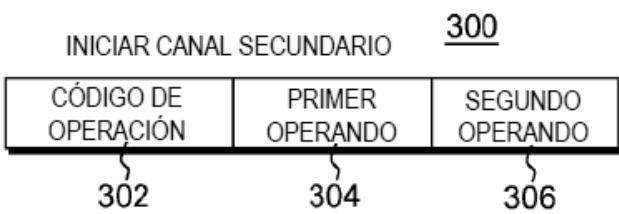

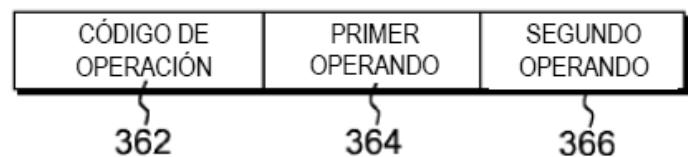

- la figura 3A representa una realización de una instrucción de Iniciar el canal secundario utilizada, de acuerdo con un aspecto de la presente invención;

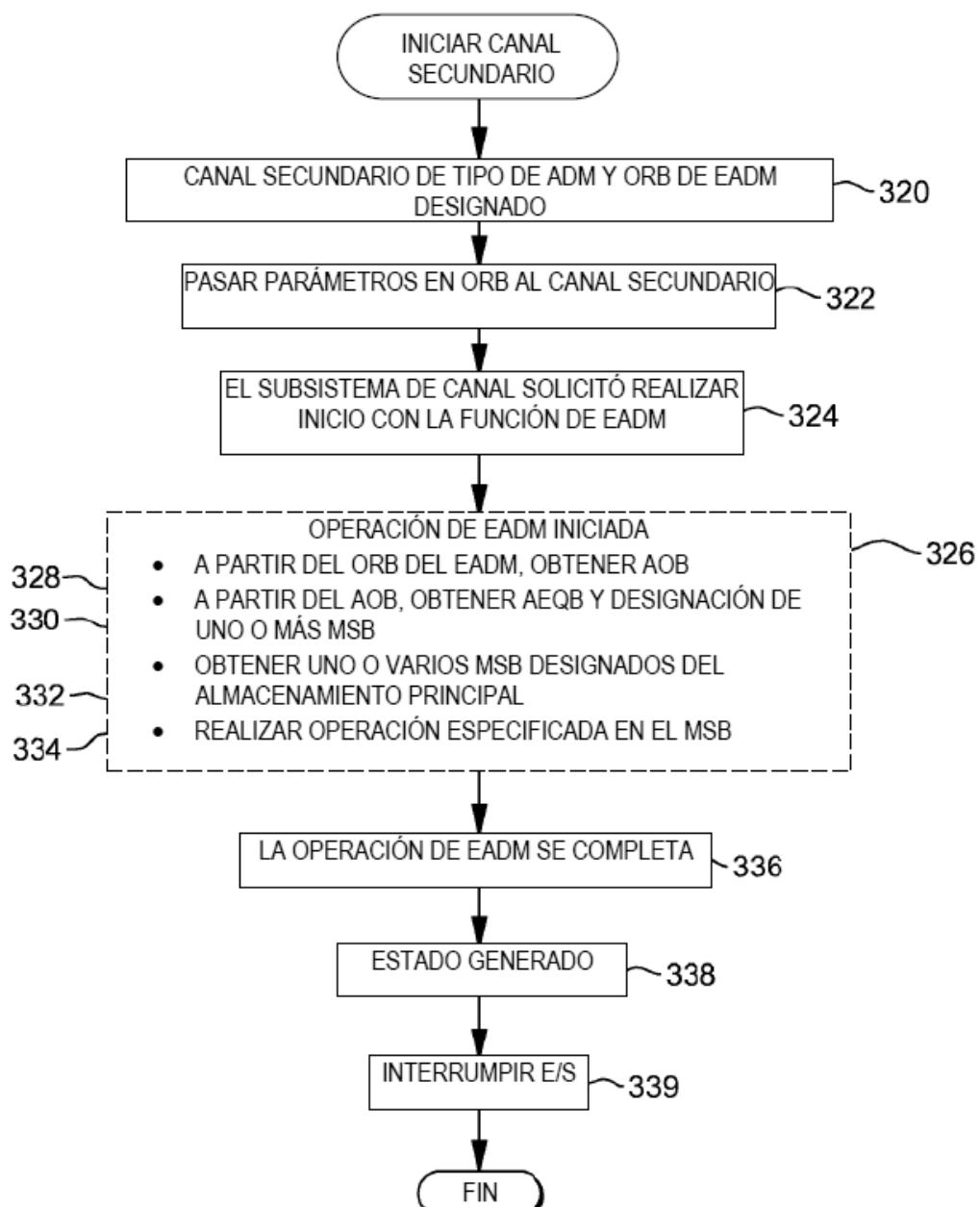

- la figura 3B representa una realización de la lógica asociada con la instrucción de Iniciar el canal secundario, de acuerdo con un aspecto de la presente invención;

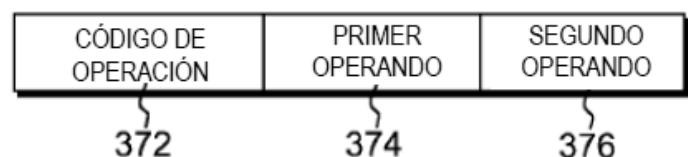

- 5 la figura 3C representa una realización de una instrucción de Borrar el canal secundario utilizada, de acuerdo con un aspecto de la presente invención;

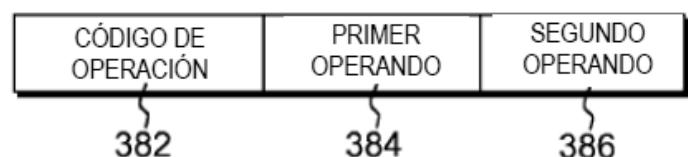

- la figura 3D representa una realización de una instrucción de Probar el canal secundario utilizada, de acuerdo con un aspecto de la presente invención;

- 10 10 la figura 3E representa una realización de una instrucción de Modificar el canal secundario utilizada, de acuerdo con un aspecto de la presente invención;

- la figura 3F representa una realización de una instrucción de Almacenar el canal secundario utilizada, de acuerdo con un aspecto de la presente invención;

- la figura 4A representa una realización de un bloque de información del canal secundario del trasladador de datos asíncronos extendidos utilizado, de acuerdo con un aspecto de la presente invención;

- 15 15 la figura 4B representa una realización de una palabra de control de gestión de la ruta del trasladador de datos asíncronos extendidos utilizada, de acuerdo con un aspecto de la presente invención;

- la figura 4C representa una realización de una palabra de estado del canal secundario utilizada, de acuerdo con un aspecto de la presente invención;

- 20 20 la figura 4D representa una realización de una palabra de estado extendida del trasladador de datos asíncronos extendidos utilizada, de acuerdo con un aspecto de la presente invención;

- la figura 5A representa una realización de un bloque de solicitud de Almacenar la información de la memoria de clase de almacenamiento utilizada, de acuerdo con un aspecto de la presente invención;

- la figura 5B representa una realización de un bloque de respuesta a Almacenar la información de la memoria de clase de almacenamiento utilizada, de acuerdo con un aspecto de la presente invención;

- 25 25 la figura 5C representa una realización de una entrada de la lista de direcciones de la memoria de clase de almacenamiento utilizada, de acuerdo con un aspecto de la presente invención;

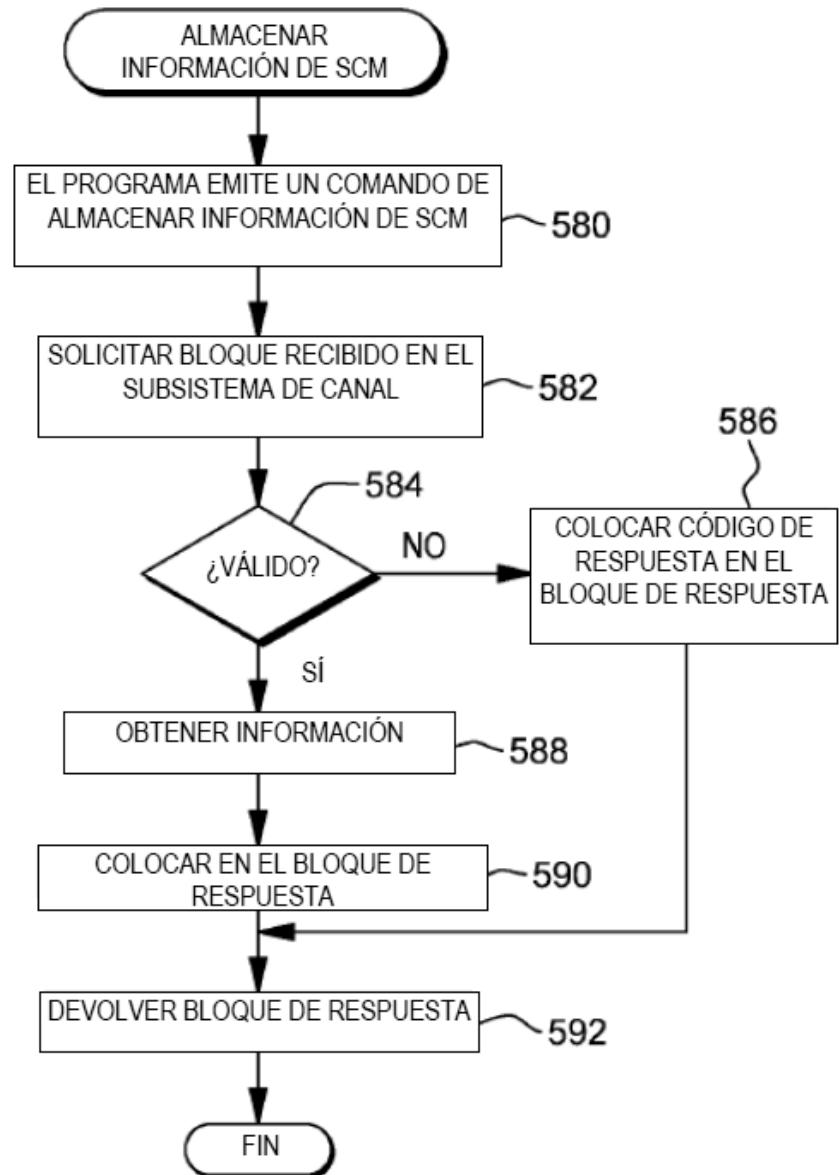

- la figura 5D representa una realización de la lógica asociada con el comando Almacenar información de la memoria de clase de almacenamiento, de acuerdo con un aspecto de la presente invención;

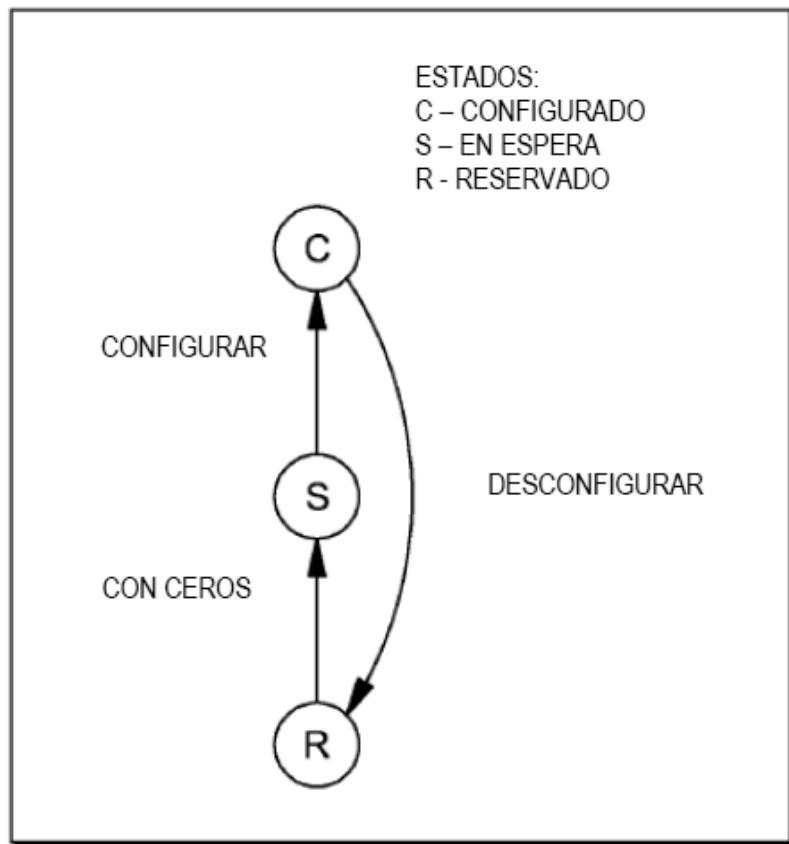

- 30 30 la figura 6A representa un ejemplo de un diagrama de estado que representa varios estados de la memoria de clase de almacenamiento, de acuerdo con un aspecto de la presente invención;

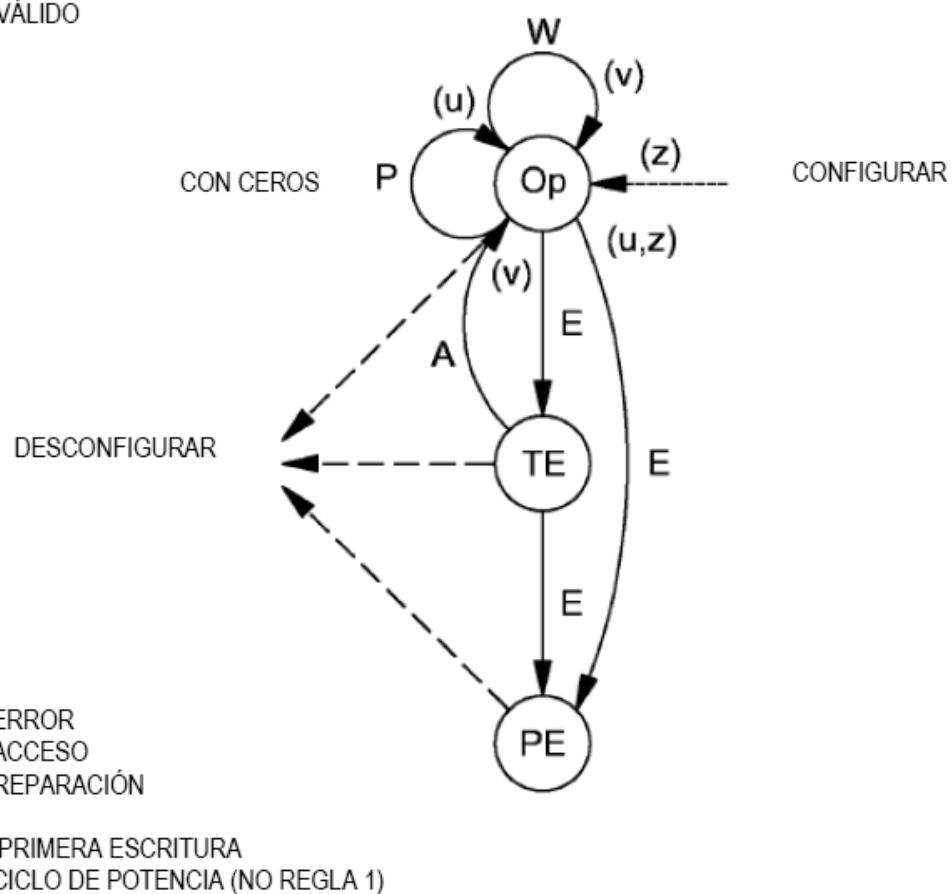

- la figura 6B representa una realización de un diagrama de estado que muestra estados de operación y estados de datos, de acuerdo con un aspecto de la presente invención;

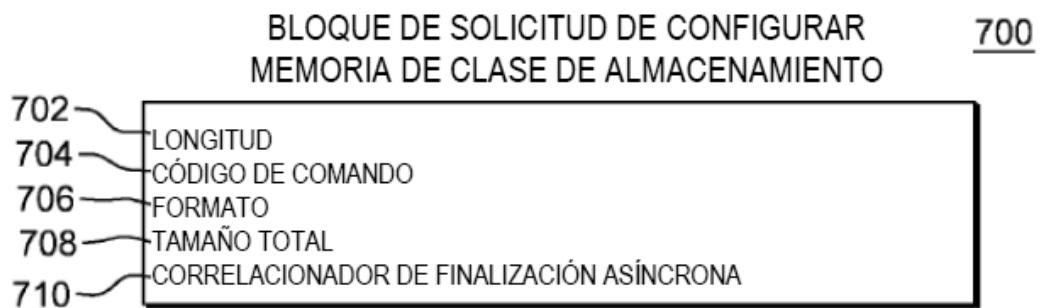

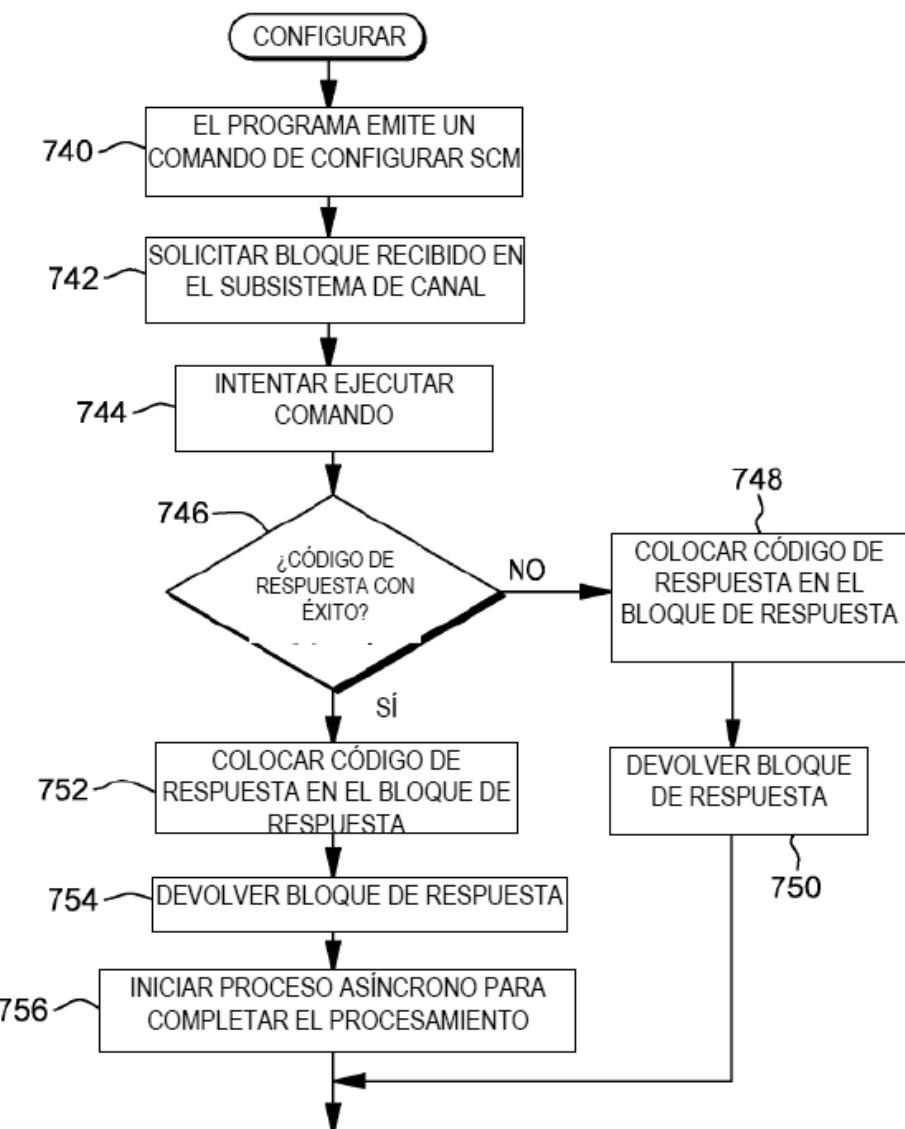

- la figura 7A representa una realización de un bloque de solicitud de Configurar la memoria de clase de almacenamiento utilizado, de acuerdo con un aspecto de la presente invención;

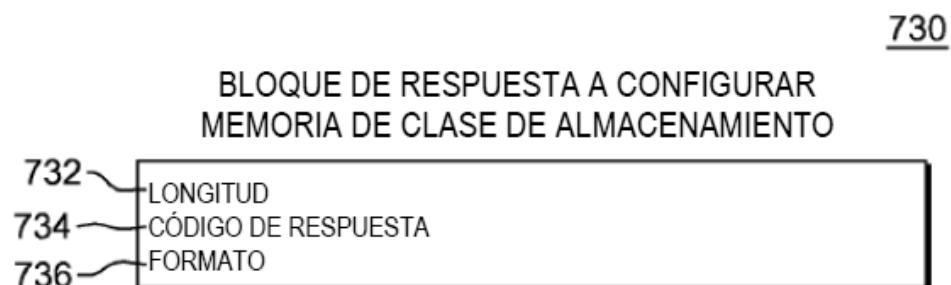

- 35 35 la figura 7B representa una realización de un bloque de respuesta a Configurar la memoria de clase de almacenamiento utilizado, de acuerdo con un aspecto de la presente invención;

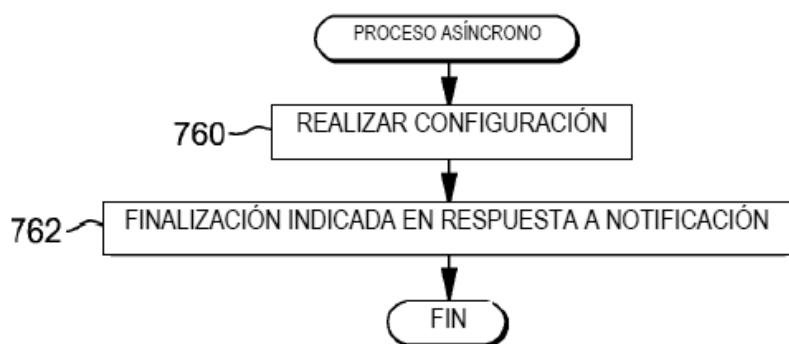

- las figuras 7C a 7D representan una realización de la lógica asociada con un comando de Configurar la memoria de clase de almacenamiento utilizada, de acuerdo con un aspecto de la presente invención;

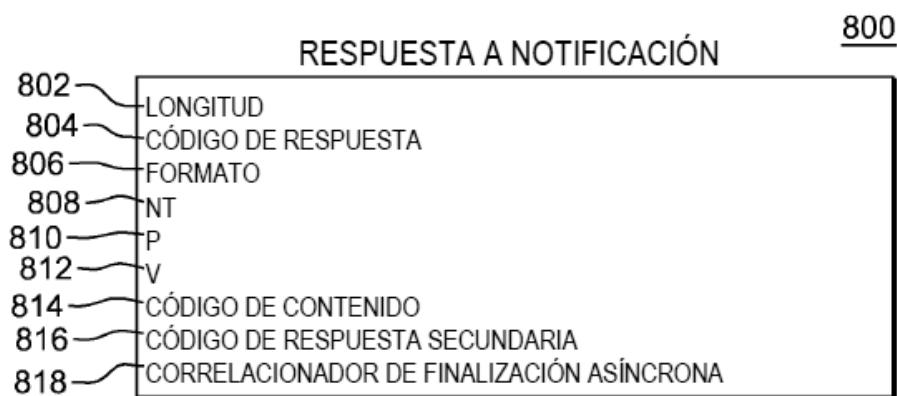

- 40 40 la figura 8A representa un ejemplo de un bloque de respuesta de notificación utilizado, de acuerdo con un aspecto de la presente invención;

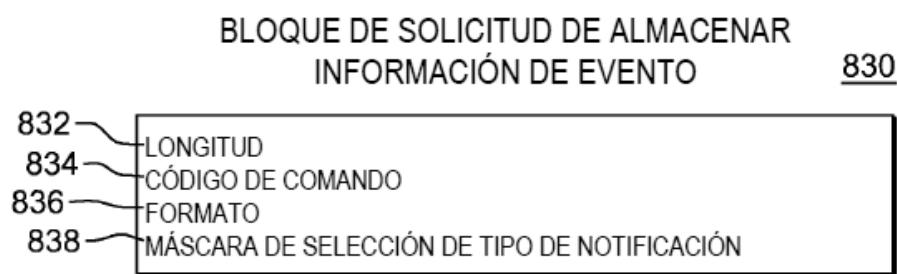

- la figura 8B representa una realización de un bloque de solicitud de Almacenar la información de un evento utilizado, de acuerdo con un aspecto de la presente invención;

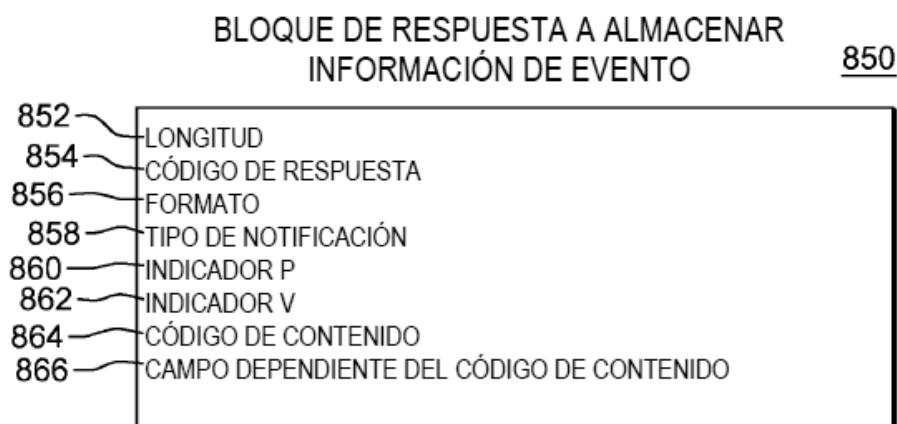

- la figura 8C representa una realización de un bloque de respuesta a Almacenar la información de un evento utilizado de acuerdo con un aspecto de la presente invención;

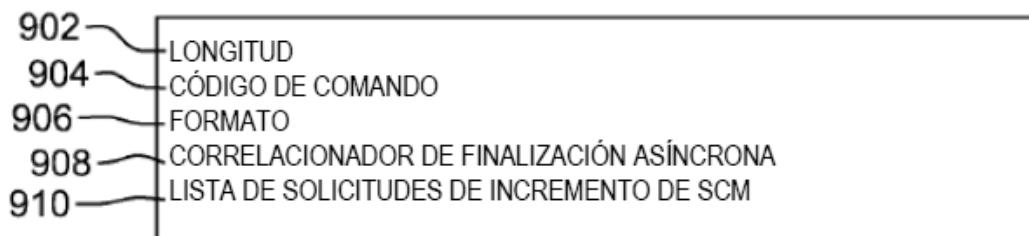

- 45 45 la figura 9A representa una realización de un bloque de solicitud de Desconfigurar la memoria de clase de almacenamiento utilizado, de acuerdo con un aspecto de la presente invención;

la figura 9B representa una realización de una entrada de la lista de solicitudes de Incrementar la memoria de clase de almacenamiento utilizada, de acuerdo con un aspecto de la presente invención;

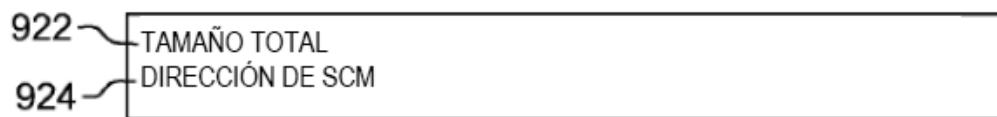

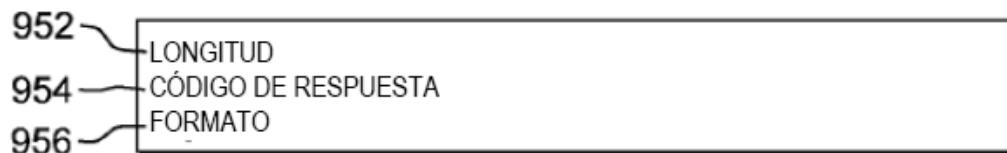

la figura 9C representa una realización de un bloque de respuesta a Desconfigurar la memoria de clase de almacenamiento utilizado, de acuerdo con un aspecto de la presente invención;

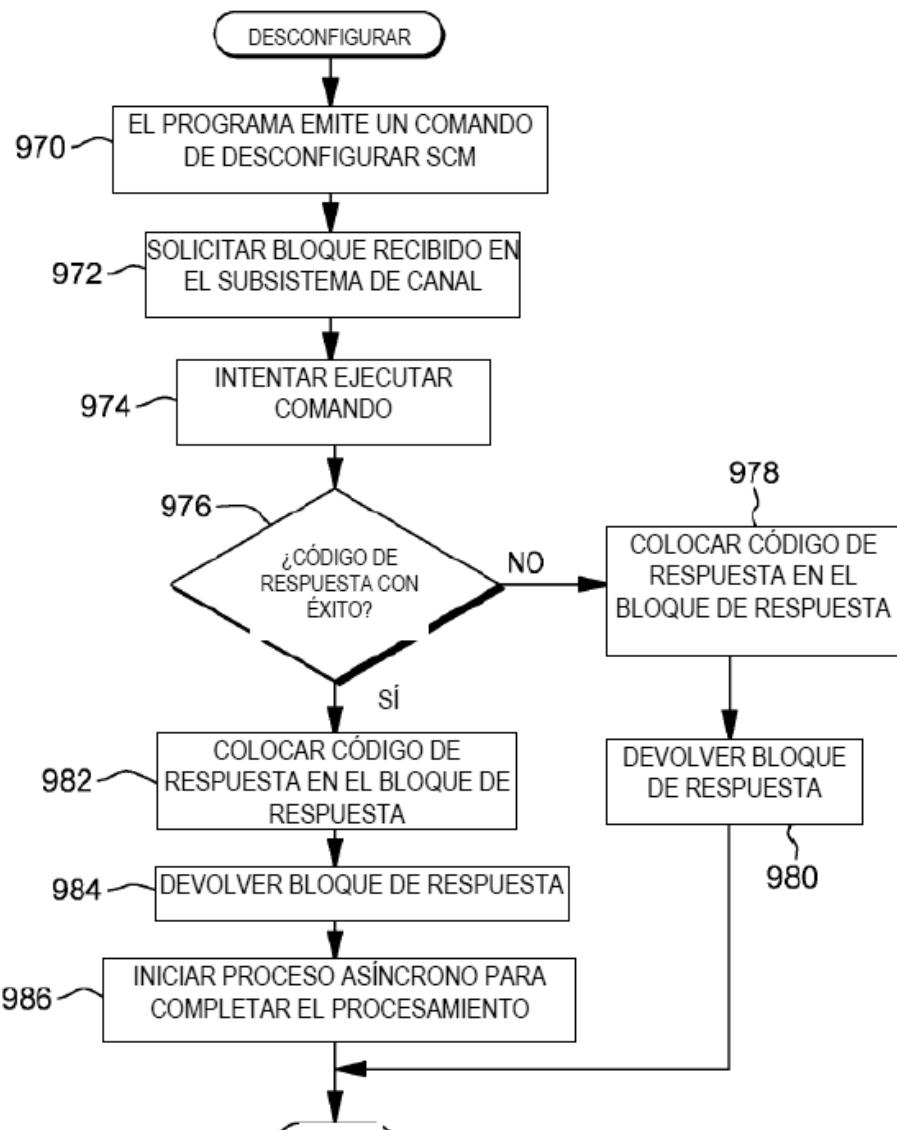

5 las figuras 9D a 9E representan una realización de la lógica asociada con un comando de Desconfigurar la memoria de clase de almacenamiento utilizada, de acuerdo con un aspecto de la presente invención;

la figura 10 representa una realización de un producto de programa informático que incorpora uno o más aspectos de la presente invención;

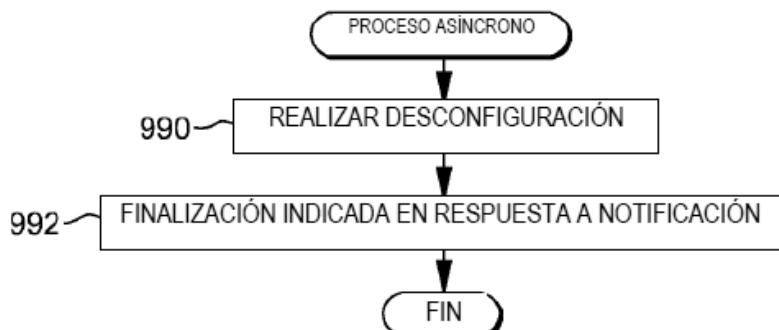

10 la figura 11 representa una realización de un sistema informático anfitrión para incorporar y utilizar uno o más aspectos de la presente invención;

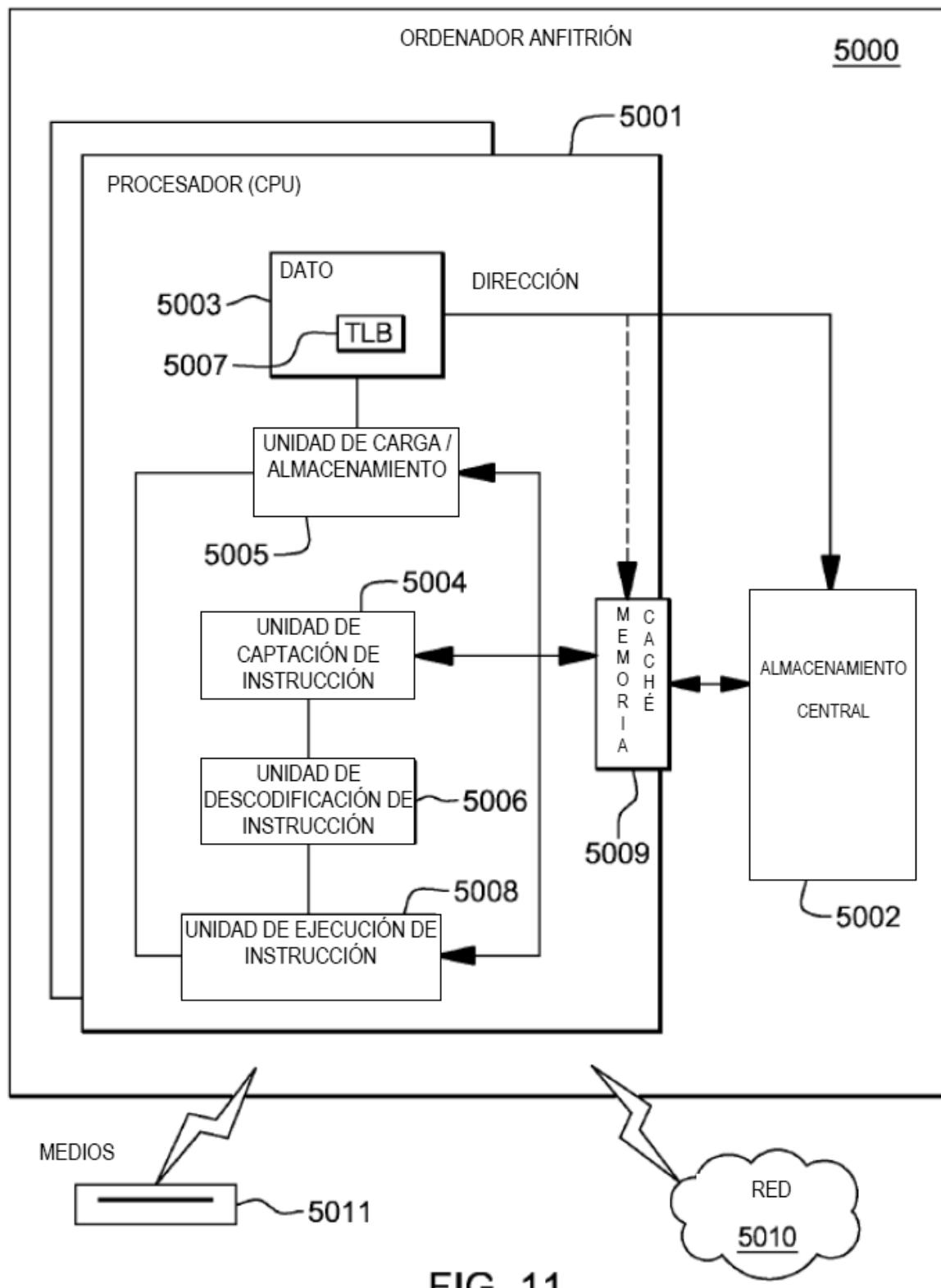

la figura 12 representa otro ejemplo de un sistema informático para incorporar y utilizar uno o más aspectos de la presente invención;

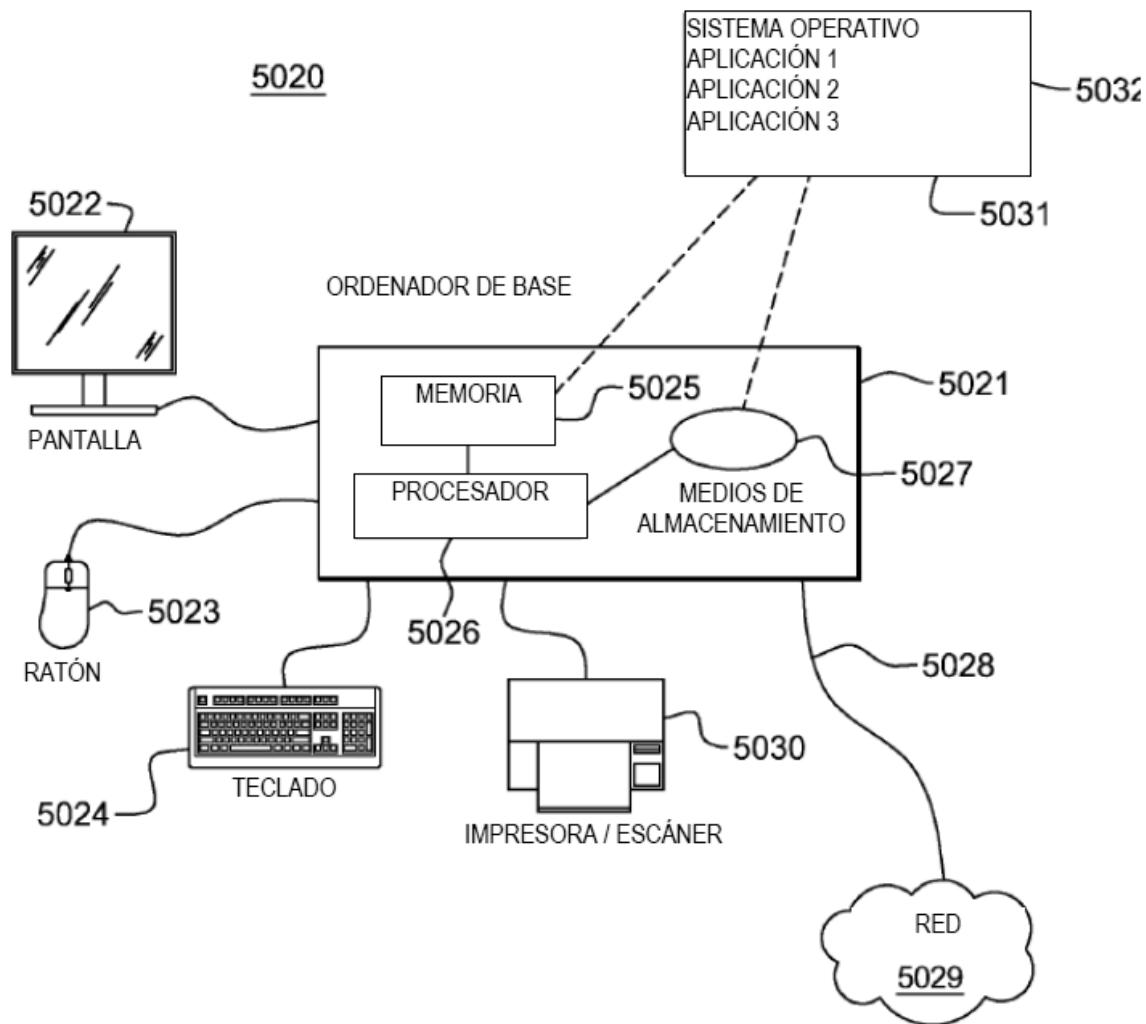

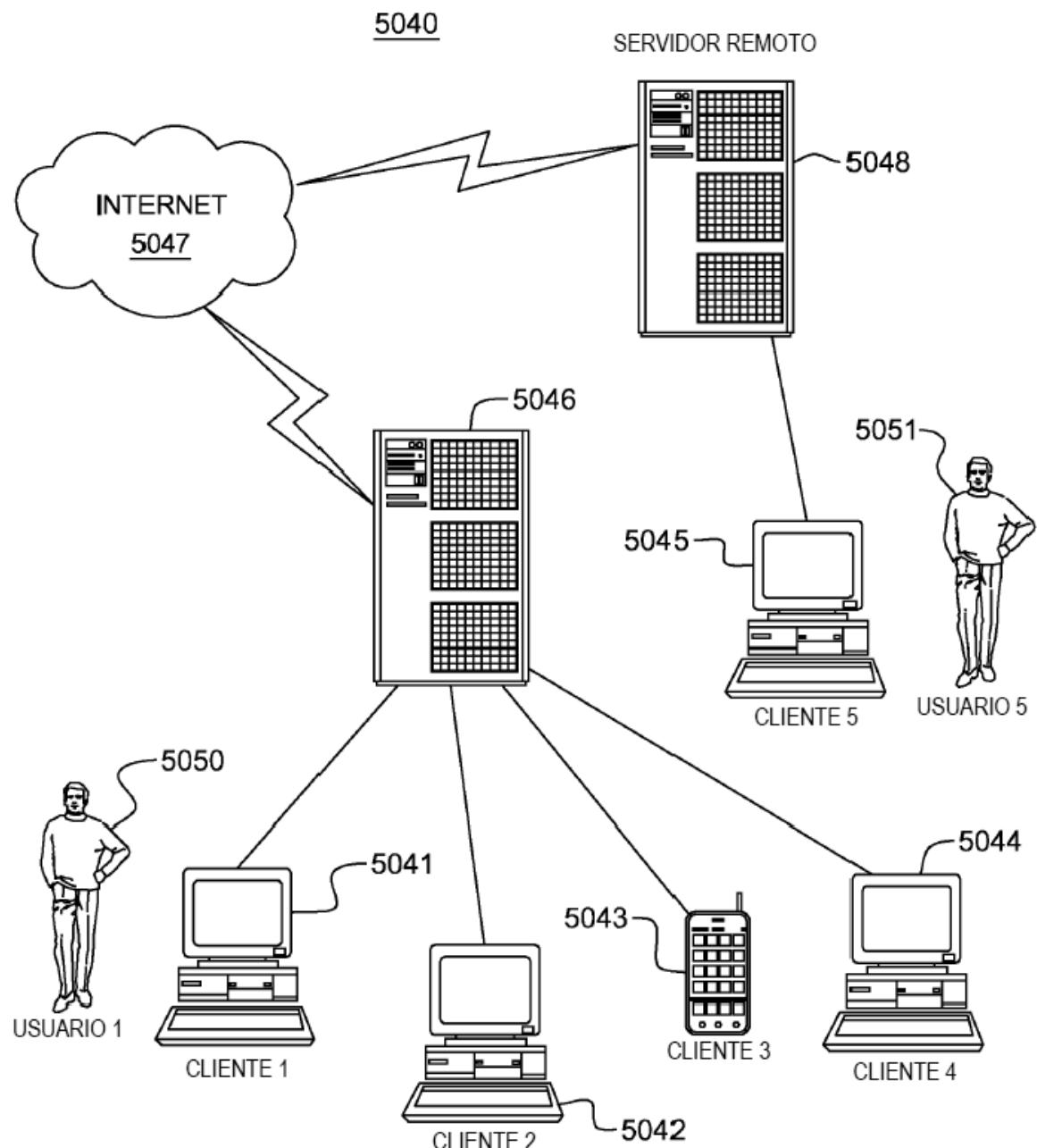

la figura 13 representa otro ejemplo de un sistema informático que comprende una red informática para incorporar y utilizar uno o más aspectos de la presente invención;

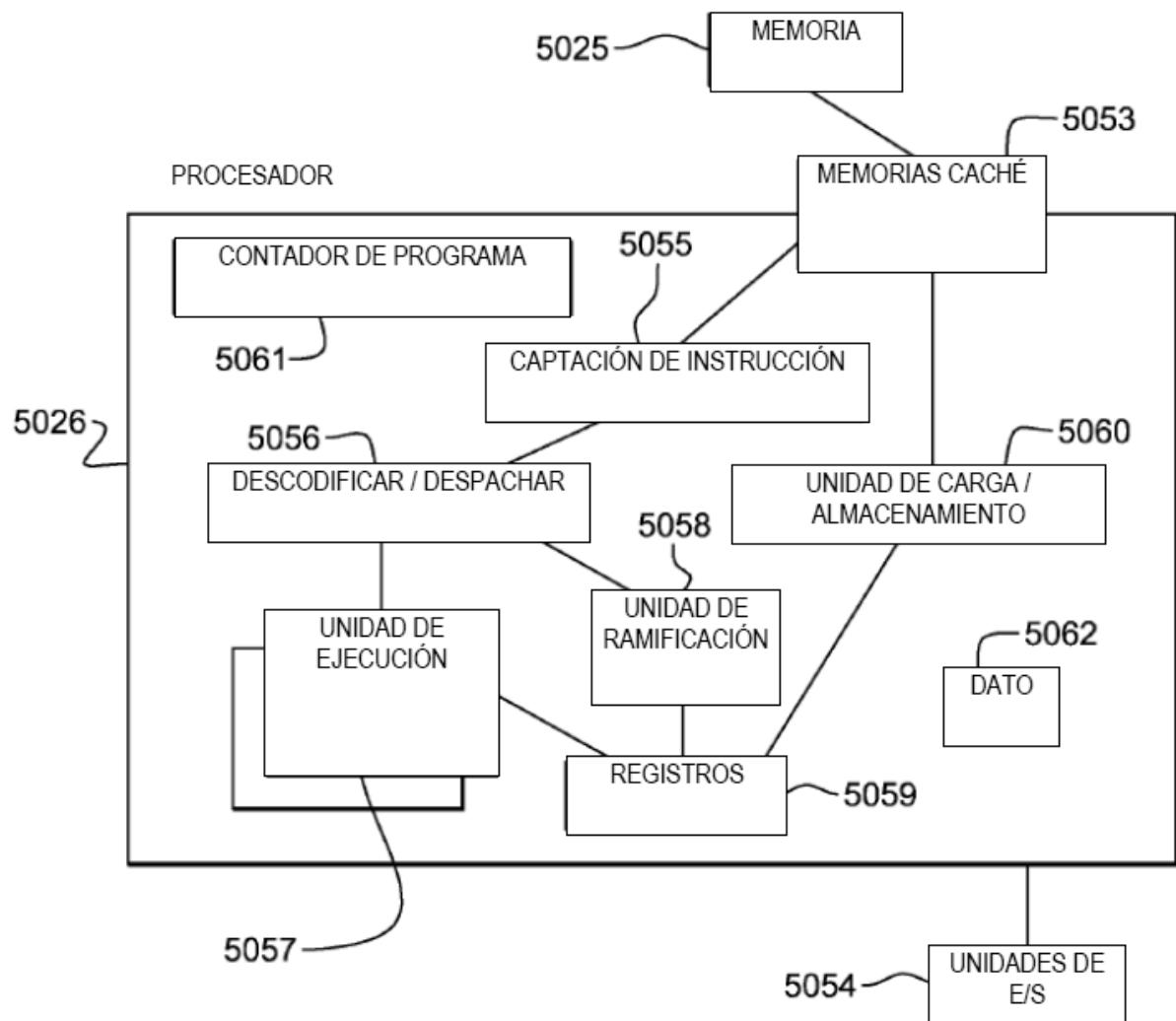

15 la figura 14 representa una realización de diversos elementos de un sistema informático para incorporar y utilizar uno o más aspectos de la presente invención;

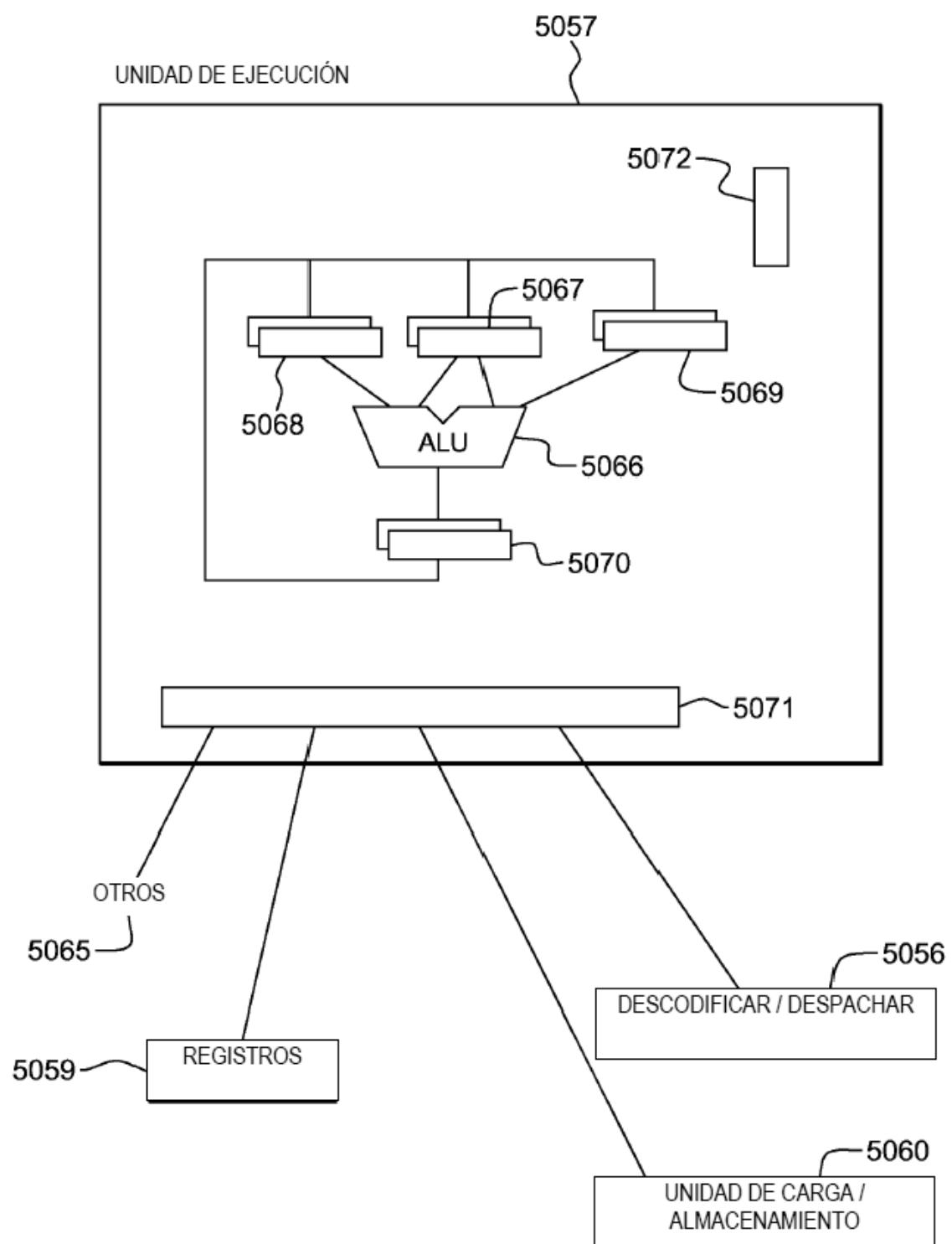

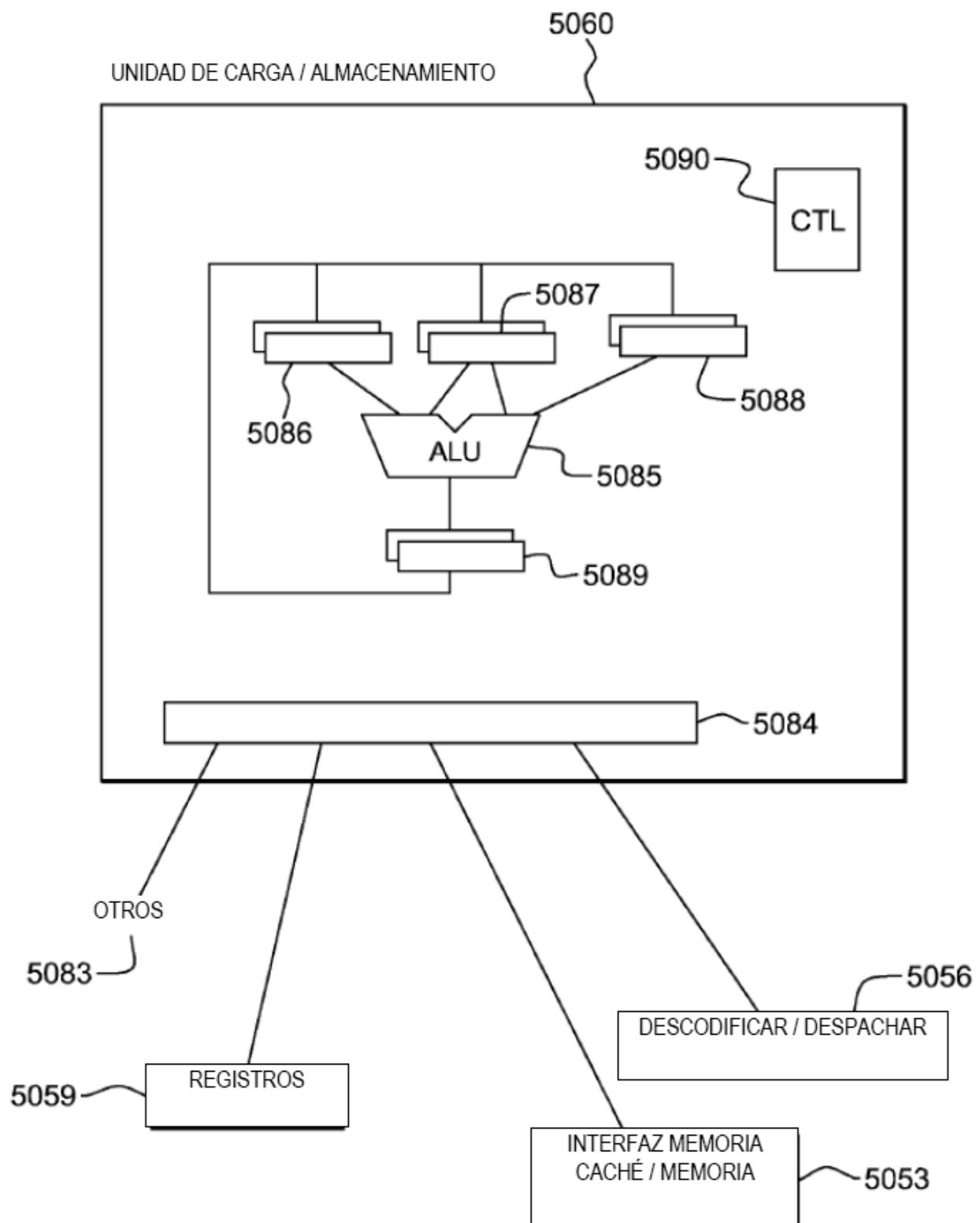

la figura 15A representa una realización de la unidad de ejecución del sistema informático de la figura 14 para incorporar y utilizar uno o más aspectos de la presente invención;

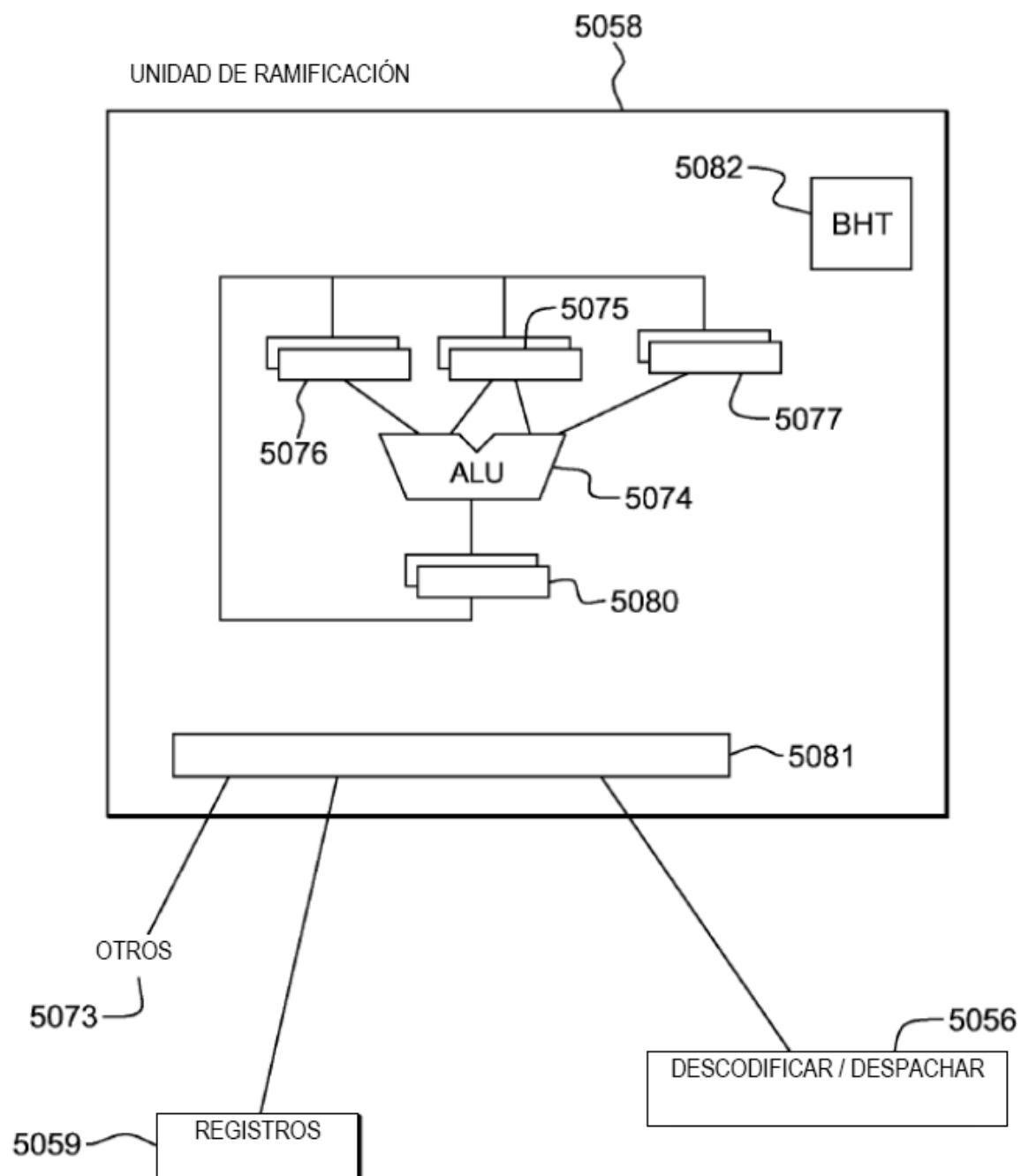

20 la figura 15B representa una realización de la unidad de bifurcación del sistema informático de la figura 14 para incorporar y utilizar uno o más aspectos de la presente invención;

la figura 15C representa una realización de la unidad de carga / almacenamiento del sistema informático de la figura 14 para incorporar y utilizar uno o más aspectos de la presente invención; y

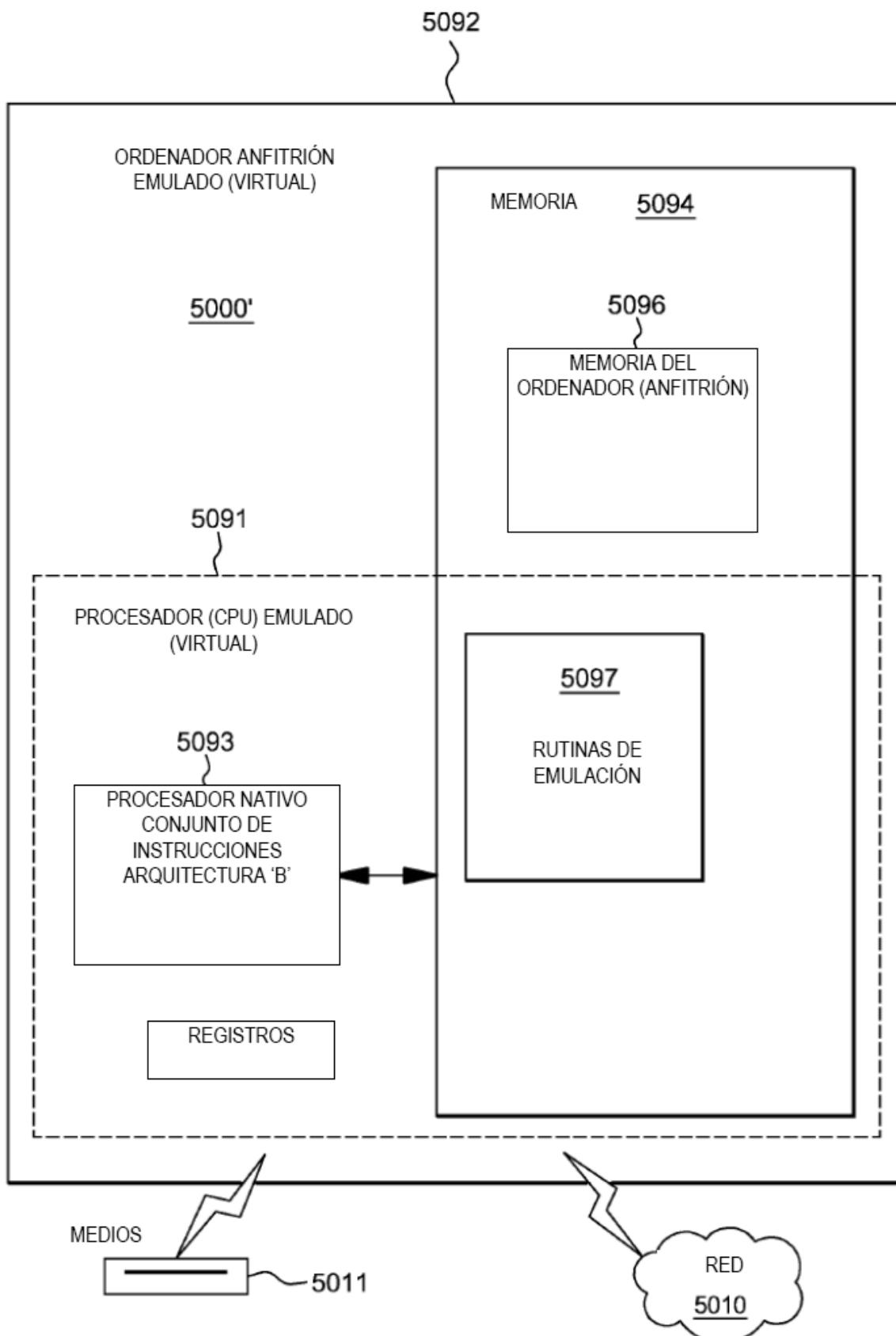

la figura 16 representa una realización de un sistema informático anfitrión emulado para incorporar y utilizar uno o más aspectos de la presente invención.

## 25 **Descripción detallada**

De acuerdo con una o más realizaciones, se proporciona una abstracción para la memoria de clase de almacenamiento que oculta los detalles de la implementación de la memoria de clase de almacenamiento desde un programa (por ejemplo, el sistema operativo) y proporciona una interfaz estándar de programación de canal para realizar ciertas acciones, tales como controlar el traslado de los datos entre el almacenamiento principal y la memoria de clase de almacenamiento.

En un ejemplo, se proporciona una función, denominada función de trasladador de datos asíncronos extendidos (EADM – Extended Asynchronous Data Mover, en inglés), que permite a los programas solicitar la transferencia de bloques de datos entre el almacenamiento principal y la memoria de clase de almacenamiento, así como solicitar otras operaciones. Los aspectos de esta función se describen en detalle a continuación.

35 Además, asociada con la función de EADM existe una función opcional denominada función de liberación de EADM. Cuando está instalada, la función de liberación de EADM proporciona un medio para que el programa especifique que ya no requiere la retención de los datos en uno o más bloques de la memoria de clase de almacenamiento. Depende del modelo si la operación de liberación está soportada por todos los bloques de la memoria de clase de almacenamiento o solo por un subconjunto de la memoria de clase de almacenamiento.

40 Una vez que se ha liberado un bloque de la memoria de clase de almacenamiento, el programa puede transferir nuevos datos al bloque, de lo contrario, las solicitudes subsiguientes para transferir datos del bloque al almacenamiento principal no tendrán éxito.

Una realización de un entorno informático para incorporar y/o utilizar uno o varios aspectos de la presente invención se describe haciendo referencia a la figura 1A. El entorno informático 100 está basado, por ejemplo, en la z / Architecture® comercializada por la firma International Business Machines Corporation (IBM®), Armonk, Nueva York. Una realización de la z / Architecture® se describe en una publicación de IBM® titulada "z / Architecture Principles of Operation", publicación de IBM N° SA22-7832-08, agosto de 2010.

En un ejemplo, un entorno informático basado en la z / Architecture® incluye el sistema zEnterprise 196 (z196) comercializado por la firma International Business Machines Corporation. IBM® y z / Architecture® son marcas comerciales registradas, y zEnterprise 196 y z196 son marcas comerciales de International Business Machines

Corporation, Armonk, Nueva York, U.S.A. Otros nombres aquí utilizados pueden ser marcas registradas, marcas comerciales o nombres de productos comercializados por la firma International Business Machines Corporation o por otras compañías.

5 Como ejemplo, el entorno informático 100 incluye una o más unidades centrales de procesamiento 102 acopladas a la memoria principal 104 a través de uno o más buses 106. Una o más de las unidades centrales de procesamiento pueden ejecutar un sistema operativo 108, como el sistema operativo z/OS® comercializado por la firma International Business Machines Corporation. En otros ejemplos, una o más de las unidades centrales de procesamiento pueden ejecutar otros sistemas operativos o ningún sistema operativo. z/OS® es una marca registrada comercializada por la firma International Business Machines Corporation, Armonk, Nueva York, U.S.A.

10 Las unidades centrales de procesamiento 102 y la memoria principal 104 se pueden acoplar adicionalmente a un concentrador de E/S 120 a través de una o más conexiones 122 (por ejemplo, buses u otras conexiones). El concentrador de E/S proporciona conectividad a uno o más adaptadores de E/S 130, que se acoplan además a uno o más dispositivos de estado sólido 140. Los adaptadores y dispositivos de estado sólido son una implementación de la memoria de clase de almacenamiento (por ejemplo, una memoria rápida (flash, en inglés). El concentrador de E/S forma parte de un subsistema de E/S 145 que facilita uno o más aspectos de una realización.

15 En otra realización, tal como se representa en la figura 1B, un entorno informático 150 puede incluir un complejo de procesamiento central (CPC – Central Processing Complex, en inglés) 152, que se basa en la z / Architecture® comercializado por la firma International Business Machines Corporation. El complejo de procesamiento central 152 incluye, por ejemplo, una o más particiones 154, un hipervisor 156, uno o más procesadores centrales 158 y uno o más componentes de un subsistema de entrada / salida 160. En este ejemplo, las particiones 154 son particiones lógicas (por ejemplo, LPAR), cada una de las cuales incluye un conjunto de recursos de hardware del sistema, virtualizado como un sistema separado.

20 Cada partición lógica 154 es capaz de funcionar como un sistema separado. Es decir, cada partición lógica se puede restablecer de manera independiente, se puede cargar inicialmente con un sistema operativo u otro código de control, si se desea, y operar con diferentes programas. Un sistema operativo o programa de aplicación que se ejecuta en una partición lógica parece tener acceso a un sistema global y completo, pero en realidad, solo una parte está disponible. Una combinación de hardware y de código interno bajo licencia (LIC – Licensed Internal Code, en inglés), conocido como firmware, evita que un programa en una partición lógica interfiera con un programa en una partición lógica diferente. Esto permite que varias particiones lógicas diferentes operen en uno o varios procesadores físicos en forma de intervalo de tiempo. Tal como se utiliza en este documento, el firmware incluye, por ejemplo, el microcódigo, el milicódigo y/o el macrocódigo del procesador (o entidad que realiza el procesamiento). Incluye, por ejemplo, las instrucciones de nivel a hardware y/o las estructuras de datos utilizadas en la implementación del código de máquina de nivel superior. En una realización, incluye, por ejemplo, un código propietario que, típicamente, se entrega como un microcódigo que incluye un software fiable o un microcódigo especificado para el hardware subyacente y controla el acceso del sistema operativo al hardware del sistema.

25 En este ejemplo, varias de las particiones lógicas tienen un sistema operativo (OS – Operating System, en inglés) 170 residente, que puede diferir para una o más particiones lógicas. En una realización, por lo menos una partición lógica está ejecutando el sistema operativo z/OS®, comercializado por la firma International Business Machines Corporation, Armonk, Nueva York.

30 40 Las particiones lógicas 154 son administradas por el hipervisor 156, que se implementa mediante un software que se ejecuta en los procesadores centrales 158. Las particiones lógicas 154 y el hipervisor 156 incluyen cada uno de los programas que residen en las porciones respectivas de la memoria principal 159 asociadas con los procesadores centrales. Un ejemplo de hipervisor 156 es el gestor de recursos y sistemas del procesador (PR/SM™ - Processor Resource / Systems Manager, en inglés), comercializado por la firma International Business Machines Corporation, Armonk, Nueva York.

45 50 Los procesadores centrales 158 son recursos físicos del procesador que están asignados a las particiones lógicas. Por ejemplo, una partición lógica 154 incluye uno o más procesadores lógicos, cada uno de los cuales representa todo o un recurso compartido de un recurso de procesador físico 158 asignado a la partición. Los procesadores lógicos de una partición particular 154 pueden estar dedicados a la partición, de tal modo que el recurso del procesador subyacente está reservado para esa partición; o compartido con otra partición, de tal modo que el recurso del procesador subyacente esté potencialmente disponible para otra partición.

55 El subsistema de entrada / salida 160 (del cual solo está representada una parte) proporciona conectividad a la memoria de clase de almacenamiento 180. En este ejemplo, se proporciona un espacio de direcciones para la memoria de clase de almacenamiento que presenta la memoria como plana, ocultando los detalles de la implementación física del programa. Como ejemplo, existe un espacio de direcciones en todo el sistema para la memoria de clase de almacenamiento, pero desde la vista de una configuración (por ejemplo, LPAR o en otra realización, un huésped virtualizado) existe un espacio de direcciones en el que los incrementos de la memoria de clase de almacenamiento son llenados para cada configuración del sistema. El espacio de direcciones de la

memoria de clase de almacenamiento está separado y aparte del espacio de direcciones de almacenamiento principal.

En un ejemplo particular de z / Architecture®, el subsistema de E/S incluye un subsistema de canal, que no solo dirige el flujo de información entre las unidades (y dispositivos) de control periférico de E/S y la memoria principal, sino también entre la memoria de clase de almacenamiento y la memoria principal. Sin embargo, el subsistema de E/S puede ser distinto de un subsistema de canal.

En el caso de un subsistema de canal, los canales secundarios se utilizan para realizar operaciones de EADM. Estos canales secundarios se denominan canales secundarios de tipo de transportador de datos asíncrono (ADM - Asynchronous Data Mover, en inglés) y están asociados con operaciones de EADM, y no como dispositivos de E/S, como otros canales secundarios de tipo E/S. Un canal secundario de tipo de ADM no contiene un número de dispositivo, ni contiene información de ruta de canal. El número de canales secundarios de tipo de ADM proporcionados para una configuración depende del modelo. Los canales secundarios de tipo de ADM son direccionados por una palabra de identificación de subsistema (SID – Subsystem Identification Word, en inglés).

Los canales secundarios de tipo de ADM son utilizados por la función del trasladador de datos asíncronos extendidos, que es una extensión del subsistema de canal. Tal como se describe en el presente documento, la función de EADM permite a un programa solicitar la transferencia de bloques de datos entre el almacenamiento principal y la memoria de clase de almacenamiento, así como realizar otras operaciones, tales como borrar un bloque de la memoria de clase de almacenamiento o liberar un bloque de memoria de clase de almacenamiento. En una realización, cuando la función de EADM está instalada:

- 20 • Se proporcionan uno o más canales secundarios de tipo de ADM que se utilizan para las operaciones de EADM.

- 25 • Las operaciones de EADM están designadas por un bloque de operación de EADM (AOB) especificado. El AOB incluye un bloque de solicitud de EADM (ARQB – EADM ReQuest Block, en inglés) y un bloque de respuesta de EADM (ARSB – EADM Response Block, en inglés), y designa una lista de bloques de especificación de traslado de EADM (MSB). Para una operación de traslado, los MSB contienen información acerca de los bloques de datos que se moverán, tal como el tamaño de los bloques, las ubicaciones de origen y destino de los bloques y la dirección del traslado de los datos.

- 30 • El número máximo de MSB que puede especificar un AOB depende del modelo. El recuento máximo de bloques que un MSB puede especificar para ser movido u operado también depende del modelo.

- 35 • Un programa inicia las operaciones de EADM emitiendo una instrucción de Iniciar el canal secundario que designa un canal secundario de tipo de ADM y un bloque de solicitud de operación de EADM (ORB). A su vez, el ORB de EADM designa un AOB. La instrucción pasa los contenidos del ORB de EADM al canal secundario designado.

- 40 • Cuando se emite una instrucción de Iniciar el canal secundario para iniciar operaciones de EADM, el subsistema de canal realiza de manera asíncrona la operación especificada.

- 45 • De acuerdo con lo observado por el programa, la memoria de clase de almacenamiento parece ser de bloques coincidentes en un tamaño de bloque mínimo que depende del modelo. Este valor que depende del modelo se denomina tamaño de coincidencia del bloque de SCM.

- 50 • Cuando se completan las operaciones de EADM, se produce una interrupción de E/S en espera del programa para el canal secundario de tipo de ADM en el que se iniciaron las operaciones.

El ORB de EADM incluye la especificación de una clave de canal secundario y la dirección del AOB que se utilizará. El AOB se designa, por ejemplo, en un límite de 4 Kbytes y puede tener un tamaño de hasta 4 Kbytes. Si se necesitan más MSB que se ajusten a un AOB de 4 Kbytes, el AOB puede especificar una lista de MSB que se extiende a áreas de almacenamiento adicionales mediante la utilización de MSB que designan la dirección del siguiente MSB en la lista, en lugar de designar un área de almacenamiento para ser utilizada para la transferencia de datos.

La primera operación de EADM es iniciada por el subsistema de canal utilizando información en el ORB de EADM designado y el ARQB en el AOB designado para obtener un MSB. El MSB incluye la información que especifica y controla la operación de EADM que se procesará.

50 Cada operación de EADM está representada por un MSB. Un MSB puede especificar, por ejemplo, una transferencia de bloques de datos del almacenamiento principal a la memoria de clase de almacenamiento; una transferencia de bloques de datos desde la memoria de clase de almacenamiento al almacenamiento principal; un borrado de bloques de la memoria de clase de almacenamiento; y la liberación de bloques de la memoria de clase de almacenamiento.

Si los bloques de almacenamiento a transferir no son contiguos en el almacenamiento principal, se puede utilizar un nuevo MSB, o el MSB puede utilizar direccionamiento indirecto especificando una lista de palabras de dirección de datos indirectos de EADM (AIDAW – EADM Indirect Data Address Words, en inglés) para designar los bloques no contiguos.

- 5 Puesto que un MSB especifica la transferencia de datos en una sola dirección, se debe utilizar un nuevo MSB cuando haya un cambio en la dirección de la transferencia.

La finalización de una operación de EADM normalmente está indicada por las situaciones de estado combinadas del fin del canal y del fin del dispositivo. Esta combinación de estados representa la combinación de estados primario y secundario que indica que el canal secundario está disponible para otra función de inicio después de que el estado ha sido borrado.

10 Una operación de EADM puede ser terminada prematuramente mediante una instrucción de Borrar el canal secundario. La ejecución de la instrucción de Borrar el canal secundario termina la ejecución del AOB en el canal secundario, borra el canal secundario de indicaciones del AOB en ejecución y realiza de manera asincrónica la función de borrado.

- 15 Otros detalles relacionados con el ORB de EADM y las estructuras de control relacionadas se describen a continuación haciendo referencia a las figuras 2A a 2F. Inicialmente, haciendo referencia a la figura 2A, se describe una realización de un ORB de EADM.

Como ejemplo, un ORB de EADM 200 incluye:

- 20 Parámetro de Interrupción 202: este campo se conserva sin modificar en el canal secundario hasta que sea reemplazado por una subsiguiente instrucción de Modificar el canal secundario o Iniciar el canal secundario. Estos bits se encuentran en el código de interrupción de E/S cuando se produce una interrupción de E/S para el canal secundario, y cuando una solicitud de interrupción es borrada por la ejecución, por ejemplo, de una instrucción de Probar interrupción pendiente.

- 25 Clave de canal secundario 204: este campo forma la clave de canal secundario para las operaciones de EADM especificadas por el ARQB y se aplica a la obtención del ARQB, a la obtención del MSB, al almacenamiento del ARSB y para acceder al almacenamiento principal para la transferencia de datos. El valor de este campo es un valor definido; de lo contrario, el subsistema de canal reconoce una situación de Comprobación del programa o reconoce una excepción de operando.

- 30 Control de extensión de ORB (X) 205: este campo especifica si el ORB está extendido. Este campo toma un valor especificado cuando se designa un canal secundario de tipo de ADM; de lo contrario, se reconoce una excepción de operando o una situación de Comprobación del programa.

Dirección 206 del bloque de operación de EADM (AOB): este campo especifica una dirección del bloque de operación de EADM (AOB). Si ciertos bits de este campo no incluyen un valor definido, entonces se reconoce una excepción de operando o una situación de Comprobación del programa.

- 35 Si este campo designa una ubicación protegida contra la captura o designa una ubicación fuera de la configuración, la función de inicio no se inicia. En este caso, el canal secundario pasa a estar en estado pendiente con el estado primario, secundario y de alerta.

- 40 Prioridad del subsistema de canal (CSS – Channel SubSystem, en inglés) 208: este campo incluye un número de prioridad del subsistema de canal que es asignado al canal secundario designado y se utiliza para ordenar la selección de canales secundarios de tipo de ADM cuando se debe iniciar una función de inicio para uno o más canales secundarios que están pendientes de inicio.

Prioridad de la memoria de clase de almacenamiento (SCM – Storage Class Memory, en inglés) 210: Este campo incluye un número de prioridad de la memoria de clase de almacenamiento (SCM) que especifica el nivel de prioridad que se aplica a todas las operaciones de EADM asociadas con la función de inicio.

- 45 Dependiendo del modelo si los contenidos del campo de prioridad de SCM son reconocidos por la función de EADM. En los modelos que no reconocen este campo, el contenido del campo está marcado y todas las operaciones de EADM asociadas con la función de inicio tienen asignado un número de prioridad implícito.

- 50 Formato (FMT - ForMaT) 212: Este campo especifica el diseño del ORB. Este campo debe incluir un valor especificado cuando se designa un canal secundario de tipo de ADM; de lo contrario, se reconoce una excepción de operando o se configura un código de situación particular.

El bloque de operación de EADM (AOB) especificado por la dirección del AOB de EADM 206 del ORB de EADM incluye la información utilizada para invocar las operaciones de EADM. Un AOB es asignado, en un ejemplo, en un límite de 4 Kbytes y tiene una longitud variable.

En un ejemplo, tal como se muestra en la figura 2B, un AOB de EADM 220 incluye tres secciones: un bloque de solicitud de EADM (ARQB) 222; un bloque de respuesta de EADM (ARSB) 224; y un área de MSB 226 que contiene hasta un número definido (por ejemplo, 124) de MSB. No obstante, el ARQB puede especificar la utilización de más de los MSB definidos, cuando se utiliza la bifurcación de MSB (es decir, utilizando la rama hacia el siguiente indicador de MSB en el MSB).

5 Una realización de un bloque de solicitud de EADM (ARQB) 222 se describe haciendo referencia a la figura 2C. En un ejemplo, ARQB 222 incluye:

10 Formato (FMT) 230: este campo especifica el diseño de ARQB. El valor de este campo es un valor definido; de lo contrario, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de código de comando en el campo de código de calificador de excepción del ARSB.

15 Código de comando 232: este campo es para especificar el comando de traslado de bloques de EADM; de lo contrario, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error en el código del comando en el campo de código de calificador de excepción del ARSB.

20 Recuento de MSB 234: este campo especifica un recuento de MSB que componen la solicitud de EADM. El número máximo de MSB que se pueden especificar depende del modelo. El valor de este campo debe ser mayor que cero y menor o igual que el valor máximo del recuento de MSB dependiente del modelo; de lo contrario, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de recuento de MSB en el campo del código de calificador de excepción del ARSB.

25 Además del bloque de solicitud de EADM, el ORB de EADM también especifica un bloque de respuesta de EADM (ARSB). El bloque de respuesta de EADM es significativo, en esta realización, solo cuando se reconoce una situación de excepción. Específicamente, un ARSB es significativo solo cuando el estado de alerta está presente en la palabra de estado de canal secundario de EADM (SCSW – SubChannel Status Word, en inglés), la palabra de estado extendida de EADM (ESW – Extended Status Word, en inglés) es significativa, y el bit de bloque de respuesta (R) de EADM almacenado es uno en la palabra de informe extendida de EADM (ERW – Extended Report Word, en inglés), cada uno de los cuales se describe a continuación. Cuando un ARSB no es significativo, el contenido del ARSB en el AOB es impredecible.

Si un programa es almacenado en el ARSB mientras el canal secundario asociado está activo en un canal secundario, se pueden producir resultados impredecibles.

Cuando se almacena un ARSB, la cantidad de datos que se ha transferido, en su caso, es impredecible.

30 Una realización de un bloque de respuesta de EADM se describe haciendo referencia a la figura 2D. En un ejemplo, el ARSB 224 incluye:

35 Formato (FMT) 240: este campo especifica el diseño del ARSB. Cuando se almacena un ARSB, el valor de este campo se almacena como un valor definido.

Indicadores de excepción (EF – Exception Flag, en inglés) 242: cuando se almacena un ARSB, este campo, cuando se configura, especifica el motivo de excepción por el que se almacena el ARSB. Las razones de excepción de ejemplo incluyen:

40 Comprobación del programa: se detectó un error de programación.

45 Comprobación de protección: el mecanismo de protección impide el acceso al almacenamiento. La protección se aplica a la obtención de ARQB, MSB, AIDAW y datos a transferir a la memoria de clase de almacenamiento y al almacenamiento de información en el ARSB y datos transferidos desde la memoria de clase de almacenamiento.

Comprobación de datos del canal: se detectó un error de almacenamiento no corregido en relación con los datos contenidos en el almacenamiento principal y que son utilizados actualmente en la ejecución de una operación de EADM. La situación puedes ser indicada cuando se detecta, incluso si los datos no se utilizan cuando se realiza una captación previa. La comprobación de datos del canal se indica cuando los datos o la clave asociada tienen un código de bloque de comprobación (CBC – Checking Block Code, en inglés) no válido en el almacenamiento principal cuando el subsistema de canal hace referencia a esos datos.

50 Comprobación de control del canal: la comprobación de control del canal se debe a un fallo de la máquina que afecta a los controles del subsistema de canal. La situación incluye un CBC no válido en un ARQB, un ARSB, un MSB, una AIDAW o la clave asociada respectiva. La situación puede indicarse cuando se detecta un CBC no válido en un ARQB, MSB, AIDAW o la clave asociada respectiva, incluso si ese ARQB, MSB o AIDAW no se utiliza.

Comprobación de la función de traslado de datos asíncronos extendidos: se ha detectado un error no corregido con respecto a los datos que están contenidos en la memoria de clase de almacenamiento y se utiliza actualmente en la ejecución de una operación de EADM.

Identificadores de bloque de control de excepciones (ECBI – Exception Control Block Identifiers, en inglés) 244: cuando se almacena un ARSB, este campo es una máscara de múltiples bits, cuyos bits, cuando se configuran, especifican cualquier componente individual o combinación de los siguientes que están asociados con la excepción reconocida designada por el campo EF:

- 5     • el bloque o bloques de control

• el área principal de datos de almacenamiento

• la memoria de clase de almacenamiento.

10   Los bits que se pueden configurar representan, por ejemplo, un bloque de especificación de traslado de EADM, una dirección de datos indirectos de EADM, datos en el almacenamiento principal y/o datos en la memoria de clase de almacenamiento.

Los bits en el campo ECBI describen los componentes asociados con una situación de excepción única. Si no se pueden identificar componentes para la situación de excepción, este campo contiene, por ejemplo, ceros.

15   Indicador de validez de campo (FVF – Field Validity Flag, en inglés) 246: cuando se almacena un ARSB, este campo incluye una máscara de múltiples bits cuyos bits indican la validez de ciertos campos en el ARSB. Cuando se ha configurado un bit de validez, el campo correspondiente ha sido almacenado y es utilizable con fines de recuperación. Los bits que pueden estar configurados representan, por ejemplo, el campo de dirección de MSB con errores, el campo de AIDAW con errores, el campo de dirección de almacenamiento principal con errores y/o el campo de dirección de memoria de clase de almacenamiento con errores.

20   Código de calificador de excepción (EQC – Exception Qualifier Code, en inglés) 248: cuando se almacena un ARSB, este campo incluye un valor de código que describe con más detalle la excepción especificada por el campo de indicadores de excepción. Los valores del código pueden representar lo siguiente, como ejemplos:

No se proporciona ninguna descripción adicional. Para este caso, el campo de identificadores de bloque de control de excepción (ECBI) y aquellos campos validados por el campo de indicadores de validez de campo pueden identificar los bloques de control para los cuales se reconoce la excepción.

25   Error de formato: el formato especificado por el campo de formato está reservado. Para este caso, el campo de identificadores de bloque de control de excepción (ECBI) y los campos validados por el campo de indicadores de validez de campo pueden identificar los bloques de control para los cuales se reconoce la excepción.

Error de código de comando: el valor especificado en el campo de código de comando del ARQB no se reconoce.

30   Error de recuento de MSB: el valor especificado en el campo de recuento de MSB del ARQB es cero o supera el máximo número de MSB dependientes del modelo que se pueden especificar.

Error de indicadores: los bits de indicador especificados por el campo de indicadores están reservados. Para este caso, el campo de identificadores de bloque de control de excepción (ECBI) y aquellos campos validados por el campo de indicadores de validez de campo pueden identificar los bloques de control para los cuales se reconoce la excepción.

35   Error de código de operación: se especifica un valor de código de operación reservado. Si el campo de indicadores de validez de campo indica que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción.

40   Error de tamaño de bloque: se especifica un valor de tamaño de bloque reservado. Si el campo de indicadores de validez de campo indica que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción.

Error de recuento de bloques: el valor especificado en el campo de recuento de bloques de un MSB es cero o excede el número máximo de bloques dependientes del modelo que pueden ser especificados por un MSB. Si el campo de indicadores de validez de campo indica que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción.

45   Error de especificación de la dirección de almacenamiento principal: se especifica una dirección de almacenamiento principal en un límite incorrecto. Dicha dirección podría haber sido designada por un MSB o por una AIDAW. Si el campo de indicadores de validez de campo indica que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de la dirección de almacenamiento principal con errores es válido, el campo contiene la dirección de almacenamiento principal para la que se reconoce la excepción.

- 5 Error de especificación de dirección de la memoria de clase de almacenamiento: se especifica una dirección de la memoria de clase de almacenamiento en un límite incorrecto. Dicha dirección es designada por un MSB. Si los indicadores de validez de campo indican que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la memoria de clase de almacenamiento con errores es válido, el campo contiene la dirección de la memoria de clase de almacenamiento para la que se reconoce la excepción.

- 10 Excepción de la dirección de almacenamiento principal: la función de EADM intentó utilizar una dirección que no está disponible en la configuración o que se ajustó a la dirección de almacenamiento máximo. Dicha dirección podría haber sido designada por un MSB o resultar de un incremento de las direcciones de almacenamiento principal durante la transferencia de datos. Si el campo de indicadores de validez de campo indica que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección del almacenamiento principal con errores es válido, el campo contiene la dirección de almacenamiento principal para la cual se reconoce la excepción.

- 15 Excepción de dirección de la memoria de clase de almacenamiento: la función de EADM intentó utilizar una dirección de la memoria de clase de almacenamiento que no está disponible en la configuración. Dicha dirección podría haber sido designada por un MSB o como resultado del incremento de las direcciones de la memoria de clase de almacenamiento durante la transferencia de datos. Si el campo de indicadores de validez de campo indica que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la memoria de clase de almacenamiento con errores es válido, el campo contiene la dirección de la memoria de clase de almacenamiento para la cual se reconoce la excepción.

- 20 Error de almacenamiento principal: se detectó un error de almacenamiento principal no corregido. Si el campo de indicadores de validez de campo indica que el campo de la dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la memoria de clase de almacenamiento con errores es válido, el campo contiene la dirección de la memoria de clase de almacenamiento para la cual se reconoce la excepción.

- 25 Excepción de dirección de la memoria de clase de almacenamiento: la función de EADM intentó utilizar una dirección de la memoria de clase de almacenamiento que no está disponible en la configuración. Dicha dirección podría haber sido designada por un MSB o como resultado del incremento de las direcciones de la memoria de clase de almacenamiento durante la transferencia de datos. Si el campo de indicadores de validez de campo indica que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la memoria de clase de almacenamiento con errores es válido, el campo contiene la dirección de la memoria de clase de almacenamiento para la cual se reconoce la excepción.

- 30 Error de almacenamiento principal: se detectó un error de almacenamiento principal no corregido. Si el campo de indicadores de validez de campo indica que el campo de la dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de almacenamiento principal con errores es válido, el campo contiene la dirección de almacenamiento principal para la cual se reconoce la excepción.

- 35 Error de lista de MSB: el AOB especifica una lista de MSB que cruza un límite de 4 Kbytes sin especificar la rama hasta el siguiente MSB (BNM – Branch to Next MSB, en inglés) para sobrepasar el límite o el MSB es el último MSB en la lista de MSB especificada y la BNM está especificado por el MSB. Si el campo de indicadores de validez de campo indica que el campo de dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción.

- 40 Error de rama del MSB: el AOB especifica una lista de MSB en la que un MSB (MSB origen de la rama) especifica una rama hasta el siguiente MSB (BNM) y el MSB que es la rama objetivo también especifica la BNM. Si el campo de indicadores de validez de campo indica que el campo de dirección de MSB con errores es válido, el campo contiene la dirección del MSB de origen de la rama para la cual se reconoce la excepción.

- 45 Error de lista de AIDAW: un MSB especifica una lista de palabras de dirección de datos indirectos (AIDAW) de EADM que cruza un límite de 4 Kbytes sin especificar la rama hasta la siguiente AIDAW (BNA – Branch to Next AIDAW) para sobrepasar el límite. Si el campo de indicadores de validez de campo indica que el campo de dirección de MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de AIDAW para la cual se reconoce la excepción.

- 50 Error de rama de AIDAW: un MSB especifica una lista de palabras de dirección de datos indirectos (AIDAW) en la que una AIDAW (AIDAW de la rama hasta el origen) especifica una AIDAW de la rama hasta el origen (BNA) y la AIDAW que es el objetivo de la rama también especifica la BNA. Si el campo de indicadores de validez de campo indica que el campo de dirección de MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW de la rama hasta el origen para la cual se reconoce la excepción.

- 55 Error temporal de la memoria de clase de almacenamiento: se detectó un error de memoria de clase de almacenamiento recuperable. Si el campo del indicador de validez de campo indica que el campo de la dirección

5 del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de la dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la memoria de clase de almacenamiento con errores es válido, el campo contiene la dirección de la memoria de clase de almacenamiento para la cual se reconoce la excepción.

10 Error de operación de liberación no soportada: se especificó una operación de liberación para la memoria de clase de almacenamiento para la cual no está soportada la operación de liberación. Si el campo de indicadores de validez de campo indica que el campo de la dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de la dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la memoria de clase de almacenamiento con errores es válido, el campo contiene la dirección de la memoria de clase de almacenamiento para la cual se reconoce la excepción.

15 20 25 Error de lectura de datos liberados: se especificó una operación de lectura para la memoria de clase de almacenamiento para la cual la última operación con éxito fue una operación de liberación. Si el campo de indicadores de validez de campo indica que el campo de la dirección del MSB con errores es válido, el campo contiene la dirección del MSB para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de la dirección de la AIDAW con errores es válido, el campo contiene la dirección de la AIDAW para la cual se reconoce la excepción. Si el campo de indicadores de validez de campo indica que el campo de dirección de la memoria de clase de almacenamiento con errores es válido, el campo contiene la dirección de la memoria de clase de almacenamiento para la cual se reconoce la excepción.

30 Dirección del MSB con errores 250: cuando un bit especificado del campo de indicadores de validez de campo está configurado, este campo indica una dirección del MSB para la cual se reconoce una excepción.

35 40 45 Dirección de la AIDAW con errores 252: cuando un bit especificado del campo de indicadores de validez de campo está configurado, este campo indica una dirección de la AIDAW para la cual se reconoce una excepción.

Dirección del almacenamiento principal con errores 254: cuando un bit especificado del campo de indicadores de validez de campo está configurado, este campo indica una dirección del bloque de almacenamiento principal para la cual se reconoce una excepción.

50 55 Dirección de la memoria de clase de almacenamiento con errores 256: cuando un bit especificado del campo de indicadores de validez de campo está configurado, este campo incluye la dirección de la SCM (por ejemplo, 64 bits) del bloque de memoria de clase de almacenamiento para el cual se reconoce una excepción.

Además del bloque de solicitud de EADM y del bloque de respuesta de EADM, el bloque de operación de EADM (AOB) especifica asimismo uno o más bloques de especificación de traslado de EADM (MSB). El AOB puede contener, por ejemplo, hasta 124 MSB. Sin embargo, el programa puede especificar más de 124 MSB designando un mayor número de MSB en el campo de recuento de ARQB y utilizando el indicador de rama hasta el siguiente MSB (BNM) para derivar hasta una continuación de la lista de MSB. Puede haber múltiples continuaciones de la lista de MSB, pero, en una realización, ninguna de estas continuaciones puede sobrepasar un límite de 4 Kbytes sin utilizar BNM para sobrepasar ese límite. No es necesario que las continuaciones de la lista de MSB sean contiguas. Cada continuación de la lista de MSB, si está designada para comenzar en un límite de 4 Kbytes, puede contener hasta 128 MSB. El número total de MSB en una lista de MSB se especifica mediante el campo de recuento de MSB en el ARQB.

Un bloque de especificación de traslado de EADM describe, por ejemplo, los bloques de almacenamiento que serán trasladados entre el almacenamiento principal y la memoria de clase de almacenamiento, o una operación que se realizará en un bloque de almacenamiento. Una realización de MSB 226 se describe haciendo referencia a la figura 2E, e incluye, por ejemplo:

50 55 Formato (FMT) 260: Este campo especifica el diseño del MSB. El valor de este campo es un valor definido; de lo contrario, se indica un error de formato MSB en el campo de código de calificador de excepción del ARSB.

Código de operación (OC – Operation Code, en inglés) 262: este campo especifica la operación a realizar. En un ejemplo, cuando un bit especificado del campo de indicadores, que se describe a continuación, es un valor definido, este campo especifica la operación a realizar. Operaciones de ejemplo incluyen:

55 Borrado de la memoria de clase de almacenamiento: cuando se designa este código, se borra la memoria de clase de almacenamiento especificada por la dirección de la memoria de clase de almacenamiento, el tamaño del bloque y el campo de recuento de bloques (por ejemplo, configurados en ceros). El campo de dirección de almacenamiento principal no tiene ningún significado para esta operación.

Lectura: cuando se designa este código, los datos se especifican para ser transferidos desde la memoria de clase de almacenamiento al almacenamiento principal. Los campos de recuento de bloques, tamaño de bloque, dirección de almacenamiento principal y dirección de memoria de clase de almacenamiento tienen significado para esta operación.

5 Escritura: cuando se designa este código, los datos se especifican para ser transferidos desde el almacenamiento principal a la memoria de clase de almacenamiento. Los campos de recuento de bloques, tamaño de bloque, dirección de almacenamiento principal y dirección de memoria de clase de almacenamiento tienen significado para esta operación.

10 Liberación: cuando se designa este código y está instalada la función de liberación de EADM, se libera la memoria de clase de almacenamiento especificada por los campos de dirección de la memoria de clase de almacenamiento, el tamaño de bloque y el recuento de bloques. El campo de la dirección del almacenamiento principal no tiene ningún significado para esta operación. Cuando la función de liberación de EADM no está instalada, este código está reservado.

15 Si se especifica un valor reservado, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de código de operación en el campo del código de calificador de excepción del ARSB.

Cuando el bit de indicador especificado del campo de indicadores no es el valor definido, este campo está reservado y no está marcado.

20 Indicadores 264: este campo identifica uno o más indicadores que se pueden configurar. Los bits de indicador que están reservados se configuran en un valor definido; de lo contrario, se indica un error de indicador en el campo de código de calificador de excepción del ARSB. Indicadores de ejemplo incluyen:

- Rama hasta el siguiente MSB (BNM): cuando se configura, este indicador indica que el MSB no especifica una operación de EADM y no se utiliza para transferir datos. En su lugar, el campo de la dirección de almacenamiento principal especifica la dirección del siguiente MSB que será utilizado para especificar una operación de EADM.

25 Cuando se configura el indicador de BNM (por ejemplo, uno) y el campo de la dirección del almacenamiento principal especifica un MSB en el que también está configurado el indicador de BNM, el subsistema de canal reconoce una situación de comprobación del programa, la dirección de la rama hasta el origen de MSB está almacenada en el campo de dirección del MSB con errores del ARSB y un error de rama de MSB se indica en el campo de código de calificador de excepción del ARSB.

30 Si un MSB termina en un límite de 4 Kbytes, el AOB especifica MSB adicionales, y el indicador de BNM no está configurado, el subsistema de canal reconoce una situación de comprobación del programa, la dirección del MSB se almacena en el campo de la dirección del MSB con errores. El ARSB y un error de lista de MSB se indican en el campo de código de calificador de excepción del ARSB.

35 Si un MSB es el último MSB en la lista de MSB especificada y está configurado el indicador de BNM, el subsistema de canal reconoce una situación de comprobación del programa, la dirección del MSB se almacena en el campo de la dirección del MSB con errores del ARSB, y un error de lista de MSB se indica en el campo del código de calificador de excepción del ARSB.

40 Cuando se configura el indicador de BNM, los indicadores restantes, el campo de código de operación, el campo de tamaño de bloque, el campo de recuento del conjunto de bloques y la dirección de la memoria de clase de almacenamiento no tienen ningún significado.

- Direccionamiento indirecto: cuando se configura, este indicador indica que el campo del almacenamiento principal designa una dirección de una palabra de dirección de datos indirectos EADM (AIDAW) o de la primera AIDAW de una lista de AIDAW que designa la ubicación o ubicaciones del almacenamiento principal, respectivamente, para ser utilizado para la transferencia de datos. Cuando no está configurado, este indicador indica que el campo de dirección del almacenamiento principal designa una dirección de la ubicación del almacenamiento principal que se utilizará para la transferencia de datos.

50 Tamaño de bloque (BS – Block Size, en inglés) 266: este campo especifica el tamaño y el límite de los bloques de datos que se transferirán tanto para el almacenamiento principal como para la memoria de clase de almacenamiento, o el tamaño y el límite de un bloque de la memoria de clase de almacenamiento sobre la que se va a actuar (por ejemplo, será borrada o liberada). Ejemplos, incluyen:

4K: cuando el valor del código es un valor definido, los bloques de datos a transferir se encuentran en un límite de 4 Kbytes y tienen un tamaño de 4 Kbytes.

1M: cuando el valor del código es otro valor definido, los bloques de datos a transferir se encuentran en un límite

de 1 Mbyte y tienen un tamaño de 1 Mbyte.

Si se especifica un valor reservado, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de tamaño de bloque en el campo del código de calificador de excepción del ARSB.

Cuando el indicador de BNM está configurado, este campo se ignora.

5 Recuento de bloques 268: este campo incluye un número de bloques de datos a ser transferidos o sobre los que se actuará (por ejemplo, serán borrados o liberados). Sobre la base del campo de tamaño de bloque, este es el recuento de bloques de 4 Kbytes o de 1 Mbyte.

10 El valor de este campo debe ser mayor que cero y menor o igual que el recuento máximo de bloques dependientes del modelo que puede especificar un MSB; de lo contrario, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de recuento de bloques en el campo de código de calificador de excepción del ARSB.

Cuando el indicador de BNM está configurado, este campo está reservado y no es comprobado.

15 Dirección de almacenamiento principal 270: cuando el campo del código de operación tiene un significado (por ejemplo, el indicador de BNM no está configurado) y especifica una operación de lectura o escritura, y el indicador de direccionamiento indirecto en el campo de indicadores no está configurado, este campo incluye una dirección de almacenamiento principal que será utilizado para la transferencia de datos, y lo siguiente se aplica:

- 20 • Cuando el campo de tamaño de bloque especifica bloques de 4 Kbytes, los bits especificados de este campo contienen un valor definido (por ejemplo, cero); de lo contrario, el subsistema de canal reconoce la situación de comprobación del programa y se indica un error de especificación de almacenamiento principal en el campo de código de calificador de excepción del ARSB.

- Cuando el campo de tamaño de bloque especifica bloques de 1 Mbyte, los bits especificados de este campo contienen un valor definido (por ejemplo, ceros); de lo contrario, el subsistema de canal reconoce la situación de comprobación del programa y se indica un error de especificación de almacenamiento principal en el campo de código de calificador de excepción del ARSB.

25 Cuando el campo del código de operación tiene un significado y especifica una operación de lectura o de escritura y el indicador de direccionamiento indirecto está configurado en el campo de indicadores, el campo incluye una dirección de almacenamiento principal de una AIDAW o de la primera de una lista de AIDAW que se utilizará para la transferencia de datos. Para este caso, ciertos bits de este campo contienen un valor definido; de lo contrario, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de especificación del almacenamiento principal en el campo del código de calificador de excepción del ARSB.

30 Cuando el indicador BNM está configurado, el código de operación no tiene significado y el MSB no especifica una operación de EADM. En su lugar, este campo incluye una dirección de almacenamiento principal del siguiente MSB que especifica una operación de EADM. Para este caso, los bits especificados de este campo contienen un valor definido; de lo contrario, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de especificación de almacenamiento principal en el campo de código de calificador de excepción del ARSB.

35 Dirección de la memoria de clase de almacenamiento 272: cuando el campo del código de operación tiene significado, este campo incluye la dirección de la memoria de clase de almacenamiento (por ejemplo, 64 bits) que se utilizará para la transferencia de datos o para actuar sobre la misma (por ejemplo, ser borrada, liberada) y lo siguiente se aplica:

- 40 • Cuando el campo de tamaño de bloque especifica bloques de 4 Kbytes, los bits especificados de este campo contienen un valor definido (por ejemplo, ceros); de lo contrario, el subsistema de canal reconoce la situación de comprobación del programa y se indica un error de especificación de la memoria de clase de almacenamiento en el campo de código de calificador de excepción del ARSB.

- Cuando el campo de tamaño de bloque especifica bloques de 1 Mbyte, los bits especificados de este campo contienen un valor definido; de lo contrario, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de especificación de la memoria de clase de almacenamiento en el campo de código de calificador de excepción del ARSB.

Cuando el indicador BNM está configurado, este campo está reservado y no es comprobado.

45 50 Tal como se indicó anteriormente, se puede especificar una palabra de dirección de datos indirectos de EADM. La palabra de dirección de datos indirectos de EADM (AIDAW) permite al programa especificar la transferencia de bloques de datos entre la memoria de clase de almacenamiento y bloques no contiguos del almacenamiento principal. Una AIDAW o una lista de AIDAW es designado por un MSB cuando el indicador de direccionamiento

indirecto en el MSB está configurado.

La cantidad de datos transferidos mediante una sola AIDAW se especifica mediante el campo de tamaño de bloque en el MSB. El número de AIDAW en una lista de AIDAW es la suma del número especificado por el campo de recuento de bloques en el MSB más el número de AIDAW que especifican la rama hasta la siguiente AIDAW. Las

5 transferencias de datos pueden ser procesadas en órdenes que son diferentes de las especificadas en una lista de AIDAW. Además, las transferencias de datos especificadas por varias AIDAW en una lista de AIDAW pueden ser procesadas al mismo tiempo.

Una AIDAW es asignada, por ejemplo, a un límite de cuatro palabras. Una lista de AIDAW puede tener cualquier longitud, pero, en un ejemplo, no se debe sobrepasar un límite de 4 Kbytes a menos que se especifique una rama hasta la siguiente AIDAW (BNA) para sobrepasar el límite. No hay ningún requisito de que la AIDAW que es el objetivo de una rama sea contigua a la BNA que especifica la AIDAW. Sin embargo, el programa debe crear una lista de AIDAW en el menor número posible de bloques de 4 Kbytes; de lo contrario, se puede producir una degradación de la ejecución.

10 Haciendo referencia a la figura 2F, en un ejemplo, una palabra de dirección de datos indirectos de EADM 280 incluye:

15 Indicadores 282: un ejemplo de indicador incluye:

20 Rama hasta la siguiente AIDAW (BNA): cuando se configura, este indicador indica que el campo de la dirección de almacenamiento principal no especifica una dirección de almacenamiento principal para ser utilizada para transferir datos. En su lugar, el campo de dirección de almacenamiento principal especifica la dirección de la siguiente AIDAW que será utilizada para transferir datos.

25 Cuando el indicador de BNA está configurado y el campo de la dirección de almacenamiento principal especifica una AIDAW en la que también está configurado el indicador de BNA, la dirección del MSB se almacena en el campo de dirección del MSB con errores del ARSB, se almacena la dirección de la AIDAW de la rama hasta el origen en el campo de dirección de almacenamiento principal con errores en el ARSB, y un error de rama de AIDAW se indica en el campo de código de calificador de excepción en el ARSB.

Si una AIDAW termina en un límite de 4 Kbytes, el MSB especifica AIDAW adicionales, y el indicador de BNA no se configura, la dirección del MSB se almacena en el campo de dirección del MSB con errores del ARSB, la dirección de la AIDAW se almacena en el campo de dirección de almacenamiento principal con errores en el ARSB, y un error de lista de AIDAW se indica en el campo del código de calificador de excepción en el ARSB.

30 Dirección de almacenamiento principal 284: cuando el campo de BNA no está configurado, este campo incluye una dirección en el almacenamiento principal que se utilizará para la transferencia de datos y lo siguiente se aplica:

- 35 • Cuando el campo de tamaño de bloque en el MSB especifica bloques de 4 Kbytes, los bits especificados de este campo contienen un valor definido (por ejemplo, cero); de lo contrario, el subsistema del canal reconoce una situación de comprobación del programa y se indica un error de especificación del almacenamiento principal en el campo del código de calificador de excepción del ARSB.

- 40 • Cuando el campo de tamaño de bloque en el MSB especifica bloques de 1 Mbyte, los bits especificados de este campo contienen un valor definido (por ejemplo, ceros); de lo contrario, el subsistema de canal reconoce una situación de comprobación del programa y se indica un error de especificación de almacenamiento principal en el campo de código de calificador de excepción del ARSB.

- 45 • Cuando el indicador BNA está configurado, este campo incluye una dirección de almacenamiento principal de la siguiente AIDAW que se utilizará para la transferencia de datos.

Tal como se describió anteriormente, las operaciones de EADM se especifican mediante una instrucción de Iniciar el canal secundario. Es decir, el programa inicia las operaciones de EADM mediante la emisión de una instrucción de Iniciar el canal secundario que designa un canal secundario de tipo de ADM y un ORB de EADM. La ejecución de la instrucción pasa los contenidos del ORB de EADM al canal secundario designado. El ORB de EADM incluye la especificación de la clave del canal secundario (utilizada para protección) y la dirección del AOB que se utilizará.

50 En un ejemplo, tal como se muestra en la figura 3A, una instrucción de Iniciar el canal secundario 300 incluye un código de operación 302 que especifica la función de Iniciar el canal secundario, un primer operando 304, que es un operando implícito situado, por ejemplo, en el registro general 1, que incluye el identificador del subsistema que designa el canal secundario de tipo de ADM que se debe iniciar, y un segundo operando 306, que es la dirección lógica del ORB de EADM. El ORB de EADM especifica los parámetros utilizados para controlar la función de inicio. Los contenidos del ORB de EADM son colocados en el canal secundario designado durante la ejecución de la instrucción de Iniciar el canal secundario, antes de configurar el código de situación. Si la ejecución de la instrucción de Iniciar el canal secundario da como resultado la configuración de un código de situación distinto a un

código que indica éxito, el contenido del ORB de EADM no se coloca en el canal secundario designado.

Posteriormente a la ejecución de la instrucción de Iniciar el canal secundario para un canal secundario de tipo de ADM, el subsistema de canal realiza de manera asíncrona la función de iniciar las operaciones de EADM con la función de EADM. La función de inicio incluye, por ejemplo, lo siguiente:

- 5 1. Obtener el ARQB del AOB.

- 2. Ejecutar las operaciones de EADM de acuerdo con lo especificado por el ARQB y los MSB que designa.

- 3. Almacenar condicionalmente la información de finalización en el ARSB en el AOB.

- 4. Hacer que el canal secundario de tipo de ADM pase a estar en estado pendiente, lo que indica que la función de inicio ha finalizado.

- 10 En una realización, haciendo referencia a la figura 3B, cuando se ejecuta la instrucción de Iniciar el canal secundario y la SID designa un canal secundario de tipo de ADM y el segundo operando designa un ORB de EADM, se especifica una operación de EADM, ETAPA 320. Los parámetros en el ORB de EADM son pasados al canal secundario designado, ETAPA 322, y se solicita al subsistema de canal que ejecute una función de inicio con la función de EADM, ETAPA 324. El subsistema de canal ejecuta de manera asíncrona la función de inicio mediante la utilización de información en el canal secundario, incluida la información pasada durante la ejecución de la instrucción de Iniciar el canal secundario, para iniciar operaciones EADM, ETAPA 326.

- 15 La ejecución de una operación de EADM (por ejemplo, la primera operación) incluye la utilización de información del ORB de EADM para obtener el AOB, ETAPA 328, y la información utilizada en el AOB para obtener el bloque de solicitud de EADM (ARQB) y una designación de uno o más bloques de especificación de traslado de EADM (MSB), ETAPA 330. Los uno o más MSB designados son capturados del almacenamiento principal, ETAPA 332, y la información especificada en los MSB se utiliza para controlar la operación de EADM solicitada. Se considera que la primera operación se ha iniciado cuando el subsistema de canal intenta iniciar la transferencia de datos o intenta una operación de borrado o liberación.

- 20 El subsistema de canal realiza la operación o las operaciones solicitadas en el MSB o los MSB, ETAPA 334. Este procesamiento es asíncrono con respecto a la ejecución del comando Iniciar.

- 25 Cuando las operaciones de EADM iniciadas por el fin de Iniciar el canal secundario, ETAPA 336, el subsistema de canal genera situaciones de estado, ETAPA 338. La generación de estas situaciones se pone en conocimiento del programa mediante una interrupción de E/S, ETAPA 339. El programa también puede consultar estas situaciones mediante la ejecución de una instrucción de Probar interrupción pendiente.

- 30 Las situaciones de estado generadas son presentadas al programa en forma de una palabra de estado de canal secundario de EADM (SCSW). La SCSW de EADM se almacena como parte del bloque de respuesta de interrupción (IRB – Interruption Response Block, en inglés) de EADM mediante la ejecución de la instrucción de Probar el canal secundario.

- 35 Cuando se terminan las operaciones de EADM especificadas en el bloque de operación de EADM (AOB), el subsistema de canal genera los estados de interrupción primario y secundario. Las operaciones de EADM pueden ser terminadas con la instrucción de Borrar el canal secundario o con una situación anormal reconocida mientras se realiza la función de inicio.

- 40 El procesamiento de un MSB por el subsistema de canal, para una operación de traslado, controla el flujo de una unidad de información hacia el almacenamiento principal o desde el mismo. Para cambiar la dirección del traslado de datos durante el procesamiento de MSB, se necesita un nuevo MSB. El ARQB designa el recuento de MSB que comprenden la solicitud.

- Cada operación de EADM está representada por un MSB. Un MSB puede especificar cualquiera de los siguientes:

- La transferencia de bloques de datos desde el almacenamiento principal a la memoria de clase de almacenamiento.

- 45 • La transferencia de bloques de datos desde la memoria de clase de almacenamiento al almacenamiento principal.

- El borrado de bloques de la memoria de clase de almacenamiento.

- La liberación de bloques de la memoria de clase de almacenamiento, cuando la función de liberación de EADM está instalada.

- 50 Si los bloques de almacenamiento a ser transferidos para una operación de traslado no son contiguos en el

almacenamiento principal, se puede utilizar un nuevo MSB, o el MSB puede utilizar direccionamiento indirecto especificando una lista de palabras de dirección de datos indirectos (AIDAW) de EADM para designar los bloques no contiguos. Puesto que un MSB puede especificar la transferencia de datos en una sola dirección, se utilizará un nuevo MSB cuando haya un cambio en la dirección de la transferencia de datos.

- 5 Las siguientes son características de las transferencias de datos de EADM:

- Las transferencias de datos pueden ser procesadas fuera de orden con respecto al orden de la lista MSB especificada.

- Las transferencias de datos especificadas mediante múltiples MSB en una lista de MSB pueden ser procesadas simultáneamente.

- 10 • Las transferencias de datos pueden ser procesadas fuera de orden con respecto al orden de la lista de AIDAW especificada.

- Las transferencias de datos especificadas en varias AIDAW en una lista de AIDAW pueden ser procesadas simultáneamente.

- 15 • Los accesos al almacenamiento principal y a la memoria de clase de almacenamiento no son necesariamente referencias de acceso único y no se realizan necesariamente en una dirección de izquierda a derecha, de acuerdo con lo observado por el programa y por otras CPU.

- Si dos o más operaciones de EADM están actualmente activas y se dirigen a las mismas ubicaciones de la SCM, ubicación de almacenamiento principal, o ambas, las operaciones pueden ser realizadas al mismo tiempo, y el contenido de diferentes operaciones puede ser intercalado; sin embargo:

- 20 – Para las operaciones de entrada, los datos almacenados por la función de EADM en cada bloque de almacenamiento principal que tiene un tamaño igual al tamaño de coincidencia del bloque de SCM consisten en datos transferidos desde la memoria de clase de almacenamiento mediante una sola de las operaciones de EADM simultáneas.

- 25 – Para las operaciones de salida, cada bloque de la memoria de clase de almacenamiento que está en un límite y tiene un tamaño igual al tamaño de coincidencia del bloque de SCM contiene los datos especificados solo por una de las operaciones de EADM simultáneas.

- 30 Lo anterior es cierto con independencia de si las operaciones de EADM son especificadas por un solo AOB y están siendo procesadas por la misma instancia de la función de inicio o si las operaciones de EADM están especificadas por diferentes AOB y están siendo procesadas por diferentes instancias de la función de inicio.

- Cuando las operaciones de EADM están activas para un canal secundario, es impredecible si los cambios realizados por el programa al ARQB, al MSB, a la AIDAW y a los datos de transferencia asociados con la operación activa son observados por la función de EADM.

- 35 Cuando todos los bloques designados por todos los MSB especificados por el AOB han sido transferidos, eliminados o liberados, el canal secundario genera un estado, que se almacena en el canal secundario, y solicita una interrupción de E/S para el canal secundario de tipo de ADM.

- 40 La finalización de una operación de EADM normalmente se indica mediante las situaciones de estado combinadas de fin del canal y fin del dispositivo. Esta combinación de estados representa la combinación de los estados primario y secundario, lo que indica que el canal secundario está disponible para otra función de inicio después de que se borra el estado.

- Tal como se describió anteriormente, un MSB puede especificar una operación de transferencia de datos, una operación de borrado o una operación de liberación, cada una de las cuales se describe a continuación.

- 45 Cuando se solicita una operación de traslado, uno o más bloques de datos son trasladados entre el almacenamiento principal y la memoria de clase de almacenamiento. Por ejemplo, para una operación de lectura, los datos de la SCM se obtienen a partir de los SSD que proporcionan el contenido designado por la dirección de la SCM especificada, y, a continuación, ese contenido es almacenado en la memoria principal. El proceso se invierte para una operación de escritura. Los adaptadores que controlan los SSD realizan el almacenamiento. Con más detalle, para realizar una operación de traslado, el firmware del sistema primero traduce una dirección de SCM dada en una dirección de adaptador (por ejemplo, una dirección de volumen lógico, en la que un volumen lógico incluye uno o más SSD). Por ejemplo, se utiliza una tabla de traslaciones que correlaciona la dirección de SCM con una dirección de adaptador. A continuación, el firmware del sistema envía uno o más comandos de traslado de adaptador correspondientes (por ejemplo, lectura o escritura) a uno o más de los adaptadores de E/S. Un comando