# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

① Número de publicación: 2 711 768

51 Int. Cl.:

H04L 25/03 (2006.01) H04L 25/497 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 03.11.2015 PCT/EP2015/075601

(87) Fecha y número de publicación internacional: 12.05.2016 WO16071339

(96) Fecha de presentación y número de la solicitud europea: 03.11.2015 E 15790126 (5)

(97) Fecha y número de publicación de la concesión europea: 05.12.2018 EP 3216182

(54) Título: Medio de transmisión para transmitir una señal de salida, medio de recepción para recibir una señal de salida, y métodos para transmitir y recibir la misma

(30) Prioridad:

04.11.2014 DE 102014222511

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **07.05.2019**

(73) Titular/es:

FRAUNHOFER-GESELLSCHAFT ZUR FÖRDERUNG DER ANGEWANDTEN FORSCHUNG E.V. (100.0%) Hansastrasse 27c 80686 München, DE

(72) Inventor/es:

HILDINGER, RAINER; TASCH, ANDREAS; ZAREI, SHAHRAM; ZERNA, CONRAD; DÄUMLER, MATTHIAS; RUIZ CABRERA, CARLOS y KOCH, ROBERT

(74) Agente/Representante:

**ARIZTI ACHA, Monica**

#### **DESCRIPCIÓN**

Medio de transmisión para transmitir una señal de salida, medio de recepción para recibir una señal de salida, y métodos para transmitir y recibir la misma

5

10

15

25

30

La presente invención se refiere a un medio de transmisión para transmitir una señal de salida, a un medio de recepción para recibir una señal de salida y a métodos para transmitir o recibir una señal de salida. La presente invención también se refiere al procesamiento de señales altamente paralelo en filtros para la corrección directa de errores (FEC), filtros con respuesta al impulso infinita (IIR), en particular filtros de precodificación Tomlinson-Harashima (THP), filtros con respuesta al impulso finita (FIR) y filtros para la transferencia de datos multi-gigabit.

Para una transferencia de datos de banda base en serie con un alto caudal (en el rango de multi-gigabit), es necesario compensar la atenuación en el canal incluso cuando se usa un método de modulación de orden superior. Los filtros de ecualización se implementan digitalmente debido a un requisito de linealidad más exigente (en comparación con la modulación binaria). El procesamiento de datos en los filtros de ecualización digital a menudo está paralelizado para los sistemas con un caudal multi-gigabit ya que incluso los procesos CMOS modernos (CMOS = semiconductor complementario de óxido metálico) están limitados con respecto a las máximas velocidades de reloj posibles.

20 En general, los filtros FIR y los filtros IIR pueden usarse para compensar la función de transferencia. Un precodificador Tomlinson-Harashima, THP, es una forma específica del filtro IIR.

Para mejorar la tasa de error de bit, normalmente se usa una codificación de bloques en forma de corrección directa de errores (FEC). Puesto que en tales métodos se codifica una redundancia (bits de paridad) asignada a datos específicos, los datos se decodifican en el mismo bloque respectivo. Esto requiere una inserción cíclica de una secuencia de marcadores conocida, un denominado encuadre de los datos, y se inicia una sincronización de la trama para su procesamiento.

Dichos enlaces seriales de alta tasa de bits también se usan en la operación múltiplex para diferentes flujos de datos. Por ejemplo, diferentes buses, protocolos y/o usuarios se acumulan y se separan nuevamente. Además, diversas fuentes de datos pueden transmitirse a o recibirse de, por ejemplo, el nodo de red, mediante una conexión local de otras redes y disipadores/fuentes de datos locales a través del enlace.

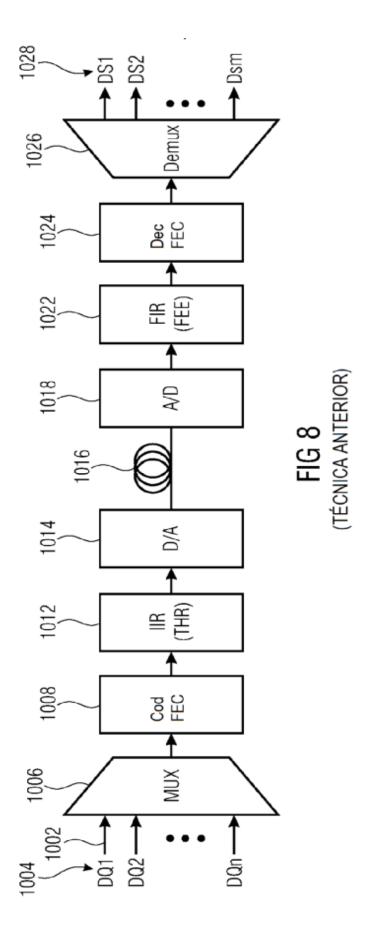

En la figura 8 se ilustra una solución conocida para el presente problema. Los datos 1002, procedentes de fuentes posiblemente diferentes 1004 (fuente de datos DQ1, DQ2,..., DQn), se combinan con un multiplexor 1006 en un flujo de datos en serie. En este caso, el multiplexor puede llevar bloques de diferentes tamaños procedentes de diferentes fuentes en cualquier orden. A continuación, este flujo de datos en serie pasa a través del procesamiento de señales en el lado del transmisor, que incluye una FEC 1008 y una predistorsión por medio de un filtro THP 1012. A continuación, el flujo de datos se transfiere, es decir, se produce lo siguiente: una conversión digital/analógica (D/A) 1014, una transferencia a través de un medio 1016, una conversión analógica/digital (A/D) 1018 y una amplificación opcional de la señal analógica o digital. En el lado del receptor, la señal pasa a través del procesamiento de la señal en la misma secuencia o una secuencia equivalente. Esto incluye una ecualización de canal (ecualizador de alimentación directa, FFE) por medio de un filtro FIR 1022 y una FEC 1024 en un lado del decodificador (Dec). A partir de entonces, los datos vuelven a dividirse por un demultiplexor 1026 y se reenvían a diversos disipadores de datos 1028 (DS1, DS2,... DSn).

Con el fin de aumentar las velocidades de caudal, se conoce una paralelización continua de filtros THP en relación con una disminución de la eficiencia en una paralelización creciente. Una estructura de filtro THP/IIR puede transformarme de tal manera que las rutas de realimentación de los filtros IIR se eliminen sin ningún retardo o con un retardo bajo. Debido a las rutas de realimentación más largas, pueden emplearse estrategias de canalización conocidas, para un aumento moderado en las velocidades de reloj alcanzables para los filtros IIR/THP. Estos métodos siguen siendo limitados debido a las velocidades de reloj alcanzables en los procesos CMOS. Para los filtros FIR, se conocen los métodos de solapamiento y almacenamiento y de solapamiento y suma con el fin de aumentar las velocidades de reloj.

55

50

El objeto de la presente invención es proporcionar un concepto que haga posible aumentar el caudal de datos de los filtros de procesamiento de señales y/o el canal de transferencia y/o mantener baja la disipación de potencia de los filtros de procesamiento de señales.

60 El objeto se resuelve por la materia de las reivindicaciones independientes.

Una idea central de la presente invención es reconocer que el objeto anterior puede resolverse por el hecho de que el procesamiento de señales de diferentes señales de datos ya puede producirse antes de la multiplexación de las mismas, y que combinando las señales de datos con una señal de referencia, puede obtenerse una respuesta de

sistema igual o comparable del filtro IIR con respecto a la señal de referencia y con respecto a otros flujos de datos filtrados. Las respuestas de sistema iguales o comparables permiten unir los diferentes flujos de datos filtrados mediante el multiplexor, de manera que el flujo de datos obtenido por el multiplexor actúa (monolíticamente) como si estuviese filtrado por un filtro monolítico, es decir, un único filtro. Esto permite un alto caudal de datos útiles a través del canal ya que el flujo de datos puede demodularse o decodificarse de manera continua. De este modo, puede reducirse el tiempo de establecimiento de los filtros de ecualización y/o puede aumentarse el caudal de datos. Además, la codificación de canal puede llegar a paralelizarse, lo que, cuando la complejidad del filtro sigue siendo la misma, conduce a un mayor caudal de datos por el aumento del número de filtros. Además, la disipación de potencia de los filtros puede reducirse preajustando los filtros a una respuesta de sistema a obtener, que el filtro respectivo proporciona como una respuesta a la señal de referencia, de manera que proporcionar el filtro con la propia señal de referencia puede omitirse parcialmente, lo que da como resultado una disipación de potencia reducida del filtro.

De acuerdo con una realización, un medio de transmisión incluye una primera estructura de filtro que comprende un primer combinador configurado para extender una primera señal de datos por una primera señal de referencia con el fin de obtener una primera señal de datos extendida. La primera estructura de filtro incluye un primer filtro IIR para filtrar la primera señal de datos extendida con el fin de obtener una primera señal de datos filtrada. El medio de transmisión incluye una segunda estructura de filtro que comprende un segundo combinador configurado para extender una segunda señal de datos por una segunda señal de referencia con el fin de obtener una segunda señal de datos extendida. La segunda estructura de filtro incluye un segundo filtro IIR para filtrar la segunda señal de datos extendida con el fin de obtener una segunda señal de datos filtrada. Este medio de transmisión incluye un multiplexor para combinar las señales de datos filtradas primera y segunda con el fin de obtener la señal de salida basándose en las señales de datos filtradas. Una respuesta de sistema del primer filtro IIR basada en la primera señal de referencia corresponde a una respuesta de sistema del segundo filtro IIR basada en la segunda señal de referencia. Las señales de datos primera y segunda pueden pasar de manera independiente a través de una cadena de procesamiento de señales, de modo que los filtros pueden paralelizarse y pueden generar un alto caudal. Además, basándose en respuestas de sistema iguales o comparables de los filtros en respuesta a las señales de referencia, las señales de datos filtradas pueden combinarse en el multiplexor sin símbolos de entrenamiento, lo que sería necesario con el fin de poner los filtros de recepción en un estado estacionario.

De acuerdo con otra realización, un medio de recepción para recibir una señal de salida incluye un demultiplexor para generar unas señales de recepción primera y segunda a partir de la señal de salida recibida. El medio de recepción incluye además una primera estructura de recepción que comprende un primer filtro de ecualización para ecualizar la primera señal de recepción y un primer separador configurado para separar una primera señal de referencia de la primera señal de recepción ecualizada. El medio de recepción incluye además una segunda estructura de recepción que comprende un segundo filtro de ecualización para ecualizar la segunda señal de recepción y un segundo separador configurado para separar una segunda señal de referencia de la segunda señal de recepción ecualizada. Dicho medio de recepción permite una ecualización paralelizada de los flujos de datos, de manera que, en comparación con los conceptos conocidos, se aumenta el caudal de todos los filtros.

40 Otras realizaciones se refieren a un sistema de transferencia que comprende un medio de transmisión y un medio de recepción, un método para transmitir una señal de salida y para recibir una señal de salida, así como un programa informático.

Otras realizaciones ventajosas son la materia de las reivindicaciones dependientes.

una señal de salida de acuerdo con una realización:

10

15

20

25

45

50

55

Figura 1a

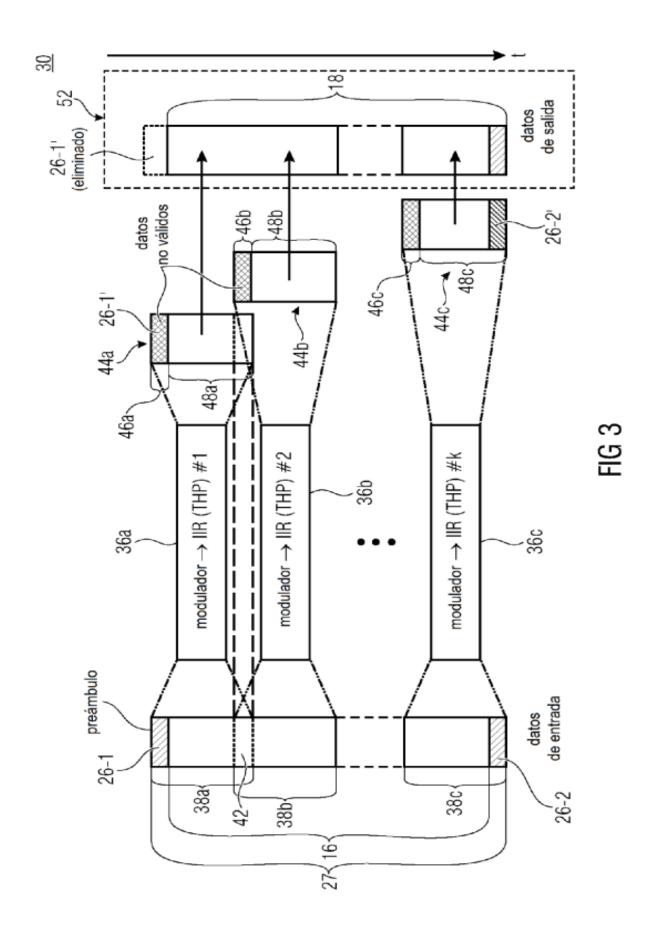

Figura 3

Las realizaciones de la presente invención se describirán con referencia a los dibujos adjuntos, en los que:

| Figura 1b | muestra una comparación esquemática de las señales de datos extendidas, las señales de datos               |

|-----------|------------------------------------------------------------------------------------------------------------|

|           | filtradas y la señal de salida de acuerdo con una realización;                                             |

| Figura 2  | muestra un diagrama de circuito de bloques esquemático de un medio de transmisión, en el que, a            |

|           | diferencia de las estructuras de filtro del medio de transmisión de la figura 1, las estructuras de filtro |

|           | compronden un media de cálcula de couerde con una realización:                                             |

comprenden un medio de cálculo de acuerdo con una realización; muestra un diagrama de circuito de bloques esquemático de un filtro de realimentación de acuerdo

muestra un diagrama de circuito de bloques esquemático de un medio de transmisión para transmitir

con una realización, que puede disponerse, por ejemplo, como un filtro IIR en el medio de transmisión

de las figuras 1 o 2;

Figura 4

Figura 5

Figura 6

Figura 6

Figura 7

Figura 8

Figura 9

Figu

60 Figura 5 muestra un diagrama de circuito de bloques esquemático de un medio de recepción que comprende unas estructuras de recepción que se modifican en comparación con las estructuras de recepción del medio de recepción de la figura 4 de acuerdo con una realización adicional:

Figura 6 muestra un diagrama de circuito de bloques esquemático de un sistema de transferencia que incluye el medio de transmisión de la figura 2 y el medio de recepción de la figura 4 de acuerdo con una

realización;

10

15

20

25

40

45

50

55

60

Figura 7 muestra un diagrama de bloques esquemático de un sistema de transferencia alternativo, en el que el

medio de transmisión incluye unos moduladores para modular las señales de datos, y el medio de

recepción incluye unos demoduladores, así como un medio de sincronización; y

Figura 8 muestra un sistema de transferencia de acuerdo con la técnica anterior.

Antes de que se expliquen en detalle las realizaciones de la presente invención con referencia a los dibujos, debe indicarse que se proporcionan elementos, objetos y/o estructuras idénticos, funcionalmente idénticos y operativamente idénticos en las diferentes figuras con números de referencia idénticos, de manera que la descripción de estos elementos en diferentes realizaciones puede intercambiarse y/o aplicarse recíprocamente.

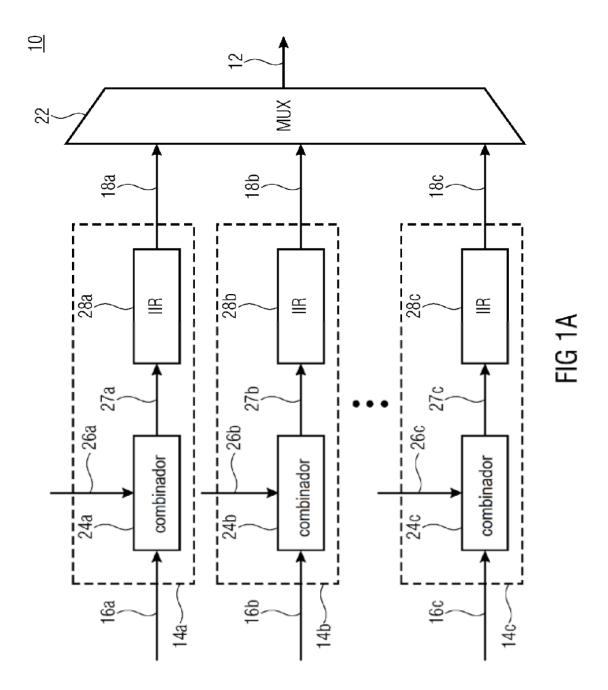

La figura 1a muestra un diagrama de circuito de bloques esquemático de un medio de transmisión 10, por ejemplo, un codificador de canal, para transmitir una señal de salida 12 a través de un medio de transferencia, tal como una conexión por cable o una conexión de fibra de vidrio o un medio de radio. El medio de transmisión 10 incluye una pluralidad de estructuras de filtro 14a-c configuradas para recibir, cada una de las mismas, una señal de datos 16a-c y para proporcionar una señal de datos filtrada 18a-c. Las señales de datos 16a-c pueden ser flujos de datos de diferentes fuentes de datos, que deben transferirse. Las fuentes de datos pueden ser cualquier tipo de fuente de datos, por ejemplo, un nodo de red, un servidor, un PC, un disco duro, una cámara de vídeo, un sensor u otros dispositivos que proporcionan o generan datos a transferir. Las señales de datos pueden recibirse por un codificador de bloques, tal como un codificador FEC, que está configurado para extender los datos de fuente de la fuente de datos bloque por bloque con redundancia (información sobre detección de errores y corrección de errores).

El medio de transmisión 10 incluye un multiplexor 22, indicado por "MUX", configurado para multiplexar las señales de datos filtradas 18a-c, es decir, para unirlas secuencialmente o en serie, con el fin de obtener la señal de salida 12. El multiplexor 22 está configurado además para emitir la señal de salida 12. Un tamaño y un orden o posición de subsecuencias de las señales de datos filtradas 18a-c o partes de las mismas en la señal de salida 12 pueden configurarse y ajustarse dinámicamente, por ejemplo, basándose en tasas de bit diferentes entre sí de las señales de datos 16a-c.

Cada una de las estructuras de filtro 14a-c comprende un combinador 24a, 24b y 24c, respectivamente, configurado para recibir la señal de datos 16a, 16b y 16c, respectivamente, y para combinar la señal de datos respectiva 16a-c con una señal de referencia 26a, 26b y 26c, respectivamente, con el fin de obtener una señal de datos extendida 27a, 27b y 27c, respectivamente. La señal de referencia puede ser una secuencia de datos conocida en todo el sistema (es decir, en el lado del transmisor y en el lado del receptor) insertada en una localización específica o predefinida de la señal de datos respectiva 16a-c. Por ejemplo, la señal de referencia 26a-c se inserta entre dos bloques de datos de la señal de datos respectiva 16a-c. Una longitud de datos de las señales de referencia 26a-c puede verse influida por una función habilitada en un receptor de la señal de salida 12, como se describirá a continuación, y permite obtener una respuesta de sistema comparable en diferentes filtros IIR del medio de transmisión.

Por ejemplo, una señal de referencia 26a-c puede combinarse con una señal de datos 16a-c, de tal manera que la señal de referencia 26a-c puede añadirse en su totalidad o en parte en una o varias localizaciones predeterminadas, por ejemplo, al principio, al final o en una posición definida entre el principio y el final de un bloque de datos de la señal de datos respectiva 16a-c. Cuando la señal de referencia 26a-c se inserta al principio y/o al final de un bloque de datos de la señal de datos respectiva 16a-c (es decir, entre dos bloques de datos), el filtro IIR respectivo 28a-c aún no ha sido influenciado (entrenado) adecuadamente por los datos de la señal de referencia 26a-c insertada al principio, cuando se filtra la señal de referencia insertada al principio. Por ejemplo, puede conducir a que los datos actúen de una manera no monolítica (es decir, que contengan una señal de error significativo en las proximidades de los puntos de transición entre los filtros 28a-c) antes de la señal de datos filtrada ya que el filtro IIR 28a-c no está en un estado estacionario. Al final del bloque de datos, la señal de datos filtrada 18a-c actúa de manera monolítica

basándose en el estado estacionario obtenido. Antes de la multiplexación, los datos que actúan de manera no monolítica pueden considerarse no válidos y/o eliminarse del flujo de datos. La eliminación de los datos no válidos puede, por ejemplo, producirse en el filtro IIR respectivo 26a-c, en el multiplexor 22 o por medio de un medio de cálculo que influye en las señales de datos filtradas 18a-c.

Las señales de referencia 26a-c pueden ser invariantes en el tiempo o variables en diferentes intervalos de tiempo. Por ejemplo, basándose en una potencia de señal variable de la señal de datos respectiva 16a-c, las señales de referencia pueden comprender una potencia de señal que también sea variable y esté adaptada, es decir, sea aproximadamente igual, a la potencia de señal de la señal de datos 16a-c. Las señales de referencia 26a-c pueden ser iguales o comprender diferente información (bits o símbolos y/o longitudes de datos iguales o diferentes).

Cada una de las estructuras de filtro 14a-c incluye un filtro IIR 28a, 28b y 28c, respectivamente, configurado para filtrar la señal de datos extendida respectiva 27a, 27b o 27c. Los filtros IIR 28a-c están, por ejemplo, configurados como filtros de distorsión previa configurados para compensar previamente una distorsión esperada de la señal de

salida 12 en el medio de transferencia. Los filtros IIR 28a-c pueden comprender cualquier estructura de filtro IIR, entre otras, también una estructura de filtro Tomlinson-Harashima (filtro THP).

Puede suponerse que la distorsión estadística de las señales de datos filtradas 18a, 18b y 18c en la señal de salida 12 sea igual, ya que todas las señales se transfieren a través del mismo canal en breves intervalos de tiempo. En consecuencia, una característica de predistorsión de los filtros IIR 28a-c puede ser igual o comparable. De acuerdo con una realización, los filtros IIR 28a-c están configurados como filtros THP.

Los filtros IIR 28a-c están configurados para filtrar la señal de datos extendida respectiva 27a-c y, por lo tanto, a veces en su totalidad o en parte, la señal de referencia respectiva 26a-c y, en otros momentos, la señal de datos 16a-c en su totalidad o en parte. Una respuesta de sistema del filtro IIR 28a basada en el filtrado de la señal de referencia 26a puede compararse, al menos al final del proceso de filtrado, con una respuesta de sistema correspondiente del filtro IIR respectivo 36b o 36c basándose en el filtrado de las señales de referencia respectivas 26b o 26c.

10

15

20

25

30

50

55

Cuando el filtro IIR 28a filtra la señal de referencia 26a, la señal de referencia 26a genera una respuesta de sistema correspondiente en el filtro 28a. Lo mismo se aplica al filtro IIR 28b con respecto a la señal de referencia 26b y al filtro IIR 28c con respecto a la señal de referencia 26c. Cuando los filtros IIR 28a-c comprenden una longitud de filtro igual y coeficientes iguales, las señales de referencia 26a-c pueden ser iguales, es decir, las señales de referencia 26a-c pueden ser la misma señal. Una respuesta de sistema de los filtros IIR 28a-c, es decir, una señal de salida parcial respectiva, es, por lo tanto, igual o comparable en función de la señal o señales de referencia 26a-c. Las respuestas de sistema de los filtros IIR 28a-c pueden ser iguales o aproximadamente iguales en función de las señales de referencia 26a-c. Cuando los filtros IIR 28a-c comprenden un estado inicial igual, una estructura de filtro igual y unos coeficientes de filtro iguales, y se aplican las mismas señales de referencia 26a-c a los filtros IIR 28a-c, también surge un estado igualmente estacionario de los filtros IIR. Sin embargo, cuando los filtros IIR 28a-c comprenden diferentes estados iniciales, por ejemplo, en función de las señales de datos diferentes entre sí 16a-c, que se han filtrado de una manera anterior, los estados iniciales también influyen en los estados futuros del sistema en función de la estructura de realimentación de los filtros 28a-c. Las señales de referencia 26a-c comprenden una longitud que reduce tales efectos hasta el punto de que estos efectos son insignificantes y las respuestas de sistema son comparables.

Por lo tanto, después de la multiplexación, la señal de salida 12 actúa como si se hubiera filtrado, es decir, calculado, por un solo filtro. Esto permite una ecualización y decodificación eficientes en el lado del receptor.

Esto puede lograrse debido a que la longitud de la señal de referencia 26a-c es al menos dos veces más larga (factor 2), al menos tres veces más larga (factor 3), al menos cinco veces más larga (factor 5) o más que una longitud de filtro de los filtros IIR 28a-c.

Los flujos de datos individuales pueden unirse en partes de las señales de datos filtradas 18a-c, que comprenden unas respuestas de sistema comparables entre sí, por medio del multiplexor 22 y, de este modo, pueden mantener una estructura correspondiente a la estructura que se habría obtenido filtrando un flujo de datos a través de un filtro, de manera que se requiere un tiempo de establecimiento reducido o nulo para recibir filtros en el lado del receptor.

El medio de transmisión 10 puede comprender cualquier número de estructuras filtradas 14a-c, por ejemplo 2, 3 o más.

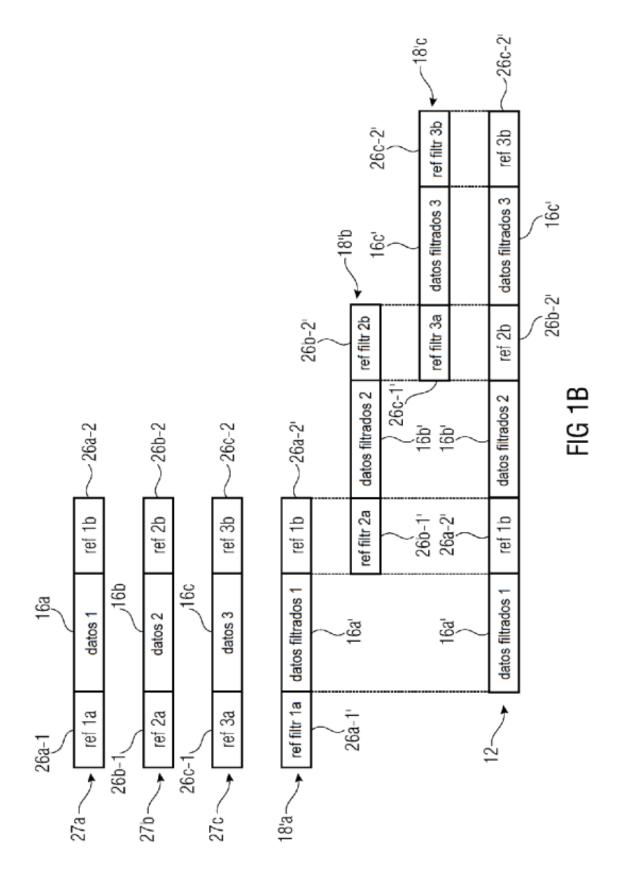

La figura 1b muestra una comparación esquemática de las señales de datos extendidas 27a, 27b y 27c. Las señales de datos extendidas 27a-c comprenden, cada una de las mismas, un bloque de datos de las señales de datos 16a, 16b y 16c (Datos 1, Datos 2, Datos 3), respectivamente, que se combinan con las señales de referencia 26a-c, de tal manera que la señal de referencia 26a-1, 26b-1 y 26c-1, respectivamente, se añade delante del bloque de datos, y la señal de referencia 26a-2, 26b-2 y 26c-2, respectivamente, se añade detrás del bloque de datos. Como ejemplo, las señales de referencia comprenden las mismas longitudes de datos pero también pueden ser diferentes entre sí, como se ha explicado anteriormente. De manera alternativa, o adicionalmente, las longitudes de datos de las señales de datos 16a-c también pueden ser iguales o diferentes entre sí. En función de las señales de datos extendidas 27a-c, las señales de datos filtradas 18'a-c se obtienen por la filtración de los filtros 28a-c. Las señales de datos filtradas 18'a-c difieren de las señales de datos filtradas 18a-c de la figura 1a en que las señales de datos filtradas 18'a-c comprenden (aún) los preámbulos no válidos 26a-1', 26b-1' y 26c-1'.

Las señales de datos filtradas 18'a-c comprenden una estructura de datos igual (señal de referencia - señal de datos - señal de referencia) que las señales de datos extendidas 27a-c, filtrándose las señales de referencia y las señales de datos, como lo indica la adición de "fil.", que significa "filtrada". La señal de datos filtrada comprende la señal de referencia filtrada 26a-1' delante de la señal filtrada 16a' y la señal de referencia filtrada 26a-2' detrás de la misma. Las señales de datos filtradas 18'b y 18'c comprenden una estructura desigual. Las señales de datos filtradas 18'a-c se combinan por medio del multiplexor 22 con la señal de salida 12.

La señal de salida obtenida 12 comprende una estructura (monolítica), es decir, actúa como si se hubiera filtrado por un solo filtro IIR. En este caso, la señal de salida 12 obtenida en un punto en el tiempo depende de las operaciones de filtro anteriores de los filtros que filtran la sección de datos respectiva. Sin embargo, las señales de referencia filtradas respectivas 26a-1', 26b-1' y 26c-1' colocadas delante no se ven afectadas por las respectivas secuencias de datos de las otras señales de datos extendidas o filtradas, que preceden a la señal de salida 12. Eso significa que la señal de referencia filtrada 26a-1' puede ser desigual con respecto a la señal de referencia filtrada 26b-1' y/o 26c-1'. Las señales filtradas 16a'-c' se filtran por medio de las señales de referencia 26a-1, 26b-1 y 26c-1 de los filtros en un estado estacionario y están suficientemente influenciadas por estas señales anteriores. De manera similar, las señales de referencia 26a-2', 26b-2' y 26c-2' adjuntas están adecuadamente influenciadas por las señales de datos respectivas 16a-c. Esto garantiza que la señal de referencia 26a-c (preámbulo) insertada delante (y detrás) de cada bloque de datos 16a-c se transfiera al final del bloque de datos filtrado respectivo 16a'-c', ya que el preámbulo se considera no válido o se elimina al principio del bloque de datos y se filtra y se transfiere correctamente al final del bloque de datos.

La estructura monolítica de la señal de salida 12 puede obtenerse configurando el multiplexor 22, el filtro IIR respectivo 28a-c o un medio (tal como un formador de señales) conectado entre los filtros 28a-c y el multiplexor 22 para eliminar las respuestas de filtro respectivas 26a-1', 26b-1' o 26c-1', que no son válidas o no están lo suficientemente influenciadas, y para emitir la señal de salida 12 en función de las señales filtradas conectadas secuencialmente 16a'-c' y 26a-2', 26b-2' y 26c-2', respectivamente. Esto significa que, como alternativa a la situación mostrada en la figura 1b, las señales de datos filtradas tampoco pueden comprender el preámbulo no válido respectivo 26a-1', 26b-1' y 26c-2', por ejemplo, cuando el filtro IIR está configurado para eliminar los datos, o cuando el filtro IIR incluye un formador de señales configurado con este fin, por ejemplo, como se describe en relación con la figura 3. En términos simplificados, de acuerdo con la realización, el preámbulo se calcula (filtra) dos veces, pero se transfiere una sola vez. Con este fin, un bloque de datos de señales de datos 16a-c se extiende por dos señales de referencia, usándose una (la que se coloca delante de la señal de datos 16a-c) para entrenar el filtro, pero rechazándose la respuesta de filtro obtenida con el fin de obtener una baja sobrecarga (proporción de la información de estado o información de gestión de enlaces). La señal de referencia respectiva 26a-2, 26b-2 y 26c-2 colocada al final de la señal de datos 16a-c se transfiere en su forma filtrada respectiva 26a-1', 26b-1' y 26c-1'. Las respuestas de filtro respectivas (señales de referencia filtradas) 26a-1', 26b-1' y 26c-1' pueden ser iguales o comparables (es decir, con diferencias insignificantes, posiblemente por debajo del ruido del sistema).

Una de las características ventajosas de la presente invención es que las combinaciones (o tuplas) (16a', 26a-2'), (16b', 26b-2') y (16c', 26c-2') pueden transmitirse en cualquier orden dado y que la forma de onda resultante siempre aparece de manera monolítica, es decir, no comprende errores en o cerca de las transiciones entre las tuplas.

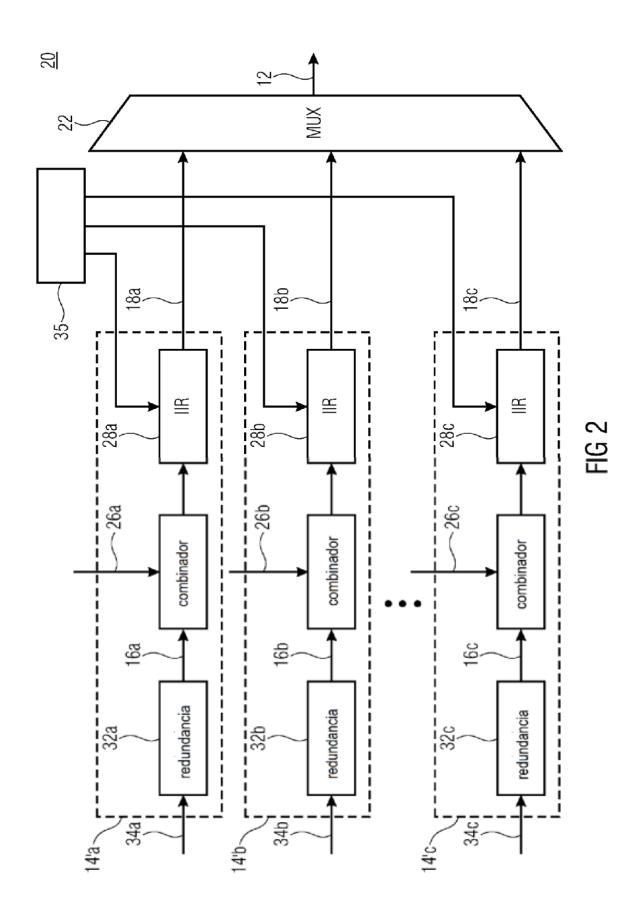

La figura 2 muestra un diagrama de circuito de bloques esquemático de un medio de transmisión 20, en el que las estructuras de filtro 14'a-c, a diferencia de las estructuras de filtro 14a-c de la figura 1, incluyen unos medios de cálculo 32a, 32b y 32c, respectivamente, configurados para recibir una señal de fuente 34a, 34b o 34c procedente de una fuente de datos y para calcular la información de redundancia con respecto a la señal de fuente respectiva 34a-c. Los medios de cálculo 32a-c pueden ser, por ejemplo, un medio para calcular símbolos de redundancia o bits de redundancia u otra codificación previa, que permite una corrección de errores en el lado del receptor. Por ejemplo, los medios de cálculo 32a-c pueden configurarse para ejecutar un algoritmo para una corrección directa de errores (FEC). Los símbolos o bits calculados de manera correspondiente pueden combinarse con la señal de fuente 34a, 34b o 34c mediante los medios de cálculo 32a-c con el fin de obtener las señales de datos respectivas 16a, 16b o 16c. Los medios de cálculo 32a-c pueden incorporarse, por ejemplo, como un procesador, una matriz de puertas programables en campo (FPGA), un circuito digital en una circuitería integrada, o similares, y pueden configurarse para recibir de manera continua o discontinua las señales de fuente 34a, 34b o 34c. Los medios de cálculo 32a-c ya pueden recibir la señal de fuente respectiva 34a-c como un bloque a procesar y pueden recibir datos de manera continua o discontinua hasta que se alcance un tamaño de bloque correspondiente, y pueden proporcionar las señales de datos 16a, 16b o 16c, respectivamente, en función de un bloque de proceso.

Por ejemplo, la combinación puede producirse añadiendo o insertando la información de redundancia (símbolos o bits) en la señal de recurso 34a-c. Una combinación de las señales de fuente 34a-c con la información de redundancia permite una mayor fiabilidad de transferencia en un sistema de transferencia, ya que pueden corregirse los errores de bit.

El medio de transmisión 20 incluye además un medio de cálculo 35, por ejemplo, un procesador o similar, configurado para ajustar los filtros IIR 28a-c, es decir, para calcular y/o adaptar los coeficientes de filtro de los filtros IIR 28a-c. Además, el medio de cálculo 35 puede configurarse para influir en una señal a aplicar al filtro respectivo 28a-c, es decir, para añadir y/o para eliminar o para suprimir partes de señal. Por ejemplo, el medio de cálculo 35 puede configurarse para eliminar datos de las señales de datos filtradas 18a-c, que no se consideran válidos. El medio de cálculo 35 puede configurarse además para calcular una respuesta de sistema o de impulso de los filtros IIR 28a-c, por ejemplo, tras aplicar la señal de referencia 26a-c en los filtros IIR 28a-c. Como alternativa, la

respuesta de sistema o de impulso puede calcularse en el lado del receptor, por ejemplo, calculando una respuesta de filtro-impulso combinada, por ejemplo, después de que se haya realizado una corrección de errores, y basándose en el filtrado de la señal de error corregida obtenida. El medio de cálculo 35 puede configurarse para almacenar los coeficientes de filtro obtenidos y enviados en consecuencia y, posiblemente, para actualizar los mismos de manera variable en el tiempo, y para ajustar los filtros IIR 28a-c en función de los coeficientes. Los filtros digitales con una estructura conocida están suficientemente definidos por sus coeficientes. Si los coeficientes son conocidos, la respuesta de impulso también puede considerarse como conocida.

10

15

20

25

30

35

40

45

50

55

60

Las señales de referencia 26a-c pueden adaptarse a la señal de fuente respectiva 34a-c o a la señal de datos 16a-c para una mejora adicional de la fiabilidad de transferencia. Por lo tanto, las señales de referencia 26a-c pueden comprender un grado de modulación que es menor que un grado de modulación de las señales de fuente 34a-c o las señales de datos 16a-c. Por ejemplo, la señal de fuente 34a y/o la señal de datos 16a pueden modularse por medio de una modulación por amplitud de pulsos (PAM) o por medio de una modulación por codificación de pulsos (PCM) y comprenden un primer número de niveles de amplitud posibles, tales como 3, 4, 5 o más. La señal de referencia 26a-c también puede comprender una modulación PAM o PCM y un segundo número de niveles de amplitud posibles, como 2, 3, 4 o más, en el que el segundo número de niveles de amplitud posibles es menor que el primer número de niveles de amplitud. Cuando se compara con la señal de datos 16a o la señal de fuente 34a, el menor grado de modulación de la señal de referencia 26a permite un aumento de la fiabilidad de interferencia con respecto a los errores de transferencia para las partes de señal de las señales de referencia 26a-c en la señal de salida 12. La potencia de señal del preámbulo, es decir, de la señal de referencia, puede ser la misma que una potencia de señal (media) de la señal de datos respectiva 16a, 16b o 16c en un intervalo de tolerancia de más/menos 20 % a lo sumo, como alternativa más/menos 10 % a lo sumo, o como alternativa más/menos 5 % a lo sumo. Además, las señales de referencia 26a-c pueden configurarse sin un valor medio con el fin de mantener la señal de salida 12 también sin un valor medio cuando la señal de datos 16 no tiene un valor medio. Como alternativa, la señal de referencia 26a-c puede comprender un valor medio para compensar un valor medio de la señal de datos 16a-c o para obtener la señal de datos filtrada 18a-c con una cantidad reducida de un valor medio de la misma. Como alternativa, la señal de referencia 18a-c puede o no comprender un valor medio independientemente de que la señal de datos 16a-c comprenda un valor medio o no. Una configuración de las señales de referencia 26a-c sin un valor medio permite una capacidad de procesamiento mejorada de la señal de salida resultante 12 en extremos delanteros analógicos, es decir, elementos tales como convertidores de digital a analógico (DAC) y/o convertidores de analógico a digital (ADC). Este puede ser un criterio de diseño importante.

Las señales de referencia 26a-c también pueden denominarse preámbulo, en particular, cuando las mismas se colocan delante de un bloque de la señal de datos 16a, 16b y 16c, respectivamente, o se adjuntan a la misma. Las señales de referencia adjuntas 16a-c actúan en un bloque posterior de la señal de datos 16a-c de manera igual o comparable a una señal colocada delante. El preámbulo puede usarse como un marcador limitante de los bloques de datos respectivos (tramas) en el flujo de datos continuo (señal de salida 12). Esto permite que el marcador se use en el receptor para sincronizar estas tramas, por ejemplo, para cadenas de procesamiento de datos paralelizadas. El preámbulo conocido en todo el sistema permite procesar independientemente los datos de entrada, que posteriormente se ajustan perfectamente entre sí en la transferencia en serie, es decir, aparecen como si se procesaran en una única cadena en serie. Por lo tanto, un enlace de comunicación entre el transmisor y el receptor puede transferir una alta carga de datos de carga útil con una sola carga mínima de "datos de gestión" que pueden usarse de manera muy eficiente, por ejemplo, para sincronizar y/o entrenar las paralelizaciones en los lados del transmisor y del receptor.

Una carga de datos de carga útil puede aumentarse o maximizarse cuando los datos de las diferentes fuentes de datos se transmiten en múltiplos de tamaños de bloque FEC, es decir, la carga de datos de carga útil de un bloque FEC se utiliza completamente. Debido a la independencia del procesamiento de datos en paralelo de las estructuras de filtro 14a-c o 14'a-c, puede manejarse una fuente de datos independiente. Las fuentes de datos pueden ser independientes del tiempo. El flujo de datos entrante de una fuente de datos (señal de fuente 34c-c) puede configurarse de manera continua y, como alternativa, de manera discontinua. La composición de un flujo continuo puede producirse después del procesamiento de señales en la serialización, es decir, por medio del multiplexor 22. A diferencia de la técnica anterior, en la que los datos para la transferencia en serie se reorganizan (multiplexan) y, a continuación, se realiza el procesamiento de señales, debido a las realizaciones anteriores, el procesamiento de señales para la transferencia puede producirse en un subconjunto del flujo de datos y en paralelo a otras cadenas de procesamiento de señales que operan independientemente, y la reorganización de los datos para el enlace en serie puede tener lugar después del procesamiento en las estructuras de filtro 14a-c o 14'a-c. A pesar de este desplazamiento de la "operación de multiplexación" a después del procesamiento de señales, la secuencia de transmisión (señal de salida 12) aparece en el canal como una sola señal procesada de manera continua. Por lo tanto, las realizaciones permiten utilizar una proporción máxima de datos de carga útil.

La figura 3 muestra un diagrama de circuito de bloques esquemático de un filtro de realimentación 30 que puede disponerse, por ejemplo, como un filtro IIR 28a, 28b o 28c en el medio de transmisión 10 o 20. Una serie secuencial de las partes de señal o la señal de datos extendida 27 y la señal de datos filtrada 18 está representada por el eje de

tiempo t. La señal de datos extendida 27 incluye las señales de referencia 26-1 y 26-2 colocadas delante o detrás de la señal de datos 16, de acuerdo con las afirmaciones con respecto a la figura 1b. Un bloque adicional de la señal de datos 16 (con la señal de referencia asignada) puede seguir a la señal de referencia 26-2 (preámbulo). El filtro de realimentación 30 incluye una pluralidad, es decir, dos, tres o más, de filtros IIR 36a-c, respectivamente, configurados para filtrar una parte de señal de la señal de datos extendida 27, lo que significa que la señal de datos extendida 27 se filtra mediante una estructura paralelizada de filtros IIR 36a-c.

10

15

20

25

30

35

40

45

50

55

60

Los filtros IIR 36a-c están configurados para cada filtro en una sección de señal 38a, 38b y 38c, respectivamente, de la señal de datos extendida 27 y pueden incorporarse como un filtro THP. Las partes de señal 38a y 38b se solapan en una parte de solapamiento 42, lo que significa que la parte de solapamiento 42 de la señal de datos extendida 27 se filtra tanto por el filtro IIR 36a al final de la parte de señal 38a como por el filtro IIR 36b al principio de la parte de señal 38b. Una parte de solapamiento 42 está dispuesta entre dos partes de señal subsiguientes respectivas 38a-c. Puesto que la respuesta de sistema del filtro IIR respectivo 36a-c depende de una forma de onda de señal anterior de una cierta duración de tiempo hasta que la realimentación de las partes de señal anteriores se atenúa hasta una parte insignificante, las partes de señal filtradas 44a, 44b o 44c, respectivamente, de los filtros IIR 36a-c también dependen de los componentes de señal anteriores. Esto puede dar como resultado que las partes de señal filtradas 44a-c comprendan una secuencia de datos inicial 46a, 46b y 46c, respectivamente, que se filtró por un filtro en un estado no estacionario (o un estado que está influenciado por un bloque no actualmente filtrado de la señal de datos extendida respectiva 27). Un estado no estacionario hace referencia a un estado teórico que se obtendría si la señal de datos extendida 27 se filtrara continuamente por un solo filtro IIR. Basándose en la paralelización del único filtro IIR en varios subfiltros 36a-c, los filtros 36a-c no se ven influenciados por las formas de onda de señal de la señal de datos extendida 27, que están dispuestas temporalmente delante de la parte de señal respectiva 38a, 38b o 38c, y en este sentido, por lo tanto, en un estado no estacionario al principio de las partes de señal 38a-c y la parte de señal 44a-c en las partes 46a-c. En estos estados no estacionarios, la respuesta de sistema del filtro es significativamente diferente de una respuesta de sistema de un solo filtro que filtra todo el bloque de datos, de manera que estos datos, tales como la señal de referencia filtrada 26-1', pueden considerarse "no válidos". El formador de señales 52 está configurado para eliminar los datos 46a-c considerados no válidos y, por lo tanto, también la respuesta de filtro en respuesta al preámbulo 26-1, de manera que la señal de datos filtrada 18 no incluye esta respuesta de filtro en el estado mostrado.

En términos simplificados, los datos de la parte de solapamiento 42 se filtran correctamente por el filtro IIR 36a y se filtran incorrectamente por el filtro IIR 36b y se usan para el filtro IIR 36b como una secuencia de entrenamiento con el fin de obtener el estado estacionario. Una respuesta de sistema de los filtros 36a-c en la secuencia de entrenamiento respectiva puede considerarse como datos no válidos y se elimina mediante el formador de señales 52.

Los filtros IIR 36a-c están configurados de tal manera que las partes de solapamiento 42 comprenden una longitud al menos correspondiente a una longitud que requiere el filtro IIR respectivo 36a, 36b o 36c con el fin de alcanzar el estado estacionario. Esto significa que, después de la parte de solapamiento 42, el filtro IIR respectivo 36a-c se ve influenciado por las partes de señal anteriores de la señal de datos extendida 27, de tal manera que la parte de señal filtrada 44a-c es la misma en las partes 48a-c en un intervalo de tolerancia como si la señal de datos extendida 27 se hubiera filtrado por un único filtro IIR. Las partes 48a-c forman la señal de datos filtrada 18 en partes.

La estructura de filtro de realimentación 30 incluye un formador de señales 52 configurado para combinar las partes de señal filtradas 44a-c, por ejemplo, de manera sucesiva secuencial, con el fin de obtener la señal de datos filtrada 18. El formador de señales 52 está configurado para eliminar las secuencias de datos consideradas no válidas, es decir, las secuencias de solapamiento 46a-c asignadas a las partes de solapamiento 42, y para unir las partes de señal 48a-c. Esto permite que la señal de datos filtrada 18 solamente comprenda aquellas señales o secuencias de señales que se obtuvieron por filtros en un estado estacionario.

Cuando el preámbulo no cambia en varios bloques de la señal de datos extendida 27, el preámbulo 26-2 puede transferirse en el bloque filtrado de la señal de salida 18. Como alternativa o adicionalmente, el formador de señales 52 puede configurarse para colocar una respuesta de sistema del filtro IIR de estado estacionario 36a basada en el preámbulo 26-1 delante de la señal de salida filtrada 18 o para insertar la misma en una localización predefinida diferente, por ejemplo, mediante una operación de desplazamiento o similar. Puesto que el preámbulo 26-1 o 26-2 es conocido en todo el sistema, y la estructura de filtro, así como los coeficientes del filtro IIR 36a son también conocidos, puede calcularse una respuesta de sistema del filtro IIR 36a en respuesta al preámbulo 26-1.

Como alternativa o adicionalmente, el formador de señales 52 o un medio de cálculo adicional, tal como el medio de cálculo 35, puede configurarse para ajustar el filtro IIR 36a a un estado (estacionario) que se obtiene cuando el filtro IIR 36a filtra el preámbulo 26-1. El filtro IIR 36a puede configurarse para filtrar la parte de señal 38a en un grado que no comprende el preámbulo 26-1 (parte de señal acortada 38a). En términos simplificados, la respuesta de sistema del filtro 36a puede sintetizarse en respuesta al preámbulo 26-1, ya que se conocen todos los parámetros (señal y estructura de filtro). Esto permite que el filtro 36a no tenga que filtrar (calcular) el preámbulo 26-1, de manera que

pueda guardarse la energía correspondiente y pueda evitarse una disipación de potencia debida a la filtración.

10

15

20

25

Una longitud de las partes de solapamiento 42 hace referencia a una serie de símbolos de la señal de datos extendida 27, una serie de bits de la misma y/o una longitud de filtro (cantidad de tomas de filtro y/o rutas de realimentación) del filtro. La longitud de las partes de solapamiento 42 puede elegirse de tal manera que comprenda una longitud (entrenamiento) que sea más larga que una profundidad de memoria o un número de coeficiente de los filtros IIR 36a-c. Un aumento de la parte de solapamiento 42 conduce a una disminución de los errores de IIR obtenidos por la paralelización. Con un solapamiento lo suficientemente grande, es decir, la longitud de la secuencia de entrenamiento y la parte de solapamiento 42, tales errores pueden reducirse a valores aceptables e insignificantes, por ejemplo, a valores que están por debajo del ruido de la transferencia o la cuantización en el sistema.

Por otro lado, un aumento en la longitud de la parte de solapamiento 42 conduce a datos de salida menos útiles (válidos) para cada filtro 36a-c por unidad de tiempo y, por lo tanto, fuerza más filtros paralelos 36a-c con el fin de mantener el mismo tiempo para calcular un bloque de la señal de datos filtrada 18. Por lo tanto, puede proporcionarse un equilibrio entre la reducción de los errores de la paralelización y la complejidad de la aplicación.

Cuando los filtros IIR 28a-c se incorporan como filtros THP en el medio de transmisión 10 y/o 20, los filtros IIR 36a-c también pueden incorporarse como filtros THP en su totalidad o en parte, mientras que los filtros IIR 36a-c se configuran, preferentemente, igual con respecto a la estructura de filtro.

En comparación con la paralelización de las cadenas de procesamiento de señales en el medio de transmisión 10 y 20, como se ilustra en las figuras 1 y 2, el filtro IIR 30 comprende una estructura paralelizada del propio filtro. La paralelización en el medio de transmisión 10 y 20 puede denominarse paralelización externa o nivel de paralelización I. Por otro lado, la paralelización en los filtros IIR individuales puede denominarse paralelización interna o nivel de paralelización II. Por lo tanto, una longitud de datos no obtenida de la señal de datos filtrada 18 puede permanecer sin cambios con respecto a la señal de datos extendida 27. La señal de referencia 26-1 (preámbulo) puede comprender una longitud correspondiente a una longitud de la parte de solapamiento 42.

- 30 La paralelización interna permite un filtrado rápido y eficiente de las señales de datos extendidas respectivas. Cuando se tiene la misma calidad de filtro, los (sub) filtros individuales 36a-c pueden comprender una complejidad menor (menos coeficientes de filtro u operaciones de cálculo) en comparación con una estructura de filtro de segmentación no paralelizada.

- Aunque la estructura de filtro 30 se ha descrito de tal manera que se filtra la señal de datos extendida 27, pueden aplicarse otras señales a la estructura de filtro 30, es decir, filtrarse, por ejemplo, señales recibidas desde un medio de recepción, como se explica a continuación.

- El concepto de paralelización descrito con referencia a la estructura de filtro 30 también puede aplicarse a los filtros 40 FIR (filtros de alimentación directa). Estos pueden llevarse a un estado estacionario (entrenado) por medio de las partes de solapamiento 42 y/o la señal de referencia 26-1 y/o 26-2 con el fin de combinar posteriormente las subseñales filtradas obtenidas y obtener una señal monolítica.

- En otras palabras, el error siempre presente sistemáticamente en el IIR (debido a la memoria de la realimentación) 45 se reduce a valores aceptados en el sistema de transferencia mediante una secuencia solapamiento/entrenamiento más larga 42, por ejemplo, más larga que el número de profundidad/coeficiente de memoria del THP. Con la elección correcta de la longitud de entrenamiento, los valores de error están por debajo del ruido por la transferencia o la cuantización en el sistema y, por lo tanto, prácticamente no restringen la precisión del filtro en comparación con un filtro no paralelizado pero cuantizado. Por medio de este método adaptado, que 50 también puede denominarse memorizar-entrenar-salvar, la respuesta de impulso del IIR paralelizado 30 aparece nuevamente como una señal calculada conjuntamente. En lugar de suministrar el primer elemento de filtro con ceros de antemano, como con el método de solapamiento y almacenamiento conocido para los filtros FIR, en memorizarentrenar- salvar, la secuencia de entrenamiento es un preámbulo conocido en todo el sistema al principio y al final, es decir, un primer y un último filtro en el nivel de paralelización interna II. Como resultado, los segmentos de datos del nivel de paralelización externa I también pueden unirse y todo el sistema aparece como una forma de onda calculada conjuntamente. El cálculo del filtrado del preámbulo prácticamente no es necesario para el primer elemento de filtro (filtro-IIR 36a). Puede producirse el restablecimiento de la memoria en el filtro IIR/THP a los valores obtenidos al calcular el preámbulo. Esto da como resultado una menor disipación de potencia en el filtro.

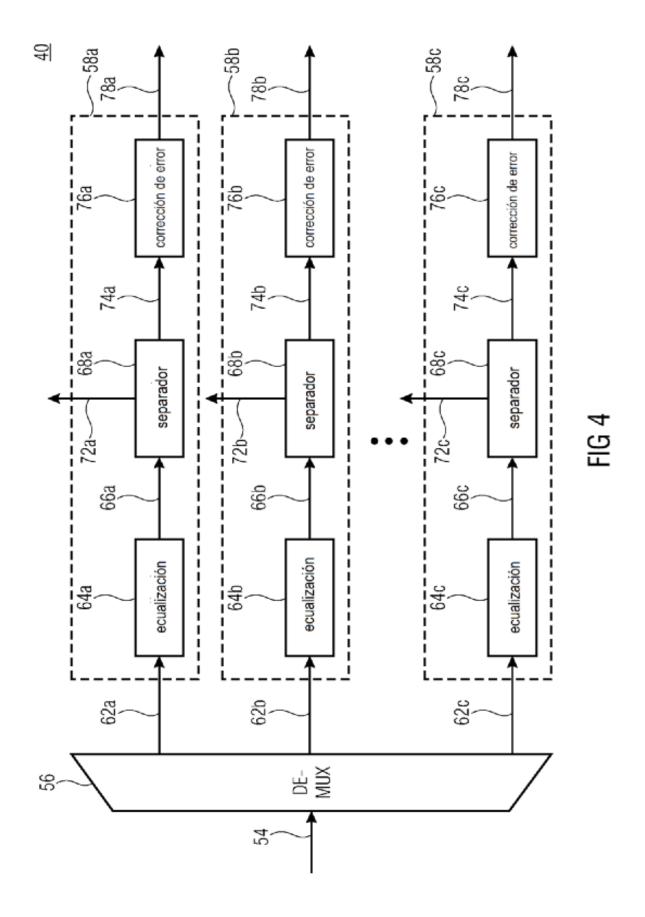

- La figura 4 muestra un diagrama de circuito de bloques esquemático de un medio de recepción 40 para recibir una señal de salida 54 transmitida por un medio de transmisión. Por ejemplo, la señal de salida 54 puede ser la señal de salida 12 del medio de transmisión 10 o 20, que se recibe a través de un medio de transferencia, tal como una línea o un medio de radio. Como alternativa, la señal de salida 54 también puede ser una señal de salida diferente, tal como desde un medio de transmisión de acuerdo con la técnica anterior, ya que la señal de salida 12 aparece como

si se calculara por una sola cadena de procesamiento de señales (técnica anterior), como se ha expuesto anteriormente. Aunque la señal de salida 12 comprende las señales de referencia añadidas, éstas también pueden considerarse como un encabezado que se repite periódicamente de un bloque de datos y/o pueden extraerse o ignorarse.

5

El medio de recepción 40 incluye un demultiplexor 56 y dos o más estructuras de recepción 58a-c. Por ejemplo, tres estructuras de recepción 58a-c se ilustran en la figura 4, mientras que los puntos entre las estructuras de recepción 58b y 58c indican que el medio de recepción 40 también puede comprender varias estructuras de recepción. Como alternativa, el medio de recepción 40 también puede comprender simplemente dos estructuras de recepción.

10

El demultiplexor 56 está configurado para generar una señal de recepción 62a, 62b y 62c, respectivamente, para cada estructura de recepción 58a-c o para los colectores de datos a los que se reenvían los datos. Por ejemplo, las estructuras de recepción 58a-c se asignan a un colector de datos, es decir, un receptor o un procesador de los datos, de manera que el demultiplexor 56 está, por ejemplo, configurado para dividir la señal de salida 54 en las señales de recepción 62a-c asignadas a los colectores de datos respectivos.

15

La disposición paralelizada de las estructuras de recepción 58a-c permite una decodificación y/o ecualización paralelizada de las señales de recepción respectivas 62a-c. Esto permite un alto caudal de datos y una baja complejidad de los filtros empleados. En particular, las señales de recepción 62a-c pueden ecualizarse y/o decodificarse de manera independiente y/o diferente entre sí.

20

Cada una de las estructuras de recepción 58a-c incluye un filtro de ecualización 64a, 64b y 64c, respectivamente, para ecualizar la señal de recepción 62a, 62b y 62c, respectivamente. Los filtros de ecualización 64a, 64b y/o 64c pueden incorporarse, por ejemplo, como una ecualización directa (ecualizador de alimentación directa-FFE).

25

Una señal de recepción ecualizada 66a, 66b y 66c obtenida de esta manera se recibe por un separador 68a, 68b y 68c, respectivamente. Posiblemente, el separador 68a, 68b y 68c está configurado para separar, es decir, para detectar y evaluar, una señal de referencia 72a, 72b y 72c, respectivamente, o para eliminar la señal de referencia 72a-c de la señal de recepción ecualizada 66a-c. Por ejemplo, la señal de referencia 72a-c puede ser la señal de referencia 26a-c. Por ejemplo, el separador 68a-c puede configurarse para determinar el principio o inicio de un bloque de datos en la señal de recepción ecualizada 66a-c. Por ejemplo, el separador 68a-c conoce el contenido de la señal de referencia respectiva 72a-c, de manera que, basándose en una operación de comparación, como una correlación cruzada de la señal de recepción ecualizada 66a-c con la señal de referencia, puede detectarse esta última. Pueden acoplarse uno o varios separadores 68a-c al demultiplexor 56, de manera que el mismo reciba información del uno o varios separadores 68a-c con respecto a la localización en la señal de salida 12 en la que se recibe o está contenida la señal de referencia. El multiplexor 56 puede configurarse para influir, basándose en esta información, en una división de la señal de salida 12 en las señales de recepción 66a-c, es decir, para sincronizar (correctamente) las mismas.

35

De acuerdo con las realizaciones, se conoce la información con respecto al tamaño del bloque de datos de las señales de recepción ecualizadas 66a-c en el separador respectivo 72a-c, de manera que la misma puede determinar, basándose en una medición de tiempo entre dos señales de referencia en la señal de recepción ecualizada 66a-c, una estimación con respecto a un desplazamiento de frecuencia. Por ejemplo, esto puede hacerse por medio de un control que comprueba las distancias (por ejemplo, en los relojes de símbolos) de las señales de referencia encontradas (preámbulos). El separador 68a-c puede configurarse, además, para realizar una sincronización de frecuencia y una sincronización de fase del reloj de símbolos en el receptor sobre la señal de salida 54 y/o las señales de recepción 66a-c. Con este fin, el separador 68a-c puede comprender los filtros correspondientes para la detección de errores de sincronización (detector de errores de temporización). Como

50

alternativa o adicionalmente, el separador 68a-c de una estructura de recepción 58a-c puede configurarse para eliminar la señal de referencia respectiva 72a-c de la señal de recepción ecualizada 66a, 66b y 66c, respectivamente, y/o para proporcionar la señal de referencia 72a-c a otros medios de cálculo para determinar la información anterior.

55

Como alternativa, la sincronización de frecuencia gruesa y fina y la sincronización de fase pueden incluirse en un solo separador, es decir, realizarse, lo que permite manejar esta tarea globalmente. De acuerdo con otra realización, esta función se implementa en una ruta paralela adicional con un filtro de ecualización y un separador, que solo evalúa un subconjunto de los datos con el fin de consumir una pequeña cantidad de energía.

60

En términos simplificados, el separador 68a-c o un medio de cálculo puede configurarse para determinar un espaciamiento temporal de la información de referencia en la señal de recepción respectiva y para determinar la información de corrección de fase basándose en una distancia temporal o para proporcionar la información de referencia 72a-c a un medio de cálculo, que realiza la determinación correspondiente de la distancia temporal así como de la información de corrección de fase.

Los separadores 68a, 68b y 68c están configurados para proporcionar una señal de salida 74a, 74b y 74c, respectivamente, que corresponde a la señal de recepción ecualizada 66a, 66b y 66c, respectivamente, o una versión de la misma que está separada de la señal de referencia 72a, 72b y 72c, respectivamente, a unos medios de cálculo 76a, 76b y 76c, respectivamente, de las estructuras de recepción 58a, 58b y 58c, respectivamente. Los medios de cálculo 76a-c están configurados para realizar una corrección de errores basándose en la información de redundancia contenida en las señales 74a-c, por ejemplo, basándose en una FEC en el medio de transmisión 10 o 20, y para proporcionar una señal de datos 78a-c que pueda reenviarse a uno o varios colectores de datos.

Por lo tanto, el medio de recepción 40 permite una paralelización de la estructura de recepción de un sistema de transferencia.

10

15

20

30

35

40

45

50

55

60

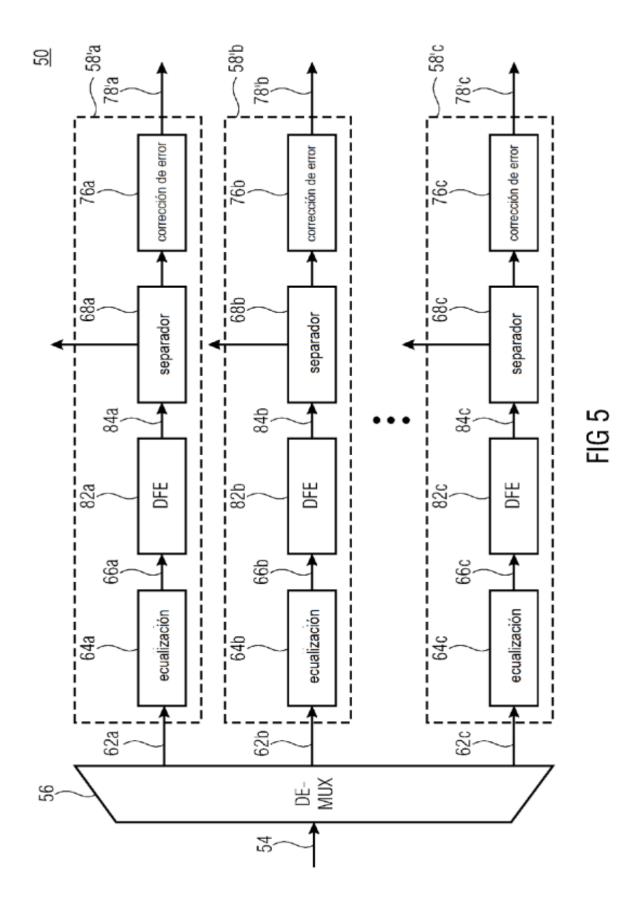

La figura 5 muestra un diagrama de circuito de bloques esquemático de un medio de recepción 50 de acuerdo con una realización adicional. En comparación con el medio de recepción 40, el medio de recepción 50 comprende, en las estructuras de recepción modificadas 58'a-c, un filtro de ecualización 82a, 82b y 82c, respectivamente, que se incorpora como un filtro de ecualizador de realimentación de decisión (DFE) y está dispuesto entre los filtros de ecualización 64a, 64b y 64c, respectivamente, que se incorporan como filtros FIR, y los separadores 68a, 68b y 68c, respectivamente. Los filtros DFE 82a-c comprenden una estructura IIR. Los filtros DFE 82a-c se incorporan como filtros IIR paralelizados, como se describe para el filtro IIR 30 en la figura 3, es decir, los filtros DFE 82a-c comprenden una pluralidad de (sub) filtros IIR paralelizados 36a-c. Los filtros DFE 82a-c están configurados para filtrar la señal ecualizada 66a, 66b o 66c y para emitir una señal ecualizada filtrada correspondiente 84a, 84b y 84c, respectivamente, y para proporcionar la misma al separador 68a, 68b y 68c, respectivamente. Las estructuras de recepción 58'a-c están configuradas para emitir una señal de datos modificada 78'a-c en comparación con las señales de datos 78a-c, que está influenciada por la ecualización adicional.

La disposición adicional de los filtros DFE 82a-c permite una adaptación a las características de variación en el tiempo de un canal de transferencia a través del que se recibe la señal de salida 54. Una paralelización por el nivel de paralelización II de estos filtros IIR permite un alto número de operaciones de filtrado paralelizadas.

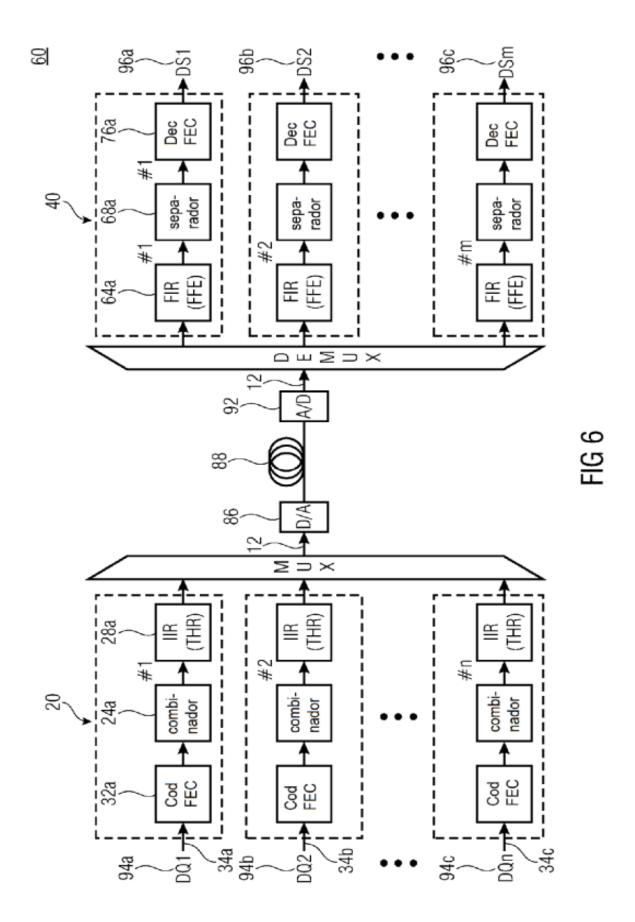

La figura 6 muestra un diagrama de circuito de bloques esquemático de un sistema de transferencia 60 que incluye el medio de transmisión 20 y el medio de recepción 40. Como alternativa, el sistema de transferencia 60 también puede incluir el medio de transmisión 10 y/o el medio de recepción 50. El sistema de transferencia 60 incluye además un convertidor de digital a analógico (D/A) 86 configurado para convertir la señal de salida 12 en una señal analógica de manera que la señal de salida pueda transmitirse con una potencia de señal correspondiente. El sistema de transferencia 60 incluye un canal de transferencia 88 y un convertidor de analógico a digital (A/D) 92 configurado para recibir la señal de salida 12 transferida a través del canal de transferencia 88 y para digitalizar la misma para su posterior procesamiento.

El medio de transmisión 20 incluye un primer número n de fuentes de datos. El medio de recepción 40 incluye un segundo número m de colectores de datos. El primer número n y el segundo número m comprenden, cada uno de los mismos, un valor de ≥ 2 y pueden comprender un mismo valor. Esto significa que, por ejemplo, una fuente de datos 94a-c proporciona o genera una señal de fuente 34a, 34b y 34c, respectivamente, que se asigna a un colector de datos 96a-c, que también puede describirse como una conexión 1:1. Como alternativa, una señal de fuente de datos 34a, 34b y/o 34c puede asignarse a al menos dos colectores de datos 96a, 96b y 96c, lo que permite un número de n<m y puede denominarse conexión 1:x. Como alternativa o adicionalmente, varias fuentes de datos 94ac pueden proporcionar, cada una de las mismas, un flujo de datos 34a-c asignado respectivamente a un colector de datos 96a-c y permitir un número de n>m, que también puede describirse como conexión x:1. Además, son posibles formas mixtas de transferencia de datos, tales como las conexiones n:m, siendo n diferente de m, tal como 3:2 o 2:3. Por ejemplo, esto puede surgir debido a una configuración de las fuentes de datos o los colectores de datos, pero también simplemente debido a una paralelización diferente para el mismo caudal de cálculo. En otras palabras, en el sistema de transferencia 60, la codificación y la predistorsión de canal no se produce en el flujo de datos en serie multiplexado sino que un encuadre de los datos ya se realiza antes del multiplexor con el fin de asignar correctamente los datos en el receptor para la decodificación en bloque. Se emplea una paralelización anidada en el procesamiento de datos. Hay un nivel de paralelización externa I en los bloques FEC y un nivel de paralelización interna II en cada uno de los bloques FEC.

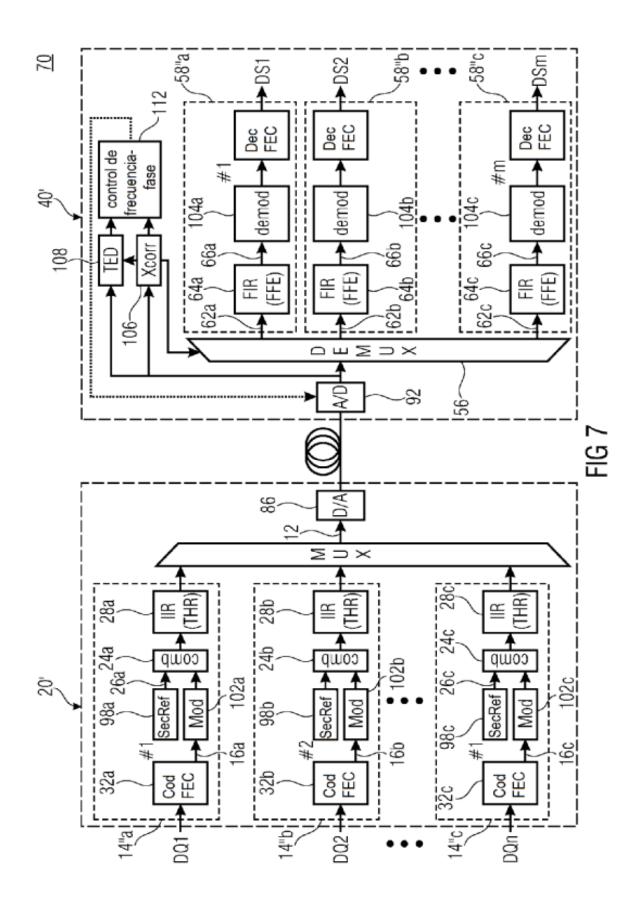

La figura 7 muestra un diagrama de circuito de bloques esquemático de un sistema de transferencia 70 que incluye, en comparación con el medio de transmisión 20, un medio de transmisión modificado 20' y, en comparación con el medio de recepción 40, un medio de recepción modificado 40'. El medio de transmisión 20' incluye el convertidor D/A 86. En comparación con el medio de transmisión 20, el medio de transmisión 20' se modifica adicionalmente de tal manera que las estructuras de filtro 14"a-c incluyen, cada una de las mismas, una memoria de señal 98a-c configurada para almacenar o generar la señal de referencia respectiva 26a-c y para proporcionar la señal de referencia 26a-c al combinador respectivo 24a-c. Los combinadores 24a-c pueden configurarse para escalar la señal de referencia 26a-c antes de insertar la misma en la señal de datos extendida. La memoria de señal 98a-c puede ser cualquier memoria volátil o no volátil, tal como una RAM, ROM, (E)EPROM, FLASH o similares. Como alternativa, en

lugar de la memoria de señal 98a-c, puede disponerse un generador de señal para generar la señal de referencia 26a-c.

Cada una de las estructuras de filtro 14"a-c incluye además un modulador 102a-c dispuesto entre el bloque de redundancia respectivo 32a-c y el combinador respectivo 24a-c y configurado para modular la señal de datos 16a-c con un grado de modulación, por ejemplo, con una modulación de una frecuencia, una fase y/o una amplitud. Por ejemplo, uno o varios moduladores 102a-c pueden configurarse para modular la señal de datos respectiva 16a-c con un PAM o PCM que tiene un grado de modulación de 2, 3, 4, 5, 6, 7, 8 o más niveles. La señal de referencia respectiva 16a-c puede obtenerse a partir de la memoria de señal respectiva 98a-c con un grado de modulación que es inferior al grado de modulación del modulador 102a-c con el fin de obtener una fiabilidad de interferencia aumentada de la señal de salida 12 con respecto a las señales de referencia 26a-c y con respecto a las señales de datos 16a-c.

10

35

40

45

55

60

El medio de recepción 40' incluye el convertidor A/D 92. Las estructuras de recepción 58"a-c del medio de recepción 40', que se modifican en comparación con las estructuras de recepción 58 y 58', comprenden un demodulador 104a, 104b y 104c, respectivamente, configurado para demodular la señal ecualizada 66a-c en función del grado o método de modulación de los moduladores 102a-c. Los demoduladores 104a-c pueden integrarse en los separadores 68a-c, pueden incluirlos o sustituirlos.

La estructura de recepción 40' incluye además un correlacionador cruzado 106 configurado para determinar la señal de referencia por medio de una correlación cruzada en una señal de salida digitalizada obtenida por el convertidor A/D 92, es decir, una secuencia de datos de la señal de salida que comprende la señal de referencia en forma filtrada. Un resultado de la correlación cruzada puede proporcionarse, por ejemplo, en una señal digital o una señal de tensión o una señal de corriente, indicando la amplitud de la misma una medida de la correlación (correspondencia) de la señal de referencia recibida y la depositada (esperada). El correlacionador cruzado 106 está configurado para suministrar información con respecto a la posición de la señal de referencia en la señal de salida 12 al demultiplexor 56 de manera que, por medio del demultiplexor 56, pueda realizarse una división correcta de la señal de salida 12 en las señales de recepción 62a-c o de la señal de referencia y los bloques FEC a los bancos de filtro (estructuras de recepción 58"a-c) y/o pueda corregirse una división errónea. Esta división se llama sincronización de bloques o sincronización de tramas. En este caso, el correlacionador cruzado 106 puede incluir una copia de un filtro 64 y/o un filtro separado para extraer el error de tiempo.

La estructura de recepción 40' incluye además un detector de errores de temporización 108 (TED) configurado para comparar entre sí la señal de referencia (conocida o depositada) y la señal de referencia recibida, y para determinar un desplazamiento de tiempo (error de temporización) de la señal de referencia de recepción con respecto a la señal de referencia depositada. Por ejemplo, el detector de errores de temporización 108 puede incorporarse como un TED basado en ecualización y/o implementar un algoritmo de Müller-Müller, y está configurado para emitir información con respecto al desplazamiento de temporización, por ejemplo, en una señal digital o una analógica. El detector de errores de temporización 108 puede incluir una copia de un filtro 64 y/o un filtro separado para extraer el error de temporización.

La estructura de recepción 40' incluye además un medio 112 para determinar y/o monitorizar la frecuencia y/o la fase de la señal de salida 12. El medio 112 está configurado para determinar, basándose en la información obtenida por el detector de errores de temporización 108 y el correlacionador cruzado 106, los valores de corrección con respecto a una frecuencia de muestreo y/o una fase de muestreo para el convertidor A/D 92, y para ajustar el convertidor A/D 92 por medio de los valores de corrección con el fin de obtener y/o aumentar una sincronización del convertidor A/D 92 con respecto a la señal de salida 12.

La información del correlacionador cruzado 106 sirve para un ajuste más grueso de la corrección de la frecuencia y/o la fase (sincronización del convertidor A/D 92) del receptor 40' al transmisor 20' o el sistema de transferencia 70, y los valores del detector de errores de temporización 108 sirven para un ajuste más fino de la misma.

Los bloques FFE (ecualización) 64a-c incluyen una operación de módulo para permitir una demodulación correcta de las señales de datos 16a-c filtradas por medio de la operación de módulo en los filtros THP 28a-c. En términos simplificados, los datos recibidos entran en el FIR/FFE, en el que va primero un segmento con una señal de referencia filtrada. Cuando un THP está activo en el transmisor, el cual, al ser un THP, posiblemente siempre realice una operación de módulo, se calcula una operación de módulo de manera preferible o posiblemente obligatoria antes de una demodulación y después de la FFE en el receptor. En una sincronización de receptor, el correlacionador cruzado 106 (Xcorr) busca en primer lugar el preámbulo (secuencia de referencia). Esto no tiene que producirse en todo el flujo de datos, sino que también puede realizarse en "instantáneas" grabadas en distancias. Esto permite reducir los requisitos de velocidad del procesamiento del correlacionador cruzado. Por ejemplo, el correlacionador cruzado 106 proporciona información tal como la posición determinada del preámbulo y la altura de los picos de correlación en el tiempo (es decir, el historial de estos valores para, por ejemplo, 20-100 instantáneas). La posición del preámbulo actual sirve al demultiplexor 56 para dividir correctamente los bloques de datos

(preámbulo + bloque FEC) en los bancos de filtros.

15

20

30

Preferentemente, el reloj de receptor es igual a la velocidad en baudios del transmisor 20', es decir, hay un valor de muestreo por símbolo. Un sobremuestreo y su control por medio del controlador de fase de frecuencia (dispositivo) 112, por ejemplo, dos valores de muestreo por símbolo, y una sincronización digital a través de un filtro de interpolación, es posible con el fin de obtener una mayor precisión, pero consume recursos (posiblemente en exceso) a altas velocidades de reloj específicas.

Como alternativa, las operaciones del correlacionador cruzado 106, el detector de errores de temporización 108 y/o el dispositivo 112 para determinar y/o controlar la frecuencia y/o la fase de la señal de salida 12 pueden realizarse total o parcialmente por el separador 68b.

Para la etapa de paralelización interna II, los filtros de compensación (filtros de ecualización) y un modulador 102a-c, o un combinador 24a-c y un demodulador 104a-c, o un separador 68a-c están paralelizados. El preámbulo (señal de referencia) también pasa a través del procesamiento de señales en el transmisor y se transfiere para el entrenamiento de los filtros de compensación paralelizados en la parte de recepción. En el caso más simple, el multiplexor y el demultiplexor pueden operar con un método similar al "Round Robin", es decir, una trama se transmite posteriormente desde cada fuente de datos y las tramas se dividen sucesivamente en los colectores de datos en el receptor. Como alternativa, puede añadirse un breve campo de información al preámbulo, por ejemplo, que contenga una ID de la fuente de datos, una ID del colector de datos, un número de trama continua y/o posiblemente una marca de tiempo. De esta manera, las tramas de cualquier fuente de datos pueden transmitirse en el transmisor, según sea necesario, y pueden asignarse fácilmente a los colectores de datos correctos en el receptor.

La estructura de ecualización del filtro THP en el lado del transmisor y el FFE en el lado del receptor puede implementarse de manera eficiente para caudales de datos muy altos.

Las realizaciones descritas anteriormente permiten una aplicación en aparatos para una transferencia de banda base, en transferencias de datos de alta velocidad, en particular usando un filtrado digital así como un procesamiento de datos digital paralelizado. Las señales de las fuentes de datos independientes pueden calcularse en paralelo y aparecer en una señal de salida como una forma de onda procesada monolíticamente, lo que permite una fácil descodificación.

El preámbulo, es decir, la señal de referencia, se adjunta, por ejemplo, al bloque FEC respectivo y/o se coloca delante del mismo en el transmisor después del codificador FEC (bloque de redundancia 32a-c). Como se describe en la figura 3, un preámbulo colocado delante también puede ser una salida en un extremo de la señal filtrada de un filtro.

El preámbulo puede usarse en el lado del transmisor con el fin de servir como una secuencia de entrenamiento para el (subfiltro) THP para permitir una paralelización (nivel de paralelización I). El preámbulo puede servir además como una secuencia de entrenamiento para los filtros FIR (ecualización 64a-c) con el fin de permitir una paralelización. El preámbulo se usa además para determinarse como un marcador para un inicio de bloque o un final de bloque para la FEC (corrección de error 76a-c). El inicio de bloque puede encontrarse a través de una correlación con el preámbulo conocido. La comprobación de las distancias de temporización (posiblemente en los relojes de símbolos) de los preámbulos encontrados puede emplearse para una estimación de desplazamiento de frecuencia aproximada. Además, el preámbulo puede usarse para una sincronización fina de la frecuencia y la fase. En este caso, los detectores de errores de temporización pueden usarse como filtros especiales para un control más preciso.

Los usos mencionados no son exhaustivos. Diferentes usos pueden llevar a un requisito diferente con respecto a la longitud del preámbulo. Mientras que un preámbulo relativamente largo puede ser necesario para determinar el inicio de bloques o un final de bloque y/o una sincronización de frecuencia aproximada con el fin de permitir un cálculo riguroso por medio de la correlación cruzada, la longitud del preámbulo puede disminuir cada vez más si una implementación de sistema se basa simplemente en una paralelización de los bloques THP (nivel de paralelización II), una sincronización fina de la fase y/o la frecuencia o una paralelización de los bloques FFE (64a-c). La implementación puede cambiar con los canales de transferencia 88 diferentes entre sí. Por ejemplo, para detectar un bloque de inicio, un preámbulo puede tener una longitud de, por ejemplo, al menos 30, al menos 40 o al menos 50 símbolos.

Las realizaciones anteriores también pueden realizarse como filtros basados en software, en los que se implementan estructuras de filtro paralelizadas y estructuras de recepción basadas en una multitud de núcleos de computación que trabajan en paralelo.

Aunque algunos aspectos se han descrito dentro del contexto de un dispositivo, se entiende que dichos aspectos también representan una descripción del método correspondiente, de manera que un bloque o un componente

estructural de un dispositivo también debe entenderse como una etapa del método correspondiente o como una característica de una etapa del método. Por analogía con esto, los aspectos que se han descrito dentro del contexto de o como una etapa del método también representan una descripción de un bloque o detalle o característica correspondiente de un dispositivo correspondiente. Algunas o todas las etapas del método pueden realizarse mientras se usa un dispositivo de hardware, tal como un microprocesador, un ordenador programable o un circuito electrónico. En algunas realizaciones, algunas o varias de las etapas más importantes del método pueden realizarse por un dispositivo de este tipo.

Dependiendo de los requisitos de implementación específicos, las realizaciones de la invención pueden implementarse en hardware o en software. La implementación puede efectuarse mientras se usa un medio de almacenamiento digital, por ejemplo, un disquete, un DVD, un disco Blu-ray, un CD, una ROM, una EPROM, una EPROM, una memoria FLASH, un disco duro o cualquier otra memoria magnética u óptica que tenga señales de control legibles electrónicamente almacenadas en la misma, que pueda cooperar, o coopere, con un sistema informático programable de tal manera que se realice el método respectivo. Es por esto que el medio de almacenamiento digital puede ser legible por ordenador.

En general, las realizaciones de la presente invención pueden implementarse como un producto de programa informático que tiene un código de programa, siendo el código del programa eficaz para realizar cualquiera de los métodos cuando el producto de programa informático se ejecuta en un ordenador.

Otras realizaciones incluyen el programa informático para realizar cualquiera de los métodos descritos en el presente documento, almacenándose dicho programa informático en un soporte legible por máquina.

20

35

En otras palabras, una realización del método de la invención es, por lo tanto, un programa informático que tiene un código de programa para realizar cualquiera de los métodos descritos en el presente documento, cuando el programa informático se ejecuta en un ordenador. El soporte de datos, el medio de almacenamiento digital o el medio grabado son habitualmente tangibles o no volátiles.

Una realización adicional del método de la invención es, por lo tanto, un flujo de datos o una secuencia de señales que representan el programa informático para realizar cualquiera de los métodos descritos en el presente documento. El flujo de datos o la secuencia de señales pueden configurarse, por ejemplo, para transferirse a través de un enlace de comunicación de datos, por ejemplo, a través de Internet.

Una realización adicional incluye un medio de procesamiento, por ejemplo, un ordenador o un dispositivo lógico programable, configurado o adaptado para realizar cualquiera de los métodos descritos en el presente documento.

Una realización adicional incluye un ordenador en el que se instala el programa informático para realizar cualquiera de los métodos descritos en el presente documento.

En algunas realizaciones, puede usarse un dispositivo lógico programable (por ejemplo, una matriz de puertas programables en campo, un FPGA) para realizar algunas o todas las funcionalidades de los métodos descritos en el presente documento. En algunas realizaciones, una matriz de puertas programables en campo puede cooperar con un microprocesador para realizar cualquiera de los métodos descritos en el presente documento. En general, los métodos se realizan, en algunas realizaciones, por cualquier dispositivo de hardware. Dicho dispositivo de hardware puede ser cualquier hardware de aplicación universal, tal como un procesador informático (CPU), o puede ser un hardware específico del método, tal como un ASIC.

Las realizaciones descritas anteriormente simplemente representan una ilustración de los principios de la presente invención. Se entiende que otros expertos en la materia apreciarán modificaciones y variaciones de las disposiciones y detalles descritos en el presente documento. Es por esto que se pretende que la invención esté limitada solo por el alcance de las siguientes reivindicaciones en lugar de por los detalles específicos que se han presentado en el presente documento por medio de la descripción y la exposición de las realizaciones.

#### **REIVINDICACIONES**

1. Medio de transmisión (10; 20; 20') para transmitir una señal de salida (12), que comprende:

20

25

35

- una primera estructura de filtro (14a; 14'a) que comprende un primer combinador (24a) configurado para extender una primera señal de datos (16a) por una primera señal de referencia (26a) con el fin de obtener una primera señal de datos extendida (27a), y que comprende un primer filtro IIR (28a) para filtrar la primera señal de datos extendida (27a) con el fin de obtener una primera señal de datos filtrada (18a):

- una segunda estructura de filtro (14b; 14'b) que comprende un segundo combinador (24b) configurado para extender una segunda señal de datos (16b) por una segunda señal de referencia (26b) con el fin de obtener una segunda señal de datos extendida (27b), y que comprende un segundo filtro IIR (28b) para filtrar la segunda señal de datos extendida (27b) con el fin de obtener una segunda señal de datos filtrada (18b);