# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 715 986

51 Int. Cl.:

G05F 1/46 (2006.01) H04M 19/00 (2006.01) H02J 9/00 (2006.01)

12 TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 16.04.2012 PCT/CN2012/074136

(87) Fecha y número de publicación internacional: 24.10.2013 WO13155670

(96) Fecha de presentación y número de la solicitud europea: 16.04.2012 E 12874565 (0)

(97) Fecha y número de publicación de la concesión europea: 19.12.2018 EP 2745386

(54) Título: Circuito de alimentación eléctrica de espera para sistema de intercomunicación de bus de 2 hilos y su aparato

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **07.06.2019**

(73) Titular/es:

ABB SCHWEIZ AG (100.0%) Brown Boveri Strasse 6 5400 Baden, CH

(72) Inventor/es:

ZHOU, DALIN; ZHANG, YANGPENG; LIU, MINGYUAN; LI, HUAPING y YE, ZHITIAN

(74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

## **DESCRIPCIÓN**

Circuito de alimentación eléctrica de espera para sistema de intercomunicación de bus de 2 hilos y su aparato

#### Campo de la invención

5

10

15

20

25

30

35

40

50

55

La invención se refiere al campo técnico del sistema de intercomunicación, y más en particular a un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos

## Antecedentes de la invención

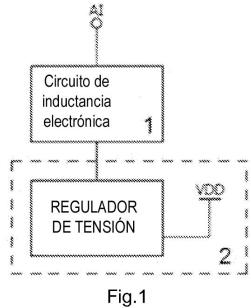

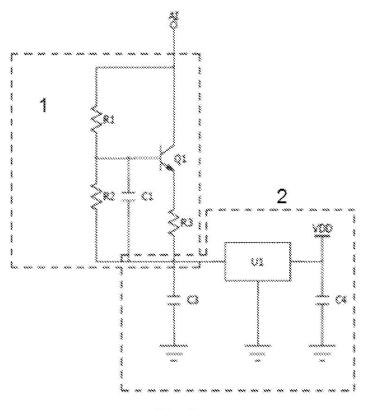

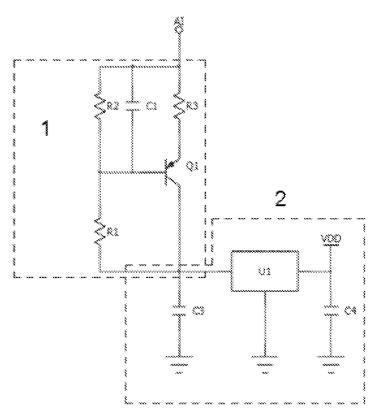

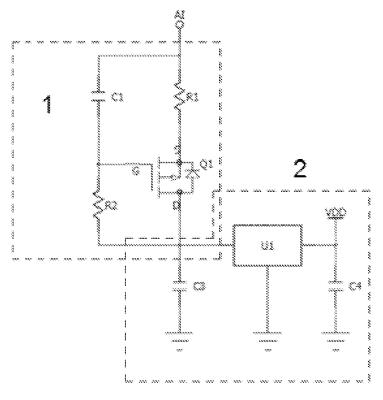

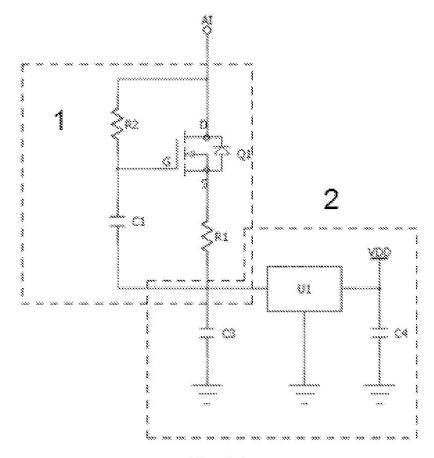

Para implementar un sistema de intercomunicación de vídeo de 2 hilos, la potencia de corriente continua, la señal del portador de vídeo, la señal de audio y la señal de datos de comando deben transmitirse en un bus común de 2 hilos simultáneamente. Por lo tanto, los circuitos de alimentación eléctrica de la alimentación eléctrica del sistema y sus dispositivos deben comprender un componente de inductancia conectado al bus común en serie, lo que permite el paso de la corriente continua mientras que también suprime la señal de corriente alterna. Sin embargo, es de sentido común para los expertos en la materia que la frecuencia de la señal de audio es baja a 300Hz si se utiliza un inductor de bobina como componente de inductancia. Con el fin de lograr la suficiente impedancia y capacidad de alimentación eléctrica, el tamaño de dicho inductor será muy grande. La figura 1 ilustra un diagrama de circuito de un circuito de alimentación eléctrica para un sistema de intercomunicación de bus de 2 hilos según la técnica anterior. Como se muestra en la figura 1, un circuito electrónico de inductancia se puede usar generalmente para reemplazar el inductor de la bobina para reducir su tamaño. En detalle, las figuras 2a-2d ilustran individualmente un diagrama de circuito de 4 circuitos de alimentación eléctrica convencionales para un sistema de intercomunicación de bus de 2 hilos según la técnica anterior. Sin embargo, solo hay una alimentación eléctrica de sistema para un sistema de intercomunicación de 2 hilos en un edificio; por lo tanto, incluso para un gran sistema de intercomunicación de 2 hilos con un gran número de cargas de dispositivos, solo permite un número muy pequeño de dispositivos en estado operativo, mientras que la mayoría absoluta de las cargas de dispositivos deben estar en estado de espera.

Como se describió anteriormente, los circuitos de alimentación eléctrica convencionales para un sistema de intercomunicación de 2 hilos consisten en un circuito de inductancia electrónica y un circuito regulador de tensión, que ofrecen alimentación eléctrica tanto a los circuitos en espera como a los circuitos de operación. Mientras que la impedancia de corriente alterna de un circuito de inductancia electrónica es limitada, especialmente una alimentación eléctrica de corriente grande con un circuito de inductancia electrónica para un circuito de operación. Sin embargo, todas las cargas de dispositivos de un sistema de intercomunicación de 2 hilos están conectadas al bus común en serie, lo que significa que la impedancia de corriente alterna de n cargas de dispositivos es 1/n de una carga de dispositivo. Cuando la cantidad de cargas del dispositivo es grande, la impedancia de la corriente alterna será insuficiente, el tamaño del sistema de intercomunicación de 2 hilos será limitado y la calidad de audio de dicho sistema de intercomunicación de 2 hilos será mucho peor.

En consecuencia, las soluciones existentes que incluyen la técnica anterior mencionada anteriormente no pueden lograr una impedancia de corriente alterna más alta en el estado de espera cuando el sistema de intercomunicación de bus de 2 hilos está conectado con una gran cantidad de cargas de dispositivos. Debido a los problemas mencionados anteriormente, la presente invención consiste en proponer un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos y un aparato del mismo.

El documento US 2003/0011247 A1 divulga un dispositivo de suministro de energía en el cual, para aumentar la velocidad de aumento de una tensión de salida y para suprimir una caída de tensión cuando se cambia entre dispositivos de suministro de energía, durante un segundo modo de operación en el que el suministro de energía es detenido, un interruptor de salida se apaga y un circuito generador de tensión de referencia aplica una tensión de referencia, que equivale a una tensión de puerta en estado estable durante el suministro de energía a la puerta de un transistor de salida.

### Sumario de la invención

El objeto principal de la presente invención es proporcionar un circuito de alimentación eléctrica con una impedancia de corriente alterna suficientemente grande para el sistema de intercomunicación de bus de 2 hilos incluso en el estado de espera. Por consiguiente, la presente invención proporciona un circuito de alimentación eléctrica de espera para el sistema de intercomunicación de bus de 2 hilos y su aparato.

De acuerdo con un aspecto de la presente invención, proporciona un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos. El circuito de la alimentación eléctrica de espera está separado en dos módulos de alimentación eléctrica; en el que el primer módulo de alimentación eléctrica es una alimentación eléctrica para el circuito en espera y el segundo módulo de alimentación eléctrica es una alimentación eléctrica para el circuito de operación; la alimentación eléctrica al circuito de operación se desconecta mediante un interruptor de corriente constante cuando la carga del dispositivo se encuentra en estado de espera; y la alimentación eléctrica del circuito en espera comprende un circuito de corriente constante, dicho circuito de corriente constante constante principal y un circuito de corriente constante auxiliar, en el que dicho circuito de corriente constante principal está configurado para hacer que la corriente a través de una

trayectoria de corriente constante principal de dicho circuito de corriente constante principal sea estable y en el que dicho circuito de corriente constante auxiliar ofrece una corriente de polarización para el circuito de corriente constante principal.

Según otra realización preferida de la presente invención, la alimentación eléctrica del circuito en espera comprende además un circuito de corriente constante conectado entre el terminal de entrada y un circuito regulador en espera.

Según otra realización preferida de la presente invención, el circuito de corriente constante comprende además un circuito de corriente constante principal y un circuito de corriente constante auxiliar, en el que el circuito de corriente constante principal está configurado para hacer que la corriente a través de la trayectoria de corriente constante sea estable; y el circuito de corriente constante auxiliar está configurado para ofrecer una corriente de polarización suficiente para el circuito de corriente constante principal con un tensión de polarización bastante más bajo y mantener una CA bastante mayor.

10

15

35

50

De acuerdo con otra realización preferida de la presente invención, el circuito de corriente constante principal comprende además una trayectoria de corriente constante principal y una unidad reguladora de tensión, en la que la unidad reguladora de tensión está configurada para hacer que la tensión sea estable, independientemente de la temperatura o la corriente fluctúe y hace que la impedancia de la corriente alterna de la trayectoria de corriente principal muy alta.

Según otra realización preferida de la presente invención, la trayectoria de corriente constante principal está a lo largo de un primer transistor y una primera resistencia; en el que el colector del primer transistor está conectado al terminal de entrada y el emisor del primer transistor está conectado con la primera resistencia en serie.

Según otra realización preferida de la presente invención, la unidad reguladora de tensión comprende, además: un diodo y un primer diodo Zener conectados de forma inversa en serie, una segunda resistencia y un primer condensador conectados en serie; y el diodo y el primer diodo Zener conectados con la segunda resistencia y el primer condensador en paralelo.

Según otra realización preferida de la presente invención, el circuito regulador de espera comprende además un conjunto de resistencias constituidas por una tercera resistencia y una cuarta resistencia conectadas en serie, un segundo diodo Zener y un segundo condensador; y el conjunto de resistencias, el segundo diodo Zener y el segundo condensador están conectados en paralelo y conectados a tierra.

Según otra realización preferida de la presente invención, la unidad reguladora de tensión comprende además un primer condensador y un primer diodo Zener conectados en paralelo.

30 Según otra realización preferida de la presente invención, el circuito regulador de espera comprende además un segundo diodo Zener y un segundo condensador conectado en paralelo y conectado a tierra.

Según otra realización preferida de la presente invención, el circuito de corriente constante auxiliar comprende una trayectoria de corriente de control y una segunda trayectoria de corriente de control, en la que la trayectoria de corriente de control está a lo largo de un segundo transistor y una quinta resistencia; la segunda trayectoria de corriente de control está a lo largo de un tercer transistor y una sexta resistencia; la quinta resistencia está conectada a la base y el emisor del tercer transistor en paralelo; y la sexta resistencia está conectada al colector y la base del segundo transistor en paralelo.

Según otra realización preferida de la presente invención, el circuito de corriente constante auxiliar comprende además un tercer condensador conectado al colector y el emisor del tercer transistor en paralelo.

De acuerdo con otra realización preferida de la presente invención, el circuito de alimentación eléctrica de espera comprende además una MCU, configurada para controlar el interruptor de corriente constante que se va a encender/apagar.

Según otra realización preferida de la presente invención, la alimentación eléctrica del circuito de operación comprende además un circuito electrónico de inductancia y un segundo circuito regulador de tensión.

De acuerdo con otra realización preferida de la presente invención, el interruptor de corriente constante está conectado entre la alimentación eléctrica del circuito en espera y la alimentación eléctrica del circuito de operación, configurado para apagarse por la alimentación eléctrica del circuito de operación cuando la carga del dispositivo está en estado de espera.

Según otra realización preferida de la presente invención, el interruptor de corriente constante comprende además al menos dos transistores, tres resistencias y un cuarto condensador, en el que la séptima resistencia está conectada al emisor y la base del cuarto transistor en paralelo; la base del cuarto transistor está conectada al colector del quinto transistor; la octava resistencia está conectada entre el emisor del quinto transistor y la tierra; y el cuarto condensador está conectado entre la base del quinto transistor y la tierra.

Según otra realización preferida de la presente invención, el colector del cuarto transistor está conectado al circuito

de inductancia electrónica; y la novena resistencia está conectada a la base del quinto transistor y una MCU.

De acuerdo con otra realización preferida de la presente invención, el circuito de inductancia electrónica comprende: una trayectoria de circuito principal a lo largo de un inductor y un terminal de fuente y un terminal de drenaje de un FET entre el condensador del terminal de entrada conectado en paralelo y conectado a tierra.

Según otra realización preferida de la presente invención, el circuito de corriente constante auxiliar comprende una trayectoria de corriente de control y una segunda trayectoria de corriente de control, en la que la trayectoria de corriente de control está a lo largo de un segundo transistor y una quinta resistencia; la segunda ruta de corriente de control está a lo largo de una tercera resistencia y un sexto transistor; la quinta resistencia está conectada a la base y el emisor del tercer transistor en paralelo; y la sexta resistencia está conectada al colector y la base del segundo transistor en paralelo.

De acuerdo con otra realización preferida de la presente invención, el circuito de corriente constante auxiliar comprende además un tercer condensador conectado al colector y el emisor del tercer transistor en paralelo.

De acuerdo con otra realización preferida de la presente invención, el circuito de suministro de energía de espera comprende además una MCU, configurada para controlar el interruptor de corriente constante que se va a encender/apagar.

De acuerdo con otra realización preferida de la presente invención, la alimentación eléctrica al circuito de operación comprende además un circuito de inductancia electrónica y un segundo circuito regulador de tensión.

De acuerdo con otra realización preferida de la presente invención, el interruptor de corriente constante está conectado entre la alimentación eléctrica al circuito en espera y la alimentación eléctrica al circuito de operación, configurado para apagarse por la alimentación eléctrica al circuito de operación cuando la carga del dispositivo es en el estado de espera.

De acuerdo con otra realización preferida de la presente invención, el interruptor de corriente constante comprende además al menos dos transistores, tres resistencias y un cuarto condensador, en el que la séptima resistencia está conectada al emisor y la base del cuarto transistor en paralelo; la base del cuarto transistor está conectada al colector del quinto transistor; la octava resistencia está conectada entre el emisor del quinto transistor y la tierra; y el cuarto condensador está conectado entre la base del quinto transistor y la tierra.

Según otra realización preferida de la presente invención, el colector del cuarto transistor está conectado al circuito electrónico de inductancia; y la novena resistencia está conectada a la base del quinto transistor y una MCU.

De acuerdo con otra realización preferida de la presente invención, el circuito de inductancia electrónica comprende:

una trayectoria de circuito principal a lo largo de un inductor y un terminal de origen y un terminal de drenaje de un

FET entre el terminal de entrada y el terminal de salida del circuito de inductancia electrónica, en el cual el inductor

está conectado al terminal de origen del FET; una resistencia y un diodo de marcha libre conectados individualmente

al inductor en paralelo; y una ruta de circuito secundaria a lo largo de un condensador conectado con una segunda

resistencia en serie entre el terminal de entrada y el terminal de salida, que está conectado a la ruta del circuito

principal en paralelo.

De acuerdo con otra realización preferida de la presente invención, el inductor y el FET están conectados en serie, y el nodo entre el condensador y la segunda resistencia está conectado con el terminal de puerta del FET.

De acuerdo con otra realización preferida de la presente invención, el FET es un FET de canal P, y el terminal de drenaje del FET de canal P está conectado al terminal de salida; y el inductor está conectado entre el terminal de entrada y el terminal de origen del FET de canal P.

De acuerdo con otra realización preferida de la presente invención, el FET es un FET de canal N, y el terminal de origen del FET de canal N está conectado al terminal de entrada; y el inductor está conectado entre el terminal de origen del FET de canal N y el terminal de salida.

Según otro aspecto de la presente invención, proporciona un aparato para un sistema de intercomunicación de bus de 2 hilos. El aparato comprende cualquiera de los circuitos de alimentación eléctrica de espera mencionados anteriormente.

Las realizaciones de la presente invención proporcionan un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos y un aparato del mismo, que logra una mayor impedancia de corriente alterna en el estado de espera y una alta calidad de audio para un sistema de intercomunicación de bus de 2 hilos.

# Breve descripción de los dibujos

15

20

25

40

50

El objeto de la invención se explicará con más detalle en la siguiente descripción con referencia a las realizaciones ejemplares preferidas que se ilustran en los dibujos, en los que:

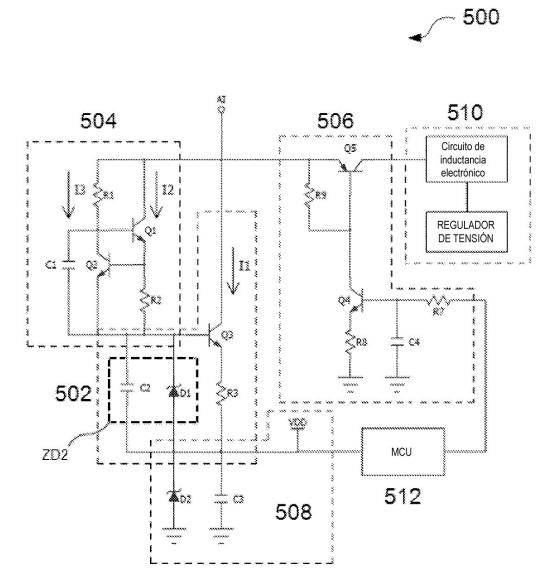

La figura 1 ilustra un diagrama de circuito de un circuito de alimentación eléctrica para un sistema de intercomunicación de bus de 2 hilos según la técnica anterior; las figuras 2a-2d ilustran individualmente un diagrama de circuito de 4 circuitos de alimentación eléctrica convencionales para un sistema de intercomunicación de bus de 2 hilos según la técnica anterior;

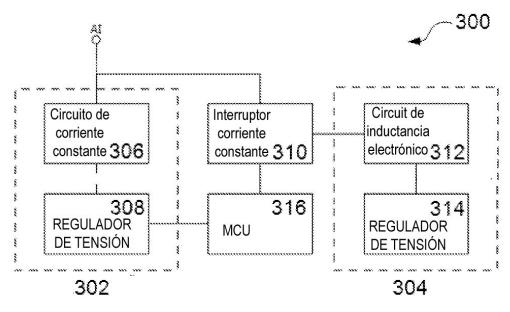

La figura 3 ilustra un diagrama de circuito de un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos según una realización preferida de la presente invención;

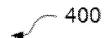

La figura 4 ilustra un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos según una realización preferida de la presente invención;

La figura 5 ilustra un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos según otra realización preferida de la presente invención;

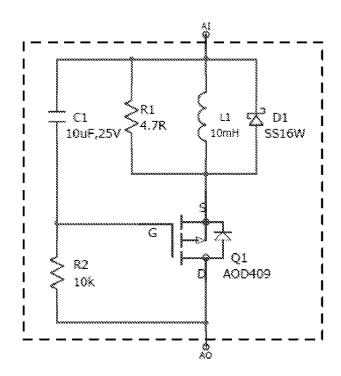

La figura 6 ilustra un diagrama de circuito de un tipo de circuito de inductancia electrónica con un FET de canal P para la alimentación eléctrica de un sistema de intercomunicación de bus de 2 hilos según una realización preferida de la presente invención; y

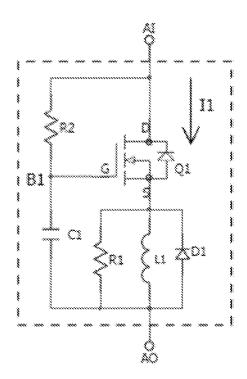

La figura 7 ilustra un diagrama de circuito de una clase de circuito de inductancia electrónica con un FET de canal N para la alimentación eléctrica de un sistema de intercomunicación de bus de 2 hilos según otra realización de la presente invención.

## Descripción detallada de las realizaciones preferidas

10

15

20

25

30

40

45

50

55

Las realizaciones ejemplares de la presente invención se describen junto con los dibujos adjuntos a continuación. En aras de la claridad y la concisión, no todas las características de las implementaciones reales se describen en la especificación.

La figura 3 ilustra un diagrama de circuito de un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos según una realización preferida de la presente invención.

Como se muestra en la figura 3, el circuito 300 de alimentación eléctrica de espera para un sistema de intercomunicación de 2 hilos de la presente invención está separado en dos módulos de alimentación eléctrica: una fuente 302 de alimentación eléctrica del circuito de espera y una fuente 304 de alimentación eléctrica del circuito de operación, la fuente 302 de alimentación eléctrica del circuito de espera comprende un circuito 306 de corriente constante conectado entre el terminal de entrada Al y un circuito 308 regulador de espera. El interruptor 310 de corriente constante está conectado entre la fuente 302 de alimentación eléctrica del circuito de espera y la fuente 304 de alimentación eléctrica del circuito de operación y está configurado para desconectarse mediante la fuente 304 de alimentación eléctrica del circuito de operación cuando la carga del dispositivo está en el estado de espera.

Como el circuito 304 de alimentación eléctrica de operación se apaga cuando la carga del dispositivo está en estado de espera, el número de este circuito 304 conectado al bus común del sistema es muy pequeño simultáneamente. La impedancia alterna del circuito 310 de inductancia electrónica no es muy grande, pero la afección de impedancia de corriente alterna en este circuito 304 es menor.

La fuente 304 de alimentación eléctrica del circuito de operación comprende un circuito 312 de inductancia electrónica y un segundo circuito 314 regulador de tensión. Es obvio para el experto en la materia que el circuito 312 de inductancia electrónica y el segundo circuito 314 regulador de tensión pueden ser cualquier circuito electrónico de inductancia y circuito regulador de tensión disponibles de acuerdo con la técnica anterior.

De acuerdo con una realización preferida de la presente invención, el circuito 300 de alimentación eléctrica de espera comprende además una MCU 316 que está configurada para instruir y controlar el interruptor 310 de corriente constante para que se encienda/apague.

La figura 4 ilustra un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos según una realización preferida de la presente invención.

Como se muestra en la figura 4, el circuito 400 de alimentación eléctrica de espera comprende un circuito 402 de corriente constante principal, un circuito 404 de corriente constante auxiliar, un interruptor 406 de corriente constante, un circuito 408 regulador de espera y una alimentación eléctrica para el circuito 410 de operación. Especialmente, el circuito 306 de corriente constante en la figura 3 comprende además un circuito 402 de corriente constante principal y un circuito 404 de corriente constante auxiliar, en el que el circuito de corriente constante principal está configurado para hacer que la corriente 11 constante principal a través de dicha trayectoria de corriente constante sea estable; y el circuito 404 de corriente constante auxiliar está configurado para ofrecer una corriente de polarización suficiente para el circuito de corriente constante principal con una tensión de polarización bastante más baja (por ejemplo, 5-10 V), además, para mantener una impedancia de CA bastante mayor (por ejemplo, aproximadamente 100 kQ). En una realización real, la impedancia de CA deseada de todo el circuito de corriente constante es de aproximadamente 80 kQ, si el circuito de corriente constante auxiliar se reemplaza directamente por una resistencia de 80 kQ, se utilizará una tensión de polarización superior a 100 V para ofrecer una corriente de 1 mA por circuito de polarización constante.

En detalle, el circuito 402 de corriente constante principal comprende además una trayectoria de corriente constante principal y una unidad reguladora de tensión configurada para hacer que la tensión sea estable independientemente

de la temperatura o la corriente fluctúen y hacer que la impedancia de corriente alterna de dicha trayectoria de corriente principal sea muy alta; en el que la trayectoria de corriente constante principal es a lo largo de un transistor Q3 y una resistencia R3, además el colector del transistor Q3 está conectado al terminal de entrada Al y el emisor del transistor Q3 está conectado con la resistencia R3 en serie.

En cuanto a la unidad reguladora de tensión, comprende además un diodo D1 y un diodo Zener U1 o un dispositivo similar (por ejemplo, un TL431) conectado de manera inversa en serie, una resistencia R4 y un condensador C2 conectado en serie; y el diodo D1 y el diodo Zener U1 conectados con la resistencia R4 y el condensador C2 en paralelo entre el circuito 404 de corriente constante auxiliar y el circuito 408 regulador de espera.

El circuito 404 de corriente constante auxiliar comprende una trayectoria de corriente de control y una segunda trayectoria de corriente de control, en la que la trayectoria de corriente de control está a lo largo del transistor NPN Q1 y una resistencia R2, la segunda trayectoria de corriente de control está a lo largo de una resistencia R1 y un transistor NPN Q2, la resistencia R2 está conectada a la base y el emisor del transistor Q2 en paralelo, la resistencia R1 está conectada al colector y la base del transistor Q1 en paralelo y la base del transistor Q1 está conectada al colector de el transistor Q2, mientras que la base del transistor Q2 está conectada al emisor del transistor Q1.

Además, un condensador C1 está conectado al colector y al emisor del transistor Q2 en paralelo.

El interruptor 406 de corriente constante está conectado entre el circuito 404 de corriente constante auxiliar y la alimentación eléctrica del circuito 410 de operación, y está configurado para desconectarse mediante dicha alimentación eléctrica del circuito de operación cuando la carga del dispositivo se encuentra en el estado de espera. En detalle, el interruptor 406 de corriente constante comprende además al menos dos transistores, tres resistencias y un cuarto condensador, en el que la resistencia R9 está conectada al emisor y la base del transistor PNP Q5 en paralelo; la base del transistor Q5 está conectada al colector del transistor NPN Q4; la resistencia R8 está conectada entre el emisor del transistor Q4 y la tierra; y el condensador C4 está conectado entre la base del transistor Q4 y la tierra.

20

30

35

40

45

50

55

Es óptimo que el interruptor 406 de corriente constante esté conectado a la MCU 412 a través de una resistencia R7.

El circuito 408 regulador de espera comprende además un conjunto de resistencias que consiste en una resistencia R5 y otra resistencia R6 conectadas en serie, un diodo Zener U2 (por ejemplo, un TL431) y un condensador C3; y el conjunto de resistencias R5 y R6, el diodo Zener U2 y el condensador C3 están conectados al circuito 402 de corriente constante principal en paralelo y con conexión a tierra.

Tomando como ejemplo la realización mostrada en la figura 3, el circuito de alimentación eléctrica de espera de la presente invención está estructurado por un circuito de corriente constante principal y un circuito de corriente constante auxiliar; en donde el circuito de corriente constante principal tiene una unidad reguladora de tensión ZD1, cuya tensión es estable incluso cuando la temperatura o la corriente fluctúan. Por lo tanto, la corriente 11 a través de la trayectoria de corriente constante principal será estable y la impedancia de corriente alterna de la trayectoria de corriente principal es muy alta. Debido a que la corriente 11 constante principal no es muy pequeña y la unidad reguladora de tensión ZD1 también necesita una corriente suficiente para garantizar la estabilidad de la tensión, por lo que la corriente 12 de control debe ser lo suficientemente grande. Si la corriente 12 de control es suministrada por una resistencia desde el terminal de entrada Al, la resistencia de dicha resistencia no será muy grande; por lo tanto, la impedancia de corriente alterna de toda la corriente constante no será muy grande. Para el circuito de corriente constante de la presente invención, la corriente de control de la corriente constante principal es suministrada por un circuito de corriente 12 constante auxiliar. Como la corriente 12 es mucho menor que 11, y el circuito de corriente constante auxiliar está estructurado por dos transistores espalda con espalda, la corriente 13 de control puede ser muy pequeña y la resistencia de R1 puede ser muy grande, por lo tanto, la impedancia de corriente alterna de toda la corriente constante puede mantenerse muy grande.

La figura 5 ilustra un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos según otra realización preferida de la presente invención.

Como se muestra en la figura 5, el circuito 500 de alimentación eléctrica de espera también comprende un circuito 502 de corriente constante principal, un circuito 504 de corriente constante auxiliar, un interruptor de corriente constante 506, un circuito 508 regulador de espera, una alimentación eléctrica del circuito 510 de operación y un MCU 512; en el cual el circuito 504 de corriente constante auxiliar, el interruptor 506 de corriente constante, el circuito 508 regulador de espera, la alimentación eléctrica del circuito 510 de operación y la MCU 512 pueden ser iguales o similares al circuito 404 de corriente constante auxiliar, el interruptor 406 de corriente constante, el circuito 408 regulador de espera, la alimentación eléctrica del circuito 410 de operación y la MCU 412 de la figura 4. Para mantener la descripción breve, ya no se describirán circuitos o componentes iguales o similares.

El circuito 502 de corriente constante principal comprende una trayectoria de corriente constante principal y una unidad reguladora de tensión, en la que la trayectoria de corriente constante es igual o similar a la de la figura 4, la unidad reguladora de tensión ZD2 está configurada para hacer que la tensión sea estable la temperatura o la corriente fluctúan y hacen que la impedancia de la corriente alterna de la trayectoria de corriente principal sea muy alta.

La unidad reguladora de tensión ZD2 comprende además un condensador C2 y un diodo Zener D1 conectados en paralelo entre el circuito 504 de corriente constante auxiliar y el circuito 508 regulador de espera.

El circuito 508 regulador de espera comprende además un diodo Zener D2 y un condensador C3 conectado al circuito 502 de corriente constante principal en paralelo y conectado a tierra.

5 Es obvio para el experto en la materia que el circuito de inductancia electrónica puede ser general o el específico que se describe a continuación.

La figura 6 ilustra un diagrama de circuito de una clase de circuito de inductancia electrónica con un FET de canal P para la alimentación eléctrica de un sistema de intercomunicación de bus de 2 hilos según una realización preferida de la presente invención.

Como se muestra en la figura 6, el circuito electrónico de inductancia EL2 comprende un condensador C1, una resistencia R1, un inductor de bobina L1, un diodo de marcha libre D1, una segunda resistencia R2, un FET Q1 de canal P y un segundo diodo. En detalle, una trayectoria del circuito principal entre el terminal de entrada Al y el terminal de salida AO del circuito electrónico de inductancia es a lo largo del inductor L1 y el terminal de origen, así como el terminal de drenaje del canal P FET Q1, y el inductor L1 y los FET Q1 están conectados en serie. Además, el inductor L1 está conectado entre el terminal Al y el terminal de origen del FET Q1, tanto la resistencia R1 como el diodo de marcha libre D1 están conectados individualmente al inductor L1 en paralelo, el terminal de drenaje de dicho canal P, FET Q1 está conectado al terminal de salida, y el nodo de conexión B1 entre el condensador C1 y la segunda resistencia R2 está conectado al terminal de puerta del canal P FET Q1. El circuito electrónico de inductancia comprende además un segundo diodo conectado a dicho terminal de origen y dicho terminal de drenaje de dicho FET en paralelo. Dicho segundo diodo es un diodo general incrustado en el MOSFET, configurado para evitar que el V<sub>DS</sub> tenga una sobretensión.

Tomando la realización de la figura 6 como ejemplo, R1 es un factor clave de la impedancia de CA del circuito y se puede establecer en aproximadamente 4,7  $\Omega$ . En una realización real, la impedancia de CA del circuito es de hasta aproximadamente 2kQ. En cuanto al capacitor L1, se elegirá para hacer que la impedancia de CA ZL = 2 \*  $\pi$  \* f \* L mucho mayor que 4,7  $\Omega$  bajo la frecuencia de 300 ~ 3400Hz. Para el inductor C1, el valor debe poder garantizar unos 300Hz de la frecuencia de corte del filtro. Al conectar Al a una alimentación eléctrica de CC regulada y AO a una carga del dispositivo (es decir, una carga de corriente), la tensión a través del condensador C1 no se puede cambiar de forma transitoria. Es decir,  $U_{C1}$  = 0,  $U_{GS}$  = 0, y Q1 todavía está desactivado. La tensión de AO se reducirá a la referencia GND por la carga del dispositivo que  $U_{AI}$  -  $U_{AO}$  =  $U_{AI}$  =  $U_{R2}$ , por lo tanto, el condensador C1 será cargado por la resistencia R2. Cuando la tensión en C1 es mayor que la tensión de umbral de la compuerta del FET Q1, Q1 comienza a encenderse. Cuando la corriente 11 alcanza el valor de corriente requerido de la carga del dispositivo, la carga del condensador C1 se detendrá y  $U_{GD}$  = 0, por lo tanto, la caída de tensión de la inductancia electrónica EL2 es  $U_{EL2}$  =  $U_{AI}$  -  $U_{AO}$  =  $U_{Z1}$  +  $U_{SG}$ .

Como el valor de resistencia de CC del inductor de bobina L1 es mucho menor que la resistencia auxiliar R1, la impedancia de CA de Z1 está determinada principalmente por el inductor de bobina L1 que Z1 = R Li // R1 sRi\_i; por lo tanto, la caída de tensión de la inductancia electrónica EL2 se representa mediante la ecuación (1) como se muestra a continuación:

donde el valor de resistencia de corriente continua del inductor de bobina es suficientemente pequeño en comparación con el valor de resistencia de la resistencia R1 que Z1 =  $R_{1,1}$ // R1 ≈  $R_{1,1}$ .

A continuación, en cuanto a la impedancia de corriente alterna de la inductancia electrónica EL2, si se produce una tensión de fluctuación  $\Delta II$  en el terminal de AO, entonces la tensión de fluctuación en C1 es  $\Delta U$ ci =  $\Delta U$  \*  $Z_{C1}/(R2 + Z_{C1})$ . Mientras tanto  $\Delta U$ ci =  $\Delta U_{SG} + \Delta U_{R1} = \Delta I1/gm + \Delta I1 * Z1$ , entonces  $\Delta U$  \*  $Z_{C1}/(R2 + Z_{C1}) = \Delta I1/gm + \Delta I1 * Z1$ ; por lo tanto,  $R1 + Z_{Q1} = \Delta U/\Delta I1 = (1 + Z1 * gm) * (R2 + Z_{C1})/(Z_{C1} * gm) = {(1 + Z1 * gm)/gm} * {(R2 + Z_{C1})/(Z_{C1})}$

Como el valor de impedancia de corriente alterna del inductor de bobina L1 es mucho mayor que la resistencia auxiliar, la impedancia de corriente alterna de Z1 la determina la resistencia auxiliar R1 que Z1 =  $R_{L1}$  // R1 ≈ R1, entonces R1 +  $Z_{C1}$  =  $\Delta U/\Delta I1$  = (1 + Z1 \* gm) \* (R2 +  $Z_{C1}$ )/( $Z_{C1}$  \* gm) \* {(1 + R1 \* gm)/gm} \* {(R2 +  $Z_{C1}$ )/Z  $C_{C1}$ }

Por lo tanto, la impedancia de corriente alterna Z<sub>EL2</sub> entre los terminales Al y AO se representa mediante la ecuación (2) como se muestra a continuación:

50

$$Z_{EL2} = (R1 + Z_{Q1}) // (R2 + Z_{C1})$$

$$= \{(1 + Z1 * gm)/gm\} * \{(R2 + Z_{C1})/Z_{C1}\} // (R2 + Z_{C1}) *$$

$$\approx \{(1 + R1 * gm)/gm\} * \{(R2 + Z_{C1})/Z_{C1}\} // (R2 + Z_{C1}) (2)$$

25

30

40

Donde,  $Z_{C1} = 1/(j * \omega * C1) = 1/(j * 2 * \pi * f)$  y "gm" representa la conductancia trans del FET.

Cuando el circuito electrónico de inductancia EL2 permite el paso de CC, es preferible que la caída de tensión UEL2 representada por la ecuación (1) sea pequeña y la CC responda rápidamente. Por otro lado, la impedancia de corriente alterna  $Z_{\text{EL2}}$  representada por la ecuación (2) debe ser suficientemente mayor que la resistencia de bucle del cable del sistema de intercomunicación, lo que es más, no cambia según el cambio de CC.

Es obvio para el experto en la materia que el circuito electrónico de inductancia EL2 puede usar un FET de canal N para construir el circuito similar a la alimentación eléctrica de un sistema de intercomunicación de bus de 2 hilos en lugar del FET de canal P.

10

15

20

30

35

La figura 7 ilustra un diagrama de circuito de una clase de circuito de inductancia electrónica con un FET de canal N para la alimentación eléctrica de un sistema de intercomunicación de bus de 2 hilos según otra realización de la presente invención.

Como se muestra en la figura 7, los componentes del circuito de inductancia electrónica son similares a los de la figura 6, a excepción de un FET Q1 de canal N; por lo tanto, una trayectoria del circuito principal entre el terminal de entrada Al y el terminal de salida AO del circuito de inductancia electrónica se encuentra a lo largo del terminal de drenaje y el terminal de la fuente del canal N FET Q1 así como el inductor L1, y el FET Q1 y el inductor L1 está conectado en serie. Además, el inductor L1 está conectado entre el terminal de origen del FET Q1 y el terminal AO, tanto la resistencia R1 como el diodo de marcha libre D1 están conectados individualmente al inductor L1 en paralelo, el terminal de drenaje de dicho canal N FET Q1 está conectado al terminal de entrada AI, y el nodo de conexión B1 entre el condensador C1 y la segunda resistencia R2 está conectado al terminal de puerta del FET Q1 de canal N. El circuito electrónico de inductancia comprende además un segundo diodo conectado a dicho terminal de origen y dicho terminal de drenaje de dicho FET en paralelo.

En resumen, el circuito que se muestra en la figura 7 es simétrico al circuito de la figura 6. Con el circuito que se muestra en la figura 7, la caída de tensión y la impedancia de corriente alterna entre los terminales Al y AO también pueden ser representadas por las ecuaciones (1) y (2) respectivamente.

Según otro aspecto de la presente invención, proporciona un aparato que comprende el circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos mencionado anteriormente. Además, también proporciona un sistema de intercomunicación que comprende un aparato mencionado anteriormente.

En comparación con las técnicas anteriores existentes, las soluciones propuestas de la presente invención comprenden un circuito de corriente constante principal y un circuito de corriente constante auxiliar, que puede lograr una impedancia de corriente alterna más grande para el sistema de intercomunicación de 2 hilos y ofrecer energía suficiente para muchas cargas de dispositivos. En las condiciones de operación y estado de espera.

Aunque la presente invención se ha descrito sobre la base de algunas realizaciones preferidas, los expertos en la técnica deberían apreciar que dichas realizaciones no deberían limitar de ninguna manera el alcance de la presente invención. Sin apartarse del espíritu y el concepto de la presente invención, cualquier variación y modificación de las realizaciones debe estar dentro de la comprensión de aquellos con conocimientos y habilidades ordinarios en la técnica, y, por lo tanto, entran en el alcance de la presente invención que se define por las reivindicaciones adjuntas.

## REIVINDICACIONES

- 1. Un circuito (300) de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos, en el que dicho circuito de alimentación eléctrica de espera está separado en dos módulos (302, 304) de alimentación eléctrica; en el que

- un primer módulo (302) de alimentación eléctrica es una fuente de alimentación para un circuito en espera y el segundo módulo (304) de alimentación eléctrica es una fuente de alimentación para un circuito de operación; dicha de alimentación (304) electrica del circuito de operación se desconecta mediante un interruptor (310) de corriente constante cuando una carga del dispositivo se encuentra en un estado de espera;

- caracterizado porque dicha alimentación (302) eléctrica del circuito en espera comprende un circuito (306) de corriente constante, dicho circuito de corriente constante comprende un circuito (402, 502) de corriente constante principal y un circuito (404, 504) de corriente constante auxiliar, en el que dicho circuito de corriente constante principal está configurado para hacer que la corriente a través de una trayectoria de corriente constante principal de dicho circuito de corriente constante sea estable; y

15

20

25

30

35

40

- en el que dicho circuito de corriente constante auxiliar ofrece una corriente de polarización para el circuito de corriente constante principal.

- 2. El circuito de alimentación eléctrica de espera según la reivindicación 1, en el que dicho circuito (402, 502) de corriente constante está conectado entre un terminal (Al) de entrada y un circuito (408, 508) regulador de espera.

- 3. El circuito de alimentación eléctrica de espera según la reivindicación 1 o 2, en el que dicho circuito (402, 502) de corriente constante principal comprende además una trayectoria de corriente constante principal y una unidad (ZD1, ZD2) reguladora de tensión, en la que dicha unidad reguladora de tensión está configurada para hacer que la tensión sea estable independientemente de la temperatura o la corriente fluctúe y la impedancia de la corriente alterna de dicha trayectoria de corriente principal es muy alta.

- 4. El circuito de alimentación eléctrica de espera según la reivindicación 3, en el que dicha trayectoria de corriente constante principal está a lo largo de un primer transistor (Q3) y una primera resistencia (R3), en el que el colector de dicho primer transistor está conectado al terminal (AI) de entrada y el emisor de dicho primer transistor está conectado con dicha primera resistencia en serie.

- 5. El circuito de alimentación eléctrica de espera según la reivindicación 3, en el que dicha unidad (ZD1) reguladora de tensión comprende, además:

- un diodo (D1) y un primer diodo (U1) Zener conectados de forma inversa en serie, una segunda resistencia (R4) y un primer condensador (C2) conectados en serie; y

- dicho diodo (D1) y dicho primer diodo (U1) Zener conectados con dicha segunda resistencia (R4) y dicho primer condensador (C2) en paralelo,

- en el que opcionalmente dicho circuito (408) regulador de espera comprende además un conjunto de resistencias constituidas por una tercera resistencia (R5) y una cuarta resistencia (R6) conectadas en serie, un segundo diodo (U2) Zener y un segundo condensador (C3), y dicho conjunto de resistencias, dicho segundo diodo Zener y dicho segundo condensador están conectados en paralelo y conectados a tierra.

- 6. El circuito de alimentación eléctrica de espera según la reivindicación 3, en el que dicha unidad (ZD2) reguladora de tensión comprende además un primer condensador (C2) y un primer diodo (D1) Zener conectado en paralelo; y dicho circuito (508) regulador de espera comprende además un segundo diodo (D2) Zener y un segundo condensador (C3) conectado en paralelo y conectado a tierra.

- 7. El circuito de alimentación eléctrica de espera según una de las reivindicaciones anteriores, en el que dicho circuito de corriente constante auxiliar comprende una trayectoria de corriente de control y una segunda trayectoria de corriente de control, en el que

- dicha trayectoria de corriente de control está a lo largo de un segundo transistor (Q1) y una quinta resistencia (R2):

- dicha segunda trayectoria de corriente de control está a lo largo de un tercer transistor (Q2) y una sexta resistencia (R1);

- dicha quinta resistencia (R2) está conectada a una base y a un emisor de dicho tercer transistor (Q2) en paralelo; y

- dicha sexta resistencia (R1) está conectada a un colector y una base de dicho segundo transistor (Q1) en paralelo,

- en el que opcionalmente dicho circuito de corriente constante auxiliar comprende además un tercer condensador (C1) conectado al colector y el emisor de dicho tercer transistor (Q2) en paralelo.

- 8. El circuito de alimentación eléctrica de espera según la reivindicación 1, en el que dicho circuito de alimentación eléctrica de espera comprende además una MCU, configurada para controlar dicho interruptor de corriente constante para ser activado/desactivado.

- 9. El circuito de alimentación eléctrica de espera según la reivindicación 1, en el que dicho circuito de alimentación eléctrica al circuito de operación comprende además un circuito de inductancia electrónica y un segundo circuito regulador de tensión.

- 10. El circuito de alimentación eléctrica de espera según la reivindicación 1, en el que dicho interruptor (310) de corriente constante está conectado entre dicha alimentación (302) eléctrica y el circuito de espera y dicha alimentación (304) eléctrica al circuito de operación, configurado para desconectarse mediante dicha alimentación eléctrica del circuito de operación cuando la carga del dispositivo está en el estado de espera.

- 11. El circuito de alimentación de espera según la reivindicación 10, en el que dicho interruptor (310) de corriente constante comprende además al menos dos transistores (Q4, Q5), tres resistencias (R7, R8, R9) y un cuarto condensador (C4), en el que

- la séptima resistencia (R9) está conectada a un emisor y una base del cuarto transistor (Q5) en paralelo; la base de dicho cuarto transistor (Q5) está conectada a un colector del quinto transistor (Q4); la octava resistencia (R8) está conectada entre un emisor de dicho quinto transistor (Q4) y la conexión a tierra; y dicho cuarto condensador (C4) está conectado entre una base de dicho quinto transistor (Q4) y la conexión a tierra, en el que opcionalmente el colector de dicho cuarto transistor (Q5) está conectado a dicho circuito de inductancia electrónica; y la novena resistencia (R7) está conectada a la base de dicho quinto transistor (Q4) y una MCU.

- 12. El circuito de alimentación de espera según la reivindicación 9, en el que dicho circuito de inductancia electrónica comprende:

- una trayectoria del circuito principal a lo largo de un inductor (L1) y un terminal (AI) de origen y un terminal (D) de drenaje de un FET entre el terminal (AI) de entrada y un terminal (AO) de salida de dicho circuito de inductancia electrónica, en dicho inductor (L1) está conectado a dicho terminal (S) de origen de dicho FET; una resistencia (R1) y un diodo (D1) de rueda libre conectados individualmente a dicho inductor (L1) en paralelo; y

- una trayectoria de circuito secundario a lo largo de un condensador (C1) conectado con una segunda resistencia (R2) en serie entre dicho terminal (AI) de entrada y dicho terminal (AO) de salida, que está conectado a dicha trayectoria de circuito principal en paralelo.

- 13. El circuito de alimentación de espera según la reivindicación 12, en el que

5

10

15

25

30

35

- dicho inductor (L1) y dicho FET están conectados en serie, y el nodo entre dicho condensador (C1) y dicha segunda resistencia (R2) está conectado con el terminal (G) de puerta de dicho FET; o

- dicho FET es un FET de canal P, y dicho terminal (D) de drenaje de dicho FET de canal P está conectado a dicho terminal (AO) de salida; y dicho inductor (L1) está conectado entre dicho terminal (AI) de entrada y dicho terminal (S) de origen de dicho FET de canal P; o

- dicho FET es un FET de canal N, y dicho terminal (D) de drenaje de dicho FET de canal N está conectado a dicho terminal (AI) de entrada; y dicho inductor (L1) está conectado entre dicho terminal (S) de origen de dicho FET de canal N y dicho terminal (AO) de salida.

- 14. Un aparato para un sistema de intercomunicación de bus de 2 hilos, en el que dicho aparato comprende un circuito de alimentación de espera según cualquiera de las reivindicaciones anteriores.

Fig.2a

Fig.2b

Fig.2c

Fig.2d

Fig.3

Fig.4

Fig.5

Fig.6

Fig.7