# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

(1) Número de publicación: 2 718 469

51 Int. CI.:

H04L 5/20 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 29.02.2008 PCT/US2008/055566

(87) Fecha y número de publicación internacional: 12.09.2008 WO08109478

(96) Fecha de presentación y número de la solicitud europea: 29.02.2008 E 08731177 (5)

(97) Fecha y número de publicación de la concesión europea: 02.01.2019 EP 2130320

(54) Título: Interfaz en serie trifásica y codificada por polaridad

(30) Prioridad:

02.03.2007 US 712941

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **02.07.2019**

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121-1714, US

(72) Inventor/es:

**WILEY, GEORGE A.**

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

## **DESCRIPCIÓN**

Interfaz en serie trifásica y codificada por polaridad

#### 5 ANTECEDENTES

#### Campo

10

20

25

30

35

40

55

[0001] La presente invención se refiere, en general, a la comunicación en serie de alta velocidad. Más en particular, la invención se refiere a esquemas de codificación de datos de modulación trifásica para comunicación en serie de alta velocidad.

## **Antecedentes**

15 **[0002]** En el campo de la comunicación en serie de alta velocidad, la demanda de velocidades de datos cada vez mayores sigue creciendo.

[0003] Muchos sistemas convencionales de interfaz en serie de alta velocidad utilizan codificación de datos sin retorno a cero (NRZ) con datos y señales de reloj por separado. Esta separación de los datos y las señales de reloj, sin embargo, habitualmente da como resultado un sesgo entre las dos señales, lo que limita la velocidad máxima posible de datos de enlace de la interfaz.

[0004] Normalmente, los circuitos de eliminación de sesgo se utilizan en el extremo receptor de la interfaz en serie para eliminar el sesgo entre los datos y las señales del reloj. En consecuencia, tanto los requisitos de estado real como el tiempo de inicio de enlace de la interfaz en serie aumentan, y esto último se vuelve desventajoso cuando la interfaz se usa intermitentemente en un ciclo bajo de trabajo para minimizar el consumo de energía del sistema.

[0005] Otros sistemas convencionales de interfaz en serie son más inmunes al sesgo, al usar datos y señales estroboscópicas, pero todavía sufren problemas de sesgo cuando funcionan a altas velocidades.

[0006] Además, ciertos dispositivos receptores integrados se construyen generalmente con una lógica más lenta porque tienen tamaños de características más grandes para controlar altos voltajes. Este es el caso, por ejemplo, de los circuitos integrados de Controlador-Accionador de LCD, que se utilizan para controlar los paneles de LCD. Como tal, sería difícil implementar una interfaz en serie de alta velocidad para tales dispositivos utilizando sistemas convencionales.

[0007] Por lo tanto, lo que se necesita es una interfaz en serie de alta velocidad que resuelva los problemas descritos anteriormente de los sistemas convencionales de interfaz en serie. Además, se necesita una interfaz en serie de alta velocidad con mayor capacidad y menor consumo de energía con respecto a los sistemas convencionales. El documento WO 2005/041164 A divulga un procedimiento y un dispositivo para transmitir unidades de datos mediante un medio de transmisión que comprende al menos tres líneas de transmisión adyacentes.

## **BREVE SUMARIO DE LA INVENCIÓN**

[0008] Una interfaz en serie de alta velocidad se proporciona en este documento. De acuerdo a la presente invención, se proporciona un procedimiento para la codificación de datos, según lo relatado por la reivindicación 1 y se proporciona un circuito transmisor de interfaz en serie según lo relatado por la reivindicación 13. A continuación, los modos de realización que no están dentro del alcance de las reivindicaciones deberían entenderse como ejemplos útiles para comprender la invención.

[0009] En un aspecto, la interfaz en serie de alta velocidad utiliza un esquema de codificación de datos de modulación trifásica para codificar conjuntamente datos e información de reloj. Por consiguiente, se elimina la necesidad de eliminar el sesgo de los circuitos en el extremo receptor de la interfaz, lo que se traduce en una reducción del tiempo de arranque del enlace y una mejora de la eficacia del enlace y del consumo de energía. En una realización, la interfaz en serie de alta velocidad utiliza menos conductores de señal que los sistemas convencionales con conductores individuales para datos e información de reloj. En otra realización, la interfaz en serie permite que los datos se transmitan a cualquier velocidad sin que el extremo receptor tenga ningún conocimiento previo de la velocidad de transmisión de datos.

- [0010] En otro aspecto, la interfaz en serie de alta velocidad utiliza un esquema de codificación de datos de modulación trifásica, codificado por polaridad, para codificar conjuntamente datos e información de reloj. Esto, además de las ventajas descritas anteriormente, aumenta aún más la capacidad de enlace de la interfaz en serie al permitir que se transmita más de un bit en cualquier intervalo de baudio único.

- 65 **[0011]** En un aspecto adicional, el esquema de codificación de datos de modulación trifásica, codificado por polaridad, se utiliza para implementar interfaces en serie de alta velocidad para ciertos controladores receptores con

circuitos lógicos más lentos. Al codificar al menos dos bits por transición en la interfaz, el esquema de codificación permite que la velocidad de transición de datos sea la mitad de la velocidad normal de datos en serie.

[0012] Una interfaz de alta velocidad que emplea el esquema de codificación de datos de modulación trifásica que se proporciona en este documento consume la mitad de la corriente que otras interfaces de alta velocidad que utilizan los mismos controladores. Esto se debe a que solo una salida del controlador está activa a la vez, en lugar de tener dos salidas simultáneamente activas, como suele ser el caso en otras interfaces en serie (por ejemplo, datos y reloj o datos y muestreo). Esta reducción del consumo de energía se combina con la capacidad de una interfaz de alta velocidad que emplea el esquema de codificación de datos de modulación trifásica para enviar datos al menos al doble de la velocidad de otras interfaces en serie.

**[0013]** Realizaciones, características y ventajas adicionales de la presente invención, así como la estructura y el funcionamiento de las diversas realizaciones de la presente invención, se describen en detalle a continuación con referencia a los dibujos adjuntos.

# **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

5

10

15

20

25

30

35

45

50

65

**[0014]** Los dibujos adjuntos, que se incorporan en el presente documento y forman parte de la especificación, ilustran la presente invención y, junto con la descripción, sirven además para explicar los principios de la invención y para permitir que una persona experta en la técnica pertinente realice y use la invención.

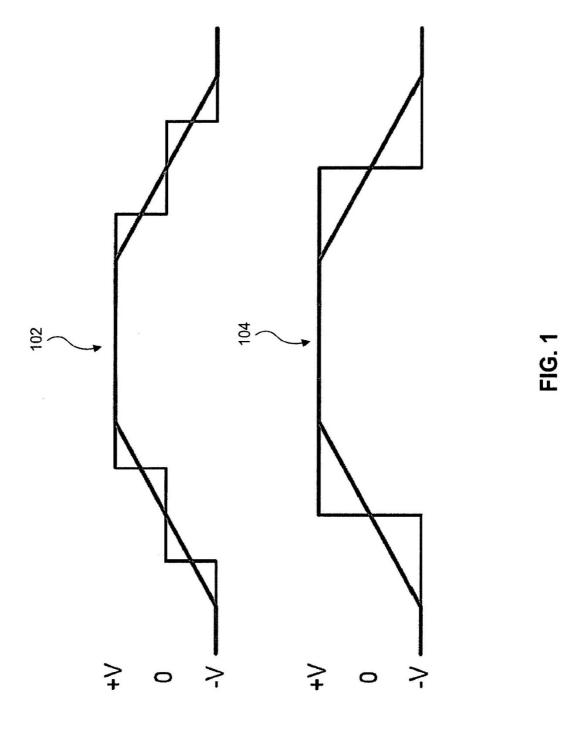

La figura 1 ilustra transiciones ejemplares en un esquema de codificación de datos diferenciales de 3 niveles.

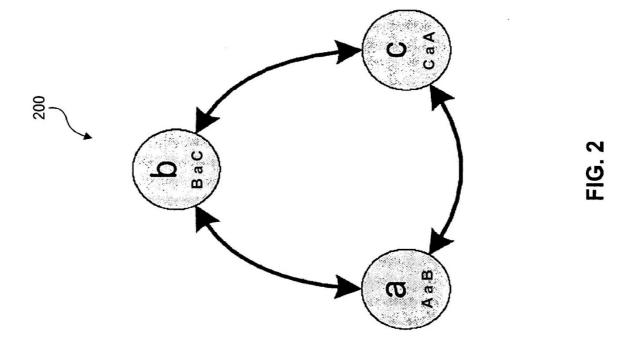

La figura 2 ilustra un diagrama de estados circular.

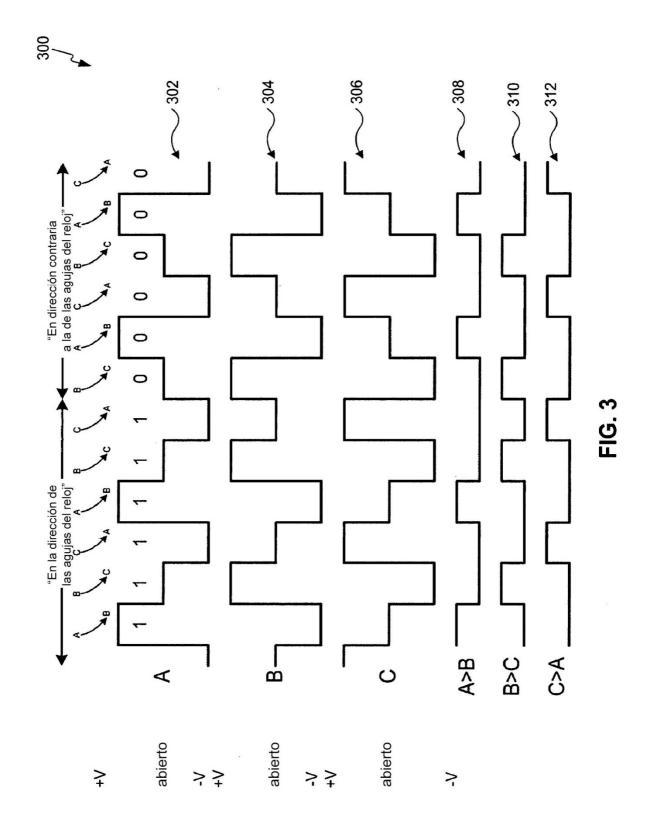

La figura 3 es un ejemplo que ilustra un esquema de codificación de datos de modulación trifásica.

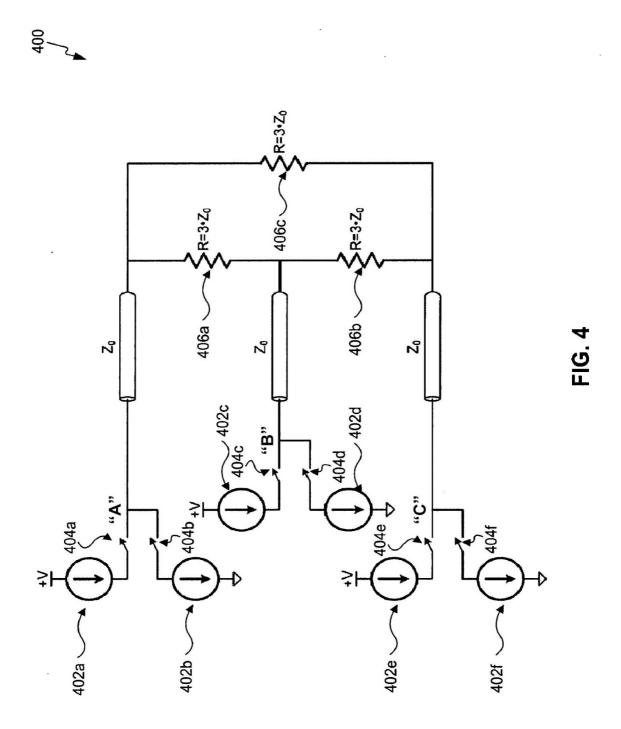

La figura 4 ilustra un transmisor de interfaz en serie para implementar un esquema de codificación de datos de modulación trifásica.

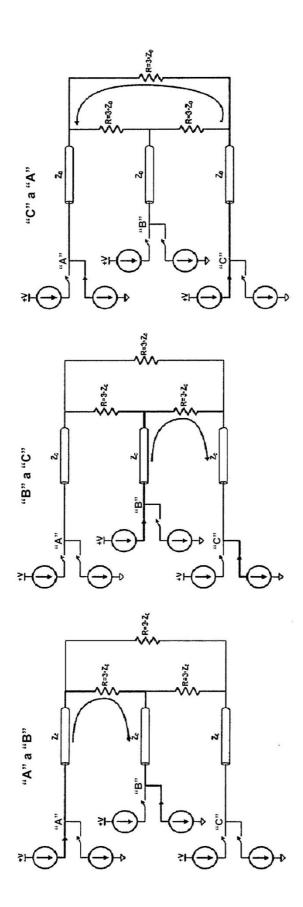

La figura 5 ilustra los escenarios de flujo actuales que corresponden a los estados de codificación de acuerdo a un esquema de codificación de datos de modulación trifásica.

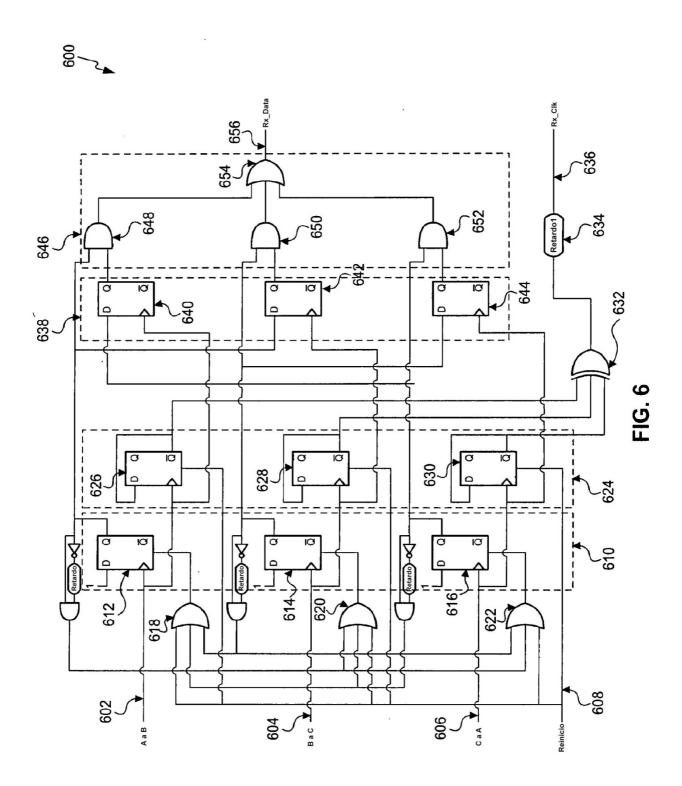

La figura 6 ilustra un circuito ejemplar de recuperación de datos para un esquema de codificación de datos de modulación trifásica.

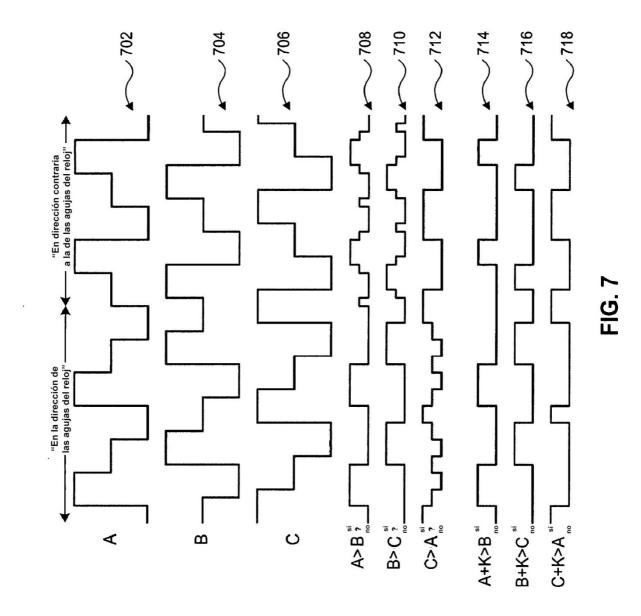

La figura 7 ilustra el impacto de los desplazamientos de temporización en el esquema de codificación de datos de modulación trifásica de la figura 3.

40 La figura 8 es una tabla ejemplar de estados de un esquema de codificación de datos de modulación trifásica, codificado por polaridad.

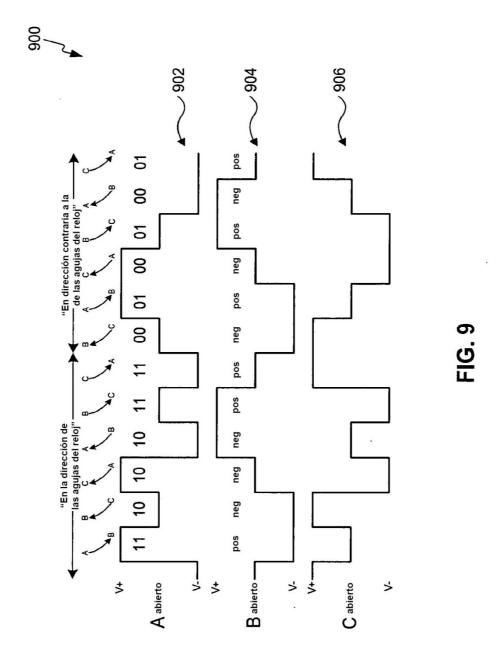

La figura 9 es un ejemplo que ilustra un esquema de codificación de datos de modulación trifásica, codificado por polaridad, de acuerdo al diagrama de estados de la figura 8.

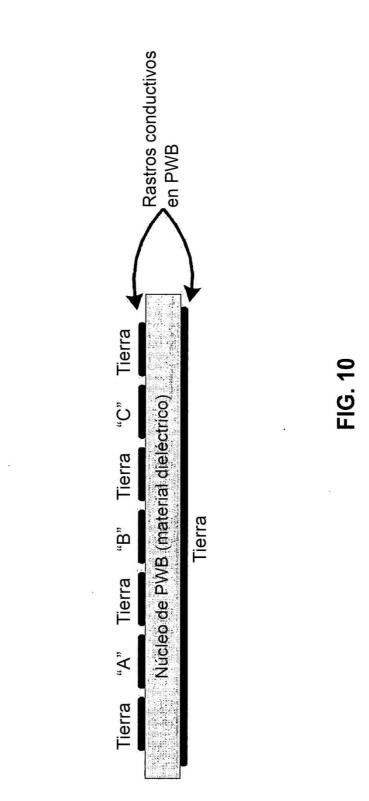

La figura 10 ilustra una implementación ejemplar de conductores de señales en una placa de cableado impreso para habilitar los esquemas de codificación de datos de modulación trifásica.

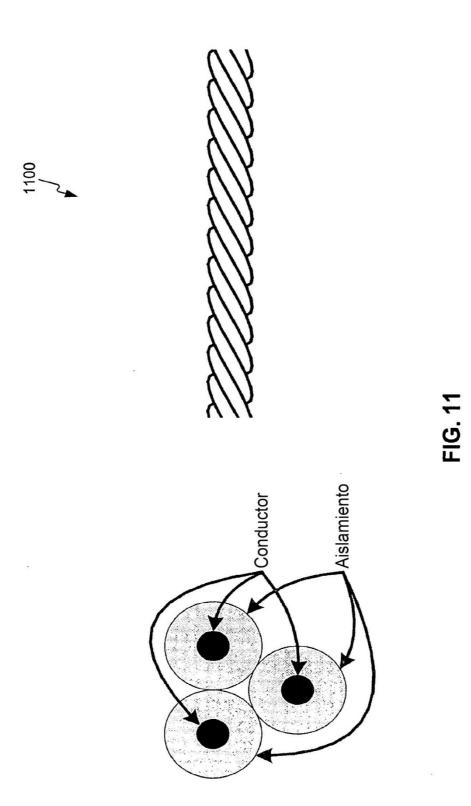

La figura 11 ilustra una implementación ejemplar de conductores de señales en un cable para habilitar los esquemas de codificación de datos de modulación trifásica.

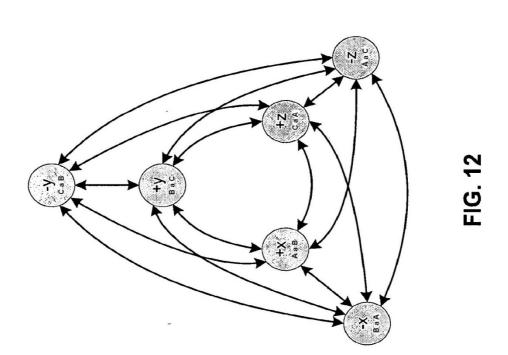

La figura 12 ilustra un diagrama ejemplar de estados de un esquema de codificación de datos de modulación trifásica, codificado por polaridad.

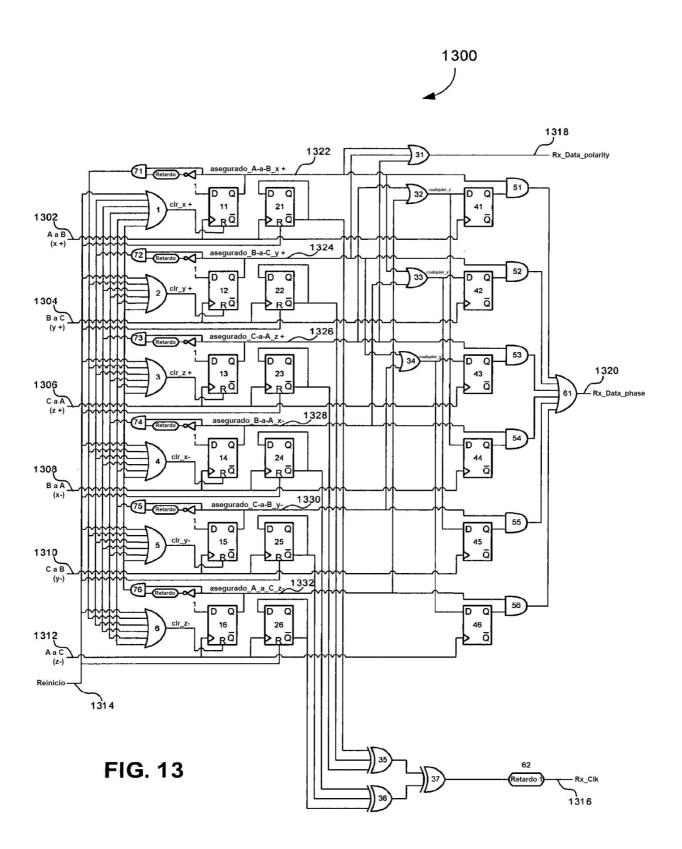

La figura 13 ilustra un circuito ejemplar de recuperación de datos para un esquema de codificación de datos de modulación trifásica, codificado por polaridad.

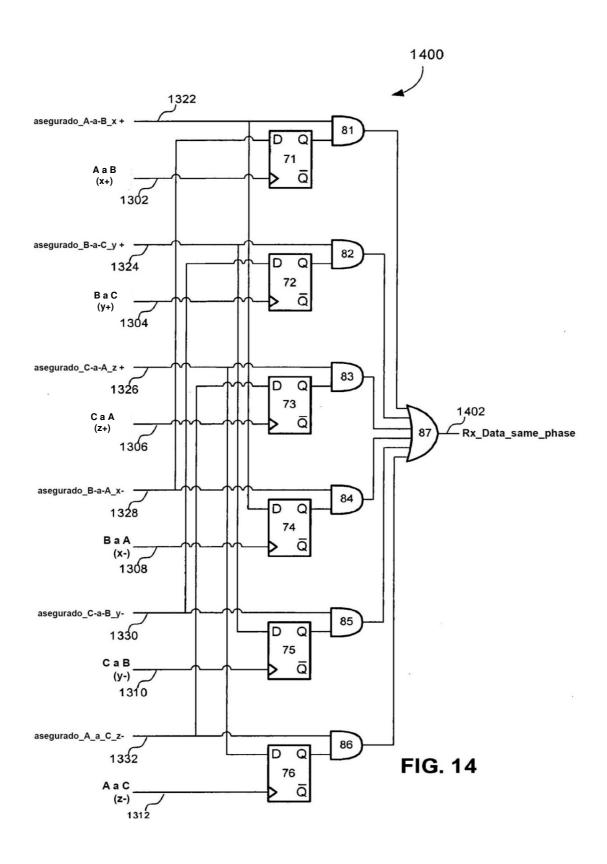

La figura 14 ilustra circuitos adicionales del circuito ejemplar de recuperación de datos de la figura 13.

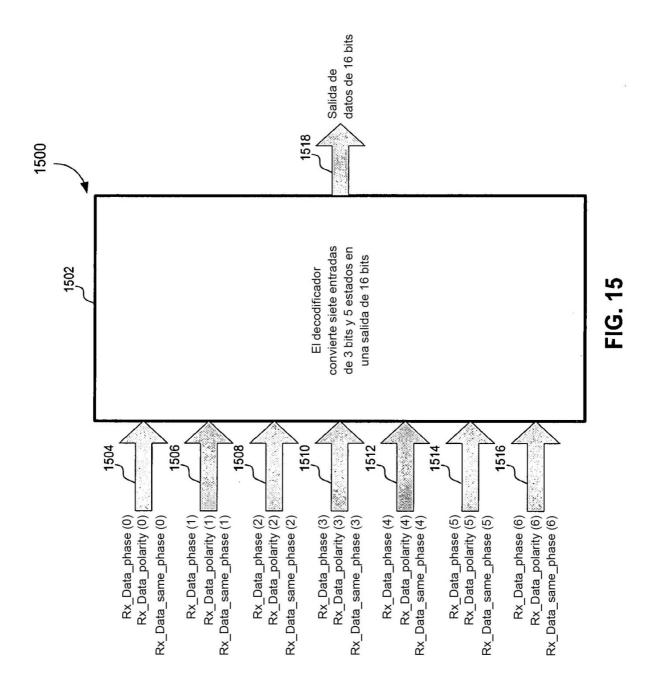

La figura 15 ilustra un decodificador ejemplar de datos para decodificar la salida del circuito de recuperación de datos de las figuras 13 y 14.

[0015] La presente invención se describirá con referencia a los dibujos adjuntos. El dibujo en el que aparece un elemento por primera vez suele estar indicado por los uno o más dígitos más a la izquierda en el número de referencia correspondiente.

#### **DESCRIPCIÓN DETALLADA**

5

10

35

65

[0016] Esta especificación divulga una o más realizaciones que incorporan las características de esta invención. La(s) realización(es) descrita(s) simplemente ejemplifica(n) la invención. El alcance de la invención no está limitado a la(s) realización(es) divulgada(s). La invención se define por las reivindicaciones adjuntas al presente documento.

[0017] La(s) realización(es) descrita(s) y las referencias en la especificación a "una realización", "una realización ejemplar", etc., indican que la(s) realización(es) descrita(s) puede(n) incluir un rasgo, una estructura o una característica particular, pero cada realización puede no incluir necesariamente el rasgo, estructura o característica particular. Además, tales frases no se refieren necesariamente a la misma realización. Además, cuando un rasgo, una estructura o una característica particular se describe en relación con una realización, se afirma que es del conocimiento de un experto en la técnica afectar dicho rasgo, dicha estructura o dicha característica en relación con otras realizaciones, ya sean o no explícitamente descritas.

15 [0018] Las realizaciones de la invención pueden implementarse en hardware, firmware, software o cualquier combinación de los mismos. Las realizaciones de la invención también pueden implementarse como instrucciones almacenadas en un medio legible por máquina, que puede ser leído y ejecutado por uno o más procesadores. Un medio legible por máquina puede incluir cualquier mecanismo para almacenar o transmitir información en una forma legible por una máquina (por ejemplo, un dispositivo informático). Por ejemplo, entre los medios legibles por máquina se incluye memoria de solo lectura ("ROM"), memoria de acceso aleatorio ("RAM"), medios de almacenamiento en disco magnético; medios de almacenamiento óptico, dispositivos de memoria flash; señales eléctricas, ópticas, acústicas u otras formas de señales propagadas (por ejemplo, ondas portadoras, señales infrarrojas, señales digitales, etc.); y otros. Además, el firmware, el software, las rutinas y las instrucciones pueden describirse en este documento como realizando ciertas acciones. Sin embargo, se debe tener en cuenta que tales descripciones son meramente por comodidad y que dichas acciones son, de hecho, resultado de dispositivos informáticos, procesadores, controladores u otros dispositivos que ejecutan el firmware, el software, rutinas, instrucciones, etc.

#### Codificación de datos con información de temporización integrada

30 **[0019]** Como se ha expuesto anteriormente, para eliminar el sesgo entre los datos y las señales de reloj o la necesidad de eliminar el sesgo en los circuitos en una interfaz en serie, es deseable codificar conjuntamente datos e información de reloj (o integrar información de temporización en la señal de datos). Una técnica común para darse cuenta de esto es mediante el uso de un esquema de codificación de datos diferenciales, por el que los datos y la información del reloj se codifican conjuntamente en transiciones de estado de una sola señal.

[0020] La mayoría de los esquemas de codificación de datos diferenciales son esquemas diferenciales de nivel, por lo que las transiciones de estado se definen en términos de cambios en el nivel (magnitud) de los datos y la señal del reloj.

40 **[0021]** La figura 1 ilustra transiciones ejemplares en un esquema de codificación de datos diferenciales de 3 niveles. Según el esquema de la figura 1, una transición del nivel de señal (voltaje) desde: - V a 0 es un 0 lógico, de -V a +V es un 1 lógico, de 0 a -V es un 0 lógico, de 0 a +V es un 1 lógico, de +V a 0 es un 1 lógico y de +V a -V es un 0 lógico.

[0022] Las transiciones ejemplares 102 y 104 ilustran dos transiciones de nivel de señal, por lo que el nivel de señal cambia de -V a + V. La transición 102 incluye una primera transición de -V a 0 seguida de una segunda transición de 0 a + V, para transmitir una secuencia de datos 01. La transición 104 incluye una única transición de -V a +V para transmitir un 1 lógico.

[0023] Sin embargo, como se muestra en la figura 1, debido a que la velocidad de giro de la señal es lenta en comparación con el tiempo de respuesta de los circuitos de recuperación de datos en el extremo receptor, ambas transiciones 102 y 104 parecen idénticas y son interpretadas como 01 por los circuitos de recuperación. Problemas similares de decodificación de transición ocurren en transiciones de +V a -V en el caso ilustrado en la figura 1, o cuando la velocidad de giro es más rápida que el tiempo de respuesta de los circuitos de recuperación de datos.

[0024] Esta ambigüedad en la decodificación de las transiciones de estado se debe a tener transiciones que deben pasar a través de estados intermedios para alcanzar un estado deseado. Por lo tanto, se necesita un esquema de codificación de datos diferenciales con transiciones de estado "circulares" para resolver las transiciones de estado ambiguas en esquemas de codificación de datos diferenciales.

#### 60 Codificación de datos diferenciales con transiciones de estado circulares

[0025] La figura 2 ilustra un diagrama de estados circular 200, que puede usarse para definir transiciones de estados en un esquema de codificación de datos diferenciales. De acuerdo al diagrama de estados 200, los datos se codifican basándose en las transiciones entre tres estados a, b y c. Téngase en cuenta que la transición entre dos estados cualesquiera (a a b, b a a, b a c, c a b, a a c y c a a) se produce en una sola etapa sin recorrer estados intermedios.

Como tales, los esquemas de codificación de datos diferenciales basados en el diagrama de estados 200 estarían libres de problemas de decodificación de transición de estado, como se ha expuesto anteriormente.

- [0026] La figura 3 ilustra un esquema de codificación de datos de modulación trifásica 300, basado en el diagrama de estados circular 200 de la figura 2. De acuerdo al esquema de codificación de datos 300, una señal trifásica que gira en dos direcciones se transmite utilizando tres conductores A, B y C. Las tres señales (transportadas por los conductores A, B y C) que componen la fase trifásica son independientes, estando cada señal desfasada en 120 grados con respecto a las dos restantes.

- [0027] En cualquier momento, exactamente dos de los conductores A, B y C llevan una señal, estando los estados de codificación de datos definidos en términos del flujo de señales entre los conductores. En una realización, tres estados (correspondientes respectivamente a los estados a, b, c de la figura 2) se definen con un flujo de señal de A a B, B a C y C a A. Las transiciones entre los tres estados se definen luego de acuerdo al diagrama de estados 200 para asegurar transiciones de estado circulares. En una realización, las transiciones en el sentido de las agujas del reloj (A a B) a (B a C), (B a C) a (C a A) y (C a A) a (A a B) se utilizan para transmitir un 1 lógico, mientras que las transiciones en el sentido contrario al de las agujas del reloj (B a C) a (A a B), (A a B) a (C a A) y (C a A) a (B a C) se utilizan para transmitir un 0 lógico.

- [0028] Con referencia de nuevo a la figura 3, se muestra un ejemplo de codificación de datos que utiliza el esquema de modulación trifásico. Las señales 302, 304 y 306 ilustran las señales de voltaje aplicadas a los conductores A, B y C, respectivamente. En cualquier momento, un primer conductor está acoplado a un voltaje positivo (+V, por ejemplo), un segundo conductor está acoplado a un voltaje negativo (-V, por ejemplo), mientras que el tercer conductor restante está en circuito abierto. Como tal, el estado de codificación está determinado por el flujo de corriente entre los conductores primero y segundo. También se observa que solo uno de los estados (A a B), (B a C) y (C a A) puede ser verdadero en cualquier momento, como se ilustra mediante las señales 308 (A > B), 310 (B > C) y 312 (C a A), con transiciones de estado en el sentido de las agujas del reloj, usadas para transmitir un 1 lógico, y transiciones de estado en sentido contrario al de las agujas del reloj, usadas para transmitir un 0 lógico. En una realización, las señales 308, 310 y 312 se generan utilizando comparadores que comparan voltajes entre los conductores A, B y C.

- [0029] La figura 4 ilustra un circuito transmisor de interfaz en serie 400 para implementar el esquema de codificación de datos de modulación trifásica 300 de la figura 3. El circuito 400 se implementa utilizando circuitos controladores de corriente. También existen otras implementaciones de circuitos, como puede apreciar una persona experta en la técnica basándose en las enseñanzas en el presente documento.

- [0030] El circuito 400 incluye una pluralidad de fuentes de corriente 402a a 402f que se pueden acoplar, utilizando los conmutadores 404a a 404f, a los primeros extremos de los conductores A, B y C. Los segundos extremos de los conductores A, B y C se acoplan entre sí utilizando las impedancias de terminación 406a a 406c. En una realización, cada uno de los conductores A, B y C tiene una impedancia natural de valor Zo, con impedancias de terminación 406a a 406c que tienen, cada una, un valor de impedancia de 3Zo.

- [0031] En cualquier momento, exactamente dos de los conmutadores 404a a 404f están cerrados para provocar un flujo de corriente entre exactamente dos de los conductores A, B y C. Como tal, existe un único trayecto de corriente en cualquier momento en el circuito. Además, de acuerdo al esquema de codificación 300, solo se permite que la corriente fluya desde el conductor A al conductor B, desde el conductor B al conductor C o desde el conductor C al conductor A. Estos tres escenarios de flujo de corriente corresponden a los únicos tres estados de codificación válidos del esquema de codificación de datos 300 y se ilustran en la figura 5 con respecto al circuito transmisor 400.

# Circuito de recuperación de datos

5

45

- [0032] En el extremo receptor de la interfaz en serie, se utiliza un circuito de recuperación de datos para decodificar los datos transmitidos por el circuito transmisor. En una realización, los voltajes a través de los resistores de terminación 406a a 406b en el circuito transmisor 400 se monitorizan para detectar transiciones de estado. Por ejemplo, se generan señales similares a las señales A> B 308, B> C 310 y C> A 312 de la figura 3, por lo que en cualquier momento exactamente una de estas señales está activa, lo que indica el estado de codificación actual.

- [0033] La figura 6 ilustra un circuito ejemplar de recuperación de datos 600 que se puede usar para decodificar datos transmitidos de acuerdo a un esquema de codificación de datos de modulación trifásica. También se puede usar otra implementación del circuito de recuperación de datos, como entendería un experto en la materia basándose en las enseñanzas en el presente documento.

- [0034] El circuito de recuperación de datos 600 incluye las capas primera, segunda y tercera 610, 624 y 638 de flip flops D y un circuito multiplexor 646.

- [0035] El circuito de recuperación de datos 600 recibe señales de entrada A a B 602, B a C 604 y C a A 606. En cualquier momento, exactamente una de las señales 602, 604 y 606 está activa, lo que indica el estado de codificación

actual que se está transmitiendo. Las señales 602, 604 y 606 se ingresan respectivamente en los flip flops de la primera capa D 612, 614 y 616.

[0036] Los flip flops de la primera capa D 612, 614 y 616 capturan la transición de estado más reciente, según lo indicado por las señales 602, 604 y 606. Téngase en cuenta que cada uno de los flip flops D 612, 614 y 616 tiene su entrada de datos D acoplada a un 1 lógico y se activa siempre que su respectiva entrada de reloj 602, 604 o 606 experimente una transición de flanco ascendente. También téngase en cuenta que cada vez que se activa uno de los flip flops D 612, 614 y 616, reinicia de forma asíncrona los otros dos flip flops D de la primera capa. En una realización, esto se hace acoplando la salida Q de cada primer flip-flop de la capa D, mediante un circuito de pulso activado por el flanco ascendente, a las entradas de reinicio de los otros dos flip-flops D de la primera capa. Por ejemplo, en la realización de la figura 6, la salida Q del flip flop D 612 está acoplada, mediante las compuertas OR 620 y 622, respectivamente, a las entradas de reinicio de los flip flops D 614 y 616. En una realización, para garantizar que los flip-flops D 612, 614 y 616 solo se reinician momentáneamente cuando ocurre un estado no respectivo, las salidas Q de los flip-flops D 612, 614 y 616 están acopladas a las compuertas OR 618, 620, y 622 a través de circuitos, lo que garantiza que las compuertas OR 618, 620 y 622 solo estén provistas de un pulso positivo estrecho y no una señal continua de valor uno. Por ejemplo, la salida Q del flip-flop D 612 está acoplada a las compuertas OR 620 y 622 mediante una compuerta AND, que recibe como entradas dicha salida Q y una versión invertida retrasada de la misma.

[0037] Los flip flops D 626, 628 y 630 de la segunda capa están configurados como flip flops de alternancia con sus salidas Q\_bar conectadas a sus entradas D. En consecuencia, los flip flops 626, 628 y 630 de la segunda capa alternan en los flancos ascendentes de sus respectivas señales de entrada de reloj 602, 604 y 606. Téngase en cuenta que los flancos ascendentes en las señales 602, 604 y 606 corresponden a transiciones de estado en el esquema de codificación de datos. Como tal, dado que exactamente una transición de estado puede ocurrir en cualquier momento, solo uno de los flip flops D de la segunda capa 626, 628, 630 alterna en cualquier momento. Las salidas Q\_bar de los flip flops 626, 628 y 630 se ingresan en una compuerta XOR 632 de tres entradas para generar un reloj receptor Rx\_Clk 636. Téngase en cuenta que el reloj receptor 636 alternará cada vez que cualquiera de las salidas Q\_bar de los flip flops 626, 628 y 630 alterne, generando así un reloj de media velocidad.

[0038] Los flip flops D 640, 642 y 644 de la tercera capa tienen entradas de reloj controladas respectivamente por las señales A-a-B 602, B-a-C 604 y C-a-A 606. Sus entradas D están acopladas en forma cruzada a las salidas Q de la primera capa, de manera que la salida Q del flip-flop 616 de la primera capa esté acoplada a la entrada D del flip flop 640, la salida Q del flip-flop 612 de la primera capa esté acoplada a la entrada D del flip flop 642 y la salida Q del flip flop 614 de la primera capa esté acoplada a la entrada D del flip flop 644.

[0039] Como tal, los flip flops 640, 642 y 644 de la tercera capa capturan las apariciones de los estados C a A, A a B y B a C, respectivamente, y emiten un 1 lógico, respectivamente, para las transiciones (C a A) a (A a B), (A a B) a (B a C) y (B a C) a (C a A). Estas transiciones son transiciones en el sentido de las agujas del reloj, como se ha indicado anteriormente con respecto a la figura 3. Para las transiciones en sentido contrario al de las agujas del reloj, los flip flops 640, 642 y 644 emiten todos un 0 lógico. Téngase en cuenta que, dado que exactamente una transición de estado puede ocurrir en cualquier momento, solo una de las salidas Q de los flip flops 640, 642 y 644 puede ser un 1 lógico en cualquier momento.

[0040] Las salidas Q de los flip flops 640, 642 y 644 se ingresan en el circuito multiplexor 646, proporcionando las salidas Q desde la primera capa 610 del flip flop las entradas de selección del multiplexor. En una realización, el multiplexor 646 incluye una capa de compuertas AND 648, 650 y 652, seguida de una compuerta OR de tres entradas 654. Las compuertas AND 648, 650 y 652 proporcionan las entradas de la compuerta OR 654, que proporciona la señal de salida 656 del circuito de recuperación de datos 600. Téngase en cuenta que la señal de salida 656 es un 1 lógico toda vez que una cualquiera de las compuertas AND 648, 650 y 652 emite un 1 lógico, lo que solo se produce en las transiciones de estado en el sentido de las agujas del reloj, como se ha descrito anteriormente. Por consiguiente, la señal de salida 656 es un 1 lógico para las transiciones de estado en el sentido de las agujas del reloj, teniendo así la capacidad de recuperar información codificada de acuerdo al esquema de modulación trifásico.

# Impacto del desplazamiento de temporización en la modulación trifásica

[0041] La figura 7 es un ejemplo 700 que ilustra el impacto de los desplazamientos de temporización en el esquema de codificación de datos de modulación trifásica. Como se muestra en la figura 7, un desplazamiento de temporización entre las señales A 702, B 704 y C 706 de los datos trifásicos y la señal de reloj provoca superposiciones de fase en la señal trifásica. Normalmente, este desplazamiento de temporización puede deberse a diferencias en los retardos de señal entre los conductores A, B y C. Como resultado, pueden aparecer condiciones ambiguas en las señales A>B 708, B>C 710 y C>A 712, que representan las entradas del circuito de recuperación de datos. Sin embargo, afortunadamente, estas condiciones ambiguas se pueden resolver mediante la adición de un voltaje o un desplazamiento de corriente, como se ilustra en las señales 714, 716 y 718.

#### Modulación trifásica codificada por polaridad

5

10

15

20

25

30

45

50

55

60

[0042] Como se ha descrito anteriormente, el esquema de codificación de datos de modulación trifásica utiliza transiciones de estado en el sentido de las agujas del reloj para transmitir unos lógicos y transiciones de estado en el sentido contrario al de las agujas del reloj para transmitir ceros lógicos. Como tal, se transmite exactamente un bit de datos durante cada transición de estado, ya sea en el sentido de las agujas del reloj o en el sentido contrario.

5

10

35

40

[0043] Sin embargo, la capacidad del esquema de codificación de datos de modulación trifásica puede aumentarse aún más aprovechando la polaridad de los estados de codificación, además de la direccionalidad de las transiciones de estado. Con referencia de nuevo a la figura 5, por ejemplo, la polaridad del flujo de corriente se puede utilizar para generar estados de codificación adicionales, tales como el positivo de A a B, el negativo de A a B, el positivo de B a C, el negativo de B a C, el positivo de C a A y el negativo de C a A. Al tener el doble del número de estados de codificación, se puede aumentar el número de transiciones de estado y, posteriormente, el número de bits de datos que se pueden codificar durante cada transición de estado. Este esquema de codificación se denomina modulación trifásica codificada por polaridad.

- 15 **[0044]** La figura 8 ilustra una tabla ejemplar de estados 800 de un esquema de codificación de datos de modulación trifásica, codificado por polaridad. Como lo entiende un experto en la materia, basándose en las enseñanzas en este documento, otros diagramas de estado también pueden ser posibles con correlaciones variadas, pero equivalentes, de transiciones de estado con bits transmitidos.

- [0045] De acuerdo a la tabla de estados 800, dos bits de datos se transmiten durante cada transición de estado, dando como resultado una duplicación de la capacidad del esquema de codificación de datos de la figura 3. También téngase en cuenta que las transiciones de estado en la tabla de estados 800 aún se ajustan a ser circulares, como se ilustra en el diagrama de estados 200 de la figura 2.

- [0046] En otras realizaciones, las transiciones de estados en la tabla ejemplar de estados 800 pueden dividirse adicionalmente para generar transiciones adicionales, admitiendo así un aumento adicional en la capacidad del esquema de codificación. Por ejemplo, la transición de estado (A a B positivo o negativo a B a C positivo) se puede dividir en dos transiciones (A a B positivo a B a C positivo) y (A a B negativo a B a C positivo). Por ejemplo, desde el estado A a B positivo, el siguiente estado puede ser uno cualquiera de los siguientes cinco estados: Negativo de A a B, positivo de B a C, negativo de B a C, positivo de C a A o negativo de C a A. Esto permite que se codifiquen log<sub>2(5)</sub> o, aproximadamente, 2,3216 bits de información en una única transición de estado. Usando esta técnica, es posible codificar 16 bits de información en 7 transiciones de estado consecutivas.

- [0047] La figura 12 ilustra un diagrama ejemplar de estados 1200 basado en el esquema de codificación de datos de modulación trifásica, codificado por polaridad, que muestra todas las posibles transiciones de estado entre los diferentes estados de codificación.

- [0048] La figura 9 es un ejemplo 900 que ilustra un esquema de codificación de datos de modulación trifásica, codificado por polaridad, según el diagrama de estados 800 de la figura 8.

- **[0049]** Una señal trifásica que gira en dos direcciones se transmite utilizando tres conductores A, B y C. Las tres señales 902, 904 y 906 (transportadas por los conductores A, B y C) que conforman la señal trifásica son independientes, estando cada señal desfasada en 120 grados con respecto a las dos restantes.

- [0050] En cualquier momento, exactamente dos de los conductores A, B y C llevan una señal, estando definidos los estados de codificación de los datos, tanto en términos de flujo de señal entre los conductores como en términos de la polaridad de dicho flujo de señal. La codificación de datos se realiza de acuerdo a las transiciones de estado según lo definido en el diagrama de estados 800. En una realización, las transiciones de estado en el sentido de las agujas del reloj (A a B a B a C, B a C a C a A y C a A a A a B) se utilizan para transmitir secuencias de datos que comienzan con un 1 lógico (10 y 11) y las transiciones de estado en el sentido contrario al de las agujas del reloj (A a B a C a A, B a C a A a B y C a A a B a C) se utilizan para transmitir secuencias de datos que comienzan con un cero lógico (00 y 01).

- [0051] La figura 13 ilustra un circuito ejemplar de recuperación de datos 1300 que se puede usar para decodificar datos transmitidos de acuerdo a un esquema de codificación de datos de modulación trifásica, codificado por polaridad. También se puede usar otra implementación del circuito de recuperación de datos, como entendería un experto en la materia basándose en las enseñanzas en el presente documento. El funcionamiento del circuito de recuperación 1300 se describe a continuación.

- [0052] El circuito de recuperación 1300 recibe las señales de entrada 1302, 1304, 1306, 1308, 1310 y 1312 desde los circuitos analógicos precedentes. En cualquier momento, solo una de las señales 1302, 1304, 1306, 1308, 1310 y 1312 puede tener un valor de uno, según cuál de los estados de codificación acaba de ocurrir. En la implementación, pueden ocurrir superposiciones o brechas entre las señales. Las señales de entrada 1302, 1304, 1306, 1308, 1310 y 1312 están acopladas respectivamente a las entradas de reloj de los flip flops D 11 a 16. Cada uno de los flip flops D 11 a 16 tiene su entrada de datos D acoplada a un uno lógico, lo que hace que su salida Q tenga un valor de uno toda vez que su respectiva entrada de reloj experimente una transición de flanco ascendente. Por ejemplo, el flip flop D 11

tendrá una salida Q de uno toda vez que la señal de entrada 1302 experimente una transición de flanco ascendente o, de manera equivalente, siempre que se produzca un estado positivo de A a B. Como tal, los flip flops D 11 a 16 capturan cuál de los seis estados acaba de ocurrir, según lo indicado por sus respectivas salidas Q 1322, 1324, 1326, 1328, 1330, 1332. Dado que solo puede ocurrir un estado en cualquier momento, solo una de las salidas 1322, 1324, 1326, 1328, 1330, 1332 puede continuar teniendo un valor de uno en cualquier momento. Como se describirá con más detalle más adelante, habrá una breve superposición toda vez que se produzca un nuevo estado, teniendo tanto las salidas Q correspondientes al estado actual como el nuevo estado un valor de uno en la duración del retraso para reiniciar los flip-flops.

- [0053] Cuando cualquiera de los estados es capturado por uno de los flip flops D 11 a 16, los otros flip flops se reiniciarán. En el circuito 1300, esto se logra utilizando las compuertas OR 1 a 6, que generan señales de reinicio para los respectivos flip flops D 11 a 16. Las compuertas OR 1 a 6 reciben, cada una, como entrada, pulsos causados por flancos ascendentes en las salidas Q de los flip flops D 11 a 16, excepto la salida Q de su respectivo flip-flop D y una señal de reinicio 1314. Por ejemplo, la compuerta OR 1 recibe pulsos causados por flancos ascendentes en las salidas Q 1324, 1326, 1328, 1330 y 1330 (pero no la salida Q 1322 de su respectivo flip flop D 11) de los flip-flops D 12 a 16 y la señal de Reinicio 1314. En consecuencia, la salida de la compuerta OR 1 será uno toda vez que se genere cualquier estado que no sea A a B positivo, o si se afirma la señal de Reinicio 1314. Por otro lado, cuando se produce el estado A a B positivo y no se afirma la señal de Reinicio 1341, la compuerta OR 1 emitirá un valor de cero.

- [0054] En una realización, para garantizar que los flip-flops D 11 a 16 solo se reinician momentáneamente cuando ocurre un estado no respectivo, las salidas Q de los flip-flops D 11 a 16 están acopladas a las compuertas OR 1 a 6 mediante circuitos, lo que garantiza que las compuertas OR 1 a 6 solo estén provistas de un pulso y no una señal continua de valor uno. Por ejemplo, la salida Q 1322 del flip-flop D 11 está acoplada a las compuertas OR 2 a 6 mediante una compuerta AND 71. La compuerta AND 71 recibe como entradas la salida Q 1322 y una versión invertida retrasada de la salida Q 1322. Téngase en cuenta que, justo antes de que el flip-flop D 11 capture una ocurrencia de estado positivo de A a B, la salida de la compuerta AND 71 es cero porque la salida Q 1322 es cero (el flip-flop D 11 se habría reiniciado previamente). Por otro lado, la versión invertida retrasada de Q tiene un valor de uno. Cuando se produce la entrada positiva de A a B, la salida Q 1322 cambia a uno. La versión invertida retrasada de Q mantiene un valor de uno en la duración del retardo (generado por un elemento de retardo, como se ilustra) antes de cambiar a cero. Por consiguiente, en la duración del retraso, la compuerta AND 71 emitirá un valor de uno, creando un pulso que reinicia los flip-flops 12 a 16.

35

40

45

60

- [0055] Los flip-flops D 21 a 26 se utilizan para generar una señal de reloj de frecuencia de datos doble Rx\_clk 1316, que efectúa una transición toda vez que se presenta una nueva entrada. Los flip-flops D 21 a 26, respectivamente, reciben como entradas de reloj las señales de entrada 1302, 1304, 1306, 1308, 1310 y 1312. Los flip-flops D 21 a 26 también reciben la señal de reinicio 1314. Como se muestra en la figura 13, cada uno de los flip flops D 21 a 26 tiene su salida Q\_bar realimentada a su entrada de datos D. Como tal, para cada uno de los flip-flops D 21 a 26, toda vez que su respectiva señal de reloj de entrada experimente una transición de flanco ascendente, su salida Q\_bar alternará entre uno y cero o entre cero y uno. Las salidas Q\_bar de los flip-flops D 21 a 26 se ingresan juntas a través de las compuertas XOR 35 y 36, como se ilustra en la figura 13. Las salidas de las compuertas XOR 35 y 36 son, a su vez, ingresadas juntas a través de la compuerta XOR 37. La compuerta XOR 37 emitirá un valor de uno toda vez que un número impar de las salidas Q\_bar de los flip-flops D 21 a 26 tengan un valor de uno. Dado que solo una de las salidas Q\_bar de los flip-flops D 21 a 26 alternará en cualquier momento mientras que las otras mantendrán el mismo valor, la salida de XOR 37 alternará para cada cambio en las entradas 1302, 1304, 1306, 1308, 1310 y 1312. Esto genera la señal de reloj de doble velocidad de datos Rx\_Clk 1316. En una realización, se utiliza un elemento de retardo 62 para garantizar que la señal Rx\_Clk esté sincronizada con las otras señales que son emitidas por el circuito de recuperación de datos 1300.

- [0056] La compuerta OR 31 genera la señal Rx\_Data\_Polarity 1318, que indica si el estado que acaba de ocurrir es de polaridad positiva o negativa. La compuerta OR 31 recibe como entradas las salidas Q 1322, 1324 y 1326 de los flip-flops D 11 a 13, respectivamente. Como tal, la compuerta OR 31 genera un valor de uno siempre que se produce una entrada de polaridad positiva (positiva de A a B, positiva de B a C o positiva de C a A). Por otro lado, la señal Rx Data Polarity 1318 tendrá un valor de cero cuando se produce un estado de polaridad negativa.

- [0057] Las compuertas OR 32, 33 y 34 se utilizan para capturar, respectivamente, cuándo ocurre un estado C a A (polaridad positiva o negativa), un estado A a B (polaridad positiva o negativa) y un estado B a C (polaridad positiva o negativa), independientemente de la polaridad. Por ejemplo, la compuerta OR 32 recibe como entradas las Salidas\_Q 1326 y 1332 de los flip-flops D 13 y 16, respectivamente. Como tal, la compuerta OR 32 genera un valor de uno toda vez que ocurre un estado positivo de C a A o uno negativo de C a A.

- [0058] Las salidas de las compuertas OR 32 a 34 están acopladas a las entradas de datos D de los flip-flops D 41 a 46, como se ilustra en la figura 13. La salida de la compuerta OR 32 está acoplada a las entradas D de los flip-flops D 41 y 44. De manera similar, la salida de la compuerta OR 33 está acoplada a las entradas D de los flip-flops D 42 y 45, y la salida de la compuerta OR 34 está acoplada a las entradas D de los flip-flops D 43 y 46. Al mismo tiempo, las entradas de reloj de los flip-flops D 41 a 46 están acopladas, respectivamente, a las entradas 1302, 1304, 1306, 1308, 1310 y 1312. En consecuencia, por ejemplo, el flip-flop D 41 tendrá una salida Q de valor uno toda vez que el estado

anterior sea de C a A (independientemente de la polaridad) y el estado actual sea de A a B positivo. Haciendo referencia a la figura 12, esto corresponde a las transiciones en el sentido de las agujas del reloj hacia el estado A a B positivo desde cualquiera de los estados C a A positivo o C a A negativo. De manera similar, el flip-flop D 44 tendrá una salida Q de valor uno toda vez que el estado anterior sea de C a A (independientemente de la polaridad) y el estado actual sea negativo de A a B. Haciendo referencia a la figura 12, esto corresponde a las transiciones en el sentido de las agujas del reloj hacia el estado A a B negativo desde cualquiera de los estados C a A positivo o C a A negativo. En consecuencia, los flip-flops D 41 a 46 capturan, cada uno, una de las seis transiciones en el sentido de las agujas del reloj en el diagrama de estados 1200 en la figura 12.

10 [0059] Las salidas Q de los flip-flops D 41 a 46 se ingresan, junto con las respectivas salidas Q de los flip-flops D 11 a 16, en las respectivas compuertas AND 51 a 56, como se ilustra en la figura 13. Por ejemplo, la salida Q del flip-flop D 41 se ingresa, junto con la salida Q 1322 del flip-flop D 11, en la compuerta AND 51. Las compuertas AND 51 a 56 se utilizan para garantizar que solo una de las seis transiciones en el sentido de las agujas del reloj se refleje en cualquier momento. En otras palabras, solo una de las salidas de las compuertas AND 51 a 56 puede tener un valor de uno en cualquier momento. Las salidas de las compuertas AND 51 a 56 se ingresan juntas en una compuerta OR 15 61 para generar la Rx Data Phase 1320. En consecuencia, la Rx Data Phase 1320 tiene un valor de uno, toda vez que se produce una transición de fase en el sentido de las agujas del reloj, y un valor de cero en caso contrario. Téngase en cuenta que la Rx Data Phase 1320 puede tener un valor de cero si se produce una transición en sentido contrario al de las agujas del reloj o de polaridad solamente (la misma transición de fase; por ejemplo, de A a B positiva 20 a A a B negativa). Por ejemplo, si el estado actual es positivo de A a B, el circuito de recuperación 1300 generará los mismos valores para la Rx Data polarity 1318 y la Rx Data phase 1320 si el siguiente estado es C a A negativo o A a B negativo. Por lo tanto, se requieren circuitos adicionales para distinguir entre estos tipos de transiciones.

[0060] La figura 14 ilustra circuitos adicionales 1400 para capturar transiciones de polaridad solamente. Las entradas a los circuitos 1400 incluyen las señales de entrada 1302, 1304, 1306, 1308, 1310 y 1312 y las salidas Q 1322, 1324, 1326, 1328, 1330 y 1332 de los flip-flops D 11 a 16. El circuito 1400 incluye los flip-flops D 71 a 76, que se utilizan para capturar transiciones de polaridad solamente. Por ejemplo, el flip-flop D 71 recibe la señal de entrada 1302 como entrada de reloj y la señal de salida Q 1328 como entrada de datos D y se utiliza para capturar transiciones de A a B negativo a A a B positivo. Téngase en cuenta que, cuando se produce un estado negativo de A a B, la salida Q de 1328 tendrá un valor de uno. Posteriormente, cuando se produce un estado positivo de A a B, la salida Q 1328 continuará teniendo un valor de uno durante la demora entre el momento en que la salida Q 1322 cambia su valor a uno y el momento en que los flip-flops 12 a 16 se reinician. Durante ese tiempo de retardo, tanto la señal de entrada 1302 como la salida Q 1328 tendrán un valor de uno, lo que provoca que la salida Q del flip-flop D 71 cambie a un valor de uno. Esto también hace que la salida de la compuerta AND 81 tenga un valor de uno. El funcionamiento de los flip-flops D 72 a 76 y las respectivas compuertas AND 82 a 86 es similar.

[0061] Las salidas de las compuertas AND 81 a 86 se ingresan juntas en una compuerta OR 87, que genera la señal de salida Rx\_Data\_same\_phase 1402. La señal de salida Rx\_Data\_same\_phase 1402 tiene, por lo tanto, un valor de uno toda vez que se produce una cualquiera de las seis posibles transiciones de estado de polaridad solamente. Como tal, la Rx\_Data\_same\_phase 1402 se puede usar para determinar si una transición es de polaridad solamente o de sentido contrario al de las agujas del reloj, siempre que la Rx\_Data\_phase 1320 de los circuitos 1300 tenga un valor de cero.

[0062] Téngase en cuenta que los circuitos 1400 son operables junto con el circuito de recuperación de datos 1300 de la figura 13. En otras palabras, la salida Rx\_Data\_same\_phase 1402 de los circuitos 1400 se proporciona, junto con las salidas Rx\_Clk 1316, Rx\_Data\_polarity 1318 y Rx\_Data\_phase 1320 del circuito 1300, a una etapa de decodificador posterior para su decodificación, como se ilustrará más adelante.

[0063] La figura 15 es una realización ejemplar 1500 de un decodificador 1502 que puede usarse para decodificar las salidas generadas por el circuito de recuperación de datos ilustrado en las figuras 13 y 14. El decodificador 1502 recibe siete conjuntos de entrada 1504, 1506, 1508, 1510, 1512, 1514 y 1516. En la realización ejemplar 1500, cada conjunto de entrada es una entrada de 3 bits con un bit para cada una de las salidas Rx\_Data\_phase, Rx\_Data\_polarity y Rx\_Data\_same\_phase del circuito de recuperación de datos ilustrado en las figuras 13 y 14. El decodificador 1502 decodifica los siete conjuntos de entrada de 3 bits recibidos para generar una salida de datos de 16 bits 1518. También son posibles otras variaciones del decodificador 1502, tal como puede entender un experto en la materia. Por ejemplo, el decodificador 1502 puede recibir más o menos de siete conjuntos de entrada y / o generar una salida de datos de longitud diferente 1518.

#### Implementaciones ejemplares de interfaz en serie

25

30

35

40

45

50

55

60

65

[0064] Las figuras 10 y 11 ilustran implementaciones ejemplares de interfaz en serie, que emplean los esquemas de codificación de datos de modulación trifásica de la presente invención. La figura 10 ilustra una implementación ejemplar 1000 en una placa de cableado impreso. Como se muestra, tres conductores A, B y C están intercalados con la tierra en una capa superior con un núcleo dieléctrico que los separa de la tierra en una capa inferior. En una realización, la impedancia de cualquier conductor a tierra tiene un valor Z0. La figura 11 ilustra una implementación ejemplar 1100 utilizando un cable de trío torcido.

## Modulación trifásica para interfaz digital de pantalla móvil (MDDI)

[0065] La interfaz digital de pantalla móvil (MDDI) es un mecanismo de transferencia efectivo en términos de coste y de bajo consumo de energía, que permite la transferencia de datos en serie a muy alta velocidad por un enlace de comunicación de corto alcance entre un anfitrión y un cliente. En ciertas realizaciones, una interfaz MDDI puede beneficiarse del uso de los esquemas de codificación de datos de modulación trifásica de la presente invención.

[0066] En un aspecto, un anfitrión de la MDDI puede comprender uno entre varios tipos de dispositivos que pueden beneficiarse del uso de los esquemas de codificación de datos de la presente invención. Por ejemplo, el anfitrión podría ser un ordenador portátil en forma de un ordenador de mano, un ordenador portátil o un dispositivo informático móvil similar. También podría ser un asistente de datos personales (PDA), un dispositivo de paginación o uno de los muchos teléfonos o módems inalámbricos. Alternativamente, el anfitrión podría ser un dispositivo portátil de entretenimiento o presentación, tal como un reproductor portátil de DVD o CD, o un dispositivo de reproducción de juegos. Además, el anfitrión puede residir como un dispositivo anfitrión o elemento de control entre otros variados productos comerciales, ampliamente utilizados o planificados, para los cuales se desea un enlace de comunicación de alta velocidad con un cliente. Por ejemplo, un anfitrión podría usarse para transferir datos a altas velocidades desde un dispositivo de grabación de vídeo a un cliente basado en almacenamiento para mejorar la respuesta, o a una pantalla más grande de alta resolución para presentaciones. En general, los expertos en la técnica apreciarán la amplia variedad de dispositivos y accesorios electrónicos modernos que pueden beneficiarse del uso de esta interfaz, así como la capacidad de retro-adaptar dispositivos más antiguos con un transporte de información a una mayor velocidad de datos, utilizando un número limitado de conductores disponibles en conectores o cables recién agregados o existentes. Al mismo tiempo, un cliente de MDDI puede comprender varios dispositivos útiles para presentar información a un usuario final, o presentar información desde un usuario al anfitrión. Por ejemplo, una micro-pantalla incorporada en antiparras o gafas, un dispositivo de proyección incorporado en un sombrero o casco, una pantalla pequeña o incluso un elemento holográfico incorporado en un vehículo, tal como en una ventana o parabrisas, o varios altavoces, auriculares o sistemas de sonido para presentación de sonido o música de alta calidad. Otros dispositivos de presentación incluyen proyectores o dispositivos de proyección utilizados para presentar información para conferencias, o para películas e imágenes de televisión. Otros ejemplos incluyen el uso de almohadillas táctiles o dispositivos sensibles, dispositivos de entrada de reconocimiento de voz, escáneres de seguridad, etc., que pueden ser solicitados para transferir una cantidad significativa de información desde un dispositivo o usuario del sistema con poca "entrada" real que no sea tacto o sonido del usuario. Además, las estaciones de acoplamiento para ordenadores y los equipos de automóviles o equipos de sobremesa y los soportes para teléfonos inalámbricos pueden actuar como dispositivos de interfaz para usuarios finales u otros dispositivos y equipos, y emplear clientes (dispositivos de salida o de entrada, como ratones) o anfitriones para asistir en la transferencia de datos, especialmente cuando se trata de redes de alta velocidad. Sin embargo, los expertos en la materia reconocerán inmediatamente que la presente invención no se limita a estos dispositivos, ya que existen muchos otros dispositivos en el mercado, y propuestos para su uso, que están concebidos para proporcionar a los usuarios finales imágenes y sonido de alta calidad, ya sea en términos de almacenamiento y transporte o en términos de presentación en reproducción. La presente invención es útil para aumentar el caudal de datos entre diversos elementos o dispositivos, para asimilar las altas velocidades de datos necesarias para realizar la experiencia de usuario deseada.

## Conclusión

5

10

15

20

25

30

35

40

45 [0067] Si bien varias realizaciones de la presente invención se han descrito anteriormente, debería entenderse que se han presentado solo a modo de ejemplo, y no de limitación. Será evidente para los expertos en la materia relevante que diversos cambios de forma y detalle pueden realizarse sin apartarse del alcance de la invención. Por lo tanto, la amplitud y el alcance de la presente invención no deberían estar limitados por ninguna de las realizaciones ejemplares descritas anteriormente, sino que deberían definirse solo de acuerdo a las siguientes reivindicaciones. 50

#### REIVINDICACIONES

- 1. Un procedimiento para la codificación de datos, que comprende:

- a) transmitir una primera señal en una primera polaridad entre los dos primeros de los conductores primero, segundo y tercero (A, B, C), dejando el conductor restante en circuito abierto;

- b) transmitir una segunda señal en una segunda polaridad entre los dos segundos de dichos conductores primero, segundo y tercero, dejando el conductor restante en circuito abierto, en donde la primera polaridad es diferente a la segunda polaridad o los dos primeros conductores son diferentes a los dos segundos conductores, o la primera polaridad y los dos primeros conductores son diferentes a la segunda polaridad y los dos segundos conductores, y donde

- la etapa a) define un primer estado de codificación de datos con la primera polaridad y los dos primeros conductores;

la etapa b) define un segundo estado de codificación de datos con la segunda polaridad y los dos segundos conductores; y

20 en donde transmitir la primera señal incluye:

10

25

35

55

durante un primero de dos intervalos de tiempo secuenciales,

- dejar en circuito abierto al primer conductor, y

- proporcionar un diferencial de voltaje entre el segundo conductor y el tercer conductor; y

- en donde transmitir la segunda señal incluye:

- 30 durante un segundo de los dos intervalos de tiempo secuenciales,

- dejar en circuito abierto el segundo conductor y proporcionar el diferencial de voltaje entre el primer conductor y el tercer conductor cuando los datos a codificar en una transición entre los dos intervalos de tiempo secuenciales tienen un primer valor, y

- dejar en circuito abierto el tercer conductor y proporcionar el diferencial de voltaje entre el primer conductor y el segundo conductor cuando los datos a codificar en la transición entre los dos intervalos de tiempo secuenciales tienen un segundo valor.

- 40 **2.** El procedimiento según la reivindicación 1, en el que el segundo conductor está en circuito abierto cuando un primer bit de los datos a codificar en la transición entre los dos intervalos de tiempo secuenciales está en un primer estado binario, y el tercer conductor está en circuito abierto cuando el primer bit de los datos está en un segundo estado binario diferente al primer estado binario.

- 45 **3.** El procedimiento según la reivindicación 2, en el que el diferencial de voltaje se proporciona aplicando un primer nivel de voltaje a un conductor y un segundo nivel de voltaje a otro conductor, teniendo el primer nivel de voltaje una polaridad diferente a la del segundo nivel de voltaje.

- El procedimiento según la reivindicación 3, en el que la codificación de un segundo bit de los datos a codificar

en una selección de polaridades para el primer nivel de tensión y el segundo nivel de tensión en la transición entre los dos intervalos de tiempo secuenciales se basa en los datos a codificar.

- 5. El procedimiento según la reivindicación 4, en el que las polaridades del primer nivel de voltaje y del segundo nivel de voltaje se seleccionan basándose en un estado binario del segundo bit de los datos a codificar.

- **6.** El procedimiento según la reivindicación 5, en el que dos bits de datos se codifican en cada transición entre una pluralidad de intervalos de tiempo secuenciales.

- 7. El procedimiento según la reivindicación 1, en el que un bit de datos se codifica en cada transición entre pares secuenciales de una pluralidad de intervalos de tiempo secuenciales.

- **8.** El procedimiento según la reivindicación 1, en el que, durante el segundo de los dos intervalos de tiempo secuenciales, la transmisión de la segunda señal incluye además:

- dejar en circuito abierto el primer conductor e invertir las polaridades de los voltajes aplicados a los conductores segundo y tercero cuando los datos a codificar en la transición entre los dos intervalos de tiempo secuenciales

tienen un tercer valor. 9. El procedimiento según la reivindicación 8, en el que 16 bits de datos se codifican utilizando 7 transiciones entre intervalos de tiempo secuenciales. 5 10. El procedimiento según la reivindicación 1, en el que uno entre el primer conductor, el segundo conductor y el tercer conductor está en circuito abierto durante cada uno entre una pluralidad de intervalos de tiempo secuenciales, se proporciona un diferencial de voltaje a los otros dos entre el primer conductor, el segundo conductor y el tercer conductor, y 10 el diferencial de voltaje tiene una polaridad que es una entre una polaridad positiva o una polaridad negativa. proporcionando así seis estados de señalización utilizando tres conductores. El procedimiento de la reivindicación 10, en el que se produce un cambio de conductor de circuito abierto en 11. 15 cada transición entre intervalos de tiempo secuenciales, y se codifican dos bits de datos en cada transición. 12. El procedimiento de la reivindicación 1, en el que al menos uno entre un cambio de polaridad del diferencial de voltaje y un cambio de conductor en circuito abierto se produce en cada transición entre intervalos de tiempo secuenciales, proporcionando así 5 posibles cambios de estado en cada transición. 20 13. Un circuito transmisor de interfaz en serie (400), que comprende: conductores primero, segundo y tercero, teniendo cada uno extremos primero y segundo; 25 una pluralidad de fuentes de corriente (402a a 402f); una pluralidad de conmutadores (404a a 404f) que acoplan selectivamente la pluralidad de fuentes de corriente a los primeros extremos de dichos conductores primero, segundo y tercero; y 30 una pluralidad de impedancias (406a a 406f) que acoplan entre sí los segundos extremos de los conductores primero, segundo y tercero; en donde el circuito está configurado para 35 a) transmitir una primera señal en una primera polaridad entre los dos primeros de los conductores primero, segundo y tercero, dejando el conductor restante en circuito abierto: b) transmitir una segunda señal en una segunda polaridad entre los dos segundos de dichos conductores primero, segundo y tercero, dejando el conductor restante en circuito abierto, en donde la primera polaridad es diferente a la segunda polaridad o los dos primeros conductores son diferentes a 40 los dos segundos conductores, o la primera polaridad y los dos primeros conductores son diferentes a la segunda polaridad y los dos segundos conductores, y en donde la etapa a) define un primer estado de codificación de datos definido por la primera polaridad y los primeros dos conductores, y la etapa b) define un segundo estado de codificación de datos definido por la segunda polaridad y los segundos 45 dos conductores, y en donde transmitir la primera señal incluye: durante un primero de dos intervalos de tiempo secuenciales, 50 dejar en circuito abierto al primer conductor, y proporcionar un diferencial de voltaje entre el segundo conductor y el tercer conductor; y en donde transmitir la segunda señal incluye: 55 durante un segundo de los dos intervalos de tiempo secuenciales, dejar en circuito abierto el segundo conductor y proporcionar el diferencial de voltaje entre el primer 60 conductor y el tercer conductor cuando los datos a codificar en una transición entre los dos intervalos

dejar en circuito abierto el tercer conductor y proporcionar el diferencial de voltaje entre el primer conductor y el segundo conductor cuando los datos a codificar en la transición entre los dos

de tiempo secuenciales tienen un primer valor, y

intervalos de tiempo secuenciales tienen un segundo valor.

14. El circuito transmisor de interfaz en serie según la reivindicación 13, en el que al menos uno entre un cambio de polaridad del diferencial de voltaje y un cambio de conductor en circuito abierto se produce en cada transición, entre intervalos de tiempo secuenciales, proporcionando así 5 posibles cambios de estado en cada transición.

FIG. 5

| 800 | ۷_ |

|-----|----|

|     | _  |

| Bits<br>Transmitidos | 1 11        | 1 10             | 1 01        | 1 00     | 1 11     | 1 10     | 1 01        | 1 00                  | 1 11        | 1 10        | 1 01     | 1 00     |

|----------------------|-------------|------------------|-------------|----------|----------|----------|-------------|-----------------------|-------------|-------------|----------|----------|

|                      | +           | +                | +           | +        | +        | +        | t<br>+      | +                     | +           | +           | +        | +        |

|                      | bit         | el bit           | bit         | bit      | bit      | bit      | el bit      | bit                   | bit         | bit         | bit      | bit      |

|                      | e1          |                  | e1          | e1       | e1       | e1       |             | el el                 | e1          | e1          | e1       | e1       |

|                      | en          | en               | en          | en       | en       | en       | en          | en                    | en          | en          | en       | en       |

|                      | ivo         | ivo              | ivo         | ivo      | ivo      | ivo      | ivo         | ivo                   | ivo         | ivo         | ivo      | ivo      |

|                      | positivo en | negativo en      | positivo en | negativo | positivo | negativo | positivo en | negativo en           | positivo en | negativo en | positivo | negativo |

|                      | ς<br>Ā      | C                | A Po        | A ne     | A P      | A ne     | ВР          | Впе                   | В           | В           | υ<br>Ď   | C        |

|                      | ď           | ď                | ď           | ď        | ď        | ď        | ď           | rd<br>T               | rd<br>_     | ď           | ď        | ď        |

|                      | В           | В                | υ           | υ        | υ        | υ        | Æ           | Ø                     | Æ           | Æ           | щ        | щ        |

|                      | ď           | Ø                | ď           | ď        | ď        | ď        | rd          | ď                     | Ŋ           | Ŋ           | Ŋ        | Ŋ        |

|                      | r r         | r r              | ¤           | r .      | r r      | r r      | r r         | r r                   | ¤           | ¤           | r r      | ¤        |

|                      | bit         | bit              | bit         | bit      | bit      | bit      | el bit      | bit                   | bit         | bit         | bit      | bit      |

|                      | e1          | e1               | e1          | e1       | e1       | e1       | e1          | e1                    | e1          | el          | el       | e1       |

|                      | en          | en               | en          | en       | en       | en       | en          | en                    | en          | en          | en       | en       |

|                      | 0           | 0                | 0           | 0        |          |          | 0           | 0                     |             | 0           | 0        |          |

|                      | ti          | ti               | ţį          | ţį       | ţį       | ţį       | ti          | ti                    | ti          | ti          | ţį       | ţį       |

|                      | negativo    | ega              | ega         | negativo | negativo | negativo | negativo    | ega                   | ega         | negativo    | negativo | negativo |

|                      | o ne        | o negativo en el | o negativo  | o ne     | o ne     | o ne     | o ne        | C positivo o negativo | o negativo  | o ne        | 0 10     | o ne     |

| _                    |             | 0                |             |          |          |          | 0           | 0                     |             |             |          |          |

| jón                  | Σįν         | ivo              | i.v         | ivo      | Σįν      | ;iv      | :iv         | ;iv                   | Σiν         | ιiν         | civo     | civo     |

| JSic                 | positivo    | sit              | sit         | sit      | positivo | sit      | sit         | sit                   | sit         | sit         | sit      | sit      |

| Transición           | Ъ           | posit            | positivo    | positi   |          | positivo | positivo    | ро                    | A positivo  | A positivo  | posit    | positi   |

| '                    | Д           | В                | аВ          | Д        | υ        | υ        | υ           | υ                     | Æ           | Æ           | Æ        | Æ        |

|                      | ď           | ď                | ď           | ď        | ø        | ď        | ď           | ď                     | ď           | ď           | ď        | ď        |

|                      | A           | A                | Ą           | A        | В        | В        | В           | В                     | ບ           | ບ           | υ        | ບ        |

|                      |             |                  |             |          |          |          |             |                       |             |             |          |          |

|                      |             |                  |             |          |          |          |             |                       |             |             |          |          |