OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 731 431

(51) Int. CI.:

C12Q 1/00 (2006.01) C12Q 1/68 (2008.01) C12M 1/34 (2006.01) G01N 33/487 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

11.03.2015 PCT/US2015/019973 (86) Fecha de presentación y número de la solicitud internacional:

(87) Fecha y número de publicación internacional: 01.10.2015 WO15148127

(96) Fecha de presentación y número de la solicitud europea: 11.03.2015 E 15769702 (0) 17.04.2019

$^{ ilde{(54)}}$ Título: Chips de secuenciación basados en nanoporos que usan tecnología de obleas apiladas

(30) Prioridad:

25.03.2014 US 201414225263

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 15.11.2019

(97) Fecha y número de publicación de la concesión europea:

(73) Titular/es:

**GENIA TECHNOLOGIES, INC. (100.0%)** 2841 Scott Blvd. Santa Clara CA 95050, US

EP 3122891

(72) Inventor/es:

TIAN, HUI

(74) Agente/Representante:

LINAGE GONZÁLEZ, Rafael

#### **DESCRIPCIÓN**

Chips de secuenciación basados en nanoporos que usan tecnología de obleas apiladas

#### 5 ANTECEDENTES DE LA INVENCIÓN

10

25

45

Los avances en microminiaturización dentro de la industria de semiconductores en los últimos años han permitido a los biotecnólogos comenzar a empaquetar herramientas de detección tradicionalmente voluminosas en factores de forma cada vez más pequeños, en los llamados biochips. Sería deseable desarrollar técnicas para los biochips que los hagan más robustos, eficientes y rentables. Un chip de secuenciación basado en nanoporos relacionado se divulga en el documento US 2010/0292101.

#### **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

Diversos modos de realización de la invención se divulgan en la siguiente descripción detallada y en los dibujos adjuntos.

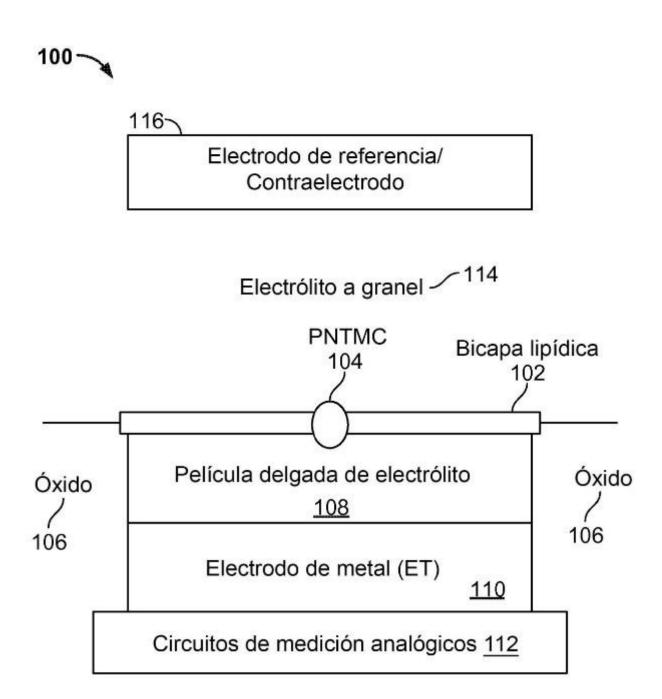

La figura 1 ilustra un modo de realización de una celda 100 en un chip de secuenciación basado en nanoporos.

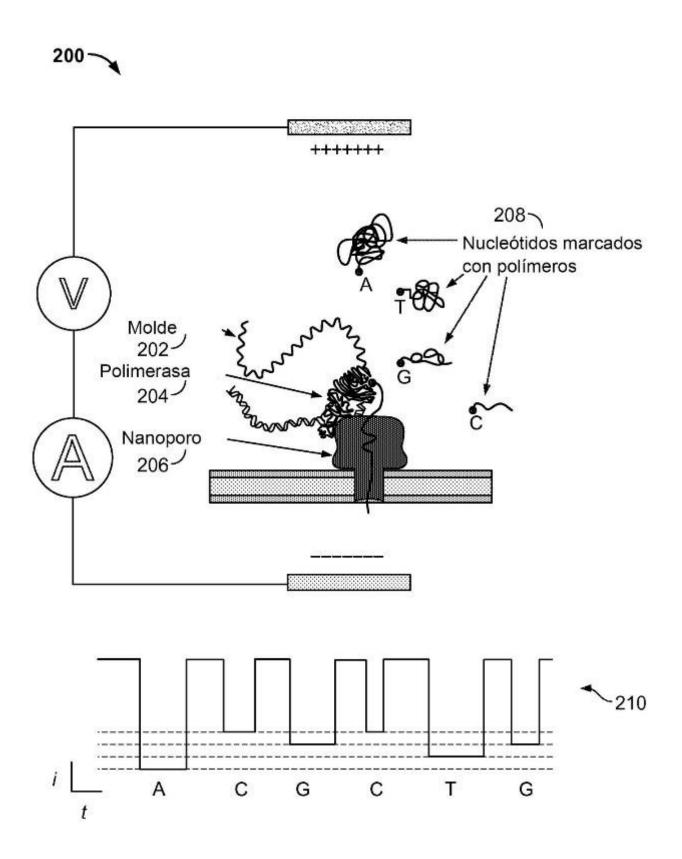

20 La figura 2 ilustra un modo de realización de una celda 200 que realiza la secuenciación de nucleótidos con la técnica nano-SBS.

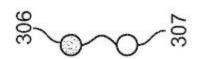

La figura 3 ilustra un modo de realización de una celda que realiza la secuenciación de nucleótidos con marcadores precargados.

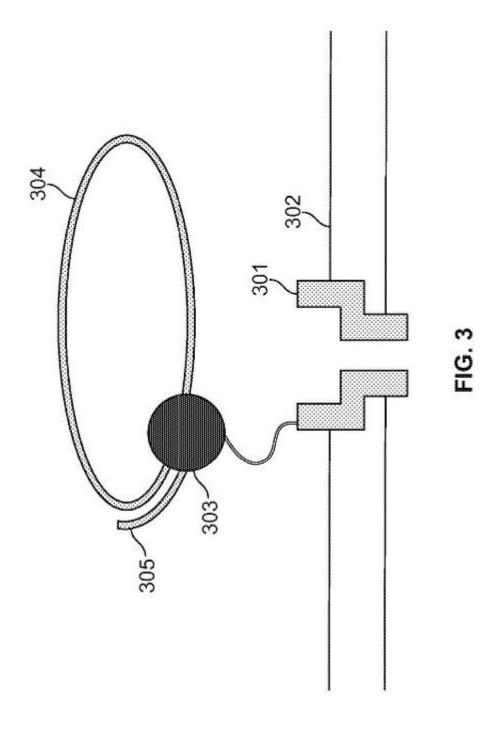

La figura 4 ilustra un modo de realización de un procedimiento 400 para la secuenciación de ácidos nucleicos con marcadores precargados.

La figura 5A ilustra un modo de realización de un chip de secuenciación basado en nanoporos de obleas apiladas 500 que incluye dos obleas separadas (502 y 504).

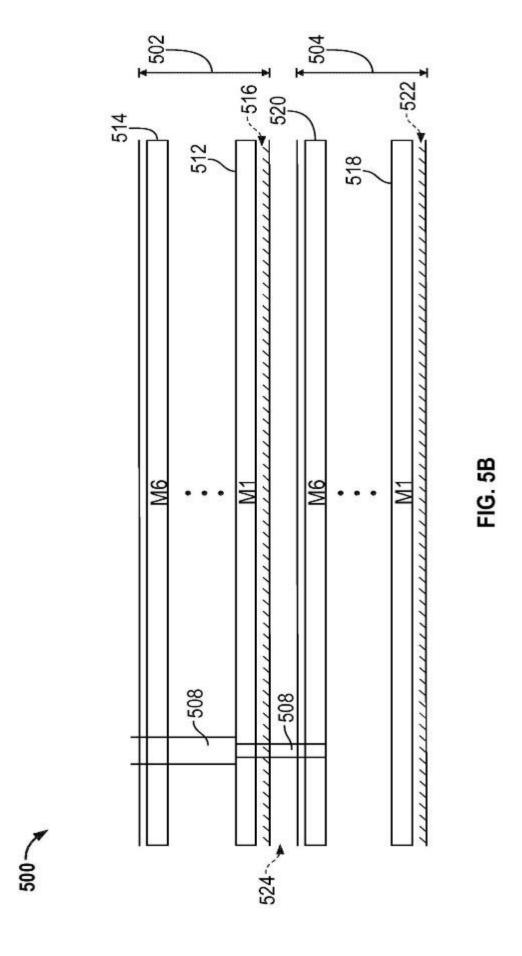

La figura 5B ilustra la vista en sección transversal del chip de secuenciación basado en nanoporos de obleas apiladas 500.

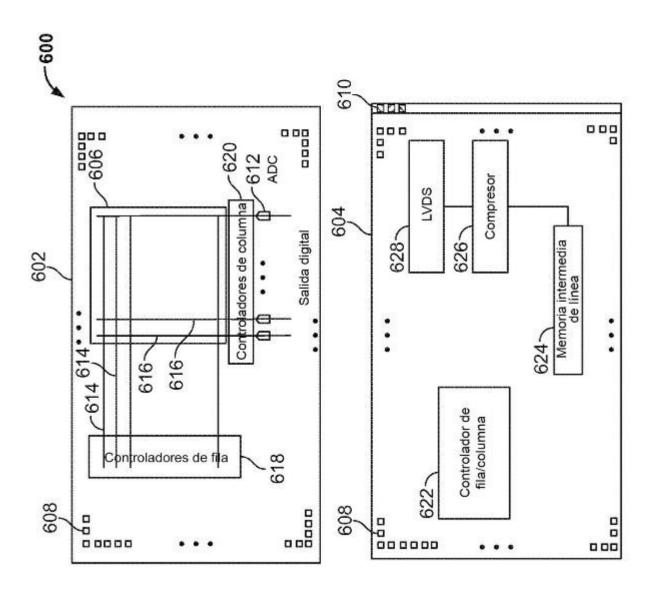

La figura 6 ilustra un modo de realización de un chip de secuenciación basado en nanoporos de obleas apiladas 600 que incluye dos obleas separadas, una oblea superior 602 y una oblea inferior 604.

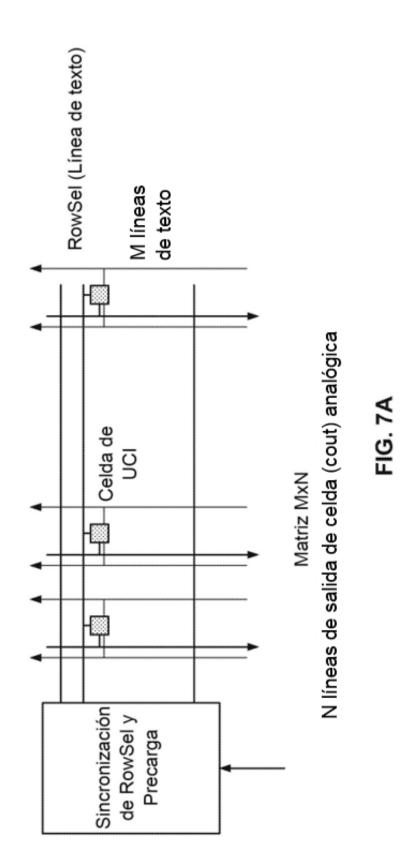

La figura 7A ilustra un modo de realización de un banco de celdas M x N.

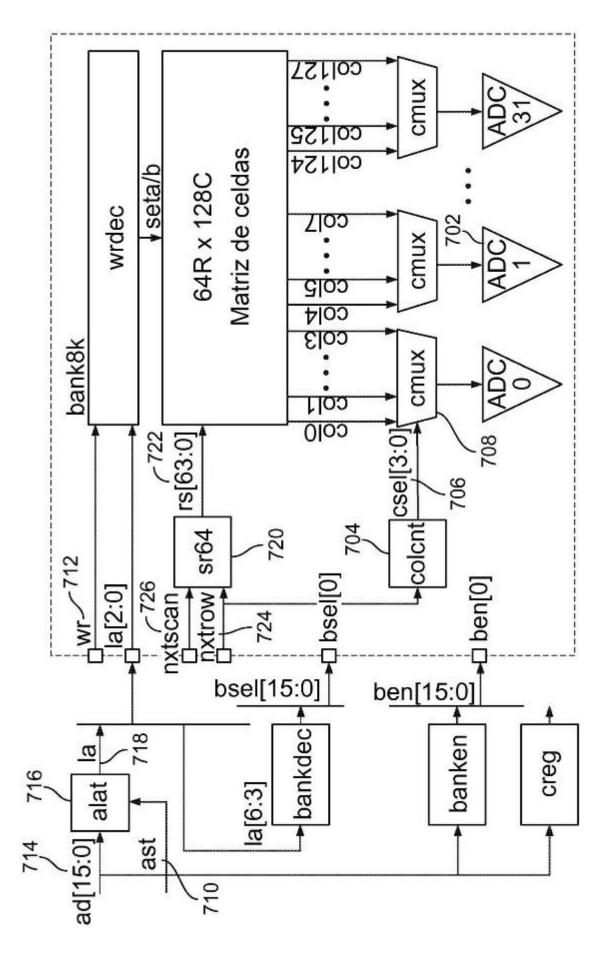

40 La figura 7B ilustra un modo de realización de un bloque bank8k.

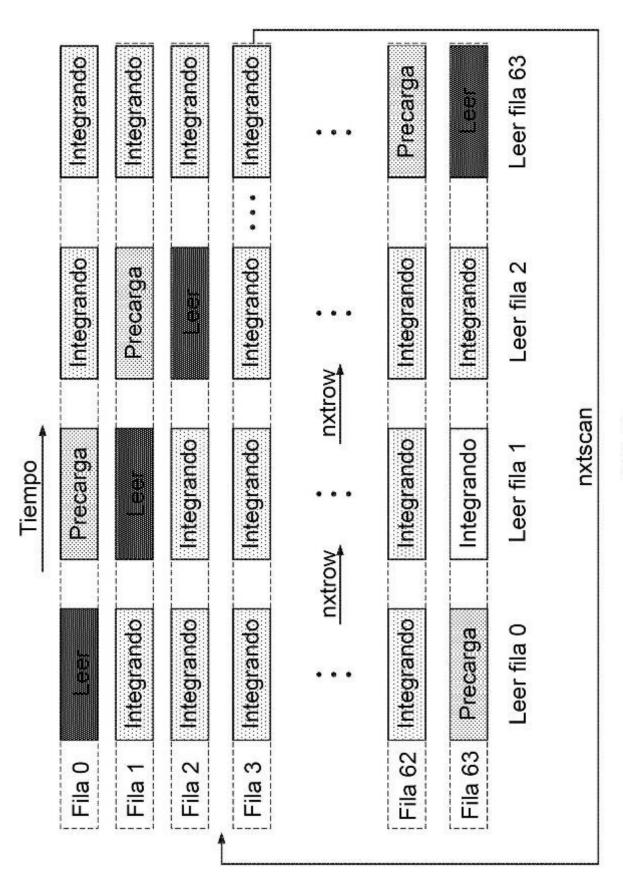

La figura 8 ilustra un modo de realización de una secuencia de escaneo.

La figura 9 ilustra un modo de realización de una secuencia de escaneo.

La figura 10 ilustra un modo de realización en el que se puede escanear una fracción de la matriz cada vez.

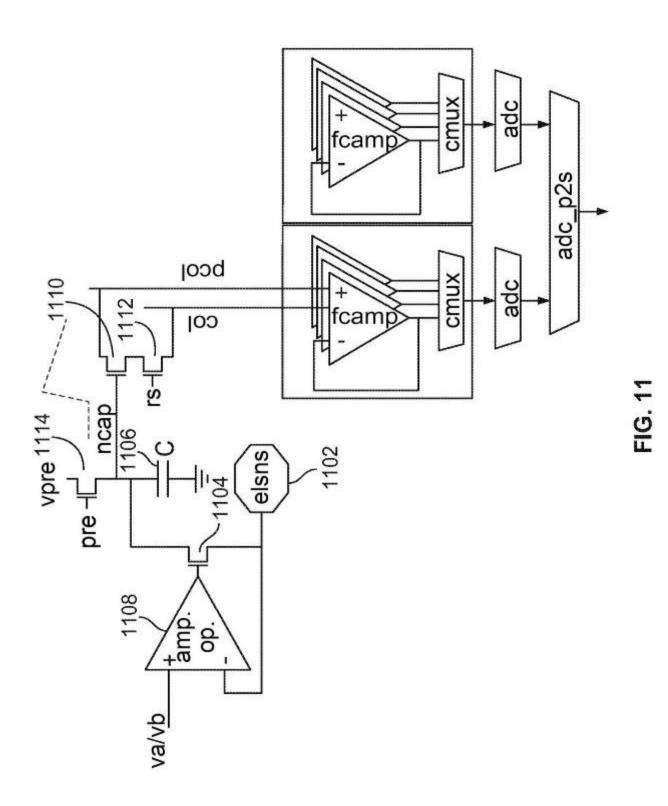

La figura 11 ilustra un modo de realización de un circuito analógico para medir la corriente en una celda.

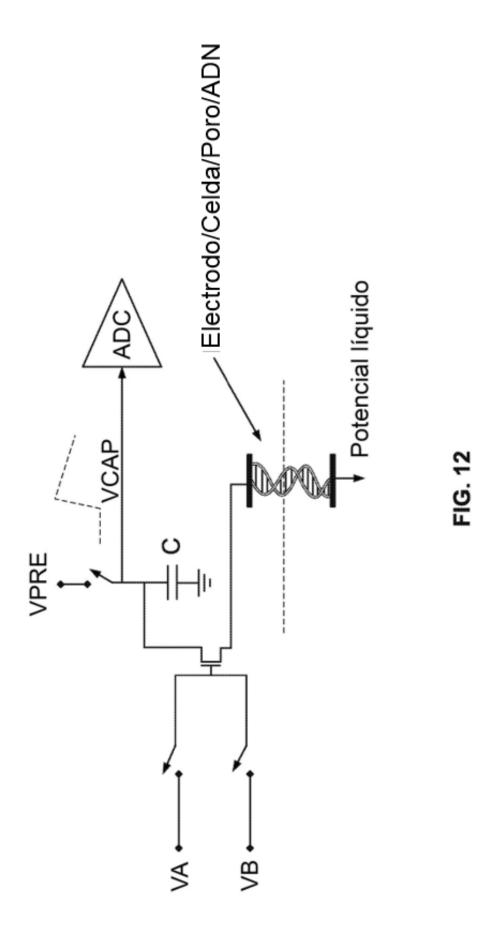

50 La figura 12 ilustra un modo de realización de un circuito analógico para medir la corriente en una celda.

#### **DESCRIPCIÓN DETALLADA**

La invención se puede implementar de numerosas maneras, incluyendo como un procedimiento; un aparato; un sistema; una composición de materia; un producto de programa de ordenador incorporado en un medio de almacenamiento legible por ordenador; y/o un procesador, tal como un procesador configurado para ejecutar instrucciones almacenadas en una memoria acoplada al procesador y/o proporcionadas por la misma. En esta memoria descriptiva, estas implementaciones, o cualquier otra forma que pueda adoptar la invención, se pueden denominar técnicas. En general, el orden de las etapas de los procedimientos divulgados se puede modificar dentro del alcance de la invención. A menos que se establezca de otro modo, un componente tal como un procesador o una memoria que se describe como configurado para realizar una tarea se puede implementar como un componente general que se configura temporalmente para realizar la tarea en un momento dado o un componente específico que se fabrica para realizar la tarea. Como se usa en el presente documento, el término "procesador" se refiere a uno o más dispositivos, circuitos y/o núcleos de procesamiento configurados para procesar datos, tal como instrucciones de un programa de ordenador.

A continuación se proporciona una descripción detallada de uno o más modos de realización de la invención junto con figuras adjuntas que ilustran los principios de la invención. La invención se describe en relación con dichos modos de realización, pero la invención no está limitada a ningún modo de realización. El alcance de la invención está limitado solo por las reivindicaciones y la invención engloba numerosas alternativas, modificaciones y equivalentes. Numerosos detalles específicos se exponen en la siguiente descripción para proporcionar una comprensión completa de la invención. Estos detalles se proporcionan para el propósito de ejemplo y la invención se puede poner en práctica de acuerdo con las reivindicaciones sin algunos o todos estos detalles específicos. Para propósitos de claridad, el material técnico que se conoce en los campos técnicos relacionados con la invención no se ha descrito en detalle, para que la invención no quede innecesariamente oscurecida.

Los dispositivos de membrana de nanoporos que tienen tamaños de poro del orden de un nanómetro de diámetro interno han resultado prometedores en la secuenciación rápida de nucleótidos. Cuando se aplica un potencial de voltaje a través de un nanoporo sumergido en un fluido conductor, se puede observar una pequeña corriente iónica atribuida a la conducción de iones a través del nanoporo. El tamaño de la corriente es sensible al tamaño de poro.

Un chip de secuenciación basado en nanoporos se puede usar para la secuenciación de ADN. Un chip de secuenciación basado en nanoporos incorpora un gran número de celdas de sensores configuradas como una matriz. Por ejemplo, una matriz de un millón de celdas puede incluir 1000 filas por 1000 columnas de celdas.

La figura 1 ilustra un modo de realización de una celda 100 en un chip de secuenciación basado en nanoporos. Se forma una bicapa lipídica 102 sobre la superficie de la celda. El electrólito a granel 114 que contiene complejos moleculares transmembranarios de nanoporos de proteínas solubles (PNTMC) y el analito de interés se coloca directamente sobre la superficie de la celda. Se inserta un único PNTMC 104 en la bicapa lipídica 102 por electroporación. Las bicapas lipídicas individuales en la matriz no están conectadas entre sí, ni química ni eléctricamente. Por tanto, cada celda de la matriz es una máquina de secuenciación independiente, que produce datos únicos para la única molécula de polímero asociada con el PNTMC. El PNTMC 104 funciona en los analitos y modula la corriente iónica a través de la bicapa impermeable de otro modo.

Con referencia continua a la figura 1, los circuitos de medición analógicos 112 se conectan a un electrodo de metal 110 cubierto por una película delgada de electrólito 108. La película delgada de electrólito 108 está aislada del electrólito a granel 114 por la bicapa lipídica impermeable a iones 102. El PNTMC 104 atraviesa la bicapa lipídica 102 y proporciona la única ruta para que la corriente iónica fluya desde el líquido a granel al electrodo de metal 110. Al electrodo de metal 110 también se le denomina electrodo de trabajo (ET). La celda también incluye un contraelectrodo/electrodo de referencia (CE/ER) 116, que es un sensor de potencial electroquímico.

En algunos modos de realización, una matriz de nanoporos permite una secuenciación paralela usando la técnica de secuenciación basada en nanoporos de molécula única mediante síntesis (nano-SBS). La figura 2 ilustra un modo de realización de una celda 200 que realiza la secuenciación de nucleótidos con la técnica nano-SBS. En la técnica nano-SBS, se introducen en la celda 200 un molde 202 que se va a secuenciar y un cebador. A este complejo molde-cebador, se añaden cuatro nucleótidos marcados de manera diferente 208 a la fase acuosa a granel. Cuando el nucleótido correctamente marcado forma un complejo con la polimerasa 204, la cola del marcador se sitúa en el cilindro del nanoporo 206. Después de que la polimerasa catalizó la incorporación del nucleótido correcto, el polifosfato unido al marcador contenido en el cilindro del nanoporo 206 genera una señal de bloqueo de corriente iónica única 210, identificando electrónicamente de este modo la base añadida debido a las distintas estructuras químicas de los marcadores.

La figura 3 ilustra un modo de realización de una célula que está a punto de realizar la secuenciación de nucleótidos con marcadores precargados. Se forma un nanoporo 301 en una membrana 302. Se asocia una enzima 303 (por ejemplo, una polimerasa, tal como una ADN polimerasa) con el nanoporo. En algunos casos, la polimerasa 303 se une covalentemente al nanoporo 301. La polimerasa 303 se asocia con una molécula de ácido nucleico monocatenario 304 para secuenciarse. En algunos modos de realización, la molécula de ácido nucleico monocatenario o bicatenario 304 es circular. En algunos casos, la molécula de ácido nucleico 304 es lineal. En algunos modos de realización, un cebador de ácido nucleico 305 se hibrida con una parte de la molécula de ácido nucleico 304. La polimerasa 303 cataliza la incorporación de nucleótidos 306 en el cebador 305 usando una molécula de ácido nucleico monocatenario 304 como molde. Los nucleótidos 306 comprenden especies marcadoras ("marcadores") 307.

La figura 4 ilustra un modo de realización de un procedimiento 400 para la secuenciación de ácidos nucleicos con marcadores precargados. La fase A ilustra los componentes como se describe en la figura 3. La fase C muestra el marcador cargado en el nanoporo. Un marcador "cargado" puede ser uno que se sitúa en y/o permanece en o cerca del nanoporo durante una cantidad de tiempo apreciable, por ejemplo, de 0,1 milisegundos (ms) a 1000 ms. En algunos casos, un marcador que está precargado se carga en el nanoporo antes de su liberación del nucleótido. En algunos casos, un marcador se precarga si la probabilidad de que el marcador pase a través de (y/o se detecte por) el nanoporo después de su liberación tras un acontecimiento de incorporación de nucleótidos es adecuadamente alta, por ejemplo, de un 90 % a un 99 %.

En la fase A, un nucleótido marcado (uno de cuatro tipos diferentes: A, T, G o C) no está asociado con la polimerasa. En la fase B, un nucleótido marcado se asocia con la polimerasa. En la fase C, la polimerasa se acopla al nanoporo. El marcador se introduce en el nanoporo durante el acoplamiento mediante una fuerza eléctrica, tal como una fuerza generada en presencia de un campo eléctrico generado por un voltaje aplicado a través de la membrana y/o el nanoporo.

Las bases de algunos de los nucleótidos marcados asociados se emparejan con la molécula de ácido nucleico monocatenario (por ejemplo, A con T y G con C). Sin embargo, las bases de algunos de los nucleótidos marcados asociados no se emparejan con la molécula de ácido nucleico monocatenario. Estos nucleótidos no emparejados típicamente son rechazados por la polimerasa dentro de una escala de tiempo que es más corta que la escala de tiempo durante la cual los nucleótidos emparejados correctamente permanecen asociados con la polimerasa. Como los nucleótidos no emparejados solo se asocian de forma transitoria con la polimerasa, el procedimiento 400 como se muestra en la figura 4 típicamente no avanza más allá de la fase D. Por ejemplo, la polimerasa rechaza un nucleótido no emparejado en la fase B o poco después de que el procedimiento entre en la fase C.

Antes de que la polimerasa se acople al nanoporo, la corriente que pasa a través del nanoporo es ~30 picoamperios (pA). En la fase C, la corriente que fluye a través del nanoporo es de aproximadamente 6 pA, 8 pA, 10 pA o 12 pA, correspondiendo cada amperaje a uno de los cuatro tipos de nucleótidos marcados. La polimerasa experimenta una isomerización y una reacción de transfosforilación para incorporar el nucleótido en la molécula de ácido nucleico en crecimiento y liberar la molécula marcadora. En la fase D, el marcador liberado pasa a través del nanoporo. El marcador se detecta por el nanoporo. En particular, cuando el marcador se mantiene en el nanoporo, se genera una señal de bloqueo de corriente iónica única (por ejemplo, véase la señal 210 en la figura 2) debido a las distintas estructuras químicas del marcador, identificando electrónicamente de este modo la base añadida. La repetición del ciclo (es decir, de la fase A a la E o de la fase A a la F) permite la secuenciación de la molécula de ácido nucleico.

En algunos casos, los nucleótidos marcados que no están incorporados en la molécula de ácido nucleico en crecimiento también pasarán a través del nanoporo, como se ve en la fase F de la figura 4. El nucleótido no incorporado se puede detectar en algunos casos por el nanoporo, pero el procedimiento proporciona un medio para distinguir entre un nucleótido incorporado y un nucleótido no incorporado, basado al menos en parte en el tiempo durante el cual el nucleótido se detecta en el nanoporo. Los marcadores unidos a nucleótidos no incorporados pasan a través del nanoporo rápidamente y se detectan durante un corto período de tiempo (por ejemplo, menos de 10 ms), mientras que los marcadores unidos a nucleótidos incorporados se cargan en el nanoporo y se detectan durante un largo período de tiempo (por ejemplo, al menos 10 ms).

En algunos modos de realización, la corriente iónica (por ejemplo, véase la señal 210 en la figura 2) se lee por el circuito de medición analógico 112 (véase la figura 1) en cada celda, se convierte en información digital y se transmite desde el chip. En algunos modos de realización, una matriz de puertas programable *in situ* (FPGA) o un circuito integrado específico de la aplicación (ASIC) recibe los datos transmitidos, procesa los datos y envía los datos a un ordenador. Sin embargo, cuando el chip de secuenciación basado en nanoporos se aumenta a escala para incluir más y más celdas, la tasa global de datos de transmisión hacia y desde el chip de secuenciación basado en nanoporos puede aumentar a una tasa inalcanzable. Por ejemplo, un chip de secuenciación basado en nanoporos con celdas de 128 k puede requerir dieciséis canales a un gigabit por segundo cada uno, mientras que un chip con un millón, diez millones o cien millones de celdas puede requerir 160 canales, 1600 canales o 16.000 canales a un gigabit por segundo por canal, respectivamente.

La tasa global de datos de transmisión del chip de secuenciación basado en nanoporos se puede reducir de varias maneras. En algunos modos de realización, se pueden usar técnicas de compresión digital para comprimir algunos de los datos en el chip de secuenciación basado en nanoporos y, a continuación, los datos comprimidos se pueden transmitir fuera del chip a una tasa de transmisión más baja. En algunos modos de realización, algunos de los datos se pueden procesar (por ejemplo, usando técnicas de lectura automática de nucleótidos) en el chip de secuenciación basado en nanoporos. Los datos procesados se pueden transmitir fuera del chip, por ejemplo, a un ordenador para su procesamiento adicional. De forma alternativa, los datos procesados se pueden usar por el chip de secuenciación basado en nanoporos para detectar acontecimientos y generar señales de control en respuesta a los acontecimientos detectados. Las señales de control generadas se pueden devolver a las celdas individuales o grupos de celdas como señales de control de entrada. Debido a que algunas de las detecciones y decisiones se hacen en el chip, se requiere transmitir menos datos fuera del chip para un procesamiento adicional y se pueden transmitir menos datos de control al chip, y también se puede reducir el tiempo de respuesta para generar los datos de control.

Como se muestra anteriormente, cuando el chip de secuenciación basado en nanoporos se aumenta a escala para incluir más celdas, el chip puede incluir diferentes tipos de componentes, por ejemplo, componentes analógicos, digitales y de memoria. Los diferentes tipos de componentes se pueden dividir en dos o más obleas que se apilan verticalmente para formar un chip de secuenciación basado en nanoporos de obleas apiladas. Por ejemplo, cada oblea apilada incluye un tipo diferente de componentes, por ejemplo, solo componentes analógicos y solo componentes digitales. Una ventaja de separar los componentes digitales y los componentes analógicos en

diferentes obleas es que elimina la necesidad de obleas de señal mixta en el chip, que son más caras que las obleas analógicas o las obleas digitales que se pueden diseñar individualmente con diferentes tipos de tecnologías, por ejemplo, tecnología de 180 nm para diseño analógico y tecnología de 28 nm para diseño digital.

La figura 5A ilustra un modo de realización de un chip de secuenciación basado en nanoporos de obleas apiladas 500 que incluye dos partes que se fabrican a partir de dos obleas separadas (502 y 504). En la figura 5A, la oblea superior 502 y la oblea inferior 504 se muestran como dos obleas separadas. La figura 5B ilustra la vista en sección transversal del chip de secuenciación basado en nanoporos de obleas apiladas 500. Como se muestra en la figura 5B, la oblea superior 502 se apila verticalmente encima de la oblea inferior 504.

10

30

35

- Con referencia a la figura 5A, la oblea superior 502 incluye una matriz de celdas de nanoporos 506. La matriz de celdas de nanoporos 506 puede incluir un gran número de celdas de sensores configuradas como una matriz. Por ejemplo, una matriz de un millón de celdas puede incluir 1000 filas por 1000 columnas de celdas.

- La oblea superior 502 incluye una matriz de celdas de nanoporos 506, que incluyen los circuitos de medición analógicos correspondientes de cada celda (por ejemplo, véanse circuitos de medición analógicos 112). En algunos modos de realización, los circuitos analógicos se pueden diseñar en tecnología de 180 nm. En algunos modos de realización, las señales analógicas de celdas individuales se envían desde las celdas a convertidores de señales analógicas a digitales (ADC) donde las señales analógicas se convierten en las señales digitales correspondientes. Las señales digitales se envían además a la periferia de la oblea superior 502 y se transmiten a través de una pluralidad de vías 508 (por ejemplo, vías a través de silicio (TSV)) a la periferia de la oblea inferior 504. Una vía es una conexión eléctrica entre capas en un circuito electrónico físico que atraviesa el plano de una o más capas adyacentes. En algunos modos de realización, una vía 508 puede tener un diámetro de 4 μm. La colocación de las vías a lo largo de la periferia de la oblea superior y la oblea inferior también se denomina apilamiento periférico.

- La oblea inferior 504 incluye circuitos lógicos digitales. En algunos modos de realización, los circuitos digitales se pueden diseñar en tecnología de 28 nm. En algunos modos de realización, algunas de las señales transmitidas desde la oblea superior 502 se pueden transmitir fuera del chip de secuenciación basado en nanoporos 500 a través de una pluralidad de almohadillas de entrada/salida (I/O) 510 sin procesamiento adicional por la oblea inferior 504. Algunas de las señales transmitidas desde la oblea superior 502 se pueden procesar adicionalmente o comprimir mediante una lógica situada en la oblea inferior 504. Los datos procesados se transmiten a continuación fuera del chip de secuenciación basado en nanoporos 500, por ejemplo, a un ordenador o una pieza de hardware, para su procesamiento adicional. De forma alternativa, los datos procesados se pueden usar por el chip de secuenciación basado en nanoporos 500 para detectar acontecimientos y generar señales de control en respuesta a los acontecimientos detectados. Las señales de control generadas se pueden enviar a través de una pluralidad de vías 508 a la oblea superior 502 y, a continuación, se pueden devolver a las celdas individuales o grupos de celdas como señales de control de entrada. Las señales se pueden transmitir desde un ordenador o una fuente fuera del chip de secuenciación basado en nanoporos 500 a la oblea inferior 504 a través de las almohadillas de I/O 510. Estas señales se pueden usar como señales de entrada o de control para controlar cualquier lógica o circuito en la oblea superior 502 o la oblea inferior 504. Para el primer caso, las señales se dirigen a través de las vías 508 a la oblea superior 502 y, a continuación, se envían a regiones específicas, celdas específicas o grupos específicos de celdas.

- 45 En algunos modos de realización, cada ADC se puede dividir en dos partes: una parte del ADC se sitúa en la oblea superior 502 y la parte restante del ADC se sitúa en la oblea inferior 504.

- Con referencia a la figura 5B, la oblea superior 502 se apila verticalmente encima de la oblea inferior 504, con una capa de óxido 524 que une las dos obleas juntas. En algunos modos de realización, la oblea superior 502 y la oblea inferior 504 incluyen cada una una pluralidad de capas metálicas, M1 (512) a M6 (514) y una capa de óxido de silicio (516 y 522). Las vías 508 proporciona una conexión eléctrica entre las capas metálicas. Las señales se transmiten entre la oblea superior 502 y la oblea inferior 504 a través de las vías 508. En algunos modos de realización, las vías 508 están llenas de volframio.

- La figura 6 ilustra un modo de realización de un chip de secuenciación basado en nanoporos de obleas apiladas 600 que incluye dos obleas separadas, una oblea superior 602 y una oblea inferior 604. La oblea superior 602 incluye una matriz de celdas de nanoporos 606. En este modo de realización, las vías 608 se colocan en la periferia de las obleas. La oblea inferior 604 incluye almohadillas de I/O 610.

- Las señales se pueden transmitir desde un ordenador o una fuente fuera del chip de secuenciación basado en nanoporos 600 a la oblea inferior 604 a través de las almohadillas de I/O 610. Estas señales se pueden usar como señales de entrada o de control para controlar cualquier lógica o circuito en la oblea superior 602 o la oblea inferior 604. Ejemplos de este tipo de señales incluyen señales de potencia y tierra. Las señales de potencia y tierra se dirigen a través de las vías 608 a la oblea superior 602 y, a continuación, se envían a regiones específicas, celdas específicas o grupos específicos de celdas.

Algunas señales que se transmiten a través de las vías 608 incluyen señales de salida desde la matriz de celdas de nanoporos 606. Las señales analógicas desde celdas individuales se envían desde las celdas a convertidores de señales analógicas a digitales (ADC) 612 donde las señales analógicas se convierten en las señales digitales correspondientes. Las señales digitales se envían además a la periferia de la oblea superior 602 y se transmiten a través de una pluralidad de vías 608 a la periferia de la oblea inferior 604. Las señales digitales se pueden recibir y guardar por una memoria intermedia de trama 624. Algunas de las señales digitales se pueden enviar además a diferentes módulos (por ejemplo, compresor 626 y módulo de señalización diferencial de bajo voltaje (LVDS) 628) para un procesamiento adicional.

- En algunos modos de realización, cada ADC 612 se comparte entre diferentes filas 614 y/o diferentes columnas 616 de celdas en la matriz de celdas de nanoporos 616. El controlador de fila y columna 622 en la oblea inferior 604 envía información de control a los controladores de fila y columna (618 y 620), que a su vez controlan las señales de salida correspondientes a diferentes filas y columnas de las celdas de nanoporos en la matriz de celdas de nanoporos 606 en sus correspondientes ADC 612.

- Algunas señales que se transmiten a través de las vías 608 incluyen señales que se envían a una celda de nanoporos específica como señales de entrada o señales de control que controlan la celda individual. Las señales de entrada o control se pueden generar por módulos en la oblea inferior 604 en respuesta a determinados acontecimientos detectados. Las señales de entrada o de control se pueden generar por un ordenador o una pieza de hardware fuera del chip de secuenciación basado en nanoporos 600 en respuesta a determinados acontecimientos detectados. Los ejemplos de estos tipos de señales incluyen señales conocidas como seta, setb, VA, VB, selección de fila y reajuste, como se describirá con mayor detalle a continuación (véase, por ejemplo, la figura 7B, la figura 11 y la figura 12).

- En algunos modos de realización, la matriz de nanoporos se divide en bancos de celdas. La figura 7A ilustra un modo de realización de un banco de celdas M x N. Las líneas de selección de fila y selección de columna se usan para controlar los estados de las celdas individuales. M y N pueden ser cualquier número entero. Por ejemplo, un banco que tiene un tamaño de 8 k (denominado bank8k) puede incluir 64 × 128 celdas.

- 30 La figura 7B ilustra un modo de realización de un bloque bank8k. El bloque de construcción bank8k se puede configurar como 64 filas por 128 columnas, como se muestra en la figura 7B. Cada bloque bank8k puede ser un subsistema completo con lógica de direccionamiento de fila y columna para lectura/escaneo, descodificadores de dirección de escritura, convertidores de señales analógicas a digitales (ADC) y salida con doble memoria intermedia.

- Puesto que cada banco es autónomo, la matriz de nanoporos se puede aumentar a escala añadiendo bancos adicionales. Por ejemplo, una matriz de 128 k se puede implementar como dieciséis elementos de bank8k. Una matriz de 512 k se puede implementar como una matriz de 8×8 de elementos de bank8k. En algunos modos de realización, la matriz de nanoporos se puede aumentar a escala para incluir millones de celdas. Se puede usar un pequeño bloque de control global para generar señales de control para seleccionar los bancos y establecer el voltaje aplicado a la celda.

- En algunos modos de realización, la ruta de lectura y la ruta de escritura del bloque bank8k están separadas y funcionan de forma multiplexada en el tiempo. Por ejemplo, una lectura va seguida de una escritura. Cada fila se escanea realizando una conversión de señal analógica a digital de todas las celdas de la fila. Posteriormente, el programa informático puede escribir opcionalmente un valor en cualquier celda en la misma fila para actualizar el estado, seleccionando de este modo entre dos voltajes aplicados diferentes.

- Cada bloque bank8k incorpora treinta y dos ADC 702 con cada ADC 702 conectado a 4 columnas. Un contador de columnas (colcnt) 704 genera un bus de selección de columnas de 4 bits (csel) 706. El bus csel 706 controla 32 multiplexores analógicos 4:1 separados 708 y selecciona cuál de las 4 columnas se conecta eléctricamente a los ADC 702. Téngase en cuenta que las celdas secuenciales leídas de una fila dada se sitúan físicamente como col0, col4, ... col1, col5, ..., y así sucesivamente. Los datos se distribuyen en líneas a través de la matriz con 16 bits. De forma similar, los datos de 16 bits se escriben en las celdas como:

```

d[0:7] \rightarrow \{col0, col16, ..., col112\}

d[8:15] \rightarrow \{col1, col17, ..., col113\}

```

5

15

35

40

45

65

60 En el modo de escaneo, todos los bancos que están habilitados se leen en paralelo.

En algunos modos de realización, el escaneo de una fila requiere leer 16 columnas, y cada columna requiere 16 ciclos de reloj. Por tanto, todas las celdas en una fila se leen en 256 relojes, o 2 µs a una frecuencia de reloj de 128 MHz. El período de precarga se produce inmediatamente después de que se haya escaneado una fila y dura 2 µs.

El bank8k es completamente síncrono con todas las señales capturadas en el borde ascendente de los relojes, incluyendo ast 710, wr 712 y el bus de datos de dirección multiplexado 714 (ad[15:0]). Durante el primer ciclo de reloj, ad[15:0] se controla con la dirección de escritura que se captura por el retenedor de dirección 716 (alat) en el borde ascendente del reloj cuando la señal estroboscópica de dirección 710 (ast) está alta. Se descodifican siete bits de dirección retenida (la) 718 para determinar en qué banco y datos textuales se escriben. Durante el segundo ciclo de reloj, ad[15:0] se debe controlar con los datos y la señal wr 712 se debe declarar alta para indicar que se trata de un ciclo de escritura de datos. Por tanto, una escritura normal requiere dos ciclos: el ciclo de dirección (indicado por la señal ast 710), seguido del ciclo de datos (indicado por la señal wr 712).

- 10 Existen tres tipos de escrituras:

- Escritura de registro de activar banco

- Escritura de registro de control

- Escritura de selección de celda A/B de banco

Algunos de los bits de la dirección retenida 718, la[8:7], se usan para determinar el tipo de escritura, como se muestra en la tabla 1 a continuación:

Tabla 1

15

20

35

55

| la[8:7] | Tipo de escritura         |  |  |  |

|---------|---------------------------|--|--|--|

| 00      | Selección de celda A/B    |  |  |  |

| 01      | Registro de activar banco |  |  |  |

| 10      | Registro de control       |  |  |  |

La lógica de registro de desplazamiento de selección de fila (rs) 720 y el contador de columna 704 (colcnt) funcionan juntos para realizar un escaneo de trama de todas las celdas en el bloque bank8k. Después de un período completo de integración, se lee una fila declarando que la señal de selección de fila 722 (rs) es alta. Juntas, la selección de fila 722 y la selección de columna 704 permiten que una sola celda controle una columna dada. Ocho columnas dentro de una fila se leen en paralelo, cada una conectada a un ADC diferente. Una celda seleccionada controla el voltaje en un condensador de integración en la línea de columna usando un amplificador seguidor de fuente en la celda.

La lógica de selección de fila es un registro de desplazamiento de 64 bits (registro sr64 720) duplicado dentro de cada bloque bank8k. Después de haber leído todas las columnas en una fila, una FPGA (matriz de puertas programable *in situ*) externa puede declarar la señal nxtrow 724, lo que hace que el registro sr64 720 se desplace. Una vez que se ha escaneado el campo de subventanas completo, la FPGA externa declara la nxtscan 726, que reajusta el registro sr64 720 a la fila cero desplazando 1 bit al primer biestable. Al cambiar el período y la duración de la señal nxtrow 724 y nxtscan 726, la matriz que se está escaneando puede funcionar en modo de ventana, como se describirá con mayor detalle a continuación.

- 40 La precarga se produce fila a fila. Una fila entra en el modo de precarga inmediatamente después de que una columna se haya muestreado por los ADC. Cada fila tiene un biestable que muestrea la señal row\_enable cuando se declara la señal nxtrow 724.

- Además, el registro de desplazamiento de selección de fila 720 también se usa para generar la señal de precarga de fila conectando la enésima señal de precarga a la señal de selección de fila (n+1):

Pre[n] = rs[n+1]

Se precarga una fila durante el período de escaneo de fila inmediatamente después de haberla leído. Esta conexión de precarga desplazada de bit se implementa como una operación de módulo 64, y por tanto la precarga[63] se conecta lógicamente a rs[0].

La figura 8 ilustra un modo de realización de una secuencia de escaneo. Después de que se hayan leído las 64 filas (junto con cualquier escritura intermedia), se declara la señal nxtscan para reiniciar el procedimiento de escaneo en la fila 0.

La figura 9 ilustra un modo de realización de una secuencia de escaneo. El muestreo doble correlacionado (CDS) se habilita declarando un pin de CDS. En un modo de medición normal sin CDS, se mide el voltaje en el condensador y, posteriormente, se declara el pin nxtrow para que se pueda leer la siguiente fila. Se precarga la

fila N mientras se lee la fila N+1. Por tanto, una fila se reajusta inmediatamente después de que se haya leído. La declaración del pin de CDS permite leer la fila que se acaba de precargar. Por tanto, el valor del voltaje reajustado se puede leer inmediatamente después de que se realiza la precarga y, posteriormente, leer de nuevo más tarde. Restando las dos mediciones, se reduce el ruido térmico kT/C del transistor de precarga 1114. Además, también se reducen los efectos del divisor de voltaje de carga compartida entre la capacitancia del integrador y el seguidor activo en la celda. Téngase en cuenta que, cuando se realiza un muestreo doble correlacionado, la tasa de medición efectiva se reduce a la mitad, puesto que se requieren dos conversiones de ADC para cada medición de corriente integrada.

- Las direcciones de fila y columna están controladas por las señales nxtrow 724 y nxtscan 726. La declaración de que la entrada nxtrow 724 es alta hace que la dirección de columna y el registro de desplazamiento se reajusten a 0 y la dirección de fila se desplace en uno. La declaración de que la entrada nxtscan 726 es alta hace que las direcciones de fila y columna se reajusten a 0.

- 15 En un funcionamiento normal, se escanea la matriz completa de celdas de 8 K dentro de cada banco. El ADC requiere 16 ciclos de reloj para realizar una conversión, y 16 de dichas conversiones se realizan para convertir una fila completa. Por tanto, cada fila requiere 256 ciclos de reloj (2,0 µs a 128 MHz).

- Por tanto, para escanear la matriz completa de celdas de 8 K, la señal nxtrow 724 se declara cada 256 ciclos y la señal nxtscan 726 se declara durante un ciclo en cada 16.384 ciclos. El uso de un reloj típico que funciona a 128 MHz produce una frecuencia de muestreo de 7,8 kHz (período de 128 μs). Sin embargo, es posible compensar el número de celdas escaneadas para una mayor frecuencia de escaneo escaneando un subconjunto de la matriz. Por ejemplo, la cuarta parte superior de las filas de la matriz se puede escanear declarando la señal nxtscan 726 después de 2048 relojes, como se muestra en la figura 10. La frecuencia de muestreo se incrementa cuatro veces, de ~8 kHz a ~32 kHz. Sin embargo, el tiempo de integración y la señal de voltaje también se reducen en 4 veces, lo que causa una degradación de la relación señal-ruido (SNR).

- En el ejemplo anterior, se escanea una cuarta parte de la matriz. Sin embargo, se puede escanear una fracción más grande o más pequeña cada vez. Por ejemplo, se pueden escanear 1/2 o 1/3 de las filas de la matriz completa cada vez.

30

35

50

- En el ejemplo anterior, tres cuartas partes de la matriz se dejan sin escanear. En algunos modos de realización, la matriz completa se escanea en múltiples pases. El primer pase es como se describe anteriormente. El segundo pase deja la señal nxtrow 724 declarada durante 16 ciclos de reloj consecutivos para circunvalar las primeras 16 filas y comenzar un nuevo escaneo en la 17.ª. El escaneo de la siguiente cuarta parte de la matriz se realiza a continuación normalmente antes de declarar el nxtscan 726 para reajustar los registros de desplazamiento de escaneo. La tercera cuarta parte salta 32 filas y comienza a escanear en la 33.ª para escanear las últimas 16 filas.

- Por tanto, mediante intercalado temporal, la matriz completa se escanea a una frecuencia mucho mayor que la normal. La frecuencia de muestreo real no mejora, ya que el tiempo requerido para escanear las cuatro cuartas partes de la matriz no varía. Existen, efectivamente, "tiempos muertos" insertados entre cada uno de los escaneos de los cuartiles. En algunos casos, la corriente es tal que la medición del voltaje se satura a la frecuencia de escaneo normal de 8 kHz. Por tanto, intercalando temporalmente escaneos más rápidos, las lecturas de estas celdas de corriente alta en la matriz se obtienen sin saturación. El programa informático se debe percatar de la señal de precarga y realizar un escaneo doble de la región deseada.

- En cada celda, la corriente se mide a diferentes voltajes aplicados. La celda incluye circuitos para aplicar un voltaje constante (voltaje de CC) o una forma de onda de voltaje alterno (voltaje de CA) al electrodo y medir simultáneamente una corriente de bajo nivel.

- En algunos modos de realización, se aplica un potencial de voltaje al líquido contenido dentro de un cilindro conductor montado en la superficie del troquel. Este potencial "líquido" se aplica al lado superior del poro y es común a todas las celdas de la matriz. El lado inferior del poro tiene un electrodo expuesto, y cada celda del sensor puede aplicar un potencial de lado inferior distinto a su electrodo. La corriente se mide entre la conexión de líquido superior y la conexión de electrodo de cada celda en el lado inferior del poro. La celda del sensor mide la corriente que viaja a través del poro según la modulación por el complejo molecular constreñido dentro del poro.

- La figura 11 ilustra un modo de realización de un circuito analógico para medir la corriente en una celda. El circuito está conectado eléctricamente a un electrodo electroquímicamente activo (por ejemplo, AgCl) a través de un nodo de detección de electrodo (ELSNS) 1102. El circuito incluye un transistor 1104. El transistor 1104 puede ser un NMOS o MOSFET (transistor de efecto de campo de semiconductor de óxido metálico) de n canales que realiza dos funciones. Se puede aplicar un potencial de voltaje controlado al nodo ELSNS 1102, y el potencial de voltaje controlado se puede variar cambiando el voltaje en la entrada a un amplificador operacional 1108 que controla el transistor 1104, que actúa como un seguidor de fuente. El transistor 1104 también funciona como un transportador de corriente para mover electrones desde un condensador 1106 hasta el nodo ELSNS 1102 (y viceversa). La corriente desde el pin fuente del transistor 1104 se propaga directamente y con exactitud a su pin de drenaje,

acumulando cargas en el condensador 1106. Por tanto, el transistor 1104 y el condensador 1106 actúan juntos como un integrador ultra compacto (UCI).

El UCI se usa para determinar la corriente que procede del electrodo o que se sume en el mismo, midiendo el cambio de voltaje integrado en el condensador 1106 de acuerdo con lo siguiente:

$I^*t = C^*\Delta V$  donde I: corriente

t: tiempo de integración

C: capacitancia

10

30

35

40

45

50

55

60

ΔV: cambio de voltaje

15 El funcionamiento típico implica precargar el condensador 1106 a un valor conocido y fijo (por ejemplo, VDD = 1,8 V) y a continuación medir el cambio de voltaje en un intervalo fijo t. Para un banco de 8 K que funciona a 128 MHz, cada celda se integra durante ~128 μs. En un ejemplo:

C = 5 fF

20 I = 20 pA

$t = 128 \, \mu s$

$\Delta V = I*t/C$

= 20 pA\*128 µs/5 fF

= 512 mV

En este ejemplo, la resolución del ADC es del orden de milivoltios. El voltaje integrado se puede incrementar reduciendo la frecuencia de reloj a menos de 128 MHz, incrementando de este modo el período de integración.

En el circuito anterior, la oscilación máxima de voltaje es de ~1 V, y por tanto el circuito se satura con una corriente superior a ~32 pA. El límite de saturación se puede incrementar reduciendo la ventana de escaneo para incrementar eficazmente la frecuencia de escaneo de la celda. Intercalando escaneos rápidos y lentos, se puede incrementar el intervalo dinámico de la corriente que se puede medir.

El transistor 1104 actúa como un transportador de corriente moviendo las cargas desde el condensador de integración 1106 al electrodo. El transistor 1104 también actúa como una fuente de voltaje, imponiendo un voltaje constante en el electrodo a través del bucle de retroalimentación del amplificador operacional. El transistor de control de columna 1110 se configura como un seguidor de fuente para amortiguar el voltaje del condensador y proporcionar una representación de baja impedancia del voltaje integrado. Esto evita que la carga compartida cambie el voltaje en el condensador.

El transistor 1112 es un transistor conectado a la señal de selección de fila (rs). Se usa como un dispositivo de acceso de fila con la salida de voltaje analógica en su fuente conectada como una columna compartida con muchas otras celdas. Solo se habilita una única fila de la señal AOUT conectada a la columna para que se mida un único voltaje de celda.

En un modo de realización alternativo, el transistor de selección de fila (transistor 1112) se puede omitir conectando el drenaje del transistor de control de columna 1110 a un "riel conmutado" seleccionable de fila.

Se usa un transistor de precarga 1114 para reajustar la celda a un voltaje de inicio predeterminado a partir del cual se integra el voltaje. Por ejemplo, la aplicación de un voltaje alto (por ejemplo, VDD = 1,8 V) a tanto vpre como pre elevará el condensador 1106 hasta un valor precargado de (VDD - Vt). El valor de inicio exacto puede variar de una celda a otra (debido a la variación de Vt del transistor de precarga 1114), así como de una medición a otra, debido al ruido térmico del conmutador de reajuste (ruido sqrt(kTC)). Es posible eliminar esta variación de Vt limitando el voltaje de precarga a menos de VDD-Vt. En este caso, el transistor de precarga 1114 se elevará todo el camino hasta el voltaje vpre. Incluso en este caso, sin embargo, el ruido kT/C todavía está presente. Como resultado, se usa una técnica de muestreo doble correlacionado (CDS) para medir el voltaje de inicio del integrador y el voltaje final para determinar el cambio de voltaje real durante el período de integración. El CDS se logra midiendo el voltaje en el condensador de integración 1106 dos veces: una vez al principio y una vez al final del ciclo de medición.

Téngase en cuenta también que el drenaje del transistor de precarga 1114 está conectado a un voltaje controlado vpre (voltaje de reajuste). En un funcionamiento normal, vpre se conduce a un voltaje fijo por encima del voltaje del electrodo. Sin embargo, también se puede conducir a un voltaje bajo. Si el nodo vpre del transistor de precarga 1114 se conduce, de hecho, a tierra, entonces el flujo de corriente se invierte (es decir, la corriente fluye desde el electrodo al circuito a través del transistor 1104 y el transistor de precarga 1114), y la noción de fuente y drenaje se intercambia. El voltaje negativo aplicado al electrodo (con respecto a la referencia del líquido) se controla mediante el voltaje vpre, suponiendo que los voltajes de compuerta de los transistores 1114 y 1104 son al menos mayores que vpre en un umbral. Por tanto, se puede usar un voltaje de tierra en vpre para aplicar un voltaje negativo al electrodo, por ejemplo, para lograr la electroporación o la formación de bicapa.

10

15

5

Un ADC mide el voltaje AOUT inmediatamente después del reajuste y nuevamente después del período de integración (es decir, realiza la medición del CDS) para determinar la corriente integrada durante un período de tiempo fijo. Se puede implementar un ADC por columna. Se puede usar un transistor separado para cada columna como un multiplexor analógico para compartir un único ADC entre múltiples columnas. El factor de multiplexor de columna se puede variar dependiendo de los requisitos de ruido, exactitud y rendimiento.

En algunos modos de realización alternativos, la combinación de amplificador operacional/transistor como se muestra en la figura 11 se puede reemplazar por un único transistor como se muestra en la figura 12.

20

En algunos modos de realización, las vías se pueden colocar dentro de una celda o dentro de un grupo de celdas. La colocación de una vía dentro de una celda o dentro de un grupo de celdas se denomina apilamiento a nivel de celda. El apilamiento a nivel de celda se puede usar cuando una vía tiene un área de sección transversal que es pequeña con respecto a la celda o grupos de celdas en los que se coloca la vía. Por ejemplo, una vía usada en el apilamiento a nivel de celda puede tener un diámetro de 1 µm.

25

En la figura 5A, la figura 5B y la figura 6, cada uno de los chips de secuenciación basados en nanoporos de obleas apiladas (500 y 600) tiene dos obleas. Sin embargo, en algunos otros modos de realización, un chip de secuenciación basado en nanoporos de obleas apiladas puede tener dos o más obleas que se apilan verticalmente

30

En un modo de realización, un chip de secuenciación basado en nanoporos de obleas apiladas incluye tres obleas. Los componentes de memoria y los componentes lógicos se sitúan en la oblea inferior. La matriz de celdas se divide entre las obleas superior e intermedia; por ejemplo, los circuitos de medición analógicos 112 (véase la figura 1) de la celda 100 se colocan en la oblea intermedia, mientras que los componentes restantes de la celda 100 se colocan en la oblea superior.

35

En un modo de realización, un chip de secuenciación basado en nanoporos de obleas apiladas incluye tres obleas.

La oblea superior incluye la matriz de celdas y los componentes analógicos. Una oblea intermedia incluye los componentes de memoria. Una oblea inferior incluye los componentes lógicos. En este modo de realización, los 40 componentes de memoria y los componentes lógicos se sitúan en obleas separadas, de modo que cada oblea se puede diseñar usando diferentes tipos de tecnologías. El apilamiento a nivel de celda se puede usar de modo que una vía entregue señales entre obleas. Supóngase que una señal de salida analógica de una celda se deba comparar con un valor, y se deba tomar una decisión basada en la comparación. La señal de salida analógica se envía a un comparador situado en la oblea superior. Una vía entrega al comparador un valor almacenado en un 45 componente de memoria correspondiente a la celda, de modo que se puede hacer una comparación de la señal de salida analógica y el valor almacenado. El resultado de la comparación se puede entregar además por una vía a los componentes lógicos situados en la oblea inferior, donde se puede tomar una decisión. En algunos modos de realización, un componente lógico se puede compartir por múltiples celdas. Por ejemplo, los resultados de la

50

comparación de cuatro celdas diferentes se pueden entregar por una única vía al componente lógico compartido, donde se hacen detecciones/toman decisiones.

Aunque los modos de realización anteriores se han descrito con cierto detalle para propósitos de claridad de comprensión, la invención no se limita a los detalles proporcionados. Existen muchas formas alternativas de implementar la invención. Los modos de realización divulgados son ilustrativos y no restrictivos.

#### REIVINDICACIONES

- 1. Un chip de secuenciación basado en nanoporos (500; 600), que comprende:

- 5 una primera parte fabricada a partir de una primera oblea (502; 602), comprendiendo la primera parte:

una matriz de celdas de nanoporos (506; 606);

un circuito de medición conectado a una o más celdas de nanoporos, produciendo el circuito de medición una señal de medición de salida; y

#### caracterizado por

15

35

50

55

una o más vías (508; 608) adaptadas para transmitir la señal de medición de salida; y

una segunda parte fabricada a partir de una segunda oblea (504; 604), comprendiendo la segunda parte:

una o más vías correspondientes (508; 608) adaptadas para recibir la señal de medición de salida.

- 20 2. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que la primera parte fabricada a partir de la primera oblea (502; 602) y la segunda parte fabricada a partir de la segunda oblea (504; 604) se apilan verticalmente una encima de la otra.

- 3. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602) y la una o más vías correspondientes (508; 608) en la segunda parte fabricada a partir de la segunda oblea (504; 604) están situadas en la periferia del chip de secuenciación basado en nanoporos (500; 600).

- 4. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602) están situadas dentro de una única celda de nanoporos.

- 5. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602) están situadas dentro de un grupo de celdas de nanoporos que comparten uno o más componentes situados en la segunda parte fabricada a partir de la segunda oblea (504; 604), y en el que la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602) transmiten la señal de medición de salida al uno o más componentes compartidos en la segunda parte fabricada a partir de la segunda oblea (504; 604).

- 40 6. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que cada parte incluye uno de los siguientes tipos de componentes: componentes analógicos, componentes lógicos y componentes de memoria.

- 7. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que la segunda parte fabricada a partir de la segunda oblea (504; 604) comprende además un módulo (626) que comprime la señal de medición de salida.

- 8. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que la segunda parte fabricada a partir de la segunda oblea (504; 604) comprende además un módulo que detecta un acontecimiento basado al menos en parte en la señal de medición de salida recibida.

- 9. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que la segunda parte fabricada a partir de la segunda oblea (504; 604) comprende además un módulo (622) que genera una señal de control, y en el que la segunda parte fabricada a partir de la segunda oblea (504; 604) comprende además una o más vías (508; 608) para transmitir la señal de control, y en el que la primera parte fabricada a partir de la primera oblea (502; 602) comprende además una o más vías (508; 608) para recibir la señal de control, y en el que la primera parte fabricada a partir de la primera oblea (502; 602) comprende además circuitos que envían la señal de control a una celda de nanoporos individual para controlar la celda de nanoporos individual.

- 60 10. El chip de secuenciación basado en nanoporos (500; 600) de la reivindicación 1, en el que la primera parte fabricada a partir de la primera oblea (502; 602) comprende además un convertidor de señal analógica a digital (ADC) que convierte la señal de medición de salida a una versión digital de la señal de medición de salida antes de la transmisión de la versión digital de la señal de medición de salida por la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602).

- 11. Un procedimiento para realizar la secuenciación de nucleótidos mediante un chip de secuenciación basado en nanoporos (500; 600), que comprende:

- dividir el chip de secuenciación basado en nanoporos (500; 600) en una primera parte fabricada a partir de una primera oblea (502; 602), comprendiendo la primera parte:

una matriz de celdas de nanoporos (506; 606);

un circuito de medición conectado a una o más celdas de nanoporos, produciendo el circuito de medición una señal para medir la salida; y

#### caracterizado por

15

20

25

30

40

una o más vías (508; 608) que transmiten la señal de medición de salida; y

dividir el chip de secuenciación basado en nanoporos (500; 600) en una segunda parte fabricada a partir de una segunda oblea (504; 604), comprendiendo la segunda parte:

una o más vías correspondientes (508; 608) que reciben la señal de medición de salida.

12. El procedimiento de la reivindicación 11, que comprende además:

apilar la primera parte fabricada a partir de la primera oblea (502; 602) y la segunda parte fabricada a partir de la segunda oblea (504; 604) verticalmente una encima de la otra.

13. El procedimiento de la reivindicación 11,

- a) en el que la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602) y la una o más vías correspondientes (508; 608) en la segunda parte fabricada a partir de la segunda oblea (504; 604) están situadas en la periferia del chip de secuenciación basado en nanoporos (500; 600); O

- b) en el que la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602) están situadas dentro de una única celda de nanoporos; O

- c) en el que la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602) están situadas dentro de un grupo de celdas de nanoporos que comparten uno o más componentes situados en la segunda parte fabricada a partir de la segunda oblea (504; 604), y en el que la una o más vías (508; 608) en la primera parte de la primera oblea (502; 602) transmiten la señal de medición de salida al uno o más componentes compartidos en la segunda parte fabricada a partir de la segunda oblea (504; 604); O

- d) en el que cada parte incluye uno de los siguientes tipos de componentes: componentes analógicos, componentes lógicos y componentes de memoria; O

- e) en el que la segunda parte fabricada a partir de la segunda oblea (504; 604) comprende además un módulo (626) que comprime la señal de medición de salida; O

- f) en el que la segunda parte fabricada a partir de la segunda oblea (504; 604) comprende además un módulo que detecta un acontecimiento basado al menos en parte en la señal de medición de salida recibida; O

- g) en el que la segunda parte fabricada a partir de la segunda oblea (504; 604) comprende además un módulo (622) que genera una señal de control, y en el que la segunda parte fabricada a partir de la segunda oblea (504; 604) comprende además una o más vías (508; 608) para transmitir la señal de control, y en el que la primera parte fabricada a partir de la primera oblea (502; 602) comprende además una o más vías (508; 608) para recibir la señal de control, y en el que la primera parte fabricada a partir de la primera oblea (502; 602) comprende además circuitos que envían la señal de control a una celda de nanoporos individual para controlar la celda de nanoporos individual; O

- h) en el que la primera parte fabricada a partir de la primera oblea (502; 602) comprende además un convertidor de señal analógica a digital (ADC) que convierte la señal de medición de salida a una versión digital de la señal de medición de salida antes de la transmisión de la versión digital de la señal de medición de salida por la una o más vías (508; 608) en la primera parte fabricada a partir de la primera oblea (502; 602).

FIG. 1

FIG. 2

FIG. 5A

FIG. 6

FIG 7R

FIG. 8

| []         | <br>       |            |            |        |                    |            |                                                      |

|------------|------------|------------|------------|--------|--------------------|------------|------------------------------------------------------|

| Integrando | Lear       | Integrar   | Integrando | • • •  | Integrando         | Integrando | Después de<br>la precarga,<br>leer fila 1<br>(cds=1) |

| Integrando | Precarga   | [sei       | Integrando | • • •  | Integrando         | Integrando | Leer fila 2<br>(cds=0)                               |

|            |            |            |            | nxtrow |                    |            |                                                      |

| aud Jajo   | Integrando | Integrando | Integrando | • • •  | Integrando         | Integrando | Después de<br>la precarga,<br>leer fila 0<br>(cds=1) |

| Precarga   |            | Integrando | Integrando |        | Fila 62 Integrando | Integrando | Leer fila 1<br>(cds=0)                               |

| Fila 0     | Fila 1     | Fila 2     | Fila 3     |        | Fila 62            | Fila 63    |                                                      |

FIG. 9