# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 734 279

51 Int. Cl.:

H01L 27/24 (2006.01) H01L 45/00 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(96) Fecha de presentación y número de la solicitud europea: 26.02.2016 E 16157505 (5)

(97) Fecha y número de publicación de la concesión europea: 24.04.2019 EP 3101689

(54) Título: Memoria de acceso aleatorio resistivo

(30) Prioridad:

01.06.2015 US 201514726626

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **05.12.2019**

(73) Titular/es:

WINBOND ELECTRONICS CORP. (100.0%) No. 8 Keya 1st Rd., Daya District, Central Taiwan Science Park Taichung City, Taiwan, TW

(72) Inventor/es:

CHEN, FREDERICK; WANG, PING-KUN y LIAO, SHAO-CHING

(74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

# **DESCRIPCIÓN**

Memoria de acceso aleatorio resistivo

#### Antecedentes de la invención

#### 1. Campo de la invención

10

5 La descripción se refiere a una memoria no volátil y, en particular, a una memoria de acceso aleatorio resistiva (RRAM).

# 2. Descripción de la técnica relacionada

Una memoria de acceso aleatorio resistiva (RRAM) es un tipo de memoria no volátil. Debido a las numerosas ventajas de la RRAM, que incluyen una estructura simple, bajo voltaje de operación, rápido tiempo de operación, almacenamiento de múltiples bits, bajo coste, buena durabilidad, actualmente son ampliamente estudiadas. La estructura básica de la RRAM comúnmente utilizada está compuesta por un transistor y una resistencia (1T1R), o un diodo y una resistencia (1D1R). El valor de resistencia de la resistencia se cambia variando la polarización aplicada, de modo que el dispositivo se encuentre en un estado de alta resistencia o en un estado de baja resistencia y, por lo tanto, se reconozca 0 o 1 de la señal digital.

- Sin embargo, la temperatura del medio ambiente donde se encuentra la RRAM es mayor, el valor de resistencia de la misma en el estado de alta resistencia es más baja y el valor de resistencia de la misma en el estado de baja resistencia es mayor, por lo tanto, puede ser causado error de juicio de 0 o 1 de la señal digital del dispositivo. Por lo tanto, el problema para superar la dificultad de reconocer la señal digital del dispositivo de RRAM en un entorno de alta temperatura se convierte en la principal tarea de estudio en la tecnología y el desarrollo actuales de RRAM.

- Los dispositivos de RRAM con estructura 1TnR de acuerdo con el preámbulo de las reivindicaciones independientes se conocen por Yeh et al, IEEE Journal of Solid-State Circuits, vol. 50, n.º 5, mayo de 2015, páginas 1299-1309, los documentos US 2008/170428 A1, US 2008/043522 A1, y WO 2005/066969 A1, por ejemplo. Los documentos US 2013/028003 A1 y US 2014/124725 A1 revelan dispositivos de RRAM con una capa limitadora de corriente entre la capa de cambio de resistencia y el electrodo superior.

## 25 Sumario de la invención

La descripción proporciona una memoria de acceso aleatorio resistiva (RRAM) (es decir, la estructura 1TnR, n es un entero de más de 1), que puede resolver el problema de la dificultad en el reconocimiento de la señal de 0 y 1 por la corriente en ambiente de alta temperatura, también guarda el área ocupada del sustrato y aumenta el nivel de integración del dispositivo.

La RRAM de la presente invención incluye un sustrato, un transistor, un electrodo inferior, una pluralidad de electrodos superiores, al menos una capa de conmutación de resistencia y al menos una corriente de capa limitante de acuerdo con las reivindicaciones independientes 1 y 2. El transistor está dispuesto sobre el sustrato. El electrodo inferior está dispuesto sobre el sustrato y conectado eléctricamente a una fuente/drenaje del transistor. Los electrodos superiores están dispuestos sobre el electrodo inferior. La al menos una capa de conmutación de resistencia está dispuesta respectivamente entre el electrodo inferior y los electrodos superiores. La al menos una capa limitadora de corriente está dispuesta respectivamente entre la(s) capa(s) de conmutación de resistencia y los electrodos superiores.

De acuerdo con un ejemplo de realización de la divulgación, un número de los electrodos superiores es 4 o más.

De acuerdo con un ejemplo de realización de la divulgación, las capas de conmutación de resistencia están formadas integralmente como una sola.

De acuerdo con un ejemplo de realización de la divulgación, la RRAM incluye además una pluralidad de capas aislantes. Las capas aislantes están dispuestas respectivamente entre las capas de cambio de resistencia y los electrodos superiores. Cada una de las capas limitantes actuales cubre respectivamente las paredes laterales de las capas aislantes.

- De acuerdo con un ejemplo de realización de la divulgación, la RRAM incluye además una pluralidad de capas aislantes. Las capas aislantes están dispuestas respectivamente sobre las capas limitantes actuales. Los electrodos superiores están dispuestos respectivamente sobre las capas aislantes, se extienden hacia abajo y cubren las paredes laterales de las capas aislantes y están directamente conectados eléctricamente a las capas limitantes actuales.

- 50 De acuerdo con un ejemplo de realización de la divulgación, el electrodo inferior es en forma de anillo.

De acuerdo con un ejemplo de realización de la divulgación, un material de la capa aislante incluye óxido de silicio.

De acuerdo con un ejemplo de realización de la divulgación, un material de los electrodos superiores y el electrodo inferior incluye TiN o ITO.

De acuerdo con un ejemplo de realización de la divulgación, un material de las capas de conmutación de resistencia incluye Ta<sub>2</sub>O<sub>5</sub> o HfO<sub>2</sub>.

5 De acuerdo con un ejemplo de realización de la divulgación, un material de las capas de limitación de corriente incluye Tao, TaO<sub>2</sub>, Tao<sub>x</sub>, TiO<sub>x</sub>, HfO<sub>x</sub>, ZrO<sub>x</sub>, o AlO<sub>x</sub> x representa una relación subestequiométrica.

De acuerdo con un ejemplo de realización de la divulgación, una dirección de extensión de los electrodos superiores y una dirección de extensión de una línea de palabra que conecta un electrodo de puerta del transistor son perpendiculares entre sí o paralelos entre sí.

- A la luz de lo anterior, en la divulgación, a través de la estructura que una pluralidad de filamentos están conectados en paralelo en la región de drenaje del transistor (es decir, la estructura 1TnR, n es el número de filamentos), el problema de la dificultad en el reconocimiento de la diferencia entre 0 y 1 se puede resolver la señal digital del dispositivo en un entorno de alta temperatura, y de este modo se logra el efecto de salvar el área ocupada del sustrato.

- Para las características y ventajas anteriores de la divulgación más comprensible, se describen varias formas de realización acompañados con dibujos en detalle como sigue.

## Breve descripción de los dibujos

En particular, los dibujos adjuntos se incluyen para proporcionar una comprensión adicional de la invención y se incorporan en y constituyen una parte de esta especificación. Los dibujos ilustran realizaciones de la divulgación y, junto con la descripción, sirven para explicar los principios de la divulgación.

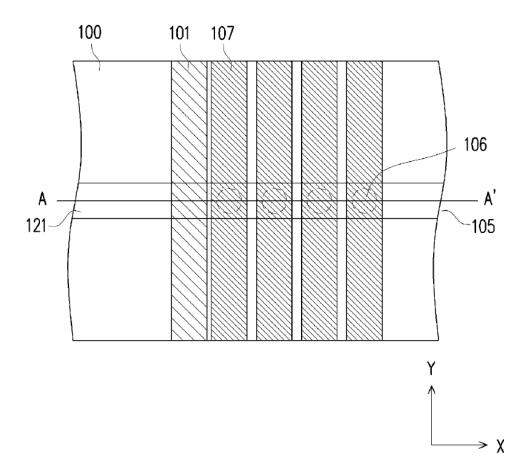

La figura 1A es una vista superior esquemática de una RRAM de acuerdo con una realización 1 de la divulgación;

La figura 1B es una vista en sección transversal esquemática de una RRAM según la realización 1 de la divulgación.

25 La figura 1C es otra vista superior esquemática de una RRAM de acuerdo con otra realización de la divulgación;

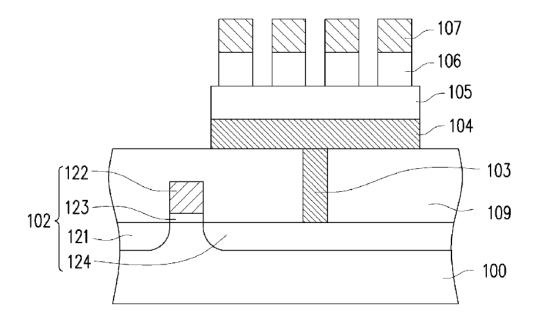

La figura 2 es una vista en sección transversal esquemática de una RRAM según la realización 2 de la divulgación.

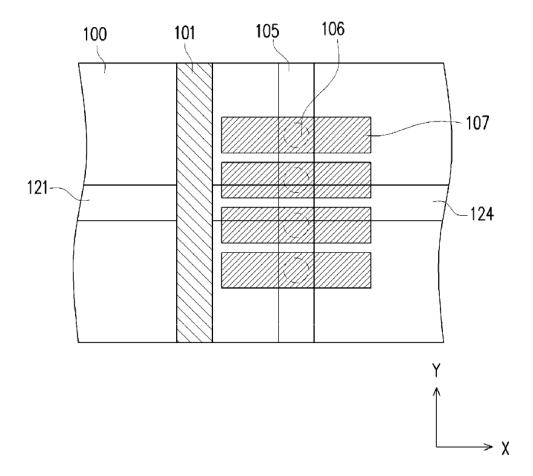

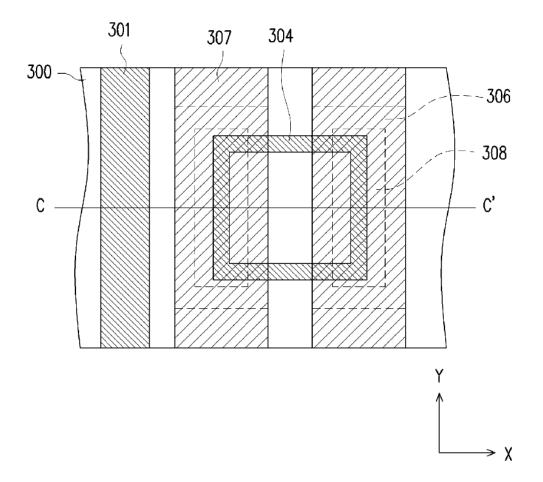

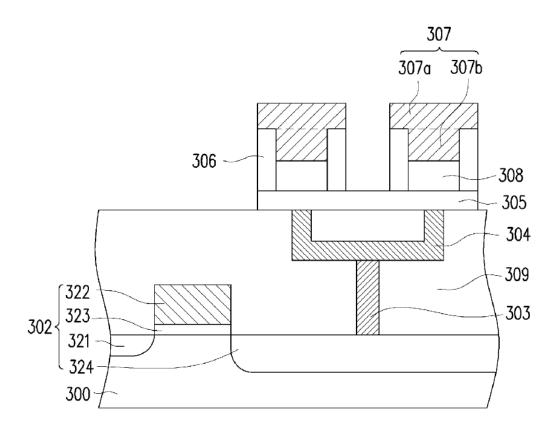

La figura 3A es una vista superior esquemática de una RRAM de acuerdo con una realización 3 de la divulgación;

La figura 3B es una vista esquemática en sección transversal de una RRAM según la realización 3 de la divulgación.

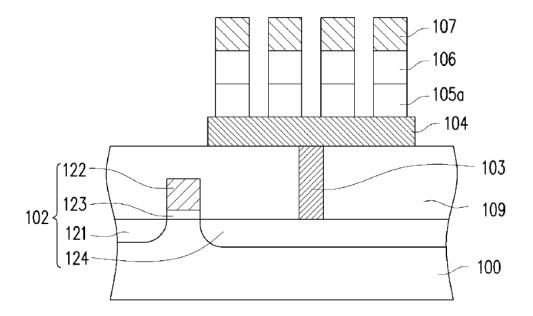

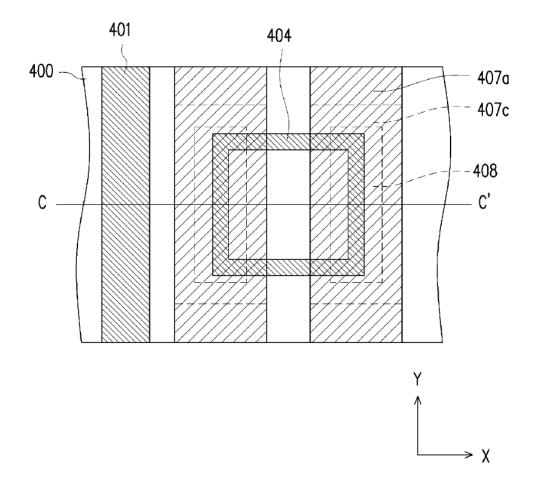

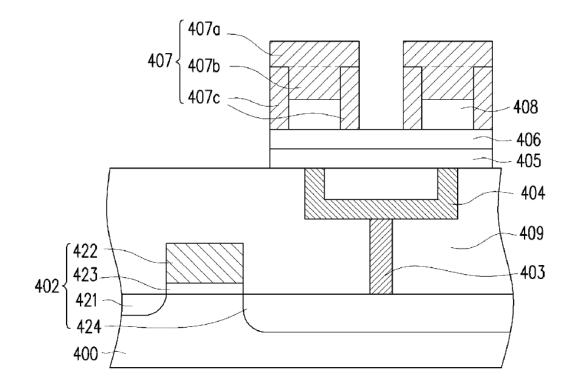

La figura 4A es una vista superior esquemática de una RRAM de acuerdo con una realización 4 de la divulgación;

La figura 4B es una vista en sección transversal esquemática de una RRAM según la realización 4 de la divulgación.

# Descripción de las realizaciones

En los ejemplos de realización descritos a continuación, siempre que sea posible, los mismos o similares números de referencia se utilizan en los dibujos y la descripción para referirse las partes iguales o similares, y la descripción de las mismas se simplifica o se omite.

# 40 Realización 1

20

La figura 1A es una vista superior esquemática de una RRAM de acuerdo con una realización 1 de la divulgación; La figura 1B es una vista en sección transversal esquemática de una RRAM según la realización 1 de la divulgación, en la que la figura 1B es una vista en sección transversal tomada a lo largo de la línea A-A' en la figura 1A. La figura 1C es otra vista superior esquemática de una RRAM de acuerdo con otra realización de la divulgación;

45 Con referencia a la figura 1A y la figura 1B, la RRAM de la divulgación incluye un transistor 102, un electrodo 104 inferior, una capa 105 de conmutación de resistencia, una pluralidad de capas 106 limitadoras de corriente y una pluralidad de electrodos 107 superiores.

Una estructura 1T4R se ejemplifica para propósitos ilustrativos únicamente en la realización, y la descripción no debe limitarse a la estructura 1T4R.

El transistor 102 está dispuesto sobre el sustrato 100. El sustrato 100 es, por ejemplo, un sustrato de silicio de tipo N o un sustrato de silicio de tipo P. El transistor 102 incluye un electrodo 122 de puerta, una capa 123 dieléctrica de puerta, una región 121 fuente y una región 124 de drenaje.

El electrodo 122 de puerta está dispuesto en el sustrato 100, y el material del electrodo 122 de puerta se dopa de polisilicio, por ejemplo. La capa 123 dieléctrica de puerta está dispuesta entre el electrodo 122 de puerta y el sustrato 100. El material de la capa 123 dieléctrica de puerta es, por ejemplo, óxido de silicio, y el material de la capa 123 dieléctrica de puerta también puede ser otro material dieléctrico. La región 121 fuente y la región 124 de drenaje están dispuestas respectivamente dentro del sustrato 100 en los dos lados del electrodo 122 de puerta.

El electrodo 104 inferior está dispuesto en el sustrato 100. El material del electrodo 104 inferior es, por ejemplo, nitruro de titanio (TiN) u óxido de estaño e indio (ITO). El electrodo 104 inferior está conectado eléctricamente a la región 124 de drenaje del transistor 102 a través de un enchufe 103. El enchufe 103 está dispuesto dentro de la capa 109 aislante entre capas, por ejemplo, y el electrodo 104 inferior está dispuesto sobre la capa 109 aislante entre capas.

Los electrodos 107 superiores están dispuestos, respectivamente, sobre el electrodo 104 inferior. El material de los electrodos 107 superiores es, por ejemplo, nitruro de titanio (TiN) u óxido de estaño e indio (ITO). En la realización, la dirección de extensión (dirección Y) de la línea 101 de palabra que conecta el electrodo 122 de puerta del transistor 102 son paralelas entre sí, por ejemplo. Por supuesto, en otra realización, como se muestra en la figura 1C, la dirección de extensión (dirección X) de los electrodos 107 superiores y la dirección de extensión (dirección Y) de la línea 101 de palabra que conecta el electrodo 122 de puerta del transistor 102 son perpendiculares entre sí.

La capa 105 de conmutación de resistencia está dispuesto entre el electrodo 104 inferior y los electrodos 107 superiores. El material de la capa 105 de conmutación de resistencia es, por ejemplo,  $Ta_2O_5$  o  $HfO_2$ . En la realización, por ejemplo, la capa 105 de conmutación de resistencia dispuesta entre el electrodo 104 inferior y los electrodos 107 superiores se forma integralmente como uno solo.

Las capas 106 de limitación de corriente se disponen, respectivamente, entre la capa 105 de conmutación de resistencia y los electrodos 107 superiores. El material de las capas 106 de limitación de corriente incluye, por ejemplo, Tao, Tao<sub>2</sub>, Tao<sub>x</sub>, TiO<sub>x</sub>, HfO<sub>x</sub>, ZrO<sub>x</sub>, o AlO<sub>x</sub>, en el que x representa una relación subestequiométrica. El valor de resistencia de las capas 106 limitadoras de corriente es más bajo que el valor de resistencia de la capa 105 de conmutación de resistencia que se encuentra en un estado de baja resistencia, pero es más alto que el valor de resistencia de la región fuente y la región de drenaje del transistor. Por ejemplo, cuando el material de la capa 105 de conmutación de resistencia es Ta<sub>2</sub>O<sub>5</sub>, el material de las capas limitantes de corriente 106 es TaO, TaO<sub>2</sub>, TaO<sub>x</sub>; cuando el material de la capa 105 de conmutación de resistencia es HfO<sub>2</sub>, el material de las capas limitantes de corriente 106 es TaO<sub>x</sub>, TiO<sub>x</sub>, HfO<sub>x</sub>, ZrO<sub>x</sub> o AlO<sub>x</sub>.

En la realización, una pluralidad de electrodos 107 superiores y toda una capa de la capa 105 de conmutación de resistencia están dispuestas en el electrodo 104 inferior, en el que el electrodo 104 inferior, la capa 105 de conmutación de resistencia, las capas 106 de limitación de corriente y cada electrodo 107 superior constituye una pluralidad de filamentos, y se forma la llamada memoria de acceso aleatorio resistiva de múltiples particiones. Cuando se realiza la operación de programación, se puede aplicar voltaje selectivamente a los electrodos superiores respectivamente para cambiar el estado conductor de cada una de las capas 105 de conmutación de resistencia, para producir una pluralidad de estados de filamentos que son separables. En la operación de lectura, se leen los estados de todos los filamentos, logrando así el propósito de leer que la memoria está en el estado de alta resistencia o en el estado de baja resistencia (es decir, la señal 0 o 1) fácilmente por el valor actual y también logrando el efecto de salvar el área ocupada del sustrato.

#### Realización 2

50

55

La figura 2 es una vista en sección transversal esquemática de una RRAM según la realización 2 de la divulgación. La figura 2 es una vista en sección transversal tomada a lo largo de la línea A-A' en la figura 1A.

La RRAM incluye un transistor 102, un electrodo 104 inferior, una pluralidad de capas 105a de conmutación de resistencia, una pluralidad de capas 106 de limitación de corriente y una pluralidad de electrodos 107 superiores.

Una estructura 1T4R se ejemplifica para propósitos ilustrativos únicamente en la realización, y la descripción no debe limitarse a la estructura 1T4R. Siempre que sea posible en lo siguiente, si los materiales y las características de los componentes no están en una descripción detallada, se asume que son iguales o similares a los de la Realización 1.

En la RRAM de la forma de realización, el transistor 102 está dispuesto en el sustrato 100. El transistor 102 incluye un electrodo 122 de puerta, una capa 123 dieléctrica de puerta, una región 121 fuente y una región 124 de drenaje. El electrodo 122 de puerta está dispuesto sobre el sustrato 100 y la capa 123 dieléctrica de puerta está dispuesta entre el electrodo 122 de puerta y el sustrato 100. La región 121 fuente y la región 124 de drenaje están dispuestas respectivamente dentro del sustrato 100 en los dos lados de un cuerpo laminado que está compuesto por el

electrodo 122 de puerta y la capa 123 dieléctrica de puerta.

El electrodo 104 inferior está dispuesto en el sustrato 100. El electrodo 104 inferior está conectado eléctricamente a la región 124 de drenaje del transistor 102 a través de un enchufe 103. El enchufe 103 está dispuesto dentro de la capa 109 aislante entre capas, por ejemplo, y el electrodo 104 inferior está dispuesto sobre la capa 109 aislante entre capas.

Los electrodos 107 superiores están respectivamente dispuestos de forma independiente en el electrodo 104 inferior. En la realización, la dirección de extensión (dirección Y) de los electrodos 107 superiores y la dirección de extensión (dirección Y) de la línea 101 de palabra que conecta el electrodo 122 de puerta del transistor 102 son paralelas entre sí. En otra realización, la dirección de extensión (dirección X) de los electrodos 107 superiores y la dirección de extensión (dirección Y) de la línea 101 de palabra que conecta el electrodo 122 de puerta del transistor 102 son perpendiculares entre sí.

Las capas 105a de conmutación de resistencia están dispuestas, respectivamente, entre el electrodo 104 inferior y los electrodos 107 superiores.

Las capas 106 de limitación de corriente se disponen, respectivamente, entre las capas 105a de conmutación de resistencia y los electrodos 107 superiores.

En la realización, una pluralidad de electrodos 107 superiores y un número correspondiente de capas 105a de conmutación de resistencia están dispuestas en el electrodo 104 inferior, en el que el electrodo 104 inferior, las capas 105 de conmutación de resistencia, las capas 107 de limitación de corriente y los electrodos 107 superiores constituyen una pluralidad de filamentos, y se forma la llamada memoria de acceso aleatorio resistiva de múltiples particiones. Cuando se realiza la operación de programación, se puede aplicar voltaje selectivamente a los electrodos superiores respectivamente para cambiar el estado conductor de cada una de las capas 105a de conmutación de resistencia, para producir una pluralidad de estados de filamentos que se pueden separar. En la operación de lectura, se leen los estados de todos los filamentos, logrando así el propósito de leer que la memoria está en el estado de alta resistencia o en el estado de baja resistencia (es decir, la señal 0 o 1) fácilmente por el valor actual y también logrando el efecto de salvar el área ocupada del sustrato.

## Realización 3

5

10

20

25

30

35

40

50

Por favor refiérase a la figura 3A y la figura 3B. La figura 3A es una vista superior esquemática de una RRAM de acuerdo con una realización 3 de la divulgación; La figura 3 es una vista en sección transversal esquemática de una RRAM según la realización 3 de la divulgación. La figura 3B es una vista en sección transversal esquemática tomada a lo largo de la línea C-C' en la figura 3A.

La RRAM incluye un transistor 302, un electrodo 304 inferior, una capa 305 de conmutación de resistencia, una pluralidad de capas 308 aislantes, una pluralidad de capas 306 de limitación de corriente y una pluralidad de electrodos 307 superiores.

Una estructura 1T2R se ejemplifica para propósitos ilustrativos únicamente en la realización, y la descripción no debe limitarse a la estructura 1T2R. Siempre que sea posible en lo siguiente, si los materiales y las características de los componentes no están en una descripción detallada, se asume que son iguales o similares a los de la Realización 1.

En la RRAM de la forma de realización, el transistor 302 está dispuesto en el sustrato 300. El transistor 302 incluye un electrodo 322 de puerta, una capa 323 dieléctrica de puerta, una región 321 fuente y una región 324 de drenaje. El electrodo 322 de puerta está dispuesto sobre el sustrato 300 y la capa 323 dieléctrica de puerta está dispuesta entre el electrodo 322 de puerta y el sustrato 300. La región 321 fuente y la región 324 de drenaje están dispuestas respectivamente dentro del sustrato 300 en los dos lados de un cuerpo laminado que está compuesto por el electrodo 322 de puerta y la capa 323 dieléctrica de puerta.

La capa 309 aislante entre capas está dispuesta en el sustrato 300. El material de la capa 309 aislante entre capas es, por ejemplo, óxido de silicio. El electrodo 304 inferior en forma de anillo está dispuesto dentro de la capa 309 de aislamiento entre capas, y el electrodo inferior en forma de anillo está cubierto por la capa 309 de aislamiento entre capas. El electrodo 304 inferior en forma de anillo está conectado eléctricamente a la región 324 de drenaje del transistor 302 a través de un enchufe 303.

Los electrodos 307 superiores están respectivamente dispuestos de forma independiente en el electrodo 304 inferior. Cada uno de los electrodos 307 superiores está compuesto por una primera porción 307a y una segunda porción 307b.

La capa 305 de conmutación de resistencia está dispuesta entre el electrodo 304 inferior y los electrodos 307 superiores de cable.

Las capas 308 aislantes están dispuestas respectivamente de forma independiente entre la capa 305 de

conmutación de resistencia y los electrodos 307 superiores. El material de las capas 308 aislantes es, por ejemplo, óxido de silicio.

Las capas 306 de limitación de corriente están respectivamente dispuestas de manera independiente entre la capa 305 de conmutación de resistencia y los electrodos 307 superiores, y cada una de ellas cubre las paredes laterales de la capa 308 aislante. Cada uno de los electrodos 307 superiores, junto con cada capa 306 de limitación de corriente y cada capa 308 aislante, constituyen un cuerpo laminado individualmente, y cada capa 306 de limitación de corriente también rodea una parte de cada electrodo 307 superior. Como se muestra en la figura 3A, la capa 306 de limitación de corriente cubre las paredes laterales de la capa 308 aislante, y se forma un hueco por encima de la capa 308 aislante. La segunda porción 307b del electrodo 307 superior se llena en el rebaje, de tal manera que la capa 306 de limitación de corriente cubre la segunda porción 307b del electrodo 307 superior. La primera porción 307a del electrodo 307 superior está dispuesta en la segunda porción 307b del electrodo 307 superior y se extiende en la dirección Y.

En la realización, los electrodos 307 superiores y una capa entera de la capa 305 de conmutación de resistencia están dispuestos sobre el electrodo 304 inferior, en el que la capa 306 de limitación de corriente es en forma de anillo. Los electrodos 307 superiores, las capas 306 de limitación de corriente, la capa 305 de conmutación de resistencia y el electrodo 304 inferior constituyen una pluralidad de filamentos, y se forma la denominada RRAM de múltiples particiones. Cuando se realiza la operación de programación, se puede aplicar voltaje selectivamente a los electrodos superiores respectivamente para cambiar el estado conductor de la capa 305 de conmutación de resistencia, para producir una pluralidad de estados de filamentos que se pueden separar. En la operación de lectura, se leen los estados de todos los filamentos, logrando así el propósito de leer que la memoria está en el estado de alta resistencia o en el estado de baja resistencia (es decir, la señal 0 o 1) fácilmente por el valor actual y también logrando el efecto de salvar el área ocupada del sustrato.

#### Realización 4

10

15

20

35

50

55

Por favor refiérase a la figura 4A y la figura 4B. La figura 4A es una vista superior esquemática de una RRAM de acuerdo con una realización 4 de la divulgación; La figura 4B es una vista en sección transversal esquemática de una RRAM según la realización 4 de la divulgación. La figura 4B es una vista en sección transversal esquemática tomada a lo largo de la línea C-C' en la figura 4A.

La RRAM incluye un transistor 402, un electrodo 404 inferior, una capa 405 de conmutación de resistencia, una capa 406 limitadora de corriente, una pluralidad de capas 408 aislantes y una pluralidad de electrodos 407 superiores.

30 Una estructura 1T2R se ejemplifica para propósitos ilustrativos únicamente en la realización, y la descripción no debe limitarse a la estructura 1T2R. Siempre que sea posible en lo siguiente, si los materiales y las características de los componentes no están en una descripción detallada, se asume que son iguales o similares a los de la Realización 3.

En la RRAM de la forma de realización, el transistor 402 está dispuesto en el sustrato 400. El transistor 402 incluye un electrodo 422 de puerta, una capa 423 dieléctrica de puerta, una región 421 fuente y una región 424 de drenaje. El electrodo 422 de puerta está dispuesto sobre el sustrato 400 y la capa 423 dieléctrica de puerta está dispuesta entre el electrodo 422 de puerta y el sustrato 400. La región 421 fuente y la región 424 de drenaje están dispuestas respectivamente dentro del sustrato 400 en los dos lados de un cuerpo laminado que está compuesto por el electrodo 422 de puerta y la capa 423 dieléctrica de puerta.

40 La capa 409 de aislamiento entre capas está dispuesta en el sustrato 400. El electrodo 404 inferior en forma de anillo está dispuesto dentro de la capa 409 de aislamiento entre capas, y el electrodo inferior en forma de anillo está cubierto por la capa 409 de aislamiento entre capas. El electrodo 404 inferior en forma de anillo está conectado eléctricamente a la región 424 de drenaje del transistor 402 a través de un enchufe 403.

La capa 405 de conmutación de resistencia está dispuesto sobre el electrodo 404 inferior. La capa 406 limitadora de corriente está dispuesta sobre la capa 405 de conmutación de resistencia. Las capas 408 aislantes están respectivamente dispuestas independientemente sobre la capa 406 limitadora de corriente.

Los electrodos 407 superiores están respectivamente dispuestos de forma independiente en las dos capas 408 aislantes, se extienden hacia abajo y cubren las paredes laterales de las capas 408 aislantes, de modo que la capa 406 limitadora de corriente es directamente conectados eléctricamente a los electrodos 407 superiores. En concreto, cada uno de los miembros 407 de cableado tiene: una primera porción 407a, una segunda porción 407b y una tercera porción 407c. La segunda porción 407b del electrodo 407 superior está dispuesta sobre la capa 408 aislante. La tercera porción 407c del electrodo 407 superior, a saber, la tercera porción 407c del electrodo superior cubre la capa 408 aislante y la segunda porción 407b del electrodo 407 superior. La primera porción 407a del electrodo 407 superior está dispuesta en la segunda porción 307b del electrodo 407 superior y se extiende en la dirección Y.

En la realización, los electrodos 407 superiores y una capa entera de la capa 405 de conmutación de resistencia están dispuestos sobre el electrodo 404 inferior, donde la porción del electrodo 407 superior, que cubre la capa 408

# ES 2 734 279 T3

aislante, tiene forma de anillo. Los electrodos 407 superiores, la capa 406 limitadora de corriente, la capa 405 de conmutación de resistencia y el electrodo 404 inferior constituyen una pluralidad de filamentos, y se forma la denominada RRAM de múltiples particiones. Cuando se realiza la operación de programación, se puede aplicar voltaje selectivamente a los electrodos superiores respectivamente para cambiar el estado conductor de la capa 405 de conmutación de resistencia, para producir una pluralidad de estados de filamentos que se pueden separar. En la operación de lectura, se leen los estados de todos los filamentos, logrando así el propósito de leer que la memoria está en el estado de alta resistencia o en el estado de baja resistencia (es decir, la señal 0 o 1) fácilmente por el valor actual y también logrando el efecto de salvar el área ocupada del sustrato.

5

A la luz de lo anterior, en la divulgación, a través de la estructura en que una pluralidad de filamentos están conectados en paralelo en la región de drenaje del transistor, el problema de la dificultad de reconocer la diferencia entre la señal digital de 0 y 1 del dispositivo en un entorno de temperatura alta, se puede resolver y, por lo tanto, se logra el efecto de salvar el área ocupada del sustrato.

#### REIVINDICACIONES

- 1. Una memoria de acceso aleatorio resistiva, que comprende:

- un sustrato (100, 300);

- un transistor (102, 302), dispuesto sobre el sustrato (100, 300);

- un electrodo (104, 304) inferior, dispuesto sobre el sustrato (100, 300) y conectado eléctricamente a una fuente (121, 321)/drenaje (124, 324) del transistor (102, 302);

- una pluralidad de electrodos (107, 307) superiores, dispuestos en el electrodo (104, 304) inferior;

- al menos una capa (105, 105a, 305) de conmutación de resistencia, dispuesta entre el electrodo (104, 304) inferior y la pluralidad de electrodos (107, 307) superiores, en la que la al menos una capa (105, 105a, 305) de conmutación de resistencia está directamente en contacto con el electrodo (104, 304) inferior; caracterizada por una pluralidad de capas (106, 306) limitadoras de corriente, respectivamente dispuestas entre la al menos una capa (105, 105a, 305) de conmutación de resistencia y la pluralidad de electrodos (107, 307) superiores, en la que la pluralidad de capas (106, 306) limitadoras de corriente está directamente en contacto con la pluralidad de electrodos (107, 307) superiores y una de las al menos una capa (105, 105a, 305) de conmutación de resistencia.

- en la que un valor de resistencia de la pluralidad de capas (106, 306) limitadoras de corriente, es más bajo que un valor de resistencia de al menos una capa (105, 105a, 305) de conmutación de resistencia, que está en un estado de baja resistencia.

- 2. Una memoria de acceso aleatorio resistiva, que comprende:

- 20 un sustrato (400);

30

45

50

55

- un transistor (402) dispuesto sobre el sustrato (400);

- un electrodo (404) inferior, dispuesto sobre el sustrato (400) y conectado eléctricamente a una fuente (421)/drenaje (424) del transistor (402);

- una pluralidad de electrodos (407) superiores, dispuestos en el electrodo (404) inferior;

- una capa (405) de conmutación de resistencia, dispuesta entre el electrodo (404) inferior y la pluralidad de electrodos (407) superiores, en la que la capa (405) de conmutación de resistencia está directamente en contacto con el electrodo (404) inferior; caracterizada por

- una capa (406) limitadora de corriente, dispuesta entre la capa (405) de conmutación de resistencia y la pluralidad de electrodos (407) superiores, en la que la capa (406) limitadora de corriente está directamente en contacto con la pluralidad de electrodos (407) superiores y la capa (405) de conmutación de resistencia,

- en la que un valor de resistencia de la capa (406) limitadora de corriente es más bajo que un valor de resistencia de la capa (405) de conmutación de resistencia que está en un estado de baja resistencia.

- 3. La memoria de acceso aleatorio resistiva según la reivindicación 1, en la que una cantidad de la pluralidad de electrodos (107) superiores es 4 o más.

- 4. La memoria de acceso aleatorio resistiva según la reivindicación 1 o la reivindicación 2, en la que un material de la pluralidad de electrodos (107, 307, 407) superiores y el electrodo (104, 304, 404) inferior comprende TiN o ITO.

- 5. La memoria de acceso aleatorio resistiva según la reivindicación 1 o la reivindicación 2, en la que un material de la capa (105, 105a, 305, 405) de conmutación de resistencia comprende  $Ta_2O_5$  o HfO<sub>2</sub>.

- 6. La memoria de acceso aleatorio resistiva según la reivindicación 1 o la reivindicación 2, en la que un material de la capa (106, 306, 406) de limitación de corriente comprende Tao, TaO<sub>2</sub>, Tao<sub>x</sub>, TiO<sub>x</sub>, HfO<sub>x</sub>, ZrO<sub>x</sub>, o A1O<sub>x</sub>, x representa una relación subestequiométrica.

- 7. La memoria de acceso aleatorio resistiva según la reivindicación 1 o la reivindicación 2, en la que una dirección de extensión de la pluralidad de electrodos (107, 307, 407) superiores y una dirección de extensión de una línea (101, 301, 401) de palabra que conecta el electrodo (122, 322, 422) de puerta del transistor (102, 302, 402) son perpendiculares entre sí o paralelas entre sí.

- 8. La memoria de acceso aleatorio resistiva según la reivindicación 1, que además comprende:

- una pluralidad de capas (308) aislantes, dispuestas respectivamente entre la capa (305) de conmutación de resistencia, y la pluralidad de electrodos (307) superiores;

- en la que cada una de la pluralidad de capas (306) limitadoras de corriente cubre respectivamente las paredes laterales de la pluralidad de capas (308) aislantes.

- 9. La memoria de acceso aleatorio resistiva según la reivindicación 2, que además comprende:

- una pluralidad de capas (408) aislantes, dispuestas respectivamente en la capa (406) limitadora de corriente; en la que la pluralidad de electrodos (407) superiores están dispuestos respectivamente sobre la pluralidad de capas (408) aislantes, se extienden hacia abajo y cubren las paredes laterales de la pluralidad de capas (408) aislantes y están directamente conectadas eléctricamente a la capa (406) limitadora de corriente.

# ES 2 734 279 T3

10. La memoria de acceso aleatorio resistiva según la reivindicación 1 o la reivindicación 2, en la que el electrodo (304, 404) inferior tiene forma de anillo.

FIG. 1A

FIG. 1B

FIG. 1C

FIG. 2

FIG. 3A

FIG. 3B

FIG. 4A

FIG. 4B