# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 735 739

(51) Int. CI.:

H04L 12/26 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

Fecha de presentación y número de la solicitud europea: 28.06.2016 E 16176638 (1)

Fecha y número de publicación de la concesión europea: 15.05.2019 EP 3125470

(54) Título: Aparato para detectar tramas Ethernet

(30) Prioridad:

30.07.2015 KR 20150108399

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 20.12.2019

(73) Titular/es:

LSIS CO., LTD. (100.0%) LS Tower, 127, LS-ro, Dongan-gu, Anyang-si Gyeonggi-do 14119, KR

(72) Inventor/es:

KIM, WOO-HYUN y BAE, GYU-SUNG

(74) Agente/Representante:

SÁNCHEZ SILVA, Jesús Eladio

### **DESCRIPCIÓN**

Aparato para detectar tramas Ethernet

#### 5 Antecedentes

#### 1. Campo técnico

La presente invención se refiere a un aparato para detectar tramas Ethernet y, más particularmente, a un aparato para detectar tramas Ethernet en el campo de la comunicación de redes Ethernet.

#### 2. Descripción de la técnica relacionada

Ethernet es la red de comunicaciones de rango corto más típica de una estructura de bus. Para transmitir datos a través del Ethernet, se usa un esquema de Acceso Múltiple con Escucha de Señal Portadora y detección de colisiones (CSMA/CD).

Al transmitir datos a través de una trama Ethernet, se añaden un encabezado y final Ethernet a un paquete de datos generado en la capa de Internet, que es una capa superior, y luego se transmite a través de un medio. Cuando los datos se reciben a través de la trama Ethernet, el encabezado y fin se separan entre sí, y el paquete de datos se envía a la capa de red.

La trama Ethernet incluye un campo Preámbulo para anunciar, a un receptor, la transmisión de la trama Ethernet y proporcionar una señal de sincronización que permite la distinción entre 0 y 1 en la trama para recibir, un campo Delimitador de Inicio que indica la posición de inicio de la trama, un campo de dirección MAC de destino, un campo de dirección MAC fuente y un campo de longitud que indica el tamaño de los datos transmitidos con una longitud variable contenida en un campo de datos, un campo de datos, un campo Checksum que permite a un servidor receptor reconocer la ocurrencia de un error de variación de datos en el proceso de la variación de datos en el proceso de transmisión de datos.

Para procesar los datos de Ethernet, la trama Ethernet recibida necesita detectarse y transferirse a través de una trayectoria donde la trama Ethernet recibida puede procesarse apropiadamente de conformidad con el resultado de la detección.

35 De conformidad con esto, existe una necesidad de un aparato de detección de la trama Ethernet capaz de detectar de manera eficiente las tramas Ethernet.

El documento US 2002/077995 describe un método y sistema ilustrativo para detectar tramas Ethernet a través de la adaptación de patrones en una red de comunicaciones.

Resumen

30

40

50

Es un aspecto de la presente invención detectar eficientemente las tramas Ethernet de varias maneras.

Es otro aspecto de la presente invención reducir los costos de producción de los circuitos de detección de la trama Ethernet y simplificar su configuración.

Además, los costos de producción de los circuitos de detección de la trama Ethernet pueden reducirse, y la configuración puede simplificarse.

El alcance de la invención se define por las reivindicaciones adjuntas.

Breve descripción de los dibujos

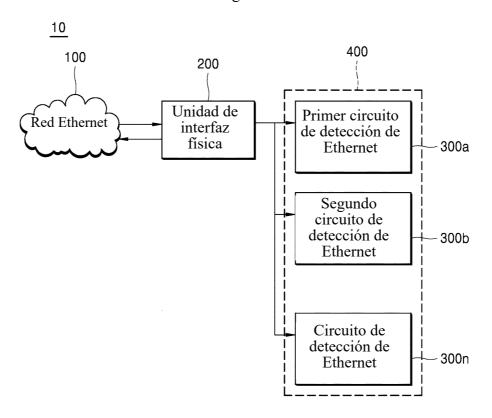

La Figura 1 es un diagrama de bloques que ilustra la configuración de un sistema Ethernet de acuerdo con una modalidad de la presente invención.

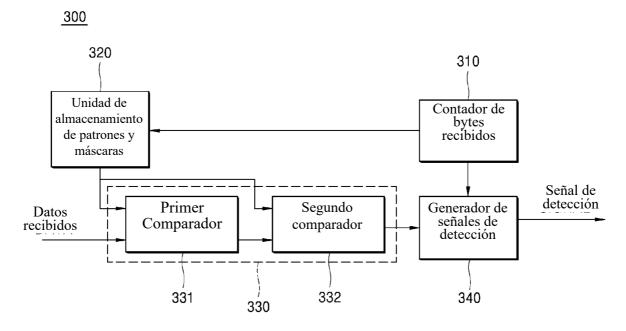

La Figura 2 es un diagrama de bloques que ilustra la configuración de un circuito de detección de Ethernet de acuerdo con una modalidad de la presente invención.

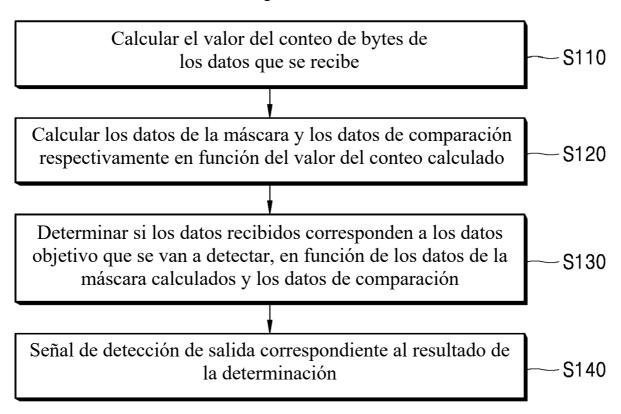

La Figura 3 es un diagrama de flujo que ilustra el funcionamiento de un circuito de detección de Ethernet de conformidad con una modalidad de la presente invención.

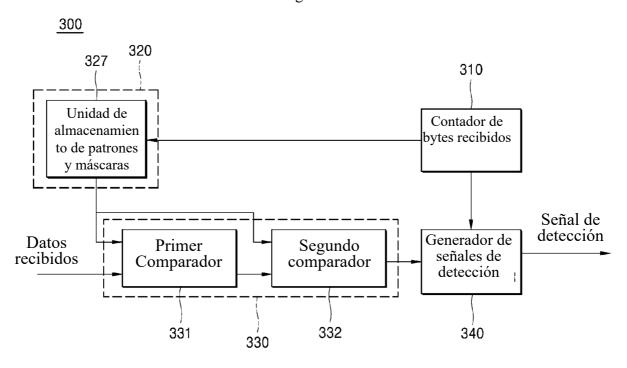

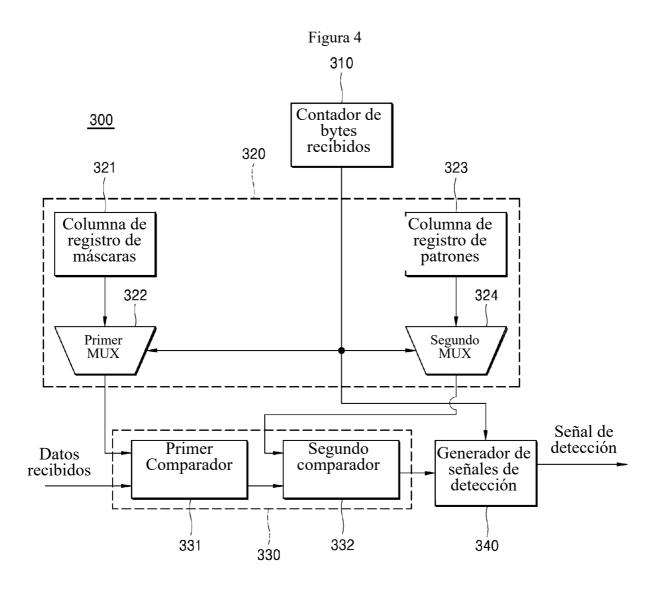

La Figura 4 es un diagrama de bloques de un circuito de detección de Ethernet que ilustra la configuración de una máscara y una unidad de almacenamiento de patrones de conformidad con una modalidad de la presente invención. La Figura 5 es un diagrama de bloques de un circuito de detección de Ethernet que ilustra la configuración de una máscara y una unidad de almacenamiento de patrones de conformidad con otra modalidad de la presente invención.

65

60

#### Descripción detallada

5

10

15

20

25

30

35

40

45

50

60

65

De ahora en adelante, las modalidades de la presente invención se describirán en detalle con referencia a los dibujos acompañantes. Tal como se usa en el presente documento, los sufijos "módulo" y "unidad" se agregan o usan de manera intercambiable para facilitar la preparación de esta descripción y no pretenden sugerir significados o funciones que se distinguen entre ellos.

Las ventajas y características de la presente invención y los métodos para lograrlos serán evidentes a partir de las descripciones de modalidades ilustrativas de la presente descripción más abajo con referencia a los dibujos adjuntos. Sin embargo, la presente invención no se limita a las modalidades ilustrativas descritas en la presente, pero puede implementarse en varias formas diferentes. Las modalidades ilustrativas se proporcionan para hacer la divulgación de la presente invención a fondo y para transmitir completamente el alcance de la presente invención a los expertos en la materia. Debe notarse que el alcance de la presente invención se define solo por las reivindicaciones. Los números de referencia similares denotan elementos similares a lo largo de las descripciones.

Al describir las modalidades de la presente invención descritas en esta memoria descriptiva, las funciones y constituyentes bien conocidos relevantes pueden no describirse en detalle si se determina que dicha descripción puede ocultar innecesariamente el objeto de la presente invención. Los términos que se usarán a continuación se definen en consideración de las funciones de los elementos correspondientes en las modalidades de la presente invención.

Debe entenderse que la presente invención no está limitada a las siguientes modalidades, y que las modalidades se proporcionan únicamente con fines ilustrativos. El alcance de la invención debe definirse únicamente por las reivindicaciones adjuntas. Las definiciones de los términos pueden variar según la intención de un usuario u operador, un caso anterior, o similares. Por lo tanto, los términos deben definirse en función de la descripción completa.

Se entenderá que cada bloque de las ilustraciones del diagrama de flujo y/o los diagramas de bloques, y las combinaciones de bloques en las ilustraciones del diagrama de flujo y/o los diagramas de bloques, pueden implementarse mediante instrucciones de programa informático. Estas instrucciones de programa informático pueden proporcionarse a un procesador de una computadora de propósito general, computadora de propósito especial u otro aparato de procesamiento de datos programable para producir una máquina, de tal manera que las instrucciones, que se ejecutan a través del procesador de la computadora u otro aparato programable de procesamiento de datos, crean medios para implementar las funciones/actos especificados en el diagrama de flujo y/o bloque o bloques del diagrama de bloques. Estas instrucciones de programas informáticos también pueden almacenarse en una memoria legible por computadora o que puede usarse en una computadora que puede dirigir a una computadora u otro aparato programable de procesamiento de datos para que funcione de una manera particular, de modo que las instrucciones almacenadas en la memoria legible por computadora o que puede usarse en una computadora produzcan un artículo de fabricación que incluya instrucciones que implementan la función especificada en el diagrama de flujo y/o bloque o bloques del diagrama de bloques. Las instrucciones del programa informático también pueden cargarse en una computadora u otro aparato programable de procesamiento de datos para hacer que una serie de etapas operativas se realicen en la computadora u otro aparato programable para producir un proceso implementado por computadora de manera tal que las instrucciones que se ejecutan en la computadora u otro aparato programable proporcionen procesos para implementar las funciones especificados en el diagrama de flujo y/o bloque o bloques del diagrama de bloques.

Además, cada bloque o etapa en el diagrama de flujo o diagramas de bloques puede representar un módulo, segmento o porción de código, que comprende una o más instrucciones ejecutables para implementar las funciones lógicas especificadas. También debe observarse que, en algunas implementaciones alternativas, las funciones señaladas en los bloques o etapas pueden producirse fuera del orden señalado en las figuras. Por ejemplo, dos bloques o etapas que se muestran en sucesión pueden llevarse a cabo, de hecho, sustancialmente de manera simultánea, o los bloques o etapas pueden llevarse a cabo en el orden inverso, en dependencia de la funcionalidad involucrada.

A continuación, se describirá un sistema Ethernet 10 de acuerdo con una modalidad de la presente invención con referencia a la Figura 1.

La Figura 1 es un diagrama de bloques que ilustra la configuración de un sistema Ethernet de acuerdo con una modalidad de la presente invención.

Con referencia a la Figura 1, un sistema Ethernet 10 incluye una red Ethernet 100, una unidad de interfaz física 200, y un aparato de detección de Ethernet 400.

La red Ethernet 100 puede representar una red de comunicación física. Por ejemplo, la red Ethernet 100 puede representar una red de área local (LAN) de una estructura de bus.

La unidad de interfaz física 200 puede ser una interfaz conectada a la red Ethernet 100 para recibir datos. El aparato de detección de Ethernet 400 puede detectar una trama Ethernet de datos recibidos.

El aparato de detección de Ethernet 400 puede incluir una pluralidad de circuitos de detección de Ethernet 300a, 300b,..300n.

5

10

20

25

30

35

40

45

50

65

En la presente, cada circuito de detección de Ethernet puede detectar una trama que tiene la longitud máxima de L bytes. De esta manera, el aparato de detección de Ethernet 400 puede detectar n tramas a través de una pluralidad de circuitos de detección de Ethernet 300a, 300b,...300n que incluyen n circuitos de detección de Ethernet.

Para facilitar la descripción, se asignará un número de referencia '300' a los circuitos de detección de Ethernet.

En lo sucesivo, un circuito de detección de Ethernet 300 se describirá en detalle con referencia a la Figura 2.

La Figura 2 es un diagrama de bloques que ilustra la configuración de un circuito de detección de Ethernet de acuerdo con una modalidad de la presente invención.

Con referencia a la Figura 2, el circuito de detección de Ethernet 300 incluye un contador de bytes recibidos 310, una unidad de almacenamiento de patrones y máscaras 320, un comparador 330, y un generador de señales de detección 340.

El contador de bytes recibidos 310 puede contar el byte de la trama Ethernet de los datos recibidos. De esta manera, el contador de bytes recibidos 310 puede calcular el valor del conteo de bytes de datos que se recibe. El contador de bytes recibidos 310 puede transmitir además el valor del conteo calculado a la máscara y a la unidad de almacenamiento de patrones 320 y al generador de señales de detección 340.

La unidad de almacenamiento de patrones y máscaras 320 puede calcular los datos de la máscara y los datos de comparación correspondientes al valor del conteo calculado basado en el registro de máscaras almacenado y la registro de patrones.

En la presente descripción, el registro de máscaras puede ser un registro que tiene una longitud de L bytes e indica una máscara de bits. En consecuencia, el registro de máscaras puede representar un registro que se usa para ignorar los bits que no necesitan detectarse. Los datos de la máscara pueden representar un registro de máscaras correspondiente al valor de conteo calculado.

El registro de patrones puede ser un registro que tiene una longitud de L bytes e indica un patrón de comparación de bits. En consecuencia, el registro de patrones puede representar un registro para indicar un patrón de tramas que se detecta. Los datos de comparación pueden representar un registro de patrones correspondiente al valor del conteo calculado.

El comparador 330 puede comparar los datos de la máscara y los datos de comparación calculados con los datos recibidos. Por ejemplo, el comparador 330 puede ignorar los bits que no necesitan detectarse en los datos recibidos, en base a los datos de máscara calculados. El comparador 330 puede detectar además un patrón de tramas que se detecta en los datos recibidos, en base a los datos de comparación calculados. En la presente descripción, los datos que contienen el patrón de tramas a detectar pueden denominarse como datos objetivos. El comparador 330 transmite el resultado de comparación con el generador de señales de detección 340.

Mientras tanto, el comparador 330 puede incluir una pluralidad de comparadores. Por ejemplo, el comparador 330 puede incluir un primer comparador 331 y un segundo comparador 332.

El primer comparador 331 puede ignorar los bits que no necesitan detectarse en los datos recibidos, en base a los datos de máscara calculados.

El segundo comparador 332 puede comparar los datos recibidos con los datos objetivos que se van a detectar, en base a los datos de comparación calculados.

Los datos recibidos pueden transferirse secuencialmente al primer comparador 331 y al segundo comparador 332.

El generador de señales de detección 340 sale de una señal de detección en base al resultado de la comparación.

El generador de señales de detección 340 puede emitir una señal de detección que indica si una trama que tiene la longitud máxima de L bytes se ha detectado como una trama que se va a detectar.

Por ejemplo, cuando se detecta una trama que se va a detectar, el generador de señales de detección 340 puede salir 1. Cuando la trama detectada no es una trama que se va a detectar, el generador de señales de detección 340 puede salir de 0.

En lo sucesivo, el funcionamiento del circuito de detección de Ethernet 300 se describirá en base a la descripción anterior.

La Figura 3 es un diagrama de flujo que ilustra el funcionamiento de un circuito de detección de Ethernet de conformidad con una modalidad de la presente invención.

Con referencia a la Figura 3, el contador de bytes recibidos 310 del circuito de detección de Ethernet 300 calcula el valor del conteo de bytes de los datos que se reciben (S110).

- El contador de bytes recibidos 310 puede contar el byte de datos que se reciben o se ha recibido en la trama Ethernet. De esta manera, el contador de bytes recibidos 310 puede calcular el valor del conteo de bytes de los datos que se reciben. El contador de bytes recibidos 310 puede transmitir el valor del conteo calculado a la máscara y a la unidad de almacenamiento de patrones 320 y al generador de señales de detección 340.

- La unidad de almacenamiento de patrones y máscaras 320 del circuito de detección de Ethernet 300 calcula los datos de la máscara y los datos de comparación respectivamente en base al valor del conteo calculado (S120).

- La unidad de almacenamiento de patrones y máscaras 320 puede calcular los datos de la máscara y los datos de comparación correspondientes al valor del conteo calculado basado en el registro de máscaras almacenado y el registro de patrones.

Un ejemplo se describirá con referencia a la Figura 4.

30

35

45

50

55

65

La Figura 4 es un diagrama de bloques de un circuito de detección de Ethernet que ilustra la configuración de una máscara y una unidad de almacenamiento de patrones de conformidad con una modalidad de la presente invención.

Con referencia a la Figura 4, la unidad de almacenamiento de patrones y máscaras 320 del circuito de detección de Ethernet 300 puede incluir una columna de registro de máscaras 321, un primer multiplexor (mux) 322, una columna de registro de patrones 323, y un segundo mux 324.

La columna de registro de máscaras 321 puede almacenar un registro de máscaras.

El primer mux 322 puede calcular los datos de máscara en base al registro de máscaras almacenada en la columna de registro de máscaras 321 y el valor de conteo calculado.

Por ejemplo, el primer mux 322 puede seleccionar los datos de máscara del registro de máscaras almacenado en la columna de registro de máscaras 321, tomando el valor de conteo calculado como una señal de selección.

El primer mux 322 puede transmitir los datos de la máscara de comparación calculada al comparador 330. Por ejemplo, el primer mux 322 puede transmitir los datos de máscara calculados al primer comparador 331.

La columna de registro de patrones 323 puede almacenar un registro de patrones.

El segundo mux 324 puede calcular los datos de comparación en base al registro de patrones almacenado en la columna de registro de patrones 323 y el valor de conteo calculado.

Por ejemplo, el segundo mux 324 puede seleccionar los datos de comparación del registro de patrones almacenados en la columna de registro de patrones 323, tomando el valor de conteo calculado como una señal de selección.

El segundo mux 324 puede transmitir los datos de comparación calculados al comparador 330. Por ejemplo, el segundo mux 324 puede transmitir los datos de comparación calculados al segundo comparador 332.

En lo sucesivo, otra modalidad se describirá con referencia a la Figura 5.

La Figura 5 es un diagrama de bloques de un circuito de detección de Ethernet que ilustra la configuración de una máscara y una unidad de almacenamiento de patrones de conformidad con otra modalidad de la presente invención.

Con referencia a la Figura 5, la unidad de almacenamiento de patrones y máscaras 320 del circuito de detección de 60 Ethernet 300 incluye una máscara y una memoria de almacenamiento de patrones 327.

La memoria de almacenamiento de patrones y máscaras 327 puede almacenar un registro de máscaras y registro de patrones. La memoria de almacenamiento de patrones y máscaras 327 puede calcular los datos de la máscara y los datos de comparación correspondientes al valor del conteo calculado, en base al registro de máscaras y registro de patrones almacenados. La memoria de almacenamiento de patrones y máscaras 327 puede transmitir los datos de la máscara y los datos de comparación calculados al comparador 330. Por ejemplo, la memoria de almacenamiento

de patrones y máscaras 327 puede transmitir los datos de máscara calculados al primer comparador 331, y transmitir los datos de comparación del cálculo al segundo comparador 332.

La memoria de almacenamiento de patrones y máscaras 327 puede incluir varios tipos de memorias. Por ejemplo, la memoria de almacenamiento de patrones y máscaras 327 puede incluir al menos una de una memoria de acceso aleatorio (RAM), una memoria de solo lectura (ROM) y una memoria flash.

El circuito de detección de Ethernet 300 que incluye la memoria de almacenamiento de patrones y máscaras 327 puede reducir el uso de un dispositivo tal como una biestable tipo D. En consecuencia, los costos de producción de los circuitos de detección de Ethernet pueden reducirse, y los chips semiconductores que constituyen el circuito de detección de Ethernet pueden reducirse en tamaño.

Se dará la descripción con referencia de vuelta a la Figura 3.

10

35

45

60

65

El comparador 330 del circuito de detección de Ethernet 300 determina si los datos recibidos corresponden a los datos que se detectan, en base a los datos de la máscara y los datos de comparación calculados (S130).

El comparador 330 puede comparar los datos de comparación calculados con los datos recibidos.

Por ejemplo, el comparador 330 puede ignorar los bits que no necesitan detectarse en los datos recibidos, en base a los datos de máscara calculados. El comparador 330 puede detectar además un patrón de una trama que se va a detectar en los datos recibidos, basado en los datos de comparación calculados. En la presente descripción, los datos que contienen el patrón de tramas a detectar pueden denominarse como datos objetivos. Por lo tanto, el comparador 330 puede determinar si los datos recibidos corresponden a los datos objetivos que se detectarán. El comparador 330 puede transmitir, al generador de señales de detección 340, el resultado de la determinación de conformidad con la comparación entre los datos de la máscara y los datos de comparación con los datos recibidos.

Como se describió anteriormente, el comparador 330 puede incluir una pluralidad de los comparadores.

30 Por ejemplo, el comparador 330 puede incluir un primer comparador 331 y un segundo comparador 332.

El primer comparador 331 puede ignorar los bits que no necesitan detectarse en los datos recibidos, en base a los datos de máscara calculados, y el segundo comparador 332 puede comparar los datos recibidos con los datos objetivo que se detectan, en base a los datos de comparación calculados. El primer comparador 331 y el segundo comparador 332 pueden transmitir el resultado de comparación con el generador de señales de detección 340.

El generador de señales de detección 340 del circuito de detección de Ethernet 300 sale de una señal de detección correspondiente al resultado de determinación (S140).

40 El generador de señales de detección 340 sale de una señal de detección en base al resultado de la determinación suministrada.

El generador de señales de detección 340 puede emitir una señal de detección que indica si una trama que tiene la longitud máxima de L bytes se ha detectado como una trama que se va a detectar.

Por ejemplo, cuando se detecta una trama que se va a detectar, el generador de señales de detección 340 puede salir 1. Cuando la trama detectada no es una trama que se va a detectar, el generador de señales de detección 340 puede salir de 0.

Como se describió anteriormente, el circuito de detección de Ethernet 300 puede emitir una señal de detección que indica si se ha detectado o no una trama con la longitud máxima de Bytes L como una trama que se va a detectar en los datos recibidos.

El aparato de detección de Ethernet 400 puede detectar una pluralidad de tramas simultáneamente a través de una pluralidad de circuitos de detección de Ethernet 300.

De esta manera, cuando el aparato de detección de Ethernet 400 incluye un circuito de detección de Ethernet 300, el aparato de detección de Ethernet 400 puede detectar tramas Ethernet que tienen el tamaño de los bytes N\*L simultáneamente.

De conformidad con una modalidad de la presente invención, el método descrito anteriormente puede implementarse con códigos legibles por un procesador en un medio legible por un procesador que tiene un programa grabado. Los ejemplos del medio legible por un procesador pueden incluir una de ROM, RAM, CD-ROM, cintas magnéticas, discos extraíbles, y dispositivos de almacenamiento de datos ópticos, e incluyen además una implementación de tipo de onda portadora (por ejemplo, transmisión a través de Internet).

Con un aparato y método para detectar las tramas Ethernet de conformidad con las modalidades de la presente invención, las tramas Ethernet pueden detectarse a través de varias configuraciones, y por lo tanto pueden cumplirse los requerimientos de propiedades para el aparato de detección de la trama Ethernet.

- 5 De conformidad con modalidades de la presente invención, los costos de producción de los circuitos de detección de la trama Ethernet pueden reducirse y la configuración de estos puede simplificarse.

- La configuración y método descritos anteriormente no se limitan a las modalidades descritas en la descripción anterior. Una parte o la totalidad de las modalidades pueden combinarse selectivamente para permitir diversas modificaciones.

- Si bien anteriormente se han descrito modalidades preferidas de la presente invención, debe entenderse que se han presentado únicamente a modo de ejemplo, y no de limitación. Será evidente para los expertos en la técnica que pueden hacerse varias modificaciones y variaciones a la presente invención sin apartarse del espíritu y alcance de la invención como se describe en las reivindicaciones adjuntas. Por lo tanto, se pretende que la presente invención incluya modificaciones y variaciones que estén dentro del alcance de las reivindicaciones adjuntas.

15

#### **REIVINDICACIONES**

- Un circuito de detección de la trama Ethernet (300) para detectar las tramas Ethernet, que comprende: un contador de bytes recibidos (310) configurado para calcular un valor del conteo de bytes de los datos recibidos:

- una unidad de almacenamiento de patrones y máscaras (320) configurada para calcular los datos de la máscara y los datos de comparación que contienen un patrón de una trama, basado en el valor del conteo de bytes calculado;

- un comparador (330) configurado para determinar si los datos recibidos corresponden a los datos objetivo que se detectan, en base a los datos de la máscara y los datos de comparación calculados; y un generador de señales de detección (340) configurado para emitir una señal de detección correspondiente a

un resultado de la determinación; caracterizado porque,

5

15

- la unidad de almacenamiento de patrones y máscaras (320) comprende una memoria de almacenamiento de patrones y máscaras (327) configurada para almacenar un registro de máscaras para ignorar los bits que no necesitan detectarse y un registro de patrones que indica una trama que se va detectar y calcular los datos de máscara y los datos de comparación correspondientes al valor de conteo de bytes calculado, basado en el registro de máscaras y en el registro de patrones almacenados.

- 20 2. El circuito de detección de la trama Ethernet de conformidad con la reivindicación 1, en donde la memoria de almacenamiento de patrones y máscaras (327) comprende al menos una de una memoria de acceso aleatorio, RAM, una memoria de solo lectura, ROM, y una memoria flash.

- 3. El circuito de detección de la trama Ethernet de conformidad con la reivindicación 1, en donde la unidad de almacenamiento de patrones y máscaras (320) comprende: una columna de registro de máscaras (321) configurada para almacenar el registro de máscaras para ignorar los bits que no necesitan detectarse;

- un primer multiplexor, mux, (322) configurado para calcular los datos de máscara en base al registro de máscaras y al valor calculado del conteo de bytes;

- una columna de registro de patrones (323) configurada para almacenar el registro de patrones que indica que se ha detectado una trama; y un segundo mux (324) configurado para calcular los datos de comparación en base al registro de patrones y al valor del conteo de bytes calculado.

- 4. El circuito de detección de la trama Ethernet de conformidad con la reivindicación 1, en donde el comparador (330) comprende:

- un primer comparador (331) configurado para ignorar bits que no necesitan detectarse en los datos recibidos, en base a los datos de máscara calculados; y

- un segundo comparador (332) configurado para comparar los datos recibidos con los datos objetivos que se detectan, en base a los datos de comparación calculados.

Figura 1

Figura 2

Figura 3

Figura 5