# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 738 852

51 Int. Cl.:

**G05D 1/00** (2006.01) **G05B 13/02** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(96) Fecha de presentación y número de la solicitud europea: 12.02.2014 E 14154896 (6)

(97) Fecha y número de publicación de la concesión europea: 01.05.2019 EP 2770393

(54) Título: Monitor de modo común de falla oscilatoria

(30) Prioridad:

12.02.2013 US 201313765385

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 27.01.2020

(73) Titular/es:

THE BOEING COMPANY (100.0%) 100 North Riverside Plaza Chicago, IL 60606-1596, US

(72) Inventor/es:

WANG, FENFEI (BRUCE) y ASHEIM, DENNIS JON

(74) Agente/Representante:

CARVAJAL Y URQUIJO, Isabel

#### **DESCRIPCIÓN**

Monitor de modo común de falla oscilatoria

Campo

La presente divulgación está en general relacionada con sistemas de monitor de modo común de falla oscilatoria.

#### 5 Antecedentes

10

25

30

35

50

55

Las leyes de control (CLAW) se pueden usar para realzar y mejorar la calidad de recorrido de una aeronave cuando los componentes (por ejemplo, alas, estabilizadores horizontales, etc.) de la aeronave están expuestos a fuerzas externas inestables (por ejemplo, viento o turbulencia). Uno o más sensores pueden estar acoplados a los componentes de la aeronave para detectar la presencia de estas fuerzas externas. Bajo ciertas condiciones de falla de sistema, los sensores pueden generar una señal oscilatoria errónea que se proporciona a un ordenador de control de vuelo de la aeronave. El ordenador de control de vuelo procesa la señal oscilatoria con base en una o más CLAWs para generar órdenes que controlan las operaciones de la aeronave. Procesar las señales oscilatorias con base en una o más CLAWs incluye amplificar la señal oscilatoria. Las órdenes generadas por el ordenador de control de vuelo pueden usarse para modificar o aumentar las órdenes generadas por controles operados por piloto.

Por ejemplo, una aeronave puede experimentar una variación de elevación aleatoria (por ejemplo, un aumento en altitud) debido a las fuerzas hacia arriba (por ejemplo, fuerzas de elevación) cuando las superficies de los componentes de la aeronave están expuestas a ráfaga vertical. Las fuerzas de elevación pueden ser detectadas por los sensores que se retroalimentan al ordenador de control de vuelo. Con base en la señal recibida de los sensores, el ordenador de control de vuelo puede ordenar a las superficies de control para contrarrestar las fuerzas de elevación detectadas,

dando como resultado en un recorrido más suave y más cómodo para los pasajeros a bordo de la aeronave. Sin embargo, las señales erróneas de sensor oscilatorio pueden llevar a una oscilación sostenida de superficies de control que puede producir daños por fatiga en la estructura de aeronave.

Las órdenes oscilatorias sostenidas generadas por un ordenador de control de vuelo pueden aumentar las cargas dinámicas en los componentes de una aeronave. Los componentes de aeronave pueden diseñarse para resistir un umbral de carga dinámica particular (por ejemplo, una carga de superficie admisible) durante un período de tiempo. El ordenador de control de vuelo puede monitorizar las señales de entrada de sensor para detectar fallas oscilatorias. Fallas oscilatorias indican que los componentes de la aeronave han experimentado cargas dinámicas en o por encima de los umbrales de carga dinámica durante el período de tiempo. Cuando se detecta una falla oscilatoria, el ordenador de control de vuelo puede desactivar las CLAW afectadas, eliminando las cargas dinámicas inducidas en los componentes de la aeronave.

Ocurre una parada falsa cuando el monitor de falla oscilatoria no puede distinguir las señales de falla oscilatoria de las variaciones de señal normales que dan cuenta de todas las cargas dinámicas experimentadas por los componentes de la aeronave en tiempo real. Como tal, debido a que un monitor de falla oscilatoria no tiene en cuenta las cargas dinámicas causadas por las órdenes generadas usando ciertas CLAWs debido a problemas de paradas falsas, puede haber una condición de falla de sistema de aeronave que puede producir que las cargas dinámicas experimentadas por los componentes de la aeronave excedan el umbral de carga dinámica durante más tiempo que la duración del período de tiempo, llevando a un verdadero fallo de estructura de aeronave.

Goupil 2011 (Control Engineering Practice 19, 524-539) divulga una estrategia para detectar fallas en los componentes de sistema de aeronave civil.

40 Goupil 2010 (Control Engineering Practice 18, 1110-1119) divulga un método para la detección de fallas oscilatorias en el sistema de control de vuelo eléctrico de aeronave Airbus.

El documento US2007/0124038 A1 divulga un dispositivo de detección para estimar una posición teórica de una superficie de control y calcular la diferencia en la posición teórica y una posición real medida por un sensor. El dispositivo entonces detecta falla oscilatoria con base en esta diferencia.

#### 45 Resumen

Se divulgan realizaciones de un sistema de monitor de modo común de falla oscilatoria (OFCM). El sistema de OFCM está configurado para recibir una señal verdadera de sensores similares y una señal sintética de sensores diferentes y para procesar las señales de acuerdo con al menos una ley de control (CLAW). Las señales pueden ser procesadas por un ordenador de control de vuelo que incluye un módulo de OFCM. El módulo de OFCM puede configurarse para detectar cargas dinámicas en tiempo real experimentadas por componentes de una aeronave causadas por las órdenes de CLAW generadas en respuesta al procesamiento de señales de falla oscilatoria de modo común de sensor verdadero. El sistema de OFCM puede aislar las fallas oscilatorias de señal de sensor en cuestión antes de que las cargas dinámicas inducidas excedan los límites de diseño y eliminar la ocurrencia de paradas falsas para una o más CLAWs (por ejemplo, una CLAW de supresión de ráfaga vertical) y mejorar la calidad de recorrido y seguridad de pasajeros que viajan a bordo de una aeronave que incluye el sistema de OFCM.

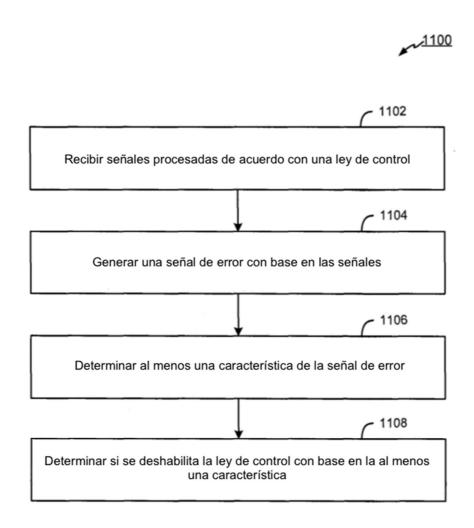

En una realización, un método incluye recibir señales procesadas de acuerdo con una ley de control (CLAW) y generar una señal de error con base en las señales. El método incluye determinar al menos una característica de la señal de error y determinar si se deshabilita la CLAW con base en la al menos una característica.

En otra realización, un sistema incluye un procesador, un módulo de demodulación, un módulo de gestión de detección, y un módulo de monitorización. El módulo de demodulación puede ser ejecutable por el procesador para recibir señales procesadas de acuerdo con una ley de control (CLAW) y para generar una señal de error con base en las señales. El módulo de gestión de detección puede ser ejecutable por el procesador para determinar al menos una característica de la señal de error y calcular los parámetros de monitorización en tiempo real. El módulo de monitorización ejecutable por el procesador para determinar si se deshabilita la CLAW con base en la al menos una característica.

En otra realización, un medio de almacenamiento legible por ordenador incluye instrucciones que, cuando son ejecutadas por un procesador, producen que el procesador reciba señales procesadas de acuerdo con una ley de control (CLAW). El medio de almacenamiento legible por ordenador también incluye instrucciones que, cuando son ejecutadas por el procesador, producen que el procesador genere una señal de error con base en las señales. El medio de almacenamiento legible por ordenador también incluye instrucciones que, cuando son ejecutadas por el procesador, producen que el procesador determine al menos una característica de la señal de error. El medio de almacenamiento legible por ordenador también incluye instrucciones que, cuando son ejecutadas por el procesador, producen que el procesador determine si se deshabilita la CLAW con base en la al menos una característica.

Breve descripción de los dibujos

20

5

10

15

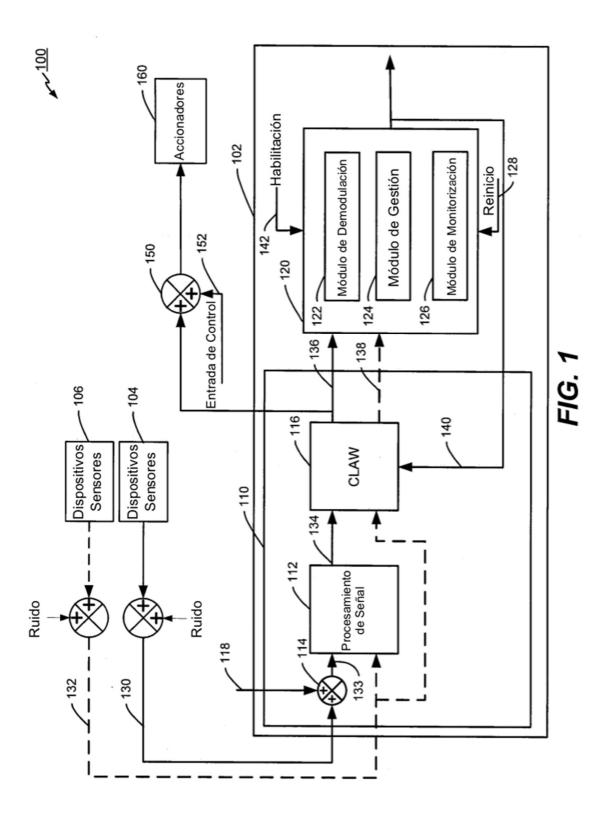

La figura 1 es una realización ilustrativa de un sistema que incluye un ordenador de control de vuelo configurado para realizar una monitorización de modo común de falla oscilatoria;

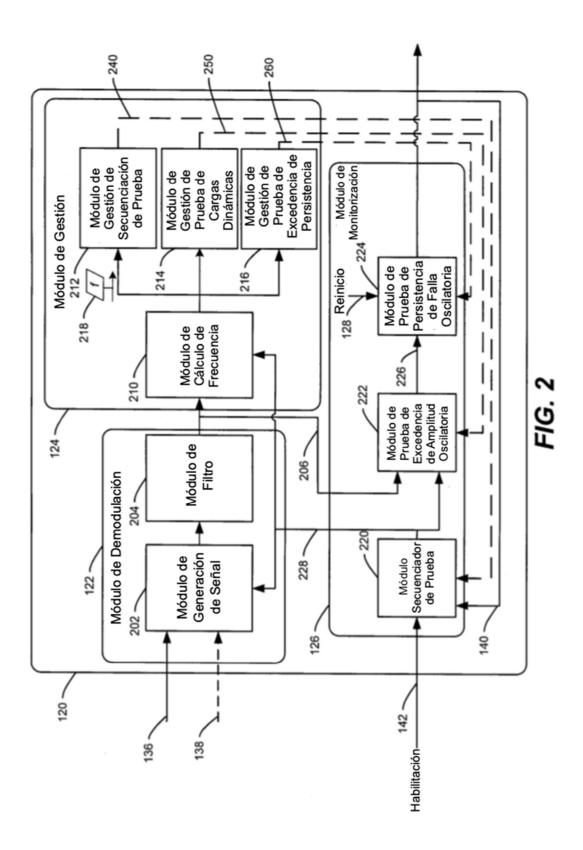

La figura 2 es una realización ilustrativa del módulo de OFCM de la figura 1;

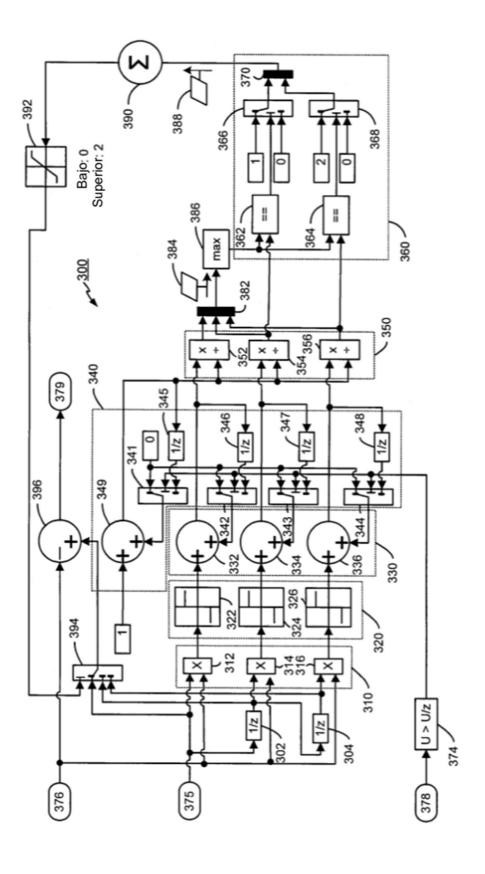

La figura 3 es una realización ilustrativa de lógica de generación de señal configurada para generar una señal de error;

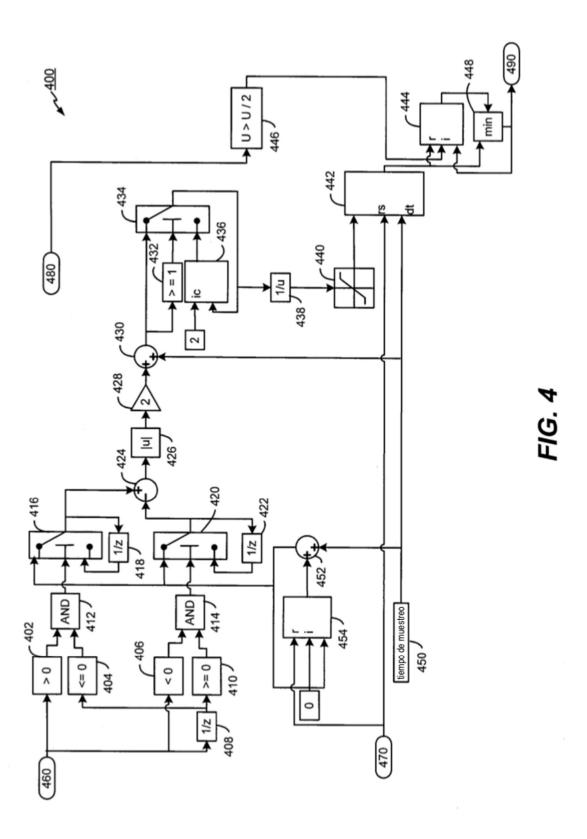

La figura 4 es una realización ilustrativa de lógica configurada para determinar una frecuencia de una señal de error usando un método de cruce por cero;

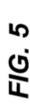

La figura 5 es una realización ilustrativa de lógica configurada para generar una señal de sincronización de prueba;

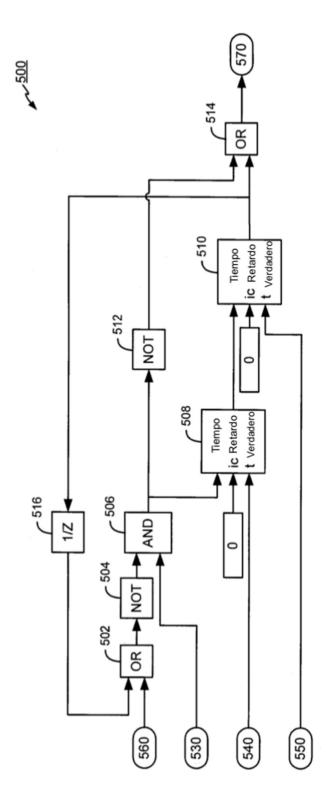

La figura 6 es una realización ilustrativa de lógica configurada para generar una señal de falla de cerrojo;

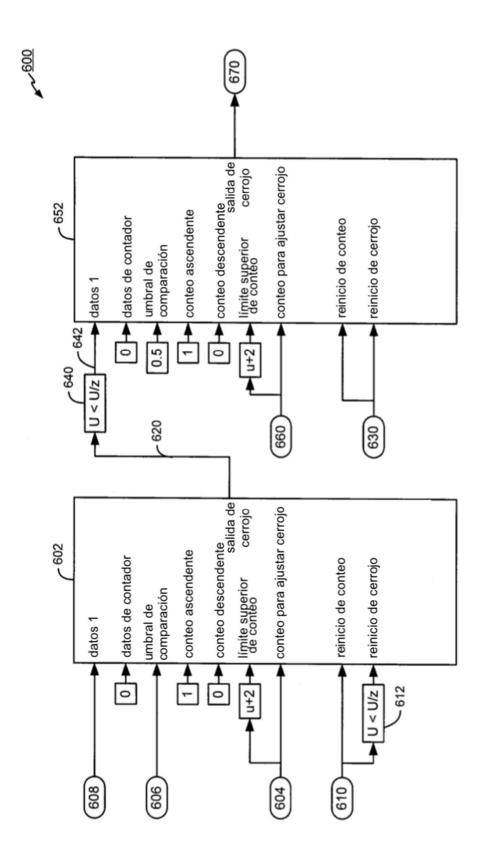

La figura 7 es una realización ilustrativa de una señal de control generada por un módulo de gestión de secuenciación de prueba;

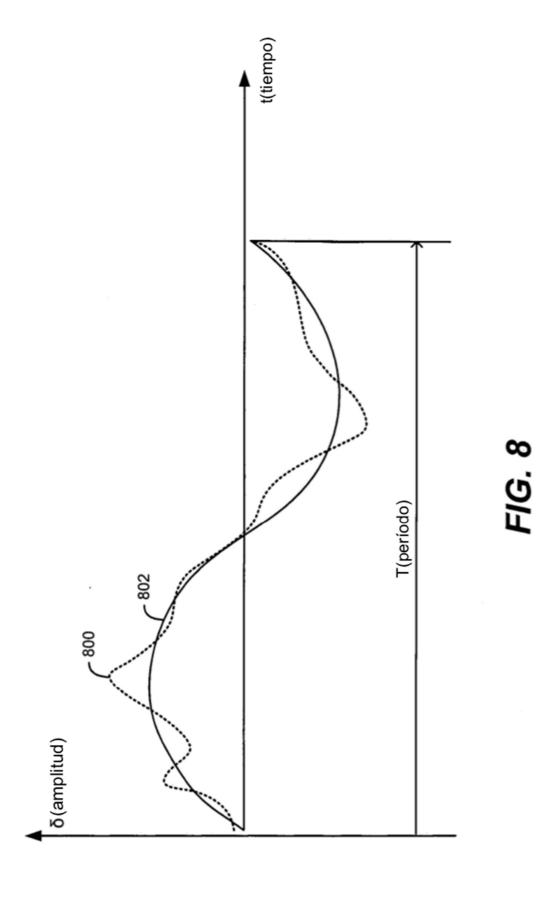

La figura 8 es una realización ilustrativa de una señal de error y una forma de onda que es una forma de onda equivalente a energía de la señal de error;

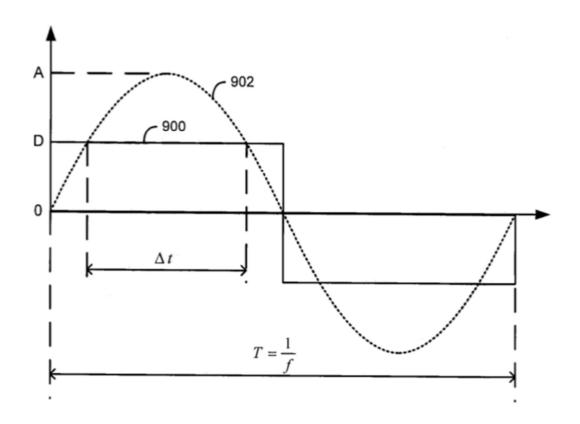

La figura 9 es una realización ilustrativa de una forma de onda cuadrada equivalente a energía y una curva de frecuencia;

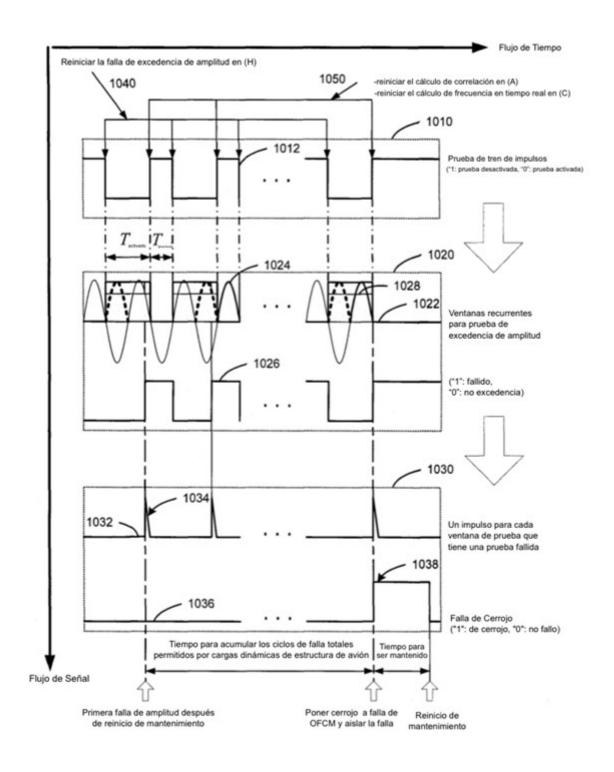

La figura 10 es un diagrama de temporización de operaciones de un módulo de monitor de modo común de falla oscilatoria (OFCM);

La figura 11 es un diagrama de flujo de un método para realizar monitorización de modo común de falla oscilatoria (OFCM);

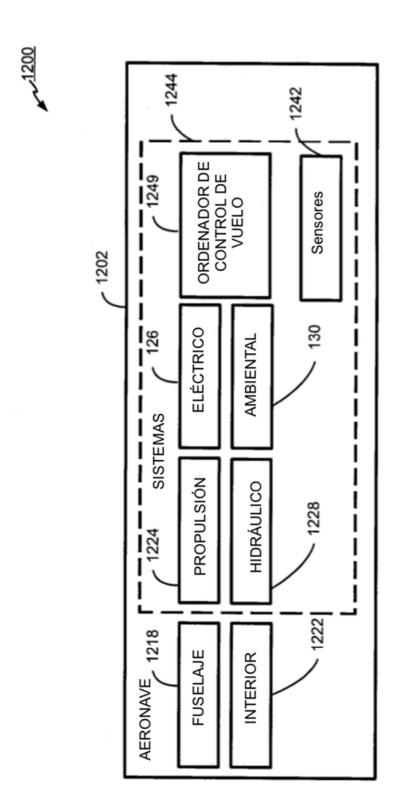

La figura 12 es una realización ilustrativa de una aeronave que incluye un ordenador de control de vuelo configurado para realizar monitorización de falla oscilatoria de acuerdo con las figuras 1-11.

Descripción detallada

45

Refiriéndose a la figura 1, se muestra una realización ilustrativa de un sistema 100 que incluye un ordenador 102 de control de vuelo configurado para realizar monitorización de modo común de falla oscilatoria. Como se muestra en la figura 1, el ordenador 102 de control de vuelo incluye un procesador 110 de señal y un módulo 120 de monitor de modo común de falla oscilatoria (OFCM). El ordenador 102 de control de vuelo puede estar acoplado a unos primeros dispositivos 104 sensores, a unos segundos dispositivos 106 sensores, y a accionadores 160. En una realización, el ordenador 102 de control de vuelo es un ordenador de control de vuelo de múltiples tasas de muestreo y el procesador 110 de señal puede operar con una primera tasa de muestreo (por ejemplo, una alta tasa de muestreo).

Los primeros dispositivos 104 sensores pueden configurarse para detectar una condición particular (por ejemplo, una carga dinámica) experimentada por un componente de aeronave particular (por ejemplo, un ala, un estabilizador vertical, un estabilizador horizontal, etc.). Cuando los dispositivos 104 sensores detectan la condición particular, los dispositivos 104 sensores pueden generar una señal 130 (por ejemplo, una señal de voltaje) indicativa de la condición particular (por ejemplo, la carga dinámica) experimentada por el componente de aeronave particular. En una realización particular, los primeros dispositivos 104 sensores pueden corresponder a un sensor de alta disponibilidad/alta integridad, tal como un ángulo de sensor de ataque. Los segundos dispositivos 106 sensores pueden generar una señal 132 (por ejemplo, una señal de voltaje). El ordenador 102 de control de vuelo puede usar la señal 132 como una señal de referencia con respecto a la señal 130. Los segundos dispositivos 106 sensores corresponden a sensores de un tipo diferente al de los dispositivos 104 sensores. Por ejemplo, los primeros dispositivos 104 sensores pueden corresponder a sensores de un primer tipo de sensor (por ejemplo, el ángulo de sensor de ataque) y los segundos dispositivos 106 sensores pueden corresponder a sensores de un segundo tipo de sensor que es diferente al del primer tipo de sensor. La señal 132 generada por los segundos dispositivos 106 sensores puede procesarse de acuerdo con un algoritmo para generar la señal de referencia (por ejemplo, la señal 132). La señal de referencia puede ser representativa de una estimación de la señal 130 generada por los dispositivos 104 sensores y puede calcularse con base en la señal 132.

10

15

20

25

45

50

55

60

Las señales 130, 132 pueden ser recibidas en el ordenador 102 de control de vuelo y proporcionarse al procesador 110 de señal. El procesador 110 de señal puede proporcionar la señal 130 a la lógica 114 de señal oscilatoria. La lógica 114 de señal oscilatoria puede configurarse para aplicar una señal 118 a la señal 130 para generar una señal 133 oscilatoria. En una realización particular, la señal 118 puede ser una señal de falla oscilatoria postulada que es ya sea intermitente o continua. Bajo condiciones particulares, la señal 118 puede anular la señal 130 para convertirse en la señal 133. Un módulo 112 de procesamiento de señal puede recibir la señal 133 oscilatoria de la lógica 114 de señal de oscilatoria y puede recibir la señal 132. El módulo 112 de procesamiento de señal procesa la señal 133 oscilatoria con base al menos en parte en la señal 132 para generar una señal 134. En una realización particular, la señal 134 corresponde a la señal 130 después de ser procesada por la lógica 114 de señal oscilatoria y el módulo 112 de procesamiento de señal. El módulo 112 de procesamiento de señal proporciona todas las selecciones de señal de entrada de sensor universal requeridas y detecciones de falla antes de que el módulo 116 de CLAW las use. El módulo 120 de OFCM está configurado para detectar la señal 118 de falla oscilatoria que el módulo 112 de procesamiento de señal no puede detectar debido a problemas de paradas falsas.

El módulo 116 de procesamiento de CLAW puede recibir la señal 134 desde el módulo 112 de procesamiento de señal. La señal 132 se puede proporcionar desde el procesador 110 de señal directamente a (es decir, sin ser procesada por el módulo 112 de procesamiento de señal) el módulo 116 de procesamiento de CLAW. El módulo 116 de procesamiento de CLAW puede generar, con base al menos en parte en la señal 134 y la señal 132, una señal 136 y una señal 138 como salida. Debido a que el módulo 116 de procesamiento de CLAW puede proporcionar características de procesamiento/acondicionamiento de señal adicionales tal como filtrado de paso de banda, límites no lineales, y lógicas de acoplamiento de función específica de condición de vuelo, etc, pasar la señal 134 y 132 a través del módulo 116 de procesamiento de CLAW puede limitar la cobertura de OFCM a las fallas oscilatorias que realmente pueden exceder los límites admisibles de cargas dinámicas. La señal 136 corresponde a la señal 130 después de ser procesada por la lógica 114 de señal oscilatoria, el módulo 112 de procesamiento de señal, y el módulo 116 de procesamiento de CLAW. La señal 138 corresponde a la señal 132 después de ser procesada por el módulo 116 de procesamiento de CLAW.

En una realización particular, el módulo 116 de procesamiento de CLAW puede estar asociado con una CLAW particular. Por ejemplo, el módulo 116 de procesamiento de CLAW se puede configurar para procesar señales (por ejemplo, las señales 132, 134) con base en una ley de control asociada con ráfaga vertical. En otra realización, el procesador 110 de señal puede incluir otros módulos de procesamiento de CLAW asociados con otras CLAW (por ejemplo, módulos de procesamiento de CLAW asociados con funciones de control de vuelo primarias, funciones de control de elevación alta, y funciones de control de vuelo automático).

La señal 136 se puede proporcionar a la lógica 150 de procesamiento. La lógica 150 de procesamiento puede corresponder a una porción de un sistema de control de vuelo por cable de la aeronave y puede generar órdenes que controlan las operaciones de los accionadores 160. En una realización, la lógica 150 de procesamiento también puede recibir una entrada 152 de control que corresponde a órdenes generadas por controles de la aeronave operada por un piloto. En esta realización, la lógica 150 de procesamiento puede agregar la señal 136 y la entrada 152 de control para generar órdenes que se proporcionan a los accionadores 160. Las órdenes pueden corresponder a órdenes configuradas para compensar los efectos de las condiciones detectadas por los dispositivos 104 sensores, los dispositivos 106 sensores, o ambos. Al contrarrestar los efectos de las condiciones experimentadas por los componentes de la aeronave, pueden aumentar las cargas dinámicas en los componentes de la aeronave. El módulo 120 de OFCM puede configurarse para monitorizar las cargas dinámicas y para detectar fallas oscilatorias (por ejemplo, detectar cuando las cargas dinámicas exceden un umbral) con base en las señales 136, 138.

Como se muestra en la figura 1, el módulo 120 de OFCM incluye un módulo 122 de demodulación, un módulo 124 de gestión, y un módulo 126 de monitorización. El módulo 120 de OFCM puede recibir las señales 136, 138 del módulo 116 de procesamiento de CLAW. El módulo 120 de OFCM puede configurarse para generar una señal 140 de falla de cerrojo con base al menos en parte en la señal 136, la señal 138, y una señal 142 de habilitación. La señal 140 de

falla de cerrojo puede ser usada por el ordenador 102 de control de vuelo para habilitar o deshabilitar selectivamente el módulo 116 de procesamiento de CLAW. Cuando se deshabilita el módulo 116 de procesamiento de CLAW, las órdenes proporcionadas a los accionadores 160 por la lógica 150 de procesamiento pueden corresponder a las órdenes recibidas desde la entrada 152 de control y no pueden modificarse con base en la señal 136 (por ejemplo, los accionadores 160 son controlados por solo la entrada 152 de control). De este modo, cuando el módulo 116 de procesamiento de CLAW se deshabilita, las cargas dinámicas experimentadas por los componentes de la aeronave pueden reducirse debido a que la señal 136 no se usa para modificar la entrada 152 de control para contrarrestar las condiciones detectadas por los dispositivos 104 sensores. Adicionalmente, debido a que la entrada 152 de control y/o ráfaga/turbulencia aerodinámica afectan a ambos dispositivos 104, 106 sensores, la diferencia entre la señal 136 y 138 es adecuadamente pequeña en comparación con los límites de carga dinámica después de que la señal se procesa en el módulo 122 de demodulación. Por lo tanto, el módulo 120 de OFCM es operable para realizar monitorización de falla oscilatoria en tiempo real mientras que reduce las paradas falsas.

5

10

15

20

25

30

35

40

45

50

55

60

Durante operación, el módulo 122 de demodulación puede configurarse para recibir las señales 136, 138 del módulo 116 de procesamiento de CLAW, y para generar una señal de error con base en las señales 136, 138. La señal de error corresponde a una diferencia entre la señal 136 y la señal 138. El módulo 122 de demodulación puede configurarse para proporcionar la señal de error al módulo 124 de gestión.

El módulo 124 de gestión puede configurarse para determinar una característica (por ejemplo, una frecuencia) de la señal de error, y para generar uno o más parámetros de monitor de detección de OFCM en tiempo real con base en la característica de la señal de error. El módulo 124 de gestión proporciona los parámetros de monitor de detección de OFCM al módulo 126 de monitorización.

El módulo 126 de monitorización se puede configurar para recibir la señal de error y los parámetros de monitor de detección de OFCM del módulo 124 de gestión y para generar la señal 140 de falla de cerrojo. La señal 140 de falla de cerrojo puede producir que el procesador 110 de señal deshabilite el módulo 116 de procesamiento de CLAW. Realizaciones ilustrativas de métodos y lógica configurados para realizar las diversas funciones del módulo 120 de OFCM, el módulo 122 de demodulación, el módulo 124 de gestión, y el módulo 126 de monitorización se describen con referencia a las figuras 2-10. De este modo, el ordenador 102 de control de vuelo que incluye el módulo 120 de OFCM puede configurarse para realizar monitorización de OFCM usando cálculos de carga dinámica en tiempo real.

Refiriéndose a la figura 2, se muestra una realización ilustrativa del módulo 120 de OFCM de la figura 1. Como se muestra en la figura 2, el módulo 120 de OFCM incluye el módulo 122 de demodulación, el módulo 124 de gestión, y el módulo 126 de monitorización. El módulo 122 de demodulación incluye un módulo 202 de generación de señal y un módulo 204 de filtro. El módulo 124 de gestión incluye un módulo 210 de cálculo de frecuencia, un módulo 212 de gestión de secuenciación de prueba, un módulo 214 de gestión de prueba de cargas dinámicas, y un módulo 216 de gestión de prueba de excedencia de persistencia. El módulo 126 de monitorización incluye un módulo 220 secuenciador de prueba, un módulo 222 de prueba de excedencia de amplitud oscilatoria, y un módulo 224 de prueba de persistencia de falla oscilatoria.

Durante operación, el módulo 120 de OFCM puede recibir las señales 136, 138 del módulo 112 de procesamiento de señal, como se describe con referencia a la figura 1. El módulo 120 de OFCM puede proporcionar las señales 136, 138 al módulo 122 de demodulación. El módulo 122 de demodulación puede proporcionar las señales 136, 138 al módulo 202 de generación de señal donde las señales 136, 138 se procesan para generar una señal 206 de error. La señal 206 de error se puede generar después de aplicar una compensación de fase de retardo de tiempo a la señal 136 y la señal 138. Una realización ilustrativa de lógica configurada para generar la señal 206 de error se describe con referencia a la figura 3.

Los retardos (por ejemplo, retardos de transporte) pueden introducirse en las señales (por ejemplo, las señales 136, 138) antes de que las señales sean recibidas en el módulo 120 de OFCM. Debido a la naturaleza asíncrona de procesamiento de señal de ordenador de control de vuelo, una falla oscilatoria falsa puede llevar a las paradas falsas durante OFCM como resultado de mala contiguidad de datos entre dos entradas de señal de comparación (por ejemplo, las señales 136, 138). El módulo 122 de demodulación puede configurarse para tener en cuenta los retardos al compensar una diferencia en fase de las señales (por ejemplo, una diferencia entre una fase de la señal 136 y una fase de la señal 138). Por ejemplo, el módulo 122 de demodulación se puede configurar para identificar una señal retardada particular que tiene una fase que se correlaciona con la fase de la señal 138. En una realización particular, el módulo 202 de generación de señal se puede configurar para aplicar un primer retardo de fase, un segundo retardo de fase, y un tercer retardo de fase a la señal 136 para generar una primera señal retardada, una segunda señal retardada, y una tercera señal. La primera señal retardada puede corresponder a la señal 136 que tiene un retardo cero (0), la segunda señal retardada puede corresponder a la señal 136 que tiene un primer retardo no cero, y la tercera señal retardada puede corresponder a la señal 136 que tiene un segundo retardo no cero que es distinto del primer retardo no cero. En una realización particular, el primer retardo no cero puede corresponder a un retardo de tiempo de uno (1) marco de ordenador y el segundo retardo no cero puede corresponder a un retardo de tiempo de dos (2) marcos de ordenador.

El módulo 122 de demodulación puede usar una correlación lineal para identificar cuál de las señales retardadas (por ejemplo, la primera señal retardada, la segunda señal retardada, y la tercera señal retardada) tiene una fase que

coincide más de cerca a la señal 138 (por ejemplo, la fase de la señal de referencia). La correlación lineal se puede determinar de acuerdo con la siguiente ecuación:

$$\gamma_{xy} = \frac{1}{N-1} \sum_{i=1}^{N} \text{señal}(x_i y_i)$$

EQ-1

En la ecuación 1 (EQ-1), γ<sub>xy</sub> corresponde a una correlación lineal entre la señal de referencia (por ejemplo, la señal 138) y una señal retardada particular (por ejemplo, una de la primera señal retardada, la segunda señal retardada, y la tercera señal retardada), N corresponde a un número de marcos (por ejemplo, muestras de las señales 136, 138) muestreadas por el módulo 122 de demodulación en un período de tiempo, x<sub>i</sub> corresponde a un valor con signo (por ejemplo, +1, 0, -1) representativo de la señal 136, y y<sub>i</sub> corresponde a un valor con signo (por ejemplo, +1, 0, -1) representativo de la señal 138. El módulo 122 de demodulación puede calcular γ<sub>xy</sub> para cada tiempo de marco para determinar cual de las señales retardadas tiene una diferencia de fase más pequeña en relación con la señal 138.

5

10

15

20

25

35

40

45

50

55

Por ejemplo, cuando la fase de una señal retardada particular (por ejemplo, una de la primera señal retardada, la segunda señal retardada, y la tercera señal retardada) está en sincronización con la fase de la señal 138, el valor de  $\gamma_{xy}$  será mayor que cuando las fases de la señal retardada particular y la señal 138 están fuera de sincronización. Para ilustrar, cuando las fases están en sincronización, los valores con signo de  $x_iy_i$  serán cero (0) o positivos (+1). Cuando las fases están fuera de sincronización, los valores con signo de  $x_iy_i$  pueden ser cero (0), uno positivo (+1), o uno negativo (-1). Con el tiempo, el valor de  $\gamma_{xy}$  para una señal retardada particular aumentará constantemente cuando las fases se sincronicen debido a que no habrá valores negativos, mientras que, con el tiempo, el valor de  $\gamma_{xy}$  para otras señales retardadas particulares puede disminuir periódicamente cuando las fases están fuera de sincronización debido a la posibilidad de que  $x_iy_i$  tenga un valor de uno negativo (-1). De este modo, la correlación lineal puede determinarse al seleccionar la señal retardada particular que tiene el valor más alto de  $\gamma_{xy}$  después de muestrear N marcos para cada una de las señales 136 retardadas.

Después de identificar la señal retardada particular que tiene una fase que se correlaciona más de cerca con una fase de la señal 138, el módulo 202 de generación de señal puede configurarse para determinar una diferencia entre la señal 138 y la señal retardada particular. El módulo 202 de generación de señal puede configurarse para generar la señal 206 de error con base en la diferencia entre la señal 138 y la señal retardada particular. El módulo 122 de demodulación puede configurarse para proporcionar la señal 206 de error desde el módulo 202 de generación de señal al módulo 204 de filtro. Una realización ilustrativa de lógica configurada para resolver la EQ-1 y para generar la señal de error se describe con referencia a la figura 3.

Para mejorar la relación señal a ruido y mejorar la eficacia de OFCM, se puede aplicar un filtro de paso de banda en el módulo 204 de filtro si es necesario. En una realización, el módulo 204 de filtro puede ser un filtro de paso alto o un filtro de lavado o un paso a través del mismo si la CLAW hace todo el filtrado de señal requerido.

En una realización particular, el módulo 122 de demodulación puede no incluir el módulo 204 de filtro. Por ejemplo, cuando el módulo 116 de procesamiento de CLAW de la figura 1 incluye un filtro (por ejemplo, un filtro de paso alto o un filtro de lavado), el módulo 122 de demodulación puede no incluir el módulo 204 de filtro o el módulo 204 de filtro puede ser un tipo diferente de filtro (por ejemplo, un filtro a través del mismo). Después de filtrar la señal 206 de error en el módulo 204 de filtro, el módulo 122 de demodulación puede configurarse para proporcionar la señal 206 de error al módulo 124 de gestión y al módulo 126 de monitorización.

El módulo 124 de gestión se puede configurar para recibir la señal 206 de error del módulo 122 de demodulación y para proporcionar la señal 206 de error al módulo 210 de cálculo de frecuencia. El módulo 210 de cálculo de frecuencia se puede configurar para determinar una frecuencia 218 con base en la señal 206 de error. En una realización particular, la frecuencia 218 puede corresponder a una curva de señal u oscilatoria representativa de la frecuencia 218. Una realización ilustrativa de la curva de señal representativa de la frecuencia 218 se describe con referencia a la figura 9. En una realización particular, el módulo 210 de cálculo de frecuencia puede determinar la frecuencia 218 de la señal 206 de error usando un método de cruce por cero. Una realización ilustrativa de lógica configurada para determinar una frecuencia (por ejemplo, la frecuencia 218) de una señal de error (por ejemplo, la señal 206 de error) que usa el método de cruce por cero se describe con referencia a la figura 4.

El módulo 124 de gestión puede configurarse para generar una o más señales de control con base al menos en parte en la frecuencia 218. Por ejemplo, el módulo 210 de cálculo de frecuencia puede configurarse para proporcionar la frecuencia 218 de la señal 206 de error al módulo 212 de gestión de secuenciación de prueba, al módulo 214 de gestión de prueba de cargas dinámicas, y al módulo 216 de gestión de prueba de excedencia de persistencia. El módulo 212 de gestión de secuenciación de prueba puede configurarse para recibir la frecuencia 218 desde el módulo 210 de cálculo de frecuencia y para generar un parámetro 240 de monitor de detección de OFCM con base en la frecuencia. En una realización particular, el parámetro 240 de monitor de detección de OFCM puede designar o definir una ventana de prueba de excedencia de amplitud que es usada por el módulo 126 de monitorización para iniciar la prueba de excedencia de cargas dinámicas. El parámetro 240 de monitor de detección de OFCM puede determinarse

con base en la frecuencia (/) 218 recibida del módulo 210 de cálculo de frecuencia de acuerdo con la siguiente ecuación:

$$T_{

m activado} = rac{N_{

m activado}}{f}$$

$T_{

m desactivado} = rac{N_{

m desactivado}}{f}$

5

10

15

35

EQ-2

En la ecuación 2 (EQ-2), Nactivado representa un número de ciclos de la señal 206 de error para ser probados dentro de cada ventana de prueba de excedencia de amplitud, y N<sub>desactivado</sub> representa un número de ciclos de la señal 206 de error que no se deben probar dentro de cada ventana de prueba de excedencia de amplitud. En una realización particular, las variables Nactivado y Ndesactivado pueden ser valores preconfigurados determinados con base en parámetros de diseño del módulo 120 de OFCM, el módulo 116 de procesamiento de CLAW, los componentes de la aeronave, los dispositivos 104 sensores, los segundos dispositivos 106 sensores, o una combinación de los mismos. La variable f corresponde a la frecuencia 218 determinada por el módulo 210 de cálculo de frecuencia. La ventana de prueba de excedencia de amplitud corresponde a Tactivado + Tdesactivado. En EQ-6, Tactivado corresponde a una cantidad de tiempo en la que se debe realizar la monitorización de falla oscilatoria y T<sub>desactivado</sub> corresponde a una cantidad de tiempo dentro de la ventana de prueba de excedencia de amplitud en la que no se debe realizar la monitorización de falla oscilatoria. Para ilustrar, cuando el parámetro 240 de monitor de detección de OFCM corresponde a Tactivado el módulo 126 de monitorización realiza monitorización de falla oscilatoria y cuando el parámetro 240 de monitor de detección de OFCM corresponde a T<sub>desactivado</sub> el módulo 126 de monitorización realiza monitorización de falla oscilatoria. El módulo 212 de gestión de secuenciación de prueba puede configurarse para proporcionar el parámetro 240 de monitor de detección de OFCM al módulo 126 de monitorización.

El módulo 214 de gestión de prueba de cargas dinámicas puede configurarse para recibir la frecuencia 218 del módulo 20 210 de cálculo de frecuencia y para generar un parámetro 250 de monitor de detección de OFCM con base en la frecuencia 218. Por ejemplo, el módulo 214 de gestión de prueba de cargas dinámicas puede generar el parámetro 250 de monitor de detección de OFCM de acuerdo con las siguientes ecuaciones:

$$A_{(0-p)} = \frac{\pi}{2 \cdot T} \cdot \int_0^T |\delta(t)| \cdot dt$$

EO-3

En la ecuación 3 (EQ-3), A<sub>(0-p)</sub> corresponde a una amplitud de pico 0 de una señal sinusoidal equivalente a energía 25 con la misma frecuencia como de la frecuencia 218, T corresponde a un período de la frecuencia 218, δ(t) corresponde a una amplitud real de la señal 206 de error en un tiempo t, y dt corresponde a un cambio en tiempo t. Debido a que la frecuencia 218 es conocida, el período (T) puede determinarse al dividir uno (1) por la frecuencia 218. En una realización particular, la amplitud A puede indicar un límite admisible de carga dinámica. El umbral (D) de amplitud de falla oscilatoria de OFCM se puede determinar usando EQ-4 para detectar todas las formas de onda arbitrarias de la 30 señal 206 de error que pueden transportar una energía igual a o mayor que la señal sinusoidal equivalente a energía definida de cargas dinámicas.

$$D = \frac{2}{\pi} \cdot A$$

EQ-4

En la ecuación 4 (EQ-4), el umbral D de amplitud de falla oscilatoria de OFCM corresponde a una amplitud de pico 0 de la forma de onda cuadrada equivalente a energía y A corresponde a la salida derivada usando EQ-3 (es decir, un valor de A<sub>(0-p)</sub>). El umbral D de amplitud de falla oscilatoria de OFCM y la amplitud A de pico 0 pueden usarse para generar el parámetro 250 de monitor de detección de OFCM usando la siguiente ecuación:

$$\begin{aligned} \text{conteo\_de\_amplitud\_para\_ajustar\_el\_cerrojo} &= & \operatorname{piso} \left( \frac{N_{\text{activado}}}{ts} \right) \\ &= & \operatorname{piso} \left( \frac{N_{\text{activado}}}{ts} \left( T - 4 \cdot \left| \frac{T}{2 \cdot \pi} \cdot \operatorname{sen}^{-1} \left( \frac{D}{A} \right) \right| \right) \right) \\ &= & \operatorname{piso} \left( 0.5607 \cdot \frac{N_{\text{activado}}}{f} \cdot \frac{f_s}{s} \right) \end{aligned}$$

EO-5

EQ-5

En la ecuación 5 (EQ-5), N<sub>activado</sub> corresponde al N<sub>activado</sub> descrito con referencia al módulo 212 de gestión de secuenciación de prueba, A corresponde a la salida derivada usando EQ-3 (por ejemplo, A<sub>(0-p)</sub>), D corresponde a la salida derivada usando EQ-4, ts corresponde a una tasa de muestreo (en segundos), y fs = 1/ts. La salida de EQ-5 (por ejemplo, el conteo\_de\_amplitud\_para\_ajustar\_el\_cerrojo) puede corresponder a un número de umbral de ocasiones en las que las cargas dinámicas indicadas por la señal 206 de error pueden exceder un umbral de carga dinámica (es decir, un número de umbral de pruebas de falla oscilatoria fallidas). Los parámetros 250 de monitor de detección de OFCM pueden corresponder a la salida de EQ-3 y EQ-5 y pueden proporcionarse al módulo 222 de prueba de excedencia de amplitud oscilatoria para uso en la determinación de si se establece un indicador que indique que el número de ciclos de la señal 206 de error cubierta por una ventana de prueba de OFCM ha excedido los límites de amplitud de cargas dinámicas. Como se puede ver en EQ-5, la salida de EQ-5 se puede determinar con base en una constante (por ejemplo, 0.5607), el valor de N<sub>activado</sub>, la frecuencia (f) (por ejemplo, la frecuencia 218), y el valor de ts. En una realización particular, el valor de la constante, el valor de N<sub>activado</sub>, y el valor de ts pueden predeterminarse con base en un diseño y configuración particulares de un ordenador de control de vuelo (por ejemplo, el ordenador 102 de control de vuelo de la figura 1).

10

40

45

50

55

El módulo 216 de gestión de prueba de excedencia de persistencia se puede configurar para recibir la frecuencia 218 del módulo 210 de cálculo de frecuencia y para generar un parámetro 260 de monitor de detección de OFCM. El módulo 216 de gestión de prueba de excedencia de persistencia puede configurarse para generar el parámetro 260 de monitor de detección de OFCM con base en la siguiente ecuación:

$${\tt conteo\_de\_persistencia\_para\_ajustar\_el\_cerrojo} = \frac{N_{\tt cargas}}{N_{\tt activado} + N_{\tt desactivado}} \\ = \frac{1}{N_{\tt cargas}} \\ = \frac{1$$

20 En la ecuación 6 (EQ-6), N<sub>cargas</sub> corresponde a un número máximo de ciclos permitidos para exceder la carga dinámica admisible indicada por el parámetro 250 de monitor de detección de OFCM. Nactivado y Ndesactivado corresponden al Ndesactivado como se describe con referencia а EQ-3. conteo\_de\_persistencia\_para\_ajustar\_el\_cerrojo de EQ-6 puede corresponder al número de ventanas de prueba de OFCM que están permitidas para exceder el umbral de carga dinámica antes de que sea apagado un módulo de 25 procesamiento de CLAW (por ejemplo, el módulo 116 de procesamiento de CLAW de la figura 1). El \*\*\* módulo 216 de gestión de prueba de excedencia de persistencia puede configurarse para proporcionar el parámetro 260 de monitor de detección de OFCM que indica el número de ciclos permitidos para exceder el umbral de carga dinámica al módulo 126 de monitorización para uso en la generación de la señal 140 de falla de cerrojo.

El módulo 126 de monitorización puede configurarse para determinar si se deshabilita el módulo 116 de procesamiento de CLAW. Por ejemplo, el módulo 126 de monitorización puede recibir la señal 206 de error, la señal 142 de habilitación, y los parámetros de monitor de detección de OFCM (por ejemplo, los parámetros 240, 250, 260 de monitor de detección de OFCM). Con base en la señal 206 de error, la señal 142 de habilitación, y los parámetros 240, 250, 260 de monitor de detección de OFCM, el módulo 126 de monitorización puede generar una señal 140 de falla de cerrojo. La señal 140 de falla de cerrojo se puede usar para habilitar o deshabilitar el módulo 116 de procesamiento de CLAW.

Como se muestra en la figura 2, el módulo 126 de monitorización incluye un módulo 220 secuenciador de prueba, un módulo 222 de prueba de excedencia de amplitud oscilatoria, y un módulo 224 de prueba de persistencia de falla oscilatoria. El módulo 220 secuenciador de prueba puede configurarse para generar una señal 228 de sincronización con base en el parámetro 240 de monitor de detección de OFCM, la señal 140 de falla de cerrojo, y la señal 142 de habilitación. En una realización particular, la señal 142 de habilitación puede ser un indicador que puede establecerse en uno de un primer valor (por ejemplo, un uno (1)) y un segundo valor (por ejemplo, un cero (0)). El módulo 126 de monitorización se puede encender o apagar con base en la señal 142 de habilitación o la señal 140 de falla de cerrojo. Por ejemplo, cuando la señal 142 de habilitación es el segundo valor (por ejemplo, un cero (0)) o la señal 140 de falla de cerrojo es uno (1), el módulo 220 secuenciador de prueba se puede apagar y puede no generar la señal 228 de sincronización. Cuando la señal 142 de habilitación es el primer valor (por ejemplo, un uno (1)) y la señal 140 de falla de cerrojo es un cero (0), el módulo 220 secuenciador de prueba se puede encender y puede generar la señal 228 de sincronización. El módulo 220 de secuenciador de prueba puede generar la señal 228 de sincronización de falla oscilatoria (es decir, cuando el módulo 116 de procesamiento de CLAW está encendido). Una realización ilustrativa de lógica configurada para generar una señal de sincronización (por ejemplo, la señal 228 de sincronización) se describe con referencia a la figura 5.

El módulo 126 de monitorización puede proporcionar la señal 228 de sincronización al módulo 122 de demodulación y el módulo 124 de gestión. El módulo 122 de demodulación puede proporcionar la señal 228 de sincronización al módulo 202 de generación de señal para uso en la generación de la señal 206 de error. El módulo 124 de gestión puede proporcionar la señal 228 de sincronización al módulo 210 de cálculo de frecuencia para uso en la determinación de la frecuencia 218. Se describen realizaciones ilustrativas del uso de la señal 228 de sincronización para generar la señal 206 de error y para determinar la frecuencia 218 con referencia a las figuras 3 y 4.

El módulo 126 de monitorización puede configurarse para proporcionar la señal 228 de sincronización desde el módulo 220 secuenciador de prueba hasta el módulo 222 de prueba de excedencia de amplitud oscilatoria. El módulo 222 de prueba de excedencia de amplitud oscilatoria puede configurarse para generar un tren de impulsos 226 de falla con base en la señal 228 de sincronización, la señal 206 de error, y el parámetro 250 de monitor de detección de OFCM. Cada vez que la carga dinámica experimentada por los componentes de la aeronave (por ejemplo, la carga dinámica indicada por la señal 206 de error) excede el umbral de carga dinámica (por ejemplo, el umbral de carga dinámica indicado por el parámetro 250 de monitor de detección de OFCM) durante una ventana de excedencia de amplitud, el módulo 222 de prueba de excedencia de amplitud oscilatoria puede configurarse para generar un impulso en el tren de impulsos 226 de falla. El módulo 222 de prueba de excedencia de amplitud oscilatoria. Una realización ilustrativa de lógica configurada para realizar las funciones del módulo 222 de prueba de excedencia de amplitud oscilatoria se describe con referencia a la figura 6.

El módulo 224 de prueba de persistencia de falla oscilatoria puede configurarse para recibir el tren de impulsos 226 de falla y el parámetro 260 de monitor de detección de OFCM del módulo 216 de gestión de prueba de excedencia de persistencia. El módulo 224 de prueba de persistencia de falla oscilatoria puede generar la señal 140 de falla de cerrojo con base en el tren de impulsos 226 de falla y el parámetro 260 de monitor de detección de OFCM. Por ejemplo, el módulo 224 de prueba de persistencia de falla oscilatoria puede incrementar un contador cada vez que se detecta un borde delantero (por ejemplo, un borde delantero del pulso) del tren de impulsos 226 de falla (por ejemplo, cada vez que falla la prueba de carga dinámica realizada en el módulo 222 de prueba de excedencia de amplitud oscilatoria). El parámetro 260 de monitor de detección de OFCM puede indicar un número máximo de ciclos infractores (por ejemplo, el resultado de EQ-5) antes de que el módulo 116 de procesamiento de CLAW deba ser deshabilitado (por ejemplo, la señal 140 de falla de cerrojo se establece en uno (1)). Cuando el valor de contador excede el número máximo de ciclos infractores indicados por el parámetro 260 de monitor de detección de OFCM, el módulo 224 de prueba de persistencia de falla oscilatoria 224 puede establecer el valor de la señal 140 de falla de cerrojo en uno (1), produciendo que el módulo 116 de procesamiento de CLAW sea deshabilitado.

El módulo 120 de OFCM puede eliminar o reducir la ocurrencia de paradas falsas debido a que el módulo 120 de OFCM está configurado para tener en cuenta, en tiempo real o casi en tiempo real, todas las cargas dinámicas experimentadas por los componentes de la aeronave que realmente exceden los limites admisibles de cargas dinámicas. Por ejemplo, como un resultado de generar la señal 206 de error después de que la señal 130 se procesa de acuerdo con la una o más CLAWs (por ejemplo, en el módulo 116 de procesamiento de CLAW), el módulo 120 de OFCM es operable para tener en cuenta las cargas dinámicas adicionales causadas por las órdenes enviadas a los accionadores 160 desde el módulo 116 de procesamiento de CLAW durante la prueba de excedencia de cargas dinámicas.

Refiriéndose a la figura 3, se muestra una realización ilustrativa de lógica 300 de generación de señal configurada para generar una señal de error. La figura 3 es simplemente ilustrativa de una posible implementación de la lógica 300 de generación de señal. En otras realizaciones, puede usarse diferente lógica configurada para realizar las operaciones de la lógica 300 de generación de señal. En una realización, la lógica 300 de generación de señal corresponde a o está incluida dentro del módulo 210 de cálculo de señal de la figura 2. En una realización, la lógica 300 de generación de señal puede implementarse como instrucciones almacenadas en un medio legible por ordenador (por ejemplo, una unidad de disco duro, una memoria). Las instrucciones pueden ser ejecutables por un procesador para realizar las diversas funciones descritas con referencia a la figura 3. En una realización adicional o alternativa, la lógica 300 de generación de señal puede implementarse como circuitería configurada para realizar las diversas funciones descritas con referencia a la figura 3. La circuitería puede incluir un dispositivo de arreglo de puerta programable de campo (FPGA), un circuito integrado de aplicación específica (ASIC), una unidad de procesamiento tal como una unidad de procesamiento central (CPU), un controlador, un dispositivo de firmware, u otro dispositivo de hardware configurado para realizar las diversas funciones descritas con referencia a la figura 3.

Como se muestra en la figura 3, la lógica 300 de generación de señal incluye la primera lógica 302 de retardo, segunda lógica 304 de retardo, un primer bloque 310 de procesamiento, un segundo bloque 320 de procesamiento, un tercer bloque 330 de procesamiento, un cuarto bloque 340 de procesamiento, un quinto bloque 350 de procesamiento, lógica 374 de detección de señal, un sexto bloque 360 de procesamiento, primera lógica 382 de procesamiento de datos, lógica 386 de determinación máxima, lógica 390 de suma, un limitador 392, conmutador 394, y lógica 396 de resta. El primer bloque 310 de procesamiento incluye un primer bloque 312 de multiplicación, un segundo bloque 314 de multiplicación, y un tercer bloque 316 de multiplicación. El segundo bloque 320 de procesamiento incluye la primera lógica 322 de signo, segunda lógica 324 de signo, y tercera lógica 326 de signo. El tercer bloque 330 de procesamiento incluye la primera lógica 332 de suma, segunda lógica 334 de suma, y tercera lógica 336 de suma. El cuarto bloque 340 de procesamiento incluye un primer conmutador 341, un segundo conmutador 342, un tercer conmutador 343, un cuarto conmutador 344, tercera lógica 345 de retardo, cuarta lógica 346 de retardo, quinta lógica 347 de retardo, sexta lógica 348 de retardo, y lógica 349 de suma. El quinto bloque 350 de procesamiento incluye la primera lógica 352 de división, segunda lógica 354 de división, y tercera lógica 356 de división. El sexto bloque 360 de procesamiento incluye un primer comparador 362, un segundo comparador 364, un primer conmutador 366 de salida, un segundo conmutador 368 de salida, y segunda lógica 370 de procesamiento de datos.

La lógica 300 de generación de señal puede recibir una primera señal 375 y una segunda señal 376. En una realización particular, la primera señal 375 corresponde a la señal 136 de las figuras 1 y 2 (es decir, la señal 130 después de ser procesada en el módulo 112 de procesamiento de señal y el módulo 116 de procesamiento de CLAW de la figura 2), y la segunda señal 376 corresponde a la señal 138 (por ejemplo, la señal 132 después de ser procesada en el módulo 116 de procesamiento de CLAW de la figura 1). La lógica 300 de generación de señal puede configurarse para generar una señal 379 con base en una diferencia de fase de la primera señal 375 en relación con la segunda señal 376. En una realización, la señal 379 corresponde a la señal 206 de la figura 2 (por ejemplo, la salida del módulo 122 de demodulación de las figuras 1 y 2).

Para ilustrar, la lógica 300 de generación de señal puede recibir la primera señal 375 y la segunda señal 376. La primera señal 375 puede proporcionarse a la primera lógica 302 de retardo y al primer bloque 312 de multiplicación. La primera lógica 302 de retardo puede aplicar un primer retardo a la señal 375 para generar una primera señal retardada. La primera señal retardada puede proporcionarse desde la primera lógica 302 de retardo a la segunda lógica 304 de retardo y al segundo bloque 314 de multiplicación. La segunda lógica 304 de retardo puede aplicar un segundo retardo a la primera señal retardada para generar una segunda señal retardada. La segunda señal retardada puede proporcionarse desde la segunda lógica 304 de retardo hasta el tercer bloque 316 de multiplicación.

20

25

30

35

40

45

50

55

60

En una realización particular, la primera lógica 302 de retardo y la segunda lógica 304 de retardo pueden aplicar una misma cantidad de retardo (por ejemplo, la primera señal retardada se retarda en relación con la señal 375 por la misma cantidad de retardo como la segunda señal retardada se retarda en relación con la primera señal retardada). Para ilustrar, suponer que la primera lógica 302 de retardo y la segunda lógica 304 de retardo cada una aplica un retardo de una décima de un segundo (0.1 segundos) a una señal de entrada. Cuando se recibe la señal 375 en la primera lógica 302 de retardo, la primera lógica 302 de retardo aplica el retardo de una décima de un segundo (0.1 segundos) a la señal 375 para generar la primera señal retardada. La primera señal retardada es representativa de la señal 375 retardada por una décima de un segundo (0.1 segundos). Cuando se recibe la primera señal retardada en la segunda lógica 304 de retardo de la primera lógica 302 de retardo, la segunda lógica 304 de retardo aplica el retardo de una décima de un segundo (0.1 segundos) a la primera señal retardada para generar la segunda señal retardada. De este modo, la segunda señal retardada es representativa de la señal 375 retardada por dos décimas de un segundo (0.2 segundos). El retardo de dos décimas de un segundo corresponde al retardo de una décima de un segundo (0.1 segundos) introducido por la primera lógica 302 de retardo y el retardo de una décima de un segundo (0.1 segundos) introducido por la segunda lógica 304 de retardo. La cantidad de retardo aplicado por la primera lógica 302 de retardo y la segunda lógica 304 de retardo puede ser menor que o mayor que una décima de un segundo (0.1 segundos). En otra realización, la primera lógica 302 de retardo y la segunda lógica 304 de retardo pueden aplicar diferentes cantidades de retardo a la señal 375.

La señal 376 se puede proporcionar al primer bloque 310 de procesamiento junto con la señal 375, la primera señal retardada, y la segunda señal retardada. Por ejemplo, la señal 375 y la señal 376 pueden proporcionarse al primer bloque 312 de multiplicación. La primera señal retardada (por ejemplo, la señal 375 retardada por la primera lógica 302 de retardo) y la señal 376 pueden proporcionarse al segundo bloque 314 de multiplicación, y la segunda señal retardada (por ejemplo, la señal 375 retardada por la primera lógica 302 de retardo y la segunda lógica 304 de retardo) y la señal 376 pueden proporcionarse al tercer bloque 316 de multiplicación. Las dos señales de entrada recibidas por cada uno de los bloques 312, 314, 316 de multiplicación pueden multiplicarse para producir una señal de salida.

Las señales de salida generadas por los bloques 312, 314, 316 de multiplicación pueden proporcionarse al segundo bloque 320 de procesamiento. Por ejemplo, la señal de salida generada por el primer bloque 312 de multiplicación puede proporcionarse a la primera lógica 322 de signo, la señal de salida generada por el segundo bloque 314 de multiplicación puede proporcionarse a la segunda lógica 324 de signo, y la señal de salida generada por el tercer bloque 316 de multiplicación puede proporcionarse a la tercera lógica 326 de signo. La primera lógica 322 de signo, la segunda lógica 324 de signo, y la tercera lógica 326 de signo pueden configurarse para generar valores numéricos que corresponden a las señales de salida recibidas de los bloques 312, 314, 316 de multiplicación. Por ejemplo, la primera lógica 322 de signo puede recibir la señal de salida del primer bloque 312 de multiplicación y generar un primer valor numérico asociado con la señal de salida recibida desde el primer bloque 312 de multiplicación, la segunda lógica 324 de signo puede recibir la señal de salida generada por el segundo el bloque 314 de multiplicación y generar un segundo valor numérico asociado con la señal de salida recibida del segundo bloque 314 de multiplicación, y la tercera lógica 326 de signo puede recibir la señal de salida generada por el tercer bloque 316 de multiplicación y generar un tercer valor numérico asociado con la señal de salida recibida desde el tercer bloque 316 de multiplicación. Los valores numéricos generados por la primera lógica 322 de signo, segunda lógica 324 de signo, tercera lógica 326 de signo pueden proporcionarse al tercer bloque 330 de procesamiento. En una realización particular, los valores numéricos generados por la primera lógica 322 de signo, segunda lógica 324 de signo, tercera lógica 326 de signo pueden ser uno de un uno positivo (+1), un cero (0), y un uno negativo (-1). Los valores numéricos corresponden a un signo de la salida de señal de cada uno de los bloques 312, 314, 316 de multiplicación.

Como se muestra en la figura 3, cada una de la primera lógica 332 de suma, la segunda lógica 334 de suma, y la tercera lógica 336 de suma pueden recibir el valor numérico generado por una correspondiente de la primera lógica 322 de signo, la segunda lógica 324 de signo, y la tercera lógica 326 de signo como una primera entrada y proporcionar el valor numérico al cuarto bloque 340 de procesamiento. El cuarto bloque 340 de procesamiento puede recibir los valores numéricos de la primera lógica 332 de suma, la segunda lógica 334 de suma, y la tercera lógica 336 de suma,

y, en respuesta a una señal de control generada por la lógica 374 de detección de señal, el cuarto bloque 340 de procesamiento puede proporcionar valores de entrada adicionales a la primera lógica 332 de suma, la segunda lógica 334 de suma, y la tercera lógica 336 de suma.

5

10

15

20

25

30

35

40

45

50

55

Por ejemplo, la lógica 374 de detección de señal puede configurarse para detectar un cambio en un valor de la señal 378 y para generar una señal de control que se proporciona a cada uno de los conmutadores 341, 342, 343, 344 durante una primera prueba de una señal de muestra (por ejemplo, un primer marco de la señal 375). En el inicio, cada uno de los conmutadores 341, 342, 343, 344 puede configurarse en un primer estado y proporcionar un valor cero (0) como una salida. Las salidas (por ejemplo, los valores cero (0)) se pueden proporcionar a la primera lógica 332 de suma, segunda lógica 334 de suma, tercera lógica 336 de suma como entradas adicionales y se pueden agregar a las entradas recibidas en la primera lógica 332 de suma, la segunda lógica 334 de suma, y la tercera lógica 336 de suma de la primera lógica 322 de signo, la segunda lógica 324 de signo, y la tercera lógica 326 de signo. La suma de las entradas de la primera lógica 322 de signo, segunda lógica 324 de signo, tercera lógica 326 de signo y las entradas adicionales de los conmutadores 342, 343, 344 pueden recibirse en los bloques 346, 347, 348 de lógica. La lógica 349 de suma puede recibir una primera entrada (por ejemplo, un uno (1)) y una segunda entrada del primera entrada de la lógica 349 de suma y la segunda entrada de la lógica 349 de suma puede proporcionarse a la tercera lógica 345 de retardo.

Durante una segunda prueba de una señal de muestra (por ejemplo, un segundo marco de la señal 375), la lógica 374 de detección de señal puede generar una segunda señal de control en respuesta a la detección de un cambio en el valor de la señal 378. La segunda señal de control puede proporcionarse a cada uno de los conmutadores 341, 342, 343, 344. En respuesta a la segunda señal de control, cada uno de los conmutadores 341, 342, 343, 344 puede estar con cerrojo a las salidas de los bloques 345, 346, 347, 348 de lógica de retardo, respectivamente, y pueden proporcionar los valores de los bloques 345, 346, 347, 348 de lógica de retardo a la una correspondiente de la primera lógica 332 de suma, la segunda lógica 334 de suma, la tercera lógica 336 de suma, y la lógica 349 de suma. Los valores recibidos en los bloques 345, 346, 347, 348 de lógica de retardo de la primera lógica 332 de suma, la segunda lógica 334 de suma, la tercera lógica 336 de suma, y la lógica 349 de suma corresponden a la suma determinada en la primera lógica 332 de suma, la segunda lógica 334 de suma, la tercera lógica 336 de suma, y la lógica 349 de suma con base en la muestra previa (por ejemplo, la primera muestra) de la señal (por ejemplo, el primer marco de la señal 375). De este modo, la primera lógica 332 de suma, la segunda lógica 334 de suma, la tercera lógica 336 de suma, y la lógica 349 de suma están configuradas para sumar valores durante la prueba de muestras de la señal 375 durante un período de tiempo (por ejemplo, una ventana de prueba de excedencia de amplitud). La suma determinada en la lógica 349 de suma corresponde a un número de marcos muestreados y las sumas determinadas en cada una de la primera lógica 332 de suma, la segunda lógica 334 de suma, y la tercera lógica 336 de suma corresponden a las sumas de los valores numéricos generados por la primera lógica 322 de signo, segunda lógica 324 de signo, tercera lógica 326 de signo para cada una de las señales 375 (por ejemplo, la señal 375 no retardada, la señal 375 retardada por la primera lógica 302 de retardo, y la señal 375 retardada tanto por la primera lógica 302 de retardo como la segunda lógica 304 de retardo).

Las salidas de la primera lógica 332 de suma, la segunda lógica 334 de suma, y la tercera lógica 336 de suma (por ejemplo, las sumas determinadas con base en las entradas recibidas de la primera lógica 322 de signo, la segunda lógica 324 de signo, la tercera lógica 326 de signo, y los bloques 346, 347, 348 de lógica de retardo) pueden proporcionarse, con la suma determinada por la lógica 349 de suma, al quinto bloque 350 de procesamiento. Los bloques 352, 354, 356 de lógica de división incluidos en el quinto bloque 350 de procesamiento pueden estar configurado para dividir cada una de las salidas de la primera lógica 332 de suma, la segunda lógica 334 de suma, y la tercera lógica 336 de suma por la salida de la lógica 349 de suma para generar un valor numérico promedio para cada una de las señales muestreadas (por ejemplo, la señal 375 no retardada, la señal 375 retardada por la primera lógica 302 de retardo, y la señal 375 retardada tanto por la primera lógica 302 de retardo como por la segunda lógica 304 de retardo). Como se describe con referencia a la figura 2, cuando una señal retardada particular (por ejemplo, la señal 375, la señal retardada por la primera lógica 302 de retardo y la segunda lógica 304 de retardo) está en sincronización con la señal 376, la suma de los valores numéricos (por ejemplo, la suma determinada en una de la primera lógica 332 de suma, la segunda lógica 334 de suma, o la tercera lógica 336 de suma que corresponde a la señal retardada particular) será mayor que cuando la señal particular y la señal 376 están fuera de sincronización.

Las salidas del quinto bloque 350 de procesamiento pueden proporcionarse a la primera lógica 382 de procesamiento de datos. La primera lógica 382 de procesamiento de datos puede configurarse para generar un vector 384 que incluya cada uno de los valores promedio determinados en los bloques 352, 354, 356 de lógica de división y para proporcionar el vector 384 a la lógica 386 de determinación máxima. La lógica 386 de determinación máxima se puede configurar para determinar un valor promedio máximo con base en los valores promedio incluidos en el vector 384. La lógica 386 de determinación máxima puede proporcionar el valor promedio máximo al sexto bloque 360 de procesamiento.

El sexto bloque 360 de procesamiento puede configurarse para recibir el valor promedio máximo de la lógica 386 de determinación máxima y los valores numéricos promedio generados en la lógica 354 de división y la lógica 356 de división. El sexto bloque 360 de procesamiento puede configurarse para determinar si la señal 375 o una de las señales 375 retardadas (por ejemplo, la señal 375 retardada por la primera lógica 302 de retardo y la señal 375 retardada por

la segunda lógica 304 de retardo) está en sincronización con la señal 376 con base en el valor promedio máximo y los valores numéricos promedio recibidos de la lógica 354 de división y la lógica 356 de división.

Por ejemplo, el valor numérico determinado por la lógica 354 de división puede proporcionarse a un primer comparador 362 y compararse con el valor promedio máximo determinado en la lógica 386 de determinación máxima. Cuando la comparación indica que el valor promedio máximo es igual al valor numérico determinado por la lógica 354 de división, el primer comparador 362 puede generar una primera señal que produce que el primer conmutador 366 de salida proporcione una primera salida (por ejemplo, un uno (1)) a la segunda lógica 370 de procesamiento de datos. Cuando la comparación indica que el valor promedio máximo no es igual al valor numérico determinado por la lógica 354 de división, el primer comparador 362 puede generar una segunda señal que produce que el primer conmutador 366 de salida proporcione una segunda salida (por ejemplo, un cero (0)) a la segunda lógica 370 de procesamiento de datos. El valor numérico determinado por la lógica 356 de división puede proporcionarse al segundo comparador 364 y compararse con el valor promedio máximo determinado en la lógica 386 de determinación máxima. Cuando la comparación indica que el valor promedio máximo es igual al valor numérico determinado por la lógica 356 de división, el segundo comparador 364 puede generar una primera señal que produce que el segundo conmutador 368 de salida proporcione una primera salida (por ejemplo, un dos (2)) a la segunda lógica 370 de procesamiento de datos. Cuando la comparación indica que el valor promedio máximo no es igual al valor numérico determinado por la lógica 356 de división, el segundo comparador 364 puede generar una segunda señal que produce que el segundo conmutador 368 de salida proporcione una segunda salida (por ejemplo, un cero (0)) a la segunda lógica 370 de procesamiento de datos.

5

10

15

35

60

20 La segunda lógica 370 de procesamiento de datos puede generar un segundo vector 388 que incluye la salida de valores mediante los conmutadores 366, 368 de salida. El segundo vector 388 puede recibirse en lógica 390 de suma donde los dos valores incluidos en el segundo vector 388 se agregan juntos para formar una salida que se proporciona al limitador 392. El limitador 392 se puede configurar para unir el valor recibido de la lógica 390 de suma entre un umbral superior (por ejemplo, dos (2)) y un umbral inferior (por ejemplo, cero (0)). En una realización particular, los 25 umbrales superior e inferior pueden determinarse con base en un número de señales procesadas por la lógica 300 de generación de señal. Por ejemplo, en la figura 3, tres (3) señales son procesadas por la lógica 300 de generación de señal. La primera señal corresponde a la señal 375 con retardo cero (0), la segunda señal corresponde a la señal 375 con el primer retardo (por ejemplo, el retardo aplicado por la primera lógica 302 de retardo), y la tercera señal corresponde a la señal 375 con el segundo retardo (por ejemplo, el retardo aplicado por la segunda lógica 304 de 30 retardo). La salida (por ejemplo, el valor unido) del limitador 392 puede indicar cual de las señales retardadas (por ejemplo, la primera señal retardada, la segunda señal retardada, o la tercera señal retardada) se debe usar para generar la señal 379 de error.

Para ilustrar, la salida del limitador 392 puede proporcionarse como una entrada de control al conmutador 394. El conmutador 394 puede configurarse para proporcionar una de la primera señal retardada (por ejemplo, la señal 375), la segunda señal retardada (por ejemplo, la señal 375 retardada por la primera lógica 302 de retardo), y la tercera señal retardada (por ejemplo, la señal 375 retardada por la primera lógica 302 de retardo y la segunda lógica 304 de retardo) a la lógica 396 de resta. La lógica 396 de resta puede restar la señal 376 de la señal recibida desde el conmutador 394 para generar una señal 379 de error. En una realización particular, la señal 379 de error corresponde a la señal 206 de error de la figura 2.

De este modo, la lógica 300 de generación de señal está configurada para recibir una primera señal y una segunda señal y generar una señal de error con base en una diferencia entre la primera señal y la segunda señal. Adicionalmente, la lógica 300 de generación de señal está configurada para determinar una cantidad de retardo para aplicar a la primera señal para sincronizar la primera señal con la segunda señal antes de determinar la diferencia entre la primera señal y la segunda señal.

45 Refiriéndose a la figura 4, se muestra una realización ilustrativa de lógica 400 configurada para determinar una frecuencia de una señal de error usando un método de cruce por cero. La figura 4 es simplemente ilustrativa de una posible implementación de la lógica 400. En otras realizaciones, se puede usar diferente lógica configurada para realizar las operaciones de la lógica 400. En una realización, la lógica 400 puede corresponder a o está incluida dentro del módulo 210 de cálculo de frecuencia de la figura 2. En una realización, la lógica 400 puede implementarse como 50 instrucciones almacenadas en un medio legible por ordenador (por ejemplo, una unidad de disco duro, una memoria). Las instrucciones pueden ser ejecutables por un procesador para realizar las diversas funciones descritas con referencia a la figura 4. En una realización adicional o alternativa, la lógica 400 puede implementarse como circuitería configurada para realizar las diversas funciones descritas con referencia a la figura 4. La circuitería puede incluir un dispositivo de arreglo de puerta programable de campo (FPGA), un circuito integrado de aplicación específica (ASIC), 55 una unidad de procesamiento tal como una unidad de procesamiento central (CPU), un controlador, un dispositivo de firmware, u otro dispositivo de hardware configurado para realizar las diversas funciones descritas con referencia a la figura 4.

Como se muestra en la figura 4, la lógica 400 incluye la primera lógica 402 de comparación, segunda lógica 404 de comparación, tercera lógica 406 de comparación, primera lógica 408 de retardo, cuarta lógica 410 de comparación, un primer bloque 412 de lógica AND, un segundo bloque 414 de lógica AND, un primer conmutador 416, segunda lógica 418 de retardo, un segundo conmutador 420, tercera lógica 422 de retardo, lógica 424 de diferencia, un bloque

426 de lógica de valor absoluto, un multiplicador 428, lógica 430 de suma, quinta lógica 432 de comparación, un tercer conmutador 434, primera lógica 436 de procesamiento, lógica 438 de determinación de frecuencia, un limitador 440, segunda lógica 442 de procesamiento, tercera lógica 444 de procesamiento, un detector 446 de señal, lógica 448 de determinación de frecuencia mínima, segunda lógica 452 de suma, y cuarta lógica 454 de procesamiento. La lógica 400 puede recibir una primera señal 450, una segunda señal 460, una tercera señal 470, y una cuarta señal 480 como entradas y generar una señal 490 de salida. En una realización particular, la segunda señal 460 puede corresponder a la señal 206 de error de la figura 2 o la señal 379 de error de la figura 3. En una realización, la cuarta señal 480 puede corresponder a la señal 228 de sincronización de la figura 2.

5

25

30

35

40

45

50

55

60

La lógica 400 puede configurarse para determinar la frecuencia de la segunda señal 460 usando un método de cruce 10 por cero. Por ejemplo, la salida del primer bloque 412 de lógica AND puede ser un primer valor (por ejemplo, un uno (1)) cuando un marco previo (por ejemplo, muestra previa de la segunda señal 460) es menor que o igual a cero (0) v un marco actual (por ejemplo, una muestra actual de la segunda señal 460) es mayor que cero (0). La salida del segundo bloque 414 de lógica AND puede ser un primer valor (por ejemplo, un uno (1)) cuando el marco previo es mayor que o igual a cero (0) y el marco actual es menor que cero (0). Las salidas del primer bloque 412 de lógica AND 15 y el segundo bloque 414 de lógica AND pueden ser ambas un segundo valor (por ejemplo, un cero (0)) cuando el marco previo y el marco actual tienen el mismo signo (es decir, el marco previo y el marco actual indican que la segunda señal 460 está en el mismo lado de cero (0)). Adicionalmente, la salida del primer bloque 412 de lógica AND puede tener el segundo valor (por ejemplo, el cero (0)) cuando la salida del segundo bloque 414 de lógica AND tiene el primer valor (por ejemplo, el uno (1)). La salida del segundo bloque 414 de lógica AND puede tener el segundo valor 20 (por ejemplo, el cero (0)) cuando la salida del segundo bloque 412 de lógica AND tiene el primer valor (por ejemplo, el uno (1)).

Como se muestra en la figura 4, la lógica 400 puede configurarse para recibir la segunda señal 460 y para proporcionar la segunda señal 460 a la primera lógica 402 de comparación, la tercera lógica 406 de comparación, y la primera lógica 408 de retardo. La primera lógica 408 de retardo puede aplicar un retardo de un (1) marco a la segunda señal 460 y proporcionar una segunda señal retardada a la segunda lógica 404 de comparación y la cuarta lógica 410 de comparación. La primera lógica 402 de comparación puede configurarse para determinar si la segunda señal es mayor que cero (0), y la segunda lógica 404 de comparación puede configurarse para determinar si la segunda señal retardada (por ejemplo, el marco previo de la segunda señal 460) es menor que o igual a cero (0).

Cuando la segunda señal 460 es mayor que cero (0), la primera lógica 402 de comparación puede proporcionar un primer valor (por ejemplo, uno (1) o verdadero) al primer bloque 412 de lógica AND. Cuando la segunda señal 460 es menor que o igual a cero (0), la primera lógica 402 de comparación puede proporcionar un segundo valor (por ejemplo, cero (0) o falso) al primer bloque 412 de lógica AND. La tercera lógica 406 de comparación puede configurarse para determinar si la segunda señal 460 es menor que cero (0) y la cuarta lógica 410 de comparación puede configurarse para determinar si la segunda señal retardada (por ejemplo, el marco previo de la segunda señal 460) es mayor que o igual a cero (0). Cuando la segunda señal 460 es menor que cero (0), la tercera lógica 406 de comparación puede proporcionar un primer valor (por ejemplo, uno (1) o verdadero) al segundo bloque 414 de lógica AND. Cuando la segunda señal 460 es mayor que o igual a cero (0), la tercera lógica 406 de comparación puede proporcionar un segundo valor (por ejemplo, cero (0) o falso) al segundo bloque 414 de lógica AND. Cuando la segunda señal retardada es mayor que o igual a cero (0), la cuarta lógica 410 de comparación puede proporcionar un primer valor (por ejemplo, uno (1) o verdadero) al segundo bloque 414 de lógica AND. Cuando la segunda señal retardada es menor que cero (0), la cuarta lógica 410 de comparación puede proporcionar un segundo valor (por ejemplo, cero (0) o falso) al segundo bloque 414 de lógica AND.

El primer bloque 412 de lógica AND puede configurarse para realizar una operación de lógica AND en sus entradas (por ejemplo, las salidas de la primera lógica 402 de comparación y la segunda lógica 404 de comparación) para generar una primera señal de control. La primera señal de control puede proporcionarse desde el primer bloque 412 de lógica AND al primer conmutador 416 y la segunda señal de control puede proporcionarse desde el segundo bloque 414 de lógica AND al segundo conmutador 420. La primera señal de control y la segunda señal de control pueden usarse para controlar una primera señal de salida del primer conmutador 416 y para controlar una segunda señal de salida del segundo conmutador 420. Cuando la salida del primer bloque 412 de lógica AND tiene un primer valor (por ejemplo, uno (1) o verdadero), el primer conmutador 416 puede estar con cerrojo a una salida de la segunda lógica 452 de suma. La salida de la segunda lógica 452 de suma puede corresponder a una señal de sincronía y puede ser usada por la lógica 400 como una referencia de tiempo. Cuando la salida del primer bloque 412 de lógica AND tiene un segundo valor (por ejemplo, cero (0) o falso), el primer conmutador 416 puede estar con cerrojo a una salida de la segunda lógica 418 de retardo. La salida de la segunda lógica 418 de retardo puede corresponder a una primera marca de tiempo. Cuando la salida del segundo bloque 414 de lógica AND tiene un primer valor (por ejemplo, uno (1) o verdadero), el segundo conmutador 420 puede estar con cerrojo a la salida de la segunda lógica 452 de suma (por ejemplo, la señal de sincronía). Cuando la salida del segundo bloque 414 de lógica AND tiene un segundo valor (por ejemplo, cero (0) o falso), el segundo conmutador 420 puede estar con cerrojo a una salida de la tercera lógica 422 de retardo. La salida de la tercera lógica 422 de retardo puede corresponder a una segunda marca de tiempo. La lógica 424 de diferencia puede configurarse para determinar una diferencia entre la salida del primer conmutador 416 y la salida del segundo conmutador 420. La diferencia entre la salida del primer conmutador 416 y la salida del segundo conmutador 420 corresponde a una mitad de un período de la segunda señal 460.

Para ilustrar, suponer que la segunda señal 460 corresponde a una forma de onda sinusoidal. En un primer tiempo (t<sub>1</sub>), la salida del primer bloque 412 de lógica AND puede ser un primer valor (por ejemplo, cero (0) o falso) y la salida del segundo bloque 414 de lógica AND puede ser un segundo valor (por ejemplo, uno (1) o verdadero), y la salida de la segunda lógica 452 de suma puede corresponder a una primera marca de tiempo (TS<sub>1</sub>) del primer tiempo (t<sub>1</sub>). En el primer tiempo (t<sub>1</sub>), el primer conmutador 416 puede permanecer con cerrojo a la salida de la segunda lógica 452 de suma y puede proporcionar una salida que corresponde a la primera marca de tiempo (TS<sub>1</sub>). Adicionalmente, el segundo conmutador 420 puede estar con cerrojo a la salida de la tercera lógica 422 de retardo. De este modo, la salida del segundo conmutador 420 puede corresponder a la salida de la segunda lógica 452 de suma. Como se muestra en la figura 4, la salida del segundo conmutador 420 se proporciona como la entrada a la tercera lógica 422 de retardo. De este modo, en el primer tiempo (t<sub>1</sub>), el segundo conmutador 420 puede proporcionar una salida que corresponde a la primera marca de tiempo (TS<sub>1</sub>) almacenada en la tercera lógica 422 de retardo. En el primer tiempo (t<sub>1</sub>), la salida de la lógica 424 de diferencia puede ser cero (0) debido a que las salidas tanto del primer conmutador 416 como del segundo conmutador 420 corresponden a la primera marca de tiempo (por ejemplo, TS<sub>1</sub>).

5

10

35

40

45

50

En un tiempo subsiguiente (t₂), la salida del primer bloque 412 de lógica AND puede ser un segundo valor (por ejemplo, uno (1) o verdadero) y la salida de la segunda lógica 452 de suma puede corresponder a una segunda marca de tiempo (TS₂). En el segundo tiempo (t₂), el primer conmutador 416 puede estar con cerrojo a la salida de la segunda lógica 418 de retardo y puede proporcionar una salida que corresponde a la primera marca de tiempo (TS₁), y el segundo conmutador 420 puede estar con cerrojo a la salida de la segunda lógica 452 de suma. En el segundo tiempo (t₂), la salida de la segunda lógica 452 de suma puede corresponder a una segunda marca de tiempo (TS₂). De este modo, en el segundo tiempo (t₂), la salida del segundo conmutador 420 puede corresponder a la segunda marca de tiempo (TS₂), y la salida de la lógica 424 de diferencia puede corresponder a una diferencia entre la primera marca de tiempo (TS₁) recibida del primer conmutador 416 y la segunda marca de tiempo (TS₂) recibida del segundo conmutador 420. La diferencia puede corresponder a una mitad de un período de la segunda señal 460.

El bloque 426 de lógica de valor absoluto puede configurarse para recibir la salida (por ejemplo, la una mitad del período de segunda señal 460) de la lógica 424 de diferencia y generar una salida que corresponde a un valor absoluto de la salida recibida de la lógica 424 de diferencia. El bloque 426 de lógica de valor absoluto puede configurarse para proporcionar la salida (por ejemplo, el valor absoluto de la salida recibida de la lógica 424 de diferencia) al multiplicador 428. El multiplicador 428 puede configurarse para determinar el período completo de la segunda señal 460 al multiplicar la salida del bloque 426 de lógica de valor absoluto por dos (2). El multiplicador 428 puede configurarse para proporcionar el período a la lógica 430 de suma.