# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 744 602

51 Int. Cl.:

H04R 3/00 (2006.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 24.09.2015 PCT/FI2015/050640

(87) Fecha y número de publicación internacional: 31.03.2016 WO16046453

96) Fecha de presentación y número de la solicitud europea: 24.09.2015 E 15791673 (5)

(97) Fecha y número de publicación de la concesión europea: 07.08.2019 EP 3198888

(54) Título: Aparato y método para ahorrar energía en un altavoz activo

(30) Prioridad:

26.09.2014 FI 20145842

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **25.02.2020**

(73) Titular/es:

GENELEC OY (100.0%) Olvitie 5 74100 lisalmi, FI

(72) Inventor/es:

MOILANEN, PEKKA; PÖYHÖNEN, KARI y VÄISÄNEN, JUHO

(74) Agente/Representante:

ELZABURU, S.L.P

#### **DESCRIPCIÓN**

Aparato y método para ahorrar energía en un altavoz activo

20

25

30

40

La invención se refiere a un método, según la reivindicación 1.

La invención también se refiere a un aparato, según la reivindicación 7.

Hoy en día, se requiere un consumo de energía reducido en todos los dispositivos eléctricos. Las presiones para reducir el consumo eléctrico provienen tanto de los consumidores como de los funcionarios públicos. El consumo eléctrico de un dispositivo electrónico moderno se puede reducir apagando automáticamente aquellas partes del dispositivo que no se requieren necesariamente en ese preciso momento. Si el dispositivo está en modo de reposo y consume la menor potencia eléctrica posible, todas las demás partes del dispositivo se pueden apagar, excepto las que detectan la llegada de una señal. Cuando llega una señal, y entonces se desea que el dispositivo funcione, dicho componente de detección activa las otras partes del dispositivo para el funcionamiento normal. Dicha monitorización se implementa, normalmente, mediante el uso de un microcontrolador en un estado especial que consume muy poca energía, de modo que se requiere una parte de la electrónica que continuamente consume suficiente energía, pero la menor cantidad posible, por medio de la cual el reconocimiento de la señal de entrada se envía al microcontrolador que controla el sistema.

En el caso de los altavoces, es cada vez más común que el propio altavoz contenga un amplificador, lo cual logra ventajas especialmente en la calidad del sonido. Se obtienen ventajas adicionales si la señal que llega al altavoz se digitaliza directamente, por medio de lo cual la señal entre el altavoz y la fuente de sonido, que puede ser un preamplificador o una fuente de sonido digital directa, será digital y, por lo tanto, en la práctica, completamente libre de distorsiones.

Se conocen métodos por medio de los cuales, en la situación mencionada anteriormente, el amplificador del altavoz se puede poner en un modo de reposo de ahorro de energía mediante el monitoreo de la señal digital que llega al altavoz como se describe en el documento US 8024055. Según la técnica anterior, la monitorización tiene lugar en un decodificador, según el análisis con respecto al cual las etapas posteriores del altavoz se controlan. Sin embargo, el microcircuito que implementa el decodificador requiere una cantidad de energía relativamente grande incluso cuando se encuentra en el modo de reposo, en comparación con los requisitos de ajuste continuo.

De manera más específica, en la técnica antes mencionada, el receptor de señal de audio digital (AES/EBU codificada) se implementa, normalmente, como un microcircuito o módulo en un circuito de sistema más amplio. En su estado operativo normal, el microcircuito que implementa el decodificador requiere una corriente de 10-30 mA (30-100 mW). Cuando el receptor está funcionando, detecta la llegada de una señal de audio digital válida y puede notificar al resto del sistema cuando se puede recibir una buena señal digital.

El consumo de energía de un dispositivo se puede reducir desactivando las funciones que no se utilizan. Si no hay una señal de audio digital disponible, el circuito que recibe una señal de audio digital se puede mantener en modo de reposo que consume poca energía.

La invención pretende crear un tipo completamente nuevo de método y aparato para ahorrar la energía eléctrica consumida por un altavoz activo en modo de reposo.

La invención se basa en el ahorro de energía eléctrica al llevar la señal digital entrante más allá del decodificador directamente a un procesador de señales, en el que se toman muestras de la línea de entrada digital a una frecuencia de reloj considerablemente reducida y el decodificador se activa solo si las condiciones predefinidas para reconocer una señal se cumplen.

Según una realización preferida de la invención, se usan métodos estadísticos para reconocer una señal de audio.

Más específicamente, el método según la invención está caracterizado por la reivindicación 1.

El aparato según la invención está, a su vez, caracterizado por la reivindicación 7.

Se obtienen ventajas considerables por medio de algunas realizaciones de la invención. Con la ayuda de la invención, se puede reconocer una señal de audio digital mediante el uso de un consumo de energía extremadamente bajo en comparación con el circuito que implementa el decodificador que se mantiene activo continuamente.

Mediante la disposición según la invención, se pueden cumplir requisitos de uso de energía ajustados y actualizados cuando el dispositivo electrónico está en modo de reposo.

Debido a que la línea ES del procesador de señales (microcontrolador) se puede utilizar para el reconocimiento, el método se puede implementar fácil y económicamente.

A continuación, la invención se examinará con la ayuda de las figuras anexas, en las que

#### ES 2 744 602 T3

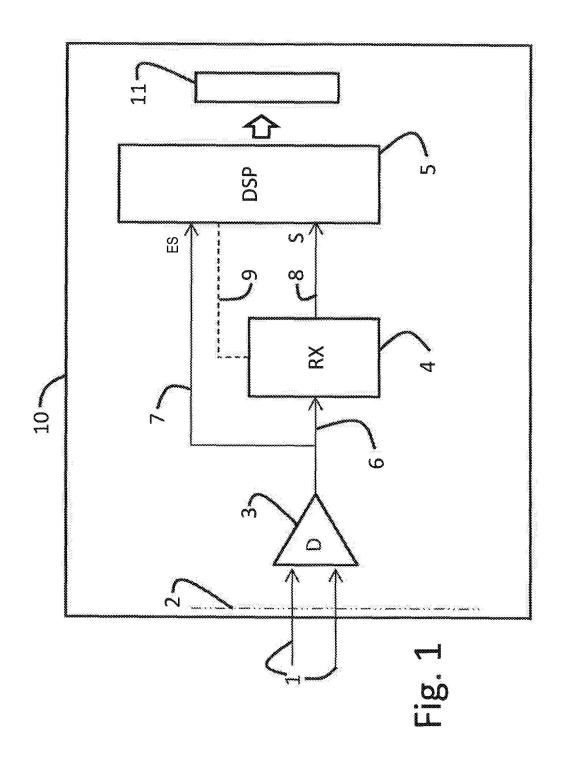

La Figura 1 muestra un diagrama de bloques de una solución según la invención.

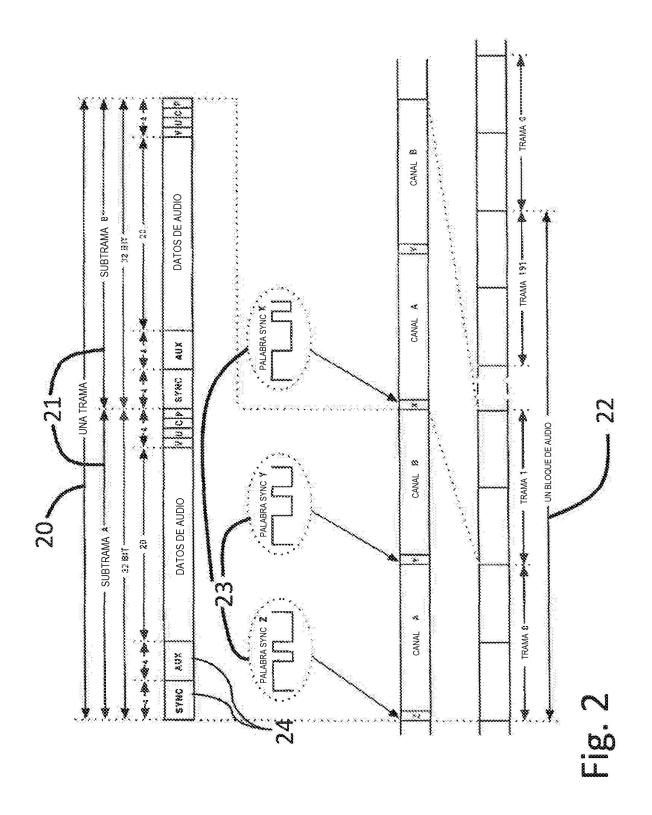

La Figura 2 muestra la señal utilizada en relación con la invención, en un plano temporal.

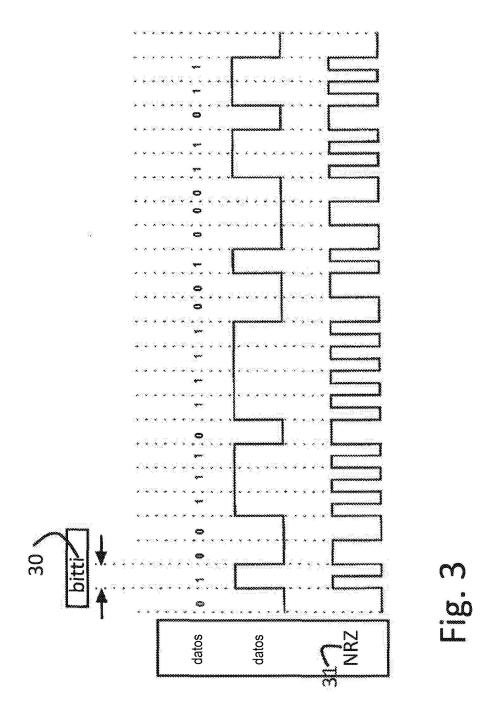

La Figura 3 muestra un detalle de la señal de la Figura 2.

En el presente documento, se utiliza la siguiente terminología en relación con las Figuras:

- 5 1 línea de señal de entrada, trae una señal AES/EBU no amplificada al dispositivo

- 2 interfaz de entrada, conector

- 3 receptor diferencial

- 4 decodificador, microcircuito que implementa un decodificador

- 5 procesador de señales, (microprocesador)

- 10 6 línea de señal no decodificada del receptor diferencial, línea AES/EBU amplificada

- 7 línea de control del receptor diferencial de la línea de señal no decodificada a la entrada ES del procesador 5 de señales (microprocesador)

- 8 línea de señal decodificada del decodificador al procesador 5 de señales (microprocesador), señal (S) de audio PCM

- 15 9 línea de señal del decodificador 4 al procesador 5 de señales (microprocesador)

- 10 altavoz activo

- amplificadores terminales y los elementos de altavoz conectados a ellos

- 20 trama

- 21 subtrama

- 20 22 bloque de audio

- 23 byte de sincronización

- 24 campo de encabezamiento (SYNC + AUX)

- 30 bit

35

40

45

- 31 señal de audio digital NRZ, datos codificados NRZ (NRZ)

- Según la Figura 1, una señal AES/EBU no amplificada se conduce a lo largo de la línea 1 de señal de entrada a un altavoz 10 activo que contiene un amplificador, a la interfaz de entrada, un conector 2, que puede ser un conector 2 conectado de forma óptica o galvánica. La señal se amplifica en un receptor 3 diferencial, desde el cual la señal AES/EBU amplificada se conduce a lo largo de la línea 6 al decodificador 4 y desde allí como una señal (S) de audio PCM decodificada a lo largo de la línea 8 al procesador 5 de señales (microprocesador), que convierte la señal en una forma analógica para enviarla al amplificador y a los elementos 11 de altavoz de la etapa terminal.

La llegada de una señal de audio digital puede reconocerse, según la técnica anterior, manteniendo activo el circuito 4 que implementa el decodificador AES/EBU de la Figura 1. Cuando el circuito 4 notifica al procesador 5 sobre la existencia de la señal a lo largo de la línea 9, las otras funciones del dispositivo pueden activarse cuando sea necesario. Sin embargo, el reconocimiento de la señal creada por el circuito 4 de implementación del decodificador AES/EBU con frecuencia requiere más potencia que todos los demás componentes del sistema combinados, incluido el mantenimiento del procesador 5 de señales que controla el sistema en funcionamiento. La señal AES/EBU es una señal de audio digital codificada NRZ (sin retorno a cero) según las Figuras 2 y 3. El bit 30 se codifica mediante el uso de un símbolo que consta de dos estados binarios. El primer estado del símbolo siempre es diferente del segundo estado del símbolo anterior. El segundo estado del símbolo es igual al primer estado en un caso en el que el valor lógico del bit que se codifica es cero (no uno). Si el valor del bit 30 es uno, el segundo valor del símbolo es diferente del primer valor del símbolo. Dicha codificación NRZ (el estándar usa el término "bifase") produce una cola digital, en la que los cambios tienen lugar ya sea a la frecuencia definida por la duración del bit digital o al doble de dicha frecuencia. En el caso de una señal AES/EBU, la duración de un bit digital se determina a partir de la frecuencia de reloj de muestra de la señal de audio. La trama AES/EBU contiene 64 bits, y la trama 20 se divide en dos subtramas 21.

Se conoce que el audio codificado NRZ puede reconocerse mediante la detección de una cola de bits que contiene una señal NRZ. Las desviaciones en la frecuencia de reloj se pueden detectar con la ayuda de un circuito de cierre PLL contenido en el circuito de receptor de audio digital. El campo 24 de encabezamiento (SYNC + AUX, Figura 2) de la señal AES/EBU contiene una desviación hacia la frecuencia de reloj normal y se desvía de la frecuencia de reloj normal. Según ello, se puede reconocer el inicio de la trama y, además, los datos contenidos en una trama individual se pueden grabar en un registro. Una vez que se han registrado los datos, la trama puede reconocerse como una trama AES/EBU según su estructura conocida. El método descrito anteriormente es relativamente oneroso en términos de cálculo, consume mucha energía y se basa en la decodificación completa de la trama AES/EBU.

10 Con la ayuda de la invención, se reconoce la existencia de una señal 31 de audio digital NRZ, mediante el uso de muy poca energía. La señal de audio posible se reconoce a partir de la línea 6 de señal, antes del circuito de receptor real, por el decodificador 4 que recoge la señal de la línea 6 de señal no decodificada a través de la línea 7 de control a la entrada ES del procesador 5 de señales.

15

20

25

30

35

50

55

Según la invención, el circuito 4 que implementa el decodificador queda, por consiguiente, sin energía y se enciende para funcionar solo cuando se encuentra una señal que satisface los criterios. Para leer el estado de la entrada 1 AES/EBU, el circuito 3 de receptor diferencial (por ejemplo, la transferencia de audio según el estándar AES/EBU usa codificación diferencial según el estándar RS-422) se mantiene encendido. El consumo de energía del receptor 3 diferencial es extremadamente bajo. El reconocimiento previo se lleva a cabo leyendo, de forma aleatoria, un número suficiente de veces el estado de la línea 6 AES/EBU en la línea 7 ES del procesador 5 de señales después del receptor 3 diferencial. La lectura puede tener lugar a una frecuencia esencialmente más baja que la frecuencia de muestreo de la señal 1 de audio AES/EBU. La lectura toma una muestra del nivel de la señal 6 amplificada AES/EBU por submuestreo aleatorio, por ejemplo, tomando muestras relativas a la frecuencia de bits de la Figura 3, por ejemplo, a un promedio de intervalos de cada 10 ... 1.000 bits. El método no requiere una densidad de lectura específica o sincronización con los datos que se leen, ya que se basa en la utilización de las propiedades estadísticas de los datos producidos por la codificación NRZ. Durante la lectura, el procesador 5 de señales calcula el número de veces en que un estado que difiere de la lectura anterior se lee de la línea. El estado se lee suficientes veces para el examen estadístico, por ejemplo, mil veces, y el procesador 5 de señales se usa para hacer un análisis estadístico a partir de estos. Si hay una señal 1 de audio digital AES/EBU típica en la línea, normalmente se observarán 300-500 cambios. La línea ES del microprocesador 5, por ejemplo, puede usarse para leer y, de esta manera, la lectura puede llevarse a cabo ventajosamente mediante el uso de cualquier procesador. Al utilizar la disposición según la invención, no es necesario encender el decodificador 4 para reconocer una señal 1 AES/EBU.

La disposición según la invención (reconocimiento previo) permite reconocer la existencia de una señal de audio digital a partir de la línea de señal con anterioridad al circuito 4 que implementa el decodificador. El circuito 4 que implementa el decodificador puede entonces mantenerse sin energía y activarse solo cuando el procesador 5 de señales dispuesto según la invención puede reconocer una señal que satisface los criterios, lo cual normalmente funciona de este modo a una frecuencia de reloj muy reducida, que es, por ejemplo, de 1/100 - 1/1.000 de la frecuencia de reloj normal, lo cual le da un consumo de energía muy bajo.

Con la ayuda de la invención, la existencia de una señal de audio AES/EBU codificada NRZ puede reconocerse con la ayuda de la información estadística descrita anteriormente.

Como ejemplo de la implementación del reconocimiento previo, la línea 6 de señal no decodificada se lee desde el receptor 3 diferencial mil veces a una frecuencia que es, normalmente, de 10 - 1.000 veces menor que la frecuencia de muestreo de una señal 31 de audio digital NRZ. El método no requiere una densidad de lectura específica o sincronización con los datos que se leen, dado que se basa en la utilización de las propiedades estadísticas de los datos producidos por la codificación NRZ. Según las propiedades de la señal NRZ, puede considerarse que la aparición teórica de cambios en la cola de muestra es del 25% al 50%, siempre que el estado de la señal NRZ se lea desde un punto aleatorio a una frecuencia que no es un múltiplo de frecuencia de muestra.

Si hay una señal de audio digital típica AES/EBU en la línea, normalmente se detectan 300 - 500 cambios por cada 1.000 lecturas (30 - 50%). Por lo general, se encuentran 0 - 9 cambios por cada 1.000 lecturas del cable no conectado. Si se detecta un número suficiente de cambios en relación con las lecturas, se indica que se ha encontrado una señal de audio digital. Más específicamente, si se detecta un número típico de cambios en relación con las lecturas, es probable que la señal sea una señal codificada NRZ. Existen entonces suficientes motivos para activar el decodificador AES/EBU del dispositivo y, de esta manera, obtener información precisa de que la señal NRZ es una señal de audio codificada AES/EBU.

En resumen, la existencia de una señal de audio digital codificada NRZ se reconoce en dos etapas. En primer lugar, mediante un método de cálculo de bajo consumo de energía basado en una propiedad estadística y solo entonces con mayor precisión mediante el uso de un circuito de receptor AES/EBU. La señal AES/EBU se reconoce mediante la lectura de los estados de la señal digital de forma asincrónica y aleatoria.

El aparato, normalmente, se restablece al modo de reposo de tal manera que, si después de un tiempo de detección específico, no llega una señal (es decir, la señal está ausente durante todo el tiempo), se establece un contador para

#### ES 2 744 602 T3

determinar el tiempo transcurrido y, si el tiempo supera un límite de tiempo predefinido, por ejemplo, 1 minuto, entonces se inicia el modo de reposo. Si el aparato detecta una señal entrante, el contador se restablece y el conteo comienza nuevamente desde el momento en que la señal desaparece.

En la presente solicitud, el término modo de reposo se refiere a un estado de un circuito eléctrico, en el que este usa claramente menos energía que en el funcionamiento normal, pero en el que puede recibir e interpretar señales en la medida en que sea esencial para despertar el dispositivo del modo de reposo. La legislación de la Unión Europea, por ejemplo, requiere que ciertos dispositivos consuman menos de 0,5 W de energía eléctrica cuando están en modo de reposo. El consumo de energía sin carga de un dispositivo de este tipo puede ser, normalmente, de 5 ... 30 W. En el modo de reposo, el dispositivo debe, por consiguiente, usar menos del 10% de su consumo de energía sin carga normal.

En la presente solicitud, el término sin energía se refiere a un estado del circuito eléctrico en el que este utiliza menos del 0,1% de su consumo de energía eléctrica normal.

El término estado de funcionamiento de baja frecuencia se refiere, en este sentido, a un estado del microprocesador o procesador de señales, en el que su frecuencia de funcionamiento se reduce para ser claramente menor, por ejemplo, de menos del 30% de su frecuencia de funcionamiento normal y preferiblemente de menos del 1% de su frecuencia de funcionamiento normal.

#### **REIVINDICACIONES**

- 1. Método para convertir una señal (1, 6) de audio digital codificada NRZ (sin retorno a cero) en una señal analógica en un sistema, en el que al menos algunos de los componentes (3, 4, 5) electrónicos están a veces en un modo de reposo o sin energía, en cuyo método

- 5 se recibe y amplifica una señal (1, 31) de audio digital codificada,

- la señal (6) amplificada no decodificada se conduce a la entrada ES de un microprocesador (5) para ser reconocida,

- un circuito que implementa el decodificador (4) se mantiene en modo de reposo, a menos que se haya reconocido una señal (1, 31) de audio digital codificada NRZ,

- y si se reconoce la señal (1, 31) de audio digital codificada NRZ, la señal (6) amplificada no decodificada se decodifica en el circuito que implementa el decodificador (4),

- la señal (8) decodificada se conduce al microprocesador (5) para su posterior procesamiento y conversión digital/analógica con el fin de crear una señal analógica, y

- se crea una señal (11) de audio a partir de la señal analógica.

- 2. Método según la reivindicación 1, en el que el reconocimiento se lleva a cabo tomando muestras de la señal (6) amplificada no decodificada a una frecuencia de muestreo que es inferior a su frecuencia de muestreo y que preferiblemente es inferior a 1/10 de la frecuencia de bits de la señal.

- 3. Método según la reivindicación 1 o 2, en el que, sin una señal reconocida, el microprocesador (5) funciona a una frecuencia de reloj que es de 1/10 1/1.000 de la frecuencia normal del microprocesador (5).

- 4. Método según cualquiera de las reivindicaciones anteriores, en el que la señal (6) amplificada no decodificada se reconoce mediante la lectura de estados binarios de la señal (6) digital amplificada no decodificada de forma asincrónica y aleatoria.

- 5. Método según cualquiera de las reivindicaciones anteriores, en el que la señal (6) no decodificada amplificada se reconoce mediante la lectura de la señal (6) no decodificada amplificada en un punto aleatorio a una frecuencia que no es un múltiplo de su frecuencia de muestreo.

- 6. Método según cualquiera de las reivindicaciones anteriores, en el que la señal digital codificada es una señal AES/EBU.

- 7. Aparato para convertir una señal (1, 6) de audio digital codificada NRZ (sin retorno a cero) en una señal analógica en un sistema, en el que al menos algunos de los componentes (3, 4, 5) electrónicos están a veces en un modo de reposo o sin energía, cuyo aparato comprende medios para

- amplificar y recibir una señal (1, 31) de audio digital codificada,

25

30

45

- conducir la señal (6) amplificada no decodificada a la entrada ES de un microprocesador (5) que se reconocerá,

- mantener el circuito que implementa un decodificador (4) en modo de reposo, a menos que se haya reconocido una señal (1, 31) de audio digital codificada NRZ,

- decodificar, si la señal (1, 31) de audio digital codificada NRZ se reconoce, la señal (6) amplificada no decodificada en un circuito que implementa el decodificador (4),

- conducir la señal (8) decodificada al microprocesador (5) para su mayor procesamiento y conversión digital/analógica con el fin de crear una señal analógica, y

- crear una señal (11) de audio a partir de la señal analógica.

- 40 8. Aparato según la reivindicación 7, en el que el aparato comprende medios para llevar a cabo el reconocimiento tomando muestras de una señal (6) no decodificada a una frecuencia de muestreo inferior a su frecuencia de muestreo, que es inferior a 1/10 de la frecuencia de bits de la señal.

- 9. Aparato según la reivindicación 7 u 8, en el que el aparato comprende medios, por los cuales, sin la señal (6) no decodificada reconocida, el microprocesador (5) puede funcionar a una frecuencia de reloj que es de 1/10 1/1.000 de la frecuencia normal del microprocesador (5).

- 10. Aparato según cualquiera de las reivindicaciones anteriores, en el que el aparato comprende medios para reconocer la señal (6) amplificada no decodificada mediante la lectura de estados binarios de la señal (6) digital de forma asincrónica y aleatoria.

## ES 2 744 602 T3

11. Aparato según cualquiera de las reivindicaciones anteriores, en el que el aparato comprende medios para reconocer la señal (6) amplificada no decodificada mediante la lectura de la señal (6) en un punto aleatorio a una frecuencia que no es un múltiplo de su frecuencia de muestreo.