# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 746 278

51 Int. Cl.:

H03K 17/10 (2006.01) H03K 17/16 (2006.01) H03K 17/567 (2006.01) H03K 17/687 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 05.05.2015 PCT/US2015/029187

(87) Fecha y número de publicación internacional: 03.12.2015 WO15183482

Fecha de presentación y número de la solicitud europea: 05.05.2015 E 15722641 (6)

Fecha y número de publicación de la concesión europea: 10.07.2019 EP 3149852

(54) Título: Circuito de conmutación de cascode

(30) Prioridad:

28.05.2014 US 201462003637 P 28.10.2014 US 201414525863

Fecha de publicación y mención en BOPI de la traducción de la patente: **05.03.2020**

(73) Titular/es:

UNITED SILICON CARBIDE INC. (100.0%)

7 Deer Park Drive, Suite E.

Monmouth Junction, NJ 08852, US

(72) Inventor/es:

LI, XUEQING y BHALLA, ANUP

(74) Agente/Representante:

IZQUIERDO BLANCO, María Alicia

### **DESCRIPCION**

Circuito de conmutación de cascode

### 5 REFERENCIA CRUZADA A SOLICITUDES RELACIONADAS

Esta solicitud reivindica el beneficio de la Solicitud Provisional de Estados Unidos Nº de serie 62/003.637 presentada el 28 de mayo de 2014 y la Solicitud de Patente de Estados Unidos 14/525.863, presentada el 28 de octubre de 2014.

### **ANTECEDENTES**

10

15

20

25

30

35

40

45

50

55

60

65

La presente invención se refiere en general a dispositivos de conmutación de semiconductores y a métodos de accionamiento de compuertas y, en particular, a conmutadores de accionamiento que comprenden un dispositivo semiconductor normalmente apagado y un dispositivo semiconductor de banda prohibida amplia de alto voltaje normalmente encendido en la disposición de cascode.

Los compuestos de semiconductores, como el carburo de silicio (SiC) y el nitruro de galio (GaN), tienen una banda prohibida o diferencia de energía entre la parte superior de la banda de valencia y la parte inferior de la banda de conducción típicamente mayor que 2 voltios de electrones, por lo tanto estos semiconductores se denominan semiconductores de banda prohibida amplia. Los semiconductores de banda prohibida amplia tienen un campo de descomposición mucho más alto que el del silicio; por ejemplo, el campo de descomposición del carburo de silicio es de aproximadamente 3x10<sup>6</sup> voltios por centímetro, que es aproximadamente 10 veces más alto que el campo de descomposición del silicio. Las propiedades de una banda prohibida amplia y un campo de descomposición alto permiten que los dispositivos de potencia hechos con semiconductores de banda prohibida amplia bloqueen un voltaje más alto con menos resistencia de encendido, cambien a una frecuencia más alta con mayor eficiencia, y operen a temperaturas más altas con menos requisitos de enfriamiento. Estas características del dispositivo son críticas para implementar un sistema de conversión de potencia de alto voltaje, alta temperatura, alta frecuencia y alta densidad de potencia.

Se han invertido tremendos esfuerzos para desarrollar transistores de efecto de campo de unión de SiC (JFET), transistores de efecto de campo de semiconductor de óxido de metal de SiC (MOSFET) y transistores de alta movilidad de electrones de GaN (HEMT). En comparación con los MOSFET de SiC, los JFET de SiC no requieren una película de óxido crítica y, por lo tanto, están libres de problemas de degradación del rendimiento y fiabilidad a largo plazo relacionados con el óxido bajo condiciones de funcionamiento de alto campo eléctrico y alta temperatura de unión. Los JFET de SiC son fiables a altas temperaturas, y continúan experimentando un gran avance en las cifras de mérito de resistencia en conducción y conmutación específicas. Controlando la apertura del canal, se puede hacer que un JFET de SiC esté normalmente encendido o normalmente apagado. Un dispositivo normalmente encendido es un dispositivo que es altamente conductor, o está en estado ENCENDIDO, cuando se aplica voltaje cero a su terminal o compuerta de control. Un dispositivo normalmente apagado es un dispositivo que es altamente resistivo, o está en estado APAGADO, cuando se aplica voltaje cero a su terminal o compuerta de control. Normalmente, los JFET de SiC han demostrado una muy baja resistencia en conducción específica. Hay una penalización en la resistencia en conducción con los JFET de SiC normalmente apagados, y requieren unidades de compuerta ajustadas apropiadamente para un rendimiento óptimo. En cuanto a los HEMT de GaN, casi todos son dispositivos normalmente encendidos.

Los dispositivos de SiC y GaN de mejor rendimiento son los dispositivos normalmente encendidos. Sin embargo, los dispositivos normalmente encendidos pueden producir una condición de cortocircuito peligrosa durante el inicio del sistema o fallos de suministro de la unidad de compuerta, lo que hace que los dispositivos normalmente encendidos sean difíciles de aplicar en muchas aplicaciones de conversión de potencia. Un método para superar el desafío de usar dispositivos normalmente encendidos aprovecha el concepto de cascode divulgado por Baliga et al. en la patente de Estados Unidos Nº 4.663.547 titulada "Composite Circuit for Power Semiconductor Switching", que comprende un MOSFET normalmente apagado de bajo voltaje conectado en serie con un JFET normalmente encendido de alto voltaje y presenta un modo de funcionamiento normalmente apagado cuando se aplica un voltaje cero a su terminal de control, la compuerta MOSFET. Las ventajas del dispositivo de cascode incluyen el modo de funcionamiento normalmente apagado, un diodo de cuerpo incorporado con baja caída de voltaje directo y muy baja capacitancia del miller. El dispositivo de cascode, como un circuito compuesto, contiene muchas inductancias parásitas de los cables de unión del dispositivo, los cables del paquete y trazas de PCB. Estas inductancias parásitas, junto con las capacitancias de los dos dispositivos en el cascode, pueden provocar oscilaciones durante el proceso de conmutación y dar como resultado inestabilidades bajo ciertas condiciones. Para garantizar un funcionamiento fiable del cascode, la tasa instantánea de cambio de voltaje a lo largo del tiempo (dv/dt) y la tasa instantánea de cambio de corriente a lo largo del tiempo (di/dt) durante el proceso de conmutación deben controlarse activamente. El resistor de compuerta de MOSFET y la inductancia parásita en la fuente del cascode caja pueden usarse para controlar eficazmente di/dt y dv/dt del proceso de encendido. Sin embargo, el control completo de di/dt y dv/dt del proceso de apagado del cascode es más difícil que en el caso del proceso de encendido.

Se han ideado varios métodos para controlar el proceso de conmutación del cascode. Rose, en la solicitud de patente de Estados Unidos titulada "Cascoded Semiconductor Devices", describe un método que usa un condensador de arranque conectado entre la compuerta del dispositivo normalmente activado de alto voltaje y la compuerta del dispositivo normalmente apagado de bajo voltaje para lograr un control activo de ambos dispositivos en un circuito de cascode usando un único controlador de compuerta. Este método desarrollará una caída de voltaje a través del condensador de arranque que invierte la polarización de la unión de la fuente de compuerta del dispositivo normalmente activado y da como resultado un aumento sustancial en la resistencia en conducción del dispositivo normalmente encendido.

10

5

Iwamura, en la Patente de Estados Unidos Nº 8.487.667 titulada "Hybrid Power Device", describe un método para controlar el proceso de conmutación de cascode con una red de resistencia-condensador-diodo (RCD) conectada a la compuerta del dispositivo normalmente encendido. Para atenuar las oscilaciones durante el proceso de conmutación a un nivel aceptable, este método reduce la velocidad de conmutación significativamente y aumenta la pérdida de conmutación del circuito de cascode.

15

20

Friedrichs, en la Patente de Estados Unidos Nº 7.777.553 titulada "Simplified Switching Circuit", y Cilio, en la Patente de Estados Unidos Nº 8.228.114 titulada "Normally-off D-mode Driven Direct Drive Cascode", describen un método de accionamiento directo. En este método, el dispositivo de bajo voltaje normalmente apagado se usa como un dispositivo de protección. En funcionamiento normal, el dispositivo de bajo voltaje normalmente apagado se mantiene siempre encendido y el dispositivo de alto voltaje normalmente encendido se conmuta independientemente. Durante el arranque o una condición de fallo, el dispositivo normalmente apagado se apagará y el circuito entero se apagará como un circuito cascode convencional. De esta manera, el cascode de accionamiento directo se comporta como un dispositivo autónomo normalmente encendido y se evitan las limitaciones del circuito cascode. Sin embargo, este método necesita un controlador de compuertas complicado para asegurar el funcionamiento seguro apropiado del dispositivo de cascode.

25

30

35

Kanazawa et al, en la Solicitud de Patente de Estados Unidos Nº 20130335134 titulada "Semiconductor Device and System Using the Same", describe un método para controlar el dispositivo de cascode. En este método, tanto los dispositivos normalmente encendidos como los normalmente apagados en el cascode se conmutan activamente al mismo tiempo durante el proceso de conmutación y se mantienen activamente en estado APAGADO por su respectiva señal de accionamiento de compuerta durante el estado APAGADO. Con un diseño apropiado del tiempo de retardo entre las señales de compuerta de los dispositivos normalmente encendidos y los normalmente apagados, el proceso de conmutación del cascode estará muy cerca del proceso de conmutación de un dispositivo normalmente encendido autónomo. Sin embargo, el dispositivo normalmente encendido no es adecuado para la conducción de corriente inversa en este método ya que su terminal de compuerta se mantiene a un potencial bajo con respecto a su fuente durante el estado APAGADO. No se utiliza la característica del diodo del cuerpo incorporado del dispositivo de cascode. Se requiere un diodo de rueda libre adicional conectado en paralelo con el dispositivo de cascode para que el dispositivo de cascode conduzca una corriente inversa.

40

Por lo tanto, todavía hay una necesidad de un dispositivo de cascode que tenga un circuito de accionamiento de compuertas simple, un proceso de conmutación controlable, y un diodo de cuerpo incorporado.

45

La DE 10 2009 002332 A1 describe un conversor que tiene una conexión en serie con dos elementos de conmutación semiconductores, y otra conexión en serie con dos elementos de conmutación semiconductores. Un circuito de generación de potencial intermedio está conectado a los puntos intermedios, donde se proporcionan transistores auto-conductores, es decir FET de compuerta de unión de carburo de silicio, y transistores de auto-bloqueo, por ejemplo, MOSFET, como los elementos de conmutación semiconductores. Un elemento rectificador, es decir diodo de carburo de silicio, está conectado entre un punto de toma potencial y uno de los puntos intermedios.

50

### **SUMARIO**

BREVE DESCRIPCIÓN DE LOS DIBUJOS

55

Un objeto de la presente invención es proporcionar un circuito de conmutación de cascode que tenga un circuito de accionamiento de compuerta simple, un proceso de conmutación controlable, y un diodo de cuerpo incorporado.

Un aparato y un método de acuerdo con la presente invención se define en las reivindicaciones adjuntas.

60

Los aspectos, características y ventajas adicionales de la invención se entenderán y se harán más evidentes cuando se considere la invención a la luz de la siguiente descripción realizada en conjunción con los dibujos acompañantes.

65

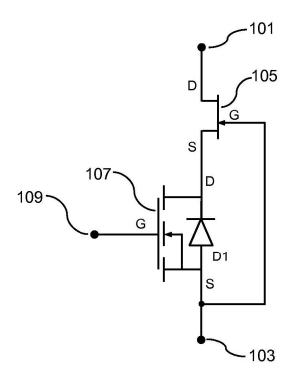

La FIG. 1 es un diagrama esquemático de circuito que ilustra un circuito de cascode convencional formado

con un dispositivo normalmente encendido y un dispositivo normalmente apagado.

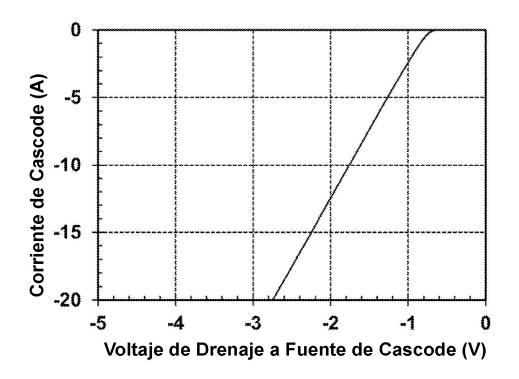

La FIG. 2 es un gráfico que ilustra la características de conducción de corriente inversa medidas en la polarización de voltaje de fuente de compuerta cero de un circuito de cascode convencional formado con un JFET normalmente encendido de SiC de 1200 voltios y un MOSFET normalmente apagado de silicio de 25 voltios normalmente. El circuito de cascode tiene una resistencia de encendido de 100 miliohmios.

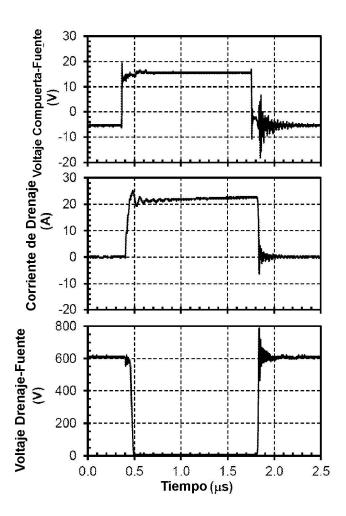

La FIG. es un gráfico que ilustra las formas de onda de conmutación medidas de un circuito de cascode convencional formado con un JFET normalmente encendido de SiC de 1200 voltios y un MOSFET normalmente apagado de silicio de 25 voltios. La prueba se realizó a una condición de carga inductiva de 600 voltios y 21 amperios. Una resistencia de 2,5 ohmios y un núcleo de ferrita conectados en serie se conectan a la compuerta del MOSFET de silicio para suprimir las oscilaciones.

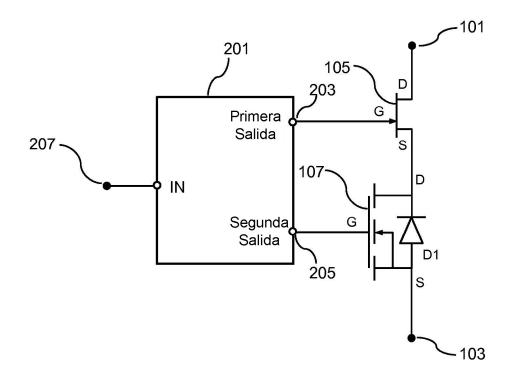

La FIG. 4 es un diagrama esquemático de circuito que ilustra un circuito de conmutación de cascode de acuerdo con una realización de la presente invención.

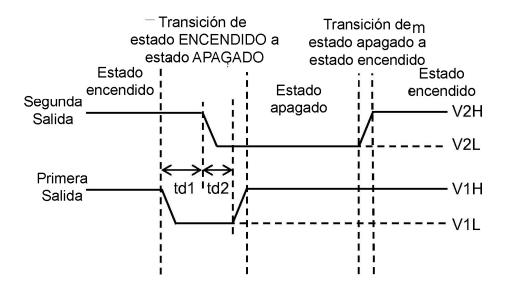

La FIG. 5 es un diagrama que ilustra esquemáticamente las formas de onda de funcionamiento de las salidas del controlador de la compuerta para controlar el circuito de conmutación de cascode ilustrado en la FIG. 4.

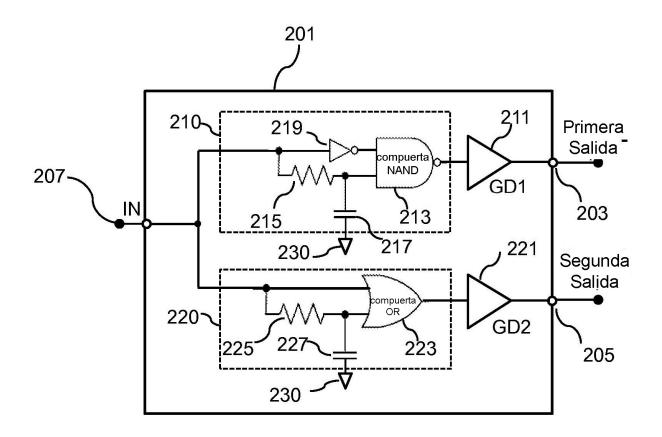

La FIG. 6 es un diagrama esquemático de circuito que ilustra un circuito ejemplar no limitativo para proporcionar las formas de onda de funcionamiento de las salidas del controlador de compuerta ilustradas en la FIG. 5 para controlar el circuito de conmutación de cascode ilustrado en la FIG. 4.

### DESCRIPCIÓN DETALLADA DE REALIZACIONES ILUSTRATIVAS

5

10

15

20

25

30

35

40

45

50

55

60

65

Ahora se proporcionará una descripción detallada de las realizaciones preferidas de la presente invención que se ilustran en los dibujos acompañantes. Siempre que sea posible, se usarán números de referencia idénticos en los dibujos y la descripción para hacer referencia a partes iguales o similares que tienen idéntica función.

La FIG. 1 muestra un circuito de conmutación de cascode convencional que incluye un MOSFET de silicio normalmente apagado 107 acoplado en serie con un JFET normalmente encendido 105. Los terminales de drenaje, fuente, y compuerta de estos dos dispositivos están marcados como D, S y G, respectivamente. El terminal de drenaje del MOSFET de silicio normalmente apagado 107 está acoplado al terminal de fuente del JFET normalmente encendido 105, y el terminal de compuerta del JFET normalmente encendido 105 está acoplado directamente al terminal fuente del MOSFET de silicio normalmente apagado 107, formando de este modo un circuito de cascode normalmente apagado de tres terminales, en el que el terminal de compuerta del MOSFET de silicio de normalmente apagado 107 funciona como el terminal de control 109, el terminal de drenaje del JFET normalmente apagado 105 funciona como el terminal de fuente 103. Cuando la polarización de voltaje entre el terminal de control 109 y el terminal de fuente 103 es cero, el MOSFET de silicio normalmente apagado 107 se opera en estado APAGADO, y la caída de voltaje a través de los terminales de drenaje y fuente del MOSFET de silicio normalmente está apagado 107 invertirá la polarización de la unión compuerta-fuente del JFET normalmente encendido 105 y obligará al JFET normalmente encendido 105 a funcionar en el estado APAGADO. Por lo tanto, el circuito de conmutación de cascode en la FIG. 1 funciona en modo normalmente apagado.

En el estado de APAGADO, el voltaje desde el terminal de control 109 al terminal de fuente 103 es en general igual a cero voltios o incluso menos de cero voltios. Si el voltaje del terminal de fuente 103 al terminal de drenaje 101 es mayor que cero voltios, el diodo del cuerpo D1 del MOSFET de silicio normalmente apagado 107 se polarizará hacia adelante y la unión de compuerta-fuente del JFET normalmente encendido 105 también se polarizará hacia adelante. Por tanto, el circuito de conmutación de cascode en la FIG. 1 puede conducir una corriente inversa en estado APAGADO que fluye a través del diodo del cuerpo D1 del MOSFET de silicio normalmente apagado 107 y el JFET normalmente encendido 105 en dirección inversa desde el terminal de fuente al terminal de drenaje.

La FIG. 2 muestra un gráfico de la corriente inversa medida en función de la tensión desde el terminal de drenaje 101 al terminal de fuente 103 del circuito de conmutación de cascode convencional en la FIG. 1 formado con un JFET normalmente encendido de SiC de 1200 voltios y un MOSFET normalmente apagado de silicio de 25 voltios. Este gráfico se obtuvo con una polarización de voltaje cero desde el terminal de control 109 al terminal de origen 103. El circuito de conmutación de cascode en la FIG. 1 tiene una resistencia en conducción de 100 miliohmios. La FIG. 2 demuestra la capacidad de conducción de corriente inversa del circuito de conmutación de cascode en la FIG. 1.

La FIG. 3 muestra un gráfico de las características de conmutación medidas del circuito de conmutación de cascode convencional en la FIG. 1 formado con un JFET normalmente encendido de SiC de 1200 voltios y un MOSFET normalmente apagado de silicio de 25 voltios. La medición se realizó a una condición de carga inductiva de 600 voltios y 21 amperios. Una resistencia de 2,5 ohmios y un núcleo de ferrita conectados en serie están conectados al terminal de control 109 para suprimir las oscilaciones. Las formas de onda de encendido son muy limpias, indicando un proceso de encendido estable y bien controlado. Sin embargo, en el apagado, hay oscilaciones sustanciales en el voltaje de la fuente de la compuerta de cascode, la corriente de drenaje y el voltaje de la fuente de drenaje, lo que puede provocar un funcionamiento inestable del dispositivo y generar problemas de interferencia

electromagnética (EMI).

Se han ideado varios métodos para controlar el proceso de apagado del cascode, pero estos métodos no pueden preservar la capacidad de conducción de corriente inversa del cascode, que es requerida por muchas aplicaciones de conmutación de potencia. Es necesario encender el diodo incorporado sin ningún control de compuerta activo cuando la corriente invierte la dirección, y apagarlo sin el control de compuerta activo cuando se le aplica un voltaje inverso. Debe usarse un diodo adicional en paralelo con el circuito de cascode para proporcionar la función de conducción de corriente inversa con el comportamiento mencionado anteriormente.

La presente invención proporciona un método para controlar eficazmente el proceso de apagado del circuito de conmutación de cascode a la vez que se conserva la capacidad de conducción de corriente inversa del circuito de conmutación de cascode. En este método, un controlador de compuerta proporciona dos salidas con la primera salida acoplada al terminal de compuerta del dispositivo normalmente encendido y la segunda salida acoplada al terminal de compuerta del dispositivo normalmente apagado, de tal manera que, durante el transitorio de apagado, la primera salida del controlador de compuerta genera un pulso de voltaje negativo para apagar activamente el dispositivo normalmente encendido, mientras que el dispositivo normalmente apagado todavía se mantiene en estado ENCENDIDO. De esta manera, el proceso de apagado del circuito de cascode es el mismo que el proceso de apagado de un solo dispositivo normalmente encendido que puede controlarse muy bien. Una vez finalizado el proceso de apagado del circuito de cascode, la segunda salida del controlador de compuerta emite una señal para apagar activamente el dispositivo normalmente apagado, y luego la primera salida del controlador de compuerta vuelve al estado anterior al proceso de apagado que permite que el dispositivo normalmente encendido conduzca una corriente inversa.

La FIG. 4 muestra un diagrama esquemático de circuito de un circuito de conmutación de cascode de acuerdo con una realización de la invención que incluye un MOSFET de silicio normalmente apagado 107 acoplado en serie con un JFET normalmente encendido 105, y un controlador de compuerta 201. Los terminales del drenaje, la fuente y la compuerta del JFET normalmente encendido 105 y el MOSFET de silicio normalmente apagado 107 están marcados como D, S y G, respectivamente. El terminal de drenaje del MOSFET de silicio normalmente apagado 107 está acoplado al terminal de fuente del JFET normalmente encendido 105. El terminal de compuerta del MOSFET de silicio normalmente apagado 107 está acoplado a la segunda salida 205 del controlador de compuerta 201. El terminal de compuerta del JFET normalmente encendido 105 se acopla a la primera salida 203 del controlador de compuerta 201. El terminal de entrada del controlador de compuerta 201, el terminal de drenaje del JFET normalmente encendido 105, y el terminal de fuente del MOSFET de silicio normalmente apagado 107, funcionan como el terminal de control 207, el terminal de drenaje 101 y el terminal de fuente 103 del circuito de conmutación de cascode en la FIG. 4, respectivamente. El controlador de compuerta 201 genera la primera salida 203 y la segunda salida 205 de acuerdo con la señal de entrada del terminal de control 207.

La FIG. 5 muestra un diagrama esquemático que ilustra las formas de onda de funcionamiento del circuito de conmutación de cascode en la FIG. 4. En el estado ENCENDIDO, el controlador de compuerta 201 produce una señal de alto nivel V2H en la segunda salida 205 y una señal de alto nivel V1H en la primera salida 203. La señal de alto nivel V2H en la segunda salida 205 es el voltaje de encendido del MOSFET de silicio normalmente apagado 107, que y está típicamente en un intervalo de +3 voltios a +15 voltios con referencia al terminal de fuente 103. La señal de alto nivel V1H en la primera salida 203 es el voltaje de encendido del JFET normalmente encendido 105, y típicamente está en un intervalo de -2 voltios a +3 voltios con referencia al terminal de fuente 103. En el estado ENCENDIDO, el circuito de conmutación de cascode en la FIG.4 funciona de la misma manera que el circuito de conmutación de cascode convencional en la FIG. 1.

En el estado APAGADO, el controlador de compuerta 201 produce una señal de bajo nivel V2L en la segunda salida 205 y mantiene la señal de alto nivel V1H en la primera salida 203. La señal de bajo nivel V2L en la segunda salida 205 es el voltaje de apagado del MOSFET de silicio normalmente apagado 107, y está típicamente en un intervalo de -15 voltios a 0 voltios con respecto al terminal de fuente 103. Como la señal de alto nivel V1H se mantiene en la primera salida 203 del controlador de compuerta 201 o el terminal de compuerta del JFET normalmente activado 105, el canal del JFET normalmente activado 105 está ENCENDIDO y puede conducir una corriente inversa, por tanto, el circuito de conmutación de cascode en la FIG. 4 puede conducir una corriente inversa durante el estado de APAGADO como el circuito de conmutación de cascode convencional en la FIG. 1.

Durante el proceso de encendido, el controlador de compuerta 201 provocará una transición del circuito de conmutación de cascode en la FIG. 4 desde el estado APAGADO al estado ENCENDIDO cambiando la segunda salida 205 del nivel bajo V2L al nivel alto V2H, a la vez que mantiene la primera salida 203 en el nivel alto de V1H. Durante un proceso de encendido, el circuito de conmutación de cascode en la FIG. 4 funciona de la misma manera que el circuito de conmutación de cascode convencional en la FIG. 1, lo que significa que el proceso de encendido se controla mediante el control del MOSFET de silicio normalmente apagado 107.

Durante un proceso de apagado, el controlador de compuerta 201 provocará una transición del circuito de conmutación de cascode en la FIG. 4 desde el estado ENCENDIDO al estado APAGADO produciendo un pulso de

voltaje negativo en la primera salida 203. El nivel bajo V1L del pulso de voltaje negativo es el voltaje de apagado del JFET normalmente encendido 105 y está típicamente en un intervalo de -8 voltios a -30 voltios para el JFET normalmente encendido de SiC con referencia al terminal de origen 103. Durante un proceso de apagado, el controlador de compuerta 201 primero baja la primera salida 203 de la V1H de alto nivel a la V1L de bajo nivel para apagar el JFET normalmente activado 105 a la vez que mantiene la segunda salida 205 en el nivel alto V2H para mantener el MOSFET de silicio normalmente apagado 107 en el estado ENCENDIDO. Una vez que el JFET normalmente activado 105 se apaga, el circuito de conmutación de cascode en la FIG. 4 estará en estado APAGADO. Como el MOSFET de silicio normalmente apagado 107 se mantiene en estado ENCENDIDO durante el transitorio de apagado, el proceso de apagado es el mismo que el de un único JFET normalmente encendido, lo que significa que el proceso de apagado se controla controlando el JFET normalmente encendido. Los métodos de control para el proceso de apagado de un único JFET normalmente encendido ampliamente y son evidentes para los expertos en la técnica.

5

10

15

20

25

30

35

40

45

50

55

60

65

Después de un primer tiempo de retardo deseado predeterminado td1, el controlador de compuerta 201 baja la segunda salida 205 del V2H de alto nivel al V2L de bajo nivel para ajustar activamente el MOSFET de silicio normalmente apagado 107 en el estado APAGADO y, luego, después de un segundo tiempo de retardo deseado predeterminado td2, eleva la primera salida 203 desde el nivel bajo V1L al nivel alto V1H. De esta manera, el estado APAGADO del circuito de conmutación de cascode en la FIG. 4 se mantiene ajustando activamente el MOSFET de silicio normalmente apagado 107 en el estado APAGADO, que devuelve el circuito al mismo estado que el circuito de conmutación de cascode convencional en la FIG. 1.

El primer tiempo de retardo deseado predeterminado td1 es el período de tiempo durante el cual el JFET normalmente encendido 105 se apaga y no se generarán oscilaciones adicionales si el MOSFET de silicio normalmente apagado 107 se ajusta al estado APAGADO. Si un circuito de aplicación que usa el circuito de conmutación en cascada está diseñado para tener inductancias parásitas muy pequeñas y es capaz de soportar altas tasas de di/dt y dv/dt, entonces el primer tiempo de retardo deseado predeterminado td1 puede ser tan pequeño como 1 nanosegundo, lo que significa que el JFET normalmente encendido 105 y el MOSFET de silicio normalmente apagado 107 se apagan casi al mismo tiempo. Si un circuito de aplicación que usa el circuito de conmutación en cascada tiene inductancias parásitas grandes, el primer tiempo de retardo deseado predeterminado td1 debería ser lo suficientemente largo para permitir que el JFET normalmente encendido 105 controle completamente el proceso de apagado. El JFET normalmente encendido de SiC en general se pueden apagar en menos de 500 nanosegundos. Un intervalo preferido del primer tiempo de retardo deseado predeterminado td1 es de 1 nanosegundo a 500 nanosegundos. El segundo tiempo de retardo deseado predeterminado td2 es el período de tiempo durante el cual el MOSFET de silicio normalmente apagado 107 se ajustado al estado APAGADO y no se generará un pico de corriente o una condición de cortocircuito si se cambia la primera salida 203 del controlador de compuerta 201 desde el nivel bajo V1L hasta el nivel alto V1H. El MOSFET de silicio normalmente apagado 107 puede apagarse muy rápido, incluso menos de 10 ns en esta condición ya que no tiene corriente de carga y tiene un bajo voltaje de drenaje durante la conmutación. La primera salida 203 del controlador de compuerta 201 debe cambiarse desde el nivel bajo V1L al nivel alto V1H antes de que el circuito de conmutación en cascada deba conducir una corriente inversa, lo que significa que el segundo tiempo de retardo deseado predeterminado td2 debe ser lo más corto posible. Un intervalo preferido del segundo tiempo de retardo deseado predeterminado td2 es de 10 nanosegundos a 500 nanosegundos.

Pueden usarse varias topologías de circuito para un controlador de compuerta para proporcionar las formas de onda de funcionamiento de las salidas del controlador de compuerta como se ilustra en la FIG. 5 para controlar el circuito de conmutación de cascode en la FIG. 4. La FIG. 6 muestra una topología ejemplar no limitativa del circuito de control de compuerta 201 que incluye un primer circuito de control de compuerta 211, un segundo circuito de control de compuerta 221, un generador de pulsos negativos 210 y un circuito de retardo de borde descendente 220. El primer circuito de accionamiento de compuerta 211 genera una señal de salida que tiene un alto nivel de V1H y un bajo nivel de V1L, que son adecuados para accionar el JFET normalmente encendido 105 en la FIG. 4. El segundo circuito de controlador de compuerta 221 genera una señal de salida que tiene un alto nivel de V2H y un bajo nivel de V2L, que son adecuados para accionar el MOSFET de silicio normalmente apagado 107 en la FIG. 4. La salida del primer circuito de accionamiento de compuerta 211 está acoplado a la primera salida 203. La salida del segundo circuito de accionamiento de compuerta 221 está acoplado a la segunda salida 205. La salida del generador de pulsos negativos 210 está acoplada a la entrada del primer circuito de accionamiento de compuerta 221. El terminal de control 207 del controlador de compuerta 201 está conectado a ambos terminales de entrada del generador de pulsos negativos 210 y el circuito de retardo de borde descendente 220.

El generador de pulsos negativos 210 incluye un inversor 219, una resistencia 215, un condensador 217 y una compuerta NAND 213 provistos con una primera entrada y una segunda entrada. El generador de pulsos negativos 210 se usa para generar una señal de pulsos negativos tras recibir un borde descendente en la señal de entrada desde el terminal de control 207. Un borde descendente es una transición de una señal lógica de la lógica 1 a la lógica 0. El terminal de salida del inversor 219 está conectado al primer terminal de entrada del generador de pulsos NAND 213. El terminal de entrada del inversor 219 está conectado al terminal de entrada del generador de pulsos

negativos 210. La resistencia 215 está conectada entre la segunda entrada de la compuerta NAND 213 y el terminal de entrada del generador de pulsos negativos 210. El condensador 217 está conectado entre la segunda entrada de la compuerta NAND 213 y la referencia de tierra de la señal del controlador de compuerta 230. Cuando se produce un borde descendente en la señal de entrada, la primera entrada de la compuerta NAND 213 se cambia de la lógica 0 a la lógica 1. La segunda entrada de la compuerta NAND 213 se mantendrá en la lógica 1 ya que el voltaje a través del condensador 217 no puede cambiar instantáneamente. Por lo tanto, la salida de la compuerta NAND 213 cambiará de la lógica 1 a la lógica 0, lo que hace que la salida del primer circuito de accionamiento de compuerta 211 cambie del nivel alto V1H al nivel bajo V1L. El voltaje a través del condensador 217 disminuirá con el tiempo debido a la descarga del condensador 217 a través de la resistencia 215. Cuando el voltaje a través del condensador 217 es más bajo que el voltaje máximo de la lógica 0, la segunda entrada de la compuerta NAND 213 se convierte en lógica 0, lo que hace que la salida de la compuerta NAND 213 cambie de la lógica 0 a la lógica 1, lo que, a su vez, hace que la salida del primer circuito controlador 211 cambie del nivel bajo V1L al nivel alto V1H. El producto de la resistencia de la resistencia 215 y la capacitancia del condensador 217 determina el tiempo durante el que el voltaje a través del condensador 217 caerá al voltaje máximo de la lógica 0 y determina además la amplitud del pulso del pulso de voltaje negativo en la primera salida 203. La amplitud de pulso deseada de una suma del primer tiempo de retardo deseado predeterminado td1 y el segundo tiempo de retardo deseado predeterminado td2 como se muestra en la FIG. 5 puede obtenerse seleccionando la resistencia apropiada para la resistencia 215 y la capacitancia apropiada para el condensador 217.

El generador de pulsos negativos 210 es un circuito monoestable, activado por borde descendente y su salida permanece en la lógica 1 durante el estado estable. Un borde anterior, que es una transición de una señal de la lógica 0 a la lógica 1, no cambiará la salida del generador de pulsos negativos 210.

El circuito de retardo de borde descendente 220 incluye una resistencia 225, un condensador 227 y una compuerta OR 223 provistas de una primera entrada y una segunda entrada. El circuito de retardo de borde descendente 220 se usa para generar un tiempo de retardo para el borde descendente de la señal de entrada. El primer terminal de entrada de la compuerta OR 223 está conectado al terminal de entrada del circuito de retardo de borde descendente 220. La resistencia 225 está conectada entre la segunda entrada de la compuerta OR 223 y el terminal de entrada del retardo de borde descendente 220. El condensador 227 está conectado entre la segunda entrada de la compuerta OR 223 y la referencia de tierra de la señal del controlador de la compuerta 230. Cuando aparece un borde descendente en la señal de entrada, la primera entrada de la compuerta OR 223 se cambia de la lógica 1 a la lógica 0 y la segunda entrada de la compuerta OR 223 se mantendrá en la lógica 1 ya que el voltaje a través del condensador 227 no puede cambiar instantáneamente. Por tanto, la salida de la compuerta OR 223 no cambiará y permanecerá en la lógica 1. El voltaje a través del condensador 227 disminuirá con el tiempo debido a la descarga del condensador 227 a través de la resistencia 225. Cuando el voltaje a través del condensador 227 es menor que el voltaje máximo de la lógica 0, la segunda entrada de la compuerta OR 223 se convierte en la lógica 0, haciendo que la salida de la compuerta OR 223 cambie de la lógica 1 a la lógica 0, que, a su vez, hace que la salida del segundo circuito controlador 221 cambiar del nivel alto V2H al nivel bajo V2L. El producto de la resistencia de la resistencia 225 y la capacitancia del condensador 227 determina el tiempo para que el voltaje a través del condensador 227 caiga hasta el voltaje máximo de la lógica 0 y determina además el tiempo de retardo del borde descendente de la señal de entrada. El primer tiempo de retardo deseado predeterminado td1 como se muestra en la FIG. 5 puede obtenerse seleccionando la resistencia apropiada de la resistencia 225 y la capacitancia apropiada del condensador 227. El circuito de retardo de borde descendente 220 no tiene efecto sobre el borde anterior de la señal de entrada.

45

50

55

60

5

10

15

20

25

30

35

40

El concepto de la presente invención se ha introducido por tanto de acuerdo con una realización, en la que el semiconductor normalmente encendido es un JFET normalmente encendido y el dispositivo semiconductor normalmente apagado es un MOSFET de silicio normalmente apagado. También pueden usarse otros tipos de dispositivos semiconductores normalmente encendidos y dispositivos semiconductores normalmente apagados para formar el circuito de conmutación de cascode. El dispositivo semiconductor normalmente encendido podría estar compuesto por un único dispositivo o múltiples dispositivos conectados en una disposición en paralelo. Los dispositivos semiconductores normalmente encendidos ejemplares incluyen JFET, MOSFET, transistores de inducción estática (SIT), y transistores de alta movilidad de electrones (HEMT); sin embargo, en general, se prefieren los JFET normalmente encendidos de SiC para las aplicaciones que requieren una capacidad de bloqueo de voltaje de más de 1000 V y los HEMT normalmente encendidos de GaN para las aplicaciones de clase 650V. Estos dispositivos normalmente encendidos pueden conducir una corriente inversa desde el terminal de fuente al terminal de drenaje con una baja caída de voltaje con una polarización de voltaje de fuente de compuerta cero. El voltaje de bloqueo máximo del JFET de SiC es de aproximadamente 10.000 voltios. Por encima de los 10.000 voltios, se prefieren los dispositivos bipolares de SiC, como un transistor bipolar de compuerta aislada (IGBT) o un transistor de apagado de compuerta (GTO) de SiC, ya que tienen una resistencia de en conducción mucho menor que el JFET de SiC. El voltaje de bloqueo preferido del JFET de SiC está en un intervalo de 1000 voltios a 4000 voltios. La estructura lateral y la descomposición dieléctrica del HEMT de GaN limitan el voltaje de bloqueo máximo de la potencia del HEMT de GaN. El voltaje de bloqueo preferido del HEMT de GaN está en un intervalo de 300 voltios a 1000 voltios.

### ES 2 746 278 T3

El dispositivo semiconductor normalmente apagado podría estar compuesto por un único dispositivo o múltiples dispositivos conectados en disposición en paralelo con un voltaje de bloqueo en un intervalo de 10 voltios a 100 voltios. Los dispositivos semiconductores normalmente apagados ejemplares incluyen JFET, MOSFET, transistores de inducción estática (SIT), transistores de unión bipolar (BJT), y transistores bipolares de compuerta aislada (IGBT); sin embargo, no se prefieren los JFET, los SIT y los BJT porque, en general, no tienen un diodo de cuerpo incorporado y, por lo tanto, no son adecuados para conducir una corriente inversa. Necesitan un diodo de bajo voltaje adicional para conducir una corriente inversa. Se prefieren los MOSFET de silicio normalmente apagados de bajo voltaje y los valores de voltaje preferidos de los MOSFET de silicio de bajo voltaje son típicamente de 20 voltios a 50 voltios. Los MOSFET de silicio tienen un diodo de cuerpo incorporado que puede conducir corriente inversa desde el terminal de fuente al terminal de drenaje durante el estado apagado.

En una realización, un circuito de conmutación de cascode incluye un dispositivo semiconductor normalmente encendido, un dispositivo semiconductor normalmente apagado y un controlador de compuerta. El dispositivo semiconductor normalmente apagado tiene una ruta de corriente acoplada en serie con una ruta de corriente del dispositivo semiconductor normalmente encendido. El controlador de compuerta tiene una primera salida acoplada a un terminal de compuerta del dispositivo semiconductor normalmente encendido y una segunda salida acoplada a un terminal de compuerta del dispositivo semiconductor normalmente apagado. El controlador de compuerta está configurado de tal manera que el proceso de encendido del circuito de conmutación de cascode se controla controlando el dispositivo semiconductor normalmente encendido.

En una realización, el dispositivo semiconductor normalmente encendido es un dispositivo semiconductor compuesto. En una realización preferida, el dispositivo semiconductor normalmente encendido es un JFET de SiC. En otra realización preferida, el dispositivo semiconductor normalmente encendido es un HEMT de GaN. En una realización, el circuito de conmutación de cascode se apaga apagando el dispositivo semiconductor normalmente encendido. En una realización, el circuito de conmutación de cascode se enciende encendiendo el dispositivo semiconductor normalmente apagado.

En una realización, se proporciona un método para controlar el proceso de conmutación de un circuito de conmutación de cascode que incluye proporcionar un dispositivo semiconductor normalmente encendido con una ruta de corriente acoplada en serie con una ruta de corriente de un dispositivo semiconductor normalmente apagado y un controlador de compuerta configurado de tal manera que el proceso de encendido del circuito de conmutación de cascode se controla controlando el dispositivo semiconductor normalmente apagado, y el proceso de apagado del circuito de conmutación de cascode se controla controlando el dispositivo semiconductor normalmente encendido.

En una realización, el método incluye formar el dispositivo semiconductor normalmente encendido con un semiconductor compuesto. En una realización, el método incluye formar el dispositivo semiconductor compuesto con un JFET de carburo de silicio. En una realización, el método incluye formar el dispositivo semiconductor compuesto con un HEMT de GaN. En una realización, el método incluye formar el dispositivo semiconductor normalmente apagado con un MOSFET de silicio. En una realización, el método incluye encender el circuito de conmutación de cascode encendiendo el dispositivo semiconductor normalmente apagado. En una realización, el método incluye apagar el circuito de conmutación de cascode apagando el dispositivo semiconductor normalmente encendido.

La descripción anterior indica que se ofrece un gran grado de flexibilidad en términos de la invención. Aunque se han descrito varias realizaciones con bastante detalle con referencia a ciertas versiones preferidas de las mismas, son posibles otras versiones. Por lo tanto, el alcance de las reivindicaciones adjuntas no debe limitarse a la descripción de las versiones preferidas contenidas en la presente.

### **REIVINDICACIONES**

- **1.** Un circuito de conmutación de cascode que comprende un dispositivo semiconductor normalmente encendido (105), un dispositivo semiconductor normalmente apagado (107) y un controlador de compuerta (201), en donde:

- dicho dispositivo semiconductor normalmente encendido (105) y dicho dispositivo semiconductor normalmente apagado (107) tienen cada uno un terminal de compuerta, un terminal de drenaje y un terminal de fuente:

- dicho controlador de compuerta (201) tiene una primera salida (203) y una segunda salida (205);

5

20

25

30

- dicha primera salida (203) de dicho controlador de compuerta (201) está acoplada a dicho terminal de compuerta de dicho dispositivo semiconductor normalmente encendido (105);

- dicha segunda salida (205) de dicho controlador de compuerta (201) está acoplada a dicho terminal de compuerta de dicho dispositivo semiconductor normalmente apagado (107);

- dicho terminal de drenaje de dicho dispositivo semiconductor normalmente apagado (107) está acoplado a dicho terminal de fuente de dicho dispositivo semiconductor normalmente encendido (105) de tal manera que se forma una ruta de corriente a través de dicho dispositivo semiconductor normalmente encendido (105) y dicho dispositivo semiconductor normalmente apagado (107):

- dicho controlador de compuerta (201) está configurado de tal manera que un proceso de encendido de dicho circuito de conmutación de cascode se controla controlando dicho dispositivo semiconductor normalmente apagado (107);

- un proceso de apagado de dicho circuito de conmutación de cascode está configurado para ser controlado controlando dicho dispositivo semiconductor normalmente encendido (105); y

- durante dicho proceso de apagado de dicho circuito de conmutación de cascode, dicho controlador de compuerta (201) está configurado para provocar una transición de dicho circuito de conmutación de cascode desde el estado ENCENDIDO al estado de APAGADO cambiando dicha primera salida (203) de dicho controlador de compuerta (201) de un primer nivel de voltaje a un segundo nivel de voltaje para apagar dicho dispositivo semiconductor normalmente encendido (105).

- luego, después de un primer tiempo de retardo predeterminado, cambiando dicha segunda salida de dicho controlador de compuerta (201) de un tercer nivel de voltaje a un cuarto nivel de voltaje para apagar dicho dispositivo semiconductor normalmente apagado (107), y

- después de un segundo tiempo de retardo predeterminado, cambiando dicha primera salida (203) de dicho controlador de compuerta (201) de dicho segundo nivel de voltaje a dicho primer nivel de voltaje.

- 2. El circuito de conmutación de cascode de la reivindicación 1, en el que dicho dispositivo semiconductor normalmente encendido (105) comprende un dispositivo semiconductor compuesto.

- **3.** El circuito de conmutación de cascode de la reivindicación 2, en el que dicho dispositivo semiconductor compuesto comprende un dispositivo de carburo de silicio.

- **4.** El circuito de conmutación de cascode de la reivindicación 3, en el que dicho dispositivo de carburo de silicio comprende un transistor de efecto de campo de unión de carburo de silicio.

- **5.** El circuito de conmutación de cascode de la reivindicación 2, en el que dicho dispositivo semiconductor compuesto comprende un dispositivo de nitruro de galio.

- **6.** El circuito de conmutación de cascode de la reivindicación 5, en el que dicho dispositivo de nitruro de galio comprende un transistor de movilidad de electrones de nitruro de galio.

- 7. El circuito de conmutación de cascode de la reivindicación 1, en el que dicho dispositivo semiconductor normalmente apagado (107) comprende un transistor de efecto de campo de semiconductor de óxido de metal de silicio.

- 8. El circuito de conmutación de cascode de la reivindicación 1, en el que, durante dicho proceso de encendido de dicho circuito de conmutación de cascode, dicho controlador de compuerta (201) está configurado para provocar una transición de dicho circuito de conmutación de cascode desde el estado APAGADO al estado ENCENDIDO cambiando dicha segunda salida de dicho controlador compuerta (201) desde dicho cuarto nivel de voltaje hasta dicho tercer nivel de voltaje para encender dicho dispositivo semiconductor normalmente apagado (107), mientras se mantiene dicha primera salida (203) de dicho controlador de compuerta (201) en dicho primer nivel de voltaje.

- 9. El circuito de conmutación de cascode de la reivindicación 1, en el que dicho primer tiempo de retardo predeterminado tiene un valor en el intervalo de aproximadamente 1 nanosegundo a aproximadamente 500 nanosegundos, y dicho segundo tiempo de retardo predeterminado tiene un valor en el intervalo de aproximadamente 10 nanosegundos a aproximadamente 500 nanosegundos.

- 65 10. El circuito de conmutación de cascode de la reivindicación 1 en el que, con una referencia a tierra a dicho

### ES 2 746 278 T3

terminal de fuente de dicho dispositivo semiconductor normalmente apagado (107), dicho primer nivel de voltaje tiene un valor en el intervalo de aproximadamente -2 voltios a 3 voltios, dicho segundo nivel de voltaje tiene un valor en el intervalo de aproximadamente -8 voltios a -30 voltios, dicho tercer nivel de voltaje tiene un valor en el intervalo de aproximadamente 3 voltios a 15 voltios, y dicho cuarto nivel de voltaje tiene un valor en el intervalo de aproximadamente 0 voltios a -15 voltios.

- **11.** El circuito de conmutación de cascode de la reivindicación 1, en el que dicho dispositivo semiconductor normalmente encendido (105) comprende un dispositivo semiconductor, o más de un dispositivo semiconductor conectado en paralelo, con una capacidad de bloqueo de voltaje en el intervalo de aproximadamente 300 voltios a aproximadamente 10.000 voltios.

- **12.** El circuito de conmutación de cascode según la reivindicación 11, en el que dicho dispositivo semiconductor normalmente apagado (107) comprende un dispositivo semiconductor, o más de un dispositivo semiconductor conectado en paralelo, con una capacidad de bloqueo de voltaje en el intervalo de aproximadamente 10 voltios a aproximadamente 100 voltios.

- **13.** El circuito de conmutación de cascode de la reivindicación 1, en el que dicho controlador de compuerta (2010) comprende además un único terminal de control (207).

- 20 14. El circuito de conmutación de cascode de la reivindicación 13, en el que dicho único terminal de control (207) de dicho controlador de compuerta (201) está configurado para controlar la generación de dicha primera salida (203) y dicha segunda salida (205) de dicho controlador de puerta (201).

- 15. Un método para operar un código de cascode por un controlador de compuerta, el método comprendiendo:

controlar un proceso de encendido de dicho cascode por dicho controlador de compuerta (201) controlando un dispositivo semiconductor normalmente apagado (107); y

controlar un proceso de apagado de dicho cascode por dicho controlador de compuerta (201) controlando un dispositivo semiconductor normalmente encendido (105),

en donde, durante dicho proceso de apagado de dicho cascode, dicho controlador de compuerta (201) provoca una transición de dicho cascode del estado ENCENDIDO al estado APAGADO cambiando dicha primera salida (203) de dicho controlador de compuerta (201) desde un primer nivel de voltaje a un segundo nivel de voltaje para apagar dicho dispositivo semiconductor normalmente encendido (105), luego, después de un primer tiempo de retardo predeterminado, cambiar dicha segunda salida de dicho controlador de compuerta (201) de un tercer nivel de voltaje a un cuarto nivel de voltaje para apagar dicho dispositivo semiconductor normalmente apagado (107), y después de un segundo tiempo de retardo predeterminado, cambiar dicha primera salida (203) de dicho controlador de compuerta (201) de dicho segundo nivel de voltaje a dicho primer nivel de voltaje,

en donde el cascode comprende dicho dispositivo semiconductor normalmente encendido (105) y dicho dispositivo semiconductor normalmente apagado (107) teniendo cada uno un terminal de compuerta, un terminal de drenaje, y un terminal fuente, dicho terminal de drenaje de dicho dispositivo semiconductor normalmente apagado (107) estando acoplado a dicho terminal fuente de dicho dispositivo semiconductor normalmente encendido (105) de tal manera que se forme una ruta de corriente a través de dicho dispositivo semiconductor normalmente encendido (105) y dicho dispositivo semiconductor normalmente apagado (107),

en donde el controlador de compuerta (201) comprende una primera salida (203) y una segunda salida (205) acopladas a dichos terminales de compuerta de dichos dispositivos semiconductores normalmente encendido y normalmente apagado, respectivamente.

50

5

10

15

25

30

35

40

45

55

60

ESTADO DE LA TECNICA FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6