# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 746 479

51 Int. Cl.:

**G06F 9/44** (2008.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 20.02.2015 PCT/EP2015/053638

(87) Fecha y número de publicación internacional: 24.09.2015 WO15139917

(96) Fecha de presentación y número de la solicitud europea: 20.02.2015 E 15705333 (1)

(97) Fecha y número de publicación de la concesión europea: 21.08.2019 EP 3120239

(54) Título: Secuencia de arranque común para el programa utilitario de control capaz de ser inicializado en múltiples arquitecturas

(30) Prioridad:

18.03.2014 US 201414217800 26.11.2014 US 201414554313

Fecha de publicación y mención en BOPI de la traducción de la patente: **06.03.2020**

(73) Titular/es:

INTERNATIONAL BUSINESS MACHINES CORPORATION (100.0%) New Orchard Road Armonk, New York 10504, US

(72) Inventor/es:

**GSCHWIND, MICHAEL KARL**

74) Agente/Representante:

ISERN JARA, Jorge

## **DESCRIPCIÓN**

Secuencia de arranque común para el programa utilitario de control capaz de ser inicializado en múltiples arquitecturas

Campo

Uno o más aspectos se relacionan, en general, con configuraciones de entornos informáticos, y en particular, con el soporte de múltiples configuraciones.

Técnica antecedente

Los entornos informáticos ofrecen un rango de capacidades y funciones dependiendo de las configuraciones arquitectónicas de los entornos. Dos arquitecturas que se han ofrecido por IBM® incluyen ESA/390 y z/Architecture®. ESA/390 es una arquitectura predecesora de z/Architecture®. Sin embargo, cuando se introdujo la z/Architecture, ESA/390 continúo siendo soportada. Para soportar ambas arquitecturas en un entorno, se siguen ciertos procedimientos. Por ejemplo, con el encendido, se arranca ESA/390, y luego, se puede hacer una conmutación a la z/Architecture, si se desea. Esto permite que el software heredado continué ejecutándose sin un cambio. Otros de dichos procedimientos se proporcionan con el fin de soportar ambas configuraciones arquitectónicas en un entorno.

20

25

30

5

10

15

El mantener una arquitectura anterior incluso cuando el software ha pasado a una arquitectura posterior agrega complejidad. El número de Publicación de Solicitud de Patente de los Estados Unidos US 2012/0297180 A1 Teng, C-Y, et al. "Method of Switching Between Multiple Operating Systems of Computer System", 22 de noviembre de 2012) divulga un método de conmutación entre múltiples sistemas operativos de un sistema informático que incluyen las siguientes etapas. En primer lugar, el sistema informático se encuentra en un entorno de un primer sistema operativo. Luego, se activa una interrupción de gestión del sistema para permitir que el sistema informático entre en un modo de gestión del sistema, y una autoridad de control del sistema informático se transfiere desde el primer sistema operativo hasta un sistema básico de entrada y salida. Luego se crea una copia de seguridad de un parámetro ambiental del primer sistema operativo. Si el segundo parámetro ambiental no está incluido en el sistema informático, se carga un segundo sistema operativo en modo normal. Por otro lado, si el segundo parámetro ambiental está incluido en el sistema informático, el segundo sistema operativo se arranca de acuerdo con el segundo parámetro ambiental.

Por lo tanto, subsiste la necesidad en la técnica de tratar el problema mencionado anteriormente.

35

## Resumen

De acuerdo con la presente invención se proporcionan un método, un sistema, un producto de programa informático y un programa informático de acuerdo con las reivindicaciones independientes.

40

Se obtienen características y ventajas adicionales. Otras realizaciones y aspectos preferidos se describen en detalle en el presente documento y se consideran una parte de la invención reivindicada.

Breve descripción de los dibujos

45

65

Ahora se describirá la presente invención solo a modo de ejemplo, con referencia a las realizaciones preferidas, como se ilustra en las siguientes figuras:

La Figura 1 representa un ejemplo de un entorno informático para incorporar y utilizar uno o más aspectos de una funcionalidad de secuencia de arrangue común, de acuerdo con una realización preferida de la presente invención:

- La Figura 2 representa otro ejemplo de un entorno informático para incorporar y utilizar uno o más aspectos de una funcionalidad de secuencia de arranque común, de acuerdo con una realización preferida de la presente invención; La Figura 3A representa aún otro ejemplo de un entorno informático para incorporar y utilizar uno o más aspectos de una funcionalidad de secuencia de arranque común, de acuerdo con una realización preferida de la presente invención:

- La Figura 3B representa detalles adicionales de la memoria de la Figura 3A, de acuerdo con una realización preferida de la presente invención;

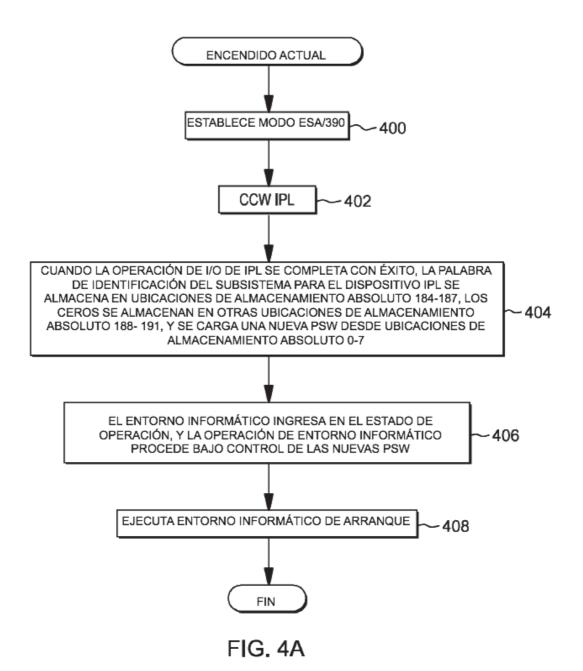

- La Figura 4A representa una realización de la lógica para encender un entorno informático en un modo arquitectónico, de acuerdo con una realización preferida de la presente invención;

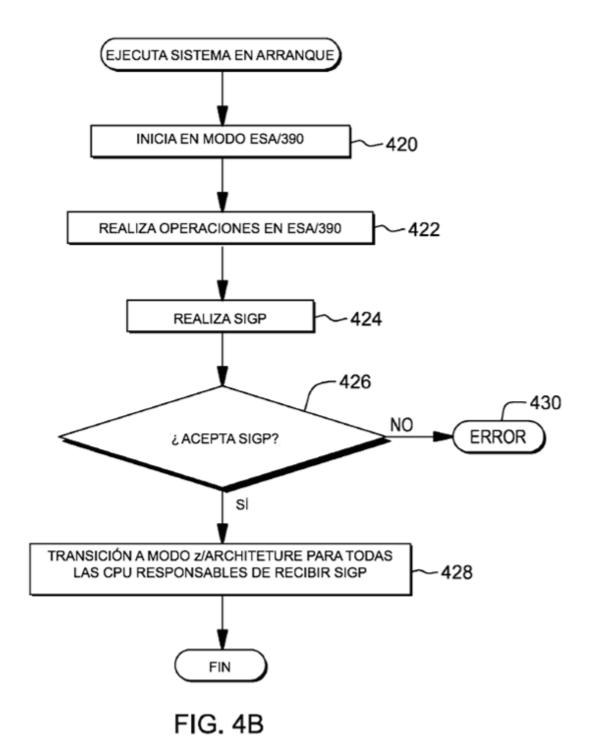

- La Figura 4B representa una realización de procesamiento adicional asociado con el proceso de encendido de la Figura 4A, de acuerdo con una realización preferida de la presente invención;

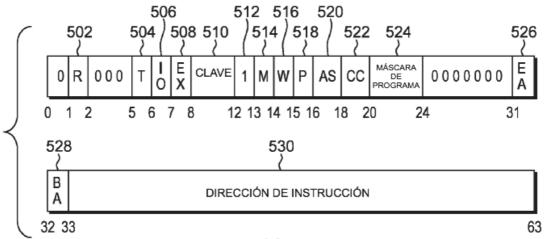

- La Figura 5 representa una realización de un formato de una palabra de estado de programa, de acuerdo con una realización preferida de la presente invención;

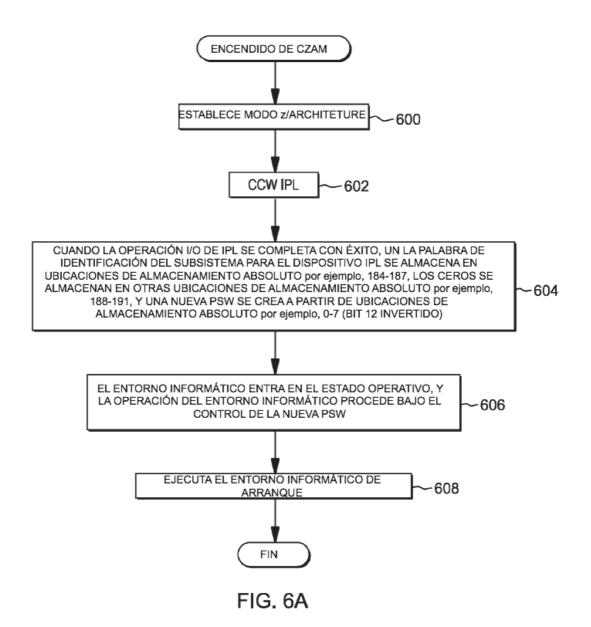

- La Figura 6A representa una realización de la lógica para encender un entorno informático en un modo arquitectónico diferente del modo arquitectónico encendido en la Figura 4A, de acuerdo con una realización preferida de la presente invención;

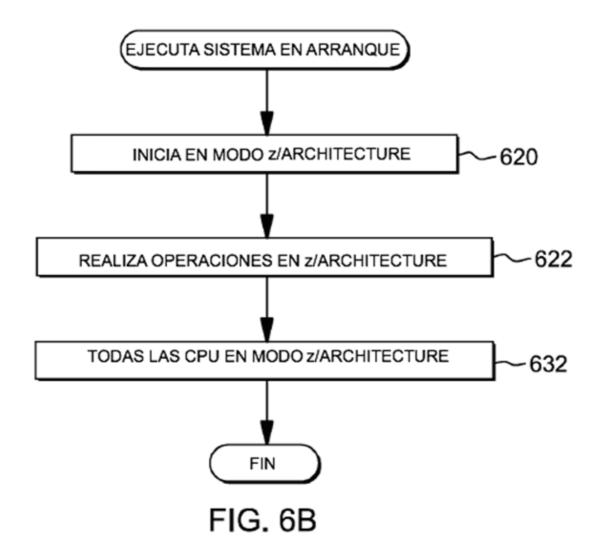

- La Figura 6B representa una realización de procesamiento adicional asociado con el proceso de encendido de la Figura 6A, de acuerdo con una realización preferida de la presente invención;

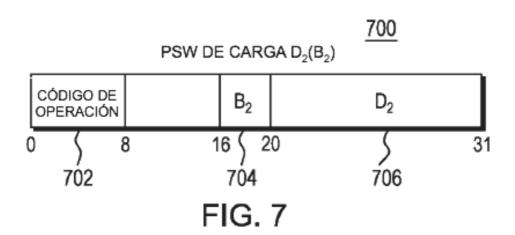

- La Figura 7 representa un formato de ejemplo de una instrucción de Palabra de Estado de Programa de Carga, de acuerdo con una realización preferida de la presente invención;

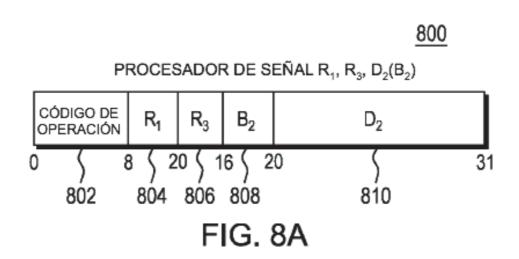

- La Figura 8A representa un formato de ejemplo de una instrucción de Procesador de Señal, de acuerdo con una realización preferida de la presente invención;

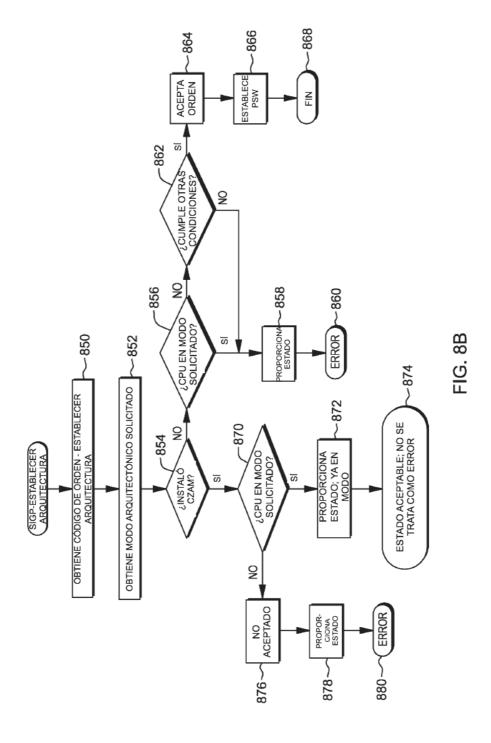

- La Figura 8B representa una realización del procesamiento asociado con la instrucción de Procesador de Señal de la Figura 8A, de acuerdo con una realización preferida de la presente invención;

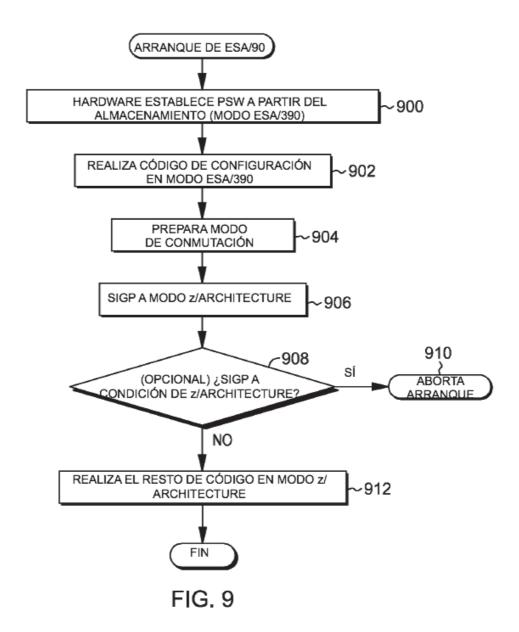

- La Figura 9 representa una realización de lógica para realizar un arranque en el que un programa utilitario de control se inicializa en ESA/390, de acuerdo con una realización preferida de la presente invención;

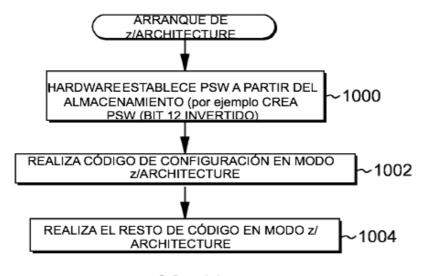

- La Figura 10 representa una realización de lógica para realizar un arranque en el que un programa utilitario de control se inicializa en z/Architecture;

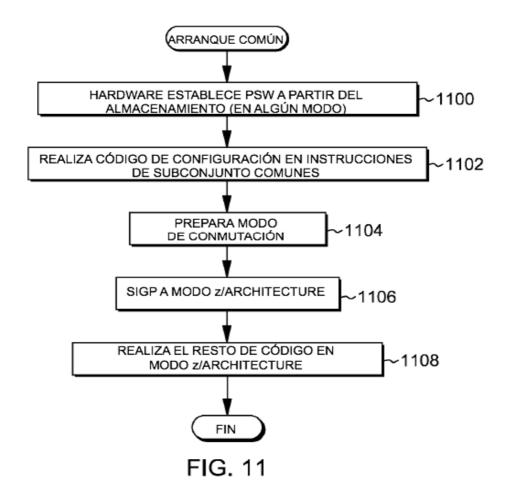

- La Figura 11 representa una realización de lógica para una secuencia de arranque común, de acuerdo con una realización preferida de la presente invención;

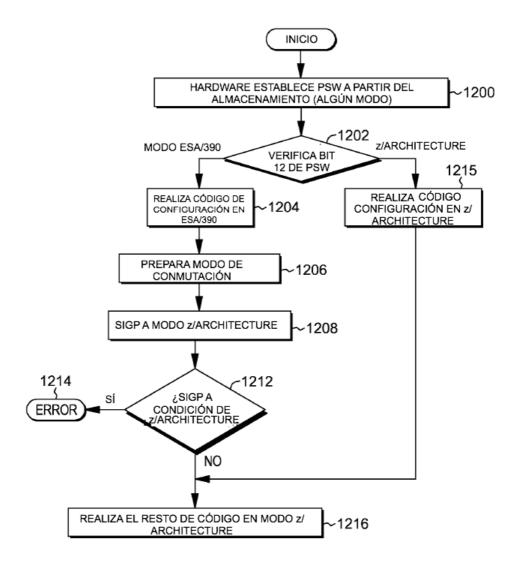

- La Figura 12 representa otra realización de lógica para una secuencia de arranque común, de acuerdo con una realización preferida de la presente invención;

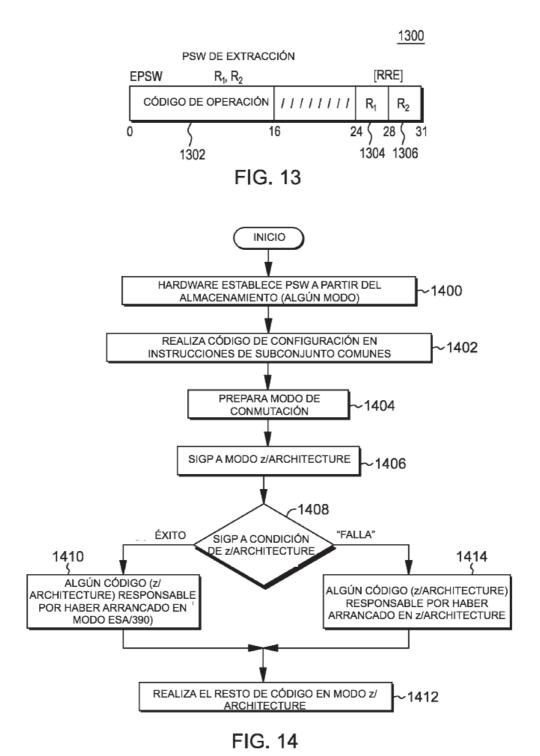

- La Figura 13 representa un formato de ejemplo de una Palabra de Estado de Programa de Extracto, de acuerdo con una realización preferida de la presente invención;

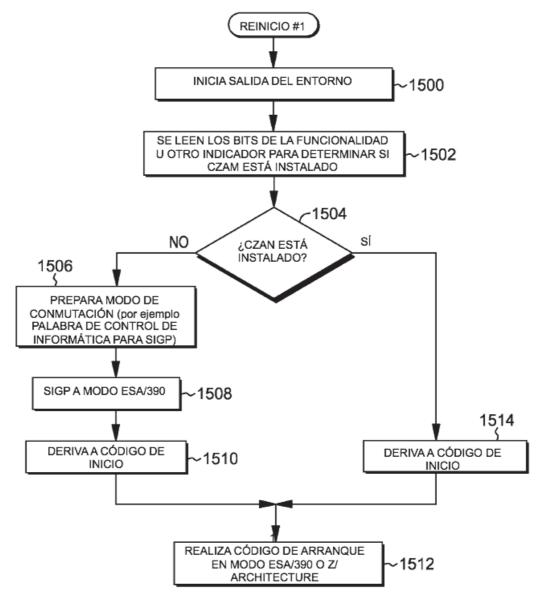

- La Figura 14 representa una realización adicional de lógica para una secuencia de arranque común, de acuerdo con una realización preferida de la presente invención;

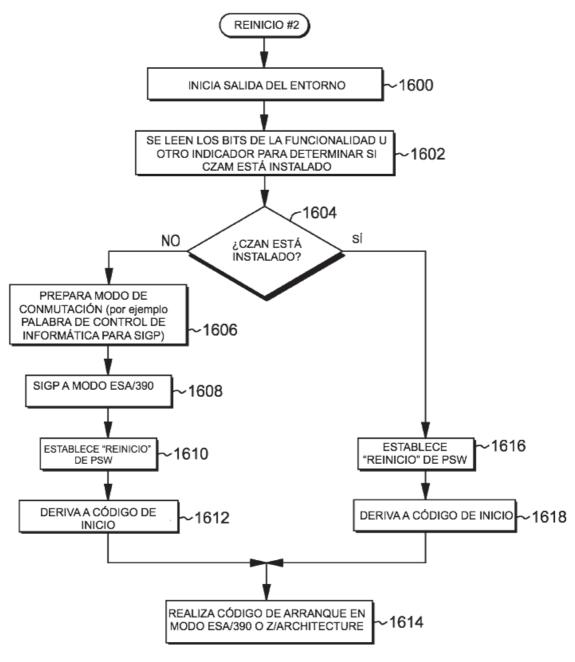

- La Figura 15 representa una realización de lógica para realizar un reinicio para volver a poner en marcha un programa utilitario de control, de acuerdo con una realización preferida de la presente invención;

- La Figura 16 representa otra realización de lógica para realizar un reinicio para volver a poner en marcha un programa utilitario de control, de acuerdo con una realización preferida de la presente invención;

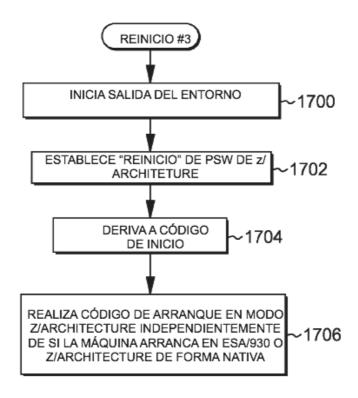

- La Figura 17 representa todavía otra realización de lógica para realizar un reinicio para volver a poner en marcha un programa utilitario de control, de acuerdo con una realización preferida de la presente invención;

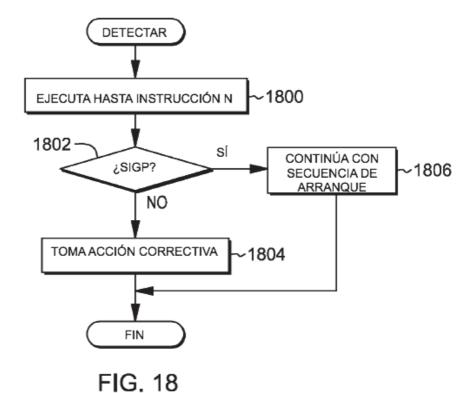

- La Figura 18 representa una realización de lógica para detectar un programa utilitario de control incompatible que se relaciona con la secuencia de arranque, de acuerdo con una realización preferida de la presente invención;

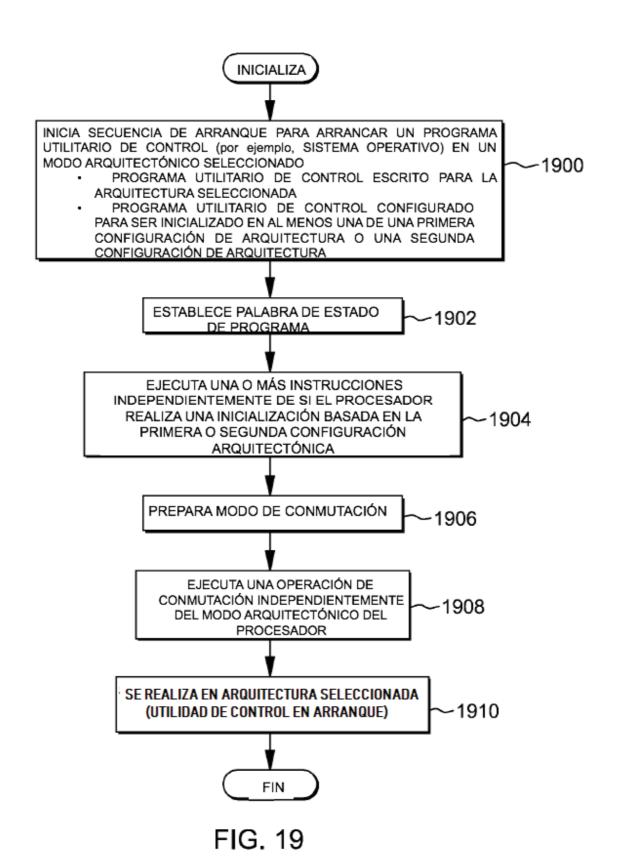

- La Figura 19 representa una realización del procesamiento asociado con realizar un arranque de un programa utilitario de control, de acuerdo con una realización preferida de la presente invención;

- La Figura 20 representa una realización de un producto de programa informático, de acuerdo con la técnica anterior, y en el que se puede implementar una realización preferida de la presente invención;

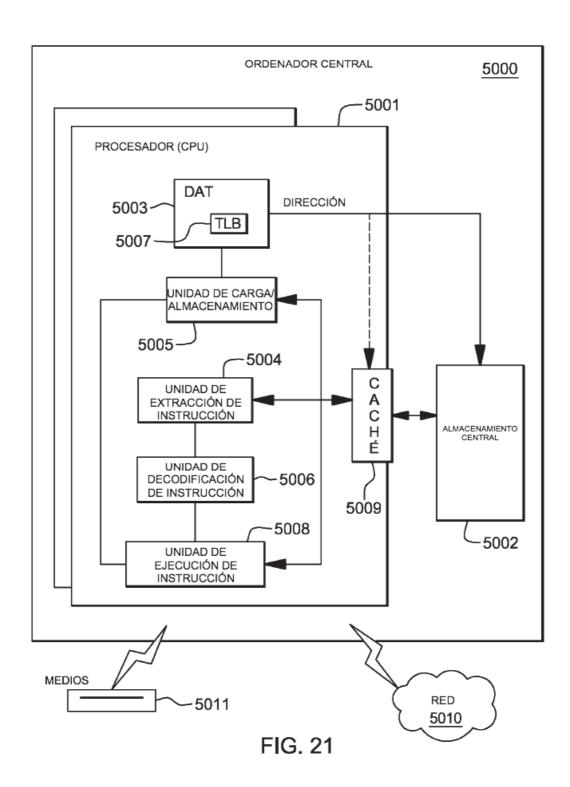

- La Figura 21 representa una realización de un sistema informático central, de acuerdo con la técnica anterior, y en el que se puede implementar una realización preferida de la presente invención;

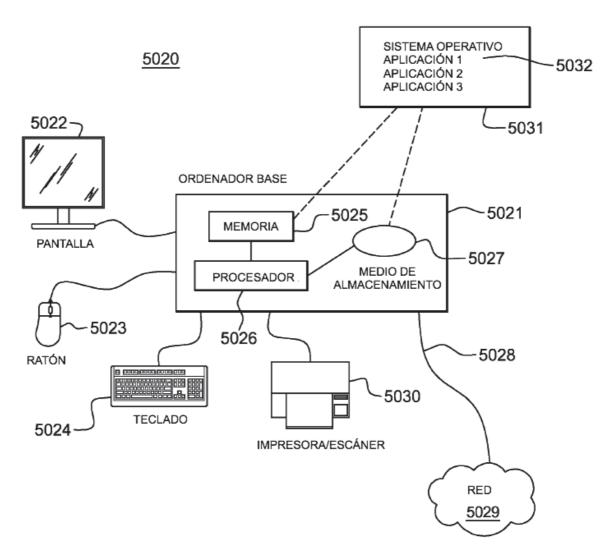

- La Figura 22 representa un ejemplo adicional de un sistema informático, de acuerdo con la técnica anterior, y en la que se puede implementar una realización preferida de la presente invención;

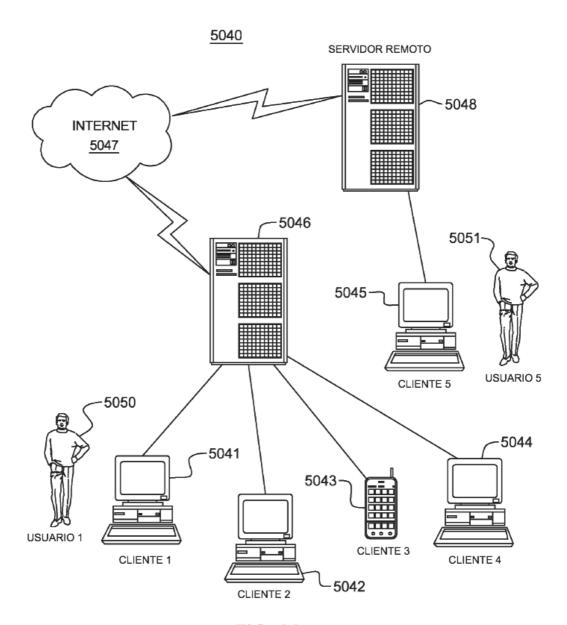

- La Figura 23 representa otro ejemplo de un sistema informático que comprende una red informática, de acuerdo con la técnica anterior, y en la que se puede implementar una realización preferida de la presente invención;

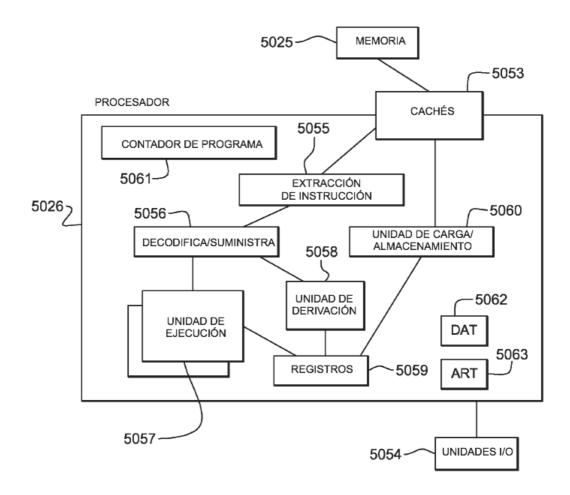

- La Figura 24 representa una realización de varios elementos de un sistema informático, de acuerdo con la técnica anterior, y en la que se puede implementar una realización preferida de la presente invención;

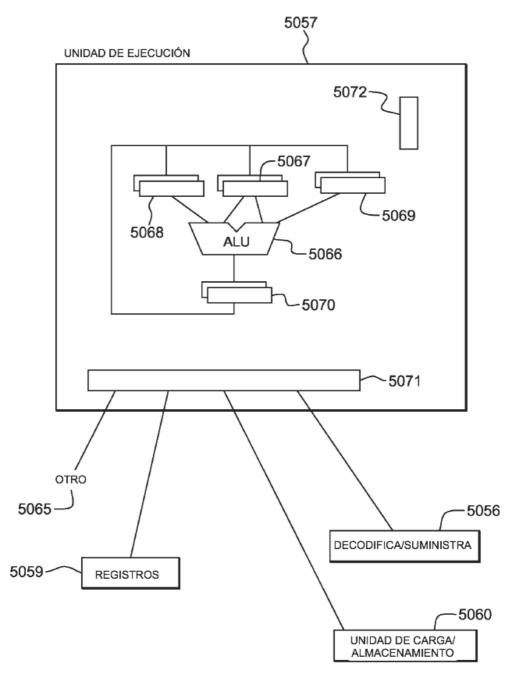

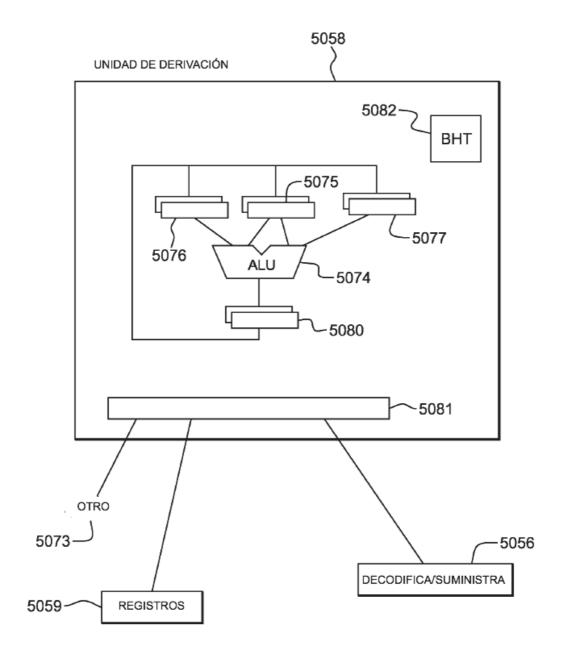

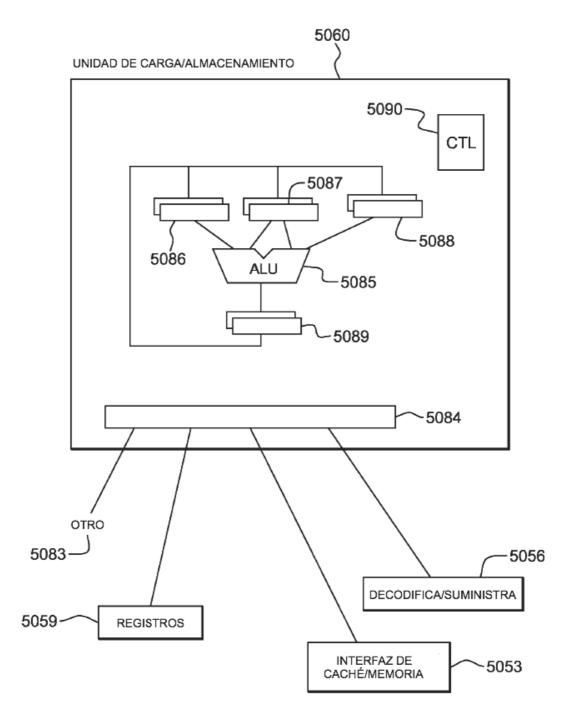

- La Figura 25A representa una realización de la unidad de ejecución del sistema informático de La Figura 24, de acuerdo con la técnica anterior, y en la que se puede implementar una realización preferida de la presente invención; La Figura 25B representa una realización de la unidad de derivación del sistema informático de la Figura 24, de acuerdo con la técnica anterior, y en la que se puede implementar una realización preferida de la presente invención;

- La Figura 25C representa una realización de la unidad de carga/almacenamiento del sistema informático de la Figura 24, de acuerdo con la técnica anterior, y en la que se puede implementar una realización preferida de la presente invención:

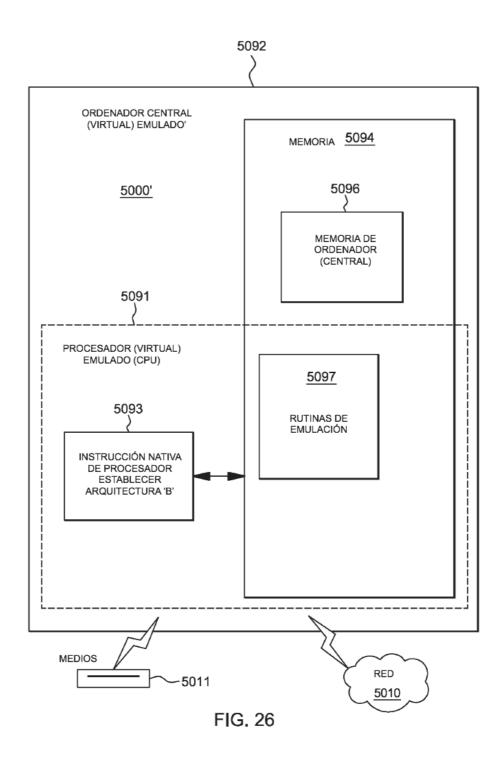

- La Figura 26 representa una realización de un sistema informático central emulado;

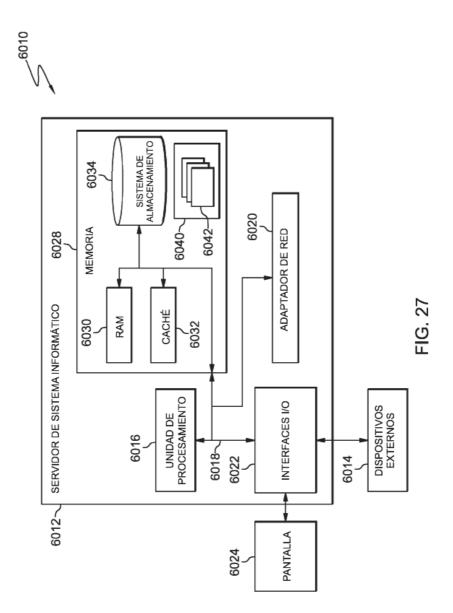

- La Figura 27 representa una realización de un nodo informático en nube, de acuerdo con la técnica anterior, y en la que se puede implementar una realización preferida de la presente invención;

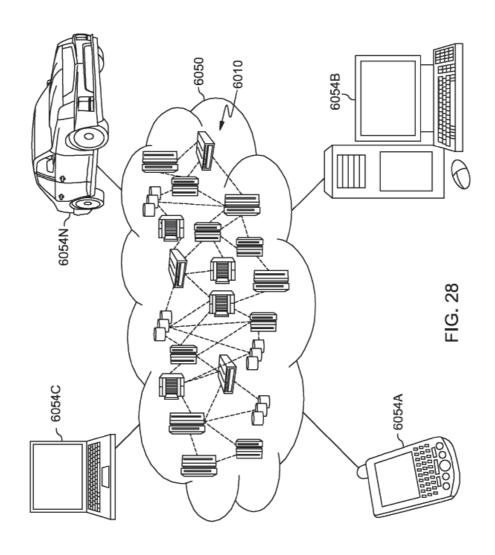

- La Figura 28 representa una realización de un entorno informático en nube, de acuerdo con la técnica anterior, y en la que se puede implementar una realización preferida de la presente invención; y

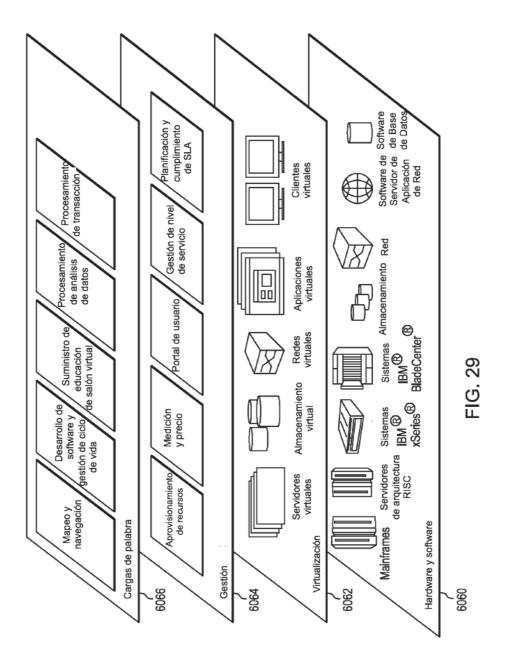

- La Figura 29 representa un ejemplo de capas del modelo de abstracción, de acuerdo con la técnica anterior, y en el que se puede implementar una realización preferida de la presente invención.

## Descripción detallada

10

30

50

55

60

65

De acuerdo con uno o más aspectos, se proporciona una funcionalidad de secuencia de arranque común que habilita un programa utilitario de control (por ejemplo, sistema operativo, programa de control u otra herramienta independiente que se inicia sin necesidad del sistema operativo, tales como programas utilitarios de mantenimiento y gestión (por ejemplo, volcado, formato de disco), como ejemplos) para arrancar en una pluralidad de configuraciones sin cambiar la secuencia de arranque. Por ejemplo, un sistema operativo u otro programa utilitario de control utiliza la secuencia de arranque común para poder arrancar en una primera configuración de arquitectura que se inicializa en una arquitectura, por ejemplo, ESA/390, y luego conmuta a otra arquitectura para el procesamiento, tal como la z/Architecture; o en una segunda configuración arquitectónica que se inicializa y procesa en, por ejemplo, la otra arquitectura, por ejemplo, z/Architecture.

Cuando se introdujo por fases z/Architecture, los programas utilitarios de control continuaron arrancando en ESA/390, un predecesor de z/Architecture, y luego, durante la secuencia de arranque, el procesamiento conmutaría a z/Architecture. Esto permitió que el software heredado continuara ejecutándose sin cambios. Sin embargo, puede haber casos en los que sea deseable arrancar directamente en z/Architecture. Por lo tanto, se proporciona una secuencia de arranque común que permite que un programa utilitario de control arranque de forma libre en cualquier configuración. Por ejemplo, un sistema operativo que está escrito para z/Architecture utiliza la secuencia de arranque para arrancar en ESA/390 y luego conmutar a z/Architecture, o simplemente arrancar directamente en z/Architecture. Aunque las realizaciones en el presente documento se describen con referencia a ESA/390 y z/Architecture, uno o más aspectos también son aplicables a otras arquitecturas.

10

15

20

25

30

35

40

45

60

65

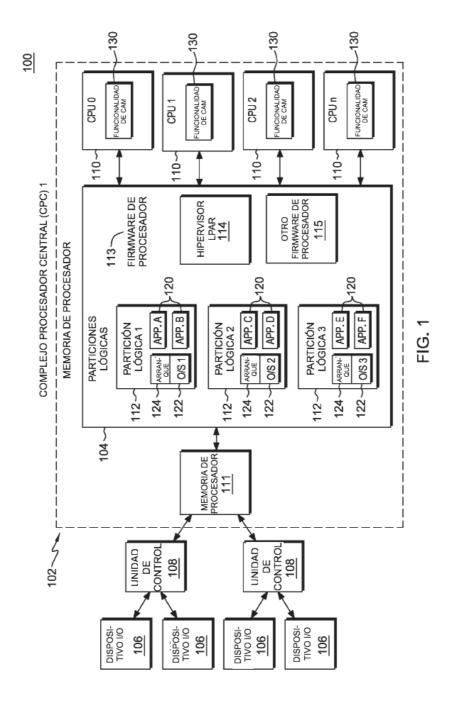

Un ejemplo de un entorno informático para incorporar y utilizar uno o más aspectos de una funcionalidad de secuencia de arranque común se describe con referencia a la Figura 1. Con referencia a la Figura 1, en un ejemplo, un entorno 100 informático se basa en la z/Architecture, ofrecida por IBM. La z/Architecture se describe en una publicación de IBM titulada "z/Architecture - Principles of Operation," Publicación No. SA22-7932-09, 10ª Edición, septiembre 2012. Aunque el entorno informático se basa en la z/Architecture, en una realización preferida, también es compatible con una o más configuraciones arquitectónicas, como ESA/390.

Como ejemplo, el entorno 100 informático incluye un complejo 102 de procesador central (CPC) acoplado a uno o más dispositivos 106 de entrada/salida (I/O) a través de una o más unidades 108 de control. El complejo 102 de procesador central incluye, por ejemplo, una memoria 104 de procesador (también conocida como memoria principal, almacenamiento principal, almacenamiento central) acoplada a uno o más procesadores centrales (también conocidos como unidades 110 de procesamiento central (CPU)) y un subsistema 111 de entrada/salida, cada uno de los cuales se describe a continuación.

La memoria 104 del procesador incluye, por ejemplo, una o más particiones 112 (por ejemplo, particiones lógicas) y el firmware 113 del procesador, que incluye un hipervisor 114 de partición lógica y otro firmware 115 de procesador. Un ejemplo del hipervisor 114 de partición lógica es el Processor Resource/Systems Manager™ (PR/SM). IBM, z/OS, z/VM, z/Architecture y Processor Resource/Systems Manager son marcas comerciales de International Business Machines Corporation, registradas en muchas jurisdicciones de todo el mundo. Otros nombres utilizados en este documento pueden ser marcas registradas, marcas comerciales o nombres de productos de International Business Machines Corporation u otras compañías.

Una partición lógica funciona como un sistema separado y tiene una o más aplicaciones 120, y opcionalmente, un sistema 122 operativo residente en el mismo, que puede diferir para cada partición lógica. En una realización preferida, el sistema operativo es el sistema operativo z/OS, el sistema operativo z/VM, el sistema operativo z/Linux o el sistema operativo TPF, ofrecido por International Business Machines Corporation, Armonk, Nueva York. Como ejemplos, el sistema operativo puede incluir una funcionalidad 124 de secuencia de arranque común o la funcionalidad de secuencia de arranque común se puede proporcionar por separado del sistema operativo, pero se utiliza para arrancar (o inicializar) el sistema operativo.

Las particiones 112 lógicas son gestionadas por el hipervisor 114 de particiones lógicas, que se implementa mediante firmware que se ejecuta en los procesadores 110. Como se utiliza en este documento, el firmware incluye, por ejemplo, el microcódigo y/o el milicódigo del procesador. Incluye, por ejemplo, las instrucciones de nivel de hardware y/o las estructuras de datos utilizadas en la implementación del código de máquina de nivel superior. En una realización preferida, incluye, por ejemplo, código privado que se entrega normalmente como microcódigo que incluye software de confianza o microcódigo específico para el hardware subyacente y controla el acceso del sistema operativo al hardware del sistema.

Los procesadores 110 centrales son recursos de procesador físicos asignados a las particiones lógicas. En particular, cada partición 112 lógica tiene uno o más procesadores lógicos, cada uno de los cuales representa todo o una parte de un procesador 110 físico asignado a la partición. Los procesadores lógicos de una partición 112 particular están dedicados a la partición, de modo que el recurso de procesador subyacente 110 está reservado para esa partición; o compartido con otra partición, de modo que el recurso de procesador subyacente esté potencialmente disponible para otra partición. En un ejemplo, una o más de las CPU pueden incluir aspectos de una funcionalidad 130 de modo arquitectónico de configuración descrita en este documento.

El subsistema 111 de entrada/salida dirige el flujo de información entre los dispositivos 106 de entrada/salida y el almacenamiento 104 principal. Está acoplado al complejo de procesamiento central, ya que puede ser parte del complejo de procesamiento central o estar separado del mismo. El subsistema de I/O alivia a los procesadores centrales de la tarea de comunicarse directamente con los dispositivos de entrada/salida y permite que el procesamiento de datos proceda simultáneamente con el procesamiento de entrada/salida. Para proporcionar comunicaciones, el subsistema de I/O emplea adaptadores de comunicaciones de I/O. Existen varios tipos de adaptadores de comunicaciones que incluyen, por ejemplo, canales, adaptadores de I/O, tarjetas en este documento, los adaptadores de comunicaciones de I/O son canales y, por lo tanto, el subsistema de I/O se

denomina en este documento un subsistema de canales. Sin embargo, este es solo un ejemplo. Se pueden utilizar otros tipos de subsistemas de I/O.

El subsistema de I/O utiliza una o más rutas de entrada/salida como enlaces de comunicación para gestionar el flujo de información hacia o desde los dispositivos 106 de entrada/salida. En este ejemplo particular, estas rutas se denominan rutas de canal, ya que los adaptadores de comunicación son canales.

5

10

15

20

25

30

35

40

45

50

55

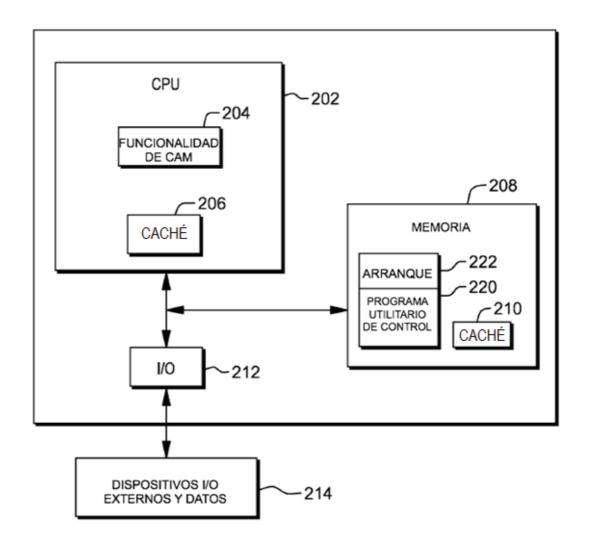

Otro ejemplo de un entorno informático para incorporar y utilizar uno o más aspectos de una funcionalidad de secuencia de arranque común se describe con referencia a la Figura 2. En este ejemplo, un entorno 200 informático incluye un entorno no particionado que se puede configurar para una pluralidad de modos arquitectónicos, que incluyen z/Architecture y ESA/390. Incluye, por ejemplo, un procesador 202 (unidad central de procesamiento - CPU) que incluye, por ejemplo, una funcionalidad 204 de modo arquitectónico de configuración, y uno o más cachés 206. El procesador 202 está acoplado comunicativamente a una porción de memoria 208 que tiene uno o más cachés 210, y a un subsistema 212 de entrada/salida (I/O). El subsistema 212 de I/O está acoplado comunicativamente a dispositivos 214 de I/O externos que pueden incluir, por ejemplo, dispositivos de entrada de datos, sensores y/o dispositivos de salida, tales como pantallas.

En un ejemplo, la porción 208 de memoria también incluye al menos un programa 220 utilitario de control, tal como un sistema operativo, que utiliza una secuencia 222 de arranque común al arrancar.

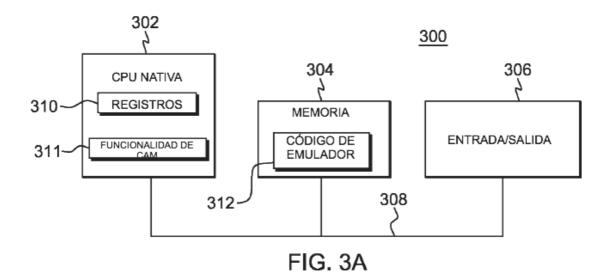

Otra realización preferida de un entorno informático para incorporar y utilizar uno o más aspectos de una funcionalidad de secuencia de arranque común se describe con referencia a la Figura 3A. En este ejemplo, un entorno 300 informático incluye, por ejemplo, una unidad 302 central de procesamiento (CPU) nativa, una memoria 304 y uno o más dispositivos de entrada/salida y/o interfaces 306 acoplados entre sí mediante, por ejemplo, uno o más buses 308 y/u otras conexiones. Como ejemplos, el entorno 300 informático puede incluir un procesador PowerPC® o un servidor Power Systems™; un HP Superdome con procesadores Intel® Itanium® II ofrecido por Hewlett Packard Co., Palo Alto, California; y/u otras máquinas basadas en arquitecturas ofrecidas por International Business Machines Corporation, Hewlett Packard, Intel, Oracle u otras. PowerPC y Power Systems son marcas comerciales de International Business Machines Corporation, registradas en muchas jurisdicciones de todo el mundo. Intel e Itanium son marcas comerciales o marcas comerciales registradas de Intel Corporation o sus subsidiarias en los Estados Unidos y otros países.

La unidad 302 de procesamiento central nativa incluye uno o más registros 310 nativos, tales como uno o más registros de propósito general y/o uno o más registros de propósito especial utilizados durante el procesamiento dentro del entorno, y opcionalmente, una funcionalidad 311 de modo arquitectónico de configuración. Estos registros incluyen información que representa el estado del medio ambiente en un momento determinado.

Adicionalmente, la unidad 302 de procesamiento central nativa ejecuta instrucciones y códigos que se almacenan en la memoria 304. En un ejemplo particular, la unidad central de procesamiento ejecuta el código 312 de emulador almacenado en la memoria 304. Este código permite que el entorno informático configurado en una arquitectura emule una o más arquitecturas. Por ejemplo, el código 312 de emulador permite que las máquinas basadas en arquitecturas distintas de la z/Architecture, como los procesadores PowerPC, los servidores Power Systems, los servidores HP Superdome u otros, emulen la z/Architecture (y/o ESA/390) y se ejecuten software e instrucciones desarrollados en base a la z/Architecture.

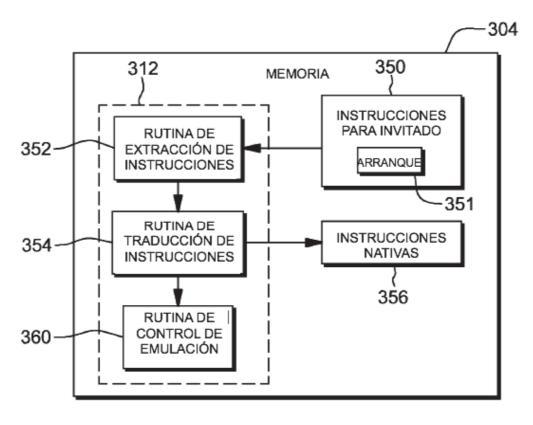

Se describen detalles adicionales relacionados con el código 312 de emulador con referencia a la Figura 3B. Las instrucciones 350 para invitados almacenadas en la memoria 304 comprenden instrucciones de software (por ejemplo, correlacionadas con las instrucciones de la máquina) que se desarrollaron para ejecutarse en una arquitectura distinta de la CPU 302 nativa. Por ejemplo, las instrucciones 350 para invitados pueden haber sido diseñadas para ejecutarse en un procesador 202 z/Architecture, pero en su lugar, se están emulando en la CPU 302 nativa, que puede ser, por ejemplo, un procesador Intel Itanium II. En un ejemplo, las instrucciones para invitados incluyen una secuencia 351 de arranque común. En un ejemplo, el código 312 de emulador incluye una rutina 352 de extracción de instrucciones para obtener una o más instrucciones 350 para invitados de la memoria 304 y, opcionalmente, proporcionar almacenamiento intermedio local para las instrucciones obtenidas. También incluye una rutina 354 de traducción de instrucciones para determinar el tipo de instrucción de invitado que se ha obtenido y para traducir la instrucción de invitado en una o más instrucciones 356. Esta traducción incluye, por ejemplo, identificar la función que debe realizar la instrucción de invitado y elegir las instrucciones nativas para realizar esa función.

Adicionalmente, el código 312 de emulador incluye una rutina 360 de control de emulación para hacer que se ejecuten las instrucciones nativas. La rutina 360 de control de emulación puede hacer que la CPU 302 nativa ejecute una rutina de instrucciones nativas que emule una o más instrucciones de invitado obtenidas previamente y, al concluir dicha ejecución, devuelva el control a la rutina de extracción de instrucciones para emular la obtención de la siguiente instrucción de invitado o un grupo de instrucciones para invitados. La ejecución de las instrucciones 356 nativas puede incluir cargar datos en un registro desde la memoria 304; almacenar datos en la memoria desde un registro; o realizar algún tipo de operación aritmética o lógica, según lo determine la rutina de traducción.

Cada rutina se implementa, por ejemplo, en un software, que se almacena en la memoria y se ejecuta mediante la unidad 302 de procesamiento central nativa. En otros ejemplos, una o más de las rutinas u operaciones se implementan en firmware, hardware, software o alguna combinación de los mismos. Los registros del procesador emulado se pueden emular utilizando los registros 310 de la CPU nativa o utilizando ubicaciones en la memoria 304. En realizaciones preferidas, las instrucciones 350 para invitados, las instrucciones 356 nativas y el código 312 de emulador pueden residir en la misma memoria o se pueden desembolsar entre diferentes dispositivos de memoria.

Los entornos informáticos descritos anteriormente son solo ejemplos de entornos informáticos que se pueden utilizar. Se pueden utilizar otros entornos, incluidos, entre otros, otros entornos no particionados, otros entornos particionados y/u otros entornos emulados ambientes; las realizaciones no están limitadas a ningún entorno.

Como se describe en este documento, se proporciona una secuencia de arranque común para iniciar un programa utilitario de control en una de una pluralidad de configuraciones arquitectónicas, que incluyen, por ejemplo, una primera configuración en la que el programa utilitario de control se inicializa en un primer modo arquitectónico (por ejemplo, un modo heredado, como ESA/390) y luego, el procesamiento cambia a un segundo modo arquitectónico (por ejemplo, un modo mejorado, tal como z/Architecture); o una segunda configuración en la que el programa utilitario de control se inicializa y procesa, por ejemplo, en el segundo modo arquitectónico. En una realización, el primer modo arquitectónico incluye una primera Establecer Arquitectura de instrucciones y tiene un primer conjunto de características compatibles, tales como direccionamiento de 31 bits, uso de registros de propósito general de 32 bits y diversas instalaciones. Adicionalmente, el segundo modo arquitectónico incluye una segunda Establecer Arquitectura de instrucciones y tiene un segundo conjunto de características compatibles, como el direccionamiento de 64 bits, el uso de registros de propósito general de 64 bits y diversas instalaciones, tales como la traducción dinámica de direcciones y/u otras instalaciones.

En una realización, la segunda configuración en la que se facilita la funcionalidad de arranque se inicializa y procesa directamente en un modo arquitectónico seleccionado, tal como z/Architecture, mediante la instalación de una funcionalidad de modo arquitectónico de configuración. Esta funcionalidad, como se describe en este documento, proporciona una secuencia de encendido o arranque para el entorno informático (por ejemplo, procesador, LPAR, invitado virtual) que arranca el entorno informático en el modo arquitectónico seleccionado. Por lo tanto, antes de proporcionar más detalles sobre la secuencia de arranque común, se describen aspectos de una funcionalidad de modo arquitectónico de configuración. Sin embargo, se observa que la capacidad de secuencia de arranque común también se puede utilizar en entornos que no incluyen una funcionalidad de modo arquitectónico de configuración.

En una realización, se instala una funcionalidad de modo arquitectónico de configuración (CAM) en uno o más procesadores (por ejemplo, unidades de procesamiento central) de un entorno informático para controlar la reconfiguración del entorno. Por ejemplo, cuando CAM se instala en un entorno informático que admite una pluralidad de modos arquitectónicos, el entorno informático se reconfigura de modo que se restringe el uso de uno o más aspectos de al menos uno de los modos arquitectónicos.

Un ejemplo particular de una funcionalidad de modo arquitectónico de configuración es la funcionalidad de Modo Arquitectónico de Configuración z/Architecture (CZAM). La instalación de CZAM se indica mediante, por ejemplo, un indicador de instalación de funcionalidad, por ejemplo, bit 138, establecido en, por ejemplo, uno. En un ejemplo particular, cuando el bit 138 se establece en uno, se instala la funcionalidad de CZAM, y cuando se instala, un reinicio normal y un reinicio de borrado colocan la configuración en el modo arquitectónico z/Architecture. Por lo tanto, el bit de funcionalidad, por ejemplo, el bit 2, que indica que el modo arquitectónico z/Architecture está activo, también se establece en uno, en un ejemplo.

Basado en la instalación de CZAM, un entorno informático (por ejemplo, un único procesador, una partición lógica, un invitado virtual, etc.) se reconfigura de modo que uno o más aspectos de una arquitectura seleccionada, por ejemplo, ESA/390, ya no es compatible. A continuación, se describen varios aspectos que ya no son compatibles y/o ciertos procesos afectados por la instalación de CZAM. Aunque en las realizaciones preferidas descritas en el presente documento, la pluralidad de modos arquitectónicos incluye una arquitectura heredada (por ejemplo, ESA/390) y una arquitectura mejorada (por ejemplo, z/Architecture) y los aspectos de la arquitectura heredada, ESA/390, ya no son compatibles, otras realizaciones preferidas pueden incluir otras arquitecturas. ESA/390 y z/Architecture son solo ejemplos.

Un proceso que se ve afectado por la instalación de CZAM es un proceso de encendido. Para describir cómo se ve afectado este proceso, inicialmente, se describe un proceso de encendido para un entorno que soporta múltiples configuraciones arquitectónicas y no incluye la funcionalidad de CZAM con referencia a las Figura 4A-4B, y luego se describe un proceso de encendido para un entorno que está configurado para múltiples configuraciones arquitectónicas y que incluye la funcionalidad de CZAM con referencia a las Figuras 6A-6B. El encendido de un sistema incluye, por ejemplo, comenzar el sistema e iniciar una secuencia de arranque u otros medios para iniciar operaciones en el sistema. Puede corresponder a un encendido físico, un reinicio de hardware y/o un encendido virtual (por ejemplo, en un sistema emulado, una máquina virtual o un entorno para invitado).

65

10

15

20

35

50

55

Con referencia inicialmente a la Figura 4A, con base en un procesador informático el entorno se enciende y se activa una tecla de operador, por ejemplo, una tecla de carga normal o una tecla de borrado de carga, el procesador entra en un estado de carga y establece el entorno informático en un modo arquitectónico particular, por ejemplo, modo ESA/390, ETAPA 400 Por ejemplo, se realiza una carga de programa inicial (IPL), tal como una carga de programa inicial (IPL) de palabra de control de canal (CCW), ETAPA 402. El arranque del programa proporciona un medio manual para hacer que un programa se lea desde un dispositivo designado y para iniciar la ejecución de ese programa. Una IPL de tipo CCW se inicia manualmente al configurar los controles de dirección de la unidad de carga en un número de cuatro dígitos para designar un dispositivo de entrada y al activar posteriormente la tecla de borrado de carga o de carga normal para una CPU en particular.

10

15

La activación de la tecla de borrado de carga hace que se realice un reinicio de borrado en la configuración; y la activación de la tecla de carga normal hace que se realice un reinicio de la CPU inicial en esta CPU (la CPU en la que se activó la tecla), un reinicio de la CPU se propaga a todas las demás CPU en la configuración y un reinicio del subsistema para realizarse en el resto de la configuración. La activación de la tecla de borrado de carga o la tecla de carga normal establece el modo arquitectónico (por ejemplo, ESA/390).

En la parte de carga de la operación, una vez que se han realizado los reinicios, esta CPU ingresa al estado de carga. Esta CPU no entra necesariamente en el estado detenido durante la ejecución de las operaciones de reinicio. El indicador de carga está encendido mientras la CPU está en estado de carga.

20

Posteriormente, se inicia una operación de lectura de programa de canal desde el dispositivo de I/O designado por los controles de dirección de unidad de carga. El efecto de ejecutar el programa de canal es como si un formato 0 CCW que comienza en la ubicación de almacenamiento absoluto 0 especificara un comando de lectura con los bits modificadores ceros, una dirección de datos de cero, un conteo de bytes de 24, el comando de cadena y los indicadores SLI unos, y todos los demás indicadores ceros.

25

30

Cuando la operación de entrada/salida de IPL se completa con éxito, una palabra de identificación del subsistema para el dispositivo IPL se almacena en ubicaciones de almacenamiento absoluto seleccionadas (por ejemplo, ubicaciones 184-187), los ceros se almacenan en otras ubicaciones de almacenamiento absoluto seleccionadas (por ejemplo, ubicaciones 188-191), y se carga una nueva palabra de estado del programa (PSW) desde ubicaciones de almacenamiento absoluto seleccionadas (por ejemplo, ubicaciones 0-7), ETAPA 404. La palabra de estado del programa controla las operaciones del entorno informático.

35

Si la carga de PSW es exitosa y no se detectan fallas en la máquina, esta CPU deja el estado de carga y el indicador de carga se apaga. Si el control de velocidad se establece en la posición del proceso, la CPU entra en el estado operativo y la operación del entorno informático continúa bajo el control de la nueva palabra de estado del programa (PSW), ETAPA 406. Luego se ejecuta el entorno informático de arranque, ETAPA 408, como se describe adicionalmente con referencia a la Figura 4B.

40

45

50

En referencia a la Figura 4B, el entorno informático de arranque se inicia en modo ESA/390, ETAPA 420, y por lo tanto, las operaciones se realizan en modo ESA/390, ETAPA 422. En algún momento, se puede hacer una solicitud para cambiar el modo arquitectónico desde ESA/390 hasta z/Architecture. En particular, un programa envía un código de orden (por ejemplo, Un código que designa Establecer Arquitectura) al procesador, que emite una instrucción de Procesador de Señal (SIGP) con el código de orden para conmutar desde el modo ESA/390 hasta el modo z/Architecture, ETAPA 424. Por ejemplo, se utiliza una funcionalidad de señalización y respuesta de la CPU que incluye la instrucción del Procesador de Señales (descrita a continuación) y un mecanismo para interpretar y actuar sobre los códigos de orden, que incluye Establecer Arquitectura. La funcionalidad proporciona comunicaciones entre las CPU, que incluye la transmisión, recepción y decodificación de un conjunto de códigos de orden asignados; iniciar la operación especificada; y responder a una CPU de señalización. Al utilizar Establecer Arquitectura, el modo arquitectónico se establece en la configuración deseada, por ejemplo, z/Architecture. Detalles adicionales de este procesamiento se describen más adelante.

55

Después de esto, se hace una determinación de que, si se aceptó la operación SIGP, PREGUNTA 426. Con base en el código de retorno, se pueden diagnosticar una serie de condiciones de error, incluida una indicación de "parámetro no válido" cuando se ha determinado que la CPU ya está en el modo arquitectónico especificado por el código (es decir, que la arquitectura establecida representa una conmutación al modo actual, o si se trata de una conmutación de un modo a otro modo). Si se acepta el SIGP y la arquitectura del conjunto representa una operación de conmutación de modo legal, entonces todos los procesadores del entorno informático que recibieron la operación de SIGP pasan al modo z/Architecture utilizando, por ejemplo, el procesamiento de Establecer Arquitectura descrito en este documento, ETAPA 428. Sin embargo, si la operación SIGP no es legal, se indica un error, ETAPA 430.

60

65

Como se describió anteriormente, la operación de encendido carga una palabra de estado del programa. Una realización de un formato de una palabra de estado de programa (PSW) se describe con referencia a la Figura 5) Con referencia a la Figura 5, en este ejemplo, el formato de la palabra de estado del programa es un formato ESA/390, excepto que el bit 31 se muestra como EA, como se indica a continuación.

En una realización, una palabra 500 de estado del programa incluye los siguientes campos, como un ejemplo:

Por máscara 502 (R): el bit 1 controla si la CPU está habilitada para las interrupciones asociadas con la grabación de eventos del programa (PER). Cuando el bit es cero, ningún evento PER puede provocar una interrupción. Cuando el bit es uno, se permiten interrupciones, sujetas a los bits de máscara de evento PER en el registro 9 de control;

Modo 504 DAT (T): el bit 5 controla si tiene lugar la traducción implícita de direcciones dinámicas (DAT) de direcciones lógicas y de instrucciones utilizadas para acceder al almacenamiento. Cuando el bit es cero, DAT está desactivado y las direcciones lógicas y de instrucciones se tratan como direcciones reales. Cuando el bit es uno, DAT está encendido y se invoca el mecanismo de traducción de dirección dinámica.

Máscara 506 de I/O (IO): el bit 6 controla si la CPU está habilitada para interrupciones I/O. Cuando el bit es cero, no se puede producir una interrupción de I/O. Cuando el bit es uno, las interrupciones de I/O están sujetas a los bits de máscara de subclase de interrupción de I/O en el registro 6 de control. Cuando un bit de máscara de subclase de interrupción de I/O es cero, no se puede producir una interrupción de I/O para esa subclase de interrupción de I/O para esa subclase de interrupción de I/O para esa subclase de interrupción de I/O;

Máscara 508 externa (EX): el bit 7 controla si la CPU está habilitada para la interrupción por condiciones incluidas en la clase externa. Cuando el bit es cero, no se puede producir una interrupción externa. Cuando el bit es uno, una interrupción externa está sujeta a los bits de máscara de subclase externa correspondientes en el registro de control 0. Cuando el bit de máscara de subclase es cero, las condiciones asociadas con la subclase no pueden provocar una interrupción. Cuando el bit de máscara de subclase es uno, se puede producir una interrupción en esa subclase.

Tecla 510 PSW (Tecla): los bits 9-11 forman la tecla de acceso para las referencias de almacenamiento de la CPU. Si la referencia está sujeta a protección controlada por clave, la tecla PSW se hace coincidir con una tecla de almacenamiento cuando se almacena la información o cuando la información se extrae de una ubicación que está protegida contra la extracción. Sin embargo, para uno de los operandos de cada uno de Mover a Primaria, Mover a Secundaria, Mover con Tecla, Mover con Tecla Fuente y Mover con Tecla de Destino, y para uno o ambos operandos de Mover con especificaciones Opcionales, se utiliza una tecla de acceso especificada como un operando en lugar de la tecla PSW.

Bit 12 512: este bit indica el modo arquitectónico actual. Está configurado a uno para el formato ESA/390 PSW. Para el formato z/Architecture PSW, este bit se define como cero. Cuando está en modo z/Architecture, se define una instrucción de carga PSW extendida (LPSWE) para cargar una verdadera PSW z/Architecture (que tiene un formato diferente al formato descrito en este documento, que incluye tener una dirección de instrucción en los bits 64-127). Sin embargo, un PSA de carga ESA/390 (LPSW) todavía es soportado y se puede utilizar para cargar un PSW de formato ESA/390. Cuando se ejecuta LPSW y el entorno informático está en modo z/Architecture, el procesador expande el formato ESA/390 PSW al formato z/Architecture, incluido el bit 12 de inversión. Esto es lo contrario de colapsar el formato z/Architecture PSW que realiza el sistema operativo para crear el formato ESA/390 PSW. Es decir, en entornos informáticos que soportan ESA/390 y z/Architecture, cuando se almacena una copia de una PSW, el sistema operativo colapsa la PSW z/Architecture completa al tamaño y formato de una PSA ESA/390. Por lo tanto, otro software con dependencias de formato PSW puede ignorar el z/Architecture PSW.

Máscara 514 de Verificación de Máquina (M): el Bit 13 controla si la CPU está habilitada para la interrupción por las condiciones de verificación de la máquina. Cuando el bit es cero, no puede ocurrir una interrupción de verificación de máquina. Cuando el bit es uno, se permiten interrupciones de verificación de la máquina debido a daños en el sistema y daños en el procesamiento de instrucciones, pero las interrupciones debidas a otras condiciones de subclase de verificación de máquina están sujetas a los bits de máscara de subclase en el registro 14 de control.

Estado 516 de espera (W): cuando el bit 14 es uno, la CPU está en espera; es decir, la CPU no procesa instrucciones, pero pueden producirse interrupciones. Cuando el bit 14 es cero, la extracción y ejecución de instrucciones se produce de la manera normal. El indicador de espera es uno cuando el bit es uno.

Estado 518 del problema (P): cuando el bit 15 es uno, la CPU está en el estado del problema. Cuando el bit 15 es cero, la CPU está en el estado de supervisor. En el estado de supervisor, todas las instrucciones son válidas. En el estado del problema, solo son válidas las instrucciones que proporcionan información significativa al programa del problema y que no pueden afectar la integridad del sistema; tales instrucciones se llaman instrucciones no privilegiadas. Las instrucciones que no son válidas en el estado del problema se denominan instrucciones privilegiadas. Cuando una CPU en el estado problemático intenta ejecutar una instrucción privilegiada, se reconoce una excepción de operación privilegiada. Otro grupo de instrucciones, llamadas instrucciones semiprivilegiadas, se ejecutan por una CPU en el estado del problema solo si se cumplen pruebas de autoridad específicas; de lo contrario, se reconoce una excepción de operación privilegiada o alguna otra excepción de programa, dependiendo del requisito particular que se viole.

65

5

10

15

35

40

50

55

Control 520 de Espacio de Dirección (AS): los bits 16 y 17, junto con el bit 5 de PSW, controlan el modo de traducción.

Código 522 de condición (CC): los bits 18 y 19 son los dos bits del código de condición. El código de condición se establece en 0, 1, 2 o 3 dependiendo del resultado obtenido al ejecutar ciertas instrucciones. La mayoría de las operaciones aritméticas y lógicas, así como algunas otras operaciones, establecen el código de condición. La instrucción DERIVACIÓN EN CONDICIÓN puede especificar cualquier selección de los valores del código de condición como criterio para la derivación.

Máscara 524 de programa: los bits 20-23 son los cuatro bits de máscara de programa. Cada bit está asociado con una excepción de programa, como sigue:

| Bit de Máscara DE Programa | Excepción del programa    |

|----------------------------|---------------------------|

| 20                         | Sobreflujo de punto fijo  |

| 21                         | Sobreflujo de decimal     |

| 22                         | Subflujo de exponente HFP |

| 23                         | Significancia de HFP      |

5

20

25

30

40

45

50

55

Cuando el bit de máscara es uno, la excepción resulta en una interrupción. Cuando el bit de máscara es cero, no se produce ninguna interrupción. La configuración del bit de máscara de subflujo de exponente de HFP del bit de máscara de significancia de HFP también determina la manera en que se completa la operación cuando se produce la excepción correspondiente.

Modo 526 de direccionamiento extendido (EA): el bit 31 controla el tamaño de las direcciones efectivas y la generación efectiva de direcciones junto con el bit 32, el bit del modo de direccionamiento básico. Cuando el bit 31 es cero, el modo de direccionamiento está controlado por el bit 32. Cuando los bits 31 y 32 son ambos uno, se especifica el direccionamiento de 64 bits.

Modo 528 de direccionamiento básico (BA): los bits 31 y 32 controlan el tamaño de las direcciones efectivas y la generación efectiva de direcciones. Cuando los bits 31 y 32 son ambos cero, se especifica el direccionamiento de 24 bits. Cuando el bit 31 es cero y el bit 32 es uno, se especifica el direccionamiento de 31 bits. Cuando los bits 31 y 32 son ambos uno, se especifica el direccionamiento de 64 bits. El bit 31 uno y el bit 32 cero son una combinación no válida que hace que se reconozca una excepción de especificación. El modo de direccionamiento no controla el tamaño de las direcciones PER o de las direcciones utilizadas para acceder a DAT, ASN, control de unidades de capacidad de suministro, enlaces, entradas y tablas de seguimiento o listas de acceso o la pila de enlaces. El control del modo de direccionamiento por los bits 31 y 32 de la PSW se resume de la siguiente manera:

| PSW: 31 | PSW: 32 | Modo de direccionamiento |

|---------|---------|--------------------------|

| 0       | 0       | 24-bit                   |

| 0       | 1       | 31-bit                   |

| 1       | 1       | 64-bit                   |

Dirección 530 de instrucción: los bits 33-63 de la PSW son la dirección de instrucción. La dirección designa la ubicación del byte más a la izquierda de la siguiente instrucción que se ejecutará, a menos que la CPU esté en el estado de espera (el bit 14 del PSW es uno).

De acuerdo con un aspecto, cuando una funcionalidad de modo arquitectónico de configuración, tal como la funcionalidad de Modo Arquitectónico z/Architecture de configuración (CZAM), se instala y activa en el entorno informático, se cambia el proceso de encendido. Una realización de un proceso de encendido CZAM se describe con referencia a la Figura 6A.

Con referencia a la Figura 6A, con base en un procesador del entorno informático que se está encendiendo, el entorno informático se establece en el modo arquitectónico particular especificado por la funcionalidad del modo arquitectónico de configuración, por ejemplo, el modo z/Architecture (también denominado ESAME) cuando se instala CZAM, ETAPA 600. Por ejemplo, se realiza una carga de programa inicial (IPL), tal como una carga de programa inicial (IPL) de palabra de control de canal (CCW), como se describió anteriormente, ETAPA 602, y cuando la operación de entrada/salida de IPL se completa con éxito, un la palabra de identificación del subsistema para el dispositivo IPL se almacena en ubicaciones de almacenamiento absoluto seleccionadas (por ejemplo, ubicaciones 184-187), los ceros se almacenan en otras ubicaciones de almacenamiento absoluto seleccionadas (por ejemplo, ubicaciones 188-191), y en esta realización, una nueva palabra de estado del programa (PSW) de 16 bytes se crea a partir de ubicaciones de almacenamiento absoluto seleccionadas (por ejemplo, ubicaciones 0-7), ETAPA 604. El nuevo PSW de 16 bytes se forma, por ejemplo, a partir del contenido de la palabra doble de almacenamiento seleccionada (por ejemplo, ubicaciones 0-7). El bit 12 de la palabra doble es uno; de lo contrario, se puede indicar un error. (El error puede ser una excepción de especificación reconocida, una verificación de la máquina u otra indicación de error). Los bits 0-32 de la PSW recién creada se establecen en los bits 0-32 de la palabra doble seleccionada, excepto con el bit 12 invertido. Los bits 33-96 de la PSW recién creada se establecen en ceros. Las

posiciones de bit 97-127 del PSW recién creado se inicializan a partir de los bits 33-63 de la palabra doble seleccionada.

En una realización, no se verifica la validez de los campos PSW que deben cargarse mediante la instrucción antes de cargarlos. En una realización, se verifica la validez del bit 12 de la PSW. En aún otra realización, se verifica la validez de todos los campos. En otra realización, cualquier bit no verificado antes de la carga de la PSW se verifica para verificar su validez después de que la PSW se haya inicializado, y el procesador puede indicar un error (por ejemplo, al generar una excepción de especificación que se reconoce, una verificación de la máquina o aún otra indicación de error).

10

El entorno informático entra en el estado operativo, y la operación del entorno informático continúa bajo el control de la nueva palabra de estado del programa (PSW), ETAPA 606. Luego se ejecuta el entorno informático de arranque, ETAPA 608, como se describe adicionalmente con referencia a la Figura 6B.

15

Con referencia a la Figura 6B, el entorno informático de arranque se inicia en modo z/Architecture, ETAPA 620, y por lo tanto, las operaciones se realizan en modo z/Architecture, ETAPA 622. No es necesario conmutar de modo, y el procesamiento continúa directamente con el procesamiento en el modo z/Architecture. Por lo tanto, en una realización, las siguientes etapas no son necesarios: una operación de Procesador de Señal (SIGP) para conmutar desde el modo ESA/390 hasta el modo z/Architecture; una determinación sobre si la operación SIGP es una operación aceptada; la transición a z/Architecture si es una operación aceptada; o la indicación de error, si no se acepta la operación SIGP.

20

25

Todos los procesadores del entorno informático (es decir, el entorno que se está configurando, por ejemplo, procesador único, partición lógica, invitado VM) están en modo z/Architecture, sin realizar las etapas indicadas anteriormente. Por lo tanto, como se describe en este documento, de acuerdo con un aspecto, la capacidad de arrancar o encender en modo ESA/390 se elimina del entorno informático configurado para ESA/390 y z/Architecture. En particular, aunque un entorno informático está configurado para admitir múltiples arquitecturas, se proporciona una capacidad para restringir ciertos aspectos de al menos una de las arquitecturas configuradas, siendo uno de los aspectos la capacidad de encender esa arquitectura.

30

En una o más realizaciones preferidas, el encendido en modo z/Architecture proporciona un mecanismo para especificar una de (1) una partición lógica (invitado-1), y (2) una partición lógica y un invitado-2 se deben arrancar y restablecer en modo z/Architecture, sin necesidad de iniciar en modo ESA/390. Esta característica se puede instalar incondicionalmente o bajo el control de un conmutador de configuración.

35

La secuencia de arranque con respecto a la inicialización de PSW se modifica. Por ejemplo, al final de IPL, se carga el IPL PSW en ubicaciones absolutas 0-7. Como se hace actualmente cuando la condición de reinicio es ESA/390, el bit 12 es uno, que hace un PSA IPL PSW ESA/390 válido, y el programa procede a ejecutar instrucciones en el modo arquitectónico ESA/390. Con CZAM instalado, la condición de reinicio es z/Architecture, el bit 12 sigue siendo uno, lo que hace un PSA IPL PSW ESA/390 válido, pero el bit 12 se invierte durante la formación del PSW actual de 16 bytes z/Architecture, como se definió anteriormente.

40

45

Además del proceso de encendido, otros procesos, comportamientos y/u operaciones también pueden modificarse o verse afectados por la instalación de una funcionalidad de modo arquitectónico de configuración. Estos procesos, comportamientos y/u operaciones afectados son específicos de los modos ESA/390 y z/Architecture. Sin embargo, procesos similares y/o diferentes pueden verse afectados por otros tipos de arquitecturas. Procesos,

comportamientos y/u operaciones de ejemplo que se pueden ver afectados en una o más realizaciones preferidas incluyen, por ejemplo:

50 (1) Habilitar un conmutador de modo a auto (por ejemplo, desde el modo z/Architecture hasta el modo z/Architecture) sin generar un error (o ignorar el error). Es decir, un procesador puede emitir una instrucción SIGP para conmutar al modo z/Architecture y, si ya está en ese modo, no se generará ningún error. Anteriormente, intentaba conmutar al modo correspondiente al modo actual generaba un error.

55

(2) Deshabilitar un conmutador al modo ESA/390. Con base en la instalación y activación de CZAM, la conmutación a ESA/390 está deshabilitada y ahora genera un error. Se evita una nueva conmutación a ESA/390 al verificar el bit 12 de la PSW y tomar una excepción, si el bit 12 no está configurado para indicar el modo z/Architecture (representado por un bit 12 de "1" en el almacenamiento que se invierte en un bit "0" para representar z/Architecture en la PSW cuando una ESA/390 PSW se convierte en una z/Architecture PSW válida).

60

(3) Modificar la operación PSW de Carga para restringir el manejo del bit 12. Si se instala la funcionalidad de Modo Arquitectónico z/Architecture de Configuración, la PSW de Carga reconoce una excepción de especificación si el bit 12 de su segundo operando no es uno. La PSW de Carga, carga los bits 0-32 de su segundo operando, excepto con el bit 12 invertido, y los bits 33-63 del operando como bits 0-32 y 97-127, respectivamente del PSW actual, y establece los bits 33-96 del PSW actual a ceros.

Se describen detalles adicionales con respecto a la instrucción de PSW de Carga con referencia a la Figura 7) En una realización, una instrucción 700 de PSW de carga incluye un campo 702 de código de operación que incluye un código de operación para indicar una operación de PSW de carga; un campo 704 base (B<sub>2</sub>); y un campo 706 de desplazamiento (D<sub>2</sub>). El contenido del registro general designado por el campo B<sub>2</sub> se agrega al contenido del campo D<sub>2</sub> para formar una dirección de un segundo operando en almacenamiento (denominado como la segunda dirección de operando).

En la operación de la instrucción de PSW de carga, la PSW actual se reemplaza por una PSW de 16 bytes formada a partir del contenido de la palabra doble en la ubicación designada por la segunda dirección de operando.

El bit 12 de la palabra doble es uno; de lo contrario, se puede reconocer una excepción de especificación, dependiendo del modelo. Si se instala la funcionalidad del Modo Arquitectónico z/Architecture de Configuración, se reconoce una excepción de especificación si el bit 12 de la palabra doble no es uno.

- Los bits 0-32 de la palabra doble, excepto con el bit 12 invertido, se colocan en las posiciones 0-32 de la PSW actual. Los bits 33-63 de la palabra doble se colocan en las posiciones 97-127 de la PSW actual. Los bits 33-96 de la PSW actual se establecen en cero.

- Se realiza una función de serialización y sincronización del punto de comprobación antes o después de extraer el operando y nuevamente después de que se completa la operación.

El operando se designará en un límite de doble palabra; de lo contrario, se reconoce una excepción de especificación.

Se puede reconocer una excepción de especificación si el bit 12 del operando es cero, dependiendo del modelo.

No se verifica la validez de los campos PSW que deben cargarse con la instrucción antes de cargarlos, excepto la verificación del bit 12. Sin embargo, inmediatamente después de la carga, se reconoce una excepción de especificación y se produce una interrupción del programa, cuando cualquiera de lo siguiente es cierto para el PSW recién cargado:

• Cualquiera de los bits 0, 2-4, 12 o 24-30 es uno.

- Los bits 31 y 32 son ambos cero, y los bits 97-103 no son todos ceros.

- Los bits 31 y 32 son uno y cero, respectivamente.

- 35 En estos casos, la operación se completa y el código de longitud de la instrucción resultante es 0.

La operación se suprime en todas las excepciones de direccionamiento y protección. Código de Condición Resultante: el código se establece como se especifica en el nuevo PSW cargado. Excepciones del programa:

40

5

10

25

30

- Acceso (extracción, operando 2)

- Operación privilegiada

- Especificación

- 45 Nota de programación: el segundo operando debe tener el formato de un ESA/390 PSW. Se reconocerá una excepción de especificación durante o después de la ejecución de PSW DE CARGA si el bit 12 del operando es cero.

- Se describen detalles ADICIONALES sobre el PSW en "Development and Attributes of z/Architecture," Plambeck et al., IBM J. Res. & Dev., Vol. 46, No. 4/5, July/September 2002.

Además de los procesos, operaciones y/o comportamientos anteriores que se pueden cambiar debido a la instalación de una funcionalidad de modo arquitectónico de configuración, el modo de reinicio también se puede cambiar en una o más realizaciones preferidas, como se explica a continuación.

55

- (4) Cambia el modo de reinicio (por ejemplo, para reinicio, reinicio de borrado y otras acciones para reinicio). Cuando se instala la funcionalidad de CZAM, el reinicio de la CPU establece el modo arquitectónico en el modo z/Architecture, si es provocado por la activación de, por ejemplo, la tecla de carga normal.

- Se presenta una serie de funciones de reinicio que se incluyen como parte de los modos ESA/390 y z/Architecture, que incluyen, por ejemplo, reinicio de la CPU, reinicio de la CPU inicial, reinicio del subsistema, reinicio de borrado y reinicio de encendido, cada uno de los cuales se describe a continuación.

Reinicio de la CPU

El reinicio de la CPU proporciona un medio para borrar las indicaciones de verificación del equipo y cualquier imprevisibilidad resultante en el estado de la CPU con la menor cantidad de información destruida. En particular, se utiliza para borrar las condiciones de verificación cuando se debe preservar el estado de la CPU para el análisis o la reanudación de la operación. Si la funcionalidad de Modo Arquitectónico z/Architecture de Configuración (CZAM) no está instalada, el reinicio de la CPU establece el modo arquitectónico en el modo ESA/390 si es provocado por la activación de la tecla de carga normal (una funcionalidad del operador). Cuando se instala la funcionalidad de CZAM, el reinicio de la CPU establece el modo arquitectónico en el modo z/Architecture si es provocado por la activación de la tecla de carga normal. Cuando el reinicio de la CPU establece el modo ESA/390, guarda el PSW actual de tal manera que PSW se pueda restaurar mediante una orden Establecer Arquitectura de Procesador de Señal que cambia el modo arquitectónico de nuevo a z/Architecture.

El reinicio de la CPU provoca las siguientes acciones, en una realización:

- 1. Se finaliza la ejecución de la instrucción actual u otra secuencia de procesamiento, como una interrupción y se borran todas las condiciones de interrupción del programa y de interrupción de la llamada del supervisor.

- 2. Se borra cualquier condición de interrupción externa pendiente que sea local para la CPU. Las condiciones de interrupción externa flotante no se borran.

- 3. Se borran cualquier condición pendiente de interrupción de verificación de máquina e indicaciones de error que sean locales para la CPU y cualquier estado de detención de verificación. Las condiciones de interrupción de verificación de máquina flotante no se borran. Se dice que cualquier condición de verificación de máquina que se reporta a todas las CPU en la configuración y que se ha hecho pendiente a una CPU es local a la CPU.

- 4. Se borran todas las copias de instrucciones u operandos extraídos previamente. Adicionalmente, se borran todos los resultados que se almacenarán debido a la ejecución de instrucciones en el intervalo de punto de verificación actual.

- 5. El búfer ART (Traducción del Registro de Acceso) –lateral y el búfer de traducción lateral se borran de las entradas.

- 6. Si el reinicio es provocado por la activación de la tecla de carga normal en cualquier CPU en la configuración, se producen las siguientes acciones:

- a. Cuando la funcionalidad de CZAM no está instalada, el modo arquitectónico de la CPU (y de todas las otras CPU en la configuración debido al reinicio de la CPU inicial o los reinicios de la CPU realizados por ellos) se cambia desde el modo z/Architecture hasta el modo ESA/390. Si la funcionalidad de CZAM está instalada, el modo arquitectónico de la CPU (y de todas las otras CPU en la configuración debido al reinicio de la CPU inicial o los reinicios de la CPU realizados por ellos) se establece en el modo z/Architecture.

- b. Cuando la funcionalidad de CZAM no está instalada, la PSW actual se guarda para su uso posterior por una orden Establecer Arquitectura de Procesador de Señal que restaura el modo z/Architecture.

- c. Cuando la funcionalidad de CZAM no está instalada, la PSW actual se cambia desde 16 bytes hasta ocho bytes.

45 Los bits de la PSW de ocho bytes se establecen de la siguiente manera: los bits 0-11 y 13-32 se establecen iguales a los mismos bits de la PSW de 16 bytes, el bit 12 se establece a uno y los bits 33-63 se establecen iguales a los bits 97-127 del PSW de 16 bytes.

- Un reinicio de la CPU provocado por la activación de la tecla de reinicio normal del sistema o por el orden de reinicio de la CPU del procesador de señal, y cualquier reinicio de la CPU en el modo ESA/390, no afecta el registro z/Architecture-PSW capturado (es decir, un PSW guardado la última vez que la CPU pasó del modo z/Architecture al modo ESA/390 debido a una orden Establecer Arquitectura con código 0 o un reinicio de la CPU debido a la activación de la tecla de carga normal).

- 7. La CPU se coloca en el estado detenido después de que se hayan completado las acciones 1-6. Cuando la secuencia IPL de tipo CCW sigue la función de reinicio en esa CPU, la CPU ingresa al estado de carga al finalizar la función de reinicio y no necesariamente ingresa al estado detenido durante la ejecución de la operación de reinicio. Cuando la secuencia de IPL dirigida por la lista sigue la función de reinicio en esa CPU, la CPU ingresa al estado operativo y no necesariamente ingresa al estado detenido durante la ejecución de la operación de reinicio.

- Los registros, el contenido de almacenamiento y el estado de las condiciones externas a la CPU no se modifican con el reinicio de la CPU. Sin embargo, el contenido posterior del registro, la ubicación o el estado son impredecibles si hay una operación en curso que cambia el contenido en el momento del reinicio. Un bloqueo mantenido por la CPU cuando se ejecuta la OPERACIÓN DE REALIZACIÓN DE BLOQUEO no se libera por el reinicio de la CPU.

65

Cuando se inicia la función de reinicio en la CPU en el momento en que la CPU está ejecutando una instrucción de I/O o está realizando una interrupción de I/O, la operación actual entre la CPU y el subsistema del canal puede o no completarse, y el estado resultante de la funcionalidad del subsistema de canal asociado puede ser impredecible.

- 5 Notas de programación:

- 1. La mayoría de las operaciones que cambiarían un estado, una condición o el contenido de un campo no pueden ocurrir cuando la CPU está en estado detenido. Sin embargo, algunas funciones del procesador de señal y algunas funciones del operador pueden cambiar estos campos. Para eliminar la posibilidad de perder un campo cuando se emite el reinicio de la CPU, se debe detener la CPU y no se deben ejecutar funciones del operador en progreso.

- 2. Si el modo arquitectónico se cambia al modo ESA/390 y el bit 31 de la PSW actual es uno, la PSW no es válida.

#### Reinicio de la CPU inicial

15

20

10

El reinicio de la CPU inicial proporciona las funciones de reinicio de la CPU junto con la inicialización de la PSW actual. PSW de z/Architecture capturada, temporizador de la CPU, comparador de reloj, prefijo, control de dirección de evento de interrupción, control de punto de flotación y registros programables de hora del día (TOD) Si la funcionalidad de CZAM no está instalada, el reinicio de la CPU inicial establece el modo arquitectónico en el modo ESA/390 si es provocado por la activación de la tecla de carga normal. Cuando se instala la funcionalidad de CZAM, el reinicio de la CPU inicial establece el modo arquitectónico en el modo z/Architecture si es provocado por la activación de la tecla de carga normal.

El reinicio de la CPU inicial combina las funciones de reinicio de la CPU con las siguientes funciones de borrado e 25 inicialización:

- 1. Cuando la funcionalidad de CZAM no está instalada, si el reinicio es provocado por la activación de la tecla de carga normal, el modo arquitectónico de la CPU (y de todas las otras CPU en la configuración) se establece en el modo ESA/390. De lo contrario, si la funcionalidad de CZAM está instalada, el modo arquitectónico de la CPU (y de todas las otras CPU en la configuración) se establece en el modo z/Architecture.

- 2. Los contenidos del PSW actual, z/Architecture-PSW capturado, prefijo, temporizador de CPU, comparador de reloj y registro programable TOD se establecen en cero. Cuando la secuencia de IPL sigue la función de reinicio en esa CPU, los contenidos de la PSW no se establecen necesariamente en cero.

35

30

- 3. Los contenidos de los registros de control se establecen en sus valores iniciales de z/Architecture. Los 64 bits de los registros de control se establecen independientemente de si la CPU está en el modo arquitectónico ESA/390 o z/Architecture.

- 40 4. Los contenidos del registro de control de punto de flotación se establece en cero.

- 5. Los contenidos del registro de dirección de evento de ruptura se inicializa en 000000000000001 hexadecimal.

Estas funciones de borrado e inicialización incluyen validación.

45

50

Establecer el PSW actual a cero cuando la CPU está en el modo arquitectónico ESA/390 al final de la operación hace que el PSW sea inválido, ya que el bit 12 de PSW será uno en ese modo. Por lo tanto, en este caso, si la CPU se coloca en el estado operativo después de un reinicio sin introducir primero una nueva PSW, se reconoce una excepción de especificación.

Reinicio del subsistema

El reinicio del subsistema proporciona un medio para borrar las condiciones de interrupción flotante, así como para invocar el reinicio del sistema de I/O.

55

Reinicio de borrado

El reinicio de borrado hace que se realice el reinicio de la CPU inicial y el reinicio del subsistema y, adicionalmente, borra o inicializa todas las ubicaciones de almacenamiento y registros en todas las CPU en la configuración, con la 60 excepción del reloj TOD. Dicho borrado es útil para depurar programas y para garantizar la privacidad del usuario. El reinicio de borrado también libera todos los bloqueos utilizados por la instrucción OPERACIÓN DE REALIZACIÓN DE BLOQUEO. Si la funcionalidad de CZAM no está instalada, el reinicio de borrado establece el modo arquitectónico en el modo ESA/390. Cuando se instala la funcionalidad de CZAM, el reinicio de borrado establece el modo arquitectónico en el modo z/Architecture. El borrado no afecta el almacenamiento externo, tal como los 65 dispositivos de almacenamiento de acceso directo utilizados por el programa de control para preservar el contenido de páginas no direccionables.

El reinicio de borrado combina la función de reinicio de la CPU inicial con una función de inicialización que provoca las siguientes acciones:

- Cuando la funcionalidad de CZAM no está instalada, el modo arquitectónico de todas las CPU en la configuración se establece en el modo ESA/390. Si la funcionalidad de CZAM está instalada, el modo arquitectónico de todas las CPU en la configuración se establece en el modo z/Architecture.

- 2. Los registros de acceso, general y de punto de flotación de todas las CPU en la configuración se establecen en cero. Todos los 64 bits de los registros generales se establecen en cero, independientemente de si la CPU estaba en el modo arquitectónico ESA/390 o z/Architecture cuando se inició la función de reinicio de borrado.

- 3. Los contenidos del almacenamiento principal en la configuración y las claves de almacenamiento asociadas se establecen en cero con un código válido de bloque de verificación.

- 4. Se liberan los bloqueos utilizados por cualquier CPU en la configuración al ejecutar la instrucción OPERACIÓN DE REALIZACIÓN DE BLOQUEO.

- 5. Se realiza un reinicio del subsistema.

La validación se incluye en la configuración de registros y en el borrado del almacenamiento y claves de almacenamiento.

#### Notas de programación:

15

20

25

40

45

50

55

60

- 1. El modo arquitectónico no se cambia mediante la activación de la tecla normal de reinicio del sistema o mediante la ejecución de una orden de reinicio de la CPU del Procesador de Señal o de reinicio inicial de CPU. Todas las CPU en la configuración están en el mismo modo arquitectónico.

- 2. Para que la operación de reinicio de la CPU no afecte los contenidos de los campos que se dejarán sin cambios, la CPU no debe ejecutar instrucciones y se debe deshabilitar para todas las interrupciones en el momento del reinicio. Excepto por el funcionamiento del temporizador de la CPU y la posibilidad de que ocurra una interrupción de la verificación de la máquina, toda la actividad de la CPU se puede detener al colocar la CPU en el estado de espera y deshabilitándola para I/O e interrupciones externas. Para evitar la posibilidad de provocar un reinicio en el momento en que se actualiza el temporizador de la CPU o se produce una interrupción de la verificación de la máquina, la CPU debe estar en el estado detenido.

- 3. El reinicio de la CPU, el reinicio de la CPU inicial, el reinicio del subsistema y el reinicio de borrado no afectan el valor y el estado del reloj TOD.

- 4. Las condiciones bajo las cuales la CPU ingresa al estado de detención de verificación dependen del modelo e incluyen fallas que impiden la finalización de la operación actual. Por lo tanto, si el reinicio de la CPU o el reinicio de la CPU inicial se ejecuta mientras la CPU se encuentra en el estado de verificación y detención, los contenidos de la PSW, los registros y las ubicaciones de almacenamiento, que incluyen las claves de almacenamiento y la ubicación de almacenamiento accedida en el momento del error, pueden tener valores impredecibles y, en algunos casos, los contenidos aún pueden estar en error después de que el estado de verificación y detención se borra por estos reinicios. En esta situación, se requiere un reinicio de borrado para borrar el error.

#### Reinicio de encendido

La función de reinicio de encendido de un componente de la máquina se realiza como parte de la secuencia de encendido de ese componente. Las secuencias de encendido para el reloj TOD, el almacenamiento principal, el almacenamiento expandido y el subsistema de canales pueden incluirse como parte de la secuencia de encendido de la CPU, o la secuencia de encendido para estas unidades puede iniciarse por separado.

Reinicio del encendido de la CPU: el reinicio del encendido provoca que se realice el reinicio de la CPU inicial y puede o no provocar el reinicio del sistema de I/O en el subsistema del canal. Los contenidos de los registros generales, los registros de acceso y los registros de punto de flotación se borran a ceros con un código válido de bloque de verificación. Los bloqueos utilizados por OPERACIÓN DE REALIZACIÓN DE BLOQUEO y asociados con la CPU se liberan a menos que sean mantenidos por una CPU ya encendida. Si la funcionalidad de CZAM no está instalada y el reinicio está asociado con el establecimiento de una configuración, la CPU se coloca en el modo ESA/390; de lo contrario, la CPU se coloca en el modo arquitectónico de las CPU que ya están en la configuración. Si la funcionalidad de CZAM está instalada, la CPU se coloca en el modo z/Architecture.

El reinicio de la CPU, el reinicio de la CPU inicial, el reinicio del subsistema y el reinicio de borrado pueden iniciarse manualmente al utilizar las funcionalidades del operador. El reinicio de la CPU inicial es parte de la función de arranque del programa. El reinicio de encendido se realiza como parte del encendido.

Cuando la funcionalidad de CZAM no está instalada, si se inicia el reinicio mediante la tecla borrado de reinicio de sistema, normal de carga o borrado de carga o mediante un reinicio de encendido de CPU que establece la configuración, el modo arquitectónico se establece en Modo ESA/390; de lo contrario, el modo arquitectónico no cambia, excepto que el reinicio de encendido establece el modo al de las CPU que ya están en la configuración. Si la funcionalidad de CZAM está instalada, el modo arquitectónico se establece en el modo z/Architecture.

10

15

20

40

45

50

55

A continuación, se describen otros procesos, operaciones y/o comportamientos que pueden cambiar debido a la instalación de una funcionalidad de modo arquitectónico de configuración:

- (5) Suprime otras acciones relacionadas con el reinicio que se toman para facilitar el cambio entre el modo ESA/390 y z/Architecture, cuando se realiza el reinicio. Cuando la funcionalidad de CZAM no está instalada, la PSW actual se guarda para su uso posterior por una orden Establecer Arquitectura de Procesador de Señal que restaura el modo z/Architecture. Cuando la funcionalidad de CZAM no está instalada, la PSW actual se cambia de 16 bytes a ocho bytes. Los bits de la PSW de ocho bytes se establecen de la siguiente manera, en un ejemplo: los bits 0-11 y 13-32 se establecen iguales a los mismos bits de la PSW de 16 bytes, el bit 12 se establece en uno y los bits 33-63 se establecen iguales a los bits 97-127 de la PSW de 16 bytes. Cuando se instala la funcionalidad de CZAM, la PSW no se guarda para su posterior uso por una orden Establecer Arquitectura de Procesador de Señal que restaura el modo z/Architecture, y la PSW actual no se cambia de 16 bytes a 8 bytes.

- (6) Cambia el proceso para configurar una CPU con un comando configure CPU SCLP (Procesador Lógico de Llamada de Servicio), y cargar las operaciones clave. Más bien que configurar en ESA/390, configurar en el modo definido por reset. El comando configure CPU SCLP coloca a la CPU en cuestión en el modo arquitectónico de las CPU que ya están en el estado configurado. Al menos la primera CPU colocada en una configuración se coloca allí junto con un reinicio de energía de la CPU y, como parte de ese reinicio, se coloca en el modo de arquitectura definido en el reinicio de encendido de la CPU. Un modelo puede establecer alternativamente el modo de las CPU que están en estado de espera cuando establece el modo de las CPU configuradas.

La activación de la tecla de carga o la tecla de carga normal establece el modo arquitectónico como se define en el reinicio de borrado o el reinicio de la CPU inicial, respectivamente.

35 7) Cambia SIGP para no permitir que una orden Establecer Arquitectura cambie el modo arquitectónico a ESA/390.

Una realización de una instrucción del Procesador de Señal (SIGP) se describe con referencia a la Figura 8A. En una realización, una instrucción 800 de Procesador de Señal tiene una pluralidad de campos, que incluyen, por ejemplo, un campo 802 de código de operación (código de operación) que tiene un código de operación que indica una operación de procesador de señal; un primer campo 804 de registro ( $R_1$ ); un segundo campo 806 de registro ( $R_3$ ); un campo 808 base ( $R_2$ ); y un campo 810 de desplazamiento ( $R_2$ ).  $R_1$  designa un registro general, cuyo contenido es el primer operando;  $R_3$  designa un registro general, cuyo contenido es el tercer operando; y el contenido de un registro designado por  $R_2$  se agrega al desplazamiento en  $R_2$  para proporcionar una dirección de un segundo operando.

En operación, un código de orden de ocho bits y, si se solicita, un parámetro de 32 bits se transmite a la CPU designada por la dirección de la CPU contenida en el tercer operando. El resultado se indica mediante el código de condición y puede detallarse mediante el estado ensamblado en las posiciones de bit 32-63 de la ubicación del primer operando.

La dirección del segundo operando no se utiliza para direccionar datos; en cambio, los bits 56-63 de la dirección contienen el código de orden de ocho bits. Los bits 0-55 de la dirección del segundo operando se ignoran. El código de orden especifica la función que debe realizar la CPU direccionada. La asignación y definición de códigos de orden incluyen, por ejemplo, lo siguiente, en un ejemplo:

| Código |       |                     |

|--------|-------|---------------------|

| (Dec)  | (Hex) | Orden               |

| 0      | 00    | No asignado         |

| 1      | 01    | Sentido             |

| 2      | 02    | Llamada externa     |

| 3      | 03    | Señal de emergencia |

| 4      | 04    | Inicio              |

| 5      | 05    | Detención           |

| 6      | 06    | Reinicio            |

| 7      | 07    | No asignado         |

| ,   |       | .,      |   |

|-----|-------|---------|---|

| 100 | ntını | uación` | ١ |

|     |       |         |   |

| Código |       |                                       |

|--------|-------|---------------------------------------|

| (Dec)  | (Hex) | Orden                                 |

| 8      | 08    | No asignado                           |

| 9      | 09    | Estado de detención y almacenamiento  |

| 10     | 0A    | No asignado                           |

| 11     | 0B    | reinicio de la CPU inicial            |

| 12     | 0C    | Reinicio de la CPU                    |

| 13     | 0D    | Prefijo de Conjunto                   |

| 14     | 0R    | Estado de almacenamiento en dirección |

| 15-17  | 0F-11 | No asignado                           |

| 18     | 12    | Establecer Arquitectura               |

| 19     | 13    | Señal de emergencia condicional       |

| 14     | 14    | No asignado                           |

| 21     | 15    | Estado de ejecución de detección      |

| 22-255 | 16-FF | No asignado                           |

El número binario de 16 bits contenido en las posiciones de bit 48-63 del registro general R<sub>3</sub> forma la dirección de la CPU. Los bits 0-47 del registro se ignoran. Cuando el orden especificado es la orden Establecer Arquitectura, la dirección de la CPU se ignora; todas las demás CPU en la configuración se consideran direccionadas.

El registro general que contiene el parámetro de 32 bits en las posiciones de bit 32-63 es  $R_1$  o  $R_1$  + 1, el que sea el registro impar. Depende del código de orden si se proporciona un parámetro y para qué se utiliza.

10 Los operandos recién descritos tienen los siguientes formatos, en un ejemplo: