# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 749 519

51 Int. Cl.:

G06F 15/167 (2006.01) G06F 12/08 (2006.01) G06F 13/16 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 27.09.2013 PCT/CN2013/084481

(87) Fecha y número de publicación internacional: 17.04.2014 WO14056405

(96) Fecha de presentación y número de la solicitud europea: 27.09.2013 E 13844885 (7)

(97) Fecha y número de publicación de la concesión europea: 12.06.2019 EP 2908251

(54) Título: Método y dispositivo para procesar datos

(30) Prioridad:

09.10.2012 CN 201210379871

Fecha de publicación y mención en BOPI de la traducción de la patente: **20.03.2020**

(73) Titular/es:

ZTE CORPORATION (100.0%) ZTE Plaza, Keji Road South, Hi-Tech Industrial Park, Nanshan District Shenzhen, Guangdong 518057, CN

(72) Inventor/es:

SHI, XINZHUO

(74) Agente/Representante:

VALLEJO LÓPEZ, Juan Pedro

## **DESCRIPCIÓN**

Método y dispositivo para procesar datos

#### 5 Campo técnico

La presente invención se refiere al campo de comunicaciones de datos, y particularmente, a un método y dispositivo para procesar datos.

#### 10 Antecedentes de la técnica relacionada

En diseños lógicos digitales a gran escala en el campo de comunicaciones de datos, en ocasiones para mejorar la capacidad de procesamiento de un circuito lógico o para igualar los anchos de bit de buses en ambos lados del circuito lógico, se necesita realizar conversión de ancho de bit en trayectoria de datos del circuito lógico. Teniendo en cuenta que los anchos de banda totales en ambos lados del circuito lógico no son necesariamente los mismos, o que puede producirse una condición de congestión en un lado, el circuito lógico también necesita ser capaz de almacenar en memoria caché los datos a transmitir.

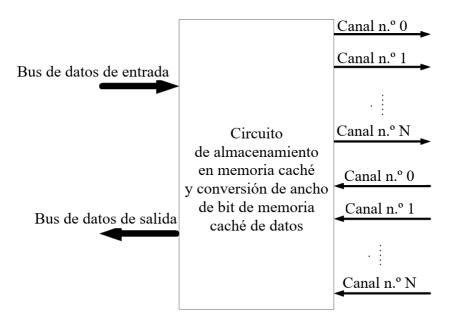

Por ejemplo, un escenario de aplicación de este tipo es como se muestra en la Figura 1. En el lado de enlace ascendente, se introducen datos por un bus de datos en un lado y transmiten a Y (Y es un número entero igual a o mayor de 1) canales en el otro lado, y en el lado de enlace descendente, los datos se agregan desde los Y canales de acuerdo con una indicación de planificación y a continuación se transmiten al bus de datos para emitir. Para los datos transmitidos en el bus de datos, cada dato es únicamente para un canal; para usar de forma eficiente el ancho de banda de los respectivos canales, únicamente se transmiten los datos válidos en los respectivos canales. El ancho de bit del bus de datos es A, el ancho de bus de cada dispositivo es B, y A es N veces (N es un número entero mayor que o igual a 1) B. Teniendo en cuenta que el ancho de banda del bus de datos no es necesariamente igual al ancho de banda total de respectivos canales y es probable que se produzca una condición de congestión tanto en el bus de datos como respectivos canales, necesitan proporcionarse memorias caché en las trayectorias de transmisión tanto de enlace ascendente como enlace descendente.

30

35

40

45

50

55

15

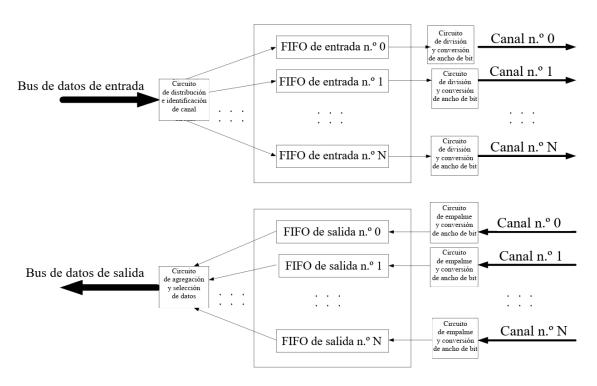

En este sentido, generalmente el circuito lógico como se muestra en la Figura 2 puede usarse para implementar la memoria caché de datos y conversión de ancho de bit, en el que se usa FIFO (primero en entrar primero en salir) para realizar la memoria caché de datos, y se usa un circuito de división y conversión de ancho de bit separado para implementar los datos conversión de ancho de bit. En el lado de enlace ascendente, un circuito de distribución e identificación de canal distribuye los datos junto con la indicación de campo de bit válido de los datos a los FIFO de entrada que tienen un ancho de bit de "A + el ancho de indicación de campo de bit válido de los datos" en una correspondencia uno a uno a respectivos canales de acuerdo con el destino de los datos en el bus de datos de entrada; cuando un correspondiente canal puede recibir los datos introducidos, los datos se leen a partir del FIFO de entrada, y la porción válida de los datos se convierte por el circuito de división y conversión de ancho de bit a un flujo de datos con un ancho de bit de B de acuerdo con la indicación de campo de bit válido de los datos, y se envían al correspondiente canal. En el lado de enlace descendente, el circuito de empalme y conversión de ancho de bit primero convierte los datos transmitidos desde los respectivos canales a datos con un ancho de bit de A, y a continuación escribe los datos en los FIFO de salida en una correspondencia uno a uno con los respectivos canales; cuando el bus de datos puede recibir datos, el circuito de agregación y selección de datos lee los datos desde las respectivas FIFO de salida de acuerdo con un orden de planificación, y agrega y emite los datos al bus de datos de salida.

En el que, el circuito de división y conversión de ancho de bit que implementa los datos conversión de ancho de bit consiste principalmente en un demultiplexor (DMUX) cuyo modo de funcionamiento es como se indica a continuación:

Para cada canal, después de que los datos con un ancho de bit de A y la indicación de campo de bit válido de los datos se leen a partir de los FIFO de entrada, se almacenan primero en un registro. El circuito de división y conversión de ancho de bit selecciona y emite los datos con una anchura de B en su primera porción en el primer ciclo, y emite los datos con una anchura de B adyacentes a los últimos datos en el segundo ciclo, y hasta que todos los datos válidos se planifican para emitir, el circuito de división y conversión de ancho de bit pasa a los siguientes datos leídos desde los FIFO de entrada, y continúa realizando la conversión de ancho de bit de acuerdo con el modo anteriormente mencionado.

60

El circuito de empalme y conversión de ancho de bit básicamente es un proceso inverso del circuito de división y conversión de ancho de bit, y consiste principalmente en un multiplexor (MUX) cuyo modo de funcionamiento es como se indica a continuación:

Para cada canal, después de que los datos con un ancho de bit de B se emiten desde los canales, se empalman juntos mediante el circuito de empalme y conversión de ancho de bit en datos con una anchura de A de acuerdo con la orden de emisión, y se escriben en las correspondientes FIFO de salida.

65

En este método, si únicamente una porción de campos de bit en los datos introducidos por el bus de datos de lado

de enlace ascendente o los datos (con todo el ancho de bit siendo A) emitidos desde los respectivos canales en el lado de enlace descendente y empalmados juntos por el circuito de empalme y conversión de ancho de bit son válidos, cuando se almacenan en el FIFO, estos datos aún necesitan ocupar una anchura de "A + el ancho de indicación de campo de bit válido de los datos", que es exactamente la misma que el caso en el que todos los campos de bit de estos datos son válidos, resultando en su relativamente baja utilización de caché.

Además, teniendo en cuenta la implementación específica del circuito: si se usa el modo de FPGA (Campo de Matriz de Puertas Programables) para implementar este circuito, porque el ancho de bit de la RAM de bloque (memoria de acceso aleatorio de bloque) para conseguir el FIFO en el FPGA es limitado, y su longitud es mucho mayor que su ancho (tomar el Virex-5 FPGA en Xilinx por ejemplo, el ancho de bit de configuración máxima de una RAM de bloque de 36 kb puede alcanzar únicamente 36 bits), teniendo en cuenta que este método necesita usar Y FIFO con el ancho de bit de "A + ancho de indicación de campo de bit válido de los datos", cuando el ancho de bus de datos A es relativamente grande, el uso del modo de FPGA necesita empalmar el ancho de bits de una pluralidad de RAM de bloque para conseguir cada FIFO. Por tanto, se consumirá una cantidad considerable de recursos de RAM de bloque y se ocupará un área de diseño grande, especialmente cuando el número de canales Y es relativamente grande. Incluso si se usa el ASIC para implementar el circuito lógico relacionado, el FIFO con un ancho de bit tan grande traerá presiones al extremo final en términos de disposición y retardo de temporización y también ocuparán una gran área de diseño.

20 El documento WO 2009/089301 divulga una memoria intermedia de datos en la que datos están fluyendo desde un lado al otro y viceversa de acuerdo con una técnica de segmentación de tiempo.

El documento US 2006/088049 divulga un árbitro de memoria intermedia que usa un algoritmo basado en intervalo de tiempo para cumplir con los requisitos de ancho de banda y latencia de múltiples canales.

#### Sumario de la invención

La invención se establece en el conjunto adjunto de las reivindicaciones. Las reivindicaciones dependientes exponen realizaciones particulares. Las realizaciones o ejemplos de la siguiente descripción que no están cubiertos por las reivindicaciones adjuntas se consideran que no son parte de la invención de acuerdo con esta descripción.

El problema técnico a resolver mediante la presente invención es proporcionar un método y dispositivo para procesar datos, para ahorrar recursos de memoria caché y mejorar la utilización de memoria caché mientras se consigue de forma fiable memoria caché de datos y conversión de ancho de bit.

Para resolver el problema técnico anteriormente mencionado, la presente invención proporciona un método para procesar datos, que comprende:

después de recibir datos introducidos por un bus de datos, de acuerdo con una indicación de destino de los datos y una indicación de campo de bit válido de los datos, escribir los datos introducidos por el bus de datos en una memoria caché compartida de lado de enlace ascendente;

interrogar la memoria caché compartida de lado de enlace ascendente de acuerdo con un orden de intervalo de tiempo fijo, leer datos en la memoria caché compartida de lado de enlace ascendente y emitir los datos a respectivos canales correspondientes.

Preferentemente, el método anterior puede tener las siguientes características: la memoria caché compartida de lado de enlace ascendente consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bits especificado, y cada pieza de RAM se divide lógicamente en Y segmentos de RAM,

dicha interrogación de la memoria caché compartida de lado de enlace ascendente de acuerdo con un orden de intervalo de tiempo fijo y lectura de datos en la memoria caché compartida de lado de enlace ascendente comprende las siguientes maneras:

cuando N≥Y, cada ciclo de interrogación es N intervalos de tiempo, y se accede a Y segmentos de RAM en cada intervalo de tiempo;

cuando N<Y, cada ciclo de interrogación es Y intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo.

Preferentemente, el método anterior tiene adicionalmente las siguientes características: en el proceso de escribir los datos introducidos por el bus de datos en una memoria caché compartida de lado de enlace ascendente, comprende además:

grabar una posición de escritura de cola de datos actuales de acuerdo con canales.

Para resolver el problema anteriormente mencionado, la presente invención proporciona adicionalmente un dispositivo para procesar datos, que comprende:

3

30

25

10

15

40

35

45

50

55

un módulo de control de escritura de lado de enlace ascendente, configurado para: después de recibir datos introducidos por un bus de datos, de acuerdo con una indicación de destino de los datos y una indicación de campo de bit válido de los datos, escribir los datos introducidos por el bus de datos en una memoria caché compartida de lado de enlace ascendente;

5

un módulo de control de lectura de lado de enlace ascendente, configurado para: interrogar de acuerdo con un orden de intervalo de tiempo fijo para leer los datos en la memoria caché compartida de lado de enlace ascendente, y emitir los datos a respectivos canales correspondientes.

10 Preferentemente, el dispositivo anterior comprende además las siguientes características:

la memoria caché compartida de lado de enlace ascendente consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bits especificado, y cada pieza de RAM se divide lógicamente en Y segmentos de RAM,

15

el módulo de control de lectura de lado de enlace ascendente se configura para interrogar de acuerdo con un orden de intervalo de tiempo fijo para leer los datos en la memoria caché compartida de lado de enlace ascendente de las siguientes maneras: cuando  $N \ge Y$ , cada ciclo de interrogación tiene N intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo; cuando N cada ciclo de interrogación tiene N intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo.

20

Preferentemente, el dispositivo anterior comprende además las siguientes características:

el módulo de control de escritura de lado de enlace ascendente se configura adicionalmente para, en el proceso de escribir los datos introducidos por el bus de datos en la memoria caché compartida de lado de enlace ascendente, grabar la posición de escritura de cola de datos actuales de acuerdo con canales.

25

Para resolver el problema anteriormente mencionado, la presente invención proporciona adicionalmente un método para procesar datos, que comprende:

30

almacenar datos emitidos por respectivos canales en una memoria caché compartida de lado de enlace descendente;

leer los datos de la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación, y emitir los datos a un bus de datos.

35 Preferentemente, el método anterior tiene adicionalmente las siguientes características:

la memoria caché compartida de lado de enlace descendente consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bits especificado, y cada pieza de RAM se divide lógicamente en Y segmentos de RAM.

40

dicho almacenamiento de datos emitidos por respectivos canales en una memoria caché compartida de lado de enlace descendente comprende:

interrogar respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo, y si una columna de segmentos de RAM que se está interrogando en la actualidad tiene espacio libre, almacenar los datos a emitir en un correspondiente canal en la columna de segmentos de RAM.

45

50

Preferentemente, el método anterior tiene adicionalmente las siguientes características: dicha interrogación de respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo comprende las siguientes maneras:

cuando  $N \ge Y$ , cada ciclo de interrogación tiene N intervalos de tiempo, y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N < Y, cada ciclo de interrogación tiene Y intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo.

55 Pi m

Preferentemente, el método anterior tiene adicionalmente las siguientes características: dicha lectura de datos de la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación comprende: calcular una cantidad general de datos almacenados en memoria caché en cada columna de segmentos de RAM, y cuando la cantidad de datos almacenados en memoria caché en la columna de segmentos de RAM es mayor que o igual a la cantidad de datos requeridos por la indicación de planificación actual, leer los datos emitidos en la planificación actual de respectivos segmentos de RAM basándose en una indicación de longitud de campo de bit de planificación.

Dana maaba

Para resolver el problema anteriormente mencionado, la presente invención proporciona adicionalmente un dispositivo para procesar datos, que comprende:

65

60

un módulo de control de escritura de lado de enlace descendente, configurado para: almacenar datos emitidos

por respectivos canales en una memoria caché compartida de lado de enlace descendente;

un módulo de control de lectura de lado de enlace descendente, configurado para: leer los datos de la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación, y emitir los datos a un bus de datos.

Preferentemente, el dispositivo anterior comprende además las siguientes características:

la memoria caché compartida de lado de enlace descendente consta de N piezas de memoria de acceso 10 aleatorio (RAM) con un ancho de bits especificado, y cada pieza de RAM se divide lógicamente en Y segmentos de RAM,

el módulo de control de escritura de lado de enlace descendente se configura para: interrogar respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo, y si una columna de segmentos de RAM que se está interrogando en la actualidad tiene espacio libre, almacenar los datos a emitir en un correspondiente canal en la columna de segmentos de RAM.

Preferentemente, el dispositivo anterior comprende además las siguientes características:

20 el módulo de control de escritura de lado de enlace descendente se configura para interrogar respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo de las siguientes maneras: cuando N ≥ Y, cada ciclo de interrogación tiene N intervalos de tiempo, y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N<Y, cada ciclo de interrogación tiene Y intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo. 25

Preferentemente, el dispositivo anterior comprende además las siguientes características:

el módulo de control de lectura de lado de enlace descendente se configura para: calcular una cantidad general de datos almacenados en memoria caché en cada columna de segmentos de RAM, y cuando la cantidad de datos almacenados en memoria caché en la columna de segmentos de RAM es mayor que o igual a la cantidad de datos requeridos por una indicación de planificación actual, leer los datos emitidos en la planificación actual de respectivos segmentos de RAM basándose en una indicación de longitud de campo de bit de planificación.

En resumen, las realizaciones de la presente invención proporcionan un método y dispositivo para procesar datos para habilitar un ahorro efectivo de recursos de memoria caché, reducción de presión en el área y temporización y mejora de la utilización de memoria caché mientras se consigue de forma fiable la memoria caché de datos y conversión de ancho de bit.

#### Breve descripción de los dibujos

- 40 En lo sucesivo, se introducirán brevemente los dibujos adjuntos necesarios en la descripción de las realizaciones y la técnica anterior. De manera evidente, los dibujos adjuntos en la siguiente descripción son únicamente algunas realizaciones de la presente invención, y para un experto en la materia, sobre la premisa de no pagar esfuerzos creativos, otros dibujos adjuntos no pueden obtenerse de acuerdo con estos dibujos adjuntos.

- 45 La Figura 1 es un diagrama esquemático de un escenario de aplicación de un circuito de conversión de ancho de bit de memoria caché de datos:

- La Figura 2 es un diagrama estructural de un circuito de almacenamiento en memoria caché y conversión de ancho de bit de memoria caché de datos en la técnica anterior;

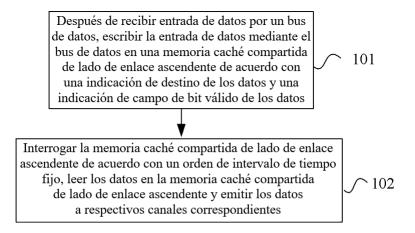

- La Figura 3 es un diagrama de flujo de un método para procesar datos en una dirección de lado de enlace ascendente de acuerdo con una realización de la presente invención;

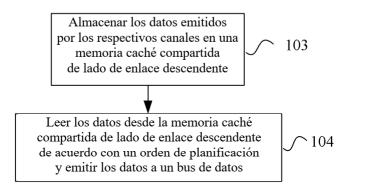

- La Figura 4 es un diagrama de flujo de un método para procesar datos en una dirección de lado de enlace descendente de acuerdo con una realización de la presente invención:

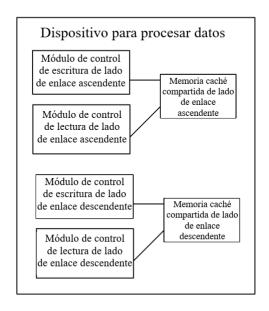

- La Figura 5 es un diagrama esquemático de un dispositivo para procesar datos de acuerdo con una realización de la presente invención;

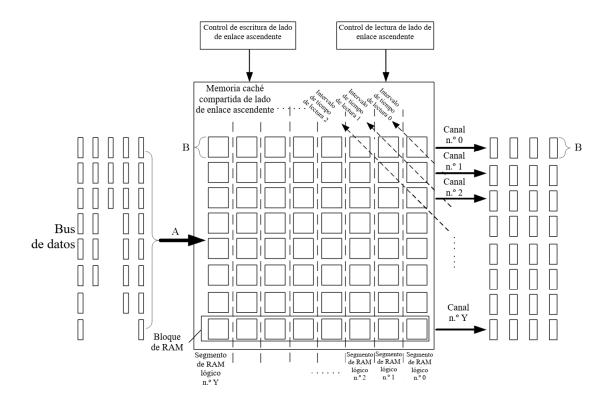

- La Figura 6 es un diagrama esquemático de un proceso de transmisión de lado de enlace ascendente de 60 acuerdo con una realización de la presente invención;

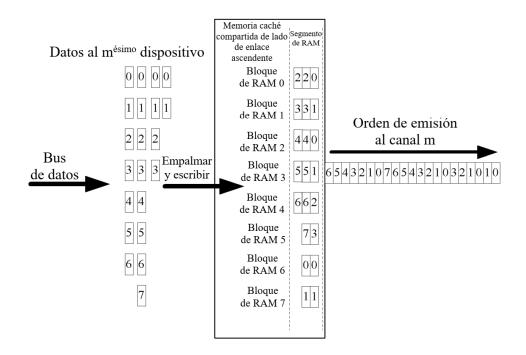

- La Figura 7 es un diagrama esquemático de un proceso de transmisión de lado de enlace ascendente de un solo canal de acuerdo con una realización de la presente invención;

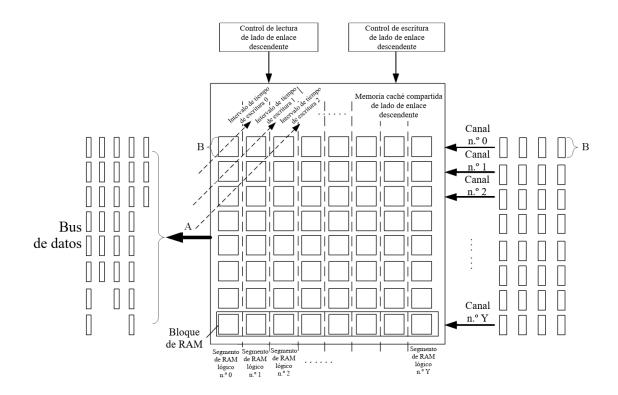

- La Figura 8 es un diagrama esquemático de un proceso de transmisión de lado de enlace descendente de

5

50

5

15

30

35

55

acuerdo con una realización de la presente invención.

## Realizaciones preferidas de la invención

15

25

30

35

- En lo sucesivo en conjunto con los dibujos adjuntos, se describirán las realizaciones de la presente invención en detalle. Se ha de observar que, en el caso de que no haya conflicto, realizaciones y características en las realizaciones de la presente solicitud pueden combinarse aleatoriamente entre sí.

- La Figura 3 es un diagrama de flujo de un método para procesar datos en una dirección de lado de enlace ascendente de acuerdo con una realización de la presente invención, y como se muestra en la Figura 3, el método de la presente realización comprende:

- Etapa 101, en una dirección de lado de enlace ascendente, después de recibir datos introducidos por el bus de datos, de acuerdo con una indicación de destino de los datos y una indicación de campo de bit válido de los datos, escribir los datos introducidos por el bus de datos en una memoria caché compartida de lado de enlace ascendente:

- en el que, la indicación de destino y la indicación de campo de bit válido de los datos actuales se proporcionan al mismo tiempo cuando los datos se introducen por el bus de datos.

- De acuerdo con la indicación de destino y la indicación de campo de bit válido de los datos, los datos introducidos por el bus de datos se almacenan en respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace ascendente.

- Etapa 102, interrogar la memoria caché compartida de lado de enlace ascendente de acuerdo con un orden de intervalo de tiempo fijo, leer los datos en la memoria caché compartida de lado de enlace ascendente y emitir los datos a correspondientes canales.

- Interrogará a respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace ascendente de acuerdo con un orden de intervalo de tiempo fijo, y si un segmento de RAM que se está interrogando en la actualidad no está vacío y un correspondiente canal de salida puede recibir datos, a continuación leerá los datos en el segmento de RAM que se está interrogando en la actualidad y emitir los datos al correspondiente canal.

- En la etapa 101, la "indicación de destino" que sincroniza con datos se usa para indicar el número del canal para el que se destinan los datos, y la "indicación de campo de bit válido" que sincroniza con datos se usa para indicar cuántas porciones (normalmente medidas con el ancho de bit B de canal, a saber el ancho de bit de RAM, como unidad) en los datos actuales son válidas. En la etapa 102, cuando se almacenan los datos en la memoria caché compartida de lado de enlace ascendente, el módulo de control de escritura necesita grabar la posición de escritura de la cola de los datos actuales de acuerdo con canales como la base de escritura en los siguientes datos destinados para el mismo canal.

- La Figura 4 es un diagrama de flujo de un método para procesar datos en una dirección de lado de enlace descendente de acuerdo con una realización de la presente invención, y como se muestra en la Figura 4, el método de la presente realización comprende:

- Etapa 103, en la dirección de lado de enlace descendente, almacenar los datos emitidos por los respectivos canales en una memoria caché compartida de lado de enlace descendente; cuando un canal tiene datos a emitir, y los segmentos de RAM en la correspondiente memoria caché compartida de lado de enlace descendente tienen espacio libre, los datos se emiten a través del canal a través del control del módulo de control de escritura de lado de enlace descendente, y almacenan en respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente.

- Etapa 104, leer los datos desde la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación y emitir los datos a un bus de datos.

- Accederá a respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación, y agregar y emitir los datos al bus de datos.

- La Figura 5 es un diagrama esquemático de un dispositivo para procesar datos de acuerdo con una realización de la presente invención, y como se muestra en la Figura 5, comprende los siguientes módulos:

- un módulo de control de escritura de lado de enlace ascendente, un módulo de control de lectura de lado de enlace ascendente, un módulo de control de escritura de lado de enlace descendente, un módulo de control de lectura de lado de enlace descendente y una memoria caché compartida de lado de enlace descendente. En el que, las memorias caché compartidas de enlace ascendente y enlace descendente se usan para implementar la función de memoria caché de datos, y los módulos de control de lectura y escritura de ancho de bit de enlace ascendente y enlace descendente y las memorias caché compartidas de enlace ascendente y enlace descendente y en

Dividiendo de acuerdo con la dirección de flujo de datos, el lado de enlace ascendente (desde el bus de datos hasta respectivos canales) comprende las siguientes partes:

un módulo de control de escritura de lado de enlace ascendente usado para, después de recibir datos introducidos por un bus de datos, de acuerdo con una indicación de destino de los datos y una indicación de campo de bit válido de los datos, escribir los datos introducidos por el bus de datos en una memoria caché compartida de lado de enlace ascendente;

5

30

40

45

- un módulo de control de lectura de lado de enlace ascendente usado para interrogar la memoria caché compartida de lado de enlace ascendente de acuerdo con un orden de intervalo de tiempo fijo, leer los datos en la memoria caché compartida de lado de enlace ascendente, y emitir los datos a respectivos canales;

- una memoria caché compartida de lado de enlace ascendente que consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bit de B, y cada pieza de RAM se divide lógicamente en Y segmentos de RAM para almacenar los datos a emitir a respectivos canales.

- En el que, el módulo de control de lectura de lado de enlace ascendente interroga de acuerdo con un orden de intervalo de tiempo fijo para leer los datos en la memoria caché compartida de lado de enlace ascendente de las siguientes maneras: cuando N≥Y, cada ciclo de interrogación es N intervalos de tiempo, y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N<Y, cada ciclo de interrogación es Y intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo.

- En el que, el módulo de control de escritura de lado de enlace ascendente se usa adicionalmente para, en el proceso de escribir los datos introducidos por el bus de datos en la memoria caché compartida de lado de enlace ascendente, grabar la posición de escritura de la cola de los datos actuales de acuerdo con canales.

- Dividiendo de acuerdo con dirección de flujo de datos, el lado de enlace descendente (desde respectivos canales al bus de datos) comprende las siguientes partes:

- un módulo de control de escritura de lado de enlace descendente usado para almacenar los datos emitidos por respectivos canales en una memoria caché compartida de lado de enlace descendente;

- un módulo de control de lectura de lado de enlace descendente usado para leer los datos de la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación y emitir los datos al bus de datos;

- una memoria caché compartida de lado de enlace descendente que consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bit de B, y cada pieza de RAM se divide lógicamente en Y segmentos de RAM para almacenar los datos a emitir al bus de datos.

- En el que, el módulo de control de escritura de lado de enlace descendente se usa específicamente para interrogar respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo, y si una columna de segmentos de RAM que se está interrogando en la actualidad tiene espacio libre, almacenar los datos a emitir mediante un correspondiente canal en la columna de segmentos de RAM.

- En el que, el módulo de control de escritura de lado de enlace descendente interroga respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo de las siguientes maneras: cuando N≥Y, cada ciclo de interrogación es N intervalos de tiempo, y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N<Y, cada ciclo de interrogación es Y intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo.

- En el que, el módulo de control de lectura de lado de enlace descendente se usa específicamente para calcular una cantidad general de datos almacenados en memoria caché en cada columna de segmentos de RAM, y cuando la cantidad de datos almacenados en memoria caché en la columna de segmentos de RAM es mayor que o igual a la cantidad de datos requeridos por la indicación de planificación actual, leer los datos emitidos en la planificación actual de los respectivos segmentos de RAM basándose en una indicación de longitud de campo de bit de planificación.

- En lo sucesivo en conjunto con los dibujos adjuntos y realizaciones específicas, la presente invención se describirá adicionalmente en detalle. Las realizaciones descritas son meramente parte de realizaciones, pero no todas las realizaciones de la presente invención. Basándose en las realizaciones de la presente invención, todas las demás realizaciones obtenidas por los expertos en la materia sin esfuerzos creativos pertenecerán al alcance de protección de la presente invención.

La presente invención emplea un modo de operación de una memoria caché compartida de acuerdo con un orden de intervalo de tiempo fijo para conseguir conversión de ancho de bit de los datos, y emplea modo de empalme y almacenamiento de los datos válidos para conseguir mejora de eficiencia de memoria caché, para resolver los problemas en la técnica anterior de que la utilización de memoria caché no es alta, y que demasiados recursos lógicos y área de diseño están ocupados cuando se implementa el FPGA.

Los diagramas de bloque para implementar las realizaciones de la presente invención se muestran en la Figura 6, la Figura 7 y la Figura 8. En las que, las memorias caché compartidas de enlace ascendente y enlace descendente constan ambas de N piezas de RAM de puerto dual simple, y cada pieza de RAM se divide lógicamente en Y segmentos de RAM. Los segmentos de RAM en la misma columna corresponden al mismo canal, y se llaman una columna de segmentos de RAM. La memoria caché compartida divide un intervalo de dirección para cada segmento de RAM lógico, y en el proceso de realización de operación de lectura o escritura en la memoria caché compartida, respectivos segmentos de RAM se distinguen a través de las direcciones de lectura y escritura; cada segmento de RAM lógico se controla por lectura y escritura de acuerdo con un intervalo de tiempo fijo, y cuando se selecciona y se activa la habilitación de lectura, se emiten los datos en la primera porción del segmento de RAM, y cuando se selecciona y la habilitación de escritura tiene que activarse, los datos se escriben en la porción terminal del segmento de RAM.

Por simplicidad y conveniencia, a continuación, el proceso de funcionamiento de la presente invención se describe en detalle únicamente tomando el caso de N=Y=8 como un ejemplo: los procesos de escritura y lectura completos en el lado de enlace ascendente se muestran en la Figura 6.

El proceso de escritura en el lado de enlace ascendente:

15

25

30

35

50

55

60

Como se muestra en la Figura 6, en el lado de enlace ascendente, la indicación de destino que sincroniza con los datos transmitidos en el bus de datos indica el número del canal para el que se destinan los datos actuales; la indicación de campo de bit válido que sincroniza con los datos indica tomar el ancho de bit B de pieza de RAM como unidad para medir cuántas porciones en los datos actuales del bit superior son válidas.

Después de que cada dato se escribe completamente, el módulo de control de escritura de lado de enlace ascendente grabará la posición final de escritura actual (escrita en qué segmento de RAM en la columna de segmentos de RAM) para la columna de segmentos de RAM escrita. En cada escritura, el módulo de control de escritura de lado de enlace ascendente selecciona una columna de segmentos de RAM de acuerdo con la indicación de destino, y a continuación toma la columna de segmentos de RAM de "la última posición final de escritura + 1" como la posición de inicio de la escritura actual, y de acuerdo con la indicación de campo de bit válido de los datos, determina activar la habilitación de escritura de las piezas de RAM de "campo de bit válido" a su vez de la posición de inicio de la escritura actual. Los datos válidos en el bus de datos también se enviarán secuencialmente a los respectivos segmentos de RAM seleccionados en la actualidad a partir de la posición de inicio de la escritura actual.

En este ejemplo, como se muestra en la Figura 7, las longitudes de campo de bit válido de los segundos datos y los terceros datos que se destinan secuencialmente para el canal n.º m son 4B y 8B, respectivamente. Antes de escribir en los segundos datos, la posición final de escritura de la columna de segmentos de RAM n.º m que corresponde al canal n.º m es el segmento de RAM n.º 1. Cuando se escribe en los segundos datos, los datos se almacenan secuencialmente en el segmento de RAM n.º 2 ~ segmento de RAM n.º 5 desde el principio hasta el final, y después de que se completa la escritura, la posición final de escritura de la columna de segmentos de RAM n.º m se actualiza como el segmento de RAM n.º 5; cuando se escribe en los terceros datos, los datos se almacenan secuencialmente desde el principio hasta el final en el segmento de RAM n.º 6, segmento de RAM n.º 7, segmento de RAM n.º 0, segmento de RAM n.º 1, segmento de RAM n.º 2, segmento de RAM n.º 3, segmento de RAM n.º 4 y segmento de RAM n.º 5, y después de que la escritura se completa, la posición final de escritura de la columna de segmentos de RAM n.º m se actualiza como el segmento de RAM n.º 5.

El proceso de lectura en el lado de enlace ascendente:

El módulo de control de lectura de lado de enlace ascendente interroga respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace ascendente en un orden fijo de acuerdo con intervalo de tiempo. Cuando N>Y, cada ciclo de interrogación es N intervalos de tiempo, y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N<Y, cada ciclo de interrogación es Y intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo. Para la misma columna de segmentos de RAM, se accede a dos segmentos de RAM superior e inferior adyacentes secuencialmente en dos intervalos de tiempo adyacentes. En este caso, su orden de interrogación se muestra como se indica a continuación: en intervalo de tiempo de lectura 0: accederá al segmento de RAM 0, grupo de RAM 0; segmento de RAM 1, grupo de RAM 4, grupo de RAM 4; segmento de RAM 5, grupo de RAM 5; segmento de RAM 4, grupo de RAM 4, grupo de RAM 1.

En intervalo de tiempo de lectura 1: accederá al segmento de RAM 0, grupo de RAM 1; segmento de RAM 1, grupo de RAM 0; segmento de RAM 2, grupo de RAM 7; segmento de RAM 3, grupo de RAM 6; segmento de RAM 4, grupo de RAM 5; segmento de RAM 5; segmento de RAM 3; segmento de RAM 3

### 7, grupo de RAM 2.

30

35

45

60

En intervalo de tiempo de lectura 2: accederá al segmento de RAM 0, grupo de RAM 2; segmento de RAM 1, grupo de RAM 1; segmento de RAM 2, grupo de RAM 0; segmento de RAM 3, grupo de RAM 7; segmento de RAM 4, grupo de RAM 6; segmento de RAM 5, grupo de RAM 6; segmento de RAM 4; segmento de RAM 7, grupo de RAM 3.

En intervalo de tiempo de lectura 3: accederá al segmento de RAM 0, grupo de RAM 3; segmento de RAM 1, grupo de RAM 2; segmento de RAM 2, grupo de RAM 1; segmento de RAM 3, grupo de RAM 0; segmento de RAM 4, grupo de RAM 7; segmento de RAM 5, grupo de RAM 6; segmento de RAM 6, grupo de RAM 5; segmento de RAM 7, grupo de RAM 4.

En intervalo de tiempo de lectura 4: accederá al segmento de RAM 0, grupo de RAM 4; segmento de RAM 1, grupo de RAM 3; segmento de RAM 2; segmento de RAM 3, grupo de RAM 1; segmento de RAM 4, grupo de RAM 0; segmento de RAM 5, grupo de RAM 6; segmento de RAM 7; segmento de RAM 6, grupo de RAM 6; segmento de RAM 7, grupo de RAM 5.

En intervalo de tiempo de lectura 5: accederá al segmento de RAM 0, grupo de RAM 5; segmento de RAM 1, grupo de RAM 4; segmento de RAM 2, grupo de RAM 3; segmento de RAM 3, grupo de RAM 2; segmento de RAM 4, grupo de RAM 1; segmento de RAM 5, grupo de RAM 6, grupo de RAM 7; segmento de RAM 7, grupo de RAM 6.

En intervalo de tiempo de lectura 6: accederá al segmento de RAM 0, grupo de RAM 6; segmento de RAM 1, grupo de RAM 5; segmento de RAM 2, grupo de RAM 4; segmento de RAM 3, grupo de RAM 3; segmento de RAM 4, grupo de RAM 2; segmento de RAM 5, grupo de RAM 0; segmento de RAM 7, grupo de RAM 7.

En intervalo de tiempo de lectura 7: accederá al segmento de RAM 0, grupo de RAM 7; segmento de RAM 1, grupo de RAM 6; segmento de RAM 2, grupo de RAM 5; segmento de RAM 3, grupo de RAM 4; segmento de RAM 4, grupo de RAM 3; segmento de RAM 5, grupo de RAM 6, grupo de RAM 1; segmento de RAM 7, grupo de RAM 0.

En el lado de enlace ascendente, cada columna de segmentos de RAM grabará la última posición final de lectura, y si la posición de un segmento de RAM que se está interrogando en la actualidad es "la última posición final de lectura de la columna de segmentos de RAM + 1", y el segmento de RAM no está vacío y mientras tanto su correspondiente canal de salida puede recibir datos en la actualidad, a continuación la habilitación de lectura de la pieza de RAM en la que se ubica el segmento de RAM se activa alta, y los datos leídos en este momento se envían a un canal que corresponde a la RAM; y en los otros casos, no se emiten datos.

40 Los procesos de escritura y lectura completos en el lado de enlace descendente se muestran como la Figura 8.

El proceso de escritura en el lado de enlace descendente:

El módulo de control de escritura de lado de enlace descendente interroga respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente en un orden fijo de acuerdo con intervalo de tiempo, y su orden es el mismo que el orden de interrogación de intervalo de tiempo de lectura en el lado de enlace ascendente. Cuando N>Y, cada ciclo de interrogación es N intervalos de tiempo, y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N<Y, cada ciclo de interrogación es Y intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo.

El módulo de control de escritura de lado de enlace descendente graba la última posición de escritura para cada columna de segmentos de RAM. Si la posición de un segmento de RAM que se está interrogando en la actualidad es "la última posición de escritura de la columna de segmentos de RAM+1", y el segmento de RAM tiene espacio libre y mientras tanto su correspondiente canal tiene datos a emitir, a continuación se activa la habilitación de escritura de la pieza de RAM en la que se ubica el segmento de RAM, y los datos introducidos desde el correspondiente canal se envían al segmento de RAM; y en los otros casos, no se realiza ninguna operación de escritura de datos.

El proceso de lectura en el lado de enlace descendente: el módulo de control de lectura de lado de enlace descendente calcula una cantidad general de datos almacenados en memoria caché para cada columna de segmentos de RAM, y cuando la cantidad de datos almacenados en memoria caché en la columna de segmentos de RAM es mayor que o igual a la cantidad de datos requeridos por la indicación de planificación actual, el módulo de control de lectura de lado de enlace descendente inicia una operación de lectura, y mientras tanto proporciona una indicación de longitud de campo de bit de planificación (tomando el ancho de bit de pieza de RAM como la unidad de medición).

65 El módulo de control de lectura de lado de enlace descendente graba la última posición final de lectura para cada columna de segmentos de RAM. Cuando se inicia la operación de lectura, el módulo de control de lectura de lado de

enlace descendente toma el segmento de RAM de "la última posición final de lectura de la columna de segmentos de RAM+1" como la posición de inicio del segmento de RAM, y lee los datos emitidos en la planificación actual de respectivos segmentos de RAM de acuerdo con una indicación de longitud de campo de bit de planificación, y envía los datos al bus de datos para emitir.

5

10

15

20

A partir de la descripción de las realizaciones anteriormente mencionadas, puede observarse que, cuando se implementan conversión de ancho de bit de datos y funciones de almacenamiento en memoria caché, ya que los datos válidos se almacenan en memoria caché por medio de empalme en los procesos de escritura de lado de enlace ascendente y enlace descendente, su utilización de memoria caché es mayor que la solución en los antecedentes de la técnica relacionada. Además, ya que en la implementación se usan N memorias de caché con una anchura de B, y si el bus de datos A es mucho mayor de B, los recursos de memoria caché en chip pueden utilizarse de forma efectiva en implementación específica, reduciendo por lo tanto el área de diseño y retardo de temporización, que es especialmente evidente cuando el número de canales Y es relativamente grande.

Los expertos en la materia pueden entender que todas o parte de las etapas del método anteriormente mencionado pueden completarse mediante programas que ordenan al hardware pertinente, y los programas anteriormente

mencionados pueden almacenarse en un medio de almacenamiento legible por ordenador, tal como memoria de solo lectura, disco magnético o óptico. Como alternativa, todas o parte de las etapas de las realizaciones anteriormente mencionadas también pueden implementarse usando uno o más circuitos integrados. Por consiguiente, cada módulo/unidad en las realizaciones anteriormente mencionadas puede realizarse en una forma de hardware o en una forma de módulos de función de software. La presente invención no se limita a ninguna forma

específica de combinaciones de hardware y software.

#### Aplicabilidad industrial

25

30

En comparación con la técnica anterior, las realizaciones de la presente invención tienen las siguientes ventajas: el método y dispositivo proporcionado en las realizaciones de la presente invención únicamente realizan conversión de memoria caché y de ancho de bit para campos de bit válidos en los datos cuando se procesan datos, y su utilización de memoria caché y eficiencia de transmisión son relativamente altas; y ya que su implementación usa N piezas de RAM con un ancho de bit de B. cuando el ancho de bit del bus de datos es relativamente grande y se usa el FPGA para implementar, los recursos de RAM en chip pueden usarse de forma efectiva para reducir el área de diseño. Por tanto se superan los problemas y deficiencias en la técnica anterior de que la utilización de memoria caché es relativamente baja, muchos de los recursos de memoria caché se consumen en la implementación específica, y las presiones en el área y temporización son demasiadas.

#### REIVINDICACIONES

1. Un método para procesar datos, que comprende:

después de recibir datos introducidos por un bus de datos, de acuerdo con una indicación de destino de los datos y una indicación de campo de bit válido de los datos, escribir los datos introducidos por el bus de datos en una memoria caché compartida de lado de enlace ascendente;

interrogar la memoria caché compartida de lado de enlace ascendente de acuerdo con un orden de intervalo de tiempo fijo, leer datos en la memoria caché compartida de lado de enlace ascendente y emitir los datos a respectivos canales correspondientes:

en donde la memoria caché compartida de lado de enlace ascendente consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bits especificado, y cada pieza de RAM se divide lógicamente en Y segmentos de RAM; los segmentos de RAM en la misma columna corresponden al mismo canal, y se llaman una columna de segmentos de RAM; comprendiendo, además:

15

20

40

50

55

60

10

en el proceso de escribir los datos introducidos por el bus de datos en la memoria caché compartida de lado de enlace ascendente,

grabar una posición de escritura de cola de datos actuales de acuerdo con los canales; en cada escritura, seleccionar una columna de segmentos de RAM de acuerdo con la indicación de destino, y tomar la columna de segmentos de RAM de "la última posición final de escritura + 1" como la posición de inicio de la escritura actual, y de acuerdo con la indicación de campo de bit válido de los datos, determinar activar la habilitación de escritura de las piezas de RAM de "campo de bit válido" a su vez a partir de la posición de inicio de la escritura actual.

25 2. El método de la reivindicación 1, en el que

dicha interrogación de la memoria caché compartida de lado de enlace ascendente de acuerdo con un orden de intervalo de tiempo fijo y lectura de datos en la memoria caché compartida de lado de enlace ascendente comprende las siguientes maneras:

30 cuando N ≥ Y, cada ciclo de interrogación tiene N intervalos de tiempo y se accede a Y segmentos de RAM en cada intervalo de tiempo;

cuando N<Y, cada ciclo de interrogación tiene Y intervalos de tiempo y se accede a N segmentos de RAM en cada intervalo de tiempo.

35 3. Un dispositivo para procesar datos, que comprende:

un módulo de control de escritura de lado de enlace ascendente, configurado para: después de recibir datos introducidos por un bus de datos, de acuerdo con una indicación de destino de los datos y una indicación de campo de bit válido de los datos, escribir los datos introducidos por el bus de datos en una memoria caché compartida de lado de enlace ascendente;

un módulo de control de lectura de lado de enlace ascendente, configurado para: interrogar de acuerdo con un orden de intervalo de tiempo fijo para leer los datos en la memoria caché compartida de lado de enlace ascendente y emitir los datos a respectivos canales correspondientes;

en donde la memoria caché compartida de lado de enlace ascendente consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bits especificado, y cada pieza de RAM está dividida lógicamente en Y segmentos de RAM; los segmentos de RAM en la misma columna corresponden al mismo canal, y se llaman una columna de segmentos de RAM;

el módulo de control de escritura de lado de enlace ascendente está configurado adicionalmente para, en el proceso de escribir los datos introducidos por el bus de datos en la memoria caché compartida de lado de enlace ascendente, grabar la posición de escritura de cola de datos actuales de acuerdo con los canales; en cada escritura, seleccionar una columna de segmentos de RAM de acuerdo con la indicación de destino, y tomar la columna de segmentos de RAM de "la última posición final de escritura + 1" como la posición de inicio de la escritura actual, y de acuerdo con la indicación de campo de bit válido de los datos, determinar activar la habilitación de escritura de las piezas de RAM de "campo de bit válido" a su vez a partir de la posición de inicio de la escritura actual.

4. El dispositivo de la reivindicación 3, en el que,

el módulo de control de lectura de lado de enlace ascendente está configurado para interrogar de acuerdo con un orden de intervalo de tiempo fijo para leer los datos en la memoria caché compartida de lado de enlace ascendente de las siguientes maneras: cuando N ≥ Y, cada ciclo de interrogación tiene N intervalos de tiempo y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N<Y, cada ciclo de interrogación tiene Y intervalos de tiempo y se accede a N segmentos de RAM en cada intervalo de tiempo.

5. Un método para procesar datos, que comprende:

65

almacenar datos emitidos por respectivos canales en una memoria caché compartida de lado de enlace

descendente:

leer los datos desde la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación,

5 y emitir los datos a un bus de datos;

en donde,

la memoria caché compartida de lado de enlace descendente consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bits especificado, y cada pieza de RAM está dividida lógicamente en Y segmentos de RAM,

dicho almacenamiento de datos emitidos por respectivos canales en una memoria caché compartida de lado de enlace descendente comprende:

interrogar respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo, y si una columna de segmentos de RAM que se está interrogando en la actualidad tiene espacio de almacenamiento, almacenar los datos a emitir en un correspondiente canal en la columna de segmentos de RAM;

en donde los segmentos de RAM en la misma columna corresponden al mismo canal, y se llaman una columna de segmentos de RAM;

dicha lectura de los datos desde la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación comprende:

calcular una cantidad general de datos almacenados en memoria caché en cada columna de segmentos de RAM, y cuando la cantidad de datos almacenados en memoria caché en la columna de segmentos de RAM es mayor que o igual a la cantidad de datos requeridos por la indicación de planificación actual, leer los datos emitidos en la planificación actual desde respectivos segmentos de RAM basándose en una indicación de longitud de campo de bit de planificación.

- 6. El método de la reivindicación 5, en el que, dicha interrogación de respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo comprende las siguientes maneras: cuando N ≥ Y, cada ciclo de interrogación tiene N intervalos de tiempo y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N<Y, cada ciclo de interrogación tiene Y intervalos de tiempo, y se accede a N segmentos de RAM en cada intervalo de tiempo.

- 7. Un dispositivo para procesar datos, que comprende:

- un módulo de control de escritura de lado de enlace descendente, configurado para: almacenar datos emitidos por respectivos canales en una memoria caché compartida de lado de enlace descendente; un módulo de control de lectura de lado de enlace descendente, configurado para: leer los datos de la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de planificación y emitir los datos a un bus de datos:

- 40 en donde.

15

20

25

30

- la memoria caché compartida de lado de enlace descendente consta de N piezas de memoria de acceso aleatorio (RAM) con un ancho de bits especificado, y cada pieza de RAM está dividida lógicamente en Y segmentos de RAM,

- el módulo de control de escritura de lado de enlace descendente está configurado para: interrogar respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo, y si una columna de segmentos de RAM que se está interrogando en la actualidad tiene espacio de almacenamiento, almacenar los datos a emitir en un correspondiente canal en la columna de segmentos de RAM;

- en donde los segmentos de RAM en la misma columna corresponden al mismo canal, y se llaman una columna de segmentos de RAM;

- el módulo de control de lectura de lado de enlace descendente está configurado para: calcular una cantidad general de datos almacenados en memoria caché en cada columna de segmentos de RAM, y cuando la cantidad de datos almacenados en memoria caché en la columna de segmentos de RAM es mayor que o igual a la cantidad de datos requeridos por una indicación de planificación actual, leer los datos emitidos en la planificación actual de respectivos segmentos de RAM basándose en una indicación de longitud de campo de bit de planificación.

- 8. El dispositivo de la reivindicación 7, en el que,

- el módulo de control de escritura de lado de enlace descendente está configurado para interrogar respectivos segmentos de RAM en respectivas piezas de RAM en la memoria caché compartida de lado de enlace descendente de acuerdo con un orden de intervalo de tiempo fijo de las siguientes maneras: cuando N ≥ Y, cada ciclo de interrogación tiene N intervalos de tiempo y se accede a Y segmentos de RAM en cada intervalo de tiempo; cuando N<Y, cada ciclo de interrogación tiene Y intervalos de tiempo y se accede a N segmentos de RAM en cada intervalo de tiempo.

65

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8