# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 750 348

51 Int. Cl.:

H02M 3/157 (2006.01) G06F 1/32 (2009.01) G05F 3/02 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: 27.01.2005 PCT/US2005/003484

(87) Fecha y número de publicación internacional: 01.09.2005 WO05079227

(96) Fecha de presentación y número de la solicitud europea: 27.01.2005 E 05712797 (9)

(97) Fecha y número de publicación de la concesión europea: 07.08.2019 EP 1745536

54 Título: Procedimiento y sistema para comunicar coeficientes de compensación de filtro para un sistema de control de potencia digital

(30) Prioridad:

12.02.2004 US 544553 P 12.07.2004 US 889806

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 25.03.2020 (73) Titular/es:

BEL POWER SOLUTIONS INC. (100.0%) 152 N. Third Street, Suite 805 San Jose, CA 95112, US

(72) Inventor/es:

**CHAPUIS, ALAIN**

(74) Agente/Representante:

**ISERN JARA, Jorge**

### **DESCRIPCIÓN**

Procedimiento y sistema para comunicar coeficientes de compensación de filtro para un sistema de control de potencia digital

#### DATOS DE SOLICITUD RELACIONADOS

Esta solicitud de patente reivindica prioridad de conformidad con 35 U.S.C. artículo 119(c) de la solicitud de patente provisional con número de serie 60/544.553, presentada el 12 de febrero de 2004. Esta solicitud de patente también reivindica prioridad como continuación parcial de conformidad con 35 U.S.C. artículo 120 a las solicitudes de patente con número de serie 10/361.667, presentada el 10 de febrero de 2003, y con número de serie 10/326.222, presentada el 21 de diciembre de 2002.

#### ANTECEDENTES DE LA INVENCIÓN

#### 1. Campo de la invención

5

10

15

20

25

30

35

40

45

50

55

60

65

La presente invención se refiere a circuitos de suministro de energía, y más particularmente a sistemas de control de potencia digital y procedimientos para programar parámetros de circuitos de suministro de energía en modo conmutado.

#### 2. Descripción de la técnica relacionada

Las fuentes de alimentación de modo conmutado son conocidas en la técnica para convertir un voltaje de nivel de corriente continua (CC) o corriente alterna (CA) disponible en otro voltaje de nivel de CC. Un convertidor reductor es un tipo particular de fuente de alimentación de modo conmutado que proporciona un voltaje de salida de CC regulado a una carga almacenando selectivamente energía en un inductor de salida acoplado a la carga al cambiar el flujo de corriente al inductor de salida. Incluye dos interruptores de alimentación que proporcionan generalmente los transistores MOSFET. Un condensador de filtro acoplado en paralelo con la carga reduce la ondulación de la corriente de salida. Se utiliza un circuito de control de modulación por ancho de pulsos (PWM) para controlar la activación de los interruptores de alimentación de manera alterna para controlar el flujo de corriente en el inductor de salida. El circuito de control de PWM utiliza señales comunicadas a través de un bucle de retroalimentación que refleja el voltaje de salida y / o el nivel de corriente para ajustar el ciclo de trabajo aplicado a los interruptores de potencia en respuesta a las condiciones de carga cambiantes.

Los circuitos de control de PWM convencionales se construyen utilizando componentes de circuitos analógicos, como amplificadores operacionales, comparadores y componentes pasivos como resistencias y condensadores para la compensación de bucle, y algunos componentes de circuitos digitales como puertas lógicas y multivibradores biestables. Pero, es deseable utilizar circuitos completamente digitales en lugar de los componentes del circuito analógico, ya que los circuitos digitales ocupan menos espacio físico, consumen menos energía y permiten la implementación de características de programabilidad o técnicas de control adaptativo.

Un circuito de control digital convencional incluye un convertidor analógico a digital (ADC) que convierte una señal de error que representa la diferencia entre una señal a controlar (por ejemplo, voltaje de salida (V<sub>0</sub>)) y una referencia en una señal digital que tiene n bits. El circuito de control digital utiliza la señal de error digital para controlar un modulador de ancho de pulso digital, que proporciona señales de control a los interruptores de potencia que tienen un ciclo de trabajo tal que el valor de salida de la fuente de alimentación rastrea la referencia. El circuito de control digital puede incluir además un filtro digital, tal como un filtro de respuesta al impulso infinita (IIR) que tiene una función de transferencia asociada. La función de transferencia incluye coeficientes de compensación que definen el funcionamiento del filtro de IIR. Es deseable tener la capacidad de alterar o programar estos coeficientes de compensación para definir el funcionamiento del filtro digital para condiciones de carga particulares.

Dado que los sistemas electrónicos con frecuencia necesitan energía suministrada a diferentes niveles de voltaje y corriente discretos, se sabe que distribuyen un voltaje de bus intermedio en todo el sistema electrónico e incluyen un regulador individual de punto de carga («POL»), por ejemplo, un convertidor de CC/CC de modo conmutado, en el punto de consumo de energía dentro del sistema electrónico. En particular, se incluiría un regulador de POL con cada circuito electrónico respectivo para convertir el voltaje del bus intermedio al nivel requerido por el circuito electrónico. Un sistema electrónico puede incluir múltiples reguladores de POL para convertir el voltaje del bus intermedio en cada uno de los múltiples niveles de voltaje. Idealmente, el regulador de POL debería estar ubicado físicamente adyacente al circuito electrónico correspondiente para minimizar la longitud de las líneas de baja tensión y alta corriente a través del sistema electrónico. El voltaje del bus intermedio se puede entregar a los múltiples reguladores de POL utilizando líneas de baja corriente que minimizan la pérdida.

Con este enfoque distribuido, es necesario coordinar el control y monitorización de los reguladores de POL del sistema de energía. Los reguladores de POL generalmente funcionan en conjunto con un controlador de fuente de alimentación que activa, programa y monitoriza los reguladores de POL individuales. Es conocido en la técnica que el controlador

utiliza un bus paralelo de conexión múltiple para activar y programar cada regulador de POL. Por ejemplo, el bus paralelo puede comunicar un bit de activación / desactivación para encender y apagar cada regulador de POL, y bits de código de identificación de voltaje (VID) para programar el punto de ajuste de voltaje de salida de los reguladores de POL. El controlador puede utilizar además conexiones adicionales para monitorizar el voltaje / corriente que se suministra por cada regulador de POL para detectar estados de error de los reguladores de POL. Un inconveniente de dicho sistema de control es que agrega complejidad y tamaño al sistema electrónico general.

El documento US 6 005 377 A describe un controlador programable para convertidores de potencia en modo conmutado que opera en un dominio digital. La porción digital del controlador es una matriz de puertas programable por campo que controla el funcionamiento del convertidor al convertir generalmente una señal de referencia analógica en el dominio digital. El controlador realiza una aritmética distribuida para generar una señal de onda cuadrada capaz de controlar un interruptor principal del convertidor.

En Peracaula y col.: «Microcomputer control of DC/DC converters for photovoltaic applications» Electrotechnical Conference, 1991. Proceedings., 22-24 mayo 1991, IEEE, páginas 214-217, se describen los resultados obtenidos con un sistema experimental que utiliza el control por microordenador de un convertidor Cuk alimentado desde paneles solares fotovoltaicos. Se utiliza un algoritmo proporcional-integral-derivativo (PID) para el controlador, donde los parámetros PID son ajustables desde el teclado del terminal de un usuario.

El documento US 6 163 143 describe un aparato de fuente de alimentación que tiene un circuito de fuente de alimentación, capaz de cambiar una operación según una notificación de una carga que tiene un primer modo de operación y un segundo modo de operación que indica un consumo de corriente menor que el primer modo de operación, para generar una salida de CC basada en una señal de pulso dada, que comprende: medios de respuesta de alta velocidad para generar una señal de pulso que deberá ser suministrada por el circuito de suministro de energía basado en un parámetro relacionado con la salida del circuito de suministro de energía; medios de respuesta de baja velocidad para generar una señal de pulso que deberá ser suministrada por el circuito de suministro de energía basado en un parámetro relacionado con la salida del circuito de suministro de energía a una velocidad de respuesta menor que dicho medio de respuesta de alta velocidad; y medios de control para detener dichos medios de respuesta de alta velocidad después de proporcionar la señal de pulso generada por dichos medios de respuesta de baja velocidad para el circuito de suministro de energía cuando se recibe una notificación sobre una transferencia desde el primer modo de operación al segundo modo de operación desde la carga.

El documento US 5 917 719 describe una fuente de alimentación internamente programable para su uso con un voltaje de entrada de CA suministrado a un terminal de entrada para producir un voltaje de salida de CC. Se proporciona al menos un módulo de conversión de energía, que tiene una entrada y una salida. La entrada del al menos un módulo de conversión de energía está adaptada para conectarse a la entrada de CA. El al menos un módulo de conversión de energía incluye medios rectificadores para convertir el voltaje de CA en un voltaje de CC y un filtro para proporcionar el voltaje de salida de CC. Un controlador digital está conectado a al menos un módulo de conversión de potencia e incluye una red de retroalimentación que tiene una pluralidad de componentes de retroalimentación para formar un bucle de retroalimentación. Se proporciona un microprocesador y un teclado accesible para el usuario se acopla al microprocesador. Un dispositivo lógico está acoplado al microprocesador y está provisto de una interfaz de programación lógica. Los interruptores acoplan el dispositivo lógico a la pluralidad de componentes de retroalimentación y se utilizan para seleccionar componentes de bucles de retroalimentación a solicitud del usuario para permitir la adaptación de la fase de la fuente de alimentación y la respuesta de frecuencia a una amplia variedad de cargas de usuario en la salida de CC.

Además, se hace referencia a la publicación de Patella y col.: «High-frequency digital controller IC for DC/DC converters», APEC 2002, 17th annual IEEE applied power electronics conference and exposition, IEEE, Estados Unidos, vol. 2 de 2. conf. 17, 10 de marzo de 2002, páginas 374-380.

Por lo tanto, sería ventajoso proporcionar un sistema y un procedimiento para controlar digitalmente una fuente de alimentación de modo conmutado que supere estos y otros inconvenientes de la técnica anterior. Sería además ventajoso proporcionar un sistema y un procedimiento para controlar y monitorizar el funcionamiento de una fuente de alimentación de modo conmutado controlada digitalmente dentro de un sistema de alimentación distribuido. Más particularmente, sería ventajoso proporcionar un sistema y un procedimiento para programar los coeficientes de compensación del filtro digital de una fuente de alimentación conmutada controlada digitalmente dentro de un sistema de alimentación distribuido.

#### RESUMEN DE LA INVENCIÓN

5

10

15

35

40

45

50

55

60

65

La invención se define mediante las reivindicaciones independientes. Las reivindicaciones dependientes están dirigidas a realizaciones preferidas de la invención.

Se proporcionará a los expertos en la materia una comprensión más completa del sistema y el procedimiento para comunicar los coeficientes del filtro a una pluralidad de reguladores de punto de carga en un sistema de potencia, así como la realización de ventajas adicionales y objetos de los mismos, mediante una consideración de la siguiente

descripción detallada de la realización preferida. Se hará referencia a las hojas de dibujos adjuntas, que primero se describirán brevemente.

#### BREVE DESCRIPCIÓN DE LOS DIBUJOS

5

10

25

30

35

40

45

50

55

60

65

La figura 1 representa una fuente de alimentación de modo conmutado que tiene un circuito de control digital;

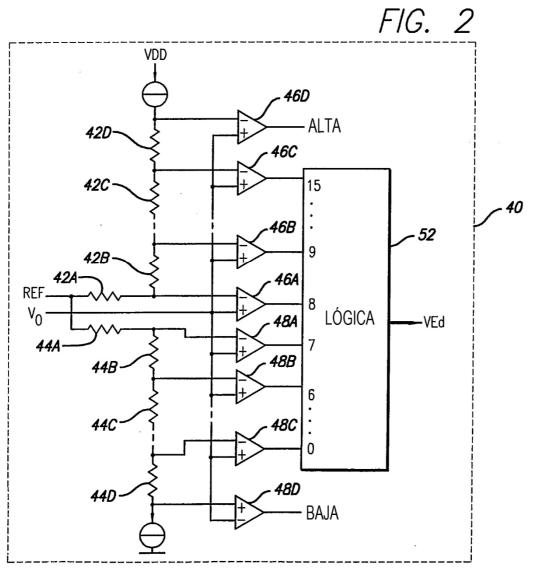

La figura 2 representa un ADC flash en ventana que proporciona señales de alta y baja saturación;

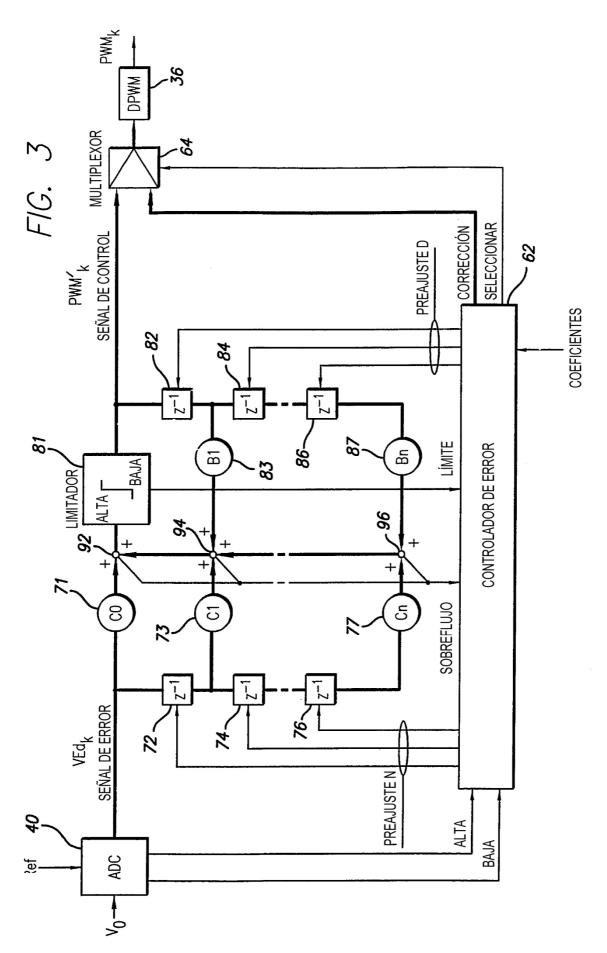

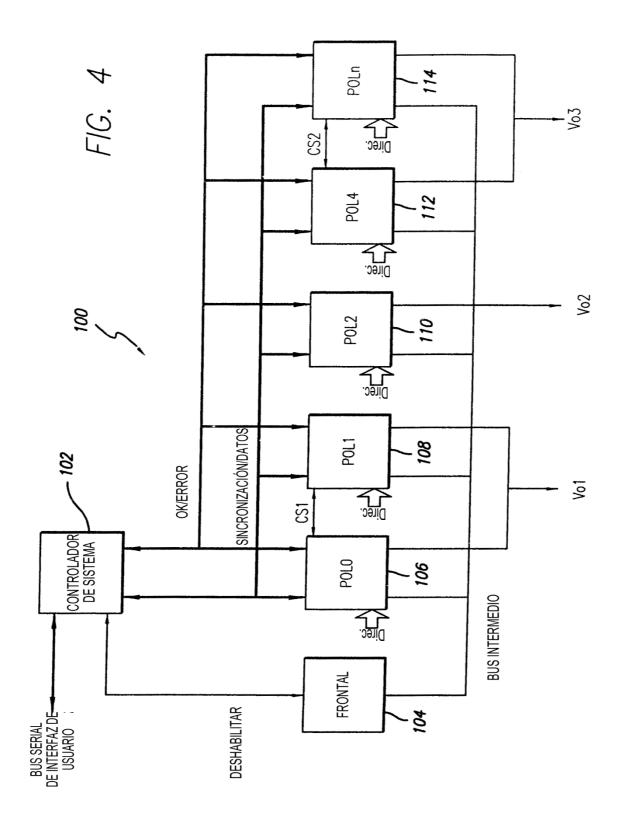

La figura 3 representa un controlador digital que tiene un filtro de respuesta al impulso infinita y un controlador de error; La figura 4 representa un sistema de control ejemplar para comunicar coeficientes de compensación de filtro de acuerdo con una realización de la presente invención;

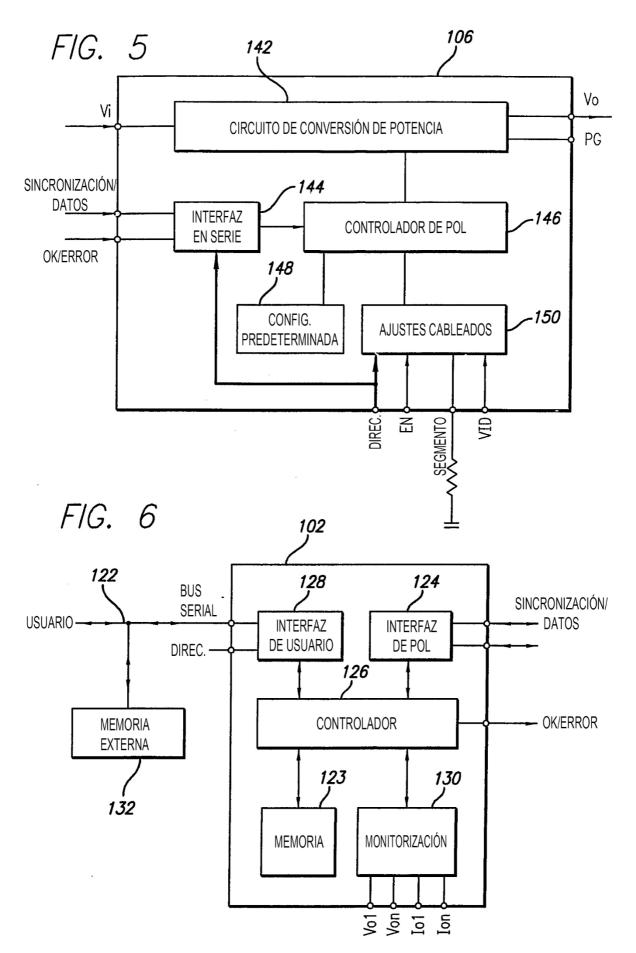

La figura 5 representa un regulador de POL ejemplar del sistema de control de POL;

La figura 6 representa un controlador de sistema ejemplar del sistema de control de POL;

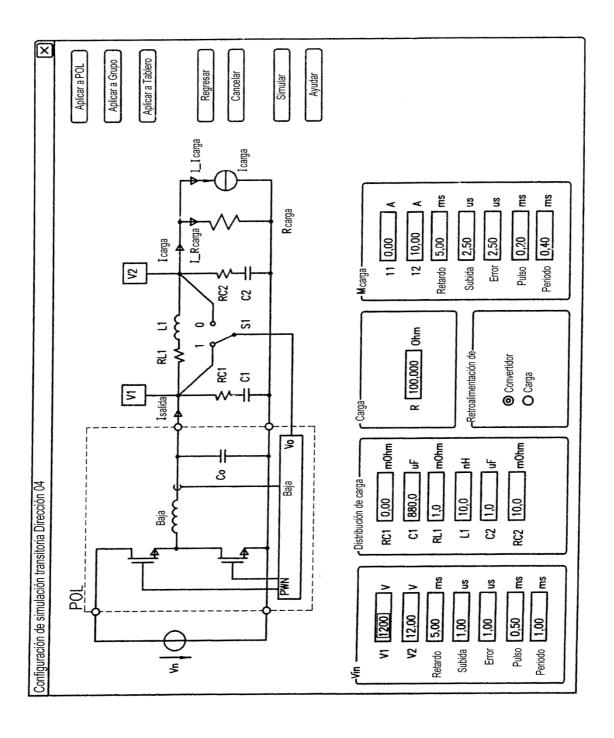

La figura 7 es una captura de pantalla ejemplar que representa una interfaz gráfica de usuario (GUI) para simular el funcionamiento de un regulador de POL; y

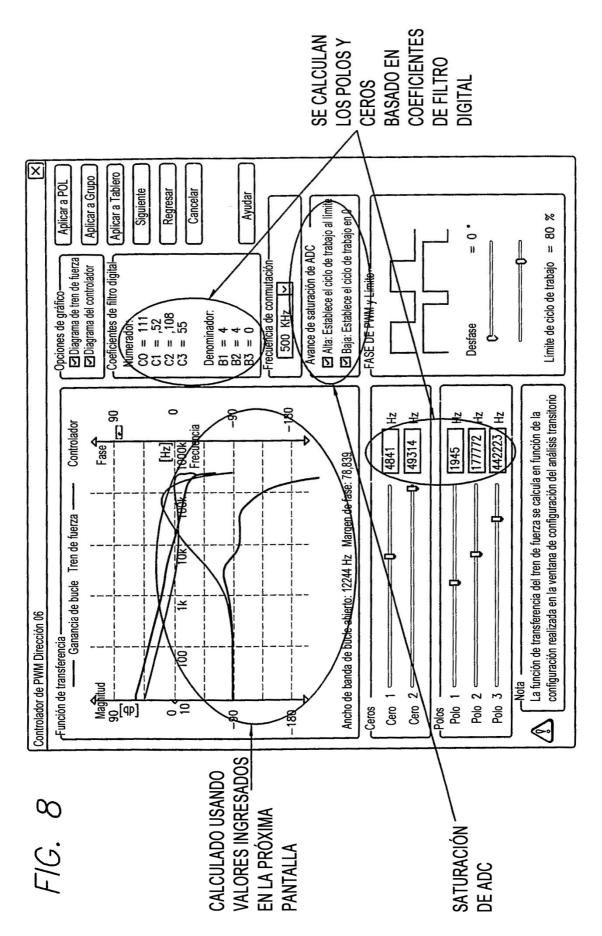

La figura 8 es una captura de pantalla ejemplar que representa una GUI para programar los coeficientes de compensación del controlador digital.

#### DESCRIPCIÓN DETALLADA DE LA REALIZACIÓN PREFERIDA

La presente invención proporciona un procedimiento para controlar digitalmente una fuente de alimentación de modo conmutado. Más particularmente, la invención proporciona un sistema y un procedimiento para programar los coeficientes de compensación del filtro digital de una fuente de alimentación conmutada controlada digitalmente dentro de un sistema de alimentación distribuido. En la descripción detallada a continuación, los números de elementos similares se usan para describir elementos similares ilustrados en una o más figuras.

La figura 1 representa una fuente de alimentación de modo conmutado ejemplar 10 que tiene un circuito de control digital de acuerdo con una realización de la presente invención. La fuente de alimentación 10 comprende una topología de convertidor reductor para convertir un voltaje de CC de entrada V<sub>in</sub> en un voltaje de CC de salida V<sub>o</sub> aplicado a una carga resistiva 20 (R<sub>car9a</sub>). La fuente de alimentación 10 incluye un par de interruptores de alimentación 12, 14 proporcionados por dispositivos MOSFET. El terminal de fuente del interruptor de alimentación del lado alto 12 está acoplado al voltaje de entrada V<sub>in</sub>, el terminal de fuente del interruptor de alimentación del lado bajo 14 está conectado a tierra, y los terminales drenadores de los interruptores de alimentación 12, 14 están acoplados entre sí para definir un nodo de fase Un inductor de salida 16 está acoplado en serie entre el nodo de fase y el terminal que proporciona el voltaje de salida V<sub>o</sub>, y un condensador 18 está acoplado en paralelo con la carga resistiva R<sub>car9a</sub>. Los respectivos controladores 22, 24 accionan alternativamente los terminales de puerta de los interruptores de alimentación 12, 14. A su vez, los controladores 22, 24 son controlados por un circuito de control digital 30 (descrito a continuación). La apertura y cierre de los interruptores de alimentación 12, 14 proporciona un voltaje intermedio que tiene una forma de onda generalmente rectangular en el nodo de fase, y el filtro formado por el inductor de salida 16 y el condensador 18 convierte la forma de onda rectangular en un voltaje de salida sustancialmente de CC V<sub>o</sub>.

El circuito de control digital 30 recibe una señal de retroalimentación desde la porción de salida de la fuente de alimentación 10. Como se muestra en la figura 1, la señal de retroalimentación corresponde al voltaje de salida  $V_o$ , aunque debe apreciarse que la señal de retroalimentación podría corresponder alternativamente (o adicionalmente) a la corriente de salida extraída por la carga resistiva  $R_{car9a}$  o cualquier otra señal que represente un parámetro para ser controlado por el circuito de control digital 30. La ruta de retroalimentación puede incluir además un divisor de voltaje (no mostrado) para reducir el voltaje de salida detectado  $V_o$  a un nivel de voltaje representativo. El circuito de control digital 30 proporciona una forma de onda modulada por ancho de pulso que tiene un ciclo de trabajo controlado para regular el voltaje de salida  $V_o$  (o corriente de salida) al nivel deseado. Aunque se ilustra que la fuente de alimentación ejemplar 10 tiene una topología de convertidor reductor, debe entenderse que el uso del control de bucle de retroalimentación de la fuente de alimentación 10 utilizando el circuito de control digital 30 es igualmente aplicable a otras topologías de fuente de alimentación conocidas, tales como convertidores de máximo y máximo-mínimo en configuraciones aisladas y no aisladas, y para diferentes estrategias de control conocidas como controladores de modo de voltaje, modo de corriente, modo de carga y / o modo de corriente promedio.

Más particularmente, el circuito de control digital 30 incluye un convertidor analógico a digital (ADC) 32, un controlador digital 34 y un modulador por ancho de pulso digital (DPWM) 36. El ADC 32 comprende además un ADC flash en ventana que recibe como entradas la señal de retroalimentación (es decir, el voltaje de salida V<sub>o</sub>) y una referencia de voltaje (Ref) y produce una señal de error de voltaje digital (VEd<sub>k</sub>) que representa la diferencia entre las entradas (Ref - V<sub>o</sub>) El controlador digital 34 tiene una función de transferencia G(z) que transforma la señal de error de voltaje VEd<sub>k</sub> en una salida digital proporcionada al DPWM 36, que convierte la señal en una forma de onda que tiene un ancho de pulso proporcional (PWM<sub>k</sub>). El controlador digital 34 recibe como entradas los coeficientes de compensación de filtro utilizados en la función de transferencia G(z), como se describirá con más detalle a continuación. Como se describió anteriormente, la forma de onda modulada por pulsos PWM<sub>k</sub> producida por el DPWM 36 está acoplada a los terminales de puerta de los interruptores de alimentación 12, 14 a través de los respectivos controladores 22, 24.

La figura 2 representa un ADC flash en ventana ejemplar 40 para su uso en el circuito de control digital 30. El ADC 40

recibe como entradas la referencia de voltaje Ref y el voltaje de salida Vo. La referencia de tensión se aplica al centro de una escalera de resistencia que incluye las resistencias 42A, 42B, 42C, 42D conectadas en serie entre el terminal de voltaje de referencia y una fuente de corriente conectada a un voltaje de alimentación positiva (Vdd), y las resistencias 44A, 44B, 44C, 44D conectadas en serie entre el terminal de voltaje de referencia y una fuente de corriente conectada a tierra. Las resistencias tienen cada una valores de resistencia correspondientes para definir, junto con las fuentes de corriente, una pluralidad de incrementos de voltaje que oscilan por encima y por debajo de la referencia de voltaje Ref. La magnitud de los valores de resistencia y / o las fuentes de corriente se pueden seleccionar para definir la resolución LSB del ADC 40. Un conjunto de comparadores está conectado a la escalera de resistencia, que incluye una pluralidad de comparadores de lado positivo 46A, 46B, 46C, 46D y una pluralidad de comparadores de lado negativo 48A, 48B, 48C, 48D. Los comparadores de lado positivo 46A, 46B, 46C, 46D tienen cada uno un terminal de entrada no inversora conectado al voltaje de salida Vo, y un terminal de entrada inversora conectado a las respectivas resistencias 42A, 42B, 42C, 42D. Del mismo modo, los comparadores de lado negativo 48A, 48B, 48C, tienen cada uno un terminal de entrada no inversora conectado al voltaje de salida Vo, y un terminal de entrada inversora conectado a las respectivas resistencias 44A, 44B, 44C, 44D. El comparador de lado negativo 48D tiene un terminal de entrada no inversora conectado a tierra y el terminal de entrada inversora conectado al voltaje de salida V<sub>o</sub>. Debe apreciarse que se puede incluir un mayor número de resistencias y comparadores para aumentar el número de incrementos de voltaje y, por lo tanto, el rango del ADC 40, y que un número limitado de resistencias y comparadores se muestra en la figura 2 solo para fines ejemplares.

10

15

35

55

60

El ADC 40 incluye además un dispositivo lógico 52 acoplado a terminales de salida de los comparadores 46A, 46B, 46C y 48A, 48B, 48C. El dispositivo lógico 52 recibe las salidas del comparador y proporciona una salida paralela de varios bits (por ejemplo, 4 bits) que representa el error de voltaje VEdk. A modo de ejemplo, un voltaje de salida Vo que excede el voltaje de referencia Ref en un incremento de voltaje (por ejemplo, 5 mV) provocaría que las salidas de los comparadores 46B, 46A, 48A, 48B y 48C se elevaran, mientras que las salidas de los comparadores 46C, 46D y 48D permanecen bajas. El dispositivo lógico 52 interpretaría esto como un nivel lógico 9 (o binario 1001) y produciría una señal de error de voltaje asociada VEdk. Debe entenderse que la referencia de voltaje Ref es variable para cambiar la ventana del ADC 40. Si el voltaje de salida Vo excede el incremento de voltaje más alto de la escalera de resistencia, el terminal de salida del comparador 46D proporciona una señal de ALTA saturación. De manera similar, si el voltaje de salida Vo es menor que el incremento de voltaje más bajo de la escalera de resistencia, el terminal de salida del comparador 48D proporciona una señal de BAJA saturación.

En la figura 3, se representa un controlador digital que tiene un filtro digital y un ADC 40. El filtro digital comprende además un filtro de respuesta por impulso infinita (IIR) que produce una salida PWM'<sub>k</sub> a partir de entradas de error de voltaje anteriores VEd<sub>k</sub> y salidas anteriores PWM'<sub>k</sub>. Como se describió anteriormente, el ADC 40 proporciona las entradas de error de voltaje VEd<sub>k</sub>. Las salidas de filtro digital PWM'<sub>k</sub> se proporcionan al modulador de ancho de pulso digital (DPWM) 36, que proporciona la señal de control modulada por ancho de pulso (PWM<sub>k</sub>) a los interruptores de alimentación de la fuente de alimentación.

El filtro de IIR se ilustra en forma de diagrama de bloques e incluye una primera pluralidad de registros de retardo 72, 74 76 (cada uno etiquetado como z¹), una primera pluralidad de operadores matemáticos (multiplicadores) con coeficientes 71, 73 77 (etiquetado como C0, C1 Cn), una segunda pluralidad de operadores matemáticos (sumadores) 92, 94, 96, una segunda pluralidad de registros de retardo 82, 84 86 (cada uno etiquetado como z¹) y una tercera pluralidad de operadores matemáticos (multiplicadores) con coeficientes 83, 87 (etiquetado como B1 Bn). Cada uno de los primeros registros de retardo 72, 74, 76 contiene una muestra anterior del error de voltaje VEdk, que luego es ponderado por uno de los coeficientes respectivos 71,73, 77. Asimismo, cada uno de los segundos registros de retardo 82, 84, 86 contiene una muestra anterior de la salida PWM¹k, que luego es ponderada por uno de los coeficientes respectivos 83, 87. Los sumadores 92, 94 y 96 combinan las muestras ponderadas de entrada y salida. Debería apreciarse que se puede incluir un mayor número de registros y coeficientes de retardo en el filtro de IIR, y que se muestra un número limitado en la figura 3 solo con fines ejemplares. La estructura de filtro digital que se muestra en la figura 3 es una implementación ejemplar de la siguiente función de transferencia G(z):

$$G(z) = \frac{PWM(z)}{VEd(z)} = \frac{C_0 + C_1 \cdot z^{-1} + C_2 \cdot z^{-2} + \dots + C_n \cdot z^{-n}}{1 - B_1 \cdot z^{-1} - B_2 \cdot z^{-2} - \dots - B_n \cdot z^{-n}}$$

El controlador de error 62 recibe una pluralidad de señales de entrada que reflejan las condiciones de error del ADC 40 y el filtro digital. Específicamente, el controlador de error 62 recibe las señales de ALTA y BAJA saturación del ADC 40, lo que refleja que el voltaje de salida V<sub>o</sub> está por encima y por debajo de la ventana de voltaje del ADC, respectivamente. Cada uno de los operadores matemáticos (sumadores) 92, 94, 96 proporciona una señal de sobreflujo al controlador de error 62 que refleja una condición de sobreflujo (es decir, bit de transporte) de los operadores matemáticos. El filtro digital incluye además un limitador de rango 81 que recorta la salida PWM'<sub>k</sub> si se alcanzan los límites de rango superior o inferior. En esa situación, el limitador de rango 81 proporciona al controlador de error 62 una señal de límite correspondiente.

El controlador de error 62 usa estas señales de entrada para alterar el funcionamiento del filtro digital con el fin de

# ES 2 750 348 T3

mejorar la capacidad de respuesta del filtro digital a las condiciones de carga cambiantes. El controlador de error 62 está acoplado a cada una de la primera pluralidad de registros de retardo 72, 74, 76 y la segunda pluralidad de registros de retardo 82, 84, 86 para permitir el restablecimiento y / o el preestablecimiento del valor almacenado en el mismo. Como se usa en el presente documento, «restablecer» se refiere a la configuración del valor a un valor inicial (por ejemplo, cero), mientras que «preestablecer» se refiere a la configuración del valor a otro número predeterminado. En particular, el controlador de error 62 puede reemplazar las muestras anteriores del error de voltaje VEdk y la salida PWM'k con valores predeterminados que cambian el comportamiento de la fuente de alimentación. El controlador de error 62 recibe como entradas externas valores de datos para ser utilizados como coeficientes 71, 73, ..., 77 y 83, ..., 87. Debe apreciarse que las características del filtro digital pueden programarse mediante la selección de valores de datos apropiados para los coeficientes 71, 73, ..., 77 y 83, ..., 87.

10

15

20

25

40

45

50

55

60

El controlador digital incluye además el multiplexor 64 que permite la selección entre la señal de salida PWM'<sub>k</sub> y una señal de salida predeterminada proporcionada por el controlador de error 62. Una señal de selección proporcionada por el controlador de error 62 determina qué señal pasa a través del multiplexor 64. Cuando el ADC 40 entra en ALTA o BAJA saturación, el controlador de error 62 establece la señal PWM'<sub>k</sub> en un valor predeterminado específico (o secuencia de valores que dependen en parte de las muestras anteriores) controlando el multiplexor 64. Para recuperarse sin problemas de dicha condición, el controlador de error también puede alterar las muestras de entrada y salida retrasadas recargando la primera pluralidad de registros de retardo 72, 74, 76 y la segunda pluralidad de registros de retardo 82, 84, 86. Esto asegurará un comportamiento controlado del bucle de retroalimentación a medida que el ADC 40 se recupera de la saturación.

A modo de ejemplo, si el ADC 40 experimenta una saturación positiva, es decir, la señal BAJA cambia de un estado bajo a un estado alto, la muestra PWM'<sub>k</sub> se puede restablecer a cero para ayudar a reducir el error. Al restablecer la muestra PWM'<sub>k</sub> a cero, el ancho de pulso suministrado al interruptor de alimentación de lado alto 12 de la fuente de alimentación 10 se pone a cero, cortando efectivamente la alimentación a la carga resistiva 20 (véase la figura 1). Para recuperarse de esta situación sin problemas, las muestras PWM'<sub>k-1</sub>, PWM'<sub>k-2</sub> PWM'<sub>k-n</sub> también pueden restablecerse a cero o preestablecerse a otro valor para permitir una recuperación sin problemas.

Del mismo modo, si el ADC 40 experimenta una saturación negativa, es decir, la señal ALTA cambia de un estado bajo a un estado alto, la muestra PWM'<sub>k</sub> puede preestablecerse a un valor máximo para aumentar el ancho de pulso suministrado al interruptor de alimentación de lado alto 12 para reducir el error. Además, cuando se produce un sobreflujo numérico interno del filtro digital, el controlador de error 62 puede tomar medidas para evitar el comando incontrolado de los interruptores de alimentación de la fuente de alimentación, como alterar las muestras de entrada y salida de los filtros digitales.

En una realización de la invención, la fuente de alimentación de modo conmutado de la figura 1 comprende además un regulador de punto de carga («POL») ubicado en el punto de consumo de energía dentro del sistema electrónico. Un sistema de control de potencia incluye una pluralidad de reguladores de POL similares, al menos un bus de datos que conecta operativamente la pluralidad de reguladores de POL, y un controlador de sistema conectado al bus de datos y adaptado para enviar y recibir datos digitales hacia y desde la pluralidad de reguladores de POL. El controlador del sistema comunicaría datos a través del bus serial para programar la función de transferencia de filtro digital G(z) con los valores de los coeficientes 71, 73, ..., 77 y 83, ..., 87.

Con referencia ahora a la figura 4, se muestra un sistema de control de POL 100 de acuerdo con una realización de la presente invención. Específicamente, el sistema de control de POL 100 incluye un controlador de sistema 102, un regulador frontal 104 y una pluralidad de reguladores de POL 106, 108, 110, 112 y 114 dispuestos en una matriz. Los reguladores de POL que se muestran en el presente documento incluyen, entre otros, reguladores de punto de carga, reguladores de potencia en carga, convertidores de CC / CC, reguladores de voltaje y todos los demás dispositivos programables de regulación de voltaje o corriente generalmente conocidos por los expertos en la materia. Se proporciona una interfaz intradispositivo entre los reguladores de POL individuales para controlar las interacciones específicas, como el uso compartido actual o en paralelo, por ejemplo, la interfaz de uso compartido actual (CS1) proporcionada entre POLO 106 y POL1 108, y CS2 proporcionada entre POL4 112 y POLn 114. En la configuración ejemplar mostrada en la figura 4, POLO 106 y POL1 108 funcionan en modo paralelo para producir voltaje de salida Vo1 con mayor capacidad de corriente, POL2 110 produce voltaje de salida Vo2, y POL4 112 y POLn 114 operan en modo paralelo para producir voltaje de salida Vo3, aunque debe apreciarse que otras combinaciones y otros números de reguladores de POL podrían ser ventajosamente utilizados.

El regulador frontal 104 proporciona un voltaje intermedio a la pluralidad de reguladores POL sobre un bus de voltaje intermedio, y puede comprender simplemente otro regulador de POL. El controlador de sistema 102 y el regulador frontal 104 pueden integrarse juntos en una sola unidad o pueden proporcionarse como dispositivos separados. Alternativamente, el regulador frontal 104 puede proporcionar una pluralidad de voltajes intermedios a los reguladores de POL sobre una pluralidad de buses de voltaje intermedio. El controlador de sistema 102 puede extraer su energía del bus de voltaje intermedio.

65 El controlador de sistema 102 se comunica con la pluralidad de reguladores de POL escribiendo y / o leyendo datos digitales (sincrónicos o asincrónicos) a través de un bus serial unidireccional o bidireccional, ilustrado en la figura 4

como el bus de sincronización / datos. El bus de sincronización / datos puede comprender un bus serial de dos cables (por ejemplo, I²C) que permite que los datos se transmitan de forma asincrónica o un bus serial de un solo cable que permite que los datos se transmitan de forma sincrónica (es decir, sincronizados con una señal de reloj). Para abordar cualquier POL específico en la matriz, cada POL se identifica con una dirección única, que puede conectarse al POL o establecerse mediante otros procedimientos. Por ejemplo, el controlador de sistema 102 comunica datos a través del bus de sincronización / datos para programar los coeficientes G(z) de la función de transferencia de filtro digital de cada regulador de POL. El controlador de sistema 102 también se comunica con la pluralidad de reguladores de POL para la gestión de errores a través de un segundo bus serial unidireccional o bidireccional, ilustrado en la figura 4 como el bus OK / error. Al agrupar varios reguladores de POL juntos al conectarlos a un bus común de OK / error, se puede lograr que los reguladores de POL tengan el mismo comportamiento en el caso de un estado de error. Además, el controlador de sistema 102 se comunica con un sistema de usuario a través de un bus de interfaz de usuario para programar, configurar y supervisar el sistema de control de POL 10. Por último, el controlador de sistema 102 se comunica con el regulador frontal 104 a través de una línea separada para deshabilitar el funcionamiento del regulador frontal

15

20

25

30

35

40

60

65

10

Un regulador de POL ejemplar 106 del sistema de control de POL 10 se ilustra con mayor detalle en la figura 5. Los otros reguladores de POL de la figura 4 tienen una configuración sustancialmente idéntica. El regulador de POL 106 incluye un circuito de conversión de potencia 142 (por ejemplo, la fuente de alimentación de modo conmutado 10 de la figura 1), una interfaz serial 144, un controlador de POL 146, una memoria de configuración predeterminada 148 y una interfaz de configuración cableada 150. El circuito de conversión de potencia 142 transforma un voltaje de entrada (VI) en el voltaje de salida deseado (V₀) según las configuraciones recibidas a través de la interfaz serial 144, las configuraciones cableadas 150 o las configuraciones predeterminadas. El circuito de conversión de potencia 142 también puede incluir sensores de monitorización para voltaje de salida, corriente, temperatura y otros parámetros que se usan para control local y que también se comunican al controlador del sistema a través de la interfaz serial 144. El circuito de conversión de potencia 142 también puede generar una señal de salida de Buena Potencia (BP) para aplicaciones autónomas con el fin de proporcionar una función de supervisión simplificada. La interfaz serial 144 recibe y envía comandos y mensajes al controlador de sistema 102 a través de los buses seriales de sincronización / datos y OK / error. La memoria de configuración predeterminada 148 almacena la configuración predeterminada para el regulador de POL 106 en los casos en que no se reciben señales de programación a través de la interfaz serial 144 o la interfaz de configuración cableada 150. La configuración predeterminada se selecciona de modo que el regulador de POL 106 funcione en una condición «segura» en ausencia de señales de programación.

La interfaz de configuración cableada 150 se comunica con conexiones externas para programar el regulador de POL sin usar la interfaz serial 144. La interfaz de configuración cableada 150 puede incluir como entradas la configuración de dirección (Addr) del POL para alterar o establecer algunas de las configuraciones en función de la dirección (es decir, el identificador del POL), por ejemplo, desplazamiento de fase, bit de habilitación / deshabilitación (En), ajuste, bits de código VID y seleccionar diferentes conjuntos (predefinidos) de coeficientes de filtro digital optimizados para diferentes configuraciones de filtro de salida. Además, la dirección identifica el regulador de POL durante las operaciones de comunicación a través de la interfaz serial 144. La entrada de ajuste permite la conexión de una o más resistencias externas para definir un nivel de voltaje de salida para el regulador de POL. Del mismo modo, los bits de código VID se pueden usar para programar el regulador de POL para un nivel de voltaje de salida / corriente deseado. El bit de habilitación / deshabilitación permite que el regulador de POL se encienda / apague al alternar una señal digital alta / baja.

El controlador de POL 146 recibe y prioriza la configuración del regulador de POL. Si no se recibe información de configuración a través de la interfaz de configuración cableada 150 o la interfaz serial 144, el controlador de POL 146 accede a los parámetros almacenados en la memoria de configuración predeterminada 148. Alternativamente, si la información de configuración se recibe a través de la interfaz de configuración cableada 150, entonces el controlador de POL 146 aplicará esos parámetros. Por lo tanto, la configuración predeterminada se aplica a todos los parámetros que no pueden establecerse o no están establecidos mediante un cableado rígido. La configuración recibida por la interfaz de configuración cableada 150 se puede sobrescribir mediante la información recibida a través de la interfaz serial 144. Por lo tanto, el regulador de POL puede funcionar en un modo independiente, un modo totalmente programable o una combinación de los mismos. Esta flexibilidad de programación permite satisfacer una pluralidad de diferentes aplicaciones de potencia con un solo regulador de POL genérico, lo que reduce el coste y simplifica la fabricación de reguladores de POL.

A modo de ejemplo, el controlador de sistema 102 comunica valores de datos a un regulador de POL particular 106 a través del bus de sincronización / datos para programar los coeficientes de filtro digital. Los valores de datos son recibidos por la interfaz serial 144 y comunicados al controlador de POL 146. El controlador de POL luego comunica los valores de datos al circuito de conversión de potencia 142 junto con instrucciones adecuadas para programar los coeficientes de filtro digital.

Un controlador de sistema ejemplar 102 del sistema de control de POL 100 se ilustra en la figura 6. El controlador de sistema 102 incluye una interfaz de usuario 122, una interfaz de POL 124, un controlador 126 y una memoria 128. La interfaz de usuario 122 envía y recibe mensajes hacia / desde el usuario a través del bus de interfaz de usuario. El bus de interfaz de usuario puede ser proporcionado por una interfaz bidireccional en serie o paralela utilizando

# ES 2 750 348 T3

protocolos de interfaz estándar, por ejemplo, una interfaz l²C. La información del usuario, como los valores de monitorización o las nuevas configuraciones del sistema, se transmitirán a través de la interfaz de usuario 122. La interfaz de POL 124 transforma datos hacia / desde los reguladores de POL a través de los buses seriales de sincronización / datos y OK / error. La interfaz de POL 124 se comunica a través del bus serial de sincronización / datos para transmitir datos de configuración y recibir datos de monitorización, y se comunica a través del bus serial OK / error para recibir señales de interrupción que indican un estado de error en al menos uno de los reguladores de POL conectados. La memoria 128 comprende un dispositivo de almacenamiento de memoria no volátil utilizado para almacenar los parámetros de configuración del sistema (por ejemplo, el voltaje de salida, el punto de ajuste de limitación de corriente, los datos de temporización, etc.) para los reguladores de POL conectados al controlador de sistema 102. Opcionalmente, una memoria externa secundaria 132 también puede conectarse a la interfaz de usuario 122 para proporcionar una mayor capacidad de memoria para monitorizar datos o configurar datos.

10

15

20

25

30

60

El controlador 126 está conectado operativamente a la interfaz de usuario 122, a la interfaz de POL 124 y a la memoria 128. El controlador 126 tiene un puerto externo para comunicar una señal de desactivación (FE DIS) al regulador frontal 104. Al arrancar el sistema de control de POL 100, el controlador 126 lee de la memoria interna 128 (y / o la memoria externa 132) la configuración del sistema y programa los reguladores de POL en consecuencia a través de la interfaz de POL 124. Cada uno de los reguladores de POL se configura y se inicia de manera prescrita según la programación del sistema. Durante el funcionamiento normal, el controlador 126 decodifica y ejecuta cualquier comando o mensaje proveniente del usuario o de los reguladores de POL. El controlador 126 supervisa el rendimiento de los reguladores de POL e informa esta información al usuario a través de la interfaz de usuario 122. Los reguladores de POL también pueden ser programados por el usuario a través del controlador 126 para ejecutar reacciones autónomas específicas a errores, tales como estados de sobrecorriente o sobretensión. Alternativamente, los reguladores de POL pueden programarse para informar solo los estados de error al controlador de sistema 102, que luego determinará la acción correctiva apropiada de acuerdo con las configuraciones predefinidas, por ejemplo, apagar el regulador frontal a través de la línea de control FE DIS.

Opcionalmente, se puede proporcionar un bloque de monitorización 130 para monitorizar el estado de uno o más niveles de voltaje o corriente de otros sistemas de potencia no conectados operativamente al controlador 102 a través de los buses de sincronización / datos u OK / error. El bloque de monitorización 130 puede proporcionar esta información al controlador 126 para informar al usuario a través de la interfaz de usuario de la misma manera que se comunica cualquier información relativa al sistema de control de POL 10. De esta manera, el sistema de control de POL 10 puede proporcionar cierta compatibilidad retroactiva con sistemas de alimentación que ya están presentes en un sistema electrónico.

- Como se describió anteriormente, el controlador de sistema 102 tiene una interfaz para comunicarse con un sistema de usuario para programar y monitorizar el rendimiento del sistema de control de POL. El sistema de usuario incluiría un ordenador acoplado a la interfaz, ya sea directamente o a través de una red, que tenga un software adecuado adaptado para comunicarse con el controlador de sistema 102. Como se conoce en la técnica, el ordenador estaría equipado con una interfaz de usuario basada en gráficos (GUI) que incorpora ventanas móviles, iconos y un ratón, como los basados en la interfaz de Microsoft Windows™. La GUI puede incluir formatos preprogramados estándar para representar texto y gráficos, como se entiende generalmente en la técnica. La GUI muestra la información recibida del controlador de sistema 102 en la pantalla del ordenador y el usuario puede programar y monitorizar el funcionamiento del sistema de control de POL haciendo cambios en las pantallas particulares de la GUI.

- La figura 7 ilustra una captura de pantalla ejemplar de una GUI utilizada para simular el funcionamiento de un regulador de POL. La captura de pantalla ilustra un regulador de POL que tiene una topología correspondiente a la fuente de alimentación de modo conmutado ejemplar 10 descrita anteriormente con respecto a la figura 1. El regulador de POL incluye un par de interruptores de alimentación provistos por dispositivos MOSFET, un inductor de salida L<sub>0</sub> y un condensador C<sub>0</sub> 18. Los terminales de salida del regulador de POL están acoplados a una resistencia de carga R<sub>I</sub> a través de un filtro pi definido por una inductancia en serie L<sub>1</sub> y una resistencia interna RL<sub>1</sub>, una capacitancia C<sub>1</sub> y una resistencia interna RC<sub>1</sub> en un primer extremo del filtro pi, y una capacitancia C<sub>2</sub> y una resistencia interna RC<sub>2</sub> en un segundo extremo del filtro pi. El regulador de POL incluye además un circuito de control que proporciona una señal de activación de PWM a los interruptores de alimentación y recibe como señales de retroalimentación la corriente de salida IL<sub>0</sub> y el voltaje de salida V<sub>0</sub>. El voltaje de salida se puede detectar desde cualquier extremo de la línea de transmisión mediante la configuración de un interruptor.

- La GUI permite al usuario definir valores de varios parámetros del regulador de POL para simular su funcionamiento. Cada parámetro definible por el usuario incluye un campo que permite al usuario ingresar los valores de datos deseados. El usuario puede seleccionar parámetros de los voltajes de salida, como definir el voltaje en el primer extremo del filtro pi V<sub>1</sub>, el voltaje en el segundo extremo del filtro pi V<sub>2</sub>, el retardo de voltaje, los tiempos de subida y bajada, y el ancho y periodo del ancho de pulso de activación del interruptor de alimentación. El usuario también puede seleccionar parámetros de distribución de carga, incluida la definición de las resistencias, capacitancias e inductancia del filtro pi. El usuario también puede definir la resistencia de carga y las características de la corriente de carga.

- Una vez que el usuario ha seleccionado los parámetros deseados para el regulador de POL, la GUI puede ejecutar una simulación basada en los parámetros seleccionados. La figura 8 ilustra una captura de pantalla ejemplar de una

# ES 2 750 348 T3

GUI en la que la función de transferencia G(z) para el regulador de POL se muestra gráficamente. La función de transferencia se ilustra gráficamente en términos de variaciones de magnitud de ganancia y fase con respecto a la frecuencia. Como parte de la simulación, los coeficientes de filtro se calculan para el filtro digital del PWM digital y se muestran en la pantalla. El usuario puede alterar la forma de los gráficos de ganancia utilizando potenciómetros deslizantes que ajustan los polos y ceros de la función de transferencia, y puede repetir la simulación del regulador de POL hasta que esté satisfecho con los resultados de rendimiento. El usuario puede optar por aplicar los coeficientes de filtro digital seleccionados a un regulador de POL individual o a un grupo de reguladores de POL o a todos los grupos de reguladores de POL en una placa de circuito impreso particular mediante la selección de un botón apropiado. Esta acción provocaría que los coeficientes de filtro seleccionados se almacenen en la memoria no volátil contenida dentro del controlador de sistema 102 y, a su vez, se comuniquen a cada regulador de POL apropiado a través del bus de sincronización / datos como se describió anteriormente.

5

10

15

Por lo tanto, con la descripción de una realización preferida de un sistema y un procedimiento para programar los coeficientes de compensación de filtro digital de una fuente de alimentación de modo conmutado controlada digitalmente dentro de un sistema de potencia distribuido, los expertos en la materia deben tener en cuenta que se han conseguido ciertas ventajas del sistema. También debe apreciarse que pueden realizarse diversas modificaciones, adaptaciones y realizaciones alternativas de las mismas dentro del alcance de la presente invención. La invención se define además mediante las reivindicaciones siguientes.

#### REIVINDICACIONES

1. Un sistema de control de potencia (100) que comprende:

15

20

25

35

50

- una pluralidad de reguladores de punto de carga (POL) (106, 108, 110, 112, 114) que comprenden cada uno al menos un interruptor de alimentación (12, 14) adaptado para transmitir energía a una carga (20) y un controlador digital (34) adaptado para controlar la operación de dicho al menos un interruptor de alimentación (12, 14) que responde a una medición de retroalimentación (V<sub>o</sub>), comprendiendo dicho controlador digital (34) además un filtro de respuesta al impulso infinita que tiene una función de transferencia definida por coeficientes de filtro plural (C<sub>o</sub>-C<sub>n</sub>, B<sub>1</sub>-B<sub>n</sub>);

- un bus de datos en serie que conecta operativamente dicha pluralidad de reguladores de POL (106, 108, 110, 112, 114); y un controlador de sistema (102) conectado a dicho bus de datos en serie y adaptado para comunicar datos digitales a dicha pluralidad de reguladores de POL (106, 108, 110, 112, 114) a través de dicho bus de datos en serie, incluyendo dichos datos digitales datos de programación para la programación de dichos coeficientes de filtro plural (C<sub>o</sub>-C<sub>n</sub>, B<sub>1</sub>-B<sub>n</sub>);

- donde dicho controlador de sistema (102) comprende además una interfaz de usuario (128) adaptada para recibir dichos datos de programación desde un sistema de usuario, comprendiendo dicho sistema de usuario al menos un ordenador de usuario, donde dicho filtro de respuesta al impulso infinita proporciona la siguiente función de transferencia G(z):

- $G(z) = \frac{PWM(z)}{VEd(z)} = \frac{C_0 + C_1 \cdot z^{-1} + C_2 \cdot z^{-2} + \dots + C_n \cdot z^{-n}}{1 B_1 \cdot z^{-1} B_2 \cdot z^{-2} \dots B_n \cdot z^{-n}}$

- donde PWM(z) es una salida de control digital, VEd(z) es una señal de error, y dichos coeficientes de filtro plural incluyen Co... Cn como coeficientes de filtro de lado de entrada y B<sub>1</sub>... B<sub>n</sub> como coeficientes de filtro de lado de salida.

- 2. El sistema de control de potencia (100) de la reivindicación 1, donde dicho controlador digital (34) comprende además:

- un convertidor analógico a digital (32, 40) que proporciona una señal de error digital que representa una diferencia entre dicha medición de retroalimentación (Vo) y un valor de referencia (Ref), proporcionando dicho filtro digital una salida de control digital basada en una suma de corriente y señales de error anteriores y salidas de control anteriores;

- un controlador de error (62) adaptado para modificar el funcionamiento de dicho filtro de respuesta al impulso infinita en un estado de error; y

- un modulador de ancho de pulso digital (36) que proporciona una señal de control a dicho al menos un interruptor de alimentación (12, 14), teniendo dicha señal de control un ancho de pulso correspondiente a dicha salida de control digital.

- 40 3. El sistema de control de potencia (100) de la reivindicación 2, donde dicho convertidor analógico a digital (32, 40) comprende además un convertidor de flash en ventana analógico a digital (32, 40).

- 4. El sistema de control de potencia (100) de la reivindicación 3, donde dicho convertidor de flash analógico a digital en ventana (32, 40) proporciona una señal ALTA que refleja una saturación negativa de dicho convertidor analógico a digital (32, 40) y una señal BAJA que refleja una saturación positiva de dicho convertidor analógico a digital (32, 40).

- 5. El sistema de control de potencia (100) de la reivindicación 4, donde dicho filtro de respuesta al impulso infinita comprende además un limitador de intervalo adaptado para recortar dicha salida de control digital si se alcanzan los límites de intervalo superior o inferior.

- 6. El sistema de control de potencia (100) de la reivindicación 2, donde limitador de intervalo proporciona una señal de límite a dicho controlador de error (62) si se alcanzan dichos límites de intervalo superior o inferior.

- 7. El sistema de control de potencia (100) de la reivindicación 2, donde dicho controlador digital (34) comprende además un multiplexor acoplado a dicho controlador de error (62) y a dicho filtro de respuesta al impulso infinita, proporcionando dicho controlador de error (62) una salida de control digital alternativa a dicho multiplexor que pasa a dicho modulador de ancho de pulso digital (36) en dicho estado de error.

- 8. El sistema de control de potencia (100) de la reivindicación 2, donde dicho controlador de error (62) está adaptado además para preestablecer al menos una de dichas señales de error anteriores con valores predeterminados en dicho estado de error.

- 9. El sistema de control de potencia (100) de la reivindicación 2, donde dicho controlador de error (62) está adaptado además para preestablecer al menos una de dichas salidas de control anteriores con valores predeterminados en dicho estado de error.

- 5 10. El sistema de control de potencia (100) de la reivindicación 2, donde dicho controlador de error (62) está adaptado además para restablecer al menos una de dichas señales de error anteriores con valores iniciales en dicho estado de error.

- El sistema de control de potencia (100) de la reivindicación 2, donde dicho controlador de error (62) está

adaptado además para restablecer al menos una de dichas salidas de control anteriores con valores iniciales en dicho estado de error.

15

- 12. El sistema de control de potencia (100) de la reivindicación 2, donde dicho estado de error comprende además una saturación de dicho convertidor analógico a digital (32, 40).

- 13. El sistema de control de potencia (100) de la reivindicación 2, donde dicho estado de error comprende además un sobreflujo matemático de dicho filtro digital.

- 14. Un procedimiento para controlar una pluralidad de reguladores de punto de carga (POL) (106, 108, 110, 112, 114) a través de un controlador de sistema (102) que comprenden cada uno de dichos reguladores de POL al menos un interruptor de alimentación (12, 14) adaptado para transmitir energía a una carga (20) y un controlador digital (34) adaptado para controlar la operación de dicho al menos un interruptor de alimentación (12, 14) que responde a una medición de retroalimentación (Vo), comprendiendo dicho controlador digital (34) además un filtro de respuesta al impulso infinita que tiene una función de transferencia definida por coeficientes de filtro plural (Co-Cn, B1-Bn), comprendiendo el procedimiento:

- recibir datos de programación en el controlador de sistema (102) para programar dichos coeficientes de filtro plurales (Co-Cn, B1-Bn) desde un ordenador de usuario externo a través de un bus de datos de interfaz de usuario;

- transmitir dichos datos de programación en serie a través de un bus de datos en serie común conectado operativamente a dicha pluralidad de reguladores de POL (106, 108, 110, 112, 114), donde dicho bus de datos en serie común está separado y es distinto de dicho bus de datos de interfaz de usuario; y programar dichos coeficientes de filtro plural (C<sub>o</sub>-C<sub>n</sub>, B<sub>1</sub>-B<sub>n</sub>) de los respectivos reguladores de POL (106, 108,

- 110, 112, 114) de acuerdo con dichos datos de programación, 35 donde dicha etapa de programación comprende además programar dicho filtro de respuesta al impulso infinita para proporcionar la siguiente función de transferencia G(z):

$$G(z) = \frac{PWM(z)}{VEd(z)} = \frac{C_0 + C_1 \cdot z^{-1} + C_2 \cdot z^{-2} + \dots + C_n \cdot z^{-n}}{1 - B_1 \cdot z^{-1} - B_2 \cdot z^{-2} - \dots - B_n \cdot z^{-n}}$$

donde PWM(z) es una salida de control digital, VEd(z) es una señal de error, y dichos coeficientes de filtro plural incluyen Co...Cn como coeficientes de filtro de lado de entrada y B<sub>1</sub>... Bn como coeficientes de filtro de lado de salida.

F1G. 7