OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 750 803

(51) Int. CI.:

H04L 12/24 (2006.01) H02J 13/00 (2006.01) H04L 12/853 (2013.01) H04Q 9/02 (2006.01) H04L 29/08 (2006.01) G06F 1/26 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- (96) Fecha de presentación y número de la solicitud europea: 29.12.2016 E 16207225 (0)

- (97) Fecha y número de publicación de la concesión europea: EP 3301884 14.08.2019

- (54) Título: Procedimiento de transferencia de datos basado en sistema de protección y control para subestación inteligente

- (<sup>30</sup>) Prioridad:

### 29.09.2016 CN 201610866118

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 27.03.2020

(73) Titular/es:

**KYLAND TECHNOLOGY CO., LTD. (100.0%)** F15 Building 2, No. 30 Shixing Road, Shijingshan Beijing 100041, CN

(72) Inventor/es: DING, YUQI

(74) Agente/Representante:

**ELZABURU, S.L.P**

### **DESCRIPCIÓN**

Procedimiento de transferencia de datos basado en sistema de protección y control para subestación inteligente

#### Sector técnico

Las realizaciones de la descripción se refieren al sector técnico de las subestaciones inteligentes, y en particular se refieren a un procedimiento de transferencia de datos basado en un sistema de protección y control para una subestación inteligente.

#### **Antecedentes**

5

10

15

20

25

30

35

40

45

50

Una subestación inteligente es una subestación que tiene dispositivos principales y secundarios de la subestación como objetos inteligentes, y que puede llevar a cabo compartición de información e interoperación estandarizando información inteligente en base a una plataforma de comunicación de red de alta velocidad, y puede asimismo llevar a cabo funciones de automatización, tales como monitorización de medición, control y protección, gestión de información y similares, en base a datos de red.

La subestación inteligente incluye un nivel de estación, un nivel de bahía y un nivel de proceso, y el contacto efectivo se realiza principalmente entre diferentes niveles a través de cables ópticos. Cada nivel incluye diferentes sistemas, dispositivos y aparatos que actúan conjuntamente y cooperan entre sí. El nivel de bahía incluye principalmente dispositivos secundarios, tales como un aparato de medición y control y un aparato de protección, y completa la medición, el control y la protección de los dispositivos a nivel de proceso analizando mensajes de valores muestreados (SV, sampled value) o mensajes de eventos de subestación genéricos orientados a objetos (GOOSE, generic object oriented substation events) transmitidos por un dispositivo integrado de unidad de fusión y terminal inteligente.

En la técnica relacionada, la subestación se divide en una parte de línea de alta tensión, una parte de transformador principal y una parte del lado de media tensión, y cada parte se divide en diferentes bahías de dispositivos. Dado que los aparatos de protección se clasifican según las bahías del dispositivo divididas por funciones, pueden existir una serie de tipos de aparatos de protección en cada bahía de la subestación y, por lo tanto, se generan muchos mensajes. En la técnica relacionada, la recepción y transmisión en tiempo real de los anteriores volúmenes de mensajes no se puede satisfacer, y la eficiencia de la transmisión de mensajes es relativamente baja, influyendo por lo tanto sobre la eficiencia de funcionamiento de la subestación.

La patente CN 103 887 885 A da a conocer una subestación inteligente integrada de 35 kV. La subestación inteligente integrada de 35 kV comprende una plataforma de información integrada, un dispositivo integrado de control de protección y medición del área de la subestación y un conjunto inteligente integral. El conjunto inteligente integral recibe valores de muestreo e información de estado de un dispositivo inteligente principal, y transmite los valores de muestreo y la información de estado al dispositivo integrado de control de protección y medición y medición del área de subestación, de la subestación, de la subestación, se lleva a cabo por medio del dispositivo integrado de control de protección y medición del área de la subestación, y se emite una instrucción GOOSE en el conjunto inteligente integral para conseguir un control de medición inteligente sobre el dispositivo inteligente principal. El dispositivo integrado de control de protección y medición del área de la subestación transmite el resultado de la valoración lógica a la plataforma de información integrada, y recibe instrucciones de planificación e instrucciones de control de la plataforma de información integrada.

La patente CN 104 008 214 A da a conocer un procedimiento y un sistema para almacenar información de ejecución en tiempo real de una subestación inteligente. El procedimiento de almacenamiento comprende las etapas de obtener información de ejecución de la subestación, extraer la información de ejecución en un modo clasificado, clasificar la información de ejecución clasificada en función de requisitos característicos respectivos y almacenar los resultados de procesamiento en un medio de almacenamiento en un modo de partición de acuerdo con la clasificación. Por medio del modo de implementación, se puede capturar rápidamente información de ejecución original de la subestación inteligente, se pueden almacenar a largo plazo los tipos importantes de información de ejecución e información de análisis de fallos, y un mantenedor puede determinar con precisión la razón del fallo en la subestación en tiempo.

## Compendio

En vista de esto, las realizaciones de la descripción dan a conocer un procedimiento de transferencia de datos basado en un sistema de protección y control para una subestación inteligente, de tal modo que se resuelven los problemas técnicos en la técnica relacionada de que no se pueden procesar cantidades de mensajes en tiempo real y de que la eficiencia de transmisión de mensajes es relativamente baja.

La invención se define mediante las reivindicaciones independientes adjuntas. Se definen otras realizaciones mediante las reivindicaciones dependientes.

## Breve descripción de los dibujos

Para describir más claramente la solución técnica de las realizaciones a modo de ejemplo de la descripción, los dibujos que se utilizarán en las descripciones de las realizaciones se introducirán de manera simple a continuación. Evidentemente, los dibujos introducidos son solamente dibujos de una parte de las realizaciones que se van a describir en la descripción, pero no la totalidad de los dibujos. Los expertos en la materia pueden obtener otros dibujos en función de dichos dibujos, sin realizar ningún trabajo creativo.

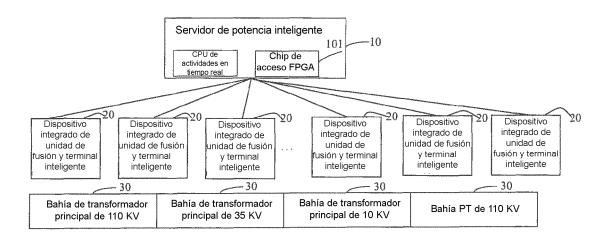

La figura 1 es un diagrama esquemático que muestra una estructura de una subestación inteligente dada a conocer por la realización I de la descripción:

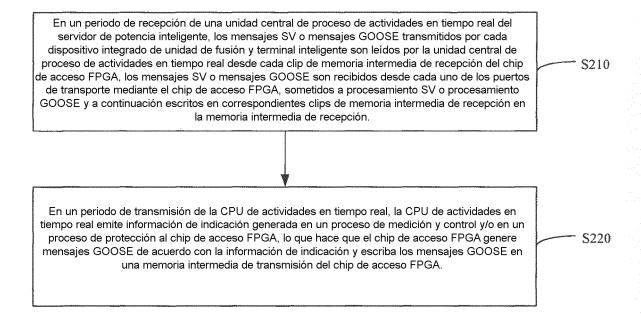

la figura 2 es un diagrama esquemático que muestra un flujo de un procedimiento de transferencia de datos basado en un sistema de protección y control para una subestación inteligente, dado a conocer por la realización I de la descripción; y

la figura 3 es un diagrama esquemático que muestra un flujo de un procedimiento de transferencia de datos basado en un sistema de protección y control para una subestación inteligente, dado a conocer por la realización II de la descripción.

### 15 Descripción detallada

La descripción se describe en mayor detalle a continuación combinando los dibujos y las realizaciones. Se debe entender que las realizaciones descritas en la presente memoria se utilizan solamente para ilustrar la descripción, no para limitar la descripción. Además, se debe observar que, para una descripción cómoda, en los dibujos se muestran solamente partes de los contenidos relacionados con la descripción, pero no todos los contenidos.

Se debe mencionar que algunas realizaciones a modo de ejemplo se describen para servir como procesos o procedimientos descritos en los diagramas de flujo, antes de que se expliquen en detalle las realizaciones a modo de ejemplo. Aunque se describen varias operaciones (o etapas) en procesamiento secuencial en el diagrama de flujo, muchas operaciones en este se pueden implementar de manera concurrente, concomitante o simultánea. Además, una secuencia de varias operaciones puede ser reordenada. El proceso puede finalizar cuando las operaciones del mismo se completan, si bien el proceso puede incluir asimismo etapas adicionales que no se muestran en los dibujos. El proceso puede corresponder a métodos, funciones, procedimientos, subrutinas, subprogramas y similares.

### Realización I

40

45

50

55

La figura 1 es un diagrama esquemático que muestra una estructura de una subestación inteligente dada a conocer por la realización I de la descripción. La figura 2 es un diagrama esquemático que muestra un flujo de un procedimiento de transferencia de datos basado en un sistema de protección y control para una subestación inteligente, dado a conocer por la realización I de la descripción. El procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente, dado a conocer por las realizaciones de la descripción se puede aplicar a un sistema de subestación inteligente mostrado en la figura 1. Tal como se muestra en la figura 1, la subestación inteligente puede incluir un servidor de potencia inteligente 10, dispositivos integrados de unidad de fusión y terminal inteligente 20, y bahías 30.

Los dispositivos integrados de unidad de fusión y terminal inteligente 20 para todas las bahías 30 en la subestación inteligente acceden directamente al servidor de potencia inteligente 10. De acuerdo con la descripción, cada dispositivo integrado de unidad de fusión y terminal inteligente 20 accede a uno de los puertos de transporte de un chip de acceso FPGA 101 en el servidor de potencia inteligente, simplemente a través de una conexión física, y toda la protección y la medición y el control de los dispositivos principales conectados a los dispositivos integrados de unidad de fusión y terminal inteligente son realizados por el servidor de potencia inteligente 10.

Los dispositivos integrados de unidad de fusión y terminal inteligente 20 para todas las bahías en la subestación inteligente acceden directamente al servidor de potencia inteligente 10, cada dispositivo integrado de unidad de fusión y terminal inteligente accede a uno de los puertos de transporte en el servidor de potencia inteligente por medio de una red de comunicación conmutada de gran ancho de banda integrada. Los datos de nivel de proceso son recogidos en tiempo real por el servidor de potencia inteligente en un modo en que cada dispositivo integrado de unidad de fusión y terminal inteligente accede al puerto de transporte en el servidor de potencia inteligente a través de la red de comunicación conmutada de gran ancho de banda integrada, se completa el procesamiento de los datos en tiempo real de los datos de nivel de proceso recogidos, y se lleva a cabo toda la protección y medición y control de los dispositivos principales conectados a los dispositivos integrados de unidad de fusión y terminal inteligente. Específicamente, la red de comunicación conmutada de gran ancho de banda integrada puede ser un bus de red de área del controlador (CAN, controller area network), un bus de protocolo de internet (IP, Internet Protocol) de campo, un bus Modbus, un bus de campo de proceso (Profibus), un bus de protocolo de comunicación abierto de transductor remoto direccionable de alta velocidad (HART, highway addressable remote transducer), un bus de campo de Foundation Feildbus (FF) o una fibra óptica.

Ilustrativamente, cada dispositivo integrado de unidad de fusión y terminal inteligente 20 accede a un puerto de transporte en el servidor de potencia inteligente 10 simplemente a través de una conexión física. Específicamente, cada dispositivo integrado de unidad de fusión y terminal inteligente está conectado a un puerto de transporte del servidor de potencia inteligente simplemente a través de un par de fibras ópticas. Un puerto de transporte del servidor de potencia inteligente incluye un puerto de recepción y un puerto de transmisión, cada dispositivo integrado de unidad de fusión y terminal inteligente accede al puerto de recepción del puerto de transporte en el servidor de potencia inteligente a través de una fibra óptica, y el dispositivo integrado de unidad de fusión y terminal inteligente accede al puerto de transmisión del puerto de transporte en el servidor de potencia inteligente a través de otra fibra óptica. Los datos de nivel de proceso son reunidos en tiempo real por el servidor de potencia inteligente simplemente a través de una conexión física. Por ejemplo, se recogen los mensajes SV y los mensajes GOOSE transmitidos por los dispositivos integrados de unidad de fusión y terminal inteligente, y los datos de nivel de proceso reunidos en tiempo real se procesan en tiempo real, consiguiendo de ese modo la protección y medición y control de los dispositivos principales conectados a los dispositivos integrados de unidad de fusión y terminal inteligente.

10

20

25

45

Sin embargo, un dispositivo integrado de unidad de fusión y terminal inteligente en la subestación tradicional tiene que acceder a una serie de diferentes aparatos físicos, y la medición y control y protección de los dispositivos principales conectados al dispositivo integrado de unidad de fusión y terminal inteligente se lleva a cabo respectivamente a través de estos diferentes aparatos físicos.

El servidor de potencia inteligente 10 puede incluir el chip de acceso FPGA 101. El chip de acceso FPGA 101 puede estar dotado de 16 puertos de transporte de alta velocidad, tales como puertos de transporte Ethernet 100M, para acceder a los dispositivos integrados de unidad de fusión y terminal inteligente 20 a través de los puertos de transporte de alta velocidad. El chip de acceso FPGA 101 puede incluir además una memoria intermedia de recepción y una memoria intermedia de transmisión. Además, una serie de clips de memoria intermedia de recepción están incluidos en la memoria intermedia de transmisión, y cada puerto de transporte corresponde a un clip de memoria intermedia de recepción/un clip de memoria intermedia de transmisión. Las bahías 30 pueden incluir muchas bahías de transformador, bahías de línea y bahías de bus, tal como una bahía de transformador principal de 10 kV, una bahía de transformador principal de 35 kV, una bahía de transformador principal de 10 kV, y cada bahía 30 incluye por lo menos un dispositivo integrado de unidad de fusión y terminal inteligente 20.

Cada dispositivo integrado de unidad de fusión y terminal inteligente 20 accede a uno de los puertos de transporte del chip de acceso FPGA 101 en el servidor de potencia inteligente simplemente a través de una conexión física, y cada puerto de transporte del chip de acceso FPGA 101 en el servidor de potencia inteligente está conectado solamente a un dispositivo integrado de unidad de fusión y terminal inteligente, es decir, los dispositivos integrados de unidad de fusión y terminal inteligente 20 y los puertos de transporte en el chip de acceso FPGA 101 están en una relación de correspondencia unívoca. Dado que cada puerto de transporte corresponde a un clip de memoria intermedia de recepción/clip de memoria intermedia de transmisión, cada dispositivo integrado de unidad de fusión y terminal inteligente 20 corresponde a un clip de memoria intermedia de recepción/clip de memoria intermedia de transmisión. El servidor de potencia inteligente 10 se puede utilizar para llevar a cabo todas las funciones de medición y control, protección, conmutación y telecontrol en la subestación inteligente.

Tal como se muestra en la figura 2, el procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente puede incluir las etapas descritas a continuación.

En S210, en un periodo de recepción de una unidad central de proceso de actividades en tiempo real del servidor de potencia inteligente, los mensajes SV o mensajes GOOSE transmitidos por cada dispositivo integrado de unidad de fusión y terminal inteligente, son leídos por la unidad central de proceso de actividades en tiempo real desde cada clip de memoria intermedia de recepción del chip de acceso FPGA. Los mensajes SV o mensajes GOOSE son recibidos desde cada uno de los puertos de transporte mediante el chip de acceso FPGA, sometidos a procesamiento SV o procesamiento GOOSE y a continuación escritos en correspondientes clips de memoria intermedia de recepción en la memoria intermedia de recepción, y los clips de memoria intermedia de recepción y los puertos de transporte están en una relación de correspondencia unívoca.

Ilustrativamente, el servidor de potencia inteligente 10 puede incluir la unidad central de proceso (CPU, central processing unit) de actividades en tiempo real, y la CPU de actividades en tiempo real se puede utilizar para las actividades en tiempo real en el servidor de potencia inteligente 10, tales como servicios de transferencia de mensajes. Opcionalmente, los servicios de transferencia de mensajes mediante la CPU de actividades en tiempo real pueden incluir un periodo de recepción y un periodo de transmisión.

La memoria intermedia de recepción es dividida en una serie de clips de memoria intermedia de recepción mediante la FPGA, y cada puerto de transporte Ethernet de la FPGA corresponde a un clip de memoria intermedia de recepción, es decir, un dispositivo integrado de unidad de fusión y terminal inteligente 20 corresponde a un clip de memoria intermedia de recepción. La FPGA detecta la recepción de mensajes de cada puerto de transporte Ethernet en tiempo real. Cuando existen mensajes en un puerto de transporte, los mensajes son recibidos por el chip de acceso FPGA 101 desde el puerto de transporte, sometidos a procesamiento SV o procesamiento GOOSE, y a

continuación escritos en correspondientes clips de memoria intermedia de recepción en la memoria intermedia de recepción.

En el periodo de recepción, los mensajes SV o mensajes GOOSE transmitidos por cada dispositivo integrado de unidad de fusión y terminal inteligente 20 son leídos por la CPU de actividades en tiempo real desde cada clip de memoria intermedia de recepción del chip de acceso FPGA 101.

En S220, en un periodo de transmisión de la CPU de actividades en tiempo real, la información de indicación generada en un proceso de medición y control y/o en un proceso de protección se emite al chip de acceso FPGA mediante la CPU de actividades en tiempo real, lo que hace que el chip de acceso FPGA genere mensajes GOOSE de acuerdo con la información de indicación y escriba a continuación los mensajes GOOSE en la memoria intermedia de transmisión del chip de acceso FPGA.

10

15

35

40

45

50

55

60

Ilustrativamente, dado que el servidor de potencia inteligente 10 puede llevar a cabo la función de medición y control y la función de protección, la CPU de actividades en tiempo real en el servidor de potencia inteligente 10 puede generar la información de indicación para los dispositivos principales en el proceso de medición y control y/o el proceso de protección. Por lo tanto, la información de indicación se puede emitir al chip de acceso FPGA 101 mediante la CPU de actividades en tiempo real en el periodo de transmisión, lo que hace que el chip de acceso FPGA 101 genere mensajes GOOSE de acuerdo con la información de indicación, y los mensajes GOOSE generados se escriben en la memoria intermedia de transmisión del chip de acceso FPGA 101.

Opcionalmente, la duración del periodo de recepción de la CPU de actividades en tiempo real es mayor que la duración del periodo de transmisión.

Se debe entender que la CPU de actividades en tiempo real lee los mensajes SV o mensajes GOOSE desde la memoria intermedia de recepción del chip de acceso FPGA 101 en el periodo de recepción, es decir, la CPU de actividades en tiempo real consulta periódicamente la memoria intermedia de recepción del chip de acceso FPGA 101 en el periodo de recepción. Los mensajes GOOSE emitidos al dispositivo integrado de unidad de fusión y terminal inteligente 20 mediante el servidor de potencia inteligente 10 se escriben en la memoria intermedia de transmisión del chip de acceso FPGA 101 en el periodo de transmisión. Dado que el tráfico de mensajes recibido desde los dispositivos de nivel de proceso es mayor que el tráfico de mensajes transmitido a los dispositivos de nivel de proceso, los mensajes de los dispositivos de nivel de proceso son recibidos preferentemente, reduciendo de ese modo el retardo en la recepción. Por lo tanto, la duración del periodo de recepción se puede ajustar para que sea mayor que la duración del periodo de transmisión, de tal modo que todos los mensajes pueden ser recibidos en el periodo de recepción, evitando de ese modo la pérdida de información debida a una recepción de mensajes inadecuada e incompleta, provocada por un periodo de recepción corto.

El chip de acceso FPGA 101 detecta mensajes en cada puerto de transporte Ethernet en tiempo real. Cuando existen mensajes en el puerto de transporte Ethernet, el chip de acceso FPGA 101 lee los mensajes en una memoria intermedia de recepción local y aumenta en uno el número total de los mensajes en el clip de memoria intermedia de recepción. Después de que un mensaje es leído por la CPU de actividades en tiempo real desde el clip de memoria intermedia de recepción, el chip de acceso FPGA 101 resta uno del número total de los mensajes en el clip de memoria intermedia de recepción, y notifica en tiempo real el número total de mensajes en cada clip de memoria intermedia de recepción a la CPU de actividades en tiempo real, en el periodo de recepción. Al mismo tiempo, el chip de acceso FPGA 101 detecta en tiempo real si la memoria intermedia de transmisión está vacía. Si la memoria intermedia de transmisión no está vacía, los mensajes GOOSE se escriben en correspondientes puertos de transporte Ethernet de acuerdo con las direcciones de destino de los mensajes GOOSE, y se escriben asimismo instrucciones de transmisión en correspondientes puertos de transporte Ethernet mediante el chip de acceso FPGA 101. Todos los puertos de transporte Ethernet pueden funcionar simultáneamente, y se pueden escribir a la vez mensajes en una serie de puertos de transporte Ethernet.

De acuerdo con el procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente dado a conocer por la realización I de la descripción, los dispositivos integrados de unidad de fusión y terminal inteligente para todas las bahías en la subestación inteligente acceden a correspondientes puertos de transporte del chip de acceso FPGA del servidor de potencia inteligente respectivamente, y los dispositivos integrados de unidad de fusión y terminal inteligente y los puertos de transporte están en una relación de correspondencia unívoca. En el periodo de recepción, los mensajes son leídos desde cada clip de memoria intermedia de recepción del chip de acceso FPGA, y procesados en consecuencia y escritos a continuación en los clips de memoria intermedia de recepción, mediante la CPU de actividades en tiempo real. En el periodo de transmisión, la CPU de actividades en tiempo real emite la información de indicación generada en el proceso de medición y control y/o de protección al chip de acceso FPGA, y el chip FPGA genera mensajes GOOSE de acuerdo con la información de indicación y los escribe en la memoria intermedia de transmisión. La récepción/transmisión de mensajes se lleva a cabo mediante la CPU de actividades en tiempo real por medio de la memoria intermedia de recepción/memoria intermedia de transmisión del chip de acceso FPGA, impidiendo de ese modo que la transmisión/recepción en tiempo real de los mensajes se vea afectada por una carga pesada de la CPU de actividades en tiempo real. Por lo tanto, el chip de acceso FPGA puede controlar de manera concurrente la transmisión de mensajes en la memoria intermedia de transmisión, leyendo al mismo tiempo mensajes a recibir

desde los puertos de transporte, acortando sensiblemente de ese modo el retardo de la transmisión y la recepción de mensajes, mejorando la propiedad de tiempo real y aliviando adicionalmente la carga de procesamiento de la CPU.

#### Realización II

15

20

25

30

35

40

45

50

55

60

La figura 3 muestra un procedimiento de transferencia de datos basado en un sistema de protección y control para una subestación inteligente dado a conocer por la realización II de la descripción. La realización se basa en la realización anterior, y se mejora en base a la realización anterior. Específicamente, se mejora la recepción y la transmisión de datos de mensaje. Tal como se muestra en la figura 3, el procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente dado a conocer por la realización II de la descripción puede incluir las etapas descritas a continuación.

En S310, la CPU de actividades en tiempo real lee mensajes de cada clip de memoria intermedia de recepción, de acuerdo con un orden descendente del número total de mensajes de cada clip de memoria intermedia de recepción.

Ilustrativamente, existen clips de memoria intermedia de recepción con una cantidad grande de mensajes almacenados en memoria intermedia, y clips de memoria intermedia de recepción con una cantidad pequeña de mensajes almacenados en memoria intermedia, debido a que el número total de mensajes almacenados en cada clip de memoria intermedia de recepción es diferente. La CPU de actividades en tiempo real lee mensajes de cada clip de memoria intermedia de recepción en función del orden descendente del número de mensajes totales almacenados en memoria intermedia en cada clip de memoria intermedia de recepción de la memoria intermedia de recepción, y lee mensajes del clip de memoria intermedia de recepción con el número máximo de mensajes totales. Opcionalmente, después de leer mensaies desde el clip de memoria intermedia de recepción, la CPU de actividades en tiempo real lee además mensajes desde un clip de memoria intermedia de recepción con el número máximo actualmente de mensajes totales. El chip de acceso FPGA 101 puede notificar el número total de mensajes de cada clip de memoria intermedia de recepción a la CPU de actividades en tiempo real en el periodo de recepción, garantizando de ese modo que la CPU de actividades en tiempo real puede conocer el número total de mensajes de cada clip de memoria intermedia de recepción en tiempo real, y garantizando además que los mensajes almacenados en memoria intermedia en cada clip de memoria intermedia de recepción pueden ser recibidos de acuerdo con el orden descendente del número total de mensajes. Una estrategia de recepción de la CPU de actividades en tiempo real puede evitar que existan demasiados mensajes en algunos clips de memoria intermedia de recepción del chip de acceso FPGA 101 mientras existen demasiados pocos mensajes en otros clips de memoria intermedia de recepción, evitando de ese modo la situación en la que un clip de memoria intermedia de recepción individual llena su cuota de almacenamiento debido a tener almacenado un gran número de mensajes, y no puede almacenar nuevos mensajes.

En S320, el chip de acceso FPGA 101 genera mensajes GOOSE de acuerdo con la información de indicación generada por la CPU de actividades en tiempo real en el proceso de medición y control y/o el proceso de protección, y escribe los mensajes en correspondientes clips de memoria intermedia de transmisión de acuerdo con la dirección MAC (control de acceso al medio) de destino en los mensajes GOOSE. La dirección MAC de destino es la dirección MAC del dispositivo integrado de unidad de fusión y terminal inteligente 20.

Ilustrativamente, la memoria intermedia de transmisión del chip de acceso FPGA 101 incluye una serie de clips de memoria intermedia de transmisión, y cada uno de los clips de memoria intermedia de transmisión corresponde a un puerto de transporte Ethernet en el chip de acceso FPGA 101. Opcionalmente, el chip de acceso FPGA 101 escribe mensajes GOOSE en correspondientes clips de memoria intermedia de transmisión de acuerdo con las direcciones MAC de destino de los mensajes GOOSE. Dado que cada puerto de transporte del chip de acceso FPGA 101 corresponde a un clip de memoria intermedia de transmisión y cada puerto de transporte corresponde a un dispositivo integrado de unidad de fusión y terminal inteligente, los mensajes en los clips de memoria intermedia de transmisión se escriben en los correspondientes puertos de transporte Ethernet y se transmiten directamente a los correspondientes dispositivos integrados de unidad de fusión y terminal inteligente a través de los puertos de transporte en el proceso de transmisión de mensajes.

De acuerdo con el procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente dado a conocer por la realización de la descripción, en el periodo de recepción de datos de mensajes, los mensajes son leídos desde cada clip de memoria intermedia de recepción de acuerdo con el orden descendente del número total de mensajes en los clips de memoria intermedia de recepción, evitando de ese modo la situación en la que un clip de memoria intermedia de recepción individual ha llenado su cuota de almacenamiento debido a tener almacenados un gran número de mensajes, y no puede almacenar nuevos mensajes. En el periodo de transmisión de datos de mensajes, el chip de acceso FPGA escribe mensajes GOOSE en correspondientes clips de memoria intermedia de transmisión de acuerdo con las direcciones MAC de destino en los mensajes GOOSE, lo que garantiza que los mensajes GOOSE se pueden escribir en correspondientes clips de memoria intermedia de transmisión, mejorando de ese modo la eficiencia de la escritura de mensajes. En conclusión, con la solución técnica anterior, la eficiencia en el procesamiento de mensajes se puede mejorar tanto en el periodo de recepción como en el periodo de transmisión, mejorando de ese modo la eficiencia de la transferencia de datos de toda la subestación inteligente y garantizando además un funcionamiento de alta eficiencia de la subestación inteligente.

#### Realización III

10

45

50

55

La realización III de la descripción da a conocer un procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente. La realización se basa en las realizaciones anteriores, y se mejora en base a las realizaciones anteriores. Específicamente, se mejora la lectura de mensajes mediante la CPU de actividades en tiempo real. De manera similar, haciendo referencia a la figura 2, el procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente dado a conocer por la realización III de la descripción puede incluir las etapas descritas a continuación.

La tarea actual es interrumpida y los mensajes GOOSE son leídos desde un clip de memoria intermedia de recepción en el que el número de mensajes GOOSE supera un primer umbral preestablecido cuando un mensaje de notificación transmitido por el chip de acceso FPGA 101 es recibido por la CPU de actividades en tiempo real. La FPGA detecta el número de mensajes GOOSE escritos en cada clip de memoria intermedia de recepción. Si se detecta que el número de mensajes GOOSE escritos en el clip de memoria intermedia de recepción supera el primer umbral preestablecido, el mensaje de notificación es transmitido para notificar que el número de mensajes GOOSE en el clip de memoria intermedia de recepción supera el primer umbral preestablecido.

Ilustrativamente, en condiciones normales, los mensajes GOOSE son retransmitidos una vez cada varios 15 milisegundos en el lado del dispositivo integrado de unidad de fusión y terminal inteligente 20, y el número de mensajes GOOSE generados es pequeño. Sin embargo, cuando se produce un fallo, una serie de semáforos de conmutación se desvían, generando de ese modo un tráfico de datos elevado. Cuando se transmiten cantidades de mensajes GOOSE mediante un dispositivo integrado de unidad de fusión y terminal inteligente 20, esto indica que se 20 producen fallos en bahías correspondientes al anterior dispositivo integrado de unidad de fusión y terminal inteligente 20, y el servidor de potencia inteligente 10 debería responder en tiempo. Para responder en tiempo a los fallos, el chip de acceso FPGA 101 identifica el tipo de mensajes leyendo al mismo tiempo los mensajes desde los puertos de transporte, y el número de mensajes GOOSE en el correspondiente clip de memoria intermedia de recepción aumenta en uno si el mensaje es el mensaje GOOSE. El chip de acceso FPGA 101 detecta el número de 25 mensajes GOOSE escrito en cada clip de memoria intermedia de recepción, y transmite el mensaje de notificación a la CPU de actividades en tiempo real si se detecta que el número de mensajes GOOSE escrito en el clip de memoria intermedia de recepción supera el primer umbral preestablecido, notificando de ese modo que el número de mensajes GOOSE en el clip de memoria intermedia de recepción supera el primer umbral preestablecido.

Opcionalmente, el primer umbral preestablecido puede ser preestablecido en operaciones reales en función del número real de mensajes GOOSE generado durante la ocurrencia de un fallo en el lado del dispositivo integrado de unidad de fusión y terminal inteligente 20. Por ejemplo, el primer umbral preestablecido puede ser un valor medio del número real de mensajes GOOSE generados durante la aparición de un fallo. La CPU de actividades en tiempo real es notificada activamente para leer preferentemente mensajes GOOSE de un determinado clip de memoria intermedia de recepción si el chip de acceso FPGA 101 detecta que el número de mensajes GOOSE en el clip de memoria intermedia de recepción aumenta súbitamente superando el primer umbral preestablecido. Después de que se reciba una notificación del primer chip de acceso FPGA 101 mediante la CPU de actividades en tiempo real, la tarea actual se interrumpe, y los mensajes GOOSE son leídos preferentemente desde el clip de memoria intermedia de recepción y a continuación la tarea interrumpida vuelve a ser procesada de forma continua.

Además, la ejecución de la actual tarea interrumpida se reanuda si el número de mensajes GOOSE en el clip de memoria intermedia de recepción es menor que el primer umbral preestablecido, al leer los mensajes GOOSE por medio de la CPU de actividades en tiempo real.

Ilustrativamente, la CPU de actividades en tiempo real interrumpe la tarea ejecutada actualmente, tras la recepción de la notificación del chip de acceso FPGA 101, y preferentemente lee mensajes GOOSE del clip de memoria intermedia de recepción en el que el número de mensajes GOOSE supera el primer umbral preestablecido. Después de cada vez que se leen los mensajes GOOSE, el chip de acceso FPGA 101 disminuye en uno el número de mensajes GOOSE en el correspondiente clip de memoria intermedia de recepción, y notifica en tiempo real el número de mensajes GOOSE en el clip de memoria intermedia de recepción actual. Cuando el número de mensajes GOOSE en el clip de memoria intermedia de recepción es menor que el primer umbral preestablecido, al leer los mensajes GOOSE por medio de la CPU de actividades en tiempo real, el número de mensajes GOOSE en el clip de memoria intermedia de recepción está en un valor normal, y la CPU de actividades en tiempo real no necesita leer preferentemente los mensajes GOOSE del clip de memoria intermedia de recepción, y entonces la CPU de actividades en tiempo real reanuda la ejecución de la tarea actual interrumpida.

Además, la ejecución de la tarea actual interrumpida se reanuda si el número de mensajes GOOSE en el clip de memoria intermedia de recepción es menor que un segundo umbral preestablecido, al leer los mensajes GOOSE por medio de la CPU de actividades en tiempo real, donde el segundo umbral preestablecido es menor que el primer umbral preestablecido.

llustrativamente, cuando el número de mensajes GOOSE en el clip de memoria intermedia de recepción es menor que el primer umbral preestablecido, al leer los mensajes GOOSE por medio de la CPU de actividades en tiempo real, aunque el número de mensajes GOOSE en el clip de memoria intermedia de recepción en ese momento sea un

valor normal, sigue existiendo un número mayor de mensajes GOOSE. Además, se generan en poco tiempo muchos mensajes GOOSE y se almacenan en el clip de memoria intermedia de recepción debido a fallos en el lado de los dispositivos integrados de unidad de fusión y terminal inteligente 20. Por lo tanto, la CPU de actividades en tiempo real puede interrumpir de nuevo la tarea actual y, por lo tanto, la ejecución de la tarea actual interrumpida se puede reanudar solamente cuando el número de mensajes GOOSE en el clip de memoria intermedia de recepción es menor que el segundo umbral preestablecido, al leer los mensajes GOOSE por medio de la CPU de actividades en tiempo real. Se debe entender que el segundo umbral preestablecido es un valor numérico menor que el primer umbral preestablecido. Dado que la ejecución de la tarea actual interrumpida se puede reanudar solamente cuando el número de mensajes GOOSE en el clip de memoria intermedia de recepción es menor que el segundo umbral preestablecido, al leer los mensajes GOOSE por medio de la CPU de actividades en tiempo real, la CPU de actividades en tiempo real puede leer un gran número de mensajes GOOSE en el clip de memoria intermedia de recepción, el número de mensajes GOOSE que permanecen en el clip de memoria intermedia de recepción es relativamente pequeño, y se puede afrontar la situación en la que se generan muchos mensajes GOOSE en poco tiempo debido a los fallos en el lado de los dispositivos integrados de unidad de fusión y terminal inteligente 20.

15 Con la solución técnica anterior, los mensajes GOOSE en el clip de memoria intermedia de recepción cuyo número de mensajes supera el valor del primer umbral preestablecido se pueden procesar preferentemente cuando se generan muchos mensajes GOOSE debido a fallos, garantizando de ese modo que los mensajes GOOSE se procesan en tiempo, garantizando la utilización normal de los clips de memoria intermedia de recepción y garantizando además una transferencia suave de datos.

#### 20 Realización IV

10

25

30

35

40

45

50

60

La realización IV de la descripción da a conocer un procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente. La realización se basa en las realizaciones anteriores, y está mejorada en base a las realizaciones anteriores. Específicamente, se describe el proceso de funcionamiento de una CPU de actividades no en tiempo real. De manera similar, haciendo referencia a la figura 2, el procedimiento de transferencia de datos basado en el sistema de protección y control para una subestación inteligente dado a conocer por la realización IV de la descripción puede incluir las etapas descritas a continuación.

La CPU de actividades no en tiempo real reúne información de notificación generada por la CPU de actividades en tiempo real en el proceso de medición y control y/o el proceso de protección, convierte direcciones MAC de los dispositivos integrados de unidad de fusión y terminal inteligente en la información de notificación en las direcciones IP de los dispositivos integrados de unidad de fusión y terminal inteligente, y transmite la información procesada a un dispositivo de nivel de estación a través de un conmutador en el servidor de potencia inteligente. La información de notificación puede ser una notificación de acción y otra información.

Ilustrativamente, la CPU de actividades en tiempo real generará la información de notificación en el proceso de medición y control y/o del proceso de protección, la información de notificación puede incluir información de medición y control y/o información de protección, las direcciones MAC de los dispositivos integrados de unidad de fusión y terminal inteligente 20 en la información de notificación se convierten en las direcciones IP de los dispositivos integrados de unidad de fusión y terminal inteligente 20, y a continuación la información de notificación se transmite al dispositivo de nivel de estación a través del conmutador en el servidor de potencia inteligente 10. Opcionalmente, el dispositivo de nivel de estación puede incluir una estación de trabajo de operador o una central de monitorización, y el servidor de potencia inteligente 10 está conectado al dispositivo de nivel de estación a través del conmutador dispuesto en el mismo. Específicamente, el dispositivo de nivel de estación puede identificar las direcciones IP de los dispositivos integrados de unidad de fusión y terminal inteligente 20, mientras la recogida de la información de medición y control y de la información de protección de los dispositivos integrados de unidad de fusión y terminal inteligente 20 mediante el servidor de potencia inteligente 10 se implementa mediante un modo de identificar las direcciones MAC de los dispositivos integrados de unidad de fusión y terminal inteligente 20. Por lo tanto, el servidor de potencia inteligente 10 puede asignar la dirección IP para los dispositivos integrados de unidad de fusión y terminal inteligente 20 accedidos, la dirección IP es única, y se almacena una relación de mapeo entre las direcciones MAC de los dispositivos integrados de unidad de fusión y terminal inteligente y las direcciones IP, formando de ese modo una tabla de mapeo entre las direcciones MAC y la dirección IP. Basándose en la relación de mapeo, las direcciones MAC en la información de medición y control y la información de protección son sustituidas con correspondientes direcciones IP, y la información de medición y control y la información de protección de adquisición que lleva las direcciones IP puede ser transmitida al dispositivo de nivel de estación a través del conmutador, garantizando de ese modo que el dispositivo de nivel de estación confirma una dirección de origen de la información de medición y control y de la información de protección, y otra información de procesamiento.

Opcionalmente, la CPU de actividades no en tiempo real reúne la información de notificación generada por la CPU de actividades en tiempo real en el proceso de medición y control y/o el proceso de protección, y se generan mensajes MMS y son transmitidos al dispositivo de nivel de estación a través del conmutador en el servidor de potencia inteligente 10.

Específicamente, la CPU de actividades en tiempo real genera la información de notificación en el proceso de medición y control y/o el proceso de protección de acuerdo con mensajes procedentes de los dispositivos integrados

de unidad de fusión y terminal inteligente 20, y añade las direcciones MAC de los dispositivos integrados de unidad de fusión y terminal inteligente 20 a la información de notificación. Cuando se implementa la función de telecontrol, la CPU de actividades no en tiempo real reúne la información de notificación generada en el proceso de medición y control y/o en el proceso de protección, convierte las direcciones MAC de los dispositivos integrados de unidad de fusión y terminal inteligente 20 en las direcciones IP a transportar en los mensajes MMS, y transmite las direcciones IP al dispositivo de nivel de estación, de tal modo que el dispositivo de nivel de estación puede gestionar los dispositivos integrados de unidad de fusión y terminal inteligente 20 de acuerdo con las direcciones IP de los dispositivos integrados de unidad de fusión y terminal inteligente 20. Por ejemplo, cada vez que se termina una operación de control, el servidor de potencia inteligente 10 transmitirá después una notificación de mensaje para notificar un resultado de la presente operación al dispositivo de nivel de estación, tal como una notificación de terminación de operación de control. Después de procesar los mensajes GOOSE, el servidor de potencia inteligente 10 transmite una notificación de señal de acción, tal como una acción diferencial en cascada.

Con la solución técnica anterior, la CPU de actividades no en tiempo real convierte las direcciones MAC de los dispositivos integrados de unidad de fusión y terminal inteligente en la información de notificación en las direcciones IP, garantizando de ese modo la gestión del dispositivo de nivel de estación sobre los dispositivos integrados de unidad de fusión y terminal inteligente. El servidor de potencia inteligente asigna una dirección IP única al dispositivo integrado de unidad de fusión y terminal inteligente que accede a la subestación inteligente, convirtiendo las direcciones MAC en la dirección IP, de tal modo que se puede llevar a cabo control en la nube y mantenimiento en la nube de la subestación, disponiendo de ese modo una base técnica para el desarrollo de grandes datos de energía e internet de energía.

Opcionalmente, el procedimiento de transferencia de datos puede incluir además:

10

15

20

30

50

55

comandos de control remoto transmitidos desde el dispositivo de nivel de estación son recibidos por la CPU de actividades no en tiempo real a través del conmutador en el servidor de potencia inteligente 10; y

los comandos de control remoto, después de ser procesados y convertidos, son transmitidos por la CPU de actividades no en tiempo real a los dispositivos integrados de unidad de fusión y terminal inteligente 20 a través del chip de acceso FPGA 101.

Ilustrativamente, la CPU de actividades no en tiempo real puede estar configurada adicionalmente para recibir comandos de control remoto transmitidos desde el dispositivo de nivel de estación a los dispositivos integrados de unidad de fusión y terminal inteligente 20 a través del conmutador en el servidor de potencia inteligente 10, y transmitir los comandos de control remoto a los dispositivos integrados de unidad de fusión y terminal inteligente 20 a través del chip de acceso FPGA 101 en el servidor de potencia inteligente 10 después de que los comandos de control remoto sean procesados y convertidos, garantizando de ese modo el control remoto del dispositivo de nivel de estación en los dispositivos integrados de unidad de fusión y terminal inteligente 20, y llevando a cabo además la función de telecontrol del servidor de potencia inteligente.

35 Opcionalmente, el procedimiento de transferencia de datos puede incluir además:

el chip de acceso FPGA 101 remite los mensajes SV o mensajes GOOSE recibidos desde cada dispositivo integrado de unidad de fusión y terminal inteligente 20 a un analizador de red a través del conmutador en el servidor de potencia inteligente 10.

Ilustrativamente, el analizador de red y el servidor de potencia inteligente 10 están dispuestos por separado en la subestación inteligente, y el chip de acceso FPGA 101 puede remitir los mensajes SV o mensajes GOOSE recibidos desde cada dispositivo integrado de unidad de fusión y terminal inteligente 20 al analizador de red por medio del conmutador en el servidor de potencia inteligente 10, llevando a cabo de ese modo la función de análisis de red de la subestación inteligente.

Opcionalmente, el procedimiento de transferencia de datos puede incluir además:

el chip de acceso FPGA 101 remite los mensajes SV o mensajes GOOSE recibidos desde cada dispositivo integrado de unidad de fusión y terminal inteligente 20 a un registro de fallos a través del conmutador en el servidor de potencia inteligente 10.

Ilustrativamente, el registro de fallos y el servidor de potencia inteligente 10 están dispuestos por separado en la subestación inteligente, y el chip de acceso FPGA 101 puede remitir los mensajes SV o los mensajes GOOSE recibidos desde cada dispositivo integrado de unidad de fusión y terminal inteligente 20 a un registro de fallos a través del conmutador en el servidor de potencia inteligente 10, llevando a cabo de ese modo una función de registro de fallos de la subestación inteligente.

Se debe observar que los terminales inteligentes en los dispositivos integrados de unidad de fusión y terminal inteligente son conjuntos inteligentes. Los terminales inteligentes están conectados a dispositivos principales, tales como un disyuntor, un conmutador de cuchillas y un transformador principal y similares, a través de cables, y conectados a dispositivos secundarios para protección, medición y control, y similares, a través de fibra óptica, para

# ES 2 750 803 T3

conseguir una función de medición, una función de control y similares, sobre los dispositivos principales. Específicamente, los terminales inteligentes tienen principalmente las funciones siguientes:

recibir instrucciones de control para protección de desconexión, y desconexión;

recibir y ejecutar funciones de control de apertura/cierre desde un dispositivo de medición y control;

5 cargar señales de posición de conmutadores de cuchillas; reunir y cargar datos de temperatura/datos de humedad.

Se debe observar que las descripciones anteriores son solamente ejemplos y principios técnicos utilizados de la descripción. La invención se define mediante las reivindicaciones independientes adjuntas. Se definen realizaciones adicionales mediante las reivindicaciones dependientes.

### **REIVINDICACIONES**

1. Un procedimiento de transferencia de datos basado en un sistema de protección y control para una subestación inteligente, en el que los dispositivos integrados de unidad de fusión y terminal inteligente para todas las bahías en la subestación inteligente acceden directamente a un servidor de potencia inteligente, cada uno de los dispositivos integrados de unidad de fusión y terminal inteligente accede a uno de los puertos de transporte de un chip de acceso de matriz de puertas programables in situ FPGA en el servidor de potencia inteligente a través de una conexión física, y los dispositivos integrados de unidad de fusión y terminal inteligente y los puertos de transporte están en una relación de correspondencia unívoca, en el que el servidor de potencia inteligente está configurado para realizar todas las funciones de medición y control, protección, conmutación y telecontrol en la subestación inteligente, y el procedimiento comprende:

10

15

30

35

40

en un periodo de recepción de un procesador central de actividades en tiempo real del servidor de potencia inteligente, leer, mediante el procesador central de actividades en tiempo real, por lo menos uno de los mensajes SV de valores muestreados y mensajes de eventos de subestación genéricos orientados a objetos GOOSE transmitidos por cada uno de los dispositivos integrados de unidad de fusión y terminal inteligente desde cada clip de memoria intermedia de recepción del chip de acceso FPGA, en el que los mensajes SV o los mensajes GOOSE son recibidos desde cada uno de los puertos de transporte por el chip de acceso FPGA, sometidos a procesamiento SV o procesamiento GOOSE, y a continuación escritos en correspondientes clips de memoria intermedia de recepción en una memoria intermedia de recepción (S210), donde los clips de memoria intermedia de recepción y los puertos de transporte están en una relación de correspondencia unívoca;

- en un periodo de transmisión del procesador central de actividades en tiempo real, emitir, mediante el procesador central de actividades en tiempo real, información de indicación generada, por lo menos, en uno de un proceso de medición y control y un proceso de protección al chip de acceso FPGA, haciendo que el chip de acceso FPGA genere los mensajes GOOSE de acuerdo con la información de indicación y escriba los mensajes GOOSE en una memoria intermedia de transmisión del chip de acceso FPGA (S220):

- en el que la etapa de leer, mediante el procesador central de actividades en tiempo real, por lo menos uno de los mensajes SV y mensajes GOOSE transmitidos por cada uno de los dispositivos integrados de unidad de fusión y terminal inteligente desde cada clip de memoria intermedia de recepción del chip de acceso FPGA, comprende:

- leer (S310), mediante el procesador central de actividades en tiempo real, mensajes desde cada clip de memoria intermedia de recepción de acuerdo con un orden descendente del número total de mensajes en cada clip de memoria intermedia de recepción, donde el chip de acceso FPGA notifica el número total de mensajes en cada clip de memoria intermedia de recepción al procesador central de actividades en tiempo real en el periodo de recepción.

- 2. El procedimiento de transferencia de datos según la reivindicación 1, en el que la etapa de leer, mediante el procesador central de actividades en tiempo real, por lo menos uno de mensajes SV y mensajes GOOSE transmitidos por cada uno de los dispositivos integrados de unidad de fusión y terminal inteligente desde cada clip de memoria intermedia de recepción del chip de acceso FPGA, comprende además:

interrumpir una tarea actual y leer los mensajes GOOSE desde un clip de memoria intermedia de recepción en el que el número de mensajes GOOSE supera un primer umbral preestablecido cuando un mensaje de notificación transmitido por el chip de acceso FPGA es recibido por el procesador central de actividades en tiempo real, en el que el mensaje de notificación es transmitido por el chip de acceso FPGA si el número de mensajes GOOSE escrito en el clip de memoria intermedia de recepción supera el primer umbral preestablecido.

- 3. El procedimiento de transferencia de datos según la reivindicación 2, en el que la ejecución de la tarea actual interrumpida se reanuda si el número de mensajes GOOSE en el clip de memoria intermedia de recepción es menor que el primer umbral preestablecido, al leer los mensajes GOOSE por medio del procesador central de actividades en tiempo real.

- 4. El procedimiento de transferencia de datos según la reivindicación 2, en el que la ejecución de la tarea actual interrumpida se reanuda si el número de mensajes GOOSE en el clip de memoria intermedia de recepción es menor que un segundo umbral preestablecido, al leer los mensajes GOOSE por medio del procesador central de actividades en tiempo real, en el que el segundo umbral preestablecido es menor que el primer umbral preestablecido.

- 5. El procedimiento de transferencia de datos según cualquiera de las reivindicaciones 1 a 4, en el que la memoria intermedia de transmisión del chip de acceso FPGA comprende una serie de clips de memoria intermedia de transmisión, en el que los clips de memoria intermedia de transmisión y los puertos de transporte están en una relación de correspondencia unívoca, y la etapa de hacer que el chip de acceso FPGA genere los mensajes GOOSE de acuerdo con la información de indicación y escriba los mensajes GOOSE en una memoria intermedia de transmisión del chip de acceso FPGA (S220) comprende:

## ES 2 750 803 T3

por medio del chip de acceso FPGA, generar los mensajes GOOSE de acuerdo con la información de indicación y escribir los mensajes GOOSE en correspondientes clips de memoria intermedia de transmisión de acuerdo con una dirección de control de acceso al medio MAC de destino en los mensajes GOOSE.

6. El procedimiento de transferencia de datos según cualquiera de las reivindicaciones 1 a 5, en el que la duración del periodo de recepción del procesador central de actividades en tiempo real es mayor que la duración del periodo de transmisión.

5

- 7. El procedimiento de transferencia de datos según cualquiera de las reivindicaciones 1 a 6, que comprende además:

- reunir, mediante un procesador central de actividades no en tiempo real, información de notificación generada mediante el procesador central de actividades en tiempo real en, por lo menos, uno del proceso de medición y control y el proceso de protección, convertir direcciones MAC de los dispositivos integrados de unidad de fusión y terminal inteligente en la información de notificación en direcciones IP de protocolo de red de los dispositivos integrados de unidad de fusión y terminal inteligente, y transmitir la información de notificación a un dispositivo de nivel de estación a través de un conmutador en el servidor de potencia inteligente.

- 15 8. El procedimiento de transferencia de datos según cualquiera de las reivindicaciones 1 a 7, que comprende además:

- recibir, mediante un procesador central de actividades no en tiempo real, comandos de control remoto transmitidos por el dispositivo de nivel de estación a través del conmutador en el servidor de potencia inteligente;

- transmitir los comandos de control remoto, después de que son procesados y convertidos por el procesador central de actividades no en tiempo real, a los dispositivos integrados de unidad de fusión y terminal inteligente a través del chip de acceso FPGA.

- 9. El procedimiento de transferencia de datos según cualquiera de las reivindicaciones 1 a 8, que comprende además:

- remitir, mediante el chip de acceso FPGA, por lo menos uno de los mensajes SV y mensajes GOOSE recibidos desde cada uno de los dispositivos integrados de unidad de fusión y terminal inteligente a un analizador de red a través del conmutador en el servidor de potencia inteligente.

- 10. El procedimiento de transferencia de datos según la reivindicación 6, 7 o 8, que comprende además:

- remitir, mediante el chip de acceso FPGA, por lo menos uno de los mensajes SV y mensajes GOOSE recibidos desde cada uno de los dispositivos integrados de unidad de fusión y terminal inteligente a un registro de fallos a través del conmutador en el servidor de potencia inteligente.

## FIG1

FIG.2

El chip de acceso FPGA 101 genera los mensajes GOOSE de acuerdo con la información de indicación generada por la CPU de actividades en tiempo real en el proceso de medición y control y/o el proceso de protección, y escribe los mensajes en correspondientes clips de memoria intermedia de transmisión de acuerdo con la dirección MAC (control de acceso al medio) de destino en los mensajes GOOSE.

FIG.3