OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 751 157

61 Int. Cl.:

G06F 12/04 (2006.01) G06F 12/06 (2006.01) G06F 3/06 (2006.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

T3

Fecha de presentación y número de la solicitud europea: 01.06.2016 E 16172469 (5)

Fecha y número de publicación de la concesión europea: 31.07.2019 EP 3118746

(54) Título: Aparato de acceso a datos que usa un dispositivo de memoria

(30) Prioridad:

13.07.2015 KR 20150098851

Fecha de publicación y mención en BOPI de la traducción de la patente: **30.03.2020**

73) Titular/es:

LSIS CO., LTD. (100.0%) LS Tower, 127, LS-ro, Dongan-gu, Anyang-si Gyeonggi-do 14119, KR

(72) Inventor/es:

PARK, TAE-BUM

(74) Agente/Representante:

SÁNCHEZ SILVA, Jesús Eladio

#### **DESCRIPCIÓN**

Aparato de acceso a datos que usa un dispositivo de memoria

#### 5 Antecedentes

35

40

45

50

55

60

#### 1. Campo técnico

La presente invención se refiere a un aparato de acceso a datos, y más particularmente, a un aparato de acceso a datos que usa un dispositivo de memoria, capaz de permitir que se lean/escriban fácilmente datos de 16 bits o más usando un dispositivo de memoria de 8 bits.

#### 2. Descripción de la técnica relacionada

- 15 En general, una CPU (unidad de procesamiento central), que ejecuta el control general de un sistema de control electrónico, realiza un proceso de acceso de lectura o escritura de datos desde o hacia un dispositivo de memoria como dispositivo de almacenamiento.

- Es decir, el proceso de acceso de lectura/escritura de datos desde/hacia el dispositivo de memoria es realizado principalmente por la CPU. En consecuencia, la operación de lectura o escritura significa que la lectura o escritura se realiza sobre la base de la CPU. La operación de lectura se refiere a llevar datos en el dispositivo de memoria a la CPU, y la operación de escritura se refiere a transmitir datos desde la CPU al dispositivo de memoria.

- Los principios generales para leer/escribir datos desde/hacia un dispositivo de memoria se describen en los documentos EP 0022622 A1, US 2004/136273 A1 y US 6226736 B1. "DSP56300 Family Manual: Capítulo 10 Controlador DMA", 2 de abril de 2002 (2002-04-02), XP055448478, describe el uso del empaquetado de bytes cuando un núcleo DSP de ancho de datos de 24 bits se interconecta con un dispositivo de memoria externa de 8 bits de ancho. Mientras tanto, un sistema inversor solar, que ha estado en el centro de atención recientemente entre los sistemas de control electrónico, es un sistema que genera electricidad al convertir la energía de CC suministrada desde un módulo solar en energía de CA.

Cuando se opera el sistema inversor solar, se almacena una variedad de tipos de información, como un voltaje, una corriente y una cantidad de generación de energía en un dispositivo de memoria y la información almacenada en el dispositivo de memoria se almacena en dispositivos externos (por ejemplo, un dispositivo de monitoreo) a través de la comunicación.

La cantidad de generación de energía en el sistema inversor solar son datos muy importantes, y la cantidad acumulada de generación de energía (es decir, la cantidad total de generación de energía hasta la fecha desde que el sistema inversor solar genera electricidad) es información muy importante para un usuario.

Mientras tanto, los dispositivos de memoria existentes de 8 y 16 bits pueden grabar al máximo 256 y 65,536 palabras de datos, respectivamente. Estas capacidades de los dispositivos de memoria son demasiado pequeñas para mostrar la cantidad acumulada de generación de energía en megawatts. Por lo tanto, se debe usar al menos un dispositivo de memoria de 24 bits (que registra al máximo 16,777,216 palabras de datos) para mostrar la cantidad acumulada de generación de energía en megawatts. Por lo tanto, existe la necesidad del método de almacenamiento de datos de 24 bits en el dispositivo de memoria comercial de 8 bits.

Debido al reciente desarrollo de métodos y dispositivos de comunicación, la cantidad de datos, que pueden transferirse al dispositivo externo del sistema inversor solar a la vez, aumenta como en datos de 8 bits, 16 bits o 24 bits. Además, la cantidad de datos transferidos al usuario a través de la comunicación aumenta gradualmente. Sin embargo, no se produce un deterioro de la velocidad de comunicación.

Sin embargo, los dispositivos de memoria de 8 bits (en particular, los dispositivos de memoria no volátiles) se utilizan principalmente para almacenar datos intercambiados a través de la comunicación, y los dispositivos de memoria de 24 bits son caros.

Además, dado que el dispositivo de memoria comercial de 8 bits debe usarse cuando se leen/escriben datos importantes desde/en el dispositivo de memoria en el sistema inversor solar, el volumen de datos está limitado a 8 bits. Además, se debe comprar un dispositivo de memoria de 24 bits en el mercado para poder leer/escribir datos de 24 bits, pero el dispositivo de memoria de 24 bits es costoso.

El dispositivo de memoria de 8 bits (los dispositivos de memoria comerciales) se utiliza principalmente en el sistema inversor solar. El dispositivo de memoria de 8 bits generalmente se usa y es barato.

Cuando se almacenan datos importantes (por ejemplo, una cantidad acumulada de generación de energía) del sistema inversor solar utilizando el dispositivo de memoria comercial de 8 bits, solo se pueden almacenar datos de 8

bits debido a la capacidad limitada (8 bits) del dispositivo de memoria.

#### Resumen

15

25

50

55

- La presente invención se define en las reivindicaciones independientes adjuntas a las que debe hacerse referencia. Las características ventajosas se exponen en las reivindicaciones dependientes adjuntas. Las modalidades o ejemplos de la siguiente descripción que no están cubiertos por las reivindicaciones adjuntas se consideran como no parte de la invención de acuerdo con esta descripción.

- 10 Es un aspecto de la presente invención proporcionar un aparato de acceso a datos que usa un dispositivo de memoria, capaz de permitir que se lean/escriban fácilmente datos de 16 bits o más usando un dispositivo de memoria de 8 bits.

- La presente invención no se limita al aspecto anterior y los expertos en la materia comprenderán claramente otros aspectos de la presente invención a partir de la siguiente descripción.

- De acuerdo con un aspecto de la presente invención, un aparato de acceso a datos de acuerdo con la invención se define en la reivindicación 1.

- El aparato de acceso a datos puede incluir además una unidad de restauración de datos para restaurar datos originales de M bits combinando el primero a N-ésimo segmentos de datos almacenados en las direcciones del dispositivo de memoria mapeado con las respectivas direcciones específicas en el primero a N-ésima regiones.

- La unidad de mapeo de direcciones puede dividir las direcciones del dispositivo de memoria en N partes de acuerdo con la configuración de un usuario, de modo que las N partes se definan como primero a N-ésima regiones.

- Las respectivas direcciones específicas en la primera a N-ésima regiones pueden ubicarse en el mismo orden en las regiones de la primera a la N-enésima regiones, respectivamente.

- El dispositivo de memoria puede ser un dispositivo de memoria de 8 bits, y el aparato de acceso a datos puede realizarse en cualquiera de los casos de N = 2 y M = 16, N = 3 y M = 24, y N = 4 y M = 32.

Breve descripción de los dibujos

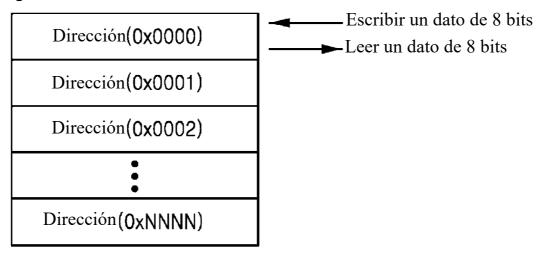

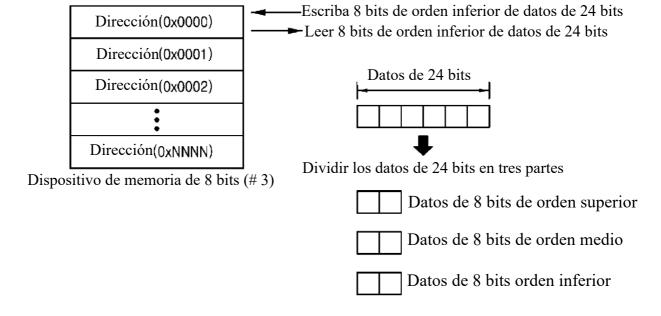

- La Figura 1 es un diagrama para explicar un método de lectura/escritura de datos de 8 bits desde/en un dispositivo de memoria de 8 bits de acuerdo con la técnica relacionada.

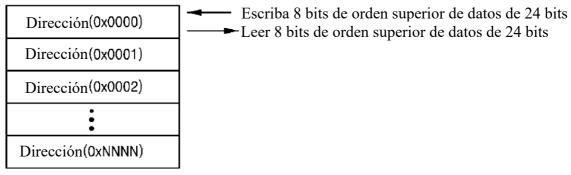

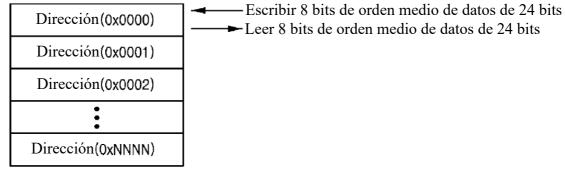

- La Figura 2 es un diagrama para explicar un método de lectura/escritura de datos de 24 bits usando una pluralidad de dispositivos de memoria de 8 bits de acuerdo con la técnica relacionada.

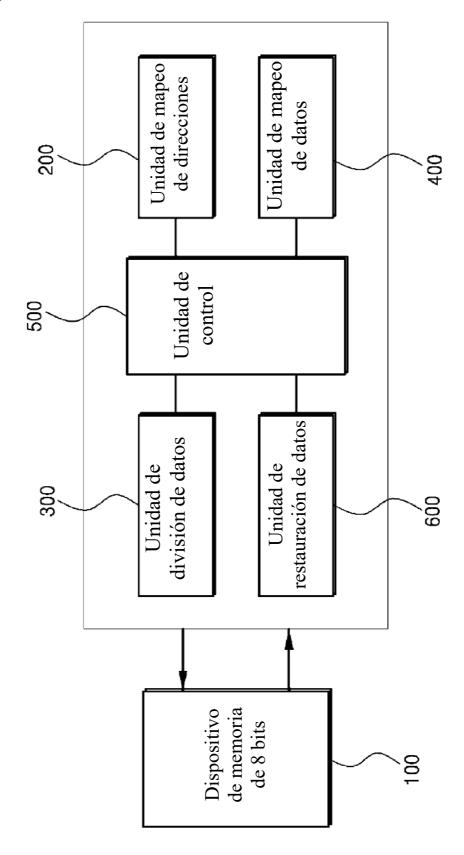

- La Figura 3 es un diagrama de bloques para explicar un aparato de acceso a datos que usa un dispositivo de memoria según una modalidad de la presente invención.

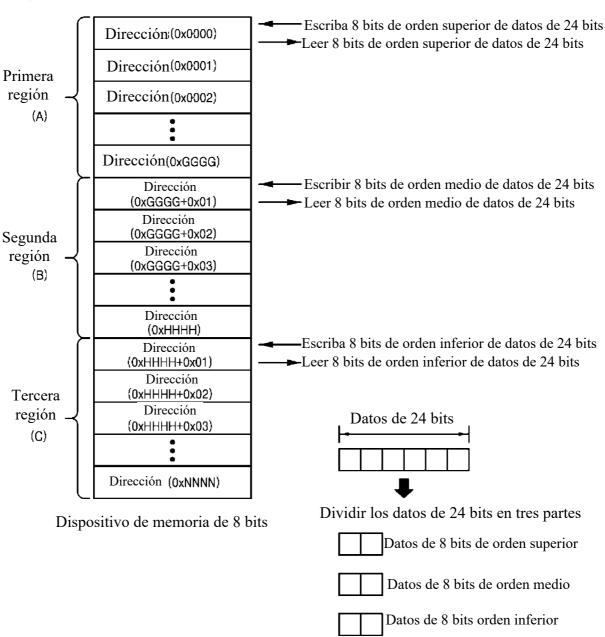

- La Figura 4 es un diagrama para explicar un método de lectura/escritura de datos de 24 bits usando un dispositivo de memoria de 8 bits de acuerdo con la modalidad de la presente invención.

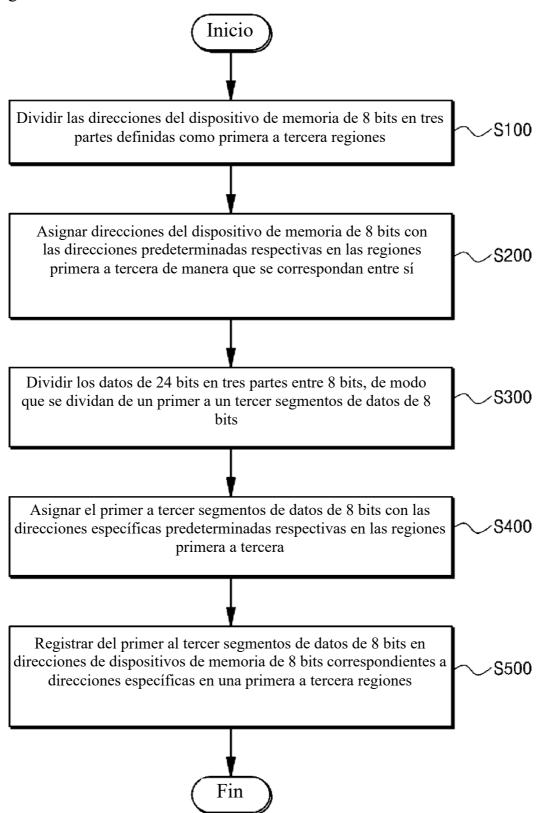

- La Figura 5 es un diagrama de flujo que ilustra un método de acceso a datos usando el dispositivo de memoria según la modalidad de la presente invención.

- 45 Descripción detallada

- A continuación, se describirán en detalle modalidades ilustrativas de la presente invención con referencia a los dibujos adjuntos. Debe entenderse que la presente invención no se limita a las siguientes modalidades, y que las modalidades se proporcionan únicamente con fines ilustrativos. El alcance de la invención debe definirse solo por las reivindicaciones adjuntas y sus equivalentes.

- Las modalidades ilustrativas de la presente invención se describirán a continuación con más detalle con referencia a los dibujos adjuntos. Sin embargo, la presente invención puede realizarse de diferentes formas y no debe interpretarse como limitada a las modalidades establecidas en el presente documento. Más bien, estas modalidades se proporcionan de modo que esta divulgación sea exhaustiva y completa, y transmitirá completamente el alcance de la presente invención a los expertos en la materia. A lo largo de la descripción, los números de referencia similares se refieren a partes similares en las diversas figuras y modalidades de la presente invención.

- La Figura 1 es un diagrama para explicar un método de lectura/escritura de datos de 8 bits desde/en un dispositivo de memoria de 8 bits de acuerdo con la técnica relacionada. Un dispositivo de memoria de 8 bits tiene direcciones de 0x0000 a 0xNNNN. En consecuencia, los datos de 8 bits se escriben y almacenan en cada dirección del dispositivo de memoria, y se leen a partir de ellos si es necesario.

- La Figura 2 es un diagrama para explicar un método de lectura/escritura de datos de 24 bits usando una pluralidad de dispositivos de memoria de 8 bits de acuerdo con la técnica relacionada. Por ejemplo, se deben usar tres dispositivos de memoria de 8 bits cuando sea necesario almacenar datos de 24 bits en un sistema inversor solar.

Los datos de 24 bits destinados a ser almacenados en los dispositivos de memoria de 8 bits en el sistema inversor solar se dividen en tres partes, es decir, tres segmentos de datos de 8 bits. A continuación, los tres segmentos divididos de datos de 8 bits se escriben respectivamente en los dispositivos de memoria de 8 bits y se leen a partir de ellos si es necesario.

Sin embargo, la técnica relacionada es problemática porque los datos almacenables en el sistema inversor solar están limitados a 8 bits, 24 bits, etc., de acuerdo con las capacidades respectivas (8 bits, 24 bits, etc.) de los dispositivos de memoria que se utilizarán. Es decir, hay problemas porque el volumen de datos que se puede leer/escribir desde/en los dispositivos de memoria que se utilizarán se determina de acuerdo con las capacidades de los mismos, y los dispositivos comerciales de memoria de 8 y 16 bits son caros.

Además, los datos de 24 bits no pueden almacenarse en el dispositivo de memoria comercial de 8 bits. Si los datos de 24 bits se almacenan utilizando cualquier dispositivo de memoria de 8 bits, se deben usar tres dispositivos de memoria de 8 bits como se ilustra en la Figura 2, lo que puede conducir a un aumento en el costo.

Para resolver los problemas mencionados anteriormente, la técnica de la presente invención se caracteriza porque los datos de 16 bits o más se leen/escriben fácilmente utilizando un dispositivo de memoria de 8 bits, por ejemplo, utilizado en un sistema inversor solar.

De acuerdo con un aparato de acceso a datos que usa un dispositivo de memoria de acuerdo con una modalidad de la presente invención, es posible resolver el problema en que los datos almacenables en el sistema inversor solar de la técnica relacionada están limitados a 8 bits, 24 bits, etc. de acuerdo con las capacidades respectivas (8 bits, 24 bits, etc.) de los dispositivos de memoria utilizados en el mismo. Además, es posible resolver el problema porque el volumen de datos que pueden leerse/escribirse desde/en los dispositivos de memoria a utilizar se determina de acuerdo con las capacidades de los mismos.

Es decir, la presente invención puede acceder a un gran volumen de datos (por ejemplo, 16 bits, 24 bits o 32 bits) a un dispositivo de memoria que es barato y tiene una capacidad pequeña (8 bits), y efectivamente reduce los costos.

La Figura 3 es un diagrama de bloques para explicar un aparato de acceso a datos que usa un dispositivo de memoria según una modalidad de la presente invención. La Figura 4 es un diagrama para explicar un método de lectura/escritura de datos de 24 bits usando un dispositivo de memoria de 8 bits de acuerdo con la modalidad de la presente invención.

Con referencia a las Figuras 3 y 4, el aparato de acceso a datos que usa un dispositivo de memoria de acuerdo con la modalidad de la presente invención incluye en gran medida un dispositivo de memoria de 8 bits 100, una unidad de mapeo de direcciones 200, una unidad de división de datos 300, una unidad de mapeo de datos 400 y un unidad de control 500.

Aquí, el dispositivo de memoria de 8 bits 100 puede ser un IC (circuito integrado) que tiene una pluralidad de direcciones (por ejemplo, direcciones de 0x0000 a 0xNNNN) de modo que los datos de 8 bits pueden leerse o escribirse.

45 El dispositivo de memoria de 8 bits 100 tiene una dirección que designa cada posición de datos y un bus de datos como cada canal de transferencia de datos. En el caso en que la unidad de control 500 lea los datos, cuando la dirección de los datos a leer se transfiera al dispositivo de memoria de 8 bits 100, el dispositivo de memoria de 8 bits 100 carga datos en la dirección designada en el bus de datos que la unidad de control 500 lee los datos. En el caso en que se escriben datos, cuando se transfiere una dirección específica al dispositivo de memoria de 8 bits 100, los datos se 50 escriben en la dirección asociada del dispositivo de memoria de 8 bits 100.

La unidad de control 500 envía la dirección como la información de posición del dispositivo de memoria de 8 bits 100 a un bus de direcciones. Cuando el dispositivo de memoria de 8 bits 100 recibe información sobre la dirección, los datos se leen o escriben desde o en la dirección asociada.

Mientras tanto, el dispositivo de memoria de 8 bits 100 puede mantener continuamente la información de datos almacenados aunque no se suministre energía al mismo. Es preferible que el dispositivo de memoria de 8 bits 100 sea una memoria no volátil (NVM o NVRAM) en la que se puede realizar una operación de lectura/escritura. La memoria no volátil puede ser, por ejemplo, una ROM, una EEPROM (memoria de solo lectura programable y borrable eléctricamente), una memoria flash, una memoria de cambio de fase, una memoria resistiva y una memoria magnética.

La unidad de mapeo de direcciones 200 divide las direcciones del dispositivo de memoria de 8 bits 100 en tres partes definidas como primera a tercera regiones A a C. Luego, la unidad de mapeo de direcciones 200 mapea las direcciones (0x0000 a 0xNNNN) de la memoria de 8 bits dispositivo 100 y direcciones predeterminadas respectivas (0x000 a 0xGGGG, 0xGGGG + 0x01 a 0xHHHH, y 0xHHHH + 0x01 a 0xNNNN) en las primera a tercera regiones A a C de manera que se correspondan entre sí.

4

20

5

10

15

30

25

40

35

55

60

65

Como se ilustra en la Figura 4, es preferible que la unidad de mapeo de direcciones 200 divida las direcciones del dispositivo de memoria de 8 bits 100 en tres partes en el orden de las direcciones para que las partes se definan como primera a tercera regiones A a C, pero la presente invención no está limitada a los mismos. Por ejemplo, las direcciones del dispositivo de memoria de 8 bits 100 pueden dividirse aleatoriamente en tres partes definidas como primera a tercera regiones A a C.

La unidad de división de datos 300 divide los datos de 24 bits en tres partes por 8 bits, de modo que se divide del primer al tercer segmentos de datos de 8 bits.

10

15

5

Como se ilustra en la Figura 4, es preferible que la unidad de división de datos 300 divida secuencialmente datos de 24 bits en datos de 8 bits de orden superior, datos de 8 bits de orden medio y datos de 8 bits de orden inferior por 8 bits de manera que se divide en primer a tercer segmentos de datos de 8 bits, pero la presente invención no se limita a los mismos. Por ejemplo, los datos de 24 bits pueden dividirse aleatoriamente en tres partes, como por ejemplo, primer a tercer segmentos de datos de 8 bits.

La unidad de mapeo de datos 400 mapea los primer a tercer segmentos de datos de 8 bits, divididos por la unidad de división de datos 300, y con las direcciones específicas predeterminadas respectivas en las primera a tercera regiones A a C definidas por la unidad de mapeo de direcciones 200.

20

En este caso, es preferible que las direcciones específicas respectivas en las regiones de la primera a la tercera A a C definidas por la unidad de mapeo de direcciones 200 sean direcciones ubicadas en el mismo orden. Por ejemplo, cuando los primeros datos de 8 bits se asignan en la dirección de "0x0000" que se encuentra primero en la primera región A, los segundos datos de 8 bits y los terceros datos de 8 bits se asignan respectivamente en las direcciones de 0xGGGG + 0x01 y 0xHHHH + 0x01 que se encuentran primero en las respectivas segunda y tercera regiones B y C.

25

Mientras tanto, las direcciones específicas respectivas en las regiones de la primera a la tercera A a C definidas por la unidad de mapeo de direcciones 200 pueden ser direcciones ubicadas en un orden diferente o aleatorio de acuerdo con la configuración del usuario.

30

La unidad de control 500 realiza una función de control de manera que los primer a tercer segmentos de datos de 8 bits, divididos por la unidad de división de datos 300, se almacenan en las direcciones del dispositivo de memoria de 8 bits 100 mapeado con las respectivas direcciones específicas en la primera a tercera regiones A a C definidas por la unidad de mapeo de direcciones 200.

35

La presente invención puede incluir además una unidad de restauración de datos 600 que restaura los datos originales de 24 bits combinando los primer a tercer segmentos de datos de 8 bits almacenados en las direcciones del dispositivo de memoria de 8 bits 100 mapeado con las respectivas direcciones específicas en las primera a tercera regiones A a C definidas por la unidad de mapeo de direcciones 200.

40

Mientras tanto, es preferible que la unidad de mapeo de direcciones 200, la unidad de división de datos 300, la unidad de mapeo de datos 400, y la unidad de restauración de datos 600 aplicadas a la modalidad de la presente invención estén programadas a manera de software para ser operadas en la unidad de control 500 o una CPU, pero la presente invención no está limitada a la misma. Por ejemplo, la unidad de mapeo de direcciones 200, la unidad de división de datos 300, la unidad de mapeo de datos 400 y la unidad de restauración de datos 600 pueden estar separadas de la unidad de control 500 o la CPU para operar a manera de hardware.

45

50

Alternativamente, la unidad de mapeo de direcciones 200, la unidad de división de datos 300, la unidad de mapeo de datos 400, la unidad de control 500 y la unidad de restauración de datos 600 aplicada a la modalidad de la presente invención pueden incluirse en una CPU.

A continuación, se describirá en detalle un método para acceder a datos utilizando el dispositivo de memoria según la modalidad de la presente invención.

55

La Figura 5 es un diagrama de flujo que ilustra el método de acceso a datos que usa el dispositivo de memoria según la modalidad de la presente invención.

60

Con referencia a las Figuras 3 a 5, cuando los datos de 24 bits se escriben en el dispositivo de memoria de 8 bits 100 por la unidad de control 500 aplicada a la modalidad de la presente invención, las direcciones del dispositivo de memoria de 8 bits 100 se dividen primero en tres partes definidas como primera a tercera regiones A a C por la unidad de mapeo de direcciones 200 (S100).

65

En este caso, es preferible que las direcciones del dispositivo de memoria de 8 bits 100 se dividan en tres partes en el orden de las direcciones predeterminadas para que las partes se definan como primera a tercera regiones A a C (véase la Figura 4).

A continuación, las direcciones del dispositivo de memoria de 8 bits 100 se mapean con las direcciones predeterminadas respectivas en las primera a tercera regiones A a C de modo que se correspondan entre sí (S200). A continuación, los datos de 24 bits que se almacenarán se dividen en tres partes por 8 bits para que la unidad de división de datos 300 (S300) los divida en segmentos de datos de 8 bits del primero al tercer segmento.

5

En este caso, es preferible que los datos de 24 bits se dividan secuencialmente en datos de 8 bits de orden superior, datos de 8 bits de orden medio y datos de 8 bits de orden inferior por 8 bits para dividirlos primero en terceros segmentos de datos de 8 bits.

10

A continuación, los primer a tercer segmentos de datos de 8 bits divididos en la etapa S300 se mapean con las direcciones específicas predeterminadas respectivas en las primera a tercera regiones A a C definidas en la etapa S100, por la unidad de mapeo de datos 400 (S400). En este caso, es preferible que las direcciones específicas respectivas en las regiones de la primera a la tercera A a C definidas en la etapa S100 sean direcciones ubicadas en el mismo orden.

15

A continuación, los primer a tercer segmentos de datos de 8 bits divididos en la etapa S300 se almacenan en las direcciones del dispositivo de memoria de 8 bits 100 mapeado con las direcciones específicas respectivas en las primera a tercera regiones A a C definidas en la etapa S100, por la unidad de control 500 (S500).

20

Es decir, los primeros datos de 8 bits de los datos de 24 bits se almacenan en la primera región A, los segundos datos de 8 bits de los datos de 24 bits se almacenan en la segunda región B, y los terceros datos de 8 bits de los datos de 24 bits se almacenan en la tercera región C.

25

Mientras tanto, cuando los datos almacenados en el dispositivo de memoria de 8 bits 100 se leen como se describió anteriormente, la unidad de restauración de datos 600 restaura los datos originales de 24 bits combinando los primer a tercer segmentos de datos de 8 bits almacenados en las direcciones del dispositivo de memoria de 8 bits 100 mapeado con las respectivas direcciones específicas en las primera a tercera regiones A a C definidas en la etapa S100, y luego se puede realizar la operación de lectura.

30 El aparato de acceso a datos que usa un dispositivo de memoria de acuerdo con la modalidad de la presente invención se aplica preferiblemente al sistema inversor solar, pero la presente invención no se limita al mismo. Por ejemplo, el aparato de acceso a datos puede aplicarse a todas las unidades de control electrónico y sistemas que pueden acceder a los datos a las memorias sobre la base de módulos de control.

35 Además, la modalidad de la presente invención se realiza de manera que los datos de 24 bits se pueden leer o escribir desde o en un dispositivo de memoria de 8 bits, pero la presente invención no se limita a los mismos. Por ejemplo, la presente invención puede realizarse de manera que el gran volumen de datos (por ejemplo, 32 bits, 64 bits o 128 bits) se lea o escriba desde o en un dispositivo de memoria que tenga una capacidad pequeña (por ejemplo, 16 bits, 32 bits, o 64 bits).

40

Por ejemplo, la presente invención puede realizarse de manera que los datos de 16 bits se dividan en dos partes para leer o escribir desde o en un dispositivo de memoria de 8 bits, o los datos de 32 bits se dividan en cuatro partes para leer o escribir desde o en un dispositivo de memoria de 8 bits. Es decir, la presente invención puede realizarse de manera que se lean o escriban datos de 16 bits o más desde o en un dispositivo de memoria de 8 bits. Mientras tanto,

45

la presente invención puede realizarse de manera que el gran volumen de datos (por ejemplo, 32 bits, 64 bits o 128 bits) se lea o escriba desde o en un dispositivo de memoria de 16 bits o más, de manera similar a la memoria de 8 bits dispositivo. El método de modalidad específico del mismo puede realizarse de manera similar a la modalidad de la presente invención mencionada anteriormente.

50

Mientras tanto, el aparato de acceso a datos que usa un dispositivo de memoria de acuerdo con la modalidad de la presente invención puede realizarse mediante códigos legibles por computadora en medios de registro legibles por computadora. Los medios de registro legibles por computadora incluyen todos los medios de registro en los que se almacenan los datos legibles por computadora.

55 Por ejemplo, los medios de registro legibles por computadora incluyen una ROM, una RAM, un CD-ROM, una cinta magnética, un disco duro, un disquete, un dispositivo de almacenamiento móvil, una memoria flash y un dispositivo de almacenamiento óptico.

60

Además, los medios de registro legibles por computadora son distribuidos por sistemas informáticos conectados a través de la red de comunicación, y pueden almacenarse como códigos legibles en la forma de distribución y ejecutados por los códigos.

65

De acuerdo con el aparato de acceso a datos que usa un dispositivo de memoria de la presente invención, es posible leer/escribir fácilmente datos de 16 bits o más usando un dispositivo de memoria de 8 bits. En consecuencia, es posible acceder efectivamente al gran volumen de datos al dispositivo de memoria, que es barato y tiene una capacidad pequeña, y para reducir efectivamente los costos.

Como se desprende de la descripción anterior, un aparato de acceso a datos que usa un dispositivo de memoria de la presente invención puede permitir que se lean/escriban fácilmente datos de 16 bits o más usando un dispositivo de memoria de 8 bits. En consecuencia, es posible acceder efectivamente a un gran volumen de datos al dispositivo de memoria que es barato y tiene una capacidad pequeña, y reducir efectivamente los costos.

5

10

Aunque el aparato de acceso a datos que usa un dispositivo de memoria según la presente invención se ha descrito con respecto a las modalidades ilustrativas, será evidente para los expertos en la materia que se pueden realizar diversas variaciones y modificaciones sin apartarse del alcance de la invención como se define en las siguientes reivindicaciones.

#### **REIVINDICACIONES**

- Un aparato de acceso a datos que utiliza un dispositivo de memoria para mapear direcciones, que comprende: un dispositivo de memoria de 8 bits (100) que tiene una pluralidad de direcciones para que los datos se puedan leer o escribir; una unidad de división de datos (300) configurada para dividir datos de 24 bits, una unidad de mapeo de direcciones (200) configurada para

- asignar direcciones del dispositivo de memoria de 8 bits con las respectivas direcciones predeterminadas, una unidad de mapeo de datos (400) configurada para asignar segmentos de datos divididos por la unidad de división de datos con las respectivas direcciones predeterminadas, y

- una unidad de control, la unidad de división de datos (300) está configurada para dividir los datos de 24 bits en datos de 8 bits de orden superior, datos de 8 bits de orden medio y datos de 8 bits de orden inferior; caracterizado por que

- la unidad de mapeo de direcciones (200) está configurada para dividir las direcciones del dispositivo de memoria en la primera región, la segunda región y la tercera región que tienen direcciones consecutivas respectivamente, y para mapear la pluralidad de direcciones del dispositivo de memoria de 8 bits con las direcciones predeterminadas respectivas en las primera, segunda y tercera regiones de manera que se correspondan entre sí:

- la unidad de mapeo de datos (400) está configurada para mapear los datos de 8 bits de orden superior con direcciones específicas predeterminadas en la primera región, los datos de 8 bits de orden medio con direcciones específicas predeterminadas en la segunda región y los datos de 8 bits de orden inferior con direcciones específicas predeterminadas en la tercera región, en donde las direcciones específicas predeterminadas en la primera a la tercera región están ubicadas en el mismo orden en las primera a tercera regiones, respectivamente, de modo que están separadas en un intervalo de direcciones predeterminado; y la unidad de control (500) está configurada para controlar el primer a tercer segmentos de datos de manera que el primer a tercer segmentos de datos se almacena en las direcciones del dispositivo de memoria de 8 bits mapeado con las respectivas direcciones específicas en las primera a tercera regiones.

- 2. El aparato de acceso a datos según la reivindicación 1, que comprende además una unidad de restauración de datos (600) configurada para restaurar datos originales de 24 bits combinando los datos de 8 bits de orden superior, los datos de 8 bits de orden medio y los datos de 8 bits de orden inferior almacenados en las direcciones del dispositivo de memoria de 8 bits mapeado con las respectivas direcciones específicas en las primera a tercera regiones.

- 35 3. El aparato de acceso a datos de acuerdo con la reivindicación 1, en el que la unidad de mapeo de direcciones (200) está configurada para dividir las direcciones del dispositivo de memoria de 8 bits en tres partes de acuerdo con la configuración de un usuario para que las tres partes se definan como primera a tercera regiones.

Figura 1

Dispositivo de memoria de 8 bits

Dispositivo de memoria de 8 bits (# 1)

Dispositivo de memoria de 8 bits (# 2)

Figura 3

Figura 4

Figura 5