# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 754 716

51 Int. Cl.:

G01R 31/333 (2006.01) G01R 31/40 (2014.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(96) Fecha de presentación y número de la solicitud europea: 12.05.2016 E 16169381 (7)

(97) Fecha y número de publicación de la concesión europea: 28.08.2019 EP 3112886

(54) Título: Circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC

(30) Prioridad:

18.06.2015 KR 20150086910

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **20.04.2020**

(73) Titular/es:

LSIS CO., LTD. (50.0%)

127, LS-ro, Dongan-gu, Anyang-si

Gyeonggi-Do 14119, KR y

PUKYONG NATIONAL UNIVERSITY INDUSTRYUNIVERSITY COOPERATION FOUNDATION

(50.0%)

(72) Inventor/es:

BAEK, SEUNG TAEK; NHO, EUI CHEOL; JUNG, JAE HUN; LEE, JIN HEE y CHUNG, YONG HO

(74) Agente/Representante:

SÁNCHEZ SILVA, Jesús Eladio

## **DESCRIPCIÓN**

Circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC

5 Campo de la invención

10

45

55

60

65

La presente descripción se refiere a un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC (corriente continua de alto voltaje). Más particularmente, la presente descripción se refiere a un circuito de prueba sintético que aplica artificialmente corriente y voltaje similares a los que aparecen en una válvula IGBT cuando un HVDC de fuente de voltaje basado en MMC (Conversor Multinivel Modular) opera normal y anormalmente, a un módulo de válvula IGBT que es independiente de un conversor, capaz de realizar una variedad de pruebas.

Antecedentes de la invención

15 El documento US2005/0284673 A1 divulga un dispositivo de fuente de energía del vehículo.

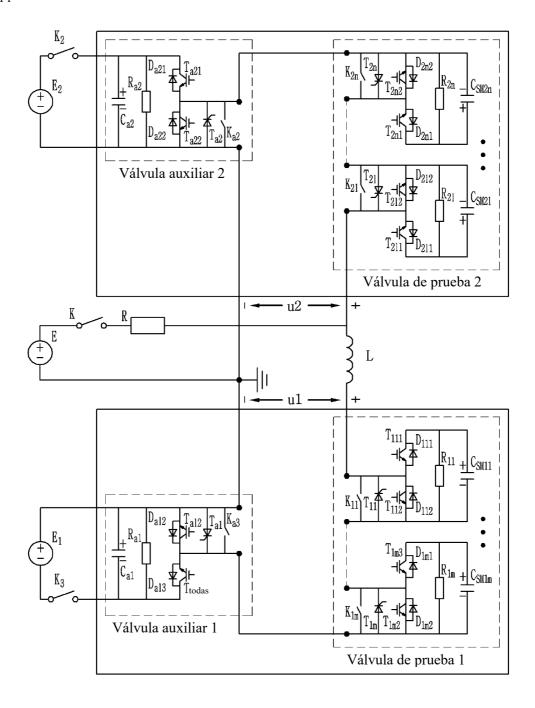

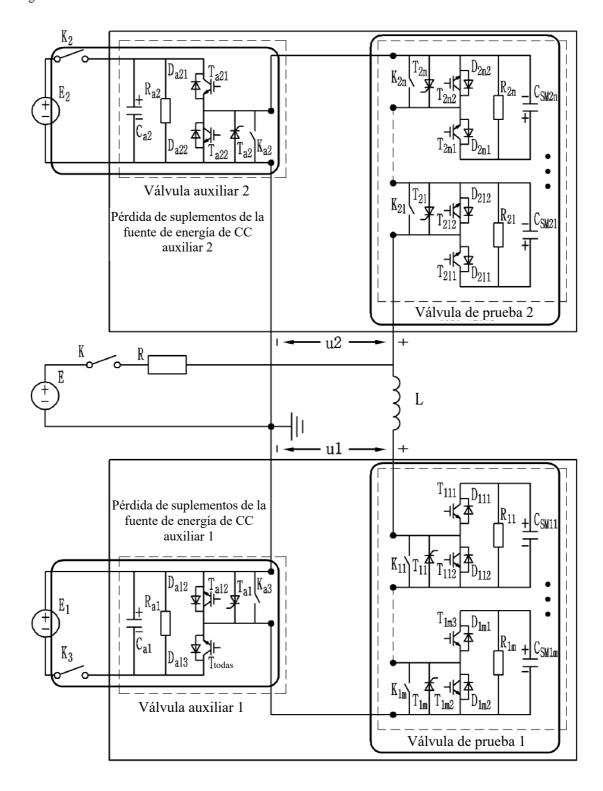

La Figura 1 es una vista que ilustra un ejemplo de un circuito de prueba sintético para una prueba de rendimiento de válvula en la técnica.

Un circuito de prueba sintético para una HVDC de fuente de voltaje ilustrado en la Figura 1 se configura de dos (2) conjuntos de válvulas de prueba (válvula de prueba 1 y válvula de prueba 2) cada una con varios submódulos conectados en serie, una fuente de energía de CC E para cargar un capacitor de la válvula de prueba, dos (2) válvulas auxiliares (válvula auxiliar 1 y válvula auxiliar 2) para complementar la pérdida ocurrida al operar el circuito de prueba sintético, dos (2) fuentes de energía de CC auxiliares (E1 y E2) para cargar un capacitor de cada válvula auxiliar, y un reactor L conectado en serie entre las válvulas de prueba para simular una corriente pseudo-sinusoidal que fluye entre las válvulas cuando realmente funciona un MMC (conversor multinivel modular).

Un submódulo se configura de un capacitor y dos (2) IGBT conectados en serie, el capacitor y dos IGBT están conectados en paralelo. La primera válvula de prueba y la segunda válvula de prueba se configuran cada una de m submódulos conectados en serie y n submódulos conectados en serie. Las válvulas auxiliares se configuran cada una de un submódulo, y para cargar el capacitor de la válvula auxiliar, cada capacitor se conecta en paralelo a una fuente de energía de CC auxiliar. El circuito de prueba sintético para una HVDC de fuente de voltaje debería ser capaz de simular una forma de onda de una corriente que fluye a través de un submódulo cuando realmente opera un MMC para la corriente que fluye a través de la válvula de prueba, de la misma manera. El sistema de la Figura 1 genera una forma de onda de corriente pseudo-sinusoidal usando una resonancia de un capacitor de una válvula de prueba y un inductor ubicado entre las válvulas de prueba respectivas, y prueba la válvula de prueba usando la forma de onda de corriente pseudo-sinusoidal.

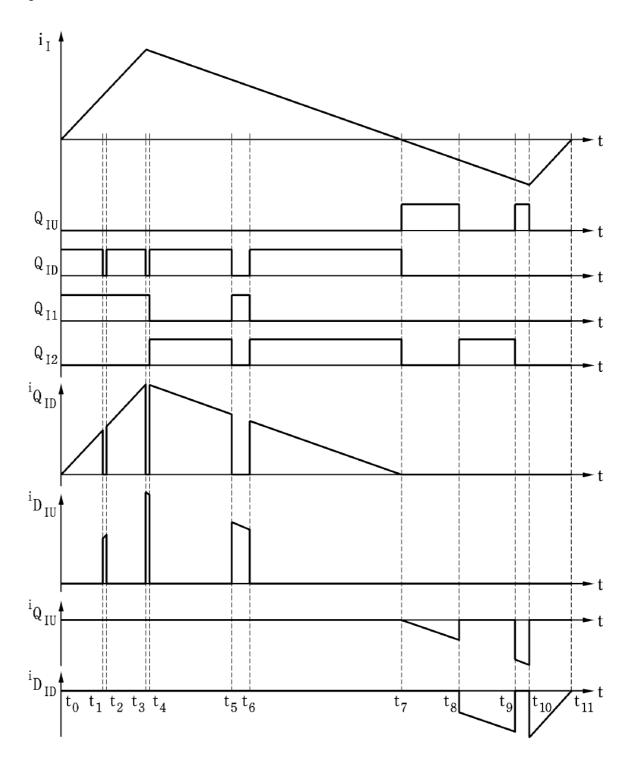

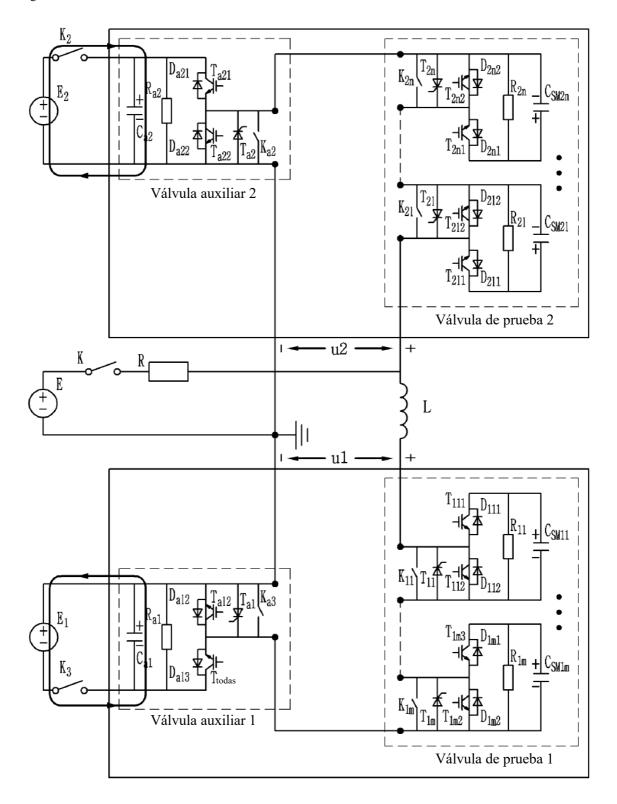

Las Figuras 2 a 4 son vistas que ilustran operaciones de circuitos de prueba sintéticos para una prueba de rendimiento de válvula en la técnica.

Con referencia a las Figuras 2 a 4, como se ilustra en la Figura 2 primero, después de configurar los voltajes de salida u1 y u2 de las válvulas de prueba que pueden generar una magnitud y una frecuencia de una corriente para simular en el circuito de prueba sintético, se carga un capacitor de una válvula auxiliar usando E1 y E2. A continuación, como se ilustra en la Figura 3, después de cargar el capacitor de la válvula de prueba usando E, todas las fuentes de energía se separan de las válvulas. Luego, como se ilustra en la Figura 4, usando un voltaje de salida de la válvula de prueba que se genera adecuadamente, se genera una corriente a simular.

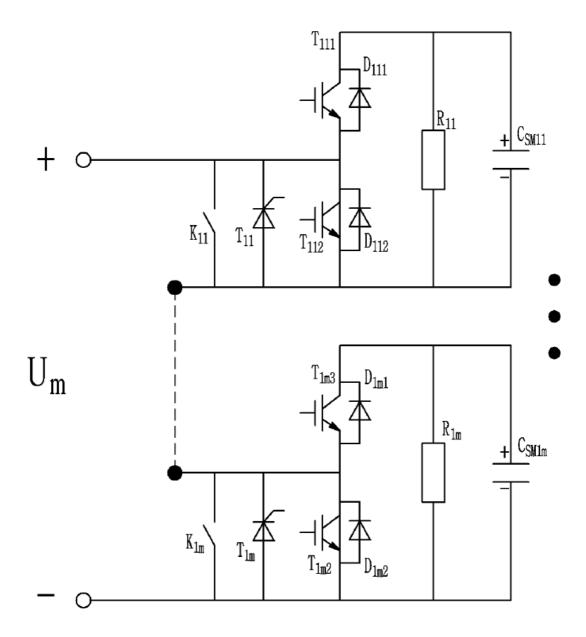

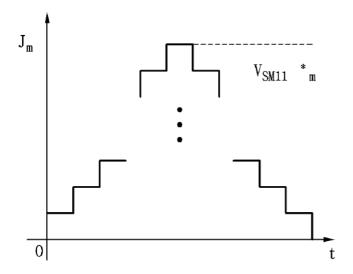

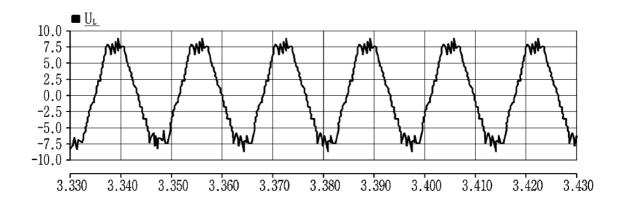

La Figura 5 es una vista que ilustra una configuración de una válvula de prueba, la Figura 6 es una vista que ilustra un voltaje de salida de una válvula de prueba, la Figura 7 es una vista que ilustra un circuito equivalente de un circuito de prueba sintético, y la Figura 8 es una vista que ilustra el voltaje de un inductor.

El principio para generar una corriente que fluye a través de una válvula de prueba real puede explicarse usando una configuración de una válvula de prueba y un voltaje de salida ilustrado en las Figuras 5 y 6, un circuito equivalente de un circuito de prueba sintético ilustrado en la Figura 7 y un voltaje inductor U<sub>L</sub> ilustrado en la Figura 8.

Al encender o apagar adecuadamente cada estado del interruptor de la válvula de prueba configurada de m submódulos ilustrados en la Figura 5, 0 al voltaje V<sub>SM11</sub> \* m[V]puede generarse como se ilustra en la Figura 6. Cuando los submódulos conectados en serie de la válvula de prueba son cinco (5) en número, se puede indicar un circuito equivalente del circuito de prueba sintético como se ilustra en la Figura 7. Además, cuando se aplica un voltaje pseudo-sinusoidal ilustrado en la Figura 8 a un inductor L ubicado entre las válvulas de prueba mediante la regulación de una fase de u2, la corriente que fluye a través del reactor también puede convertirse en una onda pseudo-sinusoidal. Al hacer eso, puede ser posible habilitar una corriente cuyo tipo es similar a un componente de CA de la corriente que fluye a través del submódulo cuando realmente opera el MMC, para fluir a través de la válvula de prueba. Sin embargo, existe la limitación de que no es posible permitir que fluya un componente de CC incluido en una operación MMC real.

El circuito de prueba sintético para una prueba de válvula de HVDC de fuente de voltaje se configura de dos (2) válvulas de prueba y dos (2) válvulas auxiliares. La válvula auxiliar sirve para complementar la pérdida ocurrida en la válvula de prueba cuando se opera el circuito de prueba sintético. Si bien se debe cargar un capacitor de submódulo y un capacitor de válvula auxiliar de la válvula de prueba antes de probar la válvula de prueba, existe el problema de que se necesita una fuente de energía de CC para cargar la válvula de prueba y dos fuentes de energía de CC para cargar una válvula auxiliar, es decir, se necesitan tres (3) fuentes de energía de CC en total. Además, dado que se genera una corriente de prueba usando una resonancia de un capacitor y un inductor de la válvula de prueba, existe el problema de que no es posible generar una forma de onda de una corriente pseudo-sinusoidal que incluye una corriente de compensación de CC que fluye a través de un submódulo individual cuando realmente opera el MMC. Además, mientras que la corriente que fluye a través de cada IGBT y diodo tiene una forma PWM cuando realmente opera el MMC, existe el problema de que dicha forma de corriente no se puede incorporar.

#### Resumen de la invención

10

20

30

35

60

65

Es un objetivo de la presente descripción proporcionar una configuración novedosa de un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC.

Es otro objetivo de la presente descripción proporcionar un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC, que es capaz de proporcionar una corriente que incluye una compensación de CC.

Otro objetivo más de la presente descripción es proporcionar una configuración de un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC, que es capaz de cambiar varias veces dentro de un período.

Todavía es otro objetivo de la presente descripción proporcionar un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC, que consume un poco de energía y es capaz de probar simultáneamente la muestra a analizar de una unidad inversora y una unidad de rectificación.

De acuerdo con la presente invención, que se define por las características de la reivindicación independiente 1, se proporciona un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC, que incluye un circuito de resonancia configurado para comprender una primera válvula de prueba para probar el funcionamiento de un modo inversor y una segunda válvula de prueba para probar el funcionamiento de un modo rectificador; una fuente de energía (P/S) configurada para proporcionar al circuito de resonancia un voltaje de operación; y un conversor CC/CC configurado para evitar una corriente de compensación de CC del circuito de resonancia, en donde la primera válvula de prueba es una unidad inversora, que tiene una compensación de corriente de CC positiva, en donde la segunda válvula de prueba es una unidad de rectificación, que tiene una compensación de corriente de CC negativa.

Breve descripción de los dibujos

Los anteriores y otros objetos y características de la presente descripción se harán evidentes a partir de la siguiente descripción de modalidades dadas junto con los dibujos adjuntos, en los que:

La Figura 1 es una vista que ilustra un ejemplo de un circuito de prueba sintético para una prueba de rendimiento de válvula en la técnica.

Las Figuras 2 a 4 son vistas que ilustran operaciones de circuitos de prueba sintéticos para una prueba de rendimiento de válvula en la técnica.

- La Figura 5 es una vista que ilustra una configuración de una válvula de prueba.

- La Figura 6 es una vista que ilustra un voltaje de salida de una válvula de prueba.

- La Figura 7 es una vista que ilustra un circuito equivalente de un circuito de prueba sintético.

- La Figura 8 es una vista que ilustra el voltaje de un inductor.

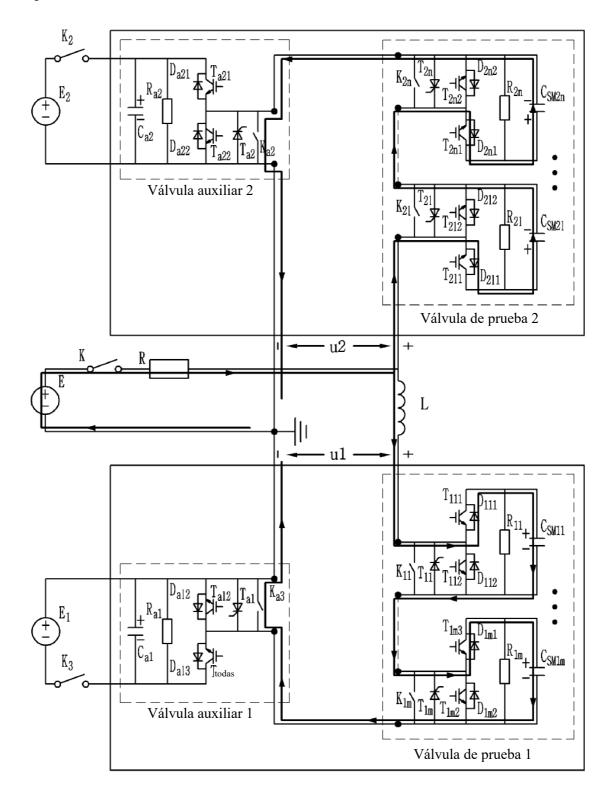

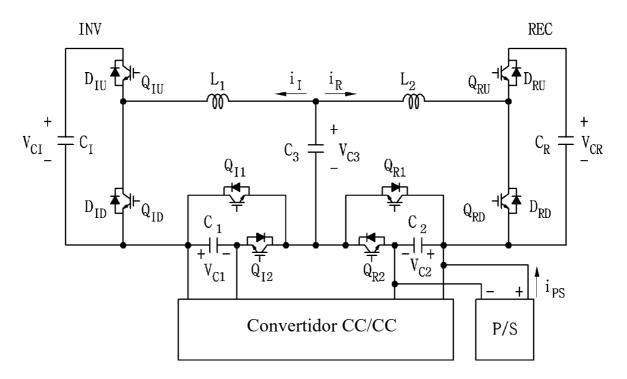

- La Figura 9 es una vista que ilustra un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con una modalidad de la presente descripción.

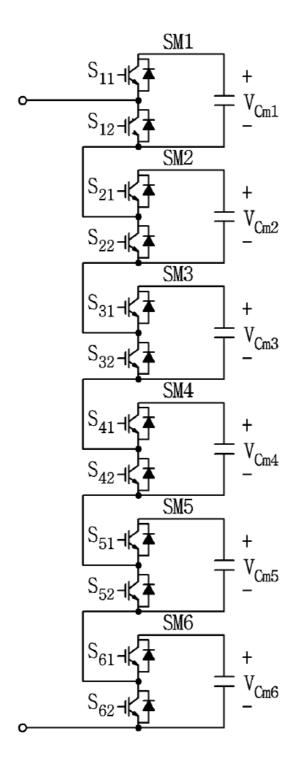

- La Figura 10 es una vista que ilustra un diagrama de circuito de una muestra a analizar con respecto a un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con una modalidad de la presente descripción.

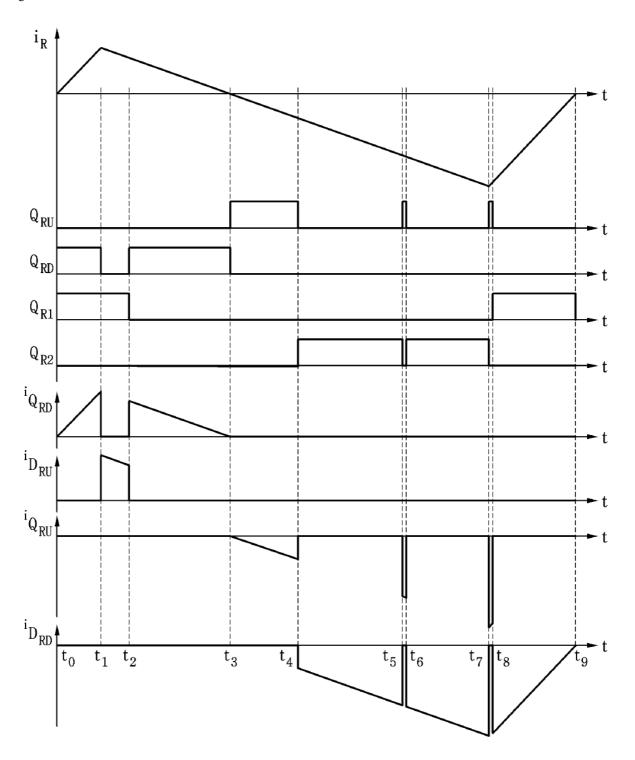

- La Figura 11 es una vista que ilustra señales de conmutación y formas de onda de corriente de un submódulo de unidad de rectificación de un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con una modalidad de la presente descripción.

- La Figura 12 es una vista que ilustra señales de conmutación y formas de onda de corriente de un submódulo de unidad inversora con respecto a un circuito de prueba sintético de una prueba de rendimiento de válvula de HVDC de acuerdo con una modalidad de la presente descripción.

Descripción detallada de las modalidades

A continuación, se describirán en detalle modalidades preferidas de un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC con referencia a los dibujos adjuntos.

# ES 2 754 716 T3

La Figura 9 es una vista que ilustra un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con una modalidad de la presente descripción, la Figura 10 es una vista que ilustra un diagrama de circuito de una muestra a analizar con respecto a un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con una modalidad de la presente descripción, la Figura 11 es una vista que ilustra las señales de conmutación y las formas de onda de corriente de un submódulo de unidad de rectificación de un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC en de acuerdo con una modalidad de la presente descripción, y la Figura 12 es una vista que ilustra señales de conmutación y formas de onda de corriente de un submódulo de unidad inversora con respecto a un circuito de prueba sintético de una prueba de rendimiento de válvula de HVDC de acuerdo con una modalidad de presente descripción.

10

5

Una unidad de conversor de potencia de una HVDC de fuente de energía basada en MMC se configura de varias decenas o cientos de válvulas IGBT (submódulos) que están conectadas en serie, lo que necesita probar el rendimiento antes de fabricarlo.

15 No

No es posible probar simultáneamente decenas o cientos de válvulas IGBT que están conectadas en serie en la prueba de rendimiento, y se describe en la regulación internacional que se probarán cinco (5) o más IGBT que están conectadas en serie. El dispositivo esencial para tal prueba es un circuito de prueba sintético.

20

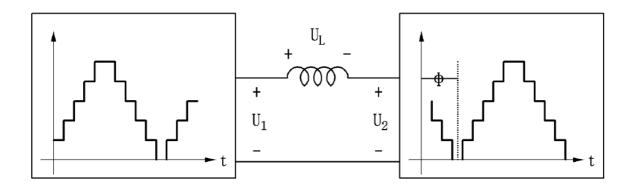

Con referencia a la Figura 9, en un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con una modalidad de la presente descripción, una válvula de prueba de una unidad REC de rectificación en el lado derecho se indica como dos IGBT (Q<sub>RU</sub>-RE<sub>RU</sub> y Q<sub>RD</sub>-RE<sub>RD</sub>) y un capacitor CR. Sin embargo, en una configuración real, la válvula de prueba puede estar formada por seis (6) válvulas IGBT (subválvulas) conectadas en serie que son las mismas que se ilustran en la Figura 10 y pueden corresponder a una muestra a analizar. Además, una unidad indicada como un inversor INV en el lado izquierdo también es la misma que la unidad REC de rectificación y corresponde a una muestra a analizar también.

25

Dado que una característica de la válvula IGBT que configura la HVDC de fuente de energía cuando funciona en un modo REC rectificador es diferente de cuando funciona en un modo INV inversor, la prueba es necesaria en cada modo de operación. Sin embargo, la presente descripción puede proporcionar una estructura con la que ambos modos de operación se pueden probar simultáneamente.

30

Con referencia a la Figura 9, dos inductores conectados en serie  $L_1$  y  $L_2$  que existen entre la unidad INV inversora y la unidad REC de rectificación tienen el mismo valor y se involucran en un flujo de corriente. Un capacitor  $C_3$  interpuesto se conecta a un contacto entre los inductores  $L_1$  y  $L_2$ , que sirve para tratar una ondulación actual de los inductores  $L_1$  y  $L_2$ . Cuatro IGBT ( $Q_{11}$ ,  $D_{12}$   $Q_{R1}$  y  $D_{R2}$ ) y dos capacitores ( $C_1$  y  $C_2$ ) en la etapa inferior sirven para evitar un componente de CC de la corriente que fluye a través de L1 y L2, y este proceso se realiza a través del conversor de CC/CC. Una potencia externa aplicada para realizar la operación en la Figura 9 puede ser suministrada por un P/S (fuente de energía).

35

Es decir, de acuerdo con la presente descripción, se incluye un circuito de resonancia que comprende una primera válvula de prueba para probar una operación de un modo inversor y una segunda válvula de prueba para probar una operación de un modo rectificador. Además, la P/S suministra al circuito de resonancia una potencia de operación. En detalle, la P/S puede suministrar las válvulas de prueba primera y segunda que configuran el circuito de resonancia con una potencia de operación. Las primera y segunda válvulas de prueba pueden incluir una pluralidad de superádulos consectados en serio y codo submédulo puedo incluir una pluralidad de ICRT y un capacitor. La primera

45

submódulos conectados en serie, y cada submódulo puede incluir una pluralidad de IGBT y un capacitor. La primera válvula de prueba puede ser una unidad INV inversora, y la segunda válvula de prueba puede ser una unidad REC de rectificación.

50

Los submódulos incluidos en las primera y segunda válvulas de prueba pueden incluir dos (2) IGBT conectados en serie y un capacitor conectado a los IGBT en paralelo.

La primera válvula de prueba tiene un extremo conectado al primer inductor  $L_1$  y el otro extremo conectado a la primera válvula auxiliar. La segunda válvula de prueba tiene un extremo conectado al segundo inductor  $L_2$  y el otro extremo conectado a la segunda válvula auxiliar.

55

El primer inductor  $L_1$  se conecta entre los IGBT de la primera válvula de prueba y la primera válvula auxiliar se conecta entre el IGBT y un capacitor de la primera válvula de prueba. El segundo inductor  $L_2$  se conecta entre IGBT de la segunda válvula de prueba y la segunda válvula auxiliar se conecta entre el IGBT y un capacitor de la segunda válvula de prueba.

60

La primera válvula auxiliar puede incluir dos (2) IGBT ( $Q_{11}$  y  $Q_{12}$ ) y un capacitor  $C_1$ , el IGBT ( $Q_{12}$ ) y el capacitor  $C_1$  están conectados en serie, y el IGBT ( $Q_{11}$ ) se conecta al otro IGBT ( $Q_{12}$ ) y el capacitor  $C_1$  en paralelo. El IGBT ( $Q_{11}$ ) se conecta en antiparalelo al otro IGBT ( $Q_{12}$ ).

65

Además, la segunda válvula auxiliar puede incluir dos (2) IGBT (Q<sub>R1</sub> y Q<sub>R2</sub>) y un capacitor C<sub>2</sub>, el IGBT (Q<sub>R2</sub>) y el capacitor C<sub>2</sub> están conectados en serie, y el IGBT (Q<sub>R1</sub>) se conecta en paralelo al otro IGBT (Q<sub>R2</sub>) y al capacitor C<sub>2</sub>. El

IGBT (Q<sub>R1</sub>) se conecta en antiparalelo al otro IGBT (Q<sub>R2</sub>).

El primer inductor  $L_1$  se conecta en serie al segundo inductor  $L_2$ , y la primera válvula auxiliar se conecta en serie a la segunda válvula auxiliar.

Un extremo del primer capacitor  $C_3$  se conecta a un contacto entre el primer inductor  $L_1$  y el segundo inductor  $L_2$ , y el otro extremo del primer capacitor  $C_3$  se conecta a un contacto entre la primera válvula auxiliar y la segunda válvula auxiliar.

10 El conversor CC/CC se conecta a ambos extremos de los capacitores C<sub>1</sub> y C<sub>2</sub> incluido en la primera y segunda válvulas auxiliares, de modo que sirve para evitar una corriente de compensación de CC.

Además, la P/S (fuente de energía) se conecta a ambos extremos del capacitor  $C_2$  incluido en la segunda válvula auxiliar, de modo que sirve para cargar una válvula de prueba y una válvula auxiliar en una operación de arranque inicial y compensar una pérdida de potencia en una operación normal. La P/S (fuente de energía) puede cargar los capacitores  $C_1$  y  $C_2$ , el primer capacitor  $C_3$  y los capacitores  $C_1$  y  $C_R$ , que se incluyen en las válvulas auxiliares primera y segunda a través de un control de conmutación.

Tal circuito de prueba sintético puede controlarse mediante un sistema de control (no ilustrado), que controla el encendido/apagado del interruptor de acuerdo con un método de operación establecido para probar las operaciones del mismo en un modo rectificador y un modo inversor.

Con referencia a la Figura 11, las señales de conmutación y las formas de onda de corriente de una válvula de prueba y una válvula auxiliar de una unidad REC de rectificación son las siguientes. Se requieren condiciones tales como las siguientes expresiones para simular de manera similar una forma de onda de corriente que fluye a través de un submódulo cuando realmente se opera un sistema HVDC de fuente de voltaje.

$$V_{C2} = V_{C1} = V_{CR} = V_{CI}$$

$$V_{C3} = \frac{3}{4} \times V_{C2}$$

40 a. Modo 1  $(t_0 \le t < t_1)$

5

15

25

Al encender Q<sub>RD</sub> y Q<sub>R1</sub>, la corriente de entrada del rectificador i<sub>R</sub> se levanta de la siguiente manera.

$$i_{R} = \frac{V_{C3}}{L_{2}} \times t$$

Aquí, la caída de voltaje en un estado ENCENDIDO de la válvula IGBT se ignora y se supone que todos los componentes son ideales, de ahora en adelante. En t = t<sub>1</sub> Q<sub>RD</sub> está apagado.

b. Modo 2 ( $t_1 \le t < t_2$ )

Al apagar Q<sub>RD</sub>, la corriente que fluye a través de Q<sub>RD</sub> comienza a fluir a través de D<sub>RU</sub> y la magnitud de la corriente es la siguiente. Aquí, i(t<sub>1</sub>) es un valor instantáneo de la corriente que fluye en un momento t<sub>1</sub>.

60

$$i_R = i_{DRU} = i(t_1) + \frac{(V_{C3} - V_{CR})}{L_2} \times t = i(t_1) - \frac{V_{CR}}{4L_2} \times t$$

c. Modo 3 ( $t_2 \le t < t_3$ )

65

En t =  $t_2$  Q<sub>R1</sub> está apagado y Q<sub>RD</sub> está encendido.

Luego, la corriente comienza a fluir a lo largo de una ruta como  $C_3 -> L_2 -> Q_{RD} -> C_2 -> D$  ( $Q_{R2}$ ) ->  $C_3$  y su magnitud es la siguiente.

$$i_{R} = i_{QRD} = i(t_{2}) + \frac{(V_{C3} - V_{C2})}{L_{2}} \times t = i(t_{2}) - \frac{V_{C2}}{4L_{2}} \times t$$

10 Cuando dicha corriente disminuye a 0, QRD está apagado.

d. Modo 4 ( $t_3 \le t < t_4$ )

En t =  $t_3$ , cuando  $Q_{RU}$  está activado, la corriente comienza a aumentar a lo largo de una ruta como  $C_R \rightarrow Q_{RU} \rightarrow L2 \rightarrow C_3$ -> D ( $Q_{R1}$ ) ->  $C_R$ .

$$i_{R} = i_{QRU} = i(t_{3}) + \frac{(V_{C3} - V_{CR})}{L_{2}} \times t = -\frac{V_{CR}}{4L_{2}} \times t$$

e. Modo 5 ( $t_4 \le t < t_5$ )

25 En t = t<sub>4</sub> Q<sub>RU</sub> está apagado y Q<sub>R2</sub> está encendido. Entonces, la corriente que fluye a través de la Q<sub>RU</sub> se transfiere a la D<sub>RD</sub> para fluir.

30

$$i_R = i_{DRD} = i(t_4) + \frac{(V_{C3} - V_{C2})}{L_2} \times t = i(t_4) - \frac{V_{C2}}{4L_2} \times t$$

f. Modo 6 ( $t_5 \le t < t_6$ )

35

45

65

En t = t<sub>5</sub>, al apagar Q<sub>R2</sub> y encender Q<sub>RU</sub>, la corriente se mueve a Q<sub>RU</sub>, de nuevo.

$$i_{R} = i_{QRU} = i(t_{5}) + \frac{(V_{C3} - V_{CR})}{L_{2}} \times t = i(t_{5}) - \frac{V_{CR}}{4L_{2}} \times t$$

g. Modo 7 ( $t_6 \le t < t_7$ )

En t =  $t_6$ , al apagar  $Q_{RU}$  y encender  $Q_{R2}$ , la corriente se mueve de  $Q_{RU}$  a  $D_{RD}$ .

$$i_{R} = i_{DRD} = i(t_{6}) + \frac{(V_{C3} - V_{C2})}{L_{2}} \times t = i(t_{6}) - \frac{V_{C2}}{4L_{2}} \times t$$

55 h. Modo 8 ( $t_7 \le t < t_8$ )

En t =  $t_7$ , al apagar  $Q_{R2}$  y encender  $Q_{RU}$ , la corriente se mueve de  $D_{RD}$  a  $Q_{RU}$ , de nuevo.

$$i_{R} = i_{DRU} = i(t_{7}) + \frac{(V_{C3} - V_{CR})}{L_{2}} \times t = i(t_{7}) - \frac{V_{CR}}{4L_{2}} \times t$$

i. Modo 9 ( $t_8 \le t < t_9$ )

En t = t<sub>8</sub>, al apagar Q<sub>RU</sub> y encender Q<sub>R1</sub>, la corriente se convierte en la siguiente.

$$i_{R} = i_{DRD} = i(t_{8}) + \frac{V_{C3}}{L_{2}} \times t$$

Cuando la magnitud de la corriente se convierte en 0, Q<sub>R1</sub> está apagado.

Con referencia a la Figura 12, las señales de conmutación y las formas de onda de corriente de la válvula de prueba y la válvula auxiliar de la unidad INV inversora son las siguientes. Se requieren condiciones tales como las siguientes expresiones para simular de forma similar una forma de onda de una corriente que fluye a través de un submódulo cuando realmente opera un sistema HVDC de fuente de voltaje.

a. Modo 1  $(t_0 \le t < t_1)$

5

15 Al encender Q<sub>ID</sub> y Q<sub>I1</sub>, la corriente de entrada del inversor i<sub>l</sub> se eleva de la siguiente manera

$$i_{I} = \frac{V_{C3}}{L_{1}} \times t$$

25 b. Modo 2  $(t_1 \le t < t_2)$

En t =  $t_1$ , al apagar  $Q_{ID}$ , la corriente se mueve de  $Q_{ID}$  a  $D_{IU}$ .

$$i_{I} = i_{DIU} = i(t_{1}) + \frac{(V_{C3} - V_{CI})}{L_{1}} \times t = i(t_{1}) - \frac{V_{CI}}{4L_{1}} \times t$$

c. Modo 3  $(t_2 \le t < t_3)$

35

En  $t = t_2$ , al encender  $Q_{ID}$ , la corriente se mueve de  $D_{IU}$  a  $Q_{ID}$ .

$$i_{I} = i_{QID} = i(t_{2}) + \frac{V_{C3}}{L_{1}} \times t$$

45 d. Modo 4 ( $t_3 \le t < t_4$ )

En t =  $t_3$ , al apagar  $Q_{ID}$ , la corriente se mueve a  $D_{IU}$ , de nuevo.

$$i_{I} = i_{DIU} = i(t_{3}) + \frac{(V_{C3} - V_{CI})}{L_{1}} \times t = i(t_{3}) - \frac{V_{CI}}{4L_{1}} \times t$$

e. Modo 5 ( $t_4 \le t < t_5$ )

En t = t<sub>4</sub>, al apagar Q<sub>I1</sub> y encender Q<sub>I2</sub> y Q<sub>ID</sub>, se aplica un voltaje inverso a L<sub>1</sub> para que la magnitud de la corriente comience a disminuir.

$$i_{I} = i_{QIU} = i(t_{4}) + \frac{(V_{C3} - V_{C1})}{L_{1}} \times t = i(t_{4}) - \frac{V_{C1}}{4L_{1}} \times t$$

f. Modo 6  $(t_5 \le t < t_6)$

En t =  $t_5$ , al apagar  $Q_{ID}$  y  $Q_{I2}$  y activando  $Q_{I1}$ , la corriente se mueve de  $Q_{ID}$  a  $D_{IU}$ .

5

10

$$i_{R} = i_{QRU} = i(t_{5}) + \frac{(V_{C3} - V_{CR})}{L_{2}} \times t = i(t_{5}) - \frac{V_{CR}}{4L_{2}} \times t$$

g. Modo 7 ( $t_6 \le t < t_7$ )

En t =  $t_6$ , al apagar  $Q_{11}$  y encender  $Q_{1D}$  y  $Q_{12}$ , la corriente se mueve de  $D_{1U}$  a  $Q_{1D}$ .

$$i_{I} = i_{QID} = i(t_{6}) + \frac{(V_{C3} - V_{C1})}{L_{1}} \times t = i(t_{6}) - \frac{V_{C1}}{4L_{1}} \times t$$

Cuando la corriente disminuye a 0,  $Q_{\text{ID}}$  y  $Q_{\text{I2}}$  están apagados.

25 h. Modo 8 ( $t_7 \le t < t_8$ )

En t = t<sub>7</sub>, al encender Q<sub>12</sub>, i<sub>1</sub> comienza a aumentar en la dirección menos (-).

$$i_{I} = i_{QIU} = i(t_{7}) + \frac{(V_{C3} - V_{CI})}{L_{1}} \times t = i(t_{7}) - \frac{V_{CI}}{4L_{1}} \times t$$

35 i. Modo 9  $(t_8 \le t < t_9)$

En t =  $t_8$ , al apagar  $Q_{IU}$  y encender  $Q_{I2}$ , la corriente se mueve de  $Q_{IU}$  a  $D_{ID}$ .

$$i_{I} = i_{DID} = i(t_{8}) + \frac{(V_{C3} - V_{C1})}{L_{1}} \times t = i(t_{8}) - \frac{V_{C1}}{4L_{1}} \times t$$

45 j. Modo 10 ( $t_9 \le t < t_{10}$ )

En  $t = t_9$ , al apagar  $Q_{12}$  y encender  $Q_{IU}$ , la corriente se mueve de  $D_{ID}$  a  $Q_{IU}$ .

$$i_{I} = i_{QIU} = i(t_{9}) + \frac{(V_{C3} - V_{CI})}{L_{1}} \times t = i(t_{9}) - \frac{V_{CI}}{4L_{1}} \times t$$

55

60

k. Modo 11 ( $t_{10} \le t < t_{11}$ )

En t =  $t_{10}$  al apagar  $Q_{IU}$ , la corriente se mueve de  $Q_{IU}$  a  $D_{ID}$

$i_{I} = i_{DID} = i(t_{10}) + \frac{V_{C3}}{L_{1}} \times t$

## ES 2 754 716 T3

Cuando la corriente se convierte en 0, el modo 11 finaliza.

Como se puede entender por las operaciones de la unidad REC de rectificación y la unidad INV inversora que se describen anteriormente, el circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con la presente descripción puede incorporar un circuito de prueba sintético que puede simular una situación real tanto como sea posible al permitir que se agregue una compensación de CC.

Es decir, como se puede ver de la corriente i<sub>R</sub> en la Figura 11 y la corriente i<sub>I</sub> en la Figura 12, la primera válvula de prueba puede tener una compensación de corriente de CC positiva y la segunda válvula de prueba puede tener una compensación de corriente de CC negativa.

Dado que una HVDC de fuente de voltaje real puede tener una corriente de compensación en la operación dependiendo de un modo rectificador o un modo inversor, la presente descripción puede incorporar un circuito de prueba sintético similar al de una situación real, capaz de asegurar la confiabilidad.

Además, el circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con la presente descripción puede permitir que la corriente de la válvula se cambie en un esquema PWM mientras se controla el ancho de pulso dentro de un (1) período, que es muy similar a una situación real, maximizando así la validez del circuito de prueba.

En el circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con la presente descripción, ya que la potencia suministrada al circuito de prueba sintético solo necesita proporcionar la pérdida en el circuito, como una pérdida del interruptor de la válvula IGBT y una línea pérdida, es posible realizar una prueba de alta potencia de una capacidad real utilizando una potencia mínima que sea inferior al 1% de una potencia real. En consecuencia, existe la ventaja de que el consumo de energía es muy pequeño en la instalación de prueba.

El circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC de acuerdo con la presente descripción puede probar simultáneamente muestras para probar en la unidad inversora y la unidad de rectificación, contribuyendo así a una productividad mejorada.

La presente descripción puede proporcionar una configuración novedosa de un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC.

Además, la presente descripción puede proporcionar un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC, que es capaz de proporcionar una corriente que incluye una compensación de CC.

Además, la presente descripción puede proporcionar una configuración de un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC, que es capaz de cambiar varias veces dentro de un período.

Además, la presente descripción puede proporcionar un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC, que consume un poco de energía y es capaz de probar simultáneamente las muestras a analizar de una unidad inversora y una unidad de rectificación.

De aquí en adelante, aunque la presente descripción se describe con referencia a modalidades, son solo ejemplos de ilustraciones y no limitan la descripción. Los expertos en la materia entenderán claramente que son posibles diversas modificaciones y aplicaciones no ilustradas anteriormente. Por ejemplo, cada componente constitucional ilustrado en detalle en las modalidades puede realizarse de forma modificada. Además, las diferencias relacionadas con tales modificaciones y aplicaciones deben interpretarse como incluidas en los ámbitos de la presente descripción.

5

10

15

20

25

30

35

45

### **REIVINDICACIONES**

- Un circuito de prueba sintético para una prueba de rendimiento de válvula de HVDC, que comprende: un circuito de resonancia que comprende una primera válvula de prueba que es una unidad inversora (INV), en donde el circuito de prueba sintético se configura para probar una operación de un modo inversor, y una segunda válvula de prueba es una unidad de rectificación (REC), en donde el circuito de prueba sintético se configura para probar una operación de un modo rectificador; y

- una fuente de energía (P/S) configurada para proporcionar al circuito de resonancia un voltaje de operación; en donde el circuito de prueba sintético comprende además:

- un conversor CC/CC configurado para evitar una corriente de compensación CC del circuito de resonancia, y una pluralidad de submódulos comprendidos en las primera y segunda válvulas de prueba respectivas, cada submódulo incluye una pluralidad de IGBT y un capacitor, en donde el circuito de prueba sintético se configura de tal manera que una corriente que fluye en un submódulo incluido en la primera válvula de prueba tiene una compensación de corriente de CC positiva, y una corriente que fluye en un submódulo incluido en la segunda válvula de prueba tiene una compensación de corriente de CC negativa.

- El circuito de prueba sintético de la reivindicación 1,

en donde el circuito de resonancia comprende un primer inductor (L1) y un segundo inductor (L2) que están

conectados en serie entre las primera y segunda válvulas de prueba, una primera válvula auxiliar y una

segunda válvula auxiliar que están conectadas en serie entre las primera y segunda válvulas de prueba, y un

primer capacitor (C3) cuyo extremo se conecta a un contacto entre el primer inductor (L1) y el segundo inductor

(L2), y cuyo otro extremo se conecta a un contacto entre la primera válvula auxiliar y la segunda válvula auxiliar.

- 3. El circuito de prueba sintético de la reivindicación 2, en donde el primer inductor (L1) está conectado entre IGBT (Q<sub>IU</sub>-D<sub>IU</sub>, Q<sub>ID</sub>-D<sub>ID</sub>) de la primera válvula de prueba, el segundo inductor (L2) se conecta entre IGBT (Q<sub>RU</sub>-D<sub>RU</sub>, Q<sub>RD</sub>-D<sub>RD</sub>) de la segunda válvula de prueba, la primera válvula auxiliar se conecta entre uno de los IGBT de la primera válvula de prueba y un capacitor (CI) de la primera válvula de prueba, y la segunda válvula auxiliar se conecta entre uno de los IGBT de la segunda válvula de prueba y un capacitor (CR) de la segunda válvula de prueba.

- 4. El circuito de prueba sintético de la reivindicación 2, en donde los submódulos comprendidos en la primera y segunda válvula de prueba comprenden cada uno dos IGBT conectados en serie (Q<sub>IU</sub>-D<sub>IU</sub>, Q<sub>ID</sub>-D<sub>ID</sub>), (Q<sub>RU</sub>-D<sub>RU</sub>, Q<sub>RD</sub>-D<sub>RD</sub>) y un capacitor (CI, CR) conectado a los IGBT en paralelo.

- 5. El circuito de prueba sintético de la reivindicación 2, en donde la primera válvula auxiliar comprende un primer IGBT (Q<sub>I1</sub>) y un segundo IGBT (Q<sub>I2</sub>) y un capacitor (C1) que están conectados al primer IGBT en paralelo y están conectados en serie entre sí, y en donde la segunda válvula auxiliar comprende un tercer IGBT (Q<sub>R1</sub>) y un cuarto IGBT (Q<sub>R2</sub>) y un capacitor (C2) que están conectados al tercer IGBT en paralelo y están conectados en serie entre sí.

- El circuito de prueba sintético de la reivindicación 5, en donde el conversor CC/CC se conecta a ambos extremos del capacitor (C1) comprendido en la primera válvula auxiliar y a ambos extremos del capacitor (C2) comprendido en la segunda válvula auxiliar.

- 45 7. El circuito de prueba sintético de la reivindicación 5, en donde la fuente de energía (P/S) se conecta a ambos extremos del capacitor (C2) comprendido en la segunda válvula auxiliar para cargar las válvulas de prueba y las válvulas auxiliares

- 8. El circuito de prueba sintético de la reivindicación 5, en donde el primer y el segundo IGBT (Q<sub>11</sub> Q<sub>12</sub>) están conectados en antiparalelo, y el tercer y cuarto IGBT (Q<sub>R1</sub> Q<sub>R2</sub>) están conectados en antiparalelo.

- 9. El circuito de prueba sintético de la reivindicación 2, en donde los inductores primero y segundo (L1, L2) tienen el mismo valor.

- 55 10. El circuito de prueba sintético de la reivindicación 1, en donde la fuente de energía proporciona a la primera y segunda válvula de prueba un voltaje de operación.

Figura 1

Figura 2

Figura 3

Figura 4

Figura 5

Figura 6

Figura 7

Figura 8

Figura 9

Figura 10

Figura 11

Figura 12