# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 755 399

51 Int. Cl.:

**G06F 1/32** (2009.01) **G06F 15/78** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(86) Fecha de presentación y número de la solicitud internacional: 14.09.2015 PCT/EP2015/070964

(87) Fecha y número de publicación internacional: 31.03.2016 WO16046008

96 Fecha de presentación y número de la solicitud europea: 14.09.2015 E 15763900 (6)

(97) Fecha y número de publicación de la concesión europea: 28.08.2019 EP 3198361

(54) Título: Dominios de potencia controlados por hardware con potencia automática a petición

(30) Prioridad:

25.09.2014 US 201414496553

Fecha de publicación y mención en BOPI de la traducción de la patente: **22.04.2020**

(73) Titular/es:

TELEFONAKTIEBOLAGET LM ERICSSON (PUBL) (100.0%)

164 83 Stockholm, SE

(72) Inventor/es:

MALMBERG, MAGNUS y ARVIDSSON, ALBERTH

74 Agente/Representante:

LINAGE GONZÁLEZ, Rafael

### **DESCRIPCIÓN**

Dominios de potencia controlados por hardware con potencia automática a petición

#### Campo técnico

5

10

15

20

25

30

35

40

45

50

55

60

La presente descripción se refiere al control de los dominios de potencia dentro de un circuito integrado y, más específicamente, se refiere al encendido y al apagado controlados mediante equipo físico informático (hardware) de los dominios de potencia dentro de un circuito integrado.

#### **Antecedentes**

El consumo de potencia en un circuito integrado específico de aplicación (ASIC) y otros circuitos integrados similares proviene principalmente de dos fuentes, a saber, la potencia dinámica y la potencia estática (es decir, una fuga). La potencia dinámica consumida por el ASIC es la potencia consumida por el ASIC debido a la conmutación de circuitos para realizar la/s tarea/s deseada/s. En otras palabras, el consumo de potencia dinámico es el consumo de potencia debido a circuitería activa dentro del ASIC durante su funcionamiento. En contraste, el consumo de potencia estática del ASIC es el consumo de potencia debido a la/s corriente/s que fluye/n constantemente a través del ASIC, siempre que el ASIC esté recibiendo potencia y no está relacionado con la/s tarea/s real/es que realiza el ASIC. En otras palabras, el consumo de potencia estática es el consumo de potencia de la circuitería dentro del ASIC cuando está inactivo.

La tendencia es a que las fugas se conviertan en una parte más grande del consumo de potencia del ASIC a medida que la tecnología utilizada para fabricar el ASIC disminuye, o se reduce, en geometría. Como resultado, cada vez es más importante gestionar las fugas de los ASIC sensibles al consumo de potencia, como, por ejemplo, los ASIC que se encuentran en dispositivos móviles (por ejemplo, en teléfonos móviles).

En la actualidad, hay varias técnicas que se utilizan para reducir las fugas. La más común de estas técnicas es la activación de potencia de dominios de potencia. Más específicamente, los dominios de potencia están controlados por tiempo mediante equipo lógico informático (software). El software desactiva, o apaga, un dominio de potencia cuando el software sabe que ningún bloque de hardware dentro del dominio de potencia necesita potencia en base a un/os casos de uso definido. El software activa, o enciende, un dominio de potencia cuando, en base al caso de uso de ejecución actual, el software sabe que un/os bloque/s de hardware dentro del dominio de potencia necesita/n potencia. El tiempo de activación para un dominio de potencia incluye el tiempo requerido por el software para tomar la decisión de activar el dominio de potencia, el tiempo necesario para los cambios de estado manipulados mediante interrupción y el tiempo necesario para controlar los conmutadores de potencia para el dominio de potencia. Adicionalmente, se debe añadir un amplio margen de seguridad de tal modo que el dominio de potencia se active antes de accederse al bloque o a los bloques de hardware. En otras palabras, el dominio de potencia debe estar recibiendo potencia durante un período de tiempo relativamente largo antes de que se acceda al bloque o a los bloques de hardware en el dominio de potencia. Como resultado, los dominios de potencia se activan, o reciben potencia, más tiempo del necesario.

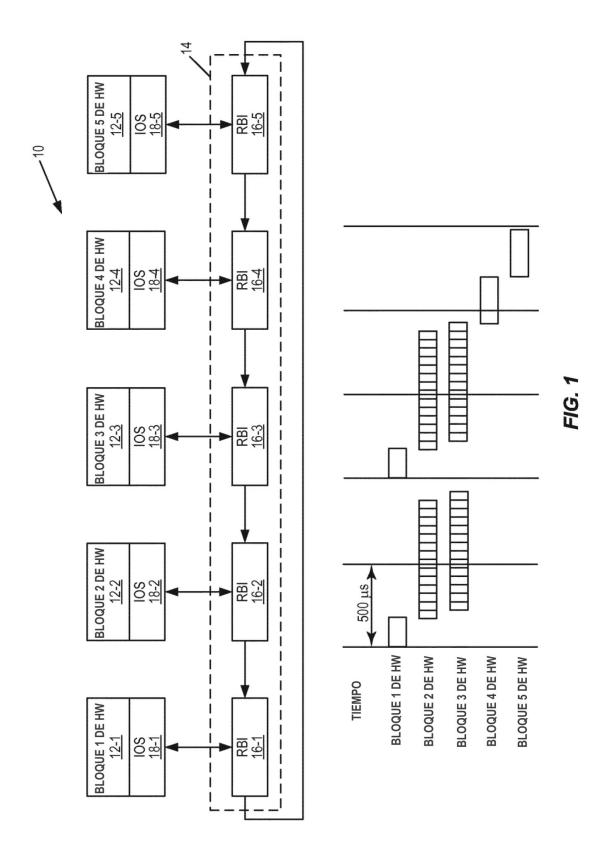

Por ejemplo, la figura 1 ilustra un sistema 10 de hardware (HW) que incluye cinco bloques 12-1 a 12-5 de HW (generalmente se denominan colectivamente "bloques 12 de HW" e individualmente "bloque 12 de HW"), así como un bus 14 de anillo que incluye una interfaz de bus de anillo (RBI) 16-1 a 16-5 separada (generalmente se denominan colectivamente "RBI 16" e individualmente "RBI 16") para cada uno de los bloques 12-1 a 12-5 de HW. Los bloques 12-1 a 12-5 de HW están conectados a las RBI correspondientes 16-1 a 16-5 mediante correspondientes tomas de entrada y salida (IOS) 18-1 a 18-5 (generalmente se denominan colectivamente "IOS 18" e individualmente "IOS 18"). La figura 1 ilustra también un ejemplo de los tiempos activos de los bloques 12 de HW. Si cada bloque 12 de HW se implanta en un dominio de potencia separado que se activa o desactiva mediante software de la manera convencional, el software tiene que tener un buen control de cuándo los bloques 12 de HW están activos así como manipular el tiempo de encendido y apagado de los dominios de potencia correspondientes. Con la sobrecarga para encender los dominios de potencia y controlar el tiempo de activación mediante interrupción u otro mecanismo, la solución más probable es que todos los bloques 12 de HW estén encendidos todo el tiempo.

De este modo, existe la necesidad de un sistema mejorado que controle el consumo de potencia, y, en particular, de fuga, en un circuito integrado.

La patente de EE.UU. núm. 7.443.759 titulada "Reduced-Power Memory with Per-Sector Ground Control" describe el control de potencia selectivo de sectores comprendidos en una memoria de potencia reducida. El control selectivo de potencia selecciona un sector de la memoria para encender en respuesta a un subconjunto de bitios de dirección para acceder a la memoria y enciende individualmente el sector seleccionado al disminuir el potencial de tierra para el sector seleccionado de un nivel de retención a un nivel de acceso.

65 La solicitud de patente de EE.UU. núm. 2008/0025123 titulada "Interface Circuit System and Method for Autonomously Performing Power Management Operations in Conjunction with a Plurality of Memory Circuits" divulga

un circuito de interfaz que está en comunicación con circuitos de memoria y un sistema. El circuito de interfaz realiza de manera autónoma una operación de gestión de potencia en asociación con al menos una porción de los circuitos de memoria. En particular, se identifica un circuito de memoria en un estado sin acceso. Se inicia una función de ahorro de potencia, tal como el apagado, para el circuito de memoria identificado.

La publicación de solicitud internacional de patente núm. WO 2008/017625 titulada "Distributed Autonomous Power Management in a Memory System" divulga una unidad de control que gestiona potencia de manera autónoma dentro y para un grupo de dispositivos de memoria.

Estas referencias se refieren a la reducción del consumo de potencia en un sistema de memoria y no se relacionan con el encendido y el apagado de los dominios de potencia de hardware.

El documento US 2009/135751 describe un método para reducir el consumo de potencia en dispositivos de red con múltiples procesadores.

El documento US 2013/0073878 describe un administrador de potencia de interconexión que coopera con un administrador de potencia de circuito integrado para controlar múltiples dominios de potencia en un circuito integrado.

#### 20 Sumario

15

25

30

35

40

55

60

65

Se divulgan sistemas y métodos relacionados con dominios de potencia controlados por hardware en un sistema de hardware (por ejemplo, un circuito integrado). La invención se resume mejor por las reivindicaciones independientes adjuntas. Se esbozan aspectos adicionales de la invención en las reivindicaciones dependientes. Las realizaciones no reivindicadas no son parte de la invención, y sirven como ejemplos útiles para comprender la invención. En una realización, el encendido y el apagado completamente automáticos de los dominios de potencia en el sistema de hardware se proporcionan sin la implicación del software. De esta manera, los tiempos de encendido y apagado para los dominios de potencia se reducen o minimizan sustancialmente, lo que a su vez permite tiempos activos más cortos para los dominios de potencia y, de este modo, se reduce el consumo de potencia (por ejemplo, aparecen fugas reducidas cuando el hardware está inactivo en los dominios de potencia).

En algunas realizaciones, un sistema de hardware comprende un bloque de hardware que comprende uno o más componentes de hardware, un controlador de potencia de hardware, y una interfaz de hardware. El controlador de potencia de hardware está configurado para controlar uno o más dominios de potencia del sistema de hardware. Los dominios de potencia del sistema de hardware comprenden un dominio de potencia del bloque de hardware. La interfaz de hardware está configurada para recibir al menos un mensaje para el bloque de hardware y almacenar el al menos un mensaje. En respuesta a la recepción del al menos un mensaje para el bloque de hardware, la interfaz de hardware está configurada para activar una solicitud de potencia desde la interfaz de hardware al controlador de potencia de hardware para solicitar, por ello, que se active la potencia para el bloque de hardware. Una vez que se encienda el dominio de potencia del bloque de hardware, la interfaz de hardware recibirá una indicación del bloque de hardware de que el bloque de hardware está listo para aceptar mensajes. En respuesta, la interfaz de hardware proporciona el al menos un mensaje al bloque de hardware. De esta manera, se proporciona un procedimiento de encendido completamente automático para el dominio de potencia del bloque de hardware.

En algunas realizaciones, el controlador de potencia de hardware está configurado para encender el dominio de potencia del bloque de hardware en respuesta a la activación de la solicitud de potencia de la interfaz de hardware. Adicionalmente, en algunas realizaciones, el bloque de hardware está configurado para, en respuesta al dominio de potencia del bloque de hardware que se está encendiendo, activar una solicitud de potencia desde el bloque de hardware al controlador de potencia de hardware para solicitar, por ello, que se mantenga la potencia para el bloque de hardware hasta que la solicitud de potencia del bloque de hardware sea desactivada.

En algunas realizaciones, la interfaz de hardware está configurada adicionalmente para desactivar la solicitud de potencia de la interfaz de hardware para el controlador de potencia de hardware al determinar que no hay más mensajes recibidos por la interfaz de hardware para el bloque de hardware que se vayan a proporcionar al bloque de hardware. Adicionalmente, en algunas realizaciones, el bloque de hardware está configurado adicionalmente para desactivar la solicitud de potencia del bloque de hardware al controlador de potencia de hardware al determinar que no hay más mensajes recibidos desde la interfaz de hardware para que sean procesados por el bloque de hardware, y el controlador de potencia de hardware está configurado adicionalmente para apagar el dominio de potencia del bloque de hardware en respuesta a la desactivación de la solicitud de potencia desde la interfaz de hardware y la desactivación de la solicitud de potencia desde el bloque de hardware.

Adicionalmente, en algunas realizaciones, el controlador de potencia de hardware está configurado adicionalmente para indicar, al bloque de hardware, que el dominio de potencia del bloque de hardware está siendo apagado, para, por ello, indicar al bloque de hardware que el bloque de hardware no va a aceptar mensajes de la interfaz de hardware.

En algunas realizaciones, en respuesta a la activación de la solicitud de potencia de la interfaz de hardware, el controlador de potencia de hardware está configurado para encender el dominio de potencia del bloque de hardware para ser estable, y, cuando la potencia dentro del dominio de potencia del bloque de hardware para ser estable, y, cuando la potencia dentro del dominio de potencia del bloque de hardware es estable, activar el bloque de hardware. En algunas realizaciones, con el fin de activar el bloque de hardware, el controlador de potencia de hardware está configurado para desactivar una o más células de aislamiento que funcionan aislando el dominio de potencia cuando se desactiva la potencia para el dominio de potencia, desactivar un reinicio del bloque de hardware, y activar un sistema a petición del bloque de hardware para, por ello, informar al bloque de hardware de que se activa la potencia para el bloque de hardware.

10

15

En algunas realizaciones, el bloque de hardware está configurado para, como respuesta al ser activado, activar una solicitud de potencia del bloque de hardware al controlador de potencia de hardware para, por ello, solicitar que el controlador de potencia de hardware mantenga la potencia para el bloque de hardware hasta que la potencia solicitada por el bloque de hardware se desactive, activar una aceptación de mensajes del bloque de hardware a la interfaz de hardware para, por ello, indicar que el bloque de hardware está listo para aceptar mensajes de la interfaz de hardware, y activar un acuse de recibo del sistema desde el bloque de hardware hasta el controlador de potencia de hardware.

20

Adicionalmente, en algunas realizaciones, la interfaz de hardware está configurada adicionalmente para desactivar la solicitud de potencia de la interfaz de hardware al controlador de potencia de hardware cuando no hay más mensajes recibidos por la interfaz de hardware para el bloque de hardware que se vayan a proporcionar al bloque de hardware, y el bloque de hardware se configura adicionalmente para desactivar la solicitud de potencia del bloque de hardware al controlador de potencia de hardware cuando el bloque de hardware no reciba más mensajes de la interfaz de hardware para que sean procesados por el bloque de hardware. El controlador de potencia de hardware está configurado adicionalmente para apagar el dominio de potencia del bloque de hardware en respuesta a la desactivación de la solicitud de potencia desde la interfaz de hardware y a la desactivación de la solicitud de potencia desde el bloque de hardware.

30

25

En algunas realizaciones, con el fin de apagar el dominio de potencia del bloque de hardware, el controlador de potencia de hardware está configurado adicionalmente para informar al bloque de hardware que la potencia para el bloque de hardware se está desactivando. En respuesta a ser informado de que la potencia para el bloque de hardware se está desactivando, el bloque de hardware se configura adicionalmente para desactivar la aceptación de mensajes del bloque de hardware a la interfaz de hardware, para indicar, por ello, que el bloque de hardware ya no acepta mensajes de la interfaz de hardware.

35

40

En algunas realizaciones, después de la desactivación de la aceptación de mensajes desde el bloque de hardware a la interfaz de hardware, el bloque de hardware se configura adicionalmente para determinar si fueron recibidos mensajes de la interfaz de hardware mientras se desactivaba la aceptación de mensajes del bloque de hardware hasta la interfaz de hardware. Si no se recibió ningún mensaje de la interfaz de hardware mientras se desactivaba la aceptación de mensajes desde el bloque de hardware hasta la interfaz de hardware, el bloque de hardware se configura para continuar con el apagado del dominio de potencia del bloque de hardware. Si se recibieron uno o más mensajes de la interfaz de hardware mientras se desactivaba la aceptación de mensajes desde el bloque de hardware hasta la interfaz de hardware, el bloque de hardware se configura para terminar el apagado del dominio de potencia del bloque de hardware.

45

En algunas realizaciones, con el fin de continuar con el apagado, el bloque de hardware se configura adicionalmente para desactivar el acuse de recibo del sistema desde el bloque de hardware hasta el controlador de potencia de hardware. En respuesta a la desactivación del acuse de recibo del sistema, el controlador de potencia de hardware se configura adicionalmente para desactivar la potencia para el dominio de potencia.

50

En algunas realizaciones, con el fin de terminar con el apagado, el bloque de hardware se configura adicionalmente para activar la solicitud de potencia del bloque de hardware al controlador de potencia de hardware, desactivar el acuse de recibo del sistema desde el bloque de hardware hasta el controlador de potencia hardware, y activar la aceptación de mensajes desde el bloque de hardware hasta la interfaz de hardware. En respuesta a la desactivación del acuse de recibo del sistema, el controlador de potencia de hardware se configura adicionalmente para informar al bloque de hardware de que se está activando la potencia para el bloque de hardware. En respuesta a ser informado de que se está activando la potencia para el bloque de hardware se configura adicionalmente para activar el acuse de recibo del sistema desde el bloque de hardware hasta el controlador de potencia de hardware.

60

65

55

En algunas realizaciones, el dominio de potencia comprende el bloque de hardware y al menos un bloque de hardware adicional, y el sistema de hardware comprende adicionalmente circuitería configurada para combinar la solicitud de potencia de la interfaz de hardware para el bloque de hardware con al menos una solicitud de potencia adicional desde la interfaz de hardware para el al menos un bloque de hardware adicional en el dominio de potencia para proporcionar una solicitud de potencia combinada desde la interfaz de hardware hasta el controlador de potencia de hardware. La solicitud de potencia combinada de la interfaz de hardware se activa cuando una solicitud

cualquiera o más de entre las solicitudes de potencia y la al menos una solicitud de potencia adicional de la interfaz de hardware se activa/n, y se desactiva cuando tanto la solicitud de potencia como la al menos una solicitud de potencia adicional desde la interfaz de hardware se desactivan. El controlador de potencia de hardware está configurado para encender el dominio de potencia en respuesta a la activación de la solicitud de potencia combinada desde la interfaz de hardware.

En algunas realizaciones, después de que se active la potencia para el dominio de potencia, el bloque de hardware se configura adicionalmente para proporcionar una solicitud de potencia desde el bloque de hardware para solicitar, por ello, que la potencia al bloque de hardware se mantenga hasta que la solicitud de potencia desde el bloque de hardware sea desactivada. Del mismo modo, el al menos un bloque de hardware adicional está configurado para proporcionar al menos una solicitud de potencia adicional desde el al menos un bloque de hardware adicional para, por ello, solicitar que se mantenga la potencia para el al menos un bloque de hardware adicional hasta que la al menos una solicitud de potencia adicional desde el al menos un bloque de hardware adicional se desactive. El sistema de hardware comprende adicionalmente circuitería configurada para combinar la solicitud de potencia desde el bloque de hardware y la al menos una solicitud de potencia adicional desde el al menos un bloque de hardware adicional para proporcionar una solicitud de potencia combinada del dominio de potencia. La solicitud de potencia combinada del dominio de potencia se activa cuando una o más de entre las solicitudes de potencia del bloque de hardware y la al menos una solicitud de potencia adicional del al menos un bloque de hardware adicional se activa/n, y se desactiva cuando tanto la solicitud de potencia del bloque de hardware como la al menos una solicitud de potencia adicional del al menos un bloque de hardware adicional se desactivan. El controlador de hardware se configura adicionalmente para apagar el dominio de potencia en respuesta a la desactivación de la solicitud de potencia combinada de la interfaz de hardware y a la desactivación de la solicitud de potencia combinada del dominio de potencia.

En algunas realizaciones, el dominio de potencia comprende el bloque de hardware y al menos un bloque de hardware adicional, y el controlador de potencia de hardware está configurado para encender el dominio de potencia en respuesta a la activación de una solicitud cualquiera o más de entre la solicitud de potencia de la interfaz de hardware para el bloque de hardware y al menos una solicitud de potencia adicional de la interfaz de hardware para el al menos un bloque de hardware adicional en el dominio de potencia.

En algunas realizaciones, después de que se active la potencia para el dominio de potencia, el bloque de hardware está configurado adicionalmente para proporcionar una solicitud de potencia desde el bloque de hardware para, por ello, solicitar que se mantenga la potencia para el bloque de hardware hasta que se desactive la solicitud de potencia del bloque de hardware. Del mismo modo, el al menos un bloque de hardware adicional está configurado para proporcionar al menos una solicitud de potencia adicional para solicitar, por ello, que se mantenga la potencia para el al menos un bloque de hardware adicional hasta que se desactive la al menos una solicitud de potencia adicional del al menos un bloque de hardware adicional. El controlador de potencia de hardware está configurado adicionalmente para apagar el dominio de potencia en respuesta a la desactivación tanto de la solicitud de potencia como de al menos una solicitud de potencia adicional de la interfaz de hardware, y a la desactivación tanto de la solicitud de potencia del bloque de hardware como de la al menos una solicitud de potencia adicional del al menos un bloque de hardware adicional.

En algunas realizaciones, la interfaz de hardware es un bus de anillo que comprende una interfaz de bus de anillo para cada bloque de hardware de una pluralidad de bloques de hardware que incluye el bloque de hardware.

En algunas realizaciones, el controlador de potencia de hardware está configurado adicionalmente para apagar el dominio de potencia del bloque de hardware en respuesta a una solicitud de apagado de software externo.

En algunas realizaciones, la interfaz de hardware está configurada adicionalmente para solicitar un reloj para el dominio de potencia en respuesta a recibir el al menos un mensaje para el bloque de hardware.

En algunas realizaciones, se proporciona un método para proporcionar control de potencia en un sistema de hardware. El sistema de hardware comprende un bloque de hardware que comprende uno o más componentes de hardware, un controlador de potencia de hardware configurado para controlar uno o más dominios de potencia del sistema de hardware que incluye un dominio de potencia del bloque de hardware y una interfaz de hardware. En esta realización, el método comprende recibir, mediante la interfaz de hardware, al menos un mensaje para un bloque de hardware que comprende uno o más componentes de hardware, y almacenar, mediante la interfaz de hardware, en respuesta a la recepción del al menos un mensaje para el bloque de hardware, una solicitud de potencia desde la interfaz de hardware hasta un controlador de potencia de hardware, recibir, mediante la interfaz de hardware, una indicación del bloque de hardware de que el bloque de hardware está listo para aceptar mensajes de la interfaz de hardware en respuesta a recibir la indicación del bloque de hardware de que el bloque de hardware está listo para aceptar mensajes de la interfaz de hardware.

65

55

60

10

15

20

30

35

40

El experto en la técnica apreciará el alcance de la presente divulgación y se percatará de los aspectos adicionales de la misma después de haber leído la siguiente descripción detallada de las realizaciones en asociación con las figuras de los dibujos que se acompañan.

#### Breve descripción de los dibujos

Las figuras de dibujo que se acompañan incorporadas en y que forman parte de esta memoria descriptiva ilustran varios aspectos de la divulgación y, junto con la descripción, sirven para explicar los principios de la divulgación.

- 10 La figura 1 ilustra un ejemplo de un sistema de hardware y de los tiempos activos de los bloques de hardware del sistema de hardware;

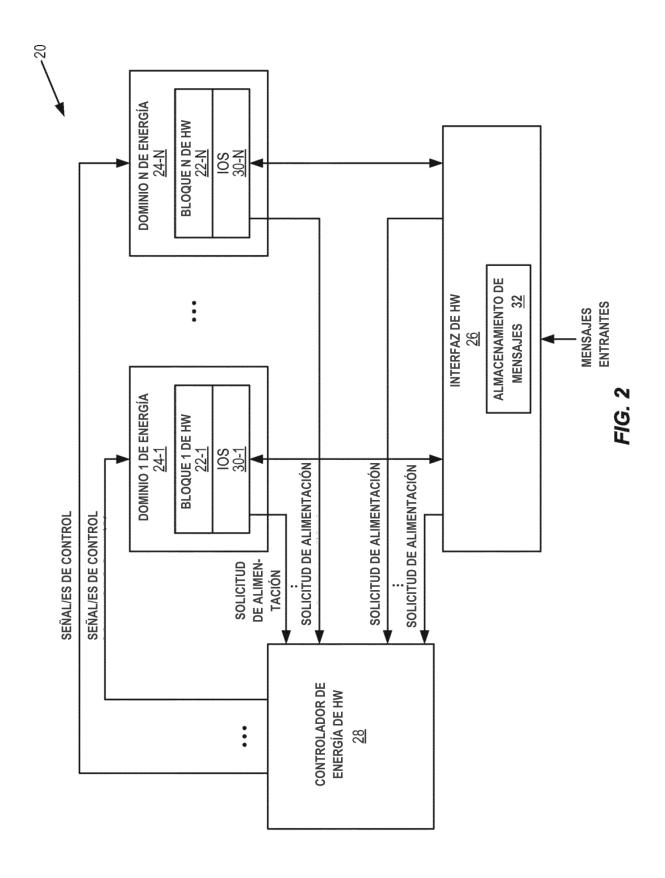

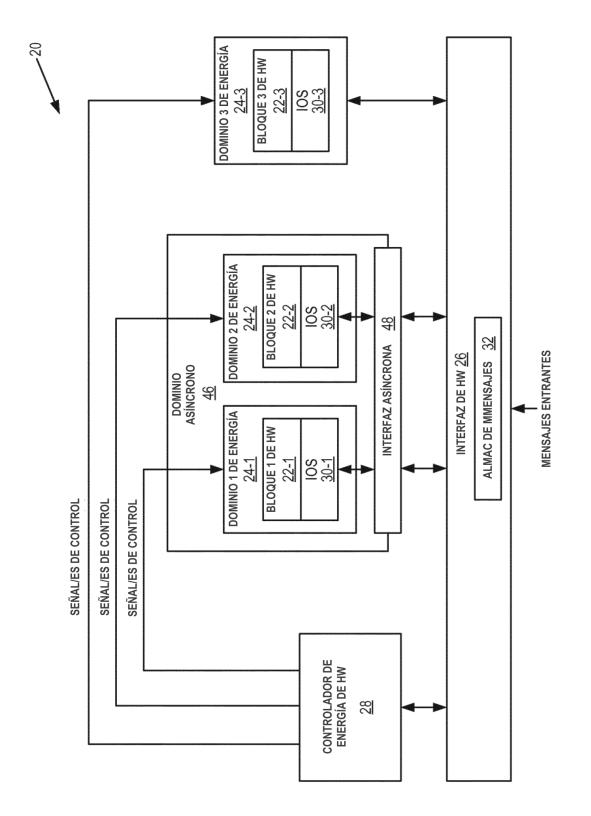

- la figura 2 ilustra un sistema de hardware que proporciona un flujo totalmente automático para el encendido y el apagado de dominios de potencia sin la implicación de software de acuerdo con una realización de la presente divulgación;

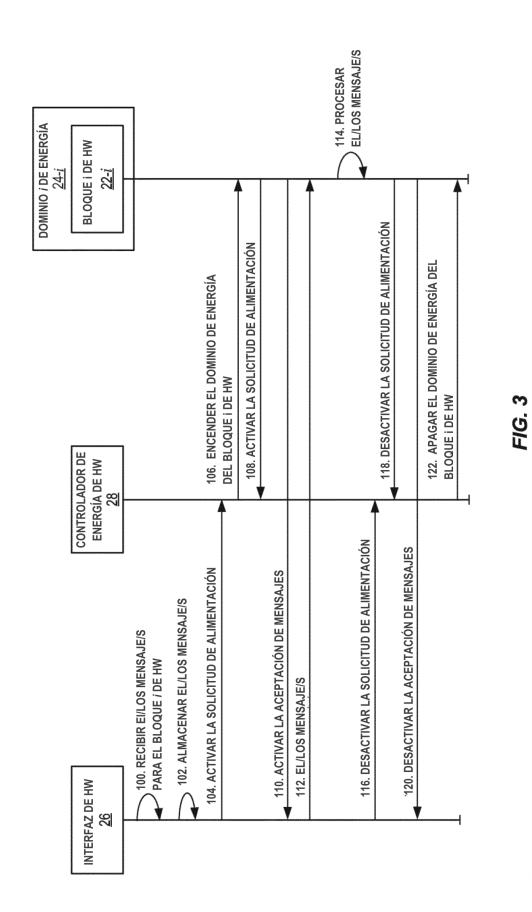

- la figura 3 ilustra el funcionamiento del sistema de hardware de la figura 2 de acuerdo con una realización de la presente descripción;

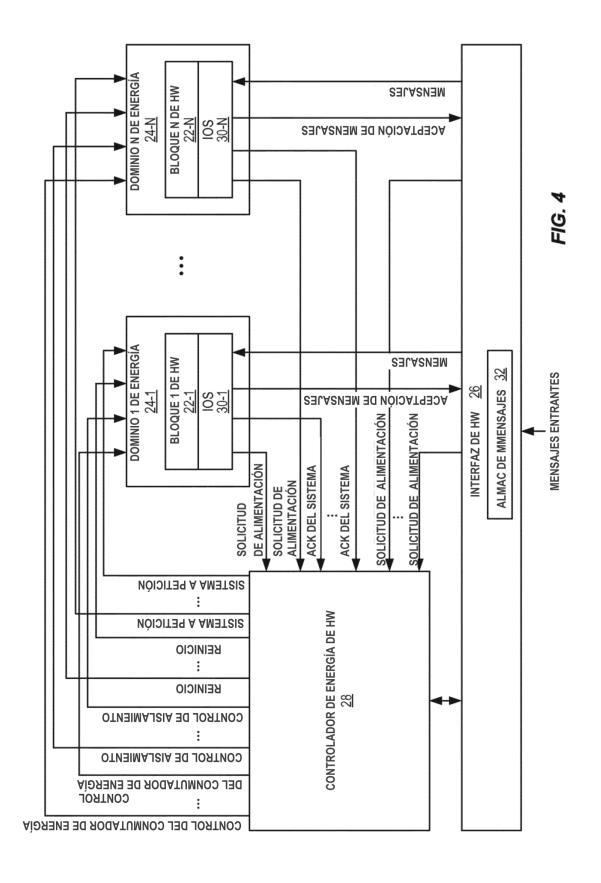

- 20 la figura 4 ilustra un sistema de hardware que proporciona un flujo totalmente automático para el encendido y el apagado de dominios de potencia sin implicación de software de acuerdo con otra realización de la presente divulgación;

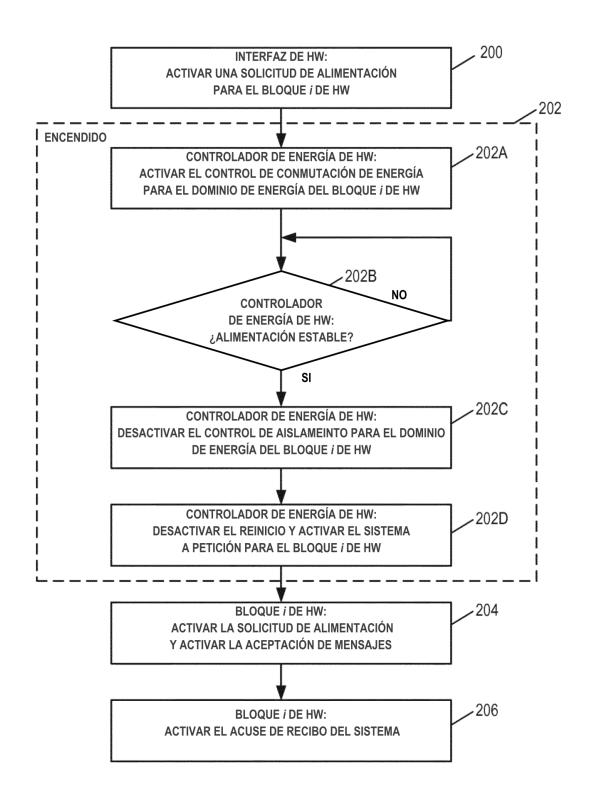

- la figura 5 ilustra un procedimiento de encendido realizado por el sistema de hardware de la figura 4 para encender un dominio de potencia de acuerdo con una realización de la presente divulgación;

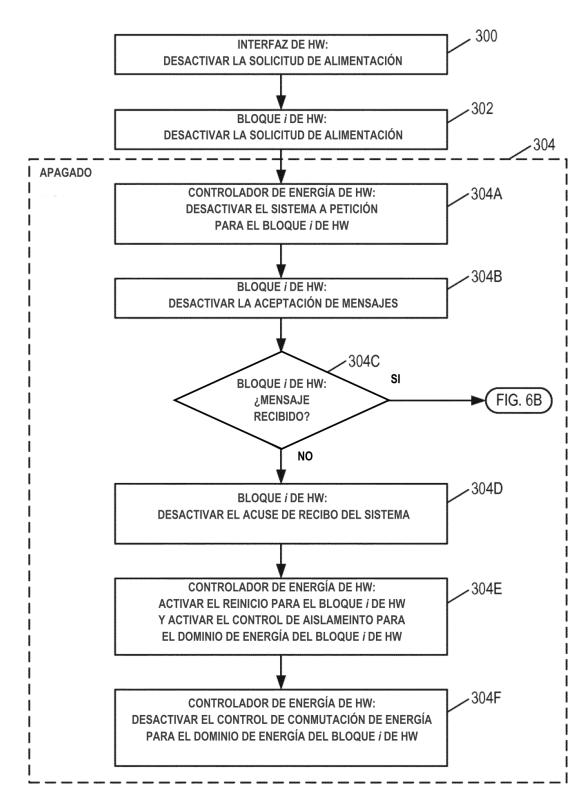

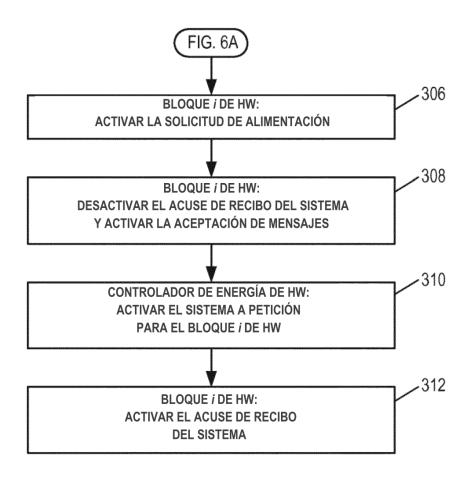

- las figuras 6A y 6B ilustran un procedimiento de apagado realizado por el sistema de hardware de la figura 4 para apagar un dominio de potencia de acuerdo con una realización de la presente divulgación;

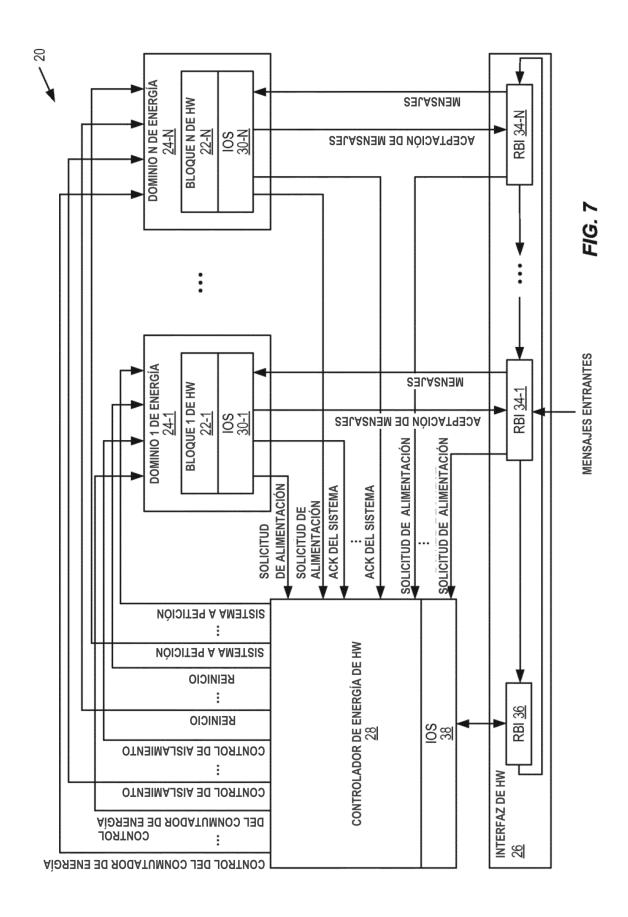

- 30 la figura 7 ilustra un sistema de hardware que proporciona un flujo totalmente automático para el encendido y el apagado de dominios de potencia sin implicación de software de acuerdo con otra realización de la presente divulgación;

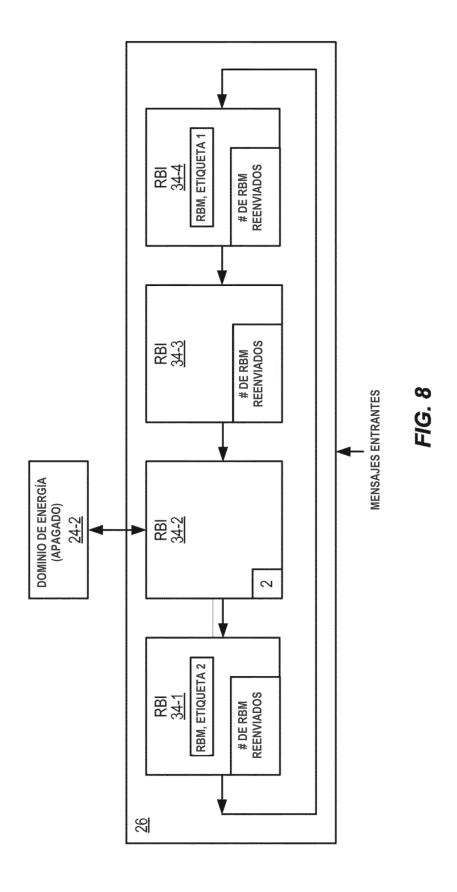

- la figura 8 ilustra el funcionamiento del bus de anillo de la figura 7 para proporcionar almacenamiento de mensajes de acuerdo con una realización de la presente divulgación;

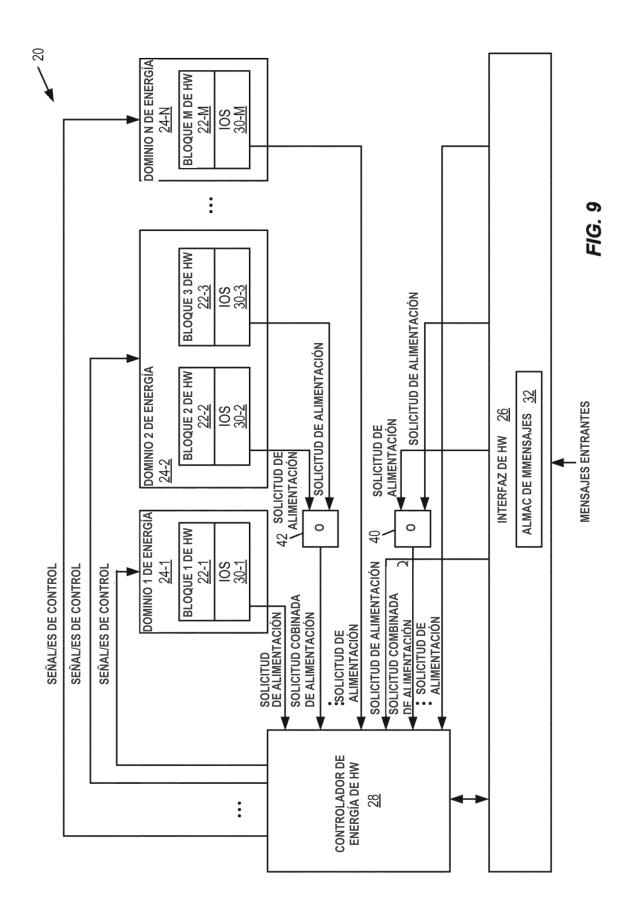

- la figura 9 ilustra un sistema de hardware que proporciona un flujo totalmente automático para el encendido y el apagado de dominios de potencia sin implicación de software de acuerdo con otra realización de la presente divulgación;

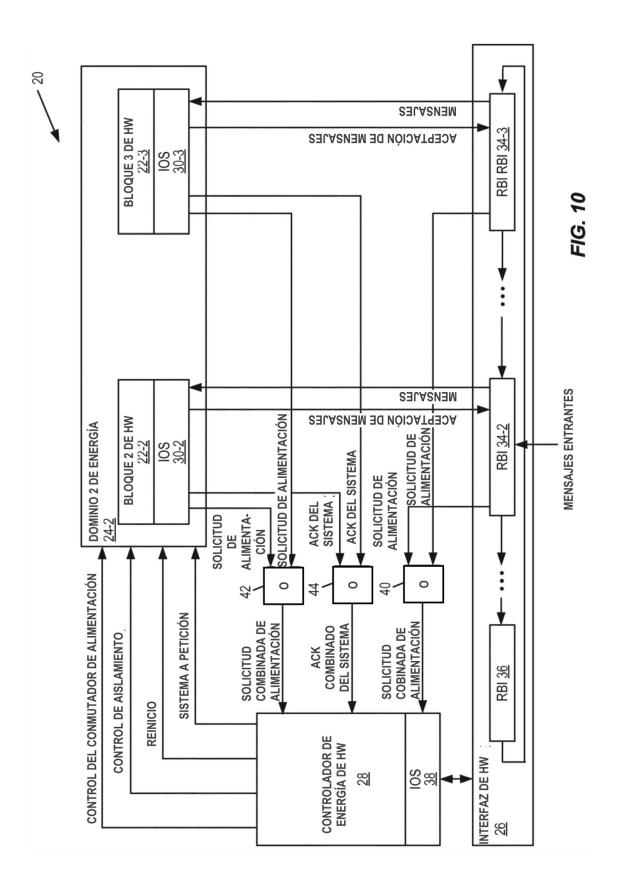

- la figura 10 ilustra el sistema de hardware de la figura 9 en el que la interfaz de hardware se implanta como un bus de anillo de acuerdo con una realización de la presente descripción;

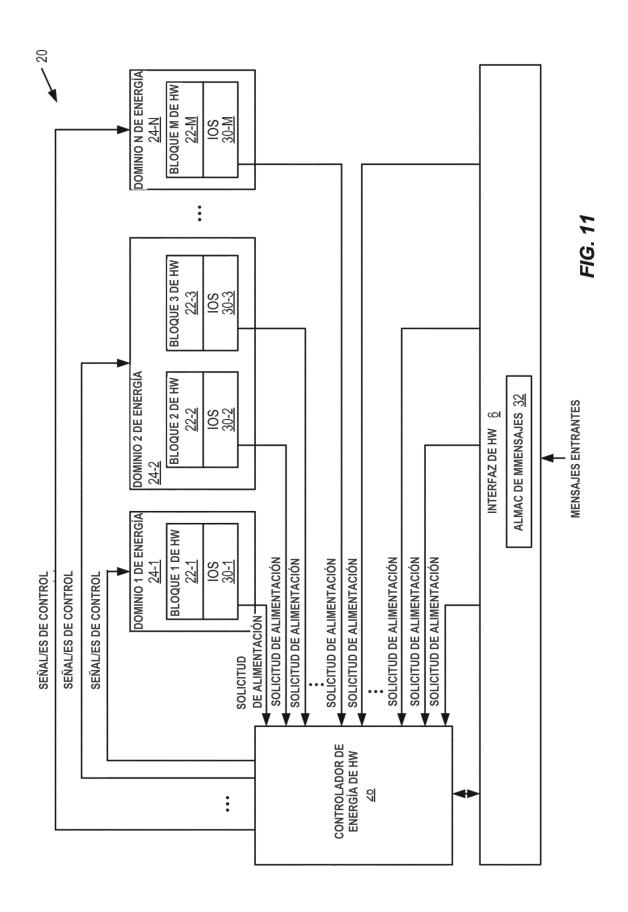

- la figura 11 ilustra un sistema de hardware que proporciona un flujo totalmente automático para el encendido y el apagado de dominios de potencia sin implicación de software de acuerdo con otra realización de la presente divulgación;

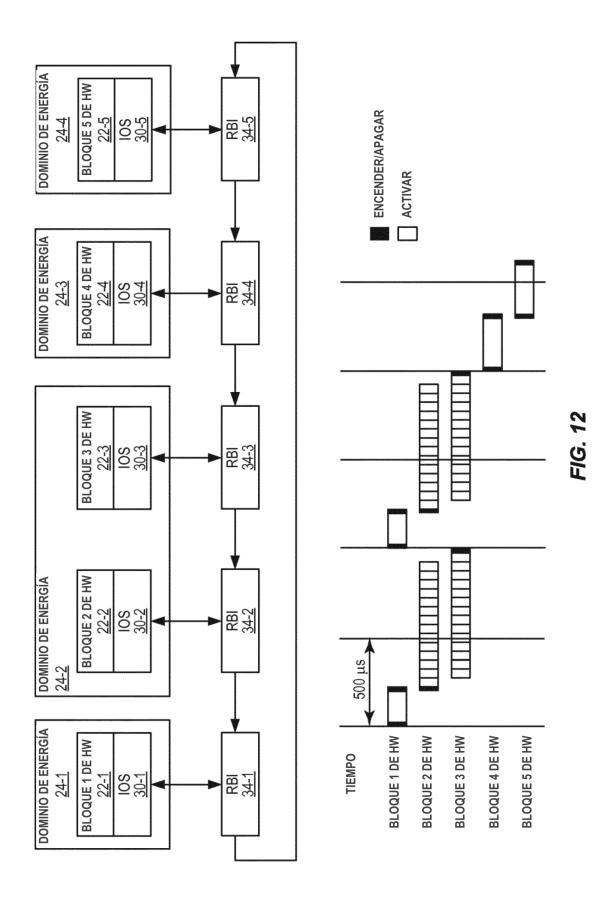

- la figura 12 ilustra ejemplos del encendido, del apagado y de los tiempos activos para un ejemplo de un sistema de hardware que proporciona un flujo totalmente automático para el encendido y el apagado de dominios de potencia sin implicación de software de acuerdo con otra realización de la presente divulgación; y

- la figura 13 ilustra un sistema de hardware que proporciona un flujo totalmente automático para el encendido y el apagado de dominios de potencia sin implicación de software de acuerdo con otra realización de la presente divulgación.

## Descripción detallada

40

50

55

- Las realizaciones expuestas a continuación representan información que permite a el experto en la técnica poner en práctica las realizaciones e ilustrar el mejor modo de practicar las realizaciones. Al leer la siguiente descripción a la luz de las figuras de los dibujos que se acompañan, el experto en la técnica comprenderá los conceptos de la divulgación y reconocerá las aplicaciones de aquellos conceptos que no se abordan particularmente en el presente documento. Debe entenderse que estos conceptos y aplicaciones caen dentro del alcance de la divulgación y las reivindicaciones adjuntas.

- 65 Los sistemas y métodos que se describen en el presente documento proporcionan flujo totalmente automático para el encendido y el apagado de los dominios de potencia sin la implicación de software. A este respecto, la figura 2

ilustra un sistema 20 de hardware (HW) que proporciona un flujo totalmente automático para el encendido y el apagado de dominios de potencia sin implicación de software de acuerdo con una realización de la presente divulgación. Obsérvese que, si bien no se requiere software, el software puede utilizarse como un activador adicional para encender o apagar los dominios de potencia. Como se ilustra, el sistema 20 de HW incluye bloques 22-1 a 22-N de HW (generalmente se denominan colectivamente "bloques 22 de HW" e individualmente "bloque 22 de HW") implantados en los correspondientes dominios 24-1 a 24-N de potencia (generalmente se denominan colectivamente "dominios 24 de potencia" e individualmente "dominio 24 de potencia"). En particular, los bloques 22 de HW son bloques de componentes de hardware que funcionan para procesar mensajes recibidos mediante una interfaz 26 de HW. Los bloques 22 de HW procesan los mensajes y no retienen ni los mensajes ni los resultados del procesamiento de los mensajes en los bloques 22 de HW ellos mismos y, en cuanto tal, pueden apagarse cuando están parados o inactivos. En este ejemplo, cada bloque 22 de HW se implanta en un dominio 24 de potencia separado. En otras palabras, cada dominio 24 de potencia incluye un solo bloque 22 de HW. Sin embargo, el sistema 20 de HW no está limitado al mismo. Por ejemplo, como se analiza a continuación, un dominio 24 de potencia puede incluir múltiples bloques 22 de HW.

15

20

25

65

10

El sistema 20 de HW también incluye la interfaz 26 de HW y un controlador 28 de potencia. Los bloques 22-1 a 22-N de HW están acoplados comunicativamente a la interfaz 26 de HW mediante correspondientes tomas de entrada y salida (IOS) 30-1 a 30-N (generalmente se denominan colectivamente "IOS 30" e individualmente "IOS 30"). Como se analiza a continuación, en una realización, la interfaz 26 de HW es un bus de anillo; sin embargo, la interfaz 26 de HW no está limitada a un bus de anillo y puede implantarse como cualquier tipo adecuado de interfaz. El controlador 28 de potencia de HW incluye, en una realización, hardware dedicado para controlar cada uno de los dominios 24 de potencia. Es importante destacar que el sistema 20 de HW y, en particular, los bloques 22 de HW, la interfaz 26 de HW, el controlador 28 de potencia de HW y las IOS 30 están implantados en hardware y funcionan para proporcionar un flujo totalmente automático para el encendido y el apagado de los dominios 24 de potencia sin implicación de software. En una realización particular, el sistema 20 de HW se implanta como o como parte de un circuito integrado específico de aplicación (ASIC) o circuito integrado similar.

En general, la interfaz 26 de HW recibe mensajes para los bloques 22 de HW. En otras palabras, la interfaz 26 de HW recibe mensajes de otro sistema de hardware y/o software que puede ser implantado en el mismo circuito 30 integrado o externo al circuito integrado en el que se implanta el sistema 20 de HW. Por ejemplo, si la interfaz 26 de HW es un bus de anillo, los mensajes se hacen entrar al bus de anillo desde algún otro sistema de hardware y/o software. Sin embargo, la interfaz 26 de HW se implanta en hardware y, de este modo, la recepción de los mensajes por la interfaz 26 de HW es una función de hardware. Al recibir un mensaje para un bloque 22 de HW particular, la interfaz 26 de HW almacena los mensajes en el almacenamiento 32 de mensajes y activa una solicitud de potencia 35 al controlador 28 de potencia de HW para ese bloque 22. La interfaz 26 de HW mantiene la solicitud de potencia para el bloque 22 de HW hasta que no haya más mensajes para que la interfaz 26 de HW haga la entrega al bloque 22 de HW. En respuesta a la activación de la solicitud de potencia de la interfaz 26 de HW para el bloque 22 de HW, el controlador 28 de potencia de HW enciende el dominio 24 de potencia de ese bloque 22 de HW usando una o más señales de control. Cuando el dominio 24 de potencia, y, de este modo, el bloque 22 de HW, está encendido, el bloque 22 de HW activa una solicitud de potencia al controlador 28 de potencia de HW. El bloque 22 de HW mantiene la solicitud de potencia hasta que el bloque 22 de HW ya no necesita potencia. Una vez que tanto la solicitud de potencia desde la interfaz 26 de HW para el bloque 22 de HW como la solicitud de potencia desde el bloque 22 de HW se han desactivado, el controlador 28 de potencia de HW apaga el dominio 24 de potencia del bloque 22 de HW. Para apagar, el controlador 28 de potencia de HW se comunica con el bloque 22 de HW para 45 impedir que el bloque 22 de HW reciba nuevos mensajes dentro del dominio 24 de potencia mientras la potencia se baja y cuando la potencia en el dominio 24 de potencia está apagada. De esta manera, el encendido y el apagado de los dominios 24 de potencia son completamente automáticos. Adicionalmente, dado que el encendido y el apagado están controlados por hardware sin implicación de software, la cantidad de tiempo necesaria para el encendido y el apagado se minimiza, lo que a su vez reduce el tiempo activo del bloque 22 de HW y, de este modo, 50 el consumo de potencia del bloque 22 de HW. Asimismo, al reducir los tiempos de encendido y apagado, los dominios 24 de potencia pueden encenderse y apagarse según sea necesario, lo que a su vez permite reducir las fugas.

La figura 3 ilustra el funcionamiento del sistema 20 de HW de la figura 2 según una realización de la presente descripción. La operación se ilustra con respecto al i-ésimo bloque 22-i de HW (es decir, 1 ≤ i ≤ N) en el i-ésimo dominio 24-i de potencia. Sin embargo, debe apreciarse que esta discusión es igualmente aplicable a los otros bloques 22 de HW. Como se ilustra, la interfaz 26 de HW recibe uno o más mensajes para el bloque 22-i de HW (paso 100). Los mensajes se reciben de algún sistema, componente o dispositivo que, por ejemplo, se implanta dentro del mismo circuito integrado (por ejemplo, dentro del mismo ASIC) o externo al circuito integrado (por ejemplo, externo al ASIC).

En este ejemplo, la interfaz 26 de HW almacena el mensaje o los mensajes dentro del almacenamiento 32 de mensajes de la interfaz 26 de HW (paso 102). Por ejemplo, en algunas realizaciones, la interfaz 26 de HW es un bus de anillo, y el mensaje o los mensajes se almacena/n dentro del bus de anillo enviando los mensajes, a través del bus de anillo, desde una interfaz de bus de anillo, para uno de los bloques 22 de HW, a una interfaz de bus de anillo para el siguiente bloque 22 de HW, y así sucesivamente. Sin embargo, el almacenamiento del mensaje o de los

mensajes no está limitado a los mismos. Se puede utilizar cualquier mecanismo de almacenamiento adecuado (por ejemplo, una memoria). El mensaje o los mensajes pueden almacenarse alternativamente de forma externa a la interfaz 26 de HW. En respuesta a la recepción del mensaje o de los mensajes, la interfaz 26 de HW activa una solicitud de potencia al controlador 28 de potencia de HW para el bloque 22-i de HW (paso 104) En algunas realizaciones, la solicitud de potencia se activa activando una señal correspondiente (por ejemplo, afirmando una señal a un "1" lógico). En respuesta a la activación de la solicitud de potencia para el bloque 22-i de HW, el controlador 28 de potencia de HW pone en funcionamiento o enciende el dominio 24-i de potencia del bloque 22-i de HW (paso 106).

- En algunas realizaciones, cuando el dominio 24-i de potencia, y, de este modo, el bloque 22-i de HW, está encendido, bloque 22-i de HW activa una solicitud de potencia al controlador 28 de potencia de HW (paso 108). El bloque 22-i de HW mantiene la solicitud de potencia al controlador 28 de potencia de HW hasta que el bloque 22-i de HW ya no necesita potencia (por ejemplo, hasta que el bloque 22-i de HW haya completado el procesamiento de todos los mensajes desde la interfaz 26 de HW y no se hayan recibido nuevos mensajes de la interfaz 26 de HW).

Obsérvese, sin embargo, que ésta es sólo una manera de que el bloque 22-i de HW indique a la interfaz 26 de HW cuándo el bloque 22-i de HW no necesita ya potencia. Por ejemplo, en otras realizaciones, el bloque 22-i de HW puede no activar una solicitud de potencia en el paso 108, y, en cambio, activar una solicitud de apagado cuando el bloque 22-i de HW ya no necesita potencia. Con el fin de comenzar a recibir mensajes desde la interfaz 26 de HW, el bloque 22-i de HW activa un indicador de aceptación de mensajes para la interfaz 26 de HW (paso 110). En respuesta al indicador de aceptación de mensajes activado desde el bloque 22-i de HW, la interfaz 26 de HW envía el mensaje o los mensajes al bloque 22-i de HW (paso 112).

- El bloque 22-i de HW procesa después el mensaje o los mensajes (paso 114). El envío del mensaje o los mensajes desde la interfaz 26 de HW al bloque 22-i de HW y el procesamiento del mensaje o los mensajes por el bloque 22-i de HW continúa hasta que la interfaz 26 de HW no tenga mensajes adicionales que enviar al bloque 22-i de HW y el bloque 22-i de HW haya completado el procesamiento de todos los mensajes. Cuando la interfaz 26 de HW no tiene más mensajes que enviar al bloque 22-i de HW, la interfaz 26 de HW desactiva la solicitud de potencia al controlador 28 de potencia de HW para el bloque 22-i de HW (paso 116). De manera similar, cuando el bloque 22-i de HW ha completado el procesamiento de los mensajes recibidos desde la interfaz 26 de HW, el bloque 22-i de HW desactiva la solicitud de potencia al controlador 28 de potencia de HW para el bloque 22-i de HW (paso 118) En respuesta a la desactivación de la solicitud de potencia del bloque 22-i de HW de la interfaz 26 de HW y a la desactivación de la solicitud de potencia del bloque 22-i de HW, el controlador 28 de potencia de HW interrumpe el funcionamiento o apaga el dominio 24-i de potencia del bloque 22-i de HW (paso 122).

- Las figuras 4, 5, 6A y 6B ilustran el sistema 20 de HW, así como el encendido y el apagado del sistema 20 de HW de acuerdo con otra realización de la presente descripción. Como se ilustra en la figura 4, el sistema 20 de HW es sustancialmente el mismo que se ilustra en la figura 2. Como se ilustra en la figura 5, un procedimiento de encendido para el i-ésimo bloque 22-i de HW comienza cuando la interfaz 26 de HW recibe y almacena uno o más mensajes para el bloque 22-i de HW, como se describió anteriormente con respecto a los pasos 100 y 102 de la figura 3. En respuesta a la recepción del mensaje o de los mensajes para el bloque 22-i de HW, la interfaz 26 de HW activa una solicitud de potencia al controlador 28 de potencia de HW para el bloque 22-i de HW (paso 200). Este paso corresponde al paso 104 de la figura 3. En respuesta, el controlador 28 de potencia de HW enciende el dominio 24-i de potencia del bloque 22-i de HW (paso 202). El paso 202 corresponde al paso 106 de la figura 3.

- 45 Más específicamente, en esta realización, el controlador 28 de potencia de HW enciende el dominio 24-i de potencia del bloque 22-i de HW mediante la activación del control de conmutador de potencia para el dominio 24-i de potencia del bloque 22-i de HW (paso 202A). Si bien no se ilustra, el dominio 24-i de potencia recibe potencia a través de uno o más conmutadores de potencia. Al activar el control de conmutador de potencia para el dominio 24-i de potencia, se cierran los conmutadores de potencia, de tal modo que se aplica potencia al dominio 24-i de potencia. Después 50 de activar el control de conmutador de potencia, el controlador 28 de potencia de HW espera hasta que la potencia para el dominio 24-i de potencia es estable (paso 202B). En una realización, el controlador 28 de potencia de HW espera una cantidad de tiempo predefinida después de la cual se sabe que la potencia para el dominio 24-i de potencia va a ser estable. Una vez que la potencia para el dominio 24-i de potencia es estable, el controlador 28 de potencia de HW desactiva el control de aislamiento para el dominio 24-i de potencia del bloque 22-i de HW (paso 55 202C). Aunque no se ilustra, el dominio 24-i de potencia puede incluir en una realización una o más células de aislamiento o circuitería de aislamiento que aísle el bloque 22-i de HW cuando el dominio 24-i de potencia se apague con el fin de, por ejemplo, impedir fugas de potencia desde los otros dominios 24 de potencia al bloque 22-i de HW. La desactivación del control de aislamiento retira el aislamiento del bloque 22-i de HW (es decir, desactiva la/s célula/s de aislamiento o la circuitería de aislamiento). El controlador 28 de potencia de HW también desactiva un 60 reinicio para el bloque 22-i de HW y activa un sistema a petición para el bloque 22-i de HW (paso 202D).

- En este punto, el dominio 24-i de potencia y, de este modo, el bloque 22-i de HW en el dominio 24-i de potencia son encendidos. Una vez encendidos, el bloque 22-i de HW activa una solicitud de potencia al controlador 28 de potencia de HW y activa un indicador de aceptación de mensajes a la interfaz 26 de HW (paso 204). Adicionalmente, en algunas realizaciones, el bloque 22-i de HW activa un acuse de recibo del sistema al controlador 28 de potencia de HW (paso 206). Desde este punto, el funcionamiento procede como se discutió anteriormente. El bloque 22-i de

HW recibe y procesa el mensaje o los mensajes de la interfaz 26 de HW. El bloque 22-i de HW queda encendido hasta que la interfaz 26 de HW no tiene más mensajes para entregar al bloque 22-i de HW y el bloque 22-i de HW ha completado el procesamiento de todos los mensajes recibidos desde la interfaz 26 de HW.

- Como se ilustra en las figuras 6A y 6B, un procedimiento de encendido durante el i-ésimo bloque 22-i de HW comienza cuando la interfaz 26 de HW desactiva la solicitud de potencia al controlador 28 de potencia de HW para el bloque 22-i de HW, y el bloque 22-i de HW desactiva la solicitud de potencia al controlador 28 de potencia de HW (pasos 300 y 302). Los pasos 300 y 302 corresponden a los pasos 116 y 118 de la figura 3. En respuesta, el controlador 28 de potencia de HW apaga el dominio 24-i de potencia del bloque 22-i de HW (paso 304). El paso 304 corresponde al paso 122 de la figura 3. Más específicamente, el controlador 28 de potencia de HW desactiva el sistema a petición para el bloque 22-i de HW (paso 304A). En respuesta, el bloque 22-i de HW desactiva el indicador de aceptación de mensajes a la interfaz 26 de HW (paso 304B). De esta manera, el bloque 22-i de HW informa a la interfaz 26 de HW de que el bloque 22-i de HW ya no puede aceptar mensajes de la interfaz 26 de HW.

- En esta realización, el bloque 22-i de HW determina si se recibió un mensaje desde la interfaz 26 de HW mientras se desactivaba el indicador de aceptación de mensajes (paso 304C). Si no fue así, el bloque 22-i de HW desactiva el acuse de recibo del sistema al controlador 28 de potencia de HW (paso 304D). En respuesta, el controlador 28 de potencia de HW activa el reinicio para el bloque 22-i de HW y activa el control de aislamiento para el dominio 24-i de potencia del bloque 22-i de HW (paso 304E). Adicionalmente, el controlador 28 de potencia de HW desactiva el control de conmutador de potencia para el dominio 24-i de potencia del bloque 22-i de HW (paso 304F). En este momento, el apagado se ha completado.

- Volviendo al paso 304C, si se recibió un mensaje desde la interfaz 26 de HW mientras se desactivaba el indicador de aceptación de mensajes, la reducción del suministro se termina. Más específicamente, en esta realización, el bloque 22-i de HW activa la solicitud de potencia al controlador 28 de potencia de HW (paso 306). Adicionalmente, el bloque 22-i de HW desactiva el acuse de recibo del sistema al controlador 28 de potencia de HW y activa el indicador de aceptación de mensajes a la interfaz 26 de HW (paso 308). En respuesta, el controlador 28 de potencia de HW activa el sistema a petición para el bloque 22-i de HW (paso 310). En respuesta, el bloque 22-i de HW activa el acuse de recibo del sistema al controlador 28 de potencia de HW (paso 312).

- Cabe señalar que la figura 5 y las figuras 6A y 6B ilustran realizaciones de los procedimientos de encendido y apagado, respectivamente. Sin embargo, no todas las acciones ilustradas en la figura 5 y las figuras 6A y 6B pueden incluirse en todas las implantaciones. Por ejemplo, en algunas implantaciones, el acuse de recibo del sistema desde el bloque 22-i de HW al controlador 28 de potencia de HW puede no estar incluido. Como otro ejemplo, con respecto al procedimiento de apagado de las figuras 6A y 6B, los pasos 304C y 306-312 pueden no estar incluidos en algunas realizaciones.

35

40

45

50

55

- La figura 7 ilustra el sistema 20 de HW de acuerdo con otra realización en la que la interfaz 26 de HW es un bus de anillo. Como se ilustra, la interfaz 26 de HW incluye interfaces de bus de anillo (RBI) 34-1 a 34-N (generalmente se denominan colectivamente "RBI 34" e individualmente "RBI 34"), cada una responsable de entregar mensajes a uno de los bloques 22 de HW correspondientes. En este ejemplo, la interfaz 26 de HW también incluye una RBI 36 para entregar mensajes al controlador 28 de potencia de HW. El controlador 28 de potencia de HW está acoplado comunicativamente con la RBI 36 a través de un IOS 38. El sistema 20 de HW funciona de la misma manera como se describió anteriormente con respecto al sistema 20 de HW de la figura 4.

- Como se discutió anteriormente, la interfaz 26 de HW incluve el almacenamiento 32 de mensaies para almacenar mensajes hasta que los bloques 22 de HW están encendidos y listos para aceptar mensajes. Si bien los mensajes pueden almacenarse de cualquier manera adecuada (por ejemplo, dentro de la memoria interna o asociada con la interfaz 26 de HW), la figura 8 ilustra el funcionamiento del bus de anillo de la figura 7 para proporcionar almacenamiento de mensajes de acuerdo con una realización de la presente divulgación. En esta realización, la característica de almacenamiento 32 de mensajes se implanta dentro del bus de anillo. Como se ilustra, cada RBI 34 almacena un número indicativo de la cantidad de mensajes (denominados "mensajes de bus de anillo" (RBM)) que ha recibido el bus de anillo para el bloque 22 de HW correspondiente. En este ejemplo, el dominio 24-2 de potencia está apagado (es decir, apagado). Mientras el dominio 24-2 de potencia está apagado, el bus de anillo recibe dos mensajes para el bloque 22-2 de HW en el dominio 24-2 de potencia. Como tal, el RBI 34-2 almacena el número "2" para indicar que se han recibido dos mensajes, y que están almacenados en el bus de anillo para el bloque 22-2 de HW. El bus de anillo almacena los mensajes al continuar propagando los mensajes alrededor del bus de anillo. Adicionalmente, en este ejemplo, los mensajes se emiten a la manera de primero en entrar, primero en salir (FIFO). Más específicamente, en este ejemplo, los mensajes están etiquetados para indicar el orden en que los mensajes fueron recibidos por el bus de anillo. Usando estas etiquetas, los mensajes pueden enviarse al bloque 22-2 de HW en el mismo orden en que los mensajes fueron recibidos por el bus de anillo una vez que el bloque 22-2 de HW está encendido y listo para aceptar mensajes.

- En las realizaciones descritas anteriormente, los dominios 24 de potencia incluyen cada uno un solo bloque 22 de HW. Sin embargo, el sistema 20 de HW no se limita a ello. A este respecto, la figura 9 ilustra el sistema 20 de HW de acuerdo con una realización en la que al menos uno de los dominios 24 de potencia incluye múltiples bloques 22

de HW. Específicamente, el sistema 20 de HW incluye dominios 24-1 a 24-N de potencia y bloques 22-1 a 22-M de HW, donde M > N. En este ejemplo, el dominio 24-2 de potencia incluye los bloques 22-2 y 22-3 de HW. Si bien no se ilustra, otros dominios 24 de potencia pueden incluir uno, dos o más bloques 22 de HW. Usando el dominio 24-2 de potencia como ejemplo, la interfaz 26 de HW proporciona solicitudes de potencia separadas para los bloques 22-2 y 22-3 de HW. De este modo, cuando la interfaz 26 de HW recibe un mensaje o unos mensajes para el bloque 22-2 de HW, la interfaz 26 de HW activa la solicitud de potencia para el bloque 22-2 de HW, la interfaz 26 de HW activa la solicitud de potencia para el bloque 22-3 de HW.

En esta realización, el sistema 20 de HW incluye una puerta lógica O 40 que combina las solicitudes de potencia de la interfaz 26 de HW para los bloques 22-2 y 23-3 de HW en el dominio 24-2 de potencia para proporcionar una solicitud combinada de potencia para el dominio 24-2 de potencia. De este modo, si una o ambas solicitudes de potencia de la interfaz 26 de HW para los bloques 22-2 y 22-3 de HW son activadas, entonces, se activa la solicitud de potencia combinada para el dominio 24-2 de potencia. En respuesta a la activación de la solicitud de potencia combinada para el dominio 24-2 de potencia, el controlador 28 de potencia de HW enciende los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia como se describió anteriormente. Por ejemplo, en una realización, el controlador 28 de potencia de HW activa el control de conmutador de potencia (es decir, cierra los conmutadores de potencia) para el dominio 24-2 de potencia, desactiva las células de aislamiento o la circuitería de aislamiento para el dominio 24-2 de potencia, desactiva las señales de reinicio para los bloques 22-2 y 22-3 de HW, y activa un sistema a petición para los bloques 22-2 y 22-3 de HW.

25

30

35

40

45

50

55

60

65

Una vez encendidos, los bloques 22-2 y 22-3 de HW, activan solicitudes de potencia al controlador 28 de potencia de HW y activan los indicadores de aceptación de mensajes a la interfaz 26 de HW (no mostrado en la figura 9). En esta realización, las solicitudes de potencia de los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia son procesadas mediante función lógica O mediante una puerta O 42 para proporcionar una solicitud de potencia combinada de los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia. El controlador 28 de potencia de HW mantiene la potencia en el dominio 24-2 de potencia hasta que tanto la solicitud de potencia combinada de los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia se desactivan (es decir, que las solicitudes de potencia de ambos bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia se desactivan) como se desactiva la solicitud de potencia combinada de la interfaz 26 de HW para el dominio 24-2 de potencia. En ese momento, el controlador 28 de potencia de HW apaga el dominio 24-2 de potencia de la manera descrita anteriormente. Por ejemplo, el controlador 28 de potencia de HW desactiva el sistema a petición para los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia. En respuesta, los bloques 22-2 y 22-3 de HW desactivan sus indicadores de aceptación de mensajes a la interfaz 26 de HW. Si los bloques 22-2 y 22-3 de HW no reciben ningún mensaje mientras se desactivan sus indicadores de aceptación de mensajes, los bloques 22-2 y 22-3 de HW desactivan sus acuses de recibo del sistema (que pueden combinarse para proporcionar un acuse de recibo combinado del sistema para el dominio 24-2 de potencia). En respuesta, el controlador 28 de potencia de HW activa una señal de reinicio para los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia y activa la/s célula/s o la circuitería de aislamiento para el dominio 24-2 de potencia. El controlador 28 de potencia de HW desactiva también el control de conmutador de potencia para el dominio 24-2 de potencia. Usando la arquitectura de la figura 9, el controlador 28 de potencia de HW no necesita tener conocimiento sobre el número de bloques 22 de HW en cada dominio 24 de potencia. Más bien, al generar las solicitudes de potencia combinadas, los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia son vistos por el controlador 28 de potencia de HW como un solo bloque 22 combinado de HW en el dominio 24-2 de potencia.

La figura 10 ilustra una realización del sistema 20 de HW de la figura 9 en la que la interfaz 26 de HW es un bus de anillo como se describió anteriormente. Obsérvese que, para mayor claridad, sólo se ilustra el dominio 24-2 de potencia en la figura 10. Adicionalmente, la figura 10 ilustra también una puerta lógica O 44 que combina los acuses de recibo del sistema de los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia para proporcionar un acuse de recibo de sistema combinado al controlador 28 de potencia de HW para el dominio 24-2 de potencia. De otro modo, el sistema 20 de HW funciona como se describió anteriormente con respecto a la figura 9.

La figura 11 ilustra una realización similar a la de la figura 9 pero donde se proporcionan solicitudes de potencia separadas para los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia al controlador 28 de potencia de HW. El procesamiento mediante función lógica O de las solicitudes de potencia se lleva a cabo dentro del controlador 28 de potencia de HW. Específicamente, el controlador 28 de potencia de HW funciona encendiendo el dominio 24-2 de potencia cuando la solicitud de potencia de la interfaz 26 de HW para el bloque 22-2 de HW y/o la solicitud de potencia de la interfaz 26 de HW se activa/n. A la contra, el controlador 28 de potencia de HW funciona apagando el dominio 24-2 de potencia cuando las solicitudes de potencia de los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia son ambas desactivadas y las solicitudes de potencia de la interfaz 26 de HW para los bloques 22-2 y 22-3 de HW en el dominio 24-2 de potencia son ambas desactivadas. De otro modo, el funcionamiento del sistema 20 de HW es como se describió anteriormente.

La figura 12 ilustra ejemplos de encendido, apagado y tiempos activos para un ejemplo del sistema 20 de HW. En este ejemplo, el sistema 20 de HW incluye cinco bloques 22 de HW y cuatro dominios 24 de potencia, en el que los

dos bloques 22-2 y 22-3 de HW están incluidos en el dominio 24-2 de potencia. Como se ilustra, los bloques 22 de HW tienen tiempos cortos de encendido y apagado (por ejemplo, unos pocos microsegundos).

La figura 13 ilustra el sistema 20 de HW de acuerdo con otra realización de la presente descripción. Esta realización es para ilustrar que el sistema 20 de HW de cualquiera de las realizaciones descritas anteriormente puede, en algunas realizaciones, incluir un dominio asíncrono 46. En este ejemplo, los dominios 24-1 y 24-2 de potencia se implantan en el dominio asíncrono 46. Una interfaz asíncrona 48 permite la comunicación entre la interfaz 26 de HW y el dominio asíncrono 46. De otro modo, el sistema 20 de HW funciona como se describe con respecto a cualquiera de las realizaciones del sistema 20 de HW descritas en el presente documento.

10

15

Los sistemas y métodos divulgados en el presente documento proporcionan numerosos beneficios y ventajas sobre los dominios de potencia convencionales controlados por software. Si bien no se limitan a ningún beneficio o ventaja particulares, algunos ejemplos son los siguientes. La fuga puede reducirse utilizando las solicitudes de potencia desde la interfaz 26 de HW y los bloques 22 de HW para activar el encendido y el apagado de los dominios 24 de potencia correspondientes, así como mover el control del encendido y el apagado de los dominios 24 de potencia al hardware dedicado (es decir, al controlador 28 de potencia de HW) con un conjunto de señales de control, máquinas de estado y comunicación interna con los bloques 22 de HW.

20

Como otro ejemplo, al permitir que los dominios 24 de potencia se activen, o se enciendan, sólo cuando sea necesario, así como al minimizar el tiempo para encender y apagar los dominios 24 de potencia, el consumo de potencia se reduce, tanto cuando los bloques 22 de HW en los dominios 24 de potencia están parados, o inactivos, como cuando los bloques 22 de HW en los dominios 24 de potencia están funcionando o activos (por ejemplo, minimizando el tiempo de encendido y apagado y, de este modo, la cantidad de tiempo que los dominios 24 de potencia están activos).

25

Como otro ejemplo, el uso de los dominios controlados 24 de potencia de HW permite que la potencia para un dominio 24 de potencia sólo se conecte cuando sea necesario, sin sobrecarga introducida por el control de software. El control de HW de los dominios 24 de potencia también permite una granularidad alta de los dominios 24 de potencia con dominios en el nivel de bloque de HW o en grupos de nivel de bloques de HW.

30

Como otro ejemplo más, mientras que los sistemas y métodos descritos anteriormente proporcionan un flujo totalmente automático para encender y apagar los dominios 24 de potencia sin la implicación de software, el software puede, en algunas implantaciones, usarse además de los sistemas y métodos descritos anteriormente como otro mecanismo para activar el encendido o el apagado. Por ejemplo, el software puede usarse para forzar el encendido o apagado de un dominio 24 de potencia.

35

40

50

Adicionalmente, obsérvese que los sistemas y métodos descritos en el presente documento pueden usarse junto con otras técnicas de reducción de fugas para reducir adicionalmente las fugas. Por ejemplo, en una realización, la solicitud de potencia desde la interfaz 26 de HW al controlador 28 de potencia de HW para un bloque 22 de HW en un dominio 24 de potencia puede usarse adicionalmente para activar una solicitud de reloj mediante la cual se activa un reloj al bloque 22 HW. El reloj puede ser activado por el controlador 28 de potencia de HW, por ejemplo activando una señal de habilitación para el reloj para el dominio 24 de potencia, o, específicamente, para el reloj para el bloque 22 de HW.

45 Los siguientes acrónimos son utilizados en toda esta descripción.

• ASIC Circuito integrado específico de aplicación

FIFO Primero en entrar, primero en salir

HW Equipo físico informático (Hardware)

IOS Toma de entrada y salida

RBI Interfaz de bus de anillo

RBM Mensaje de bus de anillo

El experto en la técnica reconocerá mejoras y modificaciones a las realizaciones de la presente divulgación. Todas tales mejoras y modificaciones se consideran dentro del alcance de los conceptos divulgados en el presente documento tal como se define en las reivindicaciones adjuntas.

#### REIVINDICACIONES

- 1. Un sistema (20) de hardware que comprende:

- 5 una pluralidad de bloques (22) de hardware que comprenden, cada uno, uno o más componentes de hardware;

un controlador (28) de potencia de hardware configurado para controlar una pluralidad de dominios (24) de potencia del sistema (20) de hardware, comprendiendo la pluralidad de dominios (24) de potencia dominios (24) de potencia de la pluralidad de bloques (22) de hardware; y

10

- una interfaz (26) de hardware, en la que la interfaz de hardware es un bus de anillo, acoplada comunicativamente con cada bloque de la pluralidad de bloques (22) de hardware a través de una correspondiente toma (30) de entrada y salida y configurada para:

- 15 recibir al menos un mensaje para un primer bloque de hardware de la pluralidad de bloques (22) de hardware;

- almacenar el al menos un mensaje;

- en respuesta a la recepción del al menos un mensaje para el primer bloque (22) de hardware, activar una solicitud

de potencia desde la interfaz (26) de hardware al controlador (28) de potencia de hardware mediante la afirmación de una señal lógica correspondiente, para solicitar por ello que se encienda el dominio de potencia del primer bloque (22) de hardware;

- recibir una indicación desde el primer bloque (22) de hardware de que el bloque (22) de hardware está listo para aceptar mensajes desde la interfaz (26) de hardware; y

- proporcionar el al menos un mensaje al primer bloque (22) de hardware en respuesta a recibir la indicación del primer bloque (22) de hardware de que el primer bloque (22) de hardware está listo para aceptar mensajes desde la interfaz (26) de hardware;

30

- en el que cada uno de la pluralidad de bloques (22) de hardware está configurado para activar un indicador de aceptación de mensajes a la interfaz de hardware con anterioridad a recibir mensajes desde la interfaz (26) de hardware.

- 2. El sistema (20) de hardware de la reivindicación 1, en el que el controlador (28) de potencia de hardware está configurado para encender el dominio (24) de potencia del primer bloque (22) de hardware en respuesta a la activación de la solicitud de potencia desde la interfaz (26) de hardware.

- 3. El sistema de hardware de la reivindicación 2, en el que el primer bloque (22) de hardware está configurado para, en respuesta al dominio (24) de potencia del primer bloque (22) de hardware que se está encendiendo, activar una solicitud de potencia del primer bloque (22) de hardware al controlador (28) de potencia de hardware para solicitar por ello que se mantenga la potencia para el primer bloque (22) de hardware hasta que se desactive la solicitud de potencia del primer bloque (22) de hardware.

- 4. El sistema de hardware de la reivindicación 3, en el que la interfaz (26) de hardware está configurada adicionalmente para desactivar la solicitud de potencia desde la interfaz (26) de hardware al controlador (28) de potencia de hardware al determinar que no hay más mensajes recibidos por la interfaz (26) de hardware para el primer bloque (22) de hardware que se vayan a proporcionar al primer bloque (22) de hardware.

- 50 5. El sistema (20) de hardware de la reivindicación 1, en el que, en respuesta a la activación de la solicitud de potencia desde la interfaz (26) de hardware, el controlador (28) de potencia de hardware está configurado para:

- encender el dominio (24) de potencia del primer bloque (22) de hardware;

- esperar a que la potencia para el dominio (24) de potencia del primer bloque (22) de hardware sea estable; y

- cuando la potencia para el dominio (24) de potencia del primer bloque (22) de hardware es estable, entonces activar el primer bloque (22) de hardware.

- 60 6. El sistema (20) de hardware de la reivindicación 5, en el que, con el fin de activar el primer bloque (22) de hardware, el controlador (28) de potencia de hardware está configurado para:

- desactivar una o más células de aislamiento que funcionan para aislar el dominio (24) de potencia cuando se desactiva la potencia para el dominio (24) de potencia;

65

desactivar un reinicio del primer bloque (22) de hardware; y

activar un sistema a petición para el primer bloque (22) de hardware para informar por ello al primer bloque (22) de hardware de que se activa la potencia para el primer bloque (22) de hardware.

5 7. El sistema (20) de hardware de la reivindicación 5, en el que el primer bloque (22) de hardware está configurado para, en respuesta a ser activado:

activar una solicitud de potencia desde el primer bloque (22) de hardware al controlador (28) de potencia de hardware para solicitar por ello que el controlador (28) de potencia de hardware mantenga la potencia para el primer bloque (22) de hardware hasta que la solicitud de potencia del primer bloque (22) de hardware sea desactivada;

activar una aceptación de mensaje desde el primer bloque (22) de hardware a la interfaz (26) de hardware para indicar por ello que el primer bloque (22) de hardware está listo para aceptar mensajes de la interfaz (26) de hardware; y

activar un acuse de recibo del sistema desde el primer bloque (22) de hardware al controlador (28) de potencia de hardware.

8. El sistema (20) de hardware de la reivindicación 1, en el que el dominio (24) de potencia comprende el primer bloque (22) de hardware y al menos un bloque (22) de hardware adicional, y el sistema (20) de hardware comprende adicionalmente:

circuitería (40) configurada para combinar la solicitud de potencia desde la interfaz (26) de hardware para el primer bloque (22) de hardware y al menos una solicitud de potencia adicional de la interfaz (26) de hardware para el al menos un bloque (22) de hardware adicional en el dominio (24) de potencia para proporcionar una solicitud de potencia combinada desde la interfaz (26) de hardware al controlador (28) de potencia de hardware que se activa cuando una cualquiera o más de entre la solicitud de potencia y la al menos una solicitud de potencia adicional de la interfaz (26) de hardware se activa y se desactiva cuando tanto la solicitud de potencia como la al menos una solicitud de potencia adicional de la interfaz (26) de hardware se desactivan;

en el que el controlador (28) de potencia de hardware está configurado para encender el dominio (24) de potencia en respuesta a la activación de la solicitud de potencia combinada desde la interfaz (26) de hardware.

9. El sistema (20) de hardware de la reivindicación 8 en el que:

después de que se activa la potencia para el dominio (24) de potencia, el primer bloque (22) de hardware se configura adicionalmente para proporcionar una solicitud de potencia desde el primer bloque (22) de hardware para solicitar por ello que se mantenga la potencia para el primer bloque (22) de hardware hasta que la solicitud de potencia del primer bloque (22) de hardware adicional se configura para proporcionar al menos una solicitud de potencia adicional desde el al menos un bloque (22) de hardware adicional para solicitar por ello que se mantenga la potencia para el al menos un bloque (22) de hardware adicional hasta que se desactive la al menos una solicitud de potencia adicional del al menos un bloque (22) de hardware adicional; y

el sistema (20) de hardware comprende adicionalmente circuitería (42) configurada para combinar la solicitud de potencia desde el primer bloque (22) de hardware y la al menos una solicitud de potencia adicional desde el al menos un bloque (22) de hardware adicional para proporcionar una solicitud de potencia combinada del dominio (24) de potencia que se activa cuando un elemento o más de entre las solicitud de potencia desde el primer bloque (22) de hardware y la al menos una solicitud de potencia adicional desde el al menos un bloque (22) de hardware adicional se activa, y se desactiva cuando tanto la solicitud de potencia del primer bloque (22) de hardware como la al menos una solicitud de potencia adicional del al menos un bloque (22) de hardware adicional se desactivan;

en el que el controlador (28) de potencia de hardware está configurado adicionalmente para apagar el dominio (24) de potencia en respuesta a la desactivación de la solicitud de potencia combinada de la interfaz (26) de hardware y a la desactivación de la solicitud de potencia combinada del dominio (24) de potencia.

- 10. El sistema (20) de hardware de la reivindicación 1, en el que el dominio (24) de potencia comprende el primer bloque (22) de hardware y al menos un bloque (22) de hardware adicional, y el controlador (28) de potencia de hardware está configurado para encender el dominio de potencia en respuesta a la activación de una solicitud cualquiera o más de entre la solicitud de potencia de la interfaz (26) de hardware para el primer bloque (22) de hardware y al menos una solicitud de potencia adicional desde la interfaz (26) de hardware para al menos un bloque (22) de hardware adicional en el dominio (24) de potencia.

- 11. El sistema (20) de hardware de la reivindicación 10 en el que:

65

60

55

10

15

25

30

35

después de que se activa la potencia para el dominio (24) de potencia, el primer bloque (22) de hardware se configura adicionalmente para proporcionar una solicitud de potencia desde el primer bloque (22) de hardware para solicitar por ello que se mantenga la potencia para el primer bloque (22) de hardware hasta que la solicitud de potencia del primer bloque (22) de hardware se desactive, y el al menos un bloque (22) de hardware adicional se configura para proporcionar al menos una solicitud de potencia adicional para solicitar por ello que la potencia para el al menos un bloque adicional el bloque (22) de hardware se mantenga hasta que se desactive la al menos una solicitud de potencia adicional del al menos un bloque (22) de hardware adicional; y

- el controlador (28) de potencia de hardware está configurado adicionalmente para apagar el dominio (24) de potencia en respuesta a la desactivación tanto de la solicitud de potencia como de la al menos una solicitud de potencia adicional desde la interfaz (26) de hardware y a la desactivación tanto de la solicitud de potencia del primer bloque (22) de hardware como de la al menos una solicitud de potencia adicional del al menos un bloque (22) de hardware adicional.

- 15 12. Un método para proporcionar control de potencia en un sistema (20) de hardware, comprendiendo, el sistema (20) de hardware, una pluralidad de bloques (22) de hardware, cada uno de los cuales comprende uno o más componentes de hardware, un controlador (28) de potencia de hardware configurado para controlar un pluralidad de dominios (24) de potencia del sistema (20) de hardware que incluye dominios (24) de potencia de la pluralidad de bloques (22) de hardware y una interfaz (26) de hardware en la que la interfaz de hardware es un bus de anillo, acoplado comunicativamente con cada bloque de entre la pluralidad de bloques (22) de hardware mediante una correspondiente toma (30) de entrada y salida, comprendiendo el método:

- recibir (100), mediante la interfaz (26) de hardware, al menos un mensaje para un primer bloque (22) de hardware de la pluralidad de bloques de hardware;

- almacenar (102), mediante la interfaz (26) de hardware, el al menos un mensaje;

25

30

45

50

- activar (104), mediante la interfaz (26) de hardware, en respuesta a la recepción del al menos un mensaje para el primer bloque de hardware, una solicitud de potencia desde la interfaz (26) de hardware al controlador (28) de potencia de hardware, para solicitar por ello que se encienda el dominio de potencia del primer bloque de hardware;

- recibir (110), mediante la interfaz (26) de hardware, una indicación del primer bloque (22) de hardware de que el primer bloque (22) de hardware está listo para aceptar mensajes de la interfaz (26) de hardware; y

- proporcionar (112), mediante la interfaz (26) de hardware, el al menos un mensaje al primer bloque (22) de hardware en respuesta a recibir la indicación del primer bloque (22) de hardware de que el primer bloque (22) de hardware está listo para aceptar mensajes de la interfaz (26) de hardware

- en el que cada uno de la pluralidad de bloques (22) de hardware está configurado para activar un indicador de 40 aceptación de mensajes a la interfaz de hardware antes de recibir mensajes desde la interfaz (26) de hardware.

- 13. El método de la reivindicación 12 que comprende adicionalmente encender (106) el dominio (24) de potencia del primer bloque (22) de hardware, mediante el controlador (28) de potencia de hardware, en respuesta a la activación de la solicitud de potencia desde la interfaz (26) de hardware.

- 14. El método de la reivindicación 13, que comprende adicionalmente, en respuesta al encendido, activar (108), mediante el primer bloque (22) de hardware, en respuesta a la puesta en funcionamiento, una solicitud de potencia desde el primer bloque (22) de hardware al controlador (28) de potencia de hardware para solicitar por ello que se mantenga la potencia para el primer bloque (22) de hardware hasta que la solicitud de potencia desde el primer bloque (22) de hardware se desactive.

- 15. El método de la reivindicación 14 que comprende adicionalmente desactivar (116), mediante la interfaz (26) de hardware, la solicitud de potencia desde la interfaz (26) de hardware al controlador (28) de potencia de hardware cuando no hay más mensajes recibidos por la interfaz (26) de hardware que se vayan a proporcionar al primer bloque (22) de hardware.

17

FIG. 5

FIG. 6A

FIG. 6B

FIG. 13