# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 759 432

61 Int. Cl.:

H02J 9/06 (2006.01) G06F 1/30 (2006.01) G06F 1/26 (2006.01) H02M 1/32 (2007.01) H02H 9/02 (2006.01) H02J 3/38 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- Fecha de presentación y número de la solicitud europea: 14.07.2015 E 15176635 (9)

Fecha y número de publicación de la concesión europea: 04.09.2019 EP 2980959

- (54) Título: Sistemas y procedimientos para explotar la capacidad de corriente en UPS estáticas

- (30) Prioridad:

30.07.2014 US 201462030847 P 12.12.2014 US 201414568817

Fecha de publicación y mención en BOPI de la traducción de la patente: 11.05.2020

(73) Titular/es:

ABB SCHWEIZ AG (100.0%) Brown Boveri Strasse 6 5400 Baden, CH

(72) Inventor/es:

COLOMBI, SILVIO; MANNUCCINI, ANDREA y DE BERNARDI, LUIGI

(74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

#### **DESCRIPCIÓN**

Sistemas y procedimientos para explotar la capacidad de corriente en UPS estáticas

El campo de la invención se refiere en general a fuentes de alimentación ininterrumpida y, más en particular, a la operación de inversores en un régimen de limitación de corriente parcial.

- Los sistemas de energía robustos permiten alimentar energía a una o más cargas. Tales sistemas de energía pueden incluir combinaciones de generación, transporte, rectificación, inversión y conversión de energía para alimentar energía para aplicaciones y cargas electrónicas, ópticas, mecánicas, y/o nucleares. Cuando se implementan sistemas y arquitecturas de energía, las consideraciones prácticas incluyen el costo, tamaño, fiabilidad y facilidad de implementación.

- 10 En al menos algunos sistemas de alimentación conocidos, una o más fuentes de alimentación ininterrumpida (UPS) facilitan la alimentación de energía a una carga. Las UPS facilitan la aseguración de que la energía se alimenta de forma continua a una o más cargas críticas, incluso cuando uno o más componentes de un sistema de energía fallan. Por consiguiente, las UPS proporcionan una fuente de alimentación redundante. El documento US 6191500 B1 describe un sistema y procedimiento para proporcionar un suministro ininterrumpido de energía a una carga crítica 15 con dos UPS. Una primera UPS está acoplada a un primer panel eléctrico a través de una primera alimentación de UPS y un interruptor de la alimentación, de manera correspondiente una segunda UPS está acoplada por separado de la primera UPS. Como resultado, las energías de salida de los módulos de UPS se pueden combinar entre sí para proporcionar una fuente suficiente de energía ininterrumpida a la carga crítica, independientemente de la diferencia de fase en la energía proporcionada por las fuentes de utilidad separadas. Las UPS se pueden utilizar en una serie 20 de aplicaciones (por ejemplo, subestaciones de utilidad, plantas industriales, sistemas marinos, sistemas de alta seguridad, hospitales, centros de comunicación de datos y telecomunicaciones, plantas de fabricación de semiconductores, plantas de energía nuclear, etc.). Además, las UPS se pueden utilizar en aplicaciones de alta, media, o baja energía. Por ejemplo, las UPS se pueden utilizar en sistemas de energía (por ejemplo, sistemas de entretenimiento o de consumo) o microsistemas de energía (por ejemplo, un sistema basado en chip) relativamente 25 pequeños.

En un aspecto, se proporciona un sistema. El sistema incluye una pluralidad de fuentes de alimentación ininterrumpida (UPS), cada UPS de la pluralidad de UPS incluye un inversor, un bus de anillo, y al menos un controlador acoplado comunicativamente a la pluralidad de UPS, el al menos un controlador configurado para controlar al menos una corriente de puente en cada UPS, la al menos una corriente de puente controlada de manera tal que el inversor de cada UPS opera en un régimen de limitación de corriente parcial entre un régimen de limitación de corriente y un modo lineal.

En otro aspecto, se proporciona al menos un controlador para controlar un sistema de fuente de alimentación que incluye un bus de anillo y una pluralidad de fuentes de alimentación ininterrumpida (UPS). El al menos un controlador incluye un procesador, y un dispositivo de memoria acoplado comunicativamente al procesador, el dispositivo de memoria almacena instrucciones ejecutables configuradas para hacer al procesador controlar al menos una corriente de puente en cada UPS de la pluralidad de UPS, la al menos una corriente de puente controlada de manera tal que un inversor de cada UPS opera en un régimen de limitación de corriente parcial entre un régimen de limitación de corriente completa y un modo lineal.

En aún otro aspecto, se proporciona un procedimiento para controlar un sistema de fuente de alimentación que incluye un bus de anillo y una pluralidad de fuentes de alimentación ininterrumpida (UPS), cada uno incluyendo un inversor. El procedimiento incluye monitorizar al menos una corriente de puente en cada UPS de la pluralidad de UPS, y controlar la al menos una corriente de puente de manera tal que el inversor de cada UPS opera en un régimen de limitación de corriente parcial entre un régimen de limitación de corriente y un modo lineal.

#### Breve descripción de los dibujos

30

35

40

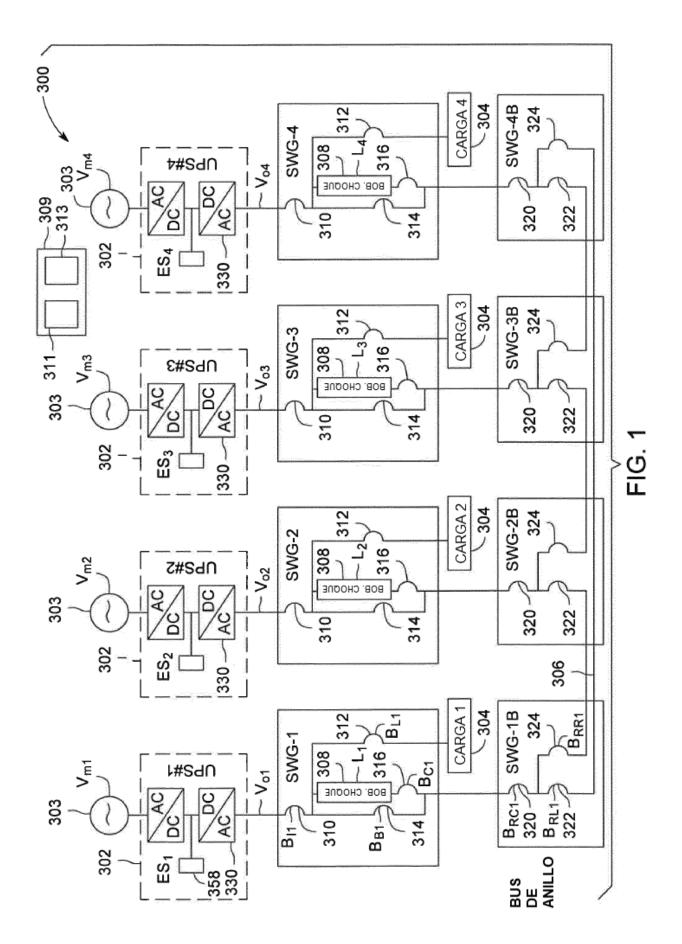

- La Fig. 1 es un diagrama de una arquitectura de bus de anillo de ejemplo.

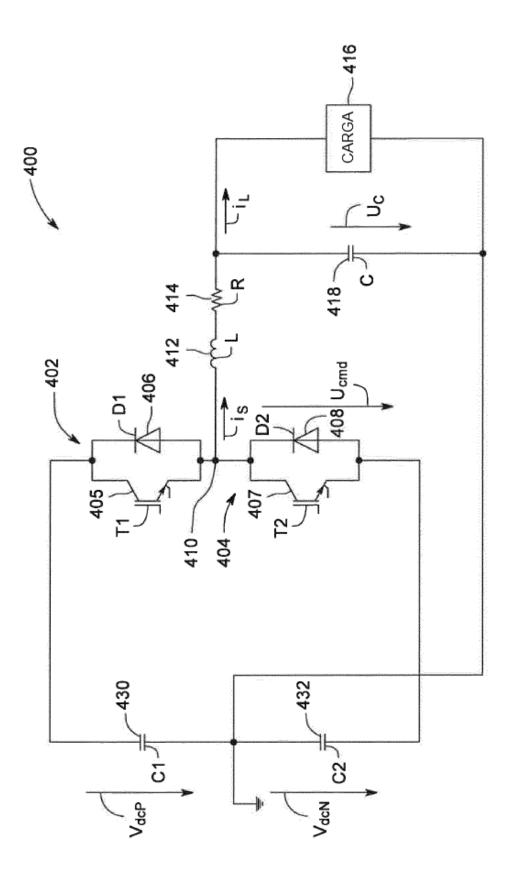

- La Fig. 2 es un diagrama de circuito de un inversor monofásico de dos niveles con fuente de tensión de ejemplo.

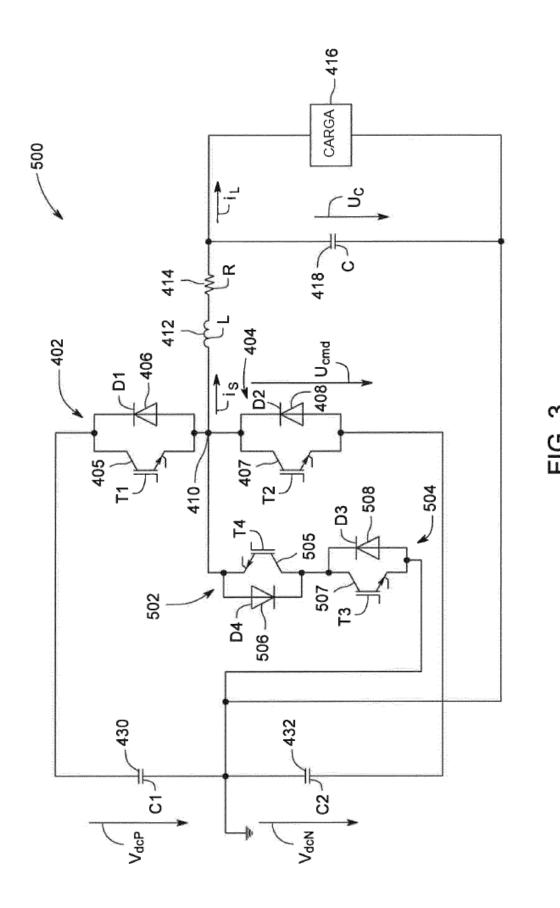

- La Fig. 3 es un diagrama de circuito de un inversor monofásico de tres niveles con fuente de tensión de ejemplo.

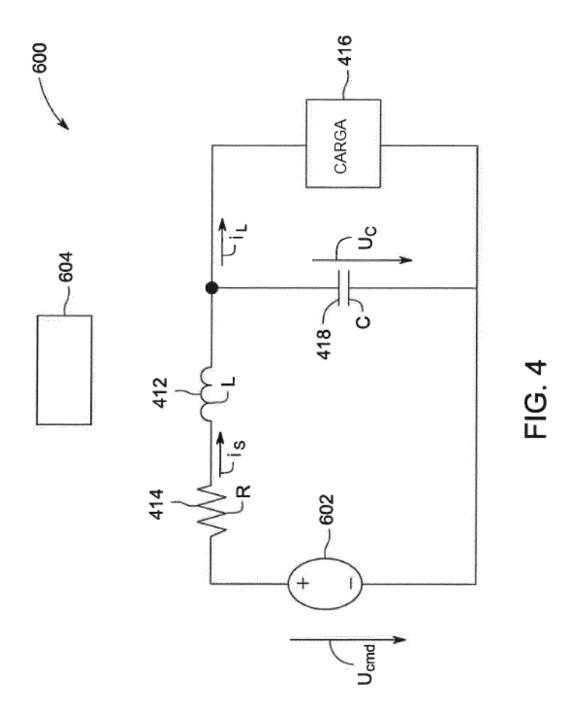

- 50 La Fig. 4 es un diagrama de circuito simplificado de un inversor monofásico.

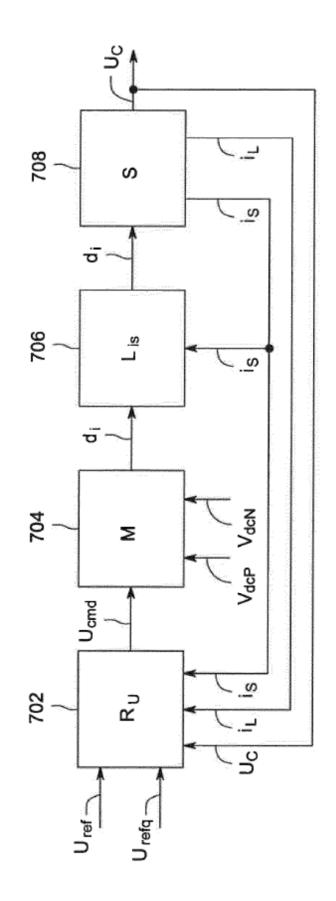

- La Fig. 5 es un diagrama de bloques de un algoritmo de control de la tensión con limitación de corriente que puede usarse con el circuito mostrado en la Fig. 4.

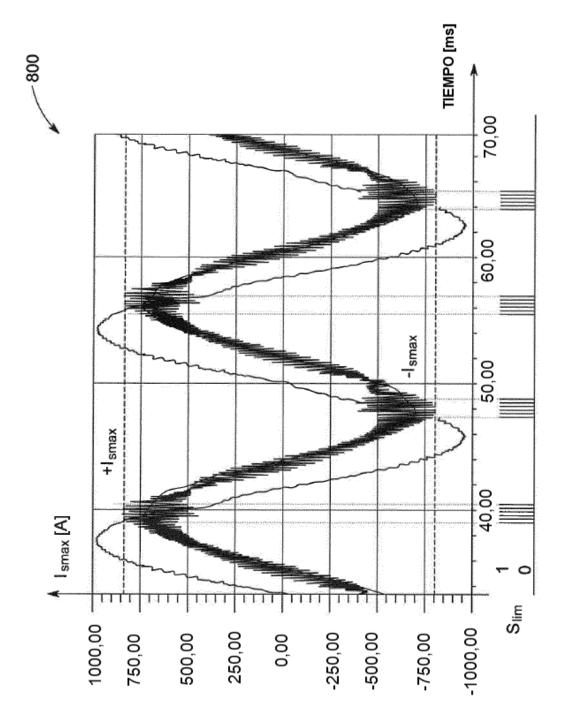

- La Fig. 6 es un gráfico que muestra periodos de limitación de corriente.

## ES 2 759 432 T3

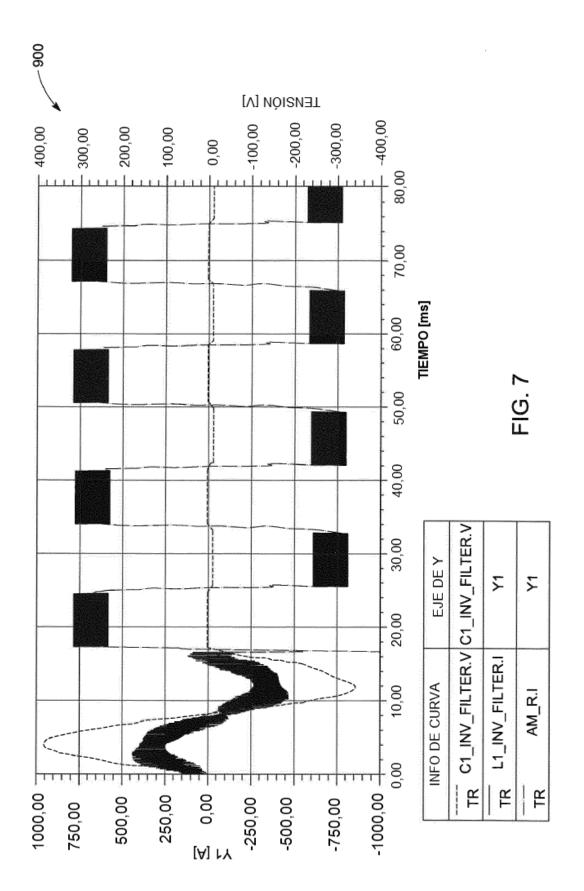

La Fig. 7 es un gráfico que muestra un cortocircuito en una salida de UPS con limitación de corriente sostenida.

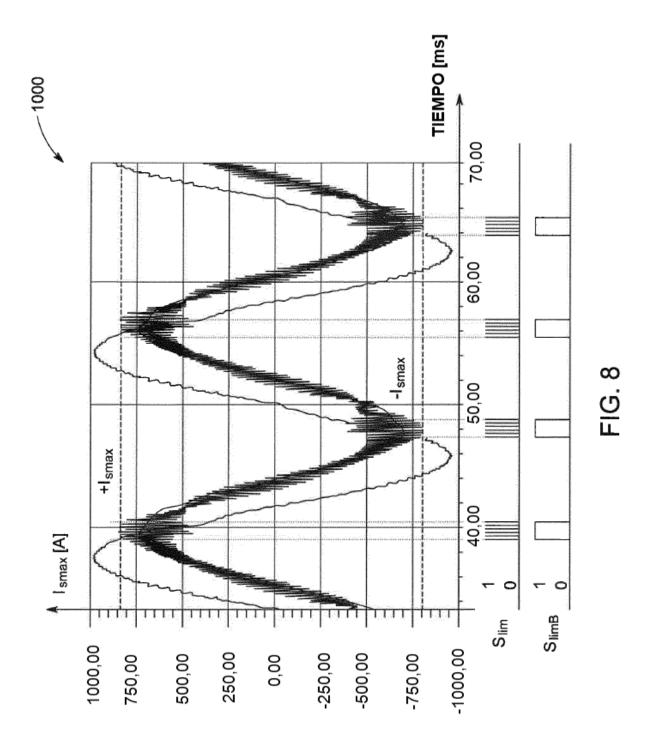

La Fig. 8 es un gráfico que ilustra periodos de limitación de corriente.

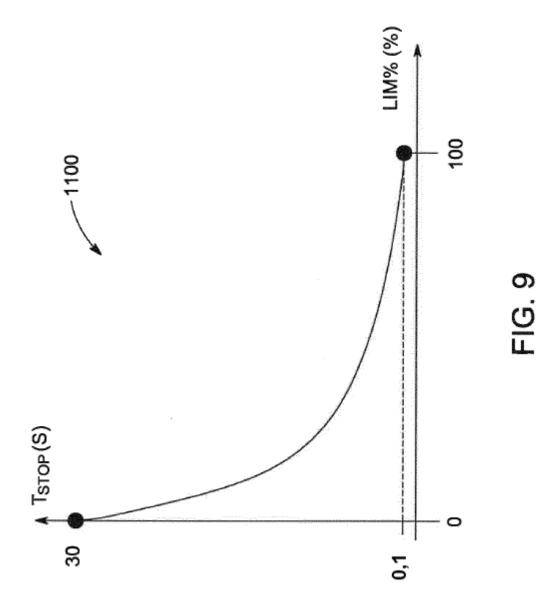

La Fig. 9 es un gráfico que ilustra características para determinar un tiempo de detención de la operación.

#### 5 Descripción detallada

10

25

30

35

50

55

Los sistemas y procedimientos descritos abordan los desafíos técnicos relacionados con el uso de las UPS estáticas en arquitecturas de bus de anillo. En particular, el tamaño de las bobinas de choque puede reducirse mediante el uso de un algoritmo de limitación de corriente que proporciona un tiempo adicional para hacer frente a un interruptor que no se abre. Esto también tiene ventajas adicionales relacionadas con el costo, factibilidad, y viabilidad de una arquitectura de UPS estática.

Se describen en la presente memoria ejemplos de realización de un sistema de alimentación ininterrumpida. Una pluralidad de fuentes de alimentación ininterrumpida están dispuestas en una configuración de bus de anillo y configuradas para alimentar energía a al menos una carga. Al menos un dispositivo de control está acoplado comunicativamente a la pluralidad de fuentes de alimentación ininterrumpida.

La Fig. 1 es un diagrama esquemático de una arquitectura de bus de anillo 300 de fuente de alimentación ininterrumpida (UPS) de aislado paralelo redundante (IP) de ejemplo. En la realización de ejemplo, la arquitectura 300 incluye una pluralidad de UPS 302 dispuestas en una arquitectura de anillo, o arquitectura paralela, como se describe en la presente memoria. Específicamente, la arquitectura 300 incluye cuatro UPS 302 en la realización de ejemplo. Alternativamente, la arquitectura 300 puede incluir cualquier número de UPS 302 que permiten a la arquitectura 300 funcionar como se describe en la presente memoria. En la realización de ejemplo, la arquitectura 300 es un sistema de tres hilos. Alternativamente, la arquitectura 300 puede ser un sistema de cuatro hilos (típicamente para alimentar cargas que requieren un cable neutro).

En la realización de ejemplo, las UPS 302 son UPS estáticas de doble conversión (es decir, verdaderos sistemas de sistema en línea). Tanto las UPS estáticas como giratorias pueden requerir técnicas de control de caída tanto para la tensión como para la frecuencia. En algunos casos, el control de caída sólo para la frecuencia puede ser suficiente. En algunas realizaciones, las técnicas de control de caída se modifican con el fin de manipular cargas no lineales.

La arquitectura 300 facilita la provisión de potencia a una o más cargas 304. En condiciones de operación normal, una o más utilidades funcionan como una fuente de tensión 303 y proporcionan corriente alterna (AC) de energía a las cargas 304. Los generadores también pueden funcionar como fuentes de tensión 303. En particular, no se requiere que las fuentes de tensión 303 estén sincronizadas en la arquitectura 300. Esto es ventajoso, dado que cada UPS 302 puede ser alimentado por un generador y/o utilidad individual, y no hay necesidad de añadir equipo adicional para sincronizar las fuentes de tensión 303.

En el caso de una falla de la fuente de tensión 303 o del rectificador de UPS, UPS 302 utiliza sistemas de almacenamiento de energía 358 (por ejemplo, baterías, volantes, etc., con su convertidor) conectados a las UPS 302 para mantener el flujo de alimentación de energía a las cargas 304, como se describe en la presente memoria. Además, si una UPS dada 302 falla, las cargas 304 se alimentan de energía a través de un bus de anillo 306, como se describe en la presente memoria. En la realización de ejemplo, la arquitectura 300 incluye cuatro cargas 304. Alternativamente, la arquitectura 300 puede incluir cualquier número adecuado de cargas 304 que permite a la arquitectura 300 funcionar como se describe en la presente memoria.

En la realización de ejemplo, cada UPS 302 está acoplada eléctricamente a una carga asociada 304, y acoplada al bus de anillo 306 a través de una bobina de choque asociada 308 (por ejemplo, un inductor). En la arquitectura 300, sin sincronización adecuada, UPS 302 puede no funcionar correctamente debido a las corrientes de circulación indeseables. Por consiguiente, en la realización de ejemplo, al menos un controlador 309 controla la operación de la UPS 302. Más específicamente, al menos un controlador 309 controla una frecuencia de una tensión de salida de cada UPS 302, como se describe en la presente memoria. La frecuencia para cada UPS 302 se calcula como una función de la energía, como se describe en la presente memoria.

En algunas realizaciones, la arquitectura 300 incluye un controlador dedicado separado 309 para cada UPS 302. Alternativamente, el sistema puede incluir un solo controlador 309 que controla la operación de todas las UPS 302. Cada controlador 309 puede incluir su propio sistema de alimentación (no mostrado) tal como una fuente de energía dedicada (por ejemplo, una batería). En algunas realizaciones, cada controlador 309 está acoplado a un controlador sustituto (no mostrado) que puede usarse en el caso de que el controlador 309 falle.

En la realización de ejemplo, cada controlador 309 se implementa mediante un procesador 311 acoplado comunicativamente a un dispositivo de memoria 313 para ejecutar instrucciones. En algunas realizaciones, se almacenan instrucciones ejecutables en el dispositivo de memoria 313. Alternativamente, el controlador 309 puede implementarse usando cualquier circuitería que permite al controlador 309 controlar la operación de las UPS 302 como se describe en la presente memoria. Por ejemplo, en algunas realizaciones, el controlador 309 puede incluir

una máquina de estado que aprende a, o está preprogramada para, determinar la información relevante a cuáles cargas 304 requieren energía.

En la realización de ejemplo, el controlador 309 realiza una o más de operaciones descritas en la presente memoria mediante la programación de un procesador 311. Por ejemplo, el procesador 311 puede programarse codificando una operación como una o más instrucciones ejecutables y proporcionando las instrucciones ejecutables en el dispositivo de memoria 313. El procesador 311 puede incluir una o más unidades de procesamiento (por ejemplo, en una configuración de múltiples núcleos). Además, el procesador 311 puede implementarse usando uno o más sistemas de procesador heterogéneos en los que un procesador principal está presente con procesadores secundarios en un solo chip. Como otro ejemplo ilustrativo, el procesador 311 puede ser un sistema de múltiples procesadores simétrico que contiene varios procesadores del mismo tipo. Además, el procesador 311 puede implementarse utilizando cualquier circuito programable adecuado que incluye uno o más sistemas y microcontroladores, microprocesadores, circuitos con conjunto reducido de instrucciones (RISC), circuitos integrados de aplicación específica (ASIC), circuitos lógicos programables, matrices de puertas programables en campo (FPGA), y cualquier otro circuito capaz de ejecutar las funciones descritas en la presente memoria. En la realización de ejemplo, el procesador 311 hace al controlador 309 operar las UPS 302, como se describe en la presente memoria.

10

15

20

25

30

35

40

45

50

55

60

En la realización de ejemplo, el dispositivo de memoria 313 es uno o más dispositivos que permiten el almacenamiento y recuperación de información tal como instrucciones y/u otros datos ejecutables. El dispositivo de memoria 313 puede incluir uno o más medios legibles por ordenador, tal como, sin limitación, memoria dinámica de acceso aleatorio (DRAM), memoria estática de acceso aleatorio (SRAM), un disco de estado sólido, y/o un disco duro. El dispositivo de memoria 313 puede estar configurado para almacenar, sin limitación, códigos de fuente de aplicación, códigos de objeto de aplicación, porciones de interés de códigos de fuente, porciones de interés de códigos de objeto, datos de configuración, actos de ejecución y/o cualquier otro tipo de datos.

En la realización de ejemplo, como se describe en más detalle a continuación, uno o más controladores 309, y más específicamente el procesador 311, calcula una frecuencia de tensión de salida para cada UPS 302, y uno o más controladores 309 operan cada UPS 302 a la frecuencia calculada. La operación de cada UPS 302 en sus respectivas frecuencias calculadas según lo determinado por los controles de caída hace posible lograr la compartición y estabilidad de carga en la arquitectura 300. Las frecuencias de operación a través de varias UPS 302 son diferentes en condiciones transitorias (por ejemplo, después de una variación de una o más cargas 304). Una vez que los controles de caída están en estado estacionario, todas las UPS 302 operan a la misma frecuencia, pero con un desplazamiento de fase a través de las bobinas de choque 308, lo que iguala la energía activa proporcionada por cada UPS 302.

En la arquitectura 300, cada UPS 302 es capaz de alimentar energía a una carga local asociada 304, así como de transferir energía activa y potencia a un bus de anillo 306 a través de una bobina de choque asociada 308. En la realización de ejemplo, la arquitectura 300 facilita el compartimiento de cargas locales 304 equitativamente entre las UPS 302 sin ninguna comunicación usando controles de caída y, en particular, frecuencia frente a energía activa y tensión frente a energía reactiva. Esto elimina las limitaciones sobre el número de UPS 302 en la arquitectura 300.

En la realización de ejemplo, la arquitectura 300 incluye un número de interruptores de circuito. Específicamente, para cada UPS 302, un primer interruptor de circuito 310 está acoplado eléctricamente entre la UPS 302 y la bobina de choque 308, un segundo interruptor de circuito 312 está acoplado eléctricamente entre el primer interruptor de circuito 310 y la carga local 304, un tercer interruptor de circuito 314 está acoplado eléctricamente entre el primer interruptor de circuito 310 y el bus de anillo 306, y un cuarto interruptor de circuito 316 está acoplado entre la bobina de choque 308 y el bus de anillo 306. Además, en el bus de anillo 306, un interruptor de circuito central 320, un interruptor de circuito izquierdo 322, y un interruptor de circuito derecho 324 están asociados con cada UPS 302, y facilitan el aislamiento de UPS 302 del bus de anillo 306 y/o de otras UPS 302 en el bus de anillo 306. Cada interruptor de circuito 310, 312, 314, 316, 320, 322, y 324 incluye lógica asociada y relés (ninguno mostrado) para la operación. El esquema de protección proporcionado por los interruptores de circuito 310, 312, 314, 316, 320, 322, y 324 facilita la localización de fallas en la arquitectura 300 y el aislamiento de tales fallas mediante la apertura de los interruptores adecuados. Además, los terceros interruptores de circuito 314, también denominados interruptores de desvío, facilitan el desvío de la bobina de choque 308 cuando la UPS asociada 302 falla o se encuentra en mantenimiento. Esto facilita la mejora de la calidad de la tensión de la carga local asociada 304 a medida que se elimina la caída de la tensión en la bobina de choque 308.

Para aplicaciones de bus de anillo, las bobinas de choque 308 están dimensionadas para sostener una falla franca del bus de anillo 306 durante un tiempo lo suficientemente extenso para garantizar el aislamiento de la falla a través de la activación de los interruptores específicos en la arquitectura 300. Además, para situaciones en las que un interruptor no se abre, debe incorporarse un tiempo adicional para determinar y ejecutar una estrategia de aislamiento de falla alternativa. Por consiguiente, para facilitar la maximización de una duración de tiempo en la que el inversor en una UPS asociada 302 puede sostener una falla franca en el bus de anillo 306, las bobinas de choque 308 pueden estar dimensionadas para operar el inversor en un modo lineal bajo un cortocircuito en el bus de anillo 306. Los sistemas y procedimientos descritos en la presente memoria facilitan la maximización del tiempo de operación en periodos limitados de corriente intermitente para proporcionar un tiempo más largo disponible para hacer frente a un

escenario en el que un interruptor no se abre. En consecuencia, el tamaño de las bobinas de choque 308 puede reducirse en cierta medida.

Como se muestra en la Fig. 1, cada UPS 302 incluye un inversor 330. Diferentes diseños son posibles para los inversores 330. Por ejemplo, para diseños sin transformador, la Fig. 2 es un diagrama de circuito de un inversor monofásico de dos niveles con fuente de tensión de ejemplo 400, y la Fig. 3 es un diagrama de circuito de un inversor monofásico de tres niveles con fuente de tensión de ejemplo 500.

5

10

15

20

25

30

35

40

45

50

55

60

Como se muestra en la Fig. 2, el inversor 400 incluye un primer dispositivo de conmutación 402 y un segundo dispositivo de conmutación 404. El primer dispositivo de conmutación 402 incluye un primer conmutador 405 (por ejemplo, un transistor) acoplado eléctricamente en paralelo con un primer diodo 406, y un segundo dispositivo de conmutación 404 incluye un segundo conmutador 407 (por ejemplo, un transistor) acoplado eléctricamente en paralelo con un segundo diodo 408. Una tensión a través del dispositivo de conmutación inferior, o segundo dispositivo de conmutación 404 se denomina en la presente memoria tensión de mando, u<sub>cmd</sub>. Un nodo 410 entre los primeros y segundos dispositivos de conmutación 402 y 404 da salida a una corriente de puente, i<sub>s</sub>, a través de un inductor 412 y un resistor 414. La corriente de puente i<sub>s</sub> se divide en una corriente de carga, I<sub>L</sub>, que fluye a la carga 416 (tal como carga local 304) y una corriente que fluye a través de un condensador 418. Una tensión a través del condensador 418 se denomina tensión del condensador, uc. El inversor 400 incluye un primer condensador de CC 430 acoplado eléctricamente entre el primer dispositivo de conmutación 402 y el neutro 420, y un segundo condensador de CC 432 acoplado eléctricamente entre el segundo dispositivo de conmutación 404 y el neutro 420. La tensión a través del primer condensador de CC 430 es una tensión de conexión de CC superior, V<sub>dcP</sub>, y la tensión a través del segundo condensador de CC 432 es una tensión de conexión de CC inferior, V<sub>dcN</sub>. Como apreciarán los expertos en la técnica, para un sistema trifásico, tres corrientes de puente se controlan como se describe en la presente memoria.

A menos que se indique lo contrario, el inversor 500 es sustancialmente similar al inversor 400. Como se muestra en la Fig. 3, el inversor 500 incluye un tercer dispositivo de conmutación 502 y un cuarto dispositivo de conmutación 504 acoplados eléctricamente en serie entre el nodo 410 y el neutro 420. El tercer dispositivo de conmutación 502 incluye un tercer conmutador 505 (por ejemplo, un transistor) acoplado eléctricamente en paralelo con un tercer diodo 506, y el cuarto dispositivo de conmutación 504 incluye un cuarto conmutador 507 (por ejemplo, un transistor) acoplado eléctricamente en paralelo con un cuarto diodo 508. Los terceros y cuartos dispositivos de conmutación 502 y 504 implementan un dispositivo de conmutación bidireccional. Alternativamente, el dispositivo de conmutación bidireccional puede implementarse usando otros componentes (por ejemplo, usando dispositivos de bloqueo inverso). Las topologías del inversor 400 y el inversor 500 pueden implementarse como conversores trifásicos por el uso de tres vías de acceso.

Para ambos del inversor 400 y el inversor 500, la Fig. 4 es un diagrama de circuito del circuito equivalente 600 de un inversor monofásico. El circuito 600 incluye la tensión de mando  $u_{cmd}$  representada como una fuente de tensión 602. La tensión de mando discontinua  $u_{cmd}$  modela el inversor de dos o tres niveles. Por lo tanto, esta tensión puede tener variaciones de onda cuadrada entre dos o tres valores posibles. En la realización de ejemplo, un controlador 604, tal como el controlador 309 (mostrado en la Fig. 1), controla la operación de uno o más componentes de circuito 600.

La Fig. 5 es un diagrama de bloques 700 de un algoritmo de control de la tensión de ejemplo con limitación de corriente que puede usarse con el circuito 600. Las etapas del diagrama de bloques 700 se pueden realizar, por ejemplo, usando el controlador 604 (mostrado en la Fig. 4). En el diagrama de bloques 700, un bloque de control de la tensión 702,  $R_u$ , implementa y determina la tensión de mando  $u_{cmd}$  con base en una tensión de referencia,  $U_{ref}$ , una tensión de referencia de cuadratura,  $u_{refQ}$ , el condensador de la tensión  $u_c$ , la corriente de carga  $i_L$  y la corriente de puente  $i_s$ . La tensión de referencia  $u_{ref}$  y la tensión de referencia de cuadratura  $u_{refQ}$  pueden ser valores predeterminados almacenados en una memoria, tal como el dispositivo de memoria 313 (mostrado en la Fig. 1). Alternativamente, la tensión de referencia  $u_{ref}$  y la tensión de referencia de cuadratura  $u_{refQ}$  pueden calcularse usando las ecuaciones, por ejemplo, de la siguiente manera:  $u_{ref} = A*sen(2*\pi*f*tiempo)$  y  $u_{refQ} = B*cos(2*\pi*f*tiempo)$ .

Un bloque de modulación 704, M, implementa de modulación que determina las señales de activación periódica  $d_i$  para conmutadores de alimentación (por ejemplo, señales de activación periódica  $D_1$  y  $D_2$  para los primeros y segundos conmutadores 405 y 407 del inversor 400, y las señales de activación periódica  $d_1$  ...  $d_4$  para los primeros, segundos, terceros, y cuartos conmutadores 405, 407, 505, y 507 del inversor 500). La modulación se adapta como una función de las tensiones instantáneas  $V_{dcP}$  y  $V_{dcN}$  de las conexiones de CC superiores e inferiores, respectivamente. Un bloque de limitación 706,  $L_{is}$ , implementa una limitación de corriente de puente que puede modificar las señales de activación periódica  $d_i$  para los conmutadores de alimentación. En la realización de ejemplo, el bloque de limitación 706 usa un comparador de histéresis para verificar si la corriente de puente  $i_s$  excede un límite de corriente predefinido,  $i_{smax}$ .

[0029] En particular, considerando una corriente positiva, cuando la corriente de puente i<sub>s</sub> excede el límite l<sub>smax</sub>, las señales de activación periódica d<sub>i</sub> para los conmutadores se modifican de manera tal de disminuir la corriente i<sub>s</sub>. Esto depende de la topología del inversor empleado. Como un ejemplo, se considera el inversor 400 de la Fig. 2. Para una corriente positiva y creciente i<sub>s</sub>, el primer conmutador 405 está cerrado y el segundo interruptor 407 está abierto. Si la corriente i<sub>s</sub> excede el límite l<sub>smax</sub>, el primer conmutador 405 recibe la orden de abrirse por el bloque de limitación 706. Como resultado, la corriente i<sub>s</sub> fluye a través del segundo diodo 408 y disminuye a medida que el filtro LC formado por el inductor 412 y el condensador 418 se polariza de forma inversa. Cuando la corriente cae por debajo de un límite

máximo inferior I<sub>smaxLOW</sub> (por ejemplo, aproximadamente 70% de I<sub>smax</sub>), el bloque de control de la tensión 702 y el bloque de modulación 704 asumen nuevamente el control. El control se realiza de manera similar para una corriente negativa, por la operación de conmutadores para causar que la corriente de puente negativa i<sub>s</sub> aumente (es decir, se mueva hacia la corriente de cero) una vez que la corriente de puente negativa i<sub>s</sub> cae por debajo de un límite I<sub>smax</sub>.

El bloque de limitación 706 puede implementar características adicionales para mejorar el rendimiento en realizaciones que incluyen un inversor de tres niveles (por ejemplo, el inversor 500). Por ejemplo, en el inversor 500, el dispositivo de conmutación bidireccional formado por los terceros y cuartos dispositivos de conmutación 502 y 504 se puede usar durante el procedimiento de limitación de corriente con el fin de evitar conmutaciones de dos niveles (es decir, de V<sub>dcP</sub> a -V<sub>dcN</sub> o recíprocas). Por ejemplo, para una corriente de puente positiva y en aumento i<sub>s</sub>, que excede el límite l<sub>smax</sub>,

los interruptores 405, 407, 506, y 508 se comandan por el bloque de limitación 706 con el fin de conmutar la tensión de mando U<sub>cmd</sub> de V<sub>dcP</sub> a 0 y después -V<sub>dcN</sub>. Esto reduce la sobretensión de conmutación en los interruptores.

En el diagrama de bloques 700, un bloque de sistema 708, S, representa el sistema controlado, en particular, el puente del inversor y el filtro LC (véanse las Fig. 2-4). Para un sistema trifásico, un inversor trifásico puede usarse en combinación con un controlador diferente 604 para cada fase. Alternativamente, la estrategia de limitación de corriente descrita en la presente memoria puede implementarse usando un enfoque de vector espacial.

15

20

25

30

35

40

Esta operación de diagrama de bloques 700 se ilustra en la Fig. 6, que es un gráfico 800 que ilustra periodos de limitación de corriente cuando  $s_{lim} = 1$ . La operación de limitación de corriente del diagrama de bloques 700 puede controlarse por un mecanismo temporizador implementado usando un controlador 604 que se activa cuando se impacta en primer lugar el límite de corriente  $l_{smax}$  y después verifica la duración contra un límite definido (por ejemplo, 100 milisegundos (ms)). Para facilitar la optimización del diseño de los inversores en la arquitectura 300, el límite de corriente puede ajustarse ligeramente por encima de la capacidad de sobrecarga de 150% máxima típica de los inversores que normalmente se puede mantener durante 30 segundos (s).

La Fig. 7 es un gráfico 900 que muestra una operación de un régimen de limitación de corriente completa. Como se demuestra por el gráfico 900, en un régimen de limitación de corriente completa, un inversor suministra una corriente de onda cuadrada de típicamente 2,2 veces una corriente nominal durante un tiempo limitado (por ejemplo, 100 ms), por ejemplo, para fundir fusibles de salida. En consecuencia, un régimen de limitación de corriente completa típico sólo puede ser sostenible durante aproximadamente 100 ms. Como se muestra en la Fig. 7, en el régimen de limitación de corriente completa, la corriente alterna entre corrientes de pico positivas y negativas.

En contraste con el uso de una región de limitación de corriente completa, el algoritmo del diagrama de bloques 700 facilita la explotación de la capacidad de corriente del inversor en una región entre un régimen de limitación de corriente completa, tal como se muestra en la Fig. 7, y una condición de sobrecarga máxima en modo lineal (es decir, sin limitación de corriente) que, en general (por ejemplo, por razones económicas) se produce en una sobrecarga de 150%. En otras palabras, la operación de inversores de acuerdo con el algoritmo del diagrama de bloques 700 proporciona un tiempo variable (por ejemplo, de 100 ms a 30s) en el que puede sostenerse un régimen de limitación de corriente parcial.

Para la implementación de este algoritmo de limitación de corriente descrito en la presente memoria se usa una medición de un tiempo porcentual de limitación real. Para ello, se genera una señal s<sub>limB</sub> cuando se producen ráfagas de periodos de limitación de corriente como se muestra en el gráfico 1000 de la Fig. 8. La Fig. 8 muestra periodos de limitación de corriente cuando s<sub>lim</sub> = 1. s<sub>lim</sub> muestra la ocurrencia de ráfagas de periodos de limitación de corriente. El tiempo porcentual de limitación de corriente se calcula según la Ecuación 1:

$$LIM\% = \frac{1}{T_s} \int_{T_s} s_{\lim B} dt$$

Ecuación 1

en la que  $T_s$  representa el periodo de una onda fundamental (por ejemplo, 20 ms para una frecuencia de 50 Hz). El uso del tiempo porcentual de limitación de corriente real, LIM%, permite al sistema sostener la operación durante un periodo de tiempo más largo (por ejemplo, 300 - 400 ms), proporcionando más tiempo para resolver una falla.

Por otra parte, un tiempo de detención de la operación se determina a partir de un T<sub>STOP</sub> característico predefinido = f(% LIM) como se muestra en el gráfico 1100 de la Fig. 9. En la realización de ejemplo, el T<sub>STOP</sub> característico de detención de la operación = f(LIM%) se determina con base en el diseño del inversor, y, en particular, el tipo y calibre de los conmutadores de los semiconductores, el sistema de refrigeración, etc. En algunas realizaciones, la presión sobre los conmutadores de los semiconductores en este modo de operación se analiza usando un modelo térmico o mediciones reales. Como se muestra en la Fig. 9, la reducción del LIM% aumenta el tiempo de detención de la operación, proporcionando más tiempo para reparar la falla de uno o más interruptores 310, 312, 314, 316, 320, 322, y 324. En una realización alternativa, el tiempo de detención de la operación se determina usando un modelo térmico que estima en tiempo real la temperatura de unión de los semiconductores.

## ES 2 759 432 T3

Los sistemas y procedimientos descritos en la presente memoria usan un algoritmo de control que explota la capacidad de corriente de un inversor en una región entre un régimen de limitación de corriente completa (es decir, operación de onda cuadrada) y una condición de sobrecarga máxima en modo lineal (es decir, sin limitación de corriente). En otras palabras, las realizaciones descritas en la presente memoria proporcionan un tiempo variable en el que puede sostenerse un régimen de limitación de corriente parcial. Esto proporciona ventajas en numerosas configuraciones y/o arquitecturas diferentes de sistemas de UPS.

Para arquitecturas de UPS individual o UPS paralela tradicional (N+1 redundante, 2N, etc.), los sistemas y procedimientos descritos en la presente memoria proporcionan una mayor capacidad para brindar tiempo de operación extendido en periodos limitados de corriente intermitente. A su vez, esto aumenta la fiabilidad del sistema de energía crítica dado que retrasa sustancialmente una transición del inversor al derivador.

Además, los sistemas y procedimientos descritos abordan los desafíos técnicos relacionados con el uso de UPS estáticas en arquitecturas de bus de anillo. En particular, el tamaño de las bobinas de choque puede reducirse en cierta medida, dado que el algoritmo de limitación de corriente proporciona un mayor tiempo en el régimen de limitación de corriente parcial. Esto también tiene ventajas adicionales relacionadas con el costo, factibilidad y viabilidad de la arquitectura de UPS estáticas.

Los sistemas y procedimientos descritos en la presente memoria son aplicables independientemente del nivel de tensión, y más en particular, son aplicables tanto a aplicaciones de baja tensión (LV) (por ejemplo, fase-fase de 480 V) como media tensión (MT) (por ejemplo, fase-fase de 13,8kV). Por ejemplo, si bien las topologías de inversores descritas en la presente memoria se usan típicamente en sistemas LV, los principios de las realizaciones descritas en la presente memoria se pueden aplicar igualmente a sistemas MT usando tecnologías de inversor adecuadas.

En comparación con al menos algunos sistemas de alimentación conocidos, los sistemas y procedimientos descritos en la presente memoria facilitan la operación de inversores entre un régimen de limitación de corriente completa y un modo lineal. Además, el control de las corrientes de puente usando los sistemas y procedimientos descritos en la presente memoria proporciona un sistema UPS con tiempo adicional para resolver una falla, tal como se describe en la presente memoria.

Las realizaciones de ejemplo de sistemas y procedimientos para fuentes de alimentación ininterrumpida se han descrito con anterioridad en detalle. Los sistemas y procedimientos no están limitados a las realizaciones específicas descritas en la presente memoria sino, más bien, los componentes de los sistemas y/u operaciones de los procedimientos pueden usarse de forma independiente y por separado de otros componentes y/u operaciones descritas en la presente memoria. Además, los componentes y/u operaciones descritas también pueden definirse en, o usarse en combinación con, otros sistemas, procedimientos y/o dispositivos, y no están limitados a la práctica sólo con los sistemas descritos en la presente memoria.

Al menos un efecto técnico de los sistemas y procedimientos descritos en la presente memoria incluye (a) monitorizar al menos una corriente de puente en cada UPS de una pluralidad de UPS; y (b) controlar la al menos una corriente de puente de manera tal que un inversor de cada UPS opera en un régimen de limitación de corriente parcial entre un régimen de limitación de corriente completa y un modo lineal.

El orden de ejecución o el rendimiento de las operaciones en las realizaciones de la invención ilustradas y descritas en la presente memoria no es esencial, a menos que se especifique lo contrario. Esto quiere decir que las operaciones se pueden realizar en cualquier orden, a menos que se especifique lo contrario, y las realizaciones de la invención pueden incluir operaciones adicionales o menos operaciones que las desveladas en la presente memoria. Por ejemplo, se contempla que la ejecución o la realización de una operación particular antes, contemporáneamente con, o después de otra operación, está dentro del ámbito de los aspectos de la invención.

Aunque las características específicas de diversas realizaciones de la invención pueden mostrarse en algunos dibujos y en otros no, esto es sólo por propósitos de conveniencia. De acuerdo con los principios de la invención, cualquier característica de un dibujo puede referirse y/o reivindicarse en combinación con cualquier característica de cualquier otro dibujo.

En la presente descripción escrita se usan ejemplos para desvelar la invención, incluyendo el mejor modo, y también para permitir a cualquier experto en la técnica poner en práctica la invención, incluyendo la fabricación y uso de cualquier dispositivo o sistema y la realización de cualquiera de los procedimientos incorporados. El ámbito patentable de la invención se define por las reivindicaciones, y puede incluir otros ejemplos ideados por los expertos en la técnica. Tales otros ejemplos están destinados a estar dentro del ámbito de las reivindicaciones si tienen elementos estructurales que no difieran de la terminología literal de las reivindicaciones, o si incluyen elementos estructurales equivalentes con diferencias insustanciales con respecto a la terminología literal de las reivindicaciones.

5

10

15

20

25

30

35

40

45

50

#### REIVINDICACIONES

- Al menos un controlador (309) para controlar un sistema de fuente de alimentación (300) que incluye un bus de anillo (306) y una pluralidad de fuentes de alimentación ininterrumpida (UPS) (302), dicho al menos un controlador (309) comprende:

- 5 un procesador (311); y

10

30

45

un dispositivo de memoria (313) acoplado comunicativamente a dicho procesador (311), dicho dispositivo de memoria (313) almacena instrucciones ejecutables configuradas para hacer a dicho procesador (311) controlar al menos una corriente de puente en cada UPS de la pluralidad de UPS (302), la al menos una corriente de puente controlada de manera tal que un inversor (330) de cada UPS opera en un régimen de limitación de corriente parcial con periodos de limitación de corriente cuando se producen ráfagas durante un régimen de limitación de corriente completa, cada UPS opera en un régimen de limitación de corriente parcial entre el régimen de limitación de corriente completa con operación de onda cuadrada y un modo lineal sin limitación de corriente.

- **2.** Al menos un controlador (309) de acuerdo con la reivindicación 1, en el que para controlar la al menos una corriente de puente, dicho procesador (311) está configurado para:

- comparar la al menos una corriente de puente con un límite de corriente predefinido; y

- modificar señales de activación periódica para los conmutadores (405, 407) en el inversor (330) cuando la al menos una corriente de puente excede el límite de corriente predefinido.

- 3. Al menos un controlador (309) de acuerdo con la reivindicación 2, en el que para modificar señales de activación periódica, dicho procesador (311) está configurado para modificar las señales de activación periódica de manera tal que disminuye una magnitud de la al menos una corriente de puente.

- 4. Al menos un controlador (309) de acuerdo con cualquiera de las reivindicaciones 1 a 3, en el que dicho procesador (311) está además configurado para detener la operación de dicho inversor (330) en el régimen de limitación de corriente parcial cuando se alcanza un tiempo de detención de la operación predeterminado.

- 25 **5.** Un sistema (300) que comprende:

una pluralidad de fuentes de alimentación ininterrumpida (UPS) (302), cada UPS de la pluralidad de UPS comprende un inversor (330);

un bus de anillo (306); y

al menos un controlador (309) acoplado comunicativamente a dicha pluralidad de UPS (302), dicho al menos un controlador (309) configurado para controlar al menos una corriente de puente en cada UPS, la al menos una corriente de puente es como se define en cualquiera de las reivindicaciones 1 a 4.

- **6.** Un sistema (300) de acuerdo con la reivindicación 5, en el que dicho al menos un controlador (309) comprende una pluralidad de controladores, cada controlador de dicha pluralidad de controladores está acoplado comunicativamente a un UPS (302) asociado de dicha pluralidad de UPS (302).

- 35 7. Un sistema (300) de acuerdo con la reivindicación 5 o 6, en el que dicho inversor (330) comprende un inversor monofásico de dos niveles con fuente de tensión (400).

- 8. Un sistema (300) de acuerdo con cualquiera de las reivindicaciones 5 a 7, en el que dicho inversor (330) comprende un inversor monofásico de tres niveles con fuente de tensión (500).

- 9. Un procedimiento de control de un sistema de fuente de alimentación (300) que incluye un bus de anillo (306) y una pluralidad de fuentes de alimentación ininterrumpida (UPS) (302) incluyendo cada uno un inversor (330), el procedimiento comprende:

monitorizar al menos una corriente de puente en cada UPS (302) de la pluralidad de UPS (302); y

controlar la al menos una corriente de puente de manera tal que el inversor (330) de cada UPS (302) opera en un régimen de limitación de corriente parcial con periodos de limitación de corriente cuando se producen ráfagas durante un régimen de limitación de corriente completa, cada UPS opera en un régimen de limitación de corriente parcial entre el régimen de limitación de corriente completa con operación de onda cuadrada y un modo lineal sin limitación de corriente.

**10.** Un procedimiento de acuerdo con la reivindicación 9, en el que controlar la al menos una corriente de puente comprende:

8

## ES 2 759 432 T3

comparar al menos una corriente de puente con un límite de corriente predefinido; y

10

modificar las señales de activación periódica para los conmutadores (405, 407, 330) en el inversor (330) cuando la al menos una corriente de puente excede el límite de corriente predefinido.

- Un procedimiento de acuerdo con la reivindicación 10, en el que modificar las señales de activación periódica

comprende modificar las señales de activación periódica de manera tal que disminuye una magnitud de la al menos una corriente de puente.

- **12.** Un procedimiento de acuerdo con cualquiera de las reivindicaciones 9 a 11, en el que controlar la al menos una corriente de puente comprende controlar la al menos una corriente de puente de manera tal que el inversor (330) opera en el régimen de limitación de corriente parcial durante un periodo de tiempo mayor que el posible bajo un régimen de limitación de corriente de onda cuadrada total.

- **13.** Un procedimiento de acuerdo con cualquiera de las reivindicaciones 9 a 12, en el que controlar la al menos una corriente de puente comprende controlar la al menos una corriente de puente de manera tal que un inversor monofásico de dos niveles con fuente de tensión (400) opera en el régimen de limitación de corriente parcial.

- 14. Un procedimiento de acuerdo con cualquiera de las reivindicaciones 9 a 13, en el que controlar la al menos una corriente de puente de manera tal que un inversor monofásico de tres niveles con fuente de tensión (500) opera en el régimen de limitación de corriente parcial.

FIG. 2

12

FIG. 5

FIG. 6