### OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 773 032

EP 3276899

(51) Int. CI.:

H04L 12/935 (2013.01) G06F 13/38 (2006.01) G06F 13/40 (2006.01) (2006.01)

G06F 13/42

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

13.01.2017 PCT/CN2017/071081 (86) Fecha de presentación y número de la solicitud internacional:

(87) Fecha y número de publicación internacional: 20.07.2017 WO17121376

(96) Fecha de presentación y número de la solicitud europea: 13.01.2017 E 17738189 (4)

(54) Título: Dispositivo de conmutación, sistema de interconexión de componentes periféricos rápida y procedimiento de inicialización del mismo

(30) Prioridad:

13.01.2016 CN 201610022697

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 09.07.2020

(97) Fecha y número de publicación de la concesión europea:

(73) Titular/es:

13.11.2019

**HUAWEI TECHNOLOGIES CO., LTD. (100.0%)** Huawei Administration Building, Bantian, **Longgang District** Shenzhen, Guangdong 518129, CN

(72) Inventor/es:

**FANG, HONGCAN**

(74) Agente/Representante:

**ELZABURU, S.L.P**

#### **DESCRIPCIÓN**

Dispositivo de conmutación, sistema de interconexión de componentes periféricos rápida y procedimiento de inicialización del mismo

#### Campo técnico

Esta aplicación se refiere al campo de las comunicaciones y, más específicamente, a un dispositivo de conmutación, un sistema de interconexión de componentes periféricos rápida y un procedimiento para inicializar un sistema de interconexión de componentes periféricos rápida.

#### **Antecedentes**

10

25

30

35

40

45

50

55

Una tecnología de virtualización de entrada/salida de raíz única (en inglés, Single-Root Input/Output Virtualization – SR-IOV) propuesta por el Grupo de Interés Especial de Interconexión de Componentes Periféricos (en inglés, Peripheral Component Interconnect Special Interest Group - PCI-SIG) se aplica a una situación en la que un dispositivo de entrada/salida (Entrada/Salida - E/S) es compartido por múltiples procesos en un host. La tecnología SR-IOV virtualiza, para un dispositivo PCI rápido (en inglés, PCI express - PCIe), múltiples funciones virtuales (en inglés, Virtual Function - VF) para un host de capa superior a invocar.

Una tecnología de entrada/salida de raíz múltiple (en inglés, Multi-Root Input/Output Virtualization - MR-IOV) se aplica a una situación en la que un dispositivo de E/S es compartido por múltiples hosts. La tecnología virtualiza múltiples jerarquías virtuales (en inglés, Virtual Hierarchies - VH) a ser invocadas por múltiples hosts, y a las múltiples jerarquías virtuales se puede hacer referencia como múltiples dominios PCI. Sin embargo, la tecnología modifica protocolos de capas, salvo una capa física y una capa de enlace de datos en un protocolo PCIe. Por lo tanto, múltiples nodos, por ejemplo, un nodo raíz (en inglés, Root Node - RN) que soporta un MR-IOV, un conmutador (Conmutador) o un dispositivo PCIe, en una estructura de topología, deben ejecutar una adaptación. La tecnología MR-IOV requiere una adaptación de la cadena industrial, lo que genera una compatibilidad pobre. Actualmente, no hay ningún producto que soporte el estándar.

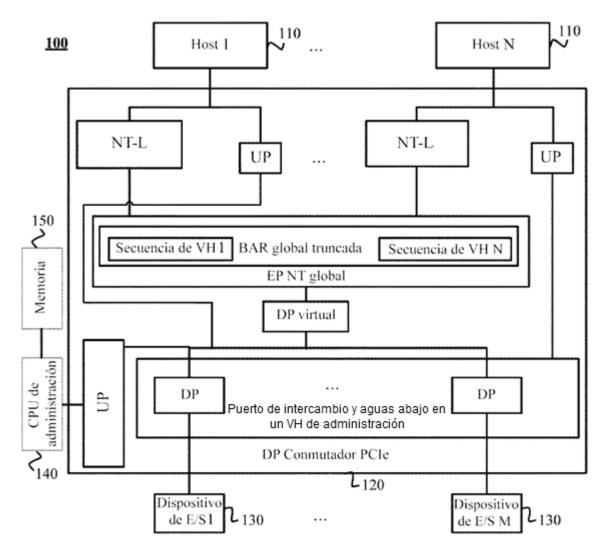

En la técnica anterior, se proporciona una solución para que múltiples hosts compartan un dispositivo de E/S mediante el uso de un dispositivo SR-IOV. La FIG. 1 muestra una implementación típica en la técnica anterior. Un sistema 100 incluye: N hosts (desde un host 1 a un host N) 110, un conmutador PCIe 120, M dispositivos de E/S (desde un dispositivo de E/S 1 a un dispositivo de E/S M) 130, una CPU de administración externa 140 y una memoria 150, donde 1 ≤ M ≤ N. La CPU de administración 140 es responsable de: ejecutar la enumeración de dispositivos y descubrir un lado de dispositivo de E/S y ejecutar la configuración y administración de dispositivos. El conmutador PCIe 120 incluye un módulo de enlace no transparente (en inglés, Non-Transparent Link − NT-L), múltiples puertos PCIe aguas arriba (en inglés, Upstream Port - UP), un módulo EP no transparente global (en inglés, Non-Transparent - NT) y múltiples puertos PCIe aguas abajo virtuales (en inglés, Downstream Port - DP). El módulo EP NT global se configura para: administrar un registro y mapear una dirección de memoria, e implementar una función virtual no transparente (en inglés, Non-Transparent Virtual - NT-V). El sistema 100 puede incluir múltiples jerarquías virtuales (en inglés, Virtual Hierarchy - VH).

En la solución técnica, debe disponerse adicionalmente una CPU de administración, debe disponerse externamente una memoria que corresponda a la CPU de administración y debe proporcionarse una interfaz de administración PCIe separada. Por tanto, la solución técnica no es adecuada para un diseño de producto. Además, en el sistema 100 que se muestra en la FIG. 1, solo una CPU de administración se dispone para administrar todo el sistema y hay solo un enlace de administración. Una vez que el enlace de administración presenta una excepción, toda una red se rompe y ya no puede usarse. En consecuencia, la estabilidad y la confiabilidad son relativamente pobres.

El documento de los EE.UU. 2012/179804 se refiere a la administración de un conmutador de interconexión de componentes periféricos PCI por sus siglas en inglés. En particular, describe que el servidor de administración incluye un módulo de administración de dispositivo PCI 200 que administra los cambios en la configuración de los conmutadores PCIe.

El documento EP 2549716 se refiere a un dispositivo de administración de red y un procedimiento para administrar una red. En particular, describe un dispositivo de administración de red que es diferente del conmutador y adquiere información de identificación del nodo que se conecta al conmutador.

#### Compendio

Las realizaciones de la presente invención proporcionan un dispositivo de conmutación para inicializar un sistema PCle, a fin de lograr una estabilidad y una confiabilidad relativamente altas. Según un primer aspecto, se proporciona un dispositivo de conmutación, incluyendo: múltiples puertos PCle aguas arriba, configurados para conectarse al, al menos un, host; al menos un puerto PCle aguas abajo, configurado para conectarse al, al menos un, dispositivo de E/S; y un aparato de procesamiento interno, conectado al, al menos un, puerto PCle aguas abajo mediante el uso de una línea de conexión interna del dispositivo de conmutación, donde el aparato de procesamiento interno se configura para:

## ES 2 773 032 T3

transmitir un paquete de lectura/escritura de configuración para el al menos un puerto PCIe aguas abajo mediante el uso de una línea de conexión interna;

recibir un paquete de respuesta de lectura/escritura de configuración por parte del al menos un puerto PCIe aguas abajo mediante el uso de la línea de conexión interna, donde el paquete de respuesta de lectura/escritura de configuración transporta una identificación de completador; y

5

10

15

20

25

30

35

40

50

55

determinar, en función de la identificación de completador transportada en el paquete de respuesta de lectura/escritura de configuración, que el dispositivo de conmutación está conectado a un dispositivo de E/S cuya identificación es la identificación de completador.

El aparato de procesamiento interno se puede configurar para enumerar un dispositivo físico (es decir, un dispositivo real) conectado al dispositivo de conmutación. Opcionalmente, el aparato de procesamiento interno puede enviar múltiples paquetes de lectura/escritura de configuración al, al menos un, puerto PCIe aguas abajo, donde los múltiples paquetes de lectura/escritura de configuración transportan diferentes identificaciones de completador. El al menos un puerto PCIe aguas abajo se configura para: reenviar los múltiples paquetes de lectura/escritura de configuración a un dispositivo físico conectado al, al menos un, puerto PCle aguas abajo, y al recibir al menos un paquete de respuesta de lectura/escritura de configuración enviado por el dispositivo físico conectado, reenviar el al menos un paquete de respuesta de lectura/escritura de configuración al aparato de procesamiento interno, donde el al menos un paquete de respuesta de lectura/escritura de configuración corresponde a al menos uno de los múltiples paquetes de lectura/escritura de configuración en una correspondencia de uno a uno, y cada paquete de respuesta de lectura/escritura de configuración transporta una identificación de completador en un paquete de lectura/escritura de configuración correspondiente al paquete de respuesta de lectura/escritura de configuración. El aparato de procesamiento interno puede recibir el al menos un paquete de respuesta de lectura/escritura de configuración reenviado por el al menos un puerto PCIe aguas abajo y determinar, en función de la identificación de completador transportada en cada uno de los al menos un paquete de respuesta de lectura/escritura de configuración, el dispositivo físico conectado al, al menos un, puerto PCIe aquas abaio (o el dispositivo de conmutación). El dispositivo físico puede incluir un dispositivo de E/S, o a demás puede incluir un conmutador de PCle y/u otro aparato.

Por lo tanto, el dispositivo de conmutación según esta realización de la presente invención incluye los múltiples puertos PCIe aguas arriba configurados para conectarse al, al menos un, host; el al menos un puerto PCIe aguas abajo configurado para conectarse al, al menos un, dispositivo de E/S; y el aparato de procesamiento interno. El aparato de procesamiento se conecta al, al menos un, puerto PCIe aguas abajo mediante el uso de una línea de conexión interna y se configura para: transmitir un paquete de lectura/escritura de configuración al, al menos un, puerto PCIe aguas abajo mediante el uso de la línea de conexión interna; recibir un paquete de respuesta de lectura/escritura de configuración transmitido mediante el al menos un puerto PCIe aguas abajo mediante el uso de una línea de conexión interna; y determinar, en función de una identificación de completador transportada en el paquete de respuesta de lectura/escritura de configuración, que el dispositivo de conmutación está conectado a un dispositivo de E/S cuya identificación (por ejemplo, una BDF) es la identificación de completador. De esta manera, cuando un dispositivo de conmutación falla, solo el al menos un host y el al menos un dispositivo de E/S que están conectados al dispositivo de conmutación resultan afectados, y otro dispositivo de conmutación, y un host y un dispositivo de E/S que están conectados al otro dispositivo de conmutación en un sistema no son afectados. Por lo tanto, en comparación con una CPU de administración externa en la técnica anterior, es posible mejorar tanto la estabilidad como la confiabilidad del sistema.

En una posible primera implementación del primer aspecto, si el al menos un puerto PCle aguas abajo se conecta a un dispositivo de E/S de función única, el dispositivo de conmutación se configura específicamente para transmitir de manera transparente información entre el dispositivo de E/S de función única y un host que corresponde al dispositivo de E/S de función única.

En este caso, una función del dispositivo de E/S de función única solo puede ser usada por uno de los al menos un host, es decir que el dispositivo de E/S de función única corresponde al host que usa la función del dispositivo de E/S de función única.

En referencia a las posibles implementaciones anteriores, en una segunda implementación posible del primer aspecto, el dispositivo de conmutación además incluye: al menos un módulo de dispositivo terminal de espejo, configurado para almacenar el contenido de configuración PCIe del al menos un dispositivo de E/S conectado al, al menos un, puerto PCIe aguas abajo; un módulo de mapeo, configurado para implementar el mapeo entre un dominio PCIe correspondiente al, al menos un, host y un dominio PCIe correspondiente al, al menos un, dispositivo de E/S; y al menos un módulo de dispositivo terminal virtual, configurado para virtualizar una función del al menos un dispositivo de E/S conectado al, al menos un, puerto PCIe aguas abajo, de modo tal que la función sea usada por el al menos un host

Opcionalmente, un extremo del al menos un módulo de dispositivo terminal de espejo se conecta al, al menos un, puerto PCIe aguas abajo, un extremo del al menos un módulo de dispositivo terminal virtual se conecta a los múltiples puertos PCIe aguas arriba, y el módulo de mapeo se conecta de manera separada a otro extremo del al menos un módulo de dispositivo terminal de espejo y otro extremo del al menos un módulo de dispositivo terminal virtual.

# ES 2 773 032 T3

Opcionalmente, el módulo de mapeo puede configurarse específicamente para implementar el mapeo entre el al menos un módulo de dispositivo terminal de espejo y el al menos un módulo de dispositivo terminal virtual, por ejemplo, identificaciones y/o direcciones.

En referencia a la posible implementación anterior, en una tercera implementación posible del primer aspecto, un primer puerto PCIe aguas abajo en el al menos un puerto PCIe aguas abajo no presenta espacio de configuración PCIe, y cada uno de los múltiples puertos PCIe aguas arriba presenta un espacio de configuración PCIe.

5

10

15

20

35

40

45

50

55

En referencia a la posible implementación anterior, en una cuarta implementación posible del primer aspecto, el dispositivo de conmutación además incluye al menos un espacio de configuración PCIe que corresponde a cada uno de los al menos un puerto PCIe aguas abajo, y el al menos un módulo de dispositivo terminal virtual se conecta específicamente a los múltiples puertos PCIe aguas arriba mediante el uso del al menos un espacio de configuración PCIe correspondiente al, al menos un, puerto PCIe aguas abajo.

En referencia a las posibles implementaciones anteriores, en una quinta posible implementación del primer aspecto, el módulo de mapeo almacena: una primera tabla de mapeo, usada para almacenar una relación de mapeo desde una identificación en el dominio PCIe correspondiente al, al menos un, host hasta una identificación en el dominio PCIe correspondiente al, al menos un, dispositivo de E/S; una segunda tabla de mapeo, usada para almacenar una relación de mapeo desde la identificación en el dominio PCIe correspondiente al, al menos un, dispositivo de E/S hasta la identificación en el dominio PCIe correspondiente al, al menos un, host.

Opcionalmente, la primera tabla de mapeo se usa para almacenar una relación de mapeo desde una identificación del al menos un módulo de dispositivo terminal virtual hasta una identificación del al menos un módulo de dispositivo terminal de espejo. La segunda tabla de mapeo se usa específicamente para almacenar una relación de mapeo desde la identificación del al menos un módulo de dispositivo terminal de espejo hasta la identificación del al menos un módulo de dispositivo terminal virtual. Opcionalmente, el módulo de mapeo se configura específicamente para implementar el mapeo entre la identificación del al menos un módulo de dispositivo terminal virtual y la identificación del al menos un módulo de dispositivo terminal de espejo en función de la primera y la segunda tabla de mapeo.

En referencia a las posibles implementaciones anteriores, en una sexta implementación posible del primer aspecto, un primer módulo de dispositivo terminal de espejo en el al menos un módulo de dispositivo terminal de espejo es específicamente una tercera tabla de mapeo, y la tercera tabla de mapeo se usa para almacenar un registro de dirección base (BAR, por sus siglas en inglés) y un tamaño de BAR de una función virtual de un primer dispositivo de E/S en el al menos un dispositivo de E/S, donde el primer módulo de dispositivo terminal de espejo se configura para almacenar el contenido de la configuración PCIe del primer dispositivo de E/S.

Opcionalmente, el módulo de mapeo se configura específicamente para implementar el mapeo desde una dirección del al menos un módulo de dispositivo terminal virtual a una dirección del al menos un módulo de dispositivo terminal de espejo en función de la tercera y la primera tabla de mapeo.

En referencia a las posibles implementaciones anteriores, en una séptima implementación posible del primer aspecto, un primer módulo de dispositivo terminal virtual en el al menos un módulo de dispositivo terminal virtual se configura específicamente para virtualizar una función física de un segundo dispositivo de E/S en el al menos un dispositivo de E/S, de modo tal que la función física sea usada por un primer host en el al menos un host, donde un lector de función física del segundo dispositivo de E/S es cargado por un procesador del primer host.

En referencia a las posibles implementaciones anteriores, en una octava implementación posible del primer aspecto, un segundo módulo de dispositivo terminal virtual en el al menos un módulo de dispositivo terminal virtual se configura específicamente para virtualizar una función virtual de un tercer dispositivo de E/S en el al menos un dispositivo de E/S, de modo tal que la función virtual sea usada por un segundo host en el al menos un host, donde un lector de función física del tercer dispositivo de E/S es cargado por un BMC de administración en el al menos un host.

En referencia a las posibles implementaciones anteriores, en una novena implementación posible del primer aspecto, un tercer módulo de dispositivo terminal virtual en el al menos un módulo de dispositivo terminal virtual se configura específicamente para virtualizar una función física y una función virtual de un cuarto dispositivo de E/S en el al menos un dispositivo de E/S, de modo tal que la función física y la función virtual sean usadas por un tercer host en el al menos un host, donde un lector de función física del cuarto dispositivo de E/S es cargado por el BMC de administración en el al menos un host, y un lector de función física del tercer módulo de dispositivo terminal virtual es cargado por un procesador del tercer host.

En referencia a las posibles implementaciones anteriores, en una décima implementación posible del primer aspecto, el dispositivo de conmutación es específicamente un dispositivo de conmutación de host y un dispositivo de conmutación de E/S, y el dispositivo de conmutación de host y el dispositivo de conmutación de E/S están conectados mediante el uso de una interfaz Ethernet, donde el dispositivo de conmutación de host incluye múltiples puertos PCle aguas arriba; y el dispositivo de conmutación de E/S incluye el aparato de procesamiento interno, el al menos un módulo de dispositivo terminal virtual, el módulo de mapeo, el al menos un módulo de dispositivo terminal de espejo y el al menos un puerto PCle aguas abajo.

En referencia a las posibles implementaciones anteriores, en una onceava implementación posible, un aparato de procesamiento interno se configura para: recibir una instrucción de inicialización enviada por el BMC de administración en el al menos un host; y transmitir, en función de la instrucción de inicialización, un paquete de lectura/escritura de configuración al, al menos un, puerto PCle aguas abajo mediante el uso de la línea de conexión interna; y el aparato de procesamiento interno además se configura para: después de que un dispositivo de E/S conectado al dispositivo de conmutación sea determinado, informar, al BMC de administración, los datos sobre el dispositivo de E/S conectado al dispositivo de conmutación, donde la información incluye información de identificación.

Opcionalmente, el aparato de procesamiento interno puede conectarse a los múltiples puertos PCle aguas arriba mediante el uso de la línea de conexión interna, y el aparato de procesamiento interno puede recibir, específicamente, mediante el uso de los múltiples puertos PCle aguas arriba, la instrucción de inicialización enviada por el BMC de administración. El aparato de procesamiento interno puede transmitir el paquete de lectura/escritura de configuración al, al menos un, puerto PCle aguas abajo en función de la instrucción de inicialización, en función de un paquete de respuesta de lectura/escritura de configuración recibido, la información sobre el dispositivo de E/S conectado al dispositivo de conmutación, e informar, al BMC de administración, mediante el uso de los múltiples puertos PCle aguas arriba, la información sobre el dispositivo de E/S conectado al dispositivo de conmutación, donde la información puede incluir información de identificación (por ejemplo, una BDF) o puede incluso contener una estructura de topología (por ejemplo, un árbol de estructura PCle) o similares.

En referencia a las posibles implementaciones anteriores, en una doceava implementación posible del primer aspecto, el aparato de procesamiento interno además se configura para: recibir información de administración de configuración enviada por el BMC de administración en el al menos un host; y configurar los múltiples puertos PCle aguas arriba y el al menos un puerto PCle aguas abajo en función de la información de administración de configuración.

En referencia a las posibles implementaciones anteriores, en una treceava implementación posible del primer aspecto, el aparato de procesamiento interno además se configura para procesar un evento de excepción y un evento de intercambio en caliente.

#### Breve descripción de los dibujos

5

10

15

20

25

30

35

40

45

50

La FIG. 1 es un diagrama de bloque esquemático de un sistema PCle en la técnica anterior;

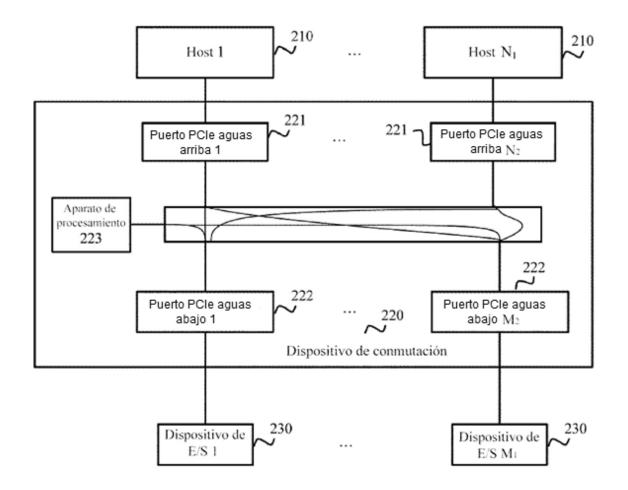

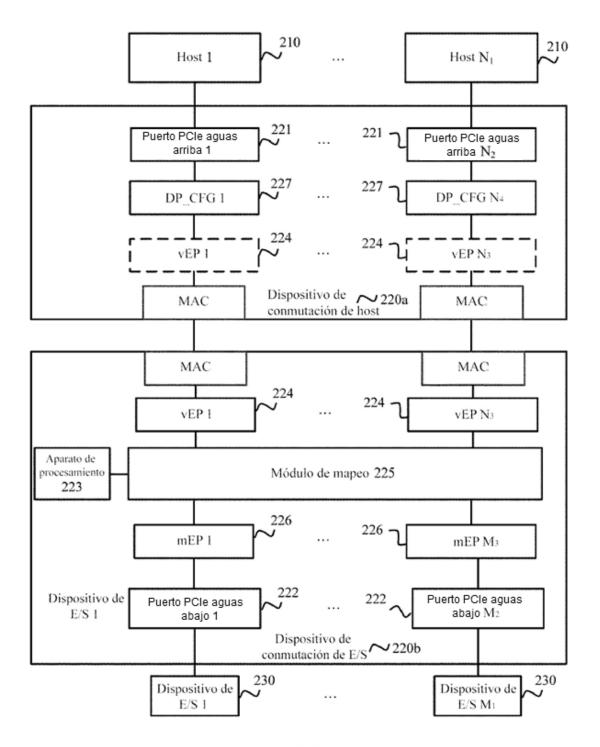

la FIG. 2 es un diagrama de bloque esquemático de un sistema PCle según una realización de la presente invención;

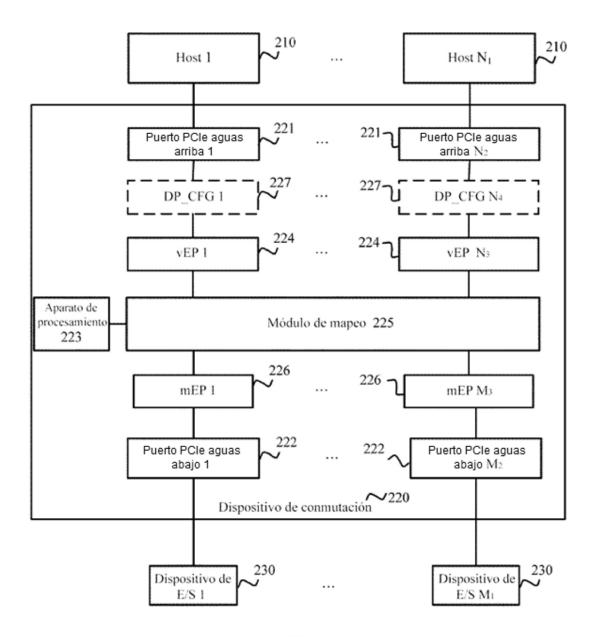

la FIG. 3 es otro diagrama de bloque esquemático de un sistema PCIe según una realización de la presente invención;

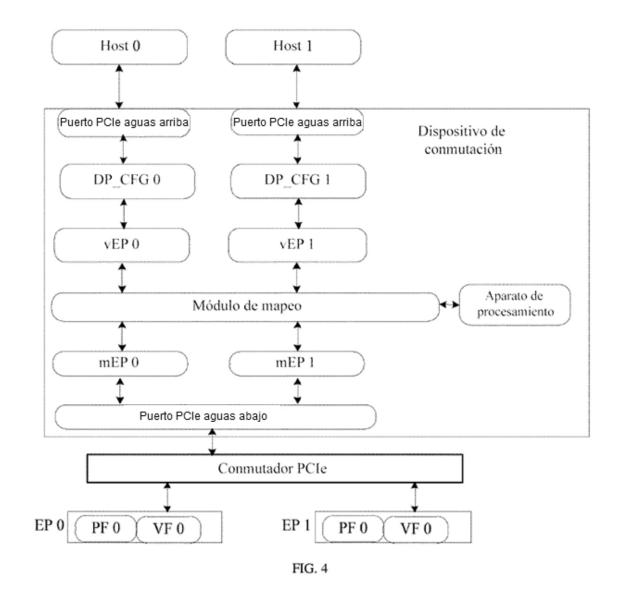

la FIG. 4 es otro diagrama de bloque esquemático de un sistema PCIe según una realización de la presente invención;

la FIG. 5 es otro diagrama de bloque esquemático de un sistema PCIe según una realización de la presente invención;

la FIG. 6 es otro diagrama de bloque esquemático de un sistema PCIe según una realización de la presente invención;

la FIG. 7 es otro diagrama de bloque esquemático de un sistema PCIe según una realización de la presente invención;

la FIG. 8 es otro diagrama de bloque esquemático de un sistema PCIe según una realización de la presente invención;

la FIG. 9 es otro diagrama de bloque esquemático de un sistema PCle según una realización de la presente invención; y

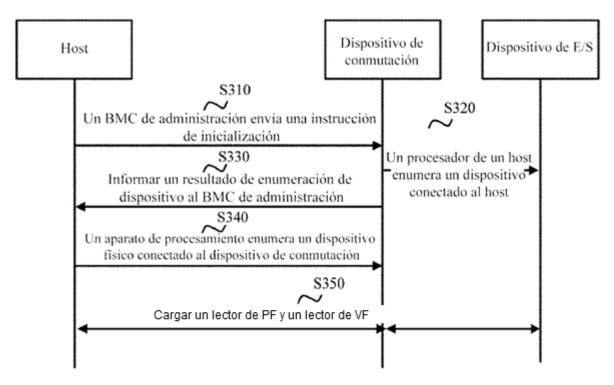

la FIG. 10 es un diagrama de flujo esquemático de un procedimiento para inicializar un sistema PCIe según una realización de la presente invención.

### Descripción de las realizaciones

La invención realizada se describe en las reivindicaciones independientes adjuntas. En el conjunto de reivindicaciones dependientes, se describen realizaciones adicionales.

Lo siguiente describe las soluciones técnicas en las realizaciones de la presente invención en referencia a los dibujos adjuntos en las realizaciones de la presente invención.

La FIG. 2 es un diagrama arquitectónico de un sistema PCIe 200 según una realización de la presente invención. El sistema PCIe 200 puede configurarse para implementar el uso compartido de un dispositivo de E/S mediante múltiples procesos en un host o implementar el uso compartido de un dispositivo de E/S por parte de múltiples hosts.

Como se muestra en la FIG. 2, el sistema PCle 200 incluye:  $N_1$  hosts 210, un dispositivo de conmutación 220 y  $M_1$  dispositivos de E/S 230, donde  $N_1 \ge 1$  y  $M_1 \ge 1$ . Al dispositivo de E/S también se puede hacer referencia como el dispositivo terminal (en inglés, Endpoint - EP).

La FIG. 2 muestra, a través del uso de un ejemplo, que el sistema PCle 200 incluye solo un dispositivo de conmutación y el dispositivo de conmutación está conectado a al menos un host y al menos un dispositivo de E/S. Sin embargo,

debe entenderse que el sistema PCle 200 puede incluir, de manera alternativa, múltiples dispositivos de conmutación, y cada dispositivo de conmutación puede estar conectado a al menos un host y al menos un dispositivo de E/S. Cada dispositivo de conmutación y al menos un host y al menos un dispositivo de E/S que están conectados al dispositivo de conmutación pueden considerarse como una unidad de red. De manera correspondiente, el sistema PCle 200 puede incluir una o más unidades de red. Sin embargo, esto no se limita a esta realización de la presente invención.

5

10

15

20

25

30

35

40

45

50

55

60

Opcionalmente, en esta realización de la presente invención, el host puede ser específicamente un dispositivo como un servidor o un ordenador personal. De manera alternativa, el host puede ser una máquina virtual. Esto no se limita a esta realización de la presente invención. Opcionalmente, algunos o todos los N₁ hosts pueden incluir un mando de administración de la placa base (en inglés, Baseboard Management Controller - BMC), es decir que los N<sub>1</sub> hosts pueden incluir uno o más BMC. Al menos uno del uno o más BMC puede presentar una función de administración de configuración, y se configura específicamente para administrar y controlar la unidad de red, incluyendo el al menos un host, el dispositivo de conmutación y el al menos un dispositivo de E/S. Por cuestiones de facilidad de descripción, en la descripción a continuación, a un BMC que presenta una función de administración de configuración se hace referencia como BMC de administración. Opcionalmente, el BMC de administración se puede configurar para implementar una función de administración de configuración que posee una CPU de administración en la técnica anterior. Sin embargo, a diferencia de la CPU de administración de la técnica anterior, el BMC de administración puede responsabilizarse solo de la administración de configuración de un dispositivo de conmutación, y al menos un host y al menos un dispositivo de E/S que se conectan al dispositivo de conmutación en una unidad de red a la que pertenece el BMC de administración, pero no puede ser responsable de la administración de configuración de los hosts, los dispositivos de E/S, y los dispositivos de conmutación en otras unidades de red que pueden existir en una red. Esto no se limita a esta realización de la presente invención.

Opcionalmente, el dispositivo de E/S puede ser específicamente un dispositivo tal como un adaptador de bus de host (en inglés, Host Bus Adapter - HBA) o un disco de estado sólido. (en inglés, Solid State disk - SSD). Esto no se limita a esta realización de la presente invención.

En esta realización de la presente invención, el dispositivo de conmutación 220 puede incluir  $N_2$  puertos PCIe aguas arriba 221,  $M_2$  puertos PCIe aguas abajo 222 y un aparato de procesamiento interno 223, donde  $N_2 > 1$  y  $M_2 \ge 1$ . Los  $N_2$  puertos PCIe aguas arriba 221 se configuran para conectarse a los  $N_1$  hosts 210. Los  $M_2$  puertos PCIe aguas abajo 222 se configuran para conectarse a los  $M_1$  dispositivos de E/S 230. El aparato de procesamiento interno 223 puede conectarse a los  $M_2$  puertos PCIe aguas abajo 222 mediante el uso de una línea de conexión interna del dispositivo de conmutación, y puede conectarse a los  $N_2$  puertos PCIe aguas arriba 221 mediante el uso de la línea de conexión interna del dispositivo de conmutación. Específicamente, el dispositivo de conmutación 220 puede conectarse a los  $N_1$  hosts 210 mediante el uso de los  $N_2$  puertos PCIe aguas arriba 221. Si  $N_2 = N_1$ , es decir, una cantidad de los puertos PCIe aguas arriba del dispositivo de conmutación es igual a la cantidad de hosts conectados al dispositivo de conmutación, los  $N_2$  puertos PCIe aguas arriba pueden conectarse a los  $N_1$  hosts en una correspondencia de uno a uno. Si  $N_2 > N_1$ , es decir, una cantidad de los puertos PCIe aguas arriba del dispositivo de conmutación es superior a una cantidad de los hosts conectados al dispositivo de conmutación,  $N_1$  de los  $N_2$  puertos PCIe aguas arriba puede conectarse a los  $N_1$  hosts en una correspondencia de uno a uno, y los puertos PCIe aguas arriba restantes ( $N_2$ - $N_1$ ) pueden permanecer inactivos o establecerse como puertos PCIe aguas abajo. Sin embargo, esto no se limita a esta realización de la presente invención.

De manera similar, el dispositivo de conmutación 220 puede conectarse a los M<sub>1</sub> dispositivos de E/S 230 mediante el uso de los M<sub>2</sub> puertos PCIe aguas abajo 222. Si M<sub>2</sub> = M<sub>1</sub>, es decir, una cantidad de los puertos PCIe aguas abajo del dispositivo de conmutación es igual a la cantidad de dispositivos de E/S conectados al dispositivo de conmutación, los M<sub>2</sub> puertos PCIe aguas abajo pueden conectarse a los M<sub>1</sub> dispositivos de E/S en una correspondencia de uno a uno. Si M<sub>2</sub> > M<sub>1</sub>, es decir, una cantidad de los puertos PCIe aguas abajo del dispositivo de conmutación es superior a una cantidad de los dispositivos de E/S conectados al dispositivo de conmutación, el M<sub>1</sub> de los M<sub>2</sub> puertos PCIe aguas abajo puede conectarse a los M<sub>1</sub> dispositivos de E/S en una correspondencia de uno a uno, y los puertos PCIe aguas abajo restantes (M<sub>2</sub>-M<sub>1</sub>) pueden permanecer inactivos o establecerse como puertos PCIe aguas arriba. Si M<sub>2</sub> < M<sub>1</sub>, es decir, una cantidad de los puertos PCIe aguas abajo del dispositivo de conmutación es inferior a la cantidad de dispositivos de E/S conectados al dispositivo de conmutación, el sistema PCIe 200 puede incluir además uno o más conmutadores PCIe, y algunos o todos los M<sub>2</sub> puertos PCIe aguas abajo pueden conectarse a los M<sub>1</sub> dispositivos de E/S mediante el uso del conmutador PCIe. De esta manera, la cantidad de los dispositivos de E/S conectados al dispositivo de conmutación puede aumentar, y el rendimiento de conmutación no se reduce. Sin embargo, esto no se limita a esta realización de la presente invención.

Opcionalmente, el sistema PCle 200 incluye además el conmutador PCle, y los M<sub>2</sub> puertos PCle aguas abajo pueden conectarse a los M<sub>1</sub> dispositivos de E/S mediante el uso del conmutador PCle.

Además, el dispositivo de conmutación 220 además incluye el aparato de procesamiento interno 223. El aparato de procesamiento interno 223 puede ser específicamente un módulo de procesamiento, por ejemplo, un procesador y/o un circuito de procesamiento de hardware. Opcionalmente, el aparato de procesamiento interno puede implementarse mediante un procesador y un circuito de hardware. De manera alternativa, el aparato de procesamiento interno puede implementarse solo mediante un circuito de hardware. Esto no se limita a esta realización de la presente invención.

En esta realización de la presente invención, el aparato de procesamiento interno puede configurarse para enumerar un dispositivo físico (es decir, un dispositivo real, incluso sin módulo funcional alguno) conectado al dispositivo de conmutación, por ejemplo, determinar un dispositivo físico conectado al dispositivo de conmutación mediante el uso de los M₂ puertos PCle aguas abajo 222, o puede, adicionalmente, obtener información, por ejemplo, una identificación (una BDF) o una estructura de topología, de múltiples dispositivos físicos conectados al dispositivo de conmutación y puede, además, configurar un árbol de estructura de dominio PCle en función la información sobre los múltiples dispositivos físicos. El dispositivo físico además puede incluir el dispositivo de E/S y/o el conmutador PCle. En este caso, el aparato de procesamiento interno puede considerarse como un puerto raíz virtual (en inglés, Root Port - RP) o un complejo raíz (en inglés, Root Complex - RC). Sin embargo, esto no se limita a esta realización de la presente invención.

5

10

15

20

25

30

35

40

45

50

55

60

Opcionalmente, el aparato de procesamiento interno 223 puede ejecutar activamente la enumeración de dispositivos, por ejemplo, ejecutar una enumeración de dispositivo en una etapa de inicialización del sistema. Alternativamente, el aparato de procesamiento interno 223 puede efectuar, al recibir una instrucción de otro dispositivo, la enumeración de dispositivos en función de la instrucción. Por ejemplo, el aparato de procesamiento interno 223 puede recibir una instrucción de inicialización o una instrucción de enumeración que se envía mediante el BMC de administración, y ejecutar la enumeración de dispositivos en función de la instrucción de inicialización o la instrucción de enumeración. Sin embargo, esto no se limita a esta realización de la presente invención.

Específicamente, al ejecutar la enumeración de dispositivos, el aparato de procesamiento interno 223 puede enviar múltiples paquetes de lectura/escritura de configuración al, al menos un, puerto PCIe aguas abajo 222. El paquete de lectura/escritura de configuración transporta una identificación de solicitud (en inglés, Request Identification - RID) y una identificación de completador (en inglés, Completer Identification - CID), donde un valor de la RID puede establecerse en una BDF del aparato de procesamiento interno 223, y un valor de la CID puede enumerarse en secuencia, comenzando desde un valor inicial. El aparato de procesamiento interno 223 puede recibir un paquete de respuesta de lectura/escritura de configuración correspondiente a al menos uno de múltiples paquetes de lectura/escritura de configuración. El paquete de respuesta de lectura/escritura de configuración transporta una RID y una CID en el paquete de lectura/escritura de configuración correspondiente. De esta manera, el aparato de procesamiento interno 223 determina, mediante el reconocimiento del paquete de respuesta de lectura/escritura de configuración (por ejemplo, mediante el reconocimiento de la CID en el paquete de respuesta de lectura/escritura de configuración), si el dispositivo de conmutación 220 está conectado a un dispositivo físico cuyo número de BDF es la CID en el paquete de respuesta de lectura/escritura de configuración Sin embargo, esto no se limita a esta realización de la presente invención.

En una realización opcional, si el aparato de procesamiento interno 223 es implementado por un procesador y un circuito de hardware, donde el procesador y el circuito de hardware pueden conectarse mediante el uso de un bus interno, el procesador se puede configurar para: recibir una instrucción de inicialización (o una instrucción de enumeración) desde el BMC de administración; generar, en función de la instrucción de inicialización, información sobre un paquete de enumeración, la cual incluye datos que necesitan los paquetes de lectura/escritura de configuración de tipo 0 (Tipo0) y tipo 1 (Tipo1); y producir la información generada al bus interno. El circuito de hardware puede recibir, mediante el uso del bus interno, la información generada por el procesador, encapsular la información como un paquete de capa de transacciones (en inglés, Transaction Layer Packet - TLP) y enviar el TLP al, al menos un puerto PCle aguas abaio 222 mediante el uso de un circuito o módulo de siguiente nivel conectado al aparato de procesamiento interno 223. Además, el circuito de hardware puede configurarse adicionalmente para reconocer un paquete de respuesta de lectura/escritura de configuración al recibir el paquete de respuesta de lectura/escritura de configuración enviado por el al menos un puerto PCIe aguas abajo 222. Por ejemplo, el circuito de hardware puede recibir un paquete de compleción (en inglés, Completion - CPL)/(en inglés, Completion Data - CPLD) transmitido por el al menos un puerto PCIe aguas abajo 222 y reconocer una ID en el paquete CPL/CPLD recibido. Por medio del disparo de interrupción del circuito de hardware, el paquete CPL/CPLD puede transmitirse al procesador del aparato de procesamiento interno 223 mediante el uso del bus interno. Específicamente, el circuito de hardware puede desensamblar el paquete CPL/CPLD en un formato de datos que cumpla con una secuencia de tiempo del bus interno y enviar el paquete CPL/CPLD al bus interno. El procesador del aparato de procesamiento interno 223 puede configurarse adicionalmente para: analizar la información del paquete recibido, almacenar la información del paquete y generar un árbol de estructura de un dominio PCle en función de la información del paquete. Después de haber completado la enumeración del dispositivo, el procesador puede transmitir, además, la información sobre el árbol de estructura PCIe generado al BMC de administración mediante el uso de los múltiples puertos PCIe aguas arriba 221. Sin embargo, esto no se limita a esta realización de la presente invención.

Por lo tanto, el sistema PCle provisto en esta realización de la presente invención incluye al menos un host, un dispositivo de conmutación y el al menos un dispositivo de E/S. El dispositivo de conmutación incluye los múltiples puertos PCle aguas arriba configurados para conectarse al, al menos un, host; el al menos un puerto PCle aguas abajo configurado para conectarse al, al menos un, dispositivo de E/S; y el aparato de procesamiento interno. El aparato de procesamiento se conecta al, al menos un, puerto PCle aguas abajo mediante el uso de un bus interno y se configura para: transmitir un paquete de lectura/escritura de configuración al, al menos un, puerto PCle aguas abajo mediante el uso de la línea de conexión interna; recibir un paquete de respuesta de lectura/escritura de configuración transmitido mediante el al menos un puerto PCle aguas abajo mediante el uso de una línea de conexión interna; y determinar, en función de una identificación de completador transportada en el paquete de respuesta de

lectura/escritura de configuración, que el dispositivo de conmutación está conectado a un dispositivo de E/S cuya identificación es la identificación de completador. De esta manera, cuando un dispositivo de conmutación en el sistema PCIe falla, solo el al menos un host y el al menos un dispositivo de E/S que están conectados al dispositivo de conmutación puede resultar afectados, y otro dispositivo de conmutación, y un host y un dispositivo de E/S que están conectados al otro dispositivo de conmutación en el sistema PCIe no son afectados. Por lo tanto, en comparación con una CPU de administración externa en la técnica anterior, es posible mejorar tanto la estabilidad como la confiabilidad del sistema PCIe.

Opcionalmente, el aparato de procesamiento interno 223 puede presentar además al menos una de las siguientes funciones: procesamiento de un evento de intercambio en caliente, procesamiento de eventos de excepción o configuración de componentes (por ejemplo, configuración de registros).

El aparato de procesamiento interno 223 se puede configurar para procesar un evento de intercambio en caliente. Específicamente, el aparato de procesamiento interno 223 puede detectar un evento de intercambio en caliente accionado por el BMC de administración y/o el hardware, y ejecutar un procedimiento de procesamiento de intercambio en caliente correspondiente. El aparato de procesamiento interno 223 puede configurarse además para procesar un evento de excepción. Específicamente, el aparato de procesamiento interno 223 puede procesar una excepción de hardware, asentar un registro de evento de excepción e informar el registro de evento de excepción. Además, el aparato de procesamiento interno 223 se puede configurar adicionalmente para configurar un componente. Específicamente, el aparato de procesamiento interno 223 puede configurar un registro en una etapa de inicialización o modificar una configuración del registro. El aparato de procesamiento interno 223 puede obtener información necesaria para la configuración de componentes en un procedimiento de enumeración de dispositivos, o puede recibir información de administración de configuración enviada por el BMC de administración, configurar el componente en función de la información de administración de configuración y similares. Esto no se limita a esta realización de la presente invención.

En una realización opcional, el aparato de procesamiento interno 223 es implementado por el procesador y el circuito de hardware, al implementar la función de procesamiento de evento de excepción, el circuito de hardware en el aparato de procesamiento interno 223 puede capturar la información de excepción relacionada con una función física del dispositivo de E/S y accionar el procesador mediante el uso de la información de interrupción configurada por el procesador en el aparato de procesamiento interno 223. El procesador del aparato de procesamiento interno 223 puede reconocer un tipo de excepción. Si este último es específicamente corregible o es un error no fatal que no puede corregirse, el procesador puede ejecutar un autoprocesamiento y producir solo una alarma sin informar. Si el tipo de excepción es específicamente un error fatal que no puede corregirse, el procesador puede romper un enlace del dispositivo de E/S e informar el enlace roto del dispositivo de E/S al BMC de administración. Después de reconocer el dispositivo de E/S cuyo enlace está roto, el BMC de administración puede desinstalar un lector correspondiente al dispositivo de E/S. Además, opcionalmente, el BMC de administración puede notificar un módulo de administración de administración de plataformas (en inglés, Shelf Management Module - SMM) sobre la actualización de la información de red. El SMM administra y controla a un host correspondiente al dispositivo de E/S que presenta una excepción, por ejemplo, ejecuta la desinstalación del lector o restablece el procesamiento de inicialización. Esto no se limita a esta realización de la presente invención.

En esta realización de la presente invención, el aparato de procesamiento interno 223 puede configurarse para: recibir un paquete de datos enviado por los M<sub>1</sub> dispositivos de E/S 230 mediante el uso de los M<sub>2</sub> puertos PCIe aguas abajo 222, procesar el paquete de datos recibido, por ejemplo, convertir una secuencia de tiempo, y enviar el paquete de datos procesado a los N<sub>2</sub> puertos PCIe aguas arriba 221 mediante el uso de la línea de conexión interna. Además, el aparato de procesamiento interno 223 puede configurarse adicionalmente para: recibir un paquete de datos enviado por los N<sub>1</sub> hosts 210 mediante el uso de los N<sub>2</sub> puertos PCIe aguas arriba 221, procesar el paquete de datos recibido, por ejemplo, convertir una secuencia de tiempo, y enviar el paquete de datos procesado a los M<sub>2</sub> puertos PCIe aguas abajo 222 mediante el uso de la línea de conexión interna.

En una realización opcional, si el aparato de procesamiento interno 223 es implementado por el procesador y el circuito de hardware, al recibir los datos enviados por el host, el procesador en el aparato de procesamiento interno puede analizar una secuencia de tiempo del bus de una interfaz del BMC de administración y producir los datos en una secuencia de tiempo del bus interno. Al recibir los datos reenviados mediante un circuito o módulo de siguiente nivel, el procesador puede analizar la secuencia de tiempo del bus interno y producir los datos para un bus de la interfaz del BMC de administración. Sin embargo, esto no se limita a esta realización de la presente invención.

Opcionalmente, en esta realización de la presente invención, el BMC de administración puede informar una información de red (o información de configuración de red) al SMM mediante el uso de un puerto de red. El SMM se puede configurar para que sea responsable de administrar toda una red. Un usuario puede establecer, en función de un requerimiento, una conexión de mapeo entre el host y el dispositivo de E/S mediante el uso de una interfaz de interacción humano-ordenador del SMM. En este caso, opcionalmente, el BMC de administración puede configurarse adicionalmente para: recibir una información de requerimiento de configuración enviada por el SMM y determinar la información de administración de configuración en función de la información de requerimiento de configuración. Sin embargo, esto no se limita a esta realización de la presente invención.

## ES 2 773 032 T3

Opcionalmente, en esta realización de la presente invención, cada uno de los  $N_2$  puertos PCIe aguas arriba 221 presenta un espacio de configuración PCIe, y ninguno de los  $M_2$  puertos PCIe aguas abajo 222 presenta espacio de configuración PCIe alguno.

5

10

15

20

25

30

40

45

50

55

En esta realización de la presente invención, el puerto PCIe aguas arriba 221 en el dispositivo de conmutación 220 presenta el espacio de configuración PCIe y es un puerto PCIe estándar (es decir, un puente P2P aguas arriba estándar). El puerto PCIe aguas abajo 222 en el dispositivo de conmutación 220 no presenta ningún espacio de configuración PCIe y no es un puerto PCIe estándar (es decir, no es un puente P2P aguas abajo estándar). Opcionalmente, el dispositivo de conmutación 220 podría no almacenar, adicionalmente, los espacios de configuración PCIe de los M₂ puertos PCIe aguas abajo 222, es decir que no hay ningún espacio de configuración PCIe del puerto PCIe aguas abajo 222 en el dispositivo de conmutación 220. De manera alternativa, el dispositivo de conmutación 220 puede almacenar, adicionalmente, un espacio de configuración de cada uno de los M₂ puertos PCIe aguas abajo 222, es decir que el espacio de configuración PCIe del puerto PCIe aguas abajo 222 se separa del puerto PCIe aguas abajo 222 en el dispositivo de conmutación 220. De manera alternativa, el dispositivo de conmutación 220 puede almacenar adicionalmente espacios de configuración PCIe de algunos de los M₂ puertos PCIe aguas abajo 222 pero no almacenar adicionalmente espacios de configuración PCIe de algunos otros puertos PCIe aguas abajo 222. Esto no se limita a esta realización de la presente invención.

Opcionalmente, en esta realización de la presente invención, el puerto PCIe aguas abajo 222 puede corresponder al, al menos un, espacio de configuración PCIe, y el al menos un espacio de configuración PCIe correspondiente al puerto PCIe aguas abajo 222 y el puerto PCIe aguas abajo 222 pueden disponerse individualmente en el dispositivo de conmutación 220, es decir, el puerto PCIe aguas abajo 222 puede estar separado del al menos un espacio de configuración PCIe correspondiente al puerto PCIe aguas abajo 222. Además, opcionalmente, el al menos un espacio de configuración PCIe correspondiente al puerto PCIe aguas abajo 222 puede pertenecer al dominio PCIe correspondiente a los N<sub>1</sub> hosts 210. De esta manera, cuando el dispositivo de conmutación 220 almacena múltiples espacios de configuración PCIe correspondientes a un puerto PCIe aguas abajo 222, el puerto PCIe aguas abajo 222 puede usarse como puertos múltiples a ser usados por los hosts 210, a fin de mejorar la utilización de recursos del sistema

Debe entenderse que, para la descripción en la realización anterior, se usa un ejemplo en el que todos los  $N_2$  puertos PCIe aguas arriba 221 en el dispositivo de conmutación 220 presentan el espacio de configuración PCIe y todos los  $M_2$  puertos PCIe aguas abajo 222 no presentan espacio de configuración PCIe alguno. Opcionalmente, algunos de los  $M_2$  puertos PCIe aguas abajo 222 pueden presentar un espacio de configuración PCIe y algunos otros puertos PCIe aguas abajo 222 podrían no presentar un espacio de configuración PCIe. De manera alternativa, todos los  $M_2$  puertos PCIe aguas abajo 222 presentan un espacio de configuración PCIe. En otra realización opcional, algunos o todos los  $N_2$  puertos PCIe aguas arriba 221 pueden no presentar espacio de configuración PCIe alguno. Esto no se limita a esta realización de la presente invención.

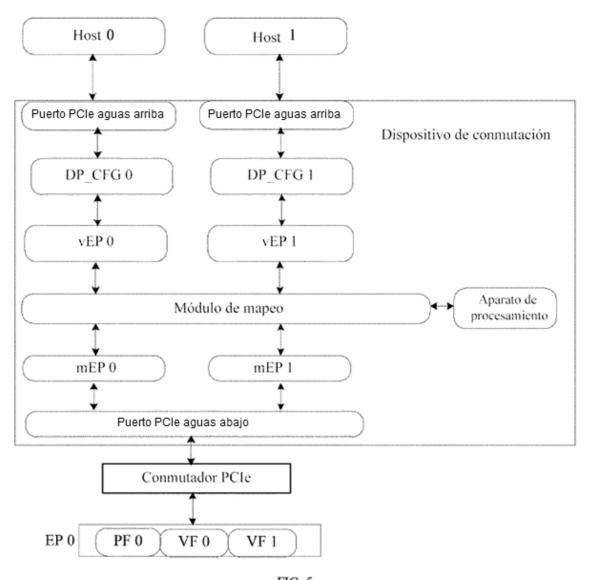

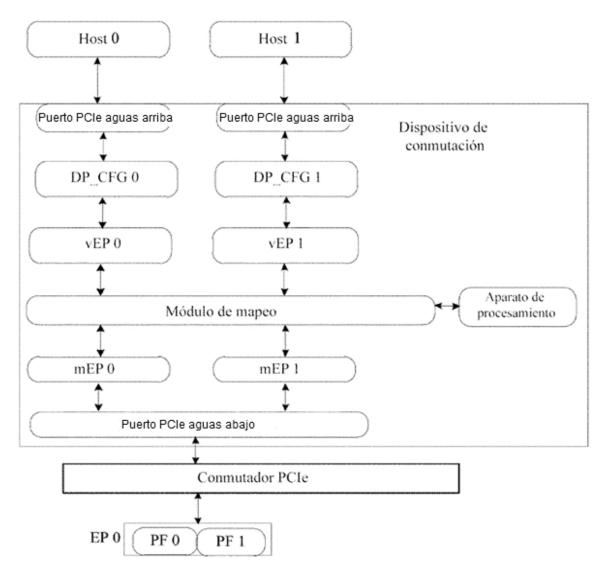

Opcionalmente, como se muestra en la FIG. 3, el dispositivo de conmutación 220 además incluye: N<sub>3</sub> módulos de dispositivo terminal virtual (abreviado, vEP, por sus siglas en inglés) 224, un módulo de mapeo (MAP, por sus siglas en inglés) 225 y M<sub>3</sub> módulos de dispositivo terminal de espejo (abreviado, mEP, por sus siglas en inglés) 226.

Los  $N_3$  vEP 224 pueden conectarse a los  $N_2$  puertos PCIe aguas arriba 221, y se configuran para virtualizar funciones de los  $M_1$  dispositivos de E/S 230 conectados a los  $M_2$  puertos PCIe aguas abajo 222, de modo tal que las funciones sean usadas por los  $N_1$  hosts 221 conectados a los  $N_2$  puertos PCIe aguas arriba 221, donde  $N_3 \ge 1$ .

Los  $M_3$  mEP 226 pueden conectarse a los  $M_2$  puertos PCIe aguas abajo 222, y se configuran para almacenar contenido de configuración PCIe de los  $M_1$  dispositivos de E/S 230 conectados a los  $M_2$  puertos PCIe aguas abajo 222, donde  $M_3 \ge 1$ .

El módulo de mapeo 225 puede conectarse por separado a los  $N_3$  vEP 224 y los  $M_3$  mEP 226, y se configura para implementar el mapeo entre un dominio PCIe correspondiente a los  $N_1$  hosts 210 y un dominio PCIe correspondiente a los  $M_1$  dispositivos de E/S 230.

En esta realización de la presente invención, opcionalmente, el dispositivo de conmutación 220 puede incluir además uno o más mEP 226, el módulo de mapeo 225 y uno o más vEP 224. Un valor de  $N_3$  puede determinarse por una cantidad de funciones que deben o pueden ser usadas por los  $N_1$  hosts 210, y  $N_3$  puede ser igual a  $N_3$  o no. Por ejemplo, tanto  $N_3$  y  $N_3$  pueden ser iguales a una cantidad total de funciones (por ejemplo, una cantidad total de VF) que poseen los  $N_1$  dispositivos de E/S 230. Esto no se limita a esta realización de la presente invención.

Específicamente, el mEP 226 puede ser un reflejo de un EP real y se configura para almacenar el contenido de configuración del dispositivo de E/S (es decir, el dispositivo terminal) 230. El vEP 224 puede configurarse para virtualizar una función física y/o una función virtual del dispositivo terminal 230, y puede ser específicamente un espacio de configuración PCIe correspondiente a la función física de la función virtual del dispositivo terminal 230. El módulo de mapeo 225 puede configurarse para implementar el mapeo entre identificaciones y/o direcciones del dominio PCIe correspondiente a los N<sub>1</sub> hosts 210 y el dominio PCIe correspondiente al, al menos un, dispositivo de E/S 230, para determinar un módulo (o componente) al que se envía la información y/o los datos recibidos. En un ejemplo opcional,

el vEP 224 puede pertenecer al dominio PCIe correspondiente al host 210 y el mEP 226 puede pertenecer al dominio PCIe correspondiente al dispositivo de E/S 230. Correspondientemente, el módulo de mapeo 225 puede configurarse específicamente para implementar un mapeo entre una identificación y/o una dirección de los  $M_3$  mEP 226 y una identificación y/o dirección de los  $N_3$  vEP 224 (es decir, ejecutar un mapeo desde los vEP a los mEP o ejecutar un mapeo desde los mEP a los vEP), a fin de ejecutar un procesamiento de reenvío en un paquete de datos transmitido entre los  $N_1$  hosts 210 y los  $M_1$  dispositivos de E/S 230. Sin embargo, esto no se limita a esta realización de la presente invención

Opcionalmente, los N<sub>2</sub> puertos PCle aguas arriba 221, los N<sub>3</sub> vEP 224, el módulo de mapeo 225, los M<sub>3</sub> mEP 226 y los M<sub>2</sub> puertos PCle aguas abajo 222 pueden conectarse en secuencia. Específicamente, un extremo del vEP 224 puede conectarse al puerto PCle aguas arriba 221 y otro extremo puede conectarse al módulo de mapeo 225. Los N<sub>3</sub> vEP 224 pueden conectarse directa o indirectamente a algunos o todos los N<sub>2</sub> puertos PCle aguas arriba 221. Un extremo del mEP 226 puede conectarse al puerto PCle aguas abajo 222 y otro extremo puede conectarse al módulo de mapeo 225. Los M<sub>3</sub> mEP 226 pueden conectarse directa o indirectamente a algunos o todos los M<sub>2</sub> puertos PCle aguas abajo 222. Sin embargo; esto no se limita a esta realización de la presente invención.

Si los espacios de configuración PCle de los M<sub>2</sub> puertos PCle aguas abajo 222 no se configuran adicionalmente en el dispositivo de conmutación 220, los N<sub>3</sub> vEP 224 pueden conectarse directamente a algunos o todos los N<sub>2</sub> puertos PCle aguas arriba 221. Opcionalmente, si el dispositivo de conmutación 220 además almacena, de manera adicional, un espacio de configuración PCle correspondiente a uno o más puertos PCle aguas abajo 222, por ejemplo, como se muestra en la FIG. 3, el dispositivo de conmutación 220 puede almacenar N<sub>4</sub> espacios de configuración de puerto PCle aguas abajo (abreviado, DP\_CFG, por sus siglas en inglés) 227, cada puerto PCle aguas abajo 222 puede corresponder a cero, uno o más piezas del DP\_CFG 227. En este caso, los N<sub>3</sub> vEP 224 pueden estar conectados a los N<sub>2</sub> puertos PCle aguas arriba 221 mediante el uso de las N<sub>4</sub> piezas del DP\_CFG 227. De este modo, el puerto PCle aguas arriba 221 se conecta al vEP 224 mediante el uso del espacio de configuración PCle que corresponde al puerto PCle aguas abajo. 222, a fin de aumentar una cantidad de vEP que puede ser usada por cada host, mejorando así el rendimiento del sistema.

Además, en esta realización de la presente invención, una función virtual se presenta al host, de modo tal que el sistema PCIe soporte cualquier versión de Windows para usar la función virtual en el host.

En una realización opcional, el módulo de mapeo 225 almacena:

5

10

35

40

45

50

55

una primera tabla de mapeo, usada para almacenar una relación de mapeo desde una identificación en el dominio PCIe correspondiente a los  $N_1$  hosts 210 hasta una identificación en el dominio PCIe correspondiente a los  $M_1$  dispositivos de E/S 230; y

una segunda tabla de mapeo, usada para almacenar una relación de mapeo desde la identificación en el dominio PCIe correspondiente a los  $M_1$  dispositivos de E/S 230 hasta la identificación en el dominio PCIe correspondiente a los  $N_1$  hosts 210.

Opcionalmente, la primera tabla de mapeo puede usarse específicamente para almacenar una relación de mapeo desde una identificación de los N<sub>3</sub> vEP 224 hasta una identificación de los M<sub>3</sub> mEP 226, por ejemplo, una relación de mapeo desde un número de RDF de al menos un vEP 224 para un número de RDF de al menos un mEP 226. La segunda tabla de mapeo puede usarse específicamente para almacenar una relación de mapeo desde la identificación de los M<sub>3</sub> mEP 226 hasta la identificación de los N<sub>3</sub> vEP 224. Sin embargo, esto no se limita a esta realización de la presente invención.

Opcionalmente, en esta realización de la presente invención, el módulo de mapeo 225 puede implementarse mediante un registro y un circuito de procesamiento de hardware. En este caso, la primera tabla de mapeo y la segunda tabla de mapeo pueden ser almacenadas individualmente por el registro. Además, opcionalmente, las identificaciones en la primera y la segunda tabla de mapeo pueden estar representadas por las BDF. De manera alternativa, una función del dispositivo de E/S 230 o una función del vEP 224 pueden volverse a enumerar, por ejemplo, con una secuencia que empieza en 1, a fin de obtener un índice de cada función, y el índice se almacena en las tablas de mapeo en una forma de índice de función, para ahorrar espacio de almacenamiento.

La Tabla 1 y la Tabla 2, respectivamente, muestran posibles implementaciones de la primera tabla de mapeo y la segunda tabla de mapeo. Como se muestra en la Tabla 1, la primera tabla de mapeo puede incluir cuatro columnas. Un valor en la columna de "índice de función" indica un índice de una función en el dominio PCIe correspondiente al dispositivo de E/S 230. El índice se puede obtener mediante la numeración de las BDF de todas las funciones, y puede ocupar uno o varios bits. Un valor en una columna de "habilitar indicación" indica si existe una función correspondiente al índice de función. Un número de bus mEP y un número de función mEP pueden indicar respectivamente un número de bus y un número de un mEP 226 correspondiente al Índice de función. El número de bus mEP y el número de función mEP se combinan en un número de BDF del mEP 226. El número de BDF del -mEP 226 se puede asociar a un número de BDF de un dispositivo de E/S 230 correspondiente al mEP 226. Una cantidad de filas incluida en la primera tabla de mapeo no se limita a esta realización de la presente invención. Por ejemplo, la primera tabla de mapeo puede incluir 1024 entradas (entrada). Sin embargo, esto no se limita a esta realización de la presente

invención.

5

10

15

20

25

30

40

Tabla 1: Posible implementación de la Primera tabla de mapeo

| Índice de función | Habilitar indicaci<br>bit) | ` | Número del bus mEF<br>(ocho bits) | Número<br>mEP | de | función |

|-------------------|----------------------------|---|-----------------------------------|---------------|----|---------|

|                   |                            |   |                                   |               |    |         |

Como se muestra en la Tabla 2, la segunda tabla de mapeo puede incluir cinco columnas. Un valor en una columna de "índice de función" indica un índice (por ejemplo, un índice de función del vEP 224) de una función en el dominio PCIe (que puede ser un módulo funcional virtual y/o un dispositivo físico descubierto por el host 210 por medio de la enumeración) correspondiente al host 210. El índice se puede obtener mediante la numeración de las BDF de todas las funciones y puede ocupar uno o varios bits. Un valor en una columna de "habilitar indicación" indica si existe una función correspondiente al índice de función. Un número de bus de eVF y un número de función de dispositivo de eVF indican, respectivamente, un número de bus y un número de función del dispositivo de una eVF 224 correspondiente al índice de función. El número de bus de eVF y el número de función del dispositivo de eVF se combinan en una BDF de la eVF 224. Un valor en una columna de "indicación PF" se usa para indicar si la función correspondiente al índice de función es una VF o un PE. Una cantidad de filas incluidas en la segunda tabla de mapeo no se limita a esta realización de la presente invención. Por ejemplo, la segunda tabla de mapeo puede incluir 1024 entradas (entrada). Sin embargo, esto no se limita a esta realización de la presente invención.

Tabla 2: Posible implementación de la Segunda tabla de mapeo

| Índice de función | Habilitar<br>indicación (un bit) | Número del bus<br>de eVF (ocho bits) | Número de función<br>del dispositivo de<br>eVF (ocho bits) | Indicación PF |

|-------------------|----------------------------------|--------------------------------------|------------------------------------------------------------|---------------|

|                   |                                  |                                      |                                                            |               |

De este modo, la relación de mapeo entre la identificación en el dominio PCIe correspondiente al host 210 y la identificación en el dominio PCIe correspondiente al dispositivo de E/S 230 se almacena de una manera de tabla de mapeo. En comparación con la técnica anterior, esta solución puede reducir el espacio de almacenamiento que ocupa el módulo de mapeo 225 y la complejidad, así como también ahorrar un recurso de almacenamiento del sistema. Además, se enumeran las BDF de todas las funciones y los números se almacenam en la tabla de mapeo. En comparación con el almacenamiento de una BDF de 16 bits, el espacio de almacenamiento que ocupa el módulo de mapeo 225 puede reducirse adicionalmente.

Opcionalmente, en esta realización de la presente invención, el contenido de la configuración PCle del dispositivo terminal 230, almacenado en el mEP 226, puede ser específicamente un espacio de configuración PCle del dispositivo terminal 230 o puede ser un contenido de configuración parcial en un espacio de configuración PCle del dispositivo terminal 230. Por ejemplo, todos los M<sub>3</sub> mEP 226 pueden ser específicamente tablas de mapeo. De manera alternativa, algunos de los M<sub>3</sub> mEP 226 pueden ser específicamente tablas de mapeo. Esto no se limita a esta realización de la presente invención.

En una realización opcional, un primer mEP en los  $M_3$  mEP 226 es específicamente una tercera tabla de mapeo. La tercera tabla de mapeo se usa para almacenar una dirección de registro de dirección de base (en inglés, Base Address Register - BAR) y un tamaño de BAR de una función virtual de un primer dispositivo de E/S en los  $M_1$  dispositivos de E/S. El primer mEP está configurado para almacenar contenido de configuración del primer dispositivo de E/S.

La Tabla 3 muestra una posible implementación de una tercera tabla de mapeo. La tercera tabla de mapeo incluye un índice de mEP y una dirección BAR y un tamaño de BAR que corresponden al índice de mEP. Opcionalmente, cada mEP puede incluir seis BAR. Sin embargo; esto no se limita a esta realización de la presente invención.

Tabla 3: Posible implementación de la Tercera tabla de mapeo

| Índice de mEP | BAR0 de VF (32<br>bits) | <br>BAR5 de VF (32<br>bits) |

|---------------|-------------------------|-----------------------------|

|               |                         |                             |

En este caso, el módulo de mapeo 225 puede implementar el mapeo desde las direcciones en el dominio PCIe del

host 210 a las direcciones en el dominio PCle del dispositivo de E/S 230 en referencia a una tercera y la primera tabla de mapeo. Sin embargo, esto no se limita a esta realización de la presente invención.

De este modo, la información de dirección de la función virtual del dispositivo de E/S se almacena en forma de tabla de mapeo. En comparación con la técnica anterior, esta solución puede reducir el espacio de almacenamiento que ocupa el mEP y ahorrar un recurso de almacenamiento del sistema.

5

10

15

20

25

30

35

40

45

50

55

Debe entenderse que los ejemplos de la Tabla 1 a la Tabla 3 pretenden ayudar a un experto en la materia a entender mejor esta realización de la presente invención, pero no limitan el alcance de esta realización de la presente invención. Aparentemente, un experto en la materia puede llevar a cabo varias modificaciones o cambios en función de los ejemplos proporcionados de la Tabla 1 a la Tabla 3. Las modificaciones o los cambios también se enmarcan en el alcance de esta realización de la presente invención.

Opcionalmente, en esta realización de la presente invención, la primera tabla de mapeo, la segunda tabla de mapeo o la tercera tabla de mapeo pueden configurarse en conjunto mediante el aparato de procesamiento interno 223 en el dispositivo de conmutación 220 y el host 210. Por ejemplo, un aparato de procesamiento interno 223 puede obtener, por medio de una enumeración de dispositivos o de otra manera, información sobre un dispositivo físico conectado al dispositivo de conmutación 220 mediante el uso de los M<sub>1</sub> puertos PCIe aguas abajo 222 y configurar la tabla de mapeo en función de la información obtenida, por ejemplo, almacenar la información sobre el dispositivo físico en la tabla de mapeo. El host 210 puede almacenar, en la tabla de mapeo, la información de configuración del dominio PCIe correspondiente al host 210, obtenida en un proceso de enumeración de dispositivos (es decir, descubriendo un dispositivo físico y/o un módulo funcional conectado al host 210) o de otra manera. Sin embargo, esto no se limita a esta realización de la presente invención.

Además, los N<sub>3</sub> vEP 224, el módulo de mapeo 225 y los M<sub>3</sub> mEP 226 pueden implementarse mediante un registro o por medio de un registro y un circuito de hardware, y son simples de usar sin implementar un árbol de estructura PCle, mediante el uso de un código de software. Además, se evita un proceso de almacenamiento y reenvío en un proceso de implementación de software mediante el uso de una operación doble de escritura de configuración de un dispositivo virtual y un dispositivo real.

En esta realización de la presente invención, el sistema PCIe 200 puede soportar múltiples modos de operación. Los múltiples modos de operación pueden incluir al menos uno de los módulos siguientes: un modo directo de VP, un modo compartido de VF, un modo compartido de PF o un modo de transmisión transparente de EP. El modo directo de VF y el modo compartido de VF puede aplicarse a un dispositivo de E/S que soporte la SR-IOV; el modo de compartido de PF puede aplicarse a un dispositivo de E/S que soporta funciones múltiples; el modo de transmisión transparente de EP puede aplicarse a un dispositivo de E/S de función única.

Específicamente, en el modo directo de VF, los N<sub>3</sub> vEP 224 se configuran para virtualizar funciones virtuales de los M<sub>1</sub> dispositivos de E/S 230. Por ejemplo, como se muestra en la FIG. 4, un sistema PCIe puede incluir: dos hosts: un host 0 y un host 1; un conmutador PCIe; dos dispositivos terminales: un EP 0 y un EP 1; y un dispositivo de conmutación. El dispositivo de conmutación incluye: dos puertos PCIe aguas arriba respectivamente conectados al host 0 y al host 1, dos puertos PCIe aguas abajo conectados respectivamente al EP 0 y al EP 1 mediante el uso del conmutador PCIe, espacios de configuración PCIe DP\_CFG 0 y DP\_CFG 1 respectivamente, correspondientes a los puertos PCIe aguas abajo, un aparato de procesamiento interno, un módulo de mapeo, un vEP 0 y un vEP 1. El vEP 0 se conecta a un puerto PCIe aguas arriba mediante el uso de DP\_CFG 0 y el vEP 1 se conecta al otro puerto PCIe aguas arriba mediante el uso de DP\_CFG 1. Tanto el EP 0 como el EP 1 presentan una PF: una PF 0; y una VF: una VF 0 correspondiente a la PF 0. En este caso, el vEP 0 puede configurarse para virtualizar la VF 0 del EP 0, de modo tal que la VF 0 sea usada por el host 0. Específicamente, el vEP 0 puede ser una combinación de espacios de configuración PCIe de la PF 0 y la VF 0 del EP 0. El vEP 1 puede configurarse para virtualizar la VF 0 del EP 0, de modo tal que la VF 0 sea usada por el host 1. Específicamente, el vEP 1 puede ser una combinación de espacios de configuración PCIe de la PF 0 y la VF 0 del EP 1. Sin embargo, esto no se limita a esta realización de la presente invención.

Opcionalmente, en el modo directo de VF, los lectores de PF de los M<sub>1</sub> dispositivos de E/S 230 pueden cargarse a través del BMC de administración y los lectores de VF de los M<sub>1</sub> dispositivos de E/S 230 pueden cargarse a través de los procesadores de los N<sub>1</sub> hosts 210. Específicamente, cada host puede cargar un lector de VF de un dispositivo de E/S, virtualizada por el vEP que es enumerado por el host.

Sin embargo; esto no se limita a esta realización de la presente invención.

En el modo compartido de VF, los  $N_3$  vEP 224 se configuran para virtualizar funciones físicas y virtuales de los  $M_1$  dispositivos de E/S 230. En este caso, en las funciones virtualizadas por el vEP 224, solo la VF puede usarse como un puerto de servicio por parte del host 210, y la PF no puede usarse como tal por el host 210. Opcionalmente, el vEP 224 puede ser específicamente un espacio de configuración PCle de una PF virtualizada. El espacio de configuración PCle puede incluir un espacio de capacidad SR-IOV. Sin embargo, esto no se limita a esta realización de la presente invención. Por ejemplo, como se muestra en la FIG. 5, el sistema PCle puede incluir: dos 'hosts: un host 0 y un host 1; un conmutador PCle; un dispositivo terminal: un EP 0; y un dispositivo de conmutación. El dispositivo de

conmutación incluye: dos puertos PCIe aguas arriba respectivamente conectados al host 0 y al host 1, un puerto PCIe aguas abajo conectado al EP 0 mediante el uso del conmutador PCIe, dos espacios de configuración PCIe DP\_CFG 0 y DP\_CFG 1 correspondientes al puerto PCIe aguas abajo, un aparato de procesamiento interno, un módulo de mapeo, un vEP 0 y un vEP 1. El EP 0 presenta una función física (en inglés, Physical Function - PF): una PF 0 y dos funciones virtuales (en inglés, Virtual Functions - VF): una VF 0 y una VF 1 correspondientes a la PF 0. En este caso, el vEP 0 y el vEP 1 pueden ser específicamente un espacio de configuración PCIe de la PF 0 que transporta un espacio de capacidad SR-IOV, a fin de virtualizar respectivamente la VF 0 y la VF 1. Opcionalmente, en el modo compartido de VF, los lectores de PF de los M1 dispositivos de E/S 230 pueden cargarse a través del BMC de administración. A diferencia del modo directo de VF, los procesadores de los N1 hosts 210 además necesitan cargar lectores de PF correspondientes a los N3 vEP 224 para habilitar una VF virtualizada por los N3 vEP 224, de modo tal que los N1 hosts 210 puedan usar normalmente la VF.

5

10

15

20

25

30

35

40

45

50

55

60

En el modo compartido de PF, los N<sub>3</sub> vEP 224 se pueden configurar para virtualizar funciones físicas de los M<sub>1</sub> dispositivos de E/S 230. En este caso, opcionalmente, los M<sub>1</sub> dispositivos de E/S 230 pueden presentar solo una PF v ninguna VF, es decir, la PF en los M<sub>1</sub> dispositivos de E/S no presentan ninguna VF correspondiente a la PF. Opcionalmente, el vEP 224 puede ser específicamente un espacio de configuración PCIe de una PF virtualizada por el vEP 224 y el espacio de configuración PCIe puede no incluir un espacio de capacidad SR-IOV. Por ejemplo, como se muestra en la FIG. 6, el sistema PCIe puede incluir: dos hosts: un host 0 y un host 1; un conmutador PCIe; un dispositivo terminal: un EP 0; y un dispositivo de conmutación. El dispositivo de conmutación incluye: dos puertos PCIe aguas arriba respectivamente conectados al host 0 y al host 1, un puerto PCIe aguas abajo conectado al EP 0 mediante el uso del conmutador PCIe, dos espacios de configuración PCIe DP\_CFG 0 y DP\_CFG 1 correspondientes al puerto PCIe aguas abajo, un aparato de procesamiento interno, un módulo de mapeo, un vEP 0 y un vEP 1. El EP 0 presenta dos PF: una PF 0 y una PF 1, y no presenta ninguna VF. En este caso, el vEP 0 puede configurarse para virtualizar la PF 0, de modo tal que la PF 0 es usada por el host 1. El vEP 1 puede configurarse para virtualizar la PF 1, de modo tal que la PF 1 sea usada por el host 2. Sin embargo, esto no se limita a esta realización de la presente invención. Opcionalmente, en el modo compartido de PF, los lectores de PF de los M₁ dispositivos de E/S 230 pueden cargarse a través de los procesadores de los N<sub>1</sub> hosts 210. Específicamente, un procesador de cada host 210 puede cargar un lector de un PF virtualizada por un vEP enumerada por el procesador.

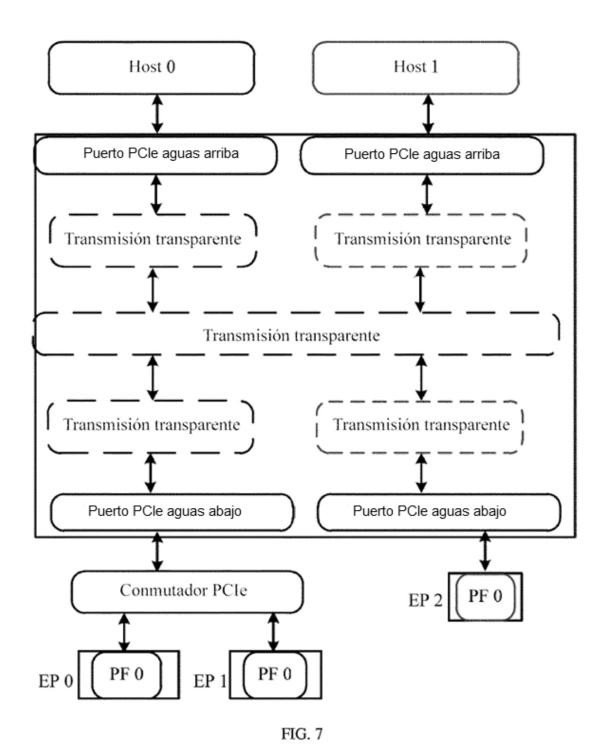

En el modo de transmisión transparente EP, el dispositivo de conmutación 220 puede transmitir de manera transparente la información transmitida entre los M₁ dispositivos de E/S 230 y los N₁ hosts 210 que están conectados al dispositivo de conmutación 220. En este caso, los M₁ dispositivos de E/S 230 pueden ser un dispositivo de función única, es decir, presentar solo una PF y ninguna VF. Por ejemplo, como se muestra en la FIG. 7, un sistema PCIe puede incluir: dos hosts: un host 0 y un host 1; un conmutador PCIe; tres dispositivos terminales: un EP 0, un EP 1 y un EP 2; y un dispositivo de conmutación. El dispositivo de conmutación incluye: dos puertos PCIe aguas arriba respectivamente conectados al host 0 y el host 1, un puerto PCIe aguas abajo conectado al EP 0 y el EP 1 mediante el uso del conmutador PCIe, y un puerto PCIe aguas abajo directamente conectado al EP 2. Tanto el EP 0, como el EP 1 y el EP 2 solo presentan una PF: una PF 0. El dispositivo de conmutación puede no almacenar ningún espacio de configuración PCIe de cualquier puerto PCIe aguas abajo. En este caso, el host 0 puede usar las PF del EP 0 y el EP 1. El host 1 puede usar una PF del EP 2. Los módulos AU en el dispositivo de conmutación ejecutan una transmisión transparente y no pueden implementar una función de compartir un mismo EP entre hosts múltiples. Opcionalmente, en el modo de transmisión transparente de EP, no es necesario cargar un lector de VF y un lector de PF.

Opcionalmente, el sistema PCle 200 puede operar siempre en un modo particular de los múltiples modos de operación anteriores, o puede conmutarse entre los múltiples modos de operación anteriores. Opcionalmente, el sistema PCle 200 puede soportar incluso otro modo de operación. Esto no se limita a esta realización de la presente invención.

Debe entenderse que los ejemplos de la FIG. 4 a la FIG. 7 pretenden ayudar a un experto en la materia a entender mejor esta realización de la presente invención, pero no limitan el alcance de esta realización de la presente invención. Aparentemente, un experto en la materia puede llevar a cabo varias modificaciones o cambios en función de los ejemplos proporcionados de la FIG. 4 a la FIG. 7. Las modificaciones o los cambios también se enmarcan en el alcance de esta realización de la presente invención.

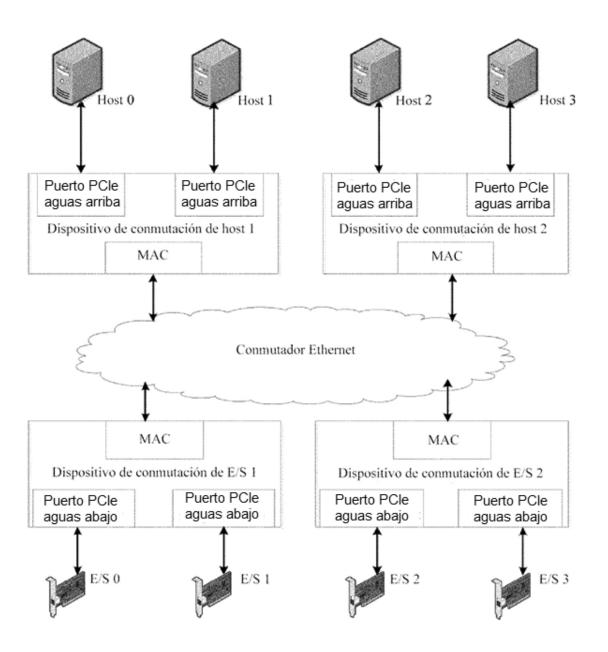

Además, debe entenderse que todos los ejemplos se describen mediante el uso de un ejemplo en el que el sistema PCIe incluye un dispositivo de conmutación. Opcionalmente, el sistema PCIe puede incluir múltiples dispositivos de conmutación. Como se muestra en la FIG. 8, el sistema PCIe 200 incluye dos dispositivos de conmutación 220: un dispositivo de conmutación 1 y un dispositivo de conmutación 2. Cada dispositivo de conmutación puede conectarse a dos hosts y a dos dispositivos de E/S. Específicamente, el dispositivo de conmutación 1 puede estar conectado por separado a un host 0, a un host 1, un ES 0 y un ES 1. El dispositivo de conmutación 2 se conecta por separado a un host 2, a un host 3, un ES 2 y un ES 3. De este modo, si un dispositivo de conmutación presenta una excepción, por ejemplo, el dispositivo de conmutación 1 conectado al ES 0 y el ES 1 presenta una excepción, un procesamiento de excepción, por ejemplo, una operación de restablecimiento o una interrupción de servicio relacionada pueden ejecutarse en función de una situación real. Si el dispositivo de conmutación 2 conectado al ES 2 y el ES 3 se ejecuta normalmente, el host 2 y el host 3 aún podrán ejecutarse de manera normal, mejorando así la confiabilidad y la estabilidad del sistema.

Además, debe entenderse que todas las realizaciones anteriores se describen mediante el uso de un ejemplo en el

que el dispositivo de conmutación 220 es específicamente un dispositivo físico. Opcionalmente, el dispositivo de conmutación 220 puede ser específicamente múltiples dispositivos físicos. Por ejemplo, como se muestra en la FIG. 8 y la FIG. 9, el dispositivo de conmutación 220 puede estar en una forma de chip AB, es decir, el dispositivo de conmutación 220 puede ser específicamente un dispositivo de conmutación 220a y un dispositivo de conmutación de E/S 220b. El dispositivo de conmutación de host 220a y el dispositivo de conmutación de E/S 220b puede conectarse mediante el uso de una interfaz Ethernet o una interfaz conmutada de otro tipo. En una realización opcional, el dispositivo de conmutación de host 220a puede incluir: N2 puertos PCIe aguas arriba 221 y al menos una primera interfaz conmutada que se configura para conectar el dispositivo de conmutación de E/S 220b. El dispositivo de conmutación de E/S 220b puede incluir: al menos una segunda interfaz conmutada para conectarse al dispositivo de conmutación de host 220a, un aparato de procesamiento interno 223 y M2 puertos PCIe aguas abajo 222. Opcionalmente, como se muestra en la FIG. 8, la al menos una interfaz conmutada y la al menos una segunda interfaz conmutada pueden conectarse directamente. De manera alternativa, como se muestra en la FIG. 9, la al menos una primera interfaz conmutada y la al menos una segunda interfaz conmutada pueden conectarse mediante el uso de un conmutador Ethernet o un dispositivo de conmutación interna de otro tipo. El dispositivo de conmutación interna puede proporcionar múltiples interfaces conmutadas configuradas para conectar el dispositivo de conmutación de host y el dispositivo de conmutación de E/S. En este caso, la al menos una primera interfaz conmutada puede configurarse para conectarse al dispositivo de conmutación interna, y la al menos una segunda interfaz conmutada puede configurarse para conectarse al dispositivo de conmutación interna. Esto no se limita a esta realización de la presente invención.

5

10

15

30

35

55

60

En otra realización opcional, el aparato de procesamiento interno 223 puede incluir un aparato de procesamiento (es decir, un primer aparato de procesamiento) ubicado en el dispositivo de conmutación del host 220a y un aparato de procesamiento (es decir, un segundo aparato de procesamiento) ubicado en el dispositivo de conmutación de E/S 220b. En este caso, el primer aparato de procesamiento interno puede conectarse de manera separada a los múltiples puertos PCIe aguas arriba y la al menos una primera interfaz conmutada mediante el uso de una línea de conectarse de manera separada al, al menos un, puerto PCIe aguas abajo y la al menos una segunda interfaz conmutada mediante el uso de una línea de conexión interna del dispositivo de conmutación de E/S. Sin embargo, esto no se limita a esta realización de la presente invención.

En este caso, opcionalmente, el primer aparato de procesamiento interno se configura para: recibir, mediante el uso de los múltiples puertos PCle aguas arriba, un primer paquete de datos desde el al menos un host; procesar el primer paquete de datos para obtener un primer paquete de datos en el que se ejecuta el primer procesamiento; y transmitir al dispositivo de conmutación interna, mediante el uso de la al menos una primera interfaz conmutada, el primer paquete de datos en el que se ejecuta el primer procesamiento.